超高速信号采集录波设计方案

主变故障录波技术规范书(220kV升压站)(DOC)

国电赤峰西大梁风电场49.5MW工程配套设备招标文件第二卷技术部分(第一包中的主变压器故障录波装置)招标编号:GDCX-FJZB10-004分包号:GDCX-FJZB10-004-01-3内蒙古电力勘测设计院编制2009年12月呼和浩特目录1 总则 (1)2 技术要求 (1)3 设备规范 (9)4采购设备需求及供货范围 (9)5 技术服务 (10)6 需方工作 (11)7 工作安排 (12)8 备品备件及专用工具 (12)9 质量保证和试验 (13)10 包装、运输和贮存 (15)附录A:主要名词解释 (17)附录B:变压器故障录波装置的输入模拟量和开关量 (17)1 总则1.1 本设备技术规范书适用于国电赤峰西大梁风电场49.5MW工程主变压器故障录波装置的功能设计、结构、性能、安装和试验等方面的技术要求。

1.2 本设备技术规范书提出的是最低限度的技术要求,并未对一切技术细节作出规定,也未充分引述有关标准和规范的条文,供方应提供符合本规范书和工业标准的优质产品。

1.3 如果供方没有以书面形式对本规范书的条文提出异议,则意味着供方提供的设备(或系统)完全符合本规范书的要求,如有异议,不管是多么微小,均应在报价书中以“对规范书的意见和同规范书的差异”为标题的专门章节中加以详细说明。

1.4 本设备技术规范书使用的标准如遇与供方所执行的标准不一致时,按较高标准执行。

1.5 本设备技术规范书经供、需双方确认后作为订货合同的技术附件,与合同正文具有同等法律效力。

1.6 本设备技术规范书未尽事宜,由供、需双方协商解决。

2 技术要求2.1 应遵循的主要标准下列标准所包含的条文,通过在本标准中引用而构成为本标准的条文。

本标准出版时,所示版本均为有效。

有新标准颁布时,执行新标准。

DL/T 5136-2001 《火力发电厂、变电所二次接线设计技术规程》DL/T 5004-2004 《电力工程直流系统设计技术规定》DL/T 873-2004 《微机型发电机变压器组动态记录装置技术条件》DL/T553-1994 《220~500kV电力系统故障动态记录技术准则》DL478-1992 《静态继电保护及安全自动装置通用技术条件》DL/T 663-1999 《220~500kV电力系统故障动态记录检验准则》GB/T14285-2006 《继电保护和安全自动装置技术规程》GB50065-1994 《交流电气装置的接地设计规范》2.2 环境条件a)本条的目的在于强调设备应遵照的环境条件要求,因为这会影响设备的寿命、结构和运行可靠性。

一种新型多路同步数据采集卡的设计与实现

Abstract : This paper presents t he principle and t he realization met hod of a new multiplex channel synchronization data acquisi2 tion board which is used for fault wave2recording device. This da2 ta acquisition board is triggered by GPS , can achieve synchro2 sampling of 24 digital input . The rate of sampling can achieve 250ksps per channel , and t he precision of sampling is 16 bit . Moreover , t his data acquisition board can easily administer t he working met hod of sampling channels in accordance wit h t he dif2 ference of wave2recording objects by t he hardware ISP ( In Sys2 tem Programming) technology of FP GA. The PCI bus ensures its real2time and universal character. Key words : fault wave2recording device ; PCI Bus ; FP GA ; GPS ; synchro2sampling ; ISP

综合论述变电站继电保护自动化系统

1概 述 从 技术 上说, 实 现 电网继 电保 护综 合 自动 化系 统 的条件 已经成 熟, 无论 是变 电站 客 户机 对 保 护信 息 的搜 集 、 信息 的 网络 传 输 还是 调 度端 服 务 器对

E S 系统 共 享数 据 的读 取 、故 障及 稳 定分 析 计算 , 可 以得 到解 决 。主 要 M 都 的 实施 难 度 在 于 此 系 统 需 要 综 合 继 电 保 护 、 调 度 、 方 式 、 远 动 、 通 信 以 及变 电站 综合 自动化 等 各个专 业 的技术 , 并且 涉及 到控 制运 行设 备, 要很 多 需 专 业人 员 的配 合, 目前条 件 而言 , 以难 实 现 继 电保护 的 自适 应 。 就 还 为 了保 证 电力系 统 的安全稳 定运 行, 必须 提 高继 电保护 的正 确动 作率 , 更 好地 满足 电力 系统 安全 运行 的要 求 。继 电保 护综 合 自动化 系统 加 强 了继 电保 护 的效 能和可 靠性 , 保证 电网安 全 稳定 运行 起 到 了重大 作 用 继 电保护 工 对 作技 术知 识密集 , 责任心 和 技术水 平要 求 高, 我们只 有 深入 细致 地研 究本 网 的 具体 情况, 认真 细致 地对 待 每一 项工 作, 遵守 规程 、完 善 图纸, 努力 掌握 微 机 保护 的硬件 电路构 成, 软件 实现 逻辑 功 能, 练 掌握 保护 的 一般 原理 、规 律, 熟 逐 步积 累经 验, 进一 步摸 清保 护工 作 的主要 问题 , 能有 针对 性地 采取 措施 解 才 决 存 在 的 问题 。 2系统 构 成 从 电网 的角度分 析 电网继 电保 护综 合 自动化 系 统获取 信 息的途 径 。电网 的结 构和参数 , 以从 调度 中心获得 : 次设备 的运行 状态 及输送 潮流 , 以通 可 一 可 过 E S 系统 实 时获得 : M 保护 装置 的投 退信 息, 由于必 须通 过调 度下 令 , 由现场 执行 , 因此 可 以从 调度 管理 系统 获得 , 并从 变 电站 监控 系统 得 到执行 情 况 的验 证: 保护 装置 故障及 异 常, 以从 微机 保护 装 置获得 : 可 电网故 障信 息, 以从微 可 机保 护及微 机 故障录 波器 获得 。通过 以上 分析 , 以看 出, 可 实现 变 电站继 电保 护综 合 自动 化 系 统 的信 息 资源 是充 分 的 。 3功 能分 析 3 1实现 对各种 复 杂故障 的准 确故 障定位 目前 的保 护和 故 障录波 器 的故 . 障测距 算法 , 以崦岈 站 50 V 行波 测 装置 采用 X 一 2 0k E c 1输 电线 路行 波测 距 装 置为 例

故障录波、行波测距及故障信息子站三合一设计方案

随着电力系统的不断发展 , 故 障录波器、 行 波 测 距 及 故 障信

息 处 理 系 统 在 电网 中得 到 了 广 泛 的应 用 ,故 障 录波 数 据 已成 为

分为三部分 : 行 波测 距 部 分 主 要 是 高 速 采 集 故 障 时 的行 波 信 息 , 故 障录 波 部 分 主 要 是 采 集 故 障 时 的 故 障 波 形 信 息 ,信 息 子 站 部 分 主要 是 获 得 变 电站 内各 类 保 护 的 信 息 ,这 三 类 信 息 采 集 后 统

si t u a t i on o f gr i d. Thi s pa per pr es e n t s a met h od o f i n t egr a t i n g t h e t h r e e s y s t ems, a nd i n t h i s wa y, t h e n e w met h od ac hi e ve s da t a s h ar i n g, r e duc e s c os t o f h ar dwa r e , an d a fo r ds f a l i t i es f or a na l yz i n g p ower f a u l t . Ke y wor ds : f a ul t r ec or der , t r a v el l i n g wa v e l o ca t i o n, f au l t I n or f mat i o n s ubs t a t i on . de s i gn . s ch e m e, DPU

交给 D P U分 析 处 理 。

启动信 号 一

撇

2 功 能 实现

充, 如 故 障 录 波 器 和 故 障信 息 处 理 系 统 可 利 用 行 波 测 距 的结 果 ,

基于嵌入式系统的一体化故障录波器

基于嵌入式系统的一体化故障录波器侯学勇;王亮;王爱华;马稷忠【摘要】为实现传统变电站向数字化变电站的平稳快速过渡,介绍了一种基于嵌入式系统的一体化故障录波器实现方案,该方案基于嵌入式Linux操作系统,使用基于PowerPC和FPGA管理板及DSP和FPGA的采样板进行开发,辅以高效串行总线实现内部数据交换,采用无旋转部件的大容量电子盘作为存储介质.设计的一体化故障录波器既可以用于常规变电站,又可以用于数字化变电站.%To implement the translation from traditional substation to digital substation rapidly and placidly, an application scheme of integrative fault recorder based on embedded system was described. The scheme which was based on embedded Linux system used PowerPC and FPGA based manage board,and DSP and FPGA based sample board,with efficient serial bus to implement internal data exchange. The large volume of electronic dish without rotating parts was used as storage media. The fault recorder can be used both in conventional substation and digital substation.【期刊名称】《仪表技术与传感器》【年(卷),期】2011(000)012【总页数】3页(P40-42)【关键词】故障录波器;DSP;嵌入式Linux系统;一体化;数字化【作者】侯学勇;王亮;王爱华;马稷忠【作者单位】南京南瑞继保电气有限公司,江苏南京211111;南京南瑞继保电气有限公司,江苏南京211111;辽宁营口供电公司,辽宁营口115000;辽宁营口供电公司,辽宁营口115000【正文语种】中文【中图分类】TM760 引言电力故障录波器是一种能自动记录电力系统发生故障或振荡时系统各种行为的装置,它可以记录因各种设备故障、系统振荡、频率或电压崩溃等大扰动引起的系统电压、电流、有功、无功及系统频率及各种设备动作的全过程[1]。

PCS-996_故障录波装置_说明书_国内中文_国内标准版_R1.04_(ZL_GZLB5118.1404)

为增强或修改现有功能,装置的软硬件均可能升级,请确认此版本使用手册和您购买的产品相兼容。

警告!

电气设备在运行时,这些装置的某些部件可能带有高压。不正确的操作可能导致严重的人身伤害或设备损坏。

只有具备资质的合格专业工作人员才允许对装置或在装置临近工作。工作人员需熟知本手册中所提到的注意事项和工作流程,以及安全规定。

工作温度范围-20℃ຫໍສະໝຸດ +55℃贮存温度范围

-40℃~+70℃

运输温度范围

-40°C~+70°C

相对湿度

5%~95%,设备内部不凝露,不结冰

2

2

波特率

4.8kbit/s、9.6kbit/s、19.2kbit/s、38.4kbit/s、57.6kbit/s、115.2kbit/s

通信规约

DL/T 667-1999(idtIEC 60870-5-103:1997)

250Vdc

开触点耐压

1000V RMS,1分钟

连续载流能力

5A@380Vac

5A@250Vdc

冲击过流能力

6A@3s

15A@0.5s

30A@0.2s

动作时间

<8ms

返回时间

<5ms

断弧能力(L/R=40ms)

0.6A@48Vdc

0.2A@110Vdc

0.1A@220Vdc

2

输入

准确度

交流额定电压(Un= V)

连接电缆

仔细处理连接的电缆避免施加过大的外力。

版权声明

版本: R1.04

P/N: ZL_GZLB5118.1404

Copyright © 2013NR南京南瑞继保电气有限公司版权所有

输电线路行波测距

行波信号的测量

• 保护与测距利用信号的带宽

– 常规电流、阻抗等保护: 0-1KHz (50Hz) – 阻抗测距装置:0-1KHz(50Hz) – 行波保护: 0-2KHz – 行波测距:0-300KHz,距离分辨率500m

• 电容式电压互感器(CVT)不能传变电压行波,早期行波测 距使用电容分压(耦合器)测量电压行波,安装复杂,需 要额外投资。 • 光PT、CT离商业化应用有距离。

• A型测距装置

–高速拍照,记录故障产生的电压行波,识别电 压脉冲故障点及母线间往返一次的时间计算故障 距离。 –装置复杂,可靠性差。 –50年代试制,没有推广应用。

• B型测距装置

–线路对端的装置在接收到故障电压脉冲后向本 端发送信号,比较本端接收到故障脉冲及对侧信 号的时间差,计算故障距离。 –可靠性较好,但需要常备通信通道,构成复杂。 –在美国、日本等个别国家安装使用,没有大量 地推广应用。

同母线上其他线路反射波的影响

• 故障行波穿过母线透射到其他健全线路上,行波在 健康线路对端被反射回来,影响故障点反射脉冲的 识别。 • 当母线上运行的线路较多时(如4条线路时),母 线行波阻抗接近零,故障行波在其他健全线路上的 透射很小,可以认为母线呈短路状态,可以不考虑 其他线路的影响。

健康线路Ⅰ 健康线路Ⅱ 健康线路Ⅰ 健康线路Ⅱ

中 心 处 理 单 元

DI/DO

人机界面 RS-232

后台工业 PC机

在XC-11行波测距装置得基础上研制成功

主要技术指标与特点

• • • • 测距精度小于1公里 最多监视8条线路 装置本身存储96次故障记录 采用图形式液晶显示器(LCD),显示装置定值输入 菜单与键入值、装置运行状态信息等。 • 使用一台工业PC机作为后台分析机,读取、分析、 长期保存故障记录 • 与有关变电站的装置通信,交换故障行波到达时间, 计算故障距离。

配网架空线行波故障测距装置设计

配网架空线行波故障测距装置设计李传健;郑文杰;钟澎;朱金超;蒙红发【摘要】The accurate fault location of distribution network over head transmission line is important measure to improve the safety operation of the electricnetwork.Whenever a fault occur since the transmissionline,the quick and exact fault location will not only reduce the manual work of the line inspectors,but also facilitate removal of fault and power restoration quickly for cutting down on economic loss due to the failure.In general the research addresses an important field that has both safety and economic implications.But in practical application the accuracy of system is decreased by the reasons of unsynchronized sampling and low sampling speed which cause the bigger location error. This thesis aims at designing the system schema of the high-speed dataacquisitiondevice for the fault locator, realizing high-speed, data acquisitionandlarge capacity data storage, analyzing the errorsource and difference between GPS system and oven controlled crystal oscillator ,providing the calibration algorithm of the second pulse of GPS system,anddeveloping the power supply for fault locator which can provide the referencefor finding fault time,judging fault type and calculating fault point distance.%农村配网长距离架空线路发生故障后,若能迅速、准确的进行故障定位,可以减少巡线任务,能够快速确定故障、恢复供电,减少和避免因配电线路长时间故障引起的损失。

高精度故障录波与行波测距装置

基于电流行波和小波变换的 故障测距方法

测距所利用信号的带宽

常规电流、阻抗等保护: 0-1KHz (50Hz) 阻抗测距装置:0-1KHz(50Hz) 行波测距:0-300KHz,距离误差率500m

电容式电压互感器(CVT)不能传变电压行波

基于电流行波和小波变换的 故障测距方法

行波法原理

利用行波在故障点和测量点之间传播的时间差来测量 故障距离

行波法优点

行波法不受故障点过渡电阻、线路结构等因素的影响, 测距精度高,适用范围广。

最早提出的电压行波测距法原理上有缺陷,且没有解 决好行波信号的测量、超高速记录、分析等问题。直到二 十世纪九十年代,行波测距技术一直没有获得实际的推广 应用。

在世界上首次提出利用普通的电流互感器测量 电流行波 并通过数字仿真分析及对实际CT的测试证明 利用CT测量电流行波优点

具有简单、易于实现的优点。 不需要额外投资 由于母线有较大的分布电容,母线处感受到电压行 波波头幅值较小且上升速度慢,而电流行波波头却 有较大的幅值且上升速度很快,利用故障电流行波 检测灵敏度高。

基于电流行波和小波变换的 故障测距方法

利用电流行波的输电线路故障测距技术特点

1)仅使用电流行波 2)采用高速数据采集技术 3)采用单片机技术 4)采用GPS技术 5)采用小波变换技术

基于电流行波和小波变换的 故障测距方法

利用电流行波的输电线路故障测距原理

1)单端行波测距原理 2)两端电气量行波测距原理 3)利用重合闸信号的行波测距原理

距 仪

故障点距S变电站距离:

XS

L

1 2

(TR

TS ) v

故障点距R变电站距离:

XR

哈尔滨博瑞特GMCS(录波)说明书

GMCS发变组故障录波系统(录波分册)用户手册哈尔滨博瑞特电子有限公司目录第一章概述 (1)§1-1 引言 (1)§1-2 主要技术参数 (1)§1-3 主要特点 (1)§1-4 主要功能 (3)第二章系统构成 (5)§2-1 系统功能框图 (5)§2-2 屏体布置图 (5)§2-3 基本原理 (6)第三章系统安装 (8)§3-1 WINDOWS NT安装 (8)§3-2 上位机软件安装 (8)§3-3 下位机软件安装 (9)第四章软件使用说明 (10)4.1主窗口 (10)4.2参数设置 (14)4.3通道修正 (21)4.4数据分析 (24)第五章下位机使用说明 (36)GMCS 概述第一章:概述§1-1 引言GMCS发电机故障录波系统,采用高档工业控制计算机,配以高速模拟量采集卡,采样率可以达到5000点/秒,上、下位机之间基于以太网进行数据传输,传输速率未10Mbps。

整体结构采用模块和层架式结构,充分考虑用户的使用和维护等诸多因素,大大方便了现场的运行和维护。

构成系统的硬件都采用了大量的最新技术,保证系统的稳定和测量的精度;系统软件在结构上严格遵循现代软件工程理论与方法,在充分进行系统分析的基础上,划分成合理的功能模块,规定了严格的接口参数,使系统可以在可靠的前提下高效地运行。

系统还采用了精确的数字滤波,使模拟量测量精度得到可靠的保证。

§1-2 主要技术参数通道容量:模拟量96路;开关量192路。

模拟量采样率:5000点/秒.开关量分辨率:1m/s.A/D转换精度:12bit有效值精度:0.2%输入信号范围:交流电压(PT二次侧)0~220V交流电压(无PT)0~900V交流电流0~100A直流电压0~2000V直流电流0~75(mV)录波时间:可调,数据总量<15MBYtes。

基于FIFO存储的高速脱机波形记录系统

基于FIFO存储的高速脱机波形记录系统贺有智;王大正;吴晨;刘福才【摘要】对于一组作用时间短,发生时刻不确定的波形,直接使用PC计算机系统记录难以实现.该波形记录系统通过被动触发的方式以指定的采样周期记录指定时间长度的波形,在实验需要时通过USB总线传至上位机.其中使用CPLD控制和协调数据采集与存储的过程,包括提供多路复用器的选路信号,模数转换器的时钟信号和FIFO写数据时钟与控制信号;最终用户可以通过上位机软件控制EZ-USB芯片以GPIF方式从FIFO中读取数据.【期刊名称】《仪表技术与传感器》【年(卷),期】2014(000)009【总页数】5页(P40-43,47)【关键词】脱机录波;EZ-USB;多路复用;CPLD;FIFO【作者】贺有智;王大正;吴晨;刘福才【作者单位】燕山大学,工业计算机控制工程河北省重点实验室,河北秦皇岛066004;燕山大学,工业计算机控制工程河北省重点实验室,河北秦皇岛066004;燕山大学,工业计算机控制工程河北省重点实验室,河北秦皇岛066004;燕山大学,工业计算机控制工程河北省重点实验室,河北秦皇岛066004【正文语种】中文【中图分类】TM835.20 引言在实验中,经常需要观察一个短暂的波形,如电容、电感放电信号等等,这类波形有作用时间短和发生时刻相对不确定两个共同的特点。

在以往的观察实验中,通常是在PC计算机上使用PCI接口的数据采集卡,利用高级语言程序控制记录,由于高级语言程序运行时的不确定性,并不能准确地记录下所需要的波形,为了保证数据的完整性,只能连续采集并筛选,这样浪费了大量的系统资源,而且计算机的处理能力直接限制采样周期和数据精度[1]。

从实现的角度来分析,PC计算机波形记录系统又有成本高,体积大,在相对恶劣的条件下不能连续工作等缺陷,不利于实际应用。

文中以在2.4 ms的时间内使用FIFO记录8路0~5 V的电压信号为例,设计了数字波形记录系统,其中每路存储1000组12bit精度的数据。

基于PCI总线的发变组故障录波采集系统的设计

输入通道少 , 记录数据量小 , 录波判据简单等特点 , 其采集系统常采用模块化结构设计 。由于模块 内部 般使用 F A H存储器作为故障数据存储介质 , LS 且 大部分元器件集中在一张 P B板上 , C 无机械 转动部 件和多余 的接插件 , 该设计具有可靠性高 、 成本低等 优点 , 泛应 用于 小型 变 电站 的线路 录波 。 广 发 电机变 压 器 组 ( 以下 简 称 发 变 组 ) 统 的运 系

关键词 :故障录波 ; P I C 总线 ; 集 中化 多通道数据 采集 ; D P D / 7 2 0 S ; L T8 3— 04 中图分类 号 :T 7 1 M 6 文献标识 码 :A 文章编号 :10 - 9 (0 6 1-0 70 0 34 7 2 0 ) 704 -4 8

0 引 言

一

行工 况 复杂 , 每周 波采 样点 数 多 , 要 监测 的输 入通 需 道多, 因此其故 障录波 系统 中判据 繁杂 , 要存 储 和 需 传 输 的 数 据 量 大 。 电 力 行 业 最 新 标 准 D / 7 - L T8 3

20 ( 04 微机型发电机变 压器组动态记录装 置技术条 件》 ( 以下简称新标准 ) 的要求 : 模拟量输人 不少 于6 路, 6 开关量不少于 18路 , 2 暂态数据记 录速率 不小 于 24 0点/ ( 8点/ 频 周期 ) 保 存 完 整暂 0 秒 4 工 ,

目前 国内故障录波采集系统设计主要有模块化 和集 中化 两种 方 案 。所 谓模 块 化设 计 是指每 个模 块 般 具有 1 O~2 模拟 通道 、 路 到 十几 路 开关 量 0路 几 通道 、 路或没有频率量输入 , 1 采用 D P为核心完成 S 数据采集 、 故障判断、 数据存储和上传等功能。而集 中化 设 计 ¨一 般 采 用 工 控 机 加 智 能 采 集 板 卡 的 形 J

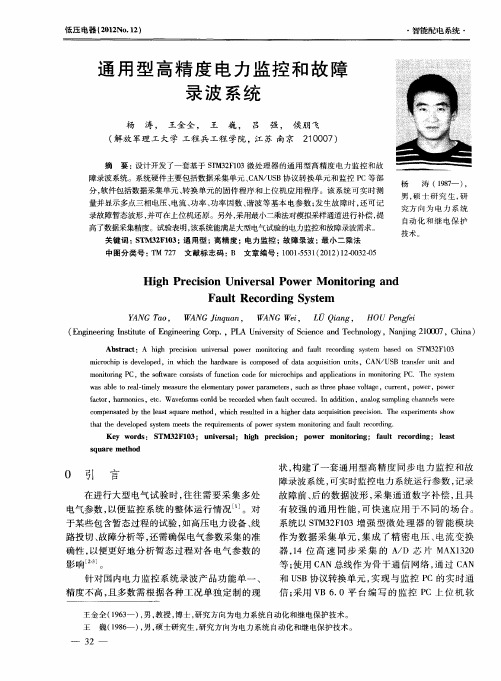

通用型高精度电力监控和故障录波系统

Ke wo d : S y rs TM3 F 0 2 1 3; u i e s l h g p e i o n v r a ; i h r cs n; p we mo i r n i o r n t i g; f u t e o d n o a l r c r i g; l a t e s

精 密互感 器转 换 成 A D转 换器 输 入 范 围内 的0— /

5V的 电压 信 号和 4~ 0m 的电 流信 号 , 2 A 低通 滤 波 器和 采样保 持器 处理 后送 人 A D转 换 器 , / 转换 为微 处 理器 可 以识 别 的数字 信号 。采集 单元 交流

电压 、 电流 的采集 原理框 图如 图 3所示 。

确性 , 以便更 好地 分 析 暂 态过 程 对 各 电气 参 数 的

影 响 。

作 为 数 据 采 集 单 元 , 成 了精 密 电压 、 集 电流 变 换

器 ,4位 高 速 同 步 采 集 的 A D 芯 片 M X 3 0 1 / A 12

等; 使用 C N总线 作 为 骨 干通 信 网络 , 过 C N A 通 A

C N U B协议转换 单元和 电气参数 采集子 单元构 A/S 成, 图 1 如 所示 。采集 子单元 主要 负 责 电气参 数 的

采集 , 每个子 单元 最 多可 配 8路 同步 A D采样 通 /

P E7

交流 D P 流/ A E 电J / D l 0 1 0

~

耋互 感IH 3 -/4压电 o 蓬感-器 置I l1 4电匿獾 怔M3 l压互H运/T l 电 I/前 As 流-电放 D 2 器l l路 H F lf 电 流

采 集 单元 1 采 集单 元 2 采 集单 元 月 采 集 单元 n +l

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3.2.2 采样模块

采样电路是高速采集卡模拟输入端,采样电路的稳定性直接决定了数据的稳 定性和抗干扰能力。通过 FMC 插槽,在每块高速信号采集板上,插放高性能 AD 模块,可进行双通道信号采集,采集信号的性能质量符合指标要求。

3.2.4 通信模块

网口模块设计,网口芯片支持 1000M 以太网,采用 BGA 封装。工作电压分 三种,数字电压、模拟电压和控制电压。

终端接插件采用专用千兆网口座,带变压器和 LED,插入损耗最大为-1.1dB。 设计上对千兆网口进行了 ESD 保护,耐 8KV 静电电压。

3.2.5 电源模块

通过底板提供的+5V,+3.3V。高速采集板上的线性稳压器分出+1.8V,+1.0V, +1.5V,+2.5V。给 DDR 等器件供电。

200MB/s。

3.3.1 磁盘控制器

磁盘控制器主要对磁盘接口的转换。硬盘支持固态硬盘和机械硬盘,协议 SRS,SATA3.0,向下兼容。

设计要求芯片和各插件距离尽量接近,提高抗干扰能力。

3.3.2 硬盘接口设计

硬盘接口采用的是标准 SATA 接口,这种设计易于更换硬盘,体积小,安装 简单。硬盘直接插到底板上不需要转接线,减少物料和安装难度。

3.2 高速采集板设计 高速采集板卡用于数据采集、存储、数传,其系统框图如图 3-4 所示。同时,

又分为主从采集板卡,主要区别为:主采集板卡用于接收处理从采集板卡的 AD

6

数据以及同存储卡联通,主采集板卡同时接收前面板的外部接口。高速采集板由 主控芯片,AD 采样模块、存储模块、通信模块、电源模块、前面板模块组成。

4

图 3-2 sync 要求:SYNC_OUT1、SYNC_OUT2 和 SYNC_OUT3 在底板上 PCB 设计时 需做等长处理。

5

采集板1

EXT_TRG

ADC

ADC_TRG

ZYNQ

TRG_IN TRG_OUT1

采集板2

ADC

ADC_TRG

ZYNQ

TRG_OUT2

时钟 驱动器

采集板3

ADC

ADC_TRG

2 总体方案设计

2.1 机械架构图 本方案设计的超高速信号采集录波器主要由:高速信号采集板、底板、存储

板组成。所有功能板均采用模块化方式,其机械架构示意图如图 2-1 所示,该种 结构具有方便升级、易扩展、易更换硬盘、易安装、易维护等特点。

采采采 集集集 板板板 ③②①

底板

电源 磁盘控制器

存 储 板

3.2.1 主控芯片

高速信号采集板卡的控制芯片为 XILINX zynq-7000 系列 7030,PS 部分包括 两个 ARM9 核,主频 1GHz。PL 逻辑资源包括 1.9M 门,9.3Mb 内存。PL 可用 IO 引脚达到 163 个,PS 可用管脚为 128 个。FPGA 的功能主要有:

1) PS 做数据管理和调度。 2) 数据采集时,将采集数据送至 DDR3 SDRAM 进行缓存,存满一个批次

超高速信号采集录波设计方案

1 关键指标

1) ADC 采样率:最大 100Msps、最小可调至 1Msps 2) ADC 分辨率:16 位 3) 录播容量:硬盘 4TB,存储带宽 200MB/s 4) 通道拓展,单板 2 路,多板扩展到 2 * N 路 5) 含外部时钟、同步信号、外部触发信号输入 6) 对外接口:千兆以太网

7

3.2.3 存储模块

高速采集板卡的存储电路分 2 类:第一类是 FPGA 本身程序存储电路,QSPI FLASH。第二类是数据缓存 DDR3 SDRAM;

DDR3 硬件设计需要注意以下四点: 1) 工作电压 VDD:内核工作电源为 1.5V。 VDDQ:数据总线 I/O 接口电源为 1.5V。 VREF:SSTL_15 电平标准参考电源为 1.5V。 VDDL:DDL 电源为 1.5V。 其中,VDD、VDDQ 、VDDL 是芯片的电源引脚,VREF 是 DDR3 SDRAM 的参考电压。除 CS 和 ODT 引脚外,DDR3 SDRAM 的其他信号都来自 VREF 电 源。这几个电源必须由同一个电源芯片提供,设计采用了 TI 专用 DDR3 电源。 2) 电源滤波 去耦滤波电容必须接,使电源的纹波和噪声减低到最低,去耦滤波电容布局 时需紧靠芯片放置。 3) PCB 布局布线 DDR3 SDRAM 的数据线和地址线必须保持等长,使数据线之间的时序延迟 尽可能小。时钟线越短越好,差分信号还需确保阻抗匹配阻值控制在 100R。

HDD

前面板

图 2-1 机械架构

1

超高速信号采集录波器的总体示意图如图 2-2 所示

图 2-2 总体结构示意图 高速采集板外部输入接口示意图如图 2-3 所示

图 2-3 高速采集板外部输入接口示意图 图中 NET 为网线接口,IN1/IN2 分别为 AD 双通道的输入端,EXT-CLK 为 外部时钟接口,SYNC 为同步时钟接口,EXT-TRG 为外部触发接口。 2.2 系统结构框图 图 2-4 为系统组成框图

ZYNQ

TRG_OUT3

底板

图 3-3 ext-trg 要求:TRG_OUT1、TRG_OUT2 和 TRG_OUT3 在底板上 PCB 设计时需做 等长处理。

3.1.2 电源接口设计

底板接插件电压有三种,分别为 12V 、5V 和 3.3V。12V 电源的电流最大 为 15A,5V 电源的电流最大为 30A,3.3V 电源的电流最大为 28A。设计中给每 组电压都提供双路接口和双路回路,确保系统的可靠性和稳定性。

(主)高速采集板卡

High speed acquisition borad SLAVE

S-IN1

ADC_100MHz

S-IN2

_16bit

PS

ZYNQ7030 PL

CLK

DDR3

SPI FLASH

(从)高速采集板卡

图 3-4 高速采集板卡系统框架图

ECLK SYNC TRG

IO

LVDSx10

POWER2Fra bibliotek图 2-4 系统组成框图

3 硬件方案设计

如图 2-4 所示,超高速信号采集录波器主要由:底板;高速采集板,存储板 构成。 3.1 底板硬件设计

底板作为各板之间的衔接桥梁,主要为各板提供电源、为高速采集板与存 储板之间提供互联、由高速采集板所接入的外部时钟也经由底板转送至各主从采 集板。

3.1.1 时钟信号设计

超高速信号采集录波器的外部时钟信号(ext-clk)、同步信号(sync)、外部 触发信号(ext-trg)为确保各信号同步作用于各高速采集板,通过主高速采集板

3

接入,经由底板,再将信号输出至各高速采集板。具体设计框图如图 3-1、3-2、 3-3 所示。

图 3-1 ext-clk 要求:50M1_P/N、50M2_P/N 和 50M3_P/N 在底板上 PCB 设计时需做等长 处理。

硬盘的接口座采用 SATA 母座,便于硬盘直接接入底板。

9

8

3.2.6 外部输入接口

主要包括外部输入的各类接口,以及网口接口。分别为 1 路千兆网接口、2 路信号输入接口、1 路外部时钟输入接口、1 路同步时钟输入接口、1 路外部触 发接口。如图 3-5 所示。

3.3 存储板设计

图 3-5 高速采集板外部输入接口

存储板主要用于对 AD 数据进行存储。设计用 4TB 的机械硬盘,存储带宽