多通道数据采集卡

多通道数据采集器-用户手册说明书

SensorHub多通道数据采集器用户手册版本:V3.0目录1.产品介绍 (5)2.设备快速使用流程 (7)设备连接SenseCAP云平台 (7)设备连接第三方的传感器和服务器 (8)3.组装设备 (9)设备包装清单(SensorHub) (9)设备接口介绍 (10)安装SIM卡 (10)安装天线 (11)连接传感器 (12)连接电源线 (12)4.配置设备连接到SenseCAP云平台 (13)绑定设备 (13)4.1.1注册账号 (13)4.1.2下载手机App (13)4.1.3绑定设备和传感器 (13)设备上电开机 (14)登录云平台查看数据和状态 (15)云平台使用说明 (15)API使用说明 (16)5.配置设备连接到第三方服务器 (17)准备工具 (17)5.1.1上位机配置软件 (17)5.1.2串口线连接和驱动安装 (18)配置工具功能介绍 (18)通用设置 (19)5.3.1设备编码(EUI)和上报周期修改 (21)5.3.2MQTT服务器配置 (22)5.3.3GPS配置 (24)5.3.4APN配置 (24)5.3.5读写操作和清空配置 (24)6.添加自定义传感器 (25)传感器标准及分类 (26)6.1.1用户自定义传感器 (26)6.1.2内建支持传感器 (26)用户自定义传感器示例:添加土壤温湿度传感器 (27)6.2.1准备 (27)6.2.2配置传感器基本信息 (27)6.2.3配置测量值信息 (29)6.2.4传感器测试 (31)6.2.5确认数据上传服务器 (32)在SenseCAP云平台添加自定义测量值和传感器 (36)6.3.1添加测量类型 (36)6.3.2添加传感器类型ID (37)7.故障排除和日志解析 (39)常见异常诊断 (39)7.1.1通道状态异常 (39)7.1.2在测试传感器时,报错:No sensor found. Is the sensor connected (39)7.1.3在测试传感器时,报错:[ERROR] rs485 err code: XX XX (39)日志解析 (41)8.设备安装和使用注意事项 (46)内置电池低温环境使用注意事项(必看) (46)传感器航空插头线序 (46)安装示例-数据采集器 (47)安装示例-太阳能板 (49)1.产品介绍SenseCAP是一套工业级传感网络系统,实现低功耗的环境物理量数据采集,包含可靠易用的硬件产品和软件平台服务。

【价格】多通道数据采集 80K 14位 16路同步模拟量输入采集卡)系列)图

PCI8008 同步采集卡硬件使用说明书阿尔泰科技发展有限公司产品研发部修订阿尔泰科技发展有限公司目录目录 (1)第一章概述 (3)第一节、产品应用 (3)第二节、AD 模拟量输入功能 (3)第三节、其他指标 (4)第四节、板卡外形尺寸 (4)第五节、产品安装核对表 (4)第六节、安装指导 (4)一、软件安装指导 (4)二、硬件安装指导 (4)第二章元件布局图及简要说明 (5)第一节、主要元件布局图 (5)一、信号输入输出连接器 (5)二、电位器 (5)三、跳线器 (5)四、物理ID 拨码开关 (6)五、指示灯 (7)第三章信号输入输出连接器 (8)第一节、AD 模拟量信号输入连接器定义 (8)第二节、模拟量输入/输出接口 (8)第三节、跳线器设置 (9)第四章各种信号的连接方法 (10)第一节、AD 模拟量输入的信号连接方法 (10)一、AD 单端输入连接方式 (10)二、AD 双端输入连接方式 (10)第二节、同步触发脉冲信号的连接方法 (11)一、同步触发脉冲信号输入连接方式 (11)二、同步触发脉冲信号输出连接方式 (11)第三节、时钟输入输出信号的连接方法 (11)第四节、触发信号连接方法 (12)第五节、多卡同步的实现方法 (12)第五章数据格式、排放顺序及换算关系 (14)第一节、AD 模拟量输入数据格式及码值换算 (14)一、AD 双极性模拟量输入数据格式 (14)二、AD 单极性模拟量输入数据格式 (14)第二节、关于AD 数据端口高位空闲部分的定义 (14)第三节、AD 多通道采集时的数据排放顺序 (15)第六章各种功能的使用方法 (16)第一节、AD 触发功能的使用方法 (16)一、AD 内触发功能 (16)二、AD 外触发功能 (16)第二节、AD 内时钟与外时钟功能的使用方法 (19)一、AD 内时钟功能 (19)二、AD 外时钟功能 (19)1PCI8008 同步采集卡硬件使用说明书版本:6.020第七章产品的应用注意事项、校准、保修 (20)第一节、注意事项 (20)第二节、AD 模拟量输入的校准 (20)第三节、保修 (20)2阿尔泰科技发展有限公司第一章概述信息社会的发展,在很大程度上取决于信息与信号处理技术的先进性。

一种基于VXI总线的多通道同步数据采集卡[实用新型专利]

![一种基于VXI总线的多通道同步数据采集卡[实用新型专利]](https://img.taocdn.com/s3/m/1a4289e8bed5b9f3f80f1c45.png)

专利名称:一种基于VXI总线的多通道同步数据采集卡专利类型:实用新型专利

发明人:郭恩全,严昭莹,李小杰,赵涛

申请号:CN200720311326.1

申请日:20071220

公开号:CN201130369Y

公开日:

20081008

专利内容由知识产权出版社提供

摘要:本实用新型提供一种基于VXI总线的多通道同步数据采集卡,每块板卡由4个完全独立的模拟信号调理子板和1块母板组成,在母板上集成有FPGA芯片、SDRAM芯片、VXI接口芯片,在子板上集成有模拟信号调理电路、A/D转换器,每个子板具有独立的信号采集通道,各通道具有1个独立的16位A/D转换器和信号调理电路,各通道独立并行采样,每通道的最高采样为2M,采样率可向下分频。

本实用新型采集卡采样率高,采样精度优于1‰,数据存储容量大、速度快,峰值数据吞吐量可达320MB/S,降低了信号毛刺对时序逻辑的影响,提高了板卡的稳定性,保证了多个通道采样的同步性,适合于对相位要求高的应用场所。

申请人:陕西海泰电子有限责任公司

地址:710075 陕西省西安市高新区高新1路18号

国籍:CN

代理机构:西安文盛专利代理有限公司

代理人:佘文英

更多信息请下载全文后查看。

多通道数据采集卡在信道化接收机中的应用

信号数字化 , 并对采样进行平滑 , 以提高信噪比。

丑 多通道数据采集卡的结构

1 。 a a y 构成 了高性 o h r 采集卡的输 入信 号为对数 检波器输 出的视频信 法器模块和超前进位链 (okaedcr ) 多达 4个数字时钟管理器模块 和 号。视频信号首先经运放调整到 A D转换器 的输入 能的算术处理功能 ; / 个全局时钟 多路 复用缓冲器 , 构成 了内部高性 能和 动态范围之 内, / A D转换器将 视频信号量化为 1 i 0 结构

二 :鱼

6. 2 0

式中 :SA为对正弦波采样后数字信号的信号与噪声 RlD N

收稿 日期 : 0 50 —8 20 - 1 ;修回 日期 : 0 51 - 。 7 20 ・12 2

加失真之比, 单位为 d , B 可按图2 所示方法获取 D 。 。

维普资讯

第3 2卷第 4期

20 0 6年 4月

电 字 工 童 师

EL C RON C E E T I NGI E NE R

V0 _ 2 No 4 l3 . Ap .2 0 r 06

多通道 数据 采集卡在 信道化接 收机 中的应用

王 坤, 乃昌 袁

给 出一些 实验 结果 。

XC S 0 —P 0 i———/ 3 4 04 Q2 8 ——

1 i 0bt

XC3 4 04 Q2 8 S0—p 0I

2 有效量化位数分析

1 i 0b t

xc3 4 04 Q2 8 s0—p 0I

A 90 D 2 3的有效量化位数按下式计算 :

数据采集卡 , 包括基本原理、 结构组成、 性能参数及其在信道化接收机 中的应 用, 对其有效量化位数进

使用多通道数据采集卡的实验方法

使用多通道数据采集卡的实验方法随着科技的不断进步,数据采集在许多领域中扮演着重要的角色。

多通道数据采集卡的出现,使得同时采集多个信号成为可能。

本文将介绍使用多通道数据采集卡的实验方法,帮助读者更好地了解和应用这一技术。

1. 什么是多通道数据采集卡多通道数据采集卡是一种硬件设备,用于采集多个信号。

它通常包括多个输入通道、模拟至数字转换器(ADC)、时钟源和接口等组件。

通过连接传感器、测量设备等到不同的通道上,数据采集卡可以将多个信号同时转换为数字信号,并提供给计算机进行存储、处理和分析。

2. 数据采集前的准备工作在进行实验之前,我们需要做一些准备工作。

首先,明确实验目的和所需的采集信号类型。

例如,如果需要监测温度和湿度,我们需要选择合适的传感器,并将它们连接到数据采集卡的相应通道上。

其次,确保数据采集卡和计算机之间的连接正常。

一般来说,数据采集卡通过USB、PCIe等接口与计算机连接。

根据设备型号和接口类型,我们可以选择合适的连接线缆,并确保稳定的连接。

另外,对于模拟信号的采集,我们需要进行校准和滤波处理。

校准可以提高信号的测量精度,滤波处理可以减少噪音对信号的干扰。

因此,在实验开始之前,我们应该对采集卡的设置进行调整,并根据需要进行校准和滤波操作。

3. 实验过程及应用案例在实验过程中,我们可以使用软件或编程语言来控制和接收数据。

许多数据采集卡提供了自带的软件,可以用于实时数据监测和保存。

此外,我们也可以使用LabVIEW、Python等编程语言进行数据采集和处理。

对于应用案例,我们以心电信号采集为例进行说明。

在实验中,我们可以将心电传感器连接到多通道数据采集卡的相应通道上,然后通过软件接收和记录心电信号。

通过设置采样频率和时间间隔,我们可以获取不同时间段内的心电数据。

然后,我们可以使用信号处理算法对心电信号进行滤波、去噪、心律分析等操作,以获得更有用的信息。

除了心电信号的采集,多通道数据采集卡还可以应用于许多其他领域,如振动分析、声音信号处理、工业自动化等。

多通道数据采集系统的使用与配置

多通道数据采集系统的使用与配置现代科技的快速发展使得各种数据的采集和处理变得愈加重要和复杂。

在许多领域,需要采集多个信号源或传感器的数据,以便进行分析和决策。

为了满足这样的需求,多通道数据采集系统应运而生。

一、多通道数据采集系统的概述多通道数据采集系统是一种集成多个采集通道的设备,用于采集和存储多个信号源的数据。

这些信号源可以是各种传感器、仪器或其他设备产生的模拟或数字信号。

多通道数据采集系统不仅能够采集数据,还能进行数据处理、分析和存储,为用户提供完整的解决方案。

二、多通道数据采集系统的配置配置一套多通道数据采集系统需要考虑以下几个方面:1. 硬件配置:选择适合实际需求的多通道数据采集硬件设备,包括采集卡、传感器和连接线等。

根据信号源和采集频率的不同,可以选择不同型号和规格的硬件设备。

2. 软件配置:多通道数据采集系统通常配套有专门的软件进行数据采集、处理和分析。

根据实际需求选择适合的软件,并进行相应的配置和参数设置。

3. 连接配置:将数据采集硬件设备与计算机或其他设备进行连接,并确保连接稳定和可靠。

根据实际情况选择合适的连接方式,如USB、PCI等。

4. 电源配置:多通道数据采集系统需要稳定的电源供应,因此需要考虑电源的配置和接口的选择,以确保设备的正常运行。

三、多通道数据采集系统的使用使用多通道数据采集系统可以采集和处理多个信号源的数据,为用户提供更全面的信息和更准确的分析结果。

使用多通道数据采集系统可以应用于多个领域,如医学、工程、环境监测等。

在医学领域,多通道数据采集系统可以用于采集和分析心电图、脑电图、血压等生理信号,用于监测和诊断疾病。

多通道数据采集系统的高精度和高灵敏度使得医生可以更准确地判断患者的病情,并做出相应的治疗方案。

在工程领域,多通道数据采集系统可以用于采集和分析各种工程测量信号,如温度、压力、流量等。

多通道数据采集系统的可靠性和稳定性使得工程师可以更好地了解和控制工程过程,提高产品质量和生产效率。

4通道同步数据采集卡,40M采样频率

PCI8504 同步采集卡

硬件使用说明书

北京阿尔泰科技发展有限公司

产品研发部修订

PCI8504 同步采集卡硬件使用说明书

版本:6.005

目

第一章 概述

信息社会的发展,在很大程度上取决于信息与信号处理技术的先进性。数字信号处理技术的出现改变了信息 与信号处理技术的整个面貌,而数据采集作为数字信号处理的必不可少的前期工作在整个数字系统中起到关键 性、乃至决定性的作用,其应用已经深入到信号处理的各个领域中。实时信号处理、数字图像处理等领域对高速 度、高精度数据采集卡的需求越来越大。ISA 总线由于其传输速度的限制而逐渐被淘汰。我公司推出的 PCI8504 数据采集卡综合了国内外众多同类产品的优点,以其使用的便捷、稳定的性能、极高的性价比,获得多家试用客 户的一致好评,是一款真正具有可比性的产品,也是您理想的选择。

注明: (一) 关于AI0~AI3信号的输入连接方法请参考《AD模拟量输入的信号连接方法》章节;、 (二)、ATR从AI0~AI3的任一通道输入; (三)、关于CLK_IN、ATR和DTR_IN的信号连接方法请参考《时钟输入输出和触发信号连接方法》章节, 其ATR、DTR_IN触发功能的使用方法请参考《AD外触发功能》章节。

第二节、AD 模拟量输入功能

注:括号中的单词为软件中的 AD 参数 ◆ 输入量程:±5V、±1V(另可定制±500mV、±200mV、±100mV) ◆ 转换精度:14 位(Bit) ◆ 采样频率(Frequency):最高 40MHz 注释:各通道实际采样速率 = 采样速率(同步采集) ◆ 物理通道数:4 通道同步 ◆ 模拟量输入方式:单端模拟输入 ◆ 数据读取方式:查询方式、DMA 方式(此方式速度最高) ◆ 存储器深度:256MB 的 DDR2 存储器 ◆ 每通道存储深度:64MB ◆ 时钟源选择(OutClockSource):板内时钟和板外时钟软件可选 ◆ 触发模式(TriggerMode):中间触发、后触发、预触发、硬件延时触发 ◆ 触发源(TriggerSource):软件触发、ATR 触发、DTR 触发、TRG0~TRG7 信号触发(用于多卡同步) ◆ 触发方向(TriggerDir):下降沿触发、上升沿触发、上下边沿均触发 ◆ 触发电平(TrigLevelVolt):由输入量程决定 ◆ 模拟量触发源(ATR)输入源:从 AI0~AI3 的任一通道输入 ◆ 模拟量触发源(ATR)输入范围:触发电平可按 12 位精度计算,具体请参考《ATR模拟触发功能》 ◆ 触发源 DTR 输入范围:标准 TTL 电平 ◆ 支持多卡同步 ◆ 耦合方式:直流、交流 ◆ 软件自动校准 ◆ 模拟输入阻抗:1MΩ(另可选 50Ω) ◆ 工作温度范围:0℃ ~ +50℃ ◆ 存储温度范围:-20℃ ~ +70℃

多通道高速数据采集卡的设计

① 煤 粉 仓 的 设计

要 保 证 计 重 机 稳 定 连 续 地 计

量 , 粉仓 的煤 粉 下 料 通 畅 是 先 决 条 件 。 因 此 在 设 计 煤 煤 粉 仓 时 , 使得 煤 粉 仓 锥 部 的 倾 斜 角 大 于 煤 粉 的安 应 息 角 , 于煤 粉 整 体 流 动 , 匀 下 料 。否 则 , 形 成 漏 便 均 将 斗 形 流 动 , 成 煤 粉下 料 不 均 匀 。 造 ② 均 压 管 的 设 置 计 重 机 内部 如 果 发 生 压 力 变

魏 娜 智 力 事 南 先

( 长春光学精 密机械学院电信舟 院, 长春 1 0 2 3 2) 0

摘

要

通对对 多通道 高速 同步数据 采榘卡 的具 体设 I 制作 , 十、 对其基 本功能 、 特点 、 总体设 计方 词 数据 采集 同步 采集 高速采 集 多 路数据

在 0 5…0 6 .

4 结束语

随着 水 泥 等 行 业 的 发 展 , 粉 料 计 量 显 得 越 来 越 对 重要 , 状天平计重机正是 这样一 种能够连 续、 确 、 环 精 稳 定 且 无 泄 漏 、 飞 扬 的 粉料 流 量 计量 系统 , 后 在 多 无 今 种 行 业 中必 将 得 到 更 加 广泛 的应 用 。

3 配套 设备 的设计

要 使 得 环 状 天 平 计 重机 稳 定 计 量 , 达到 设 计 精 度 , 其 前后 配套 设 备 设 计 的好 坏 , 得 至 关 重 要 , 显 主要 有 以

下两点:

传感 器 测 出 的 称重 信 号 和 转 速 信 号 , 控 制 器 内 算 出 在 流 量 值 , 经 过 PB运 算 , 出 2个 调 速 信 号 , 别 送 再 I 输 分 给 定 量供 给 机 和 流 量 计 重 机 的 电 机 变 频 器 , 节 电机 调 的转 速 , 而 使 得 实 际 的 给 料 量 与 设 定 的 给 料 量 相 一 从

戴浦科技采集卡说明书

戴浦科技采集卡说明书一、引言戴浦科技采集卡是一种用于数据采集和传输的设备,广泛应用于各个领域,如工业控制、仪器仪表、自动化设备等。

本说明书将介绍戴浦科技采集卡的主要特点、技术参数、安装和使用方法等内容,以帮助用户更好地了解和使用该产品。

二、产品特点1. 多通道采集:戴浦科技采集卡具有多通道输入功能,可同时采集多个信号源的数据,满足复杂系统的需求。

2. 高精度采集:采用先进的模拟数字转换技术,戴浦科技采集卡具有高精度的数据采集能力,保证数据的准确性。

3. 快速采样率:采用高速采样芯片,戴浦科技采集卡具有较高的采样率,能够快速捕捉信号的变化。

4. 宽电压输入范围:戴浦科技采集卡支持宽电压输入范围,适应各种信号源的输入。

5. 良好的抗干扰能力:采用专业的抗干扰技术,戴浦科技采集卡能够有效抵御外界干扰,提高信号的稳定性和可靠性。

三、技术参数1. 通道数:戴浦科技采集卡提供不同通道数的型号可供选择,包括4通道、8通道、16通道等,满足不同应用需求。

2. 分辨率:采样精度为16位或24位,可根据用户需求选择。

3. 采样率:戴浦科技采集卡的采样率范围广泛,从几十Hz到几百kHz不等,可根据具体应用场景进行调整。

4. 输入范围:戴浦科技采集卡支持不同的输入范围,如±10V、±5V、0-5V等,用户可根据实际需求进行选择。

5. 接口类型:戴浦科技采集卡提供多种接口类型,如PCI、PCIe、USB等,方便用户与计算机进行连接。

四、安装方法1. 将戴浦科技采集卡插入计算机的相应插槽或连接USB接口。

2. 安装采集卡的驱动程序,可从戴浦科技官方网站下载最新版本的驱动程序。

3. 根据实际需求,连接需要采集的信号源到采集卡的输入端口。

4. 完成硬件连接后,启动计算机,等待系统自动识别并配置采集卡。

五、使用方法1. 打开数据采集软件,选择相应的采集卡型号和通道数。

2. 配置采样率、输入范围等参数,根据实际需求选择合适的参数设置。

多通道数据采集系统的设计与实现

多通道数据采集系统的设计与实现近年来,随着科技的不断发展和数据的迅速增长,对于多通道数据采集系统的需求越来越迫切。

多通道数据采集系统旨在通过多个输入通道同时采集、传输和处理多组数据,以满足大规模数据采集和处理的需求。

本文将详细介绍多通道数据采集系统的设计与实现。

1. 系统需求分析在设计多通道数据采集系统之前,首先要明确系统的需求。

根据具体的应用场景和目标,我们需要确定以下几个方面的需求:1.1 数据采集范围:确定需要采集的数据范围,包括数据类型、数据量和采集频率等。

这将直接影响系统的硬件选择和设计参数。

1.2 数据传输和存储要求:确定数据传输和存储的方式和要求。

例如,是否需要实时传输数据,是否需要数据缓存和压缩等。

1.3 系统的实时性要求:确定系统对数据采集和处理的实时性要求。

根据实际应用场景,可以确定系统对数据延迟和响应时间的要求。

1.4 系统的可扩展性:考虑系统的可扩展性,以满足未来可能的扩展需求。

这包括硬件和软件的可扩展性。

2. 系统设计在需求分析的基础上,我们进行多通道数据采集系统的设计。

系统设计主要包括硬件设计和软件设计两个方面。

2.1 硬件设计根据需求分析中确定的数据采集范围和要求,我们选择合适的硬件设备进行数据采集。

常用的硬件设备包括传感器、模拟信号采集卡和数字信号处理器等。

2.2 传感器选择根据需要采集的数据类型,选择合适的传感器进行数据采集。

不同的传感器适用于不同的数据类型,如温度传感器、压力传感器、光传感器等。

2.3 采集卡设计针对多通道数据采集系统的特点,我们需要选择合适的模拟信号采集卡进行数据采集。

采集卡应具备多个输入通道,并能够同时采集多个通道的数据。

2.4 数字信号处理器设计针对采集到的模拟信号数据,我们需要进行数字信号处理。

选择合适的数字信号处理器进行数据处理,如滤波、采样和转换等。

2.5 软件设计针对系统的需求和硬件的设计,我们需要进行软件设计,以实现数据采集、传输和处理。

NI采集卡的多通道不同功能采集的配置操作方法

NI采集卡的多通道不同功能采集的配置操作方法1. 打开NI采集卡的配置软件:首先需要打开NI采集卡对应的配置软件,例如NI-DAQmx或者LabVIEW,这些软件提供了图形化界面和API 接口来配置和控制采集卡。

2.确定采集通道数目:在软件界面上,需要确定采集的通道数目,即同时采集的信号源数量。

根据具体应用需求,可以选择多通道采集配置。

3.配置采集参数:针对每个通道,需要配置采集参数,例如采样率、量程、触发模式等。

采样率是指每秒采样的次数,量程是指信号的幅度范围,触发模式是指启动采集的条件。

4.设定物理连接:将各个信号源与采集卡的输入端口进行物理连接。

通常,使用BNC线缆将信号源连接到采集卡的输入通道。

5.配置数据存储方式:在采集卡配置软件中,可以选择数据存储的方式。

可以选择将数据保存在计算机的硬盘中,或者直接存储在采集卡的内存中。

6.设置数据处理功能:如果需要对采集到的数据进行进一步的处理,可以在配置软件中设置数据处理功能。

例如,可以选择进行滤波、数字信号处理、实时显示等操作。

7.验证配置:在完成配置后,可以进行配置的验证。

可以通过软件提供的测试功能,发送一个已知的测试信号,并观察是否能够正确采集到该信号。

8.启动采集:完成配置后,可以启动采集操作。

可以通过配置软件提供的开关按钮或者编程接口来启动采集操作。

一旦启动,采集卡将开始按照配置的参数进行数据采集。

9. 数据后处理:采集完数据后,可以进行数据后处理操作。

可以使用MATLAB、LabVIEW等软件进行数据分析、图像显示等。

总结:NI采集卡的多通道不同功能采集的配置操作方法包括打开配置软件、确定通道数目、配置采集参数、物理连接、配置数据存储方式、设置数据处理功能、验证配置、启动采集和数据后处理。

通过这些步骤,可以正确配置NI采集卡以满足不同应用的需求。

多通道数据采集卡同步功能的设计与实现_高健

第25卷第1期2008年1月机 电 工 程M EC HAN ICAL &ELECTR ICAL ENG INEER I NG M AGA Z I NE V o.l 25N o .1Jan .2008收稿日期:2007-07-24作者简介:高 健(1982-),男,浙江安吉人,主要从事嵌入式系统设计方面的研究。

多通道数据采集卡同步功能的设计与实现高 健,杨成忠,唐明明(杭州电子科技大学自动化学院,浙江杭州310018)摘 要:介绍了多通道数据采集卡同步功能的实现方法,讨论和处理了实现同步功能的相关问题。

该设计采用一种二级时钟分配方案,不仅实现了板内各通道的真正实时的同步采集,并且可以方便灵活地实现多块板卡的板间同步,具有高速、高精度、多路同步采集的特点,可广泛应用于对信号的同步性能要求较高的数据测量系统中。

关键词:数据采集;同步触发;A /D 转换中图分类号:TP393 文献标识码:A文章编号:1001-4551(2008)01-0082-04D esign and rea lization of t he si m ult aneous f unction in t he m ult-i channel data acquisition cardGAO Jian ,YANG Cheng -zhong ,TANG M ing -m i n g(C ollege of A uto m ation ,H angzhou D ianzi University,H angzhou 310018,China)Abstrac t :The design and rea lization of the s i m u ltaneous f unc ti on i n the mu lt-i channe l data acqu isiti on card w ere i ntroduced .A nd also the corre l a ti ve po i nts o f t he si m ultaneous function w ere d iscussed and d i sposed .The desi gn used a t w o -step c l ock distr-i bu tion ,which not only rea lized the rea-l ti m e mu lt-i channe l si m u ltaneous acqu isiti on i n one card ,bu t also rea lized t he si m u ltane -ous acqu i sition f uncti on i n m ore t han one card v ery conven ientl y.The ca rd has the feat ures o f h i gh -speed ,h i gh precision and mu lt-i channel si m ultaneous acqu i s ition ,can be w i de l y used in t he da ta acqu isiti on system w hich has h i gh request of t he si m ulta -neous si gna.lK ey word s :data acquisiti on ;si m u ltaneous tri gge r ;A /D conve rt0 前 言随着电子技术的深入发展和科研生产的需要,人们已经不再满足于用单路A /D 数据采集来分时采集多路测试信号。

多通道数据采集卡同步功能的设计与实现

多通道数据采集卡同步功能的设计与实现

高健;杨成忠;唐明明

【期刊名称】《机电工程》

【年(卷),期】2008(025)001

【摘要】介绍了多通道数据采集卡同步功能的实现方法,讨论和处理了实现同步功能的相关问题.该设计采用一种二级时钟分配方案,不仅实现了板内各通道的真正实时的同步采集,并且可以方便灵活地实现多块板卡的板间同步,具有高速、高精度、多路同步采集的特点,可广泛应用于对信号的同步性能要求较高的数据测量系统中.【总页数】4页(P82-85)

【作者】高健;杨成忠;唐明明

【作者单位】杭州电子科技大学,自动化学院,浙江,杭州,310018;杭州电子科技大学,自动化学院,浙江,杭州,310018;杭州电子科技大学,自动化学院,浙江,杭州,310018【正文语种】中文

【中图分类】TP393

【相关文献】

1.振动信号多通道同步整周期数据采集卡设计 [J], 杨世锡;梁文军;于保华

2.基于PC/104总线与FPGA的多通道同步数据采集卡的研究 [J], 刘朝华;戴怡;石秀敏

3.利用FPGA实现的多通道同步数据采集卡 [J], 田多华;邱宏安;陆宇鹏;邵立群

4.一种多接口多通道的同步数据采集卡的设计与实现 [J], 郑晨曦;吴次南;蒋小菲

5.凌华科技推出高密度多通道同步数据采集卡 [J],

因版权原因,仅展示原文概要,查看原文内容请购买。

基于USB的高精度多通道数据采集卡设计

时间是 32 s . ,对 应 的采集 时间是 0 8I 。因此 ,为 . s x

了得 到最 大 的输 出数 据率 ,读取 数据 可 以在 下一 个转 换期 间进 行 。

A S34 中 的 采 样/ 持 模 块 以 最 大 吞 吐 率 D 86 保

2 0k 工 作 ,它 的输 入 带 宽 大 于 A C的奈 奎 斯 特频 5 B D

1 多通道 , 高精度的 AD转换 /

A S 34是美 国 T 公 司生 产 的高 速 、低功 耗 ,6 D 86 I 通道 同步采样 1 6位模 数转换 器 。A S 3 4采用 + D 86 5V 工 作 电压 ,并带 有 8 B共模抑 制 的全差 分 输入 通 道 0d 以及 6个 4 s 连续 近似 的模数转 换器 、6个差 分采样

Deino B- ae gl rc in Mut C a n l t q i t n C r s f g US B sdHilP ei o l - h n e DaaAc us i a d - s i io

La g Z e g, LiXi oe g n h n a fn

(c ol f c ne i a n esy in7 0 7 ,C i ) Sho o i c ,Xd nU i rt,X’ 0 h a Se i v i a 1 1 n

Ab ta t Th a e e cie l — y sn h o iain d t c usto ad ma e u fUS c n rle sr c e p p r d s rb s a mut wa y c r nz t aa a q ii n c r d p o B o tolr i o i CY7C 8 1 n 6 0 3 a d AD o v re c n etrADS 3 4. I rn — n i uta d te F GA o to rc s r ie . Th aaa — 86 t fo te d cr i n h P s c c nrlp o e sa egv n ed t c

利用FPGA实现的多通道同步数据采集卡

PCI04作为一种国际标准的控制总线,在测试和控 制中得到了广泛应用,但目前市场上与之配套的同步 数据采集卡还很少。基于PCI04总线的高精度数据采集 卡的主要功能是把外界模拟信号的电压参量经过A/D 转换器转换成数字量,并把转换结果存储以便分析处 理。本文所述采集卡采用了AD公司推出的高速、低功 耗、四通道同步采样12位并行接口的A/D转换器 AD7864,用FPGA进行逻辑功能控制和数据缓存,使得 该数据采集卡硬件电路极为简单。 1数据采集卡的原理及组成

降沿来表示。此时片选信号/CS端接地,由读信号/RD读出

数据。当读信号/RD和片选信号/CS同时保持低电平时

才可读数据,读操作在工作时要确保写信号,WR处于高

电平。每次读数据操作增加输出数据寄存器指针,读完

最后一个转换数据时,将输出数据寄存器指针复位。写

操作主要完成工作模式的设置,一般只在初始化或转换

‘OR2

图3中断产生电路

2.2.3主机读取数据电路 当主机响应了读中断请求之后,就会开始从FIFO

中取数,但是六个FIFO的工作基本保持一致,所以存在 主机先从哪一个FIFO中读取数据的问题,因此需要设 计一个数据选择读取电路,如图4所示。

图中数据选择电路通过三位地址a0、a1、a2来对六 个FIFO的六路数据选择输出。 2.2.4 AID转换启动信号发生电路

品中。系统通过FPGA来实现高速数据缓存及逻辑控

制。采用的器件是FI正X1K系列的EPIK30TCl44—1器

件,其最大工作频率为40MHz,消耗1 533个LC,平均编

码时间为20个时钟周期。FPGA除了要满足相应的时

序要求外,还要求控制数据的位数和A/D转换器的位

多通道数据采集卡设计

作者简介 :陈光辉 ( 1 9 8 3 一) ,男 ,四川资阳人 ,湖南科技学院 电子与信息工程学 院教师 ,主要研 究方向 : 集成 电路设 计与 验证 ,系统设计 ,数字信号处理 。

3 7

参 考文 献 :

[ 1 】 裴喜龙, 童莉. 基于 P C I 总线的高速数据采集卡系统设计与实现 [ J 】 _ 北京 : 微计算机信息, 2 0 0 6 : 1 . 5 . [ 2 ] 王勉 . 高效2 0 1 2 , ( 0 2 ) : 1 0 8 . 1 1 1 .

'

第3 6卷 第 5 期

湖 南科 技 学 院 学报

J o u ma l o f Hu n a n Un i v e r s i t y o f S c i e n c e a n d En g i n e e r i n g

V. 0 l - 3 6 NO . 5

集 系统 是监控 系统的核心部分 。本数据采集卡 就是用于解决如何采集 实时信息 ,跟换不 同数据接受模 块可 以完成不同信

息 的采 集 ,能有效降低设计成本 。

1 硬 件整 体设 计 方案

本数据采集卡使用 P C I 接 口芯片与 F P G A相结合 的方案,系统硬件 结构 图如 图 1所示。数据 采集卡只能处理数字信号 ,

些存储单元来缓存数据 ,既减少开发周期 ,又能减 少开 发成 本。数据采集到后 ,要传输给数据处理芯片 ,本设计采 用 P C I

总线协议 ,支持 3 2 位/ 3 3 MH z ;本地端可编程实现 8 、1 6 、3 2 位数据 宽度, 传输速率最高可到 1 3 2 M 字节/ 秒 ,本地 总线 端时 钟最高可达 5 0 MH z , 支持复 用( J 模式) 和 非复 用 3 2 位地址/ 数据 ( c模式) ,还直接主模式, 直接 从模 式和 D M A 模式 。缓存到存 储单元 中的数据按 照 P C I 协议传输给主机 ,从而 完成数据 的采集 和传输 过程。数据采集卡包括模数转换模块、数据缓存模

凌华科技推出高密度多通道同步数据采集卡

凌华科技推出高密度多通道同步数据采集卡

佚名

【期刊名称】《测控技术》

【年(卷),期】2010(29)9

【摘要】亚洲最大的数据采集与PXI产品供货商——凌华科技推出第一款多通道

同步数据采集卡PXI-2020/2022系列。

凌华科技PXI-2020/2022系列分别提

供8和16个模拟输入通道,分辨率为16位,最高可达250kS/s的采样率。

由

于可对多通道模拟输入信号进行同步采样,因此适用于高等物理、粒子物理学研究、雷达、声纳、超音波应用、汽车引擎的测试或飞机噪音检测,以及需要对多点信号同步侦测的领域。

同时,高密度多通道同步采样的设计,能有效地帮助用户节省整个PXI系统的构建成本与使用空间。

【总页数】1页(P104-104)

【关键词】数据采集卡;同步采样;凌华科技;多通道;高密度;粒子物理学;PXI产

品;PXI系统

【正文语种】中文

【中图分类】TP274.2

【相关文献】

1.凌华科技推出4通道16位800kS/s高速同步数据采集卡 [J],

2.凌华科技推出DAQ—MTLB for MATLAB 数据采集工具箱全系列凌华数据采集卡均适用加速MATLAB环境应用开发进程 [J],

3.凌华科技领先全球发表PCI Express同步高速数据采集卡 [J],

4.凌华科技发表PCI Express同步高速数据采集卡 [J],

5.凌华科技推出4通道16位800 kS/s高速同步数据采集卡 [J],

因版权原因,仅展示原文概要,查看原文内容请购买。

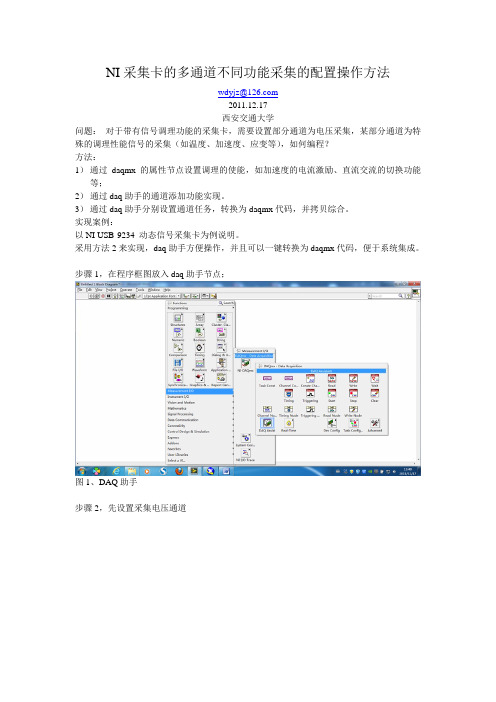

NI采集卡的多通道不同功能采集的配置操作方法

NI采集卡的多通道不同功能采集的配置操作方法

wdyjz@

2011.12.17

西安交通大学

问题:对于带有信号调理功能的采集卡,需要设置部分通道为电压采集,某部分通道为特殊的调理性能信号的采集(如温度、加速度、应变等),如何编程?

方法:

1)通过daqmx 的属性节点设置调理的使能,如加速度的电流激励、直流交流的切换功能等;

2)通过daq助手的通道添加功能实现。

3)通过daq助手分别设置通道任务,转换为daqmx代码,并拷贝综合。

实现案例:

以NI USB-9234 动态信号采集卡为例说明。

采用方法2来实现,daq助手方便操作,并且可以一键转换为daqmx代码,便于系统集成。

步骤1,在程序框图放入daq助手节点;

图1、DAQ助手

步骤2,先设置采集电压通道

图2、设置采集电压

步骤3,设置电压采集的具体参数

图3、电压采集参数设置(通道0)步骤4,添加加速度采集通道

图4、添加加速度采集通道

步骤5,设置加速度采集参数

图5、加速度通道参数采集设置步骤6,采集效果

图6、采集效果图

步骤7,转换为daqmx 代码

步骤8,转换后的效果。

多通道数据采集系统的操作技巧

多通道数据采集系统的操作技巧多通道数据采集系统是一种广泛应用于科学研究、工业控制和生物医学等领域的数据采集装置。

它能够同时采集多个通道的数据,并通过计算机进行实时分析和处理。

为了充分发挥多通道数据采集系统的作用,掌握一些操作技巧是非常重要的。

操作技巧一:确保设备正确连接在使用多通道数据采集系统之前,首先要确保设备正确连接。

通常,多通道数据采集系统包括传感器、信号调理器和数据采集卡。

在连接传感器时,要注意每个传感器与信号调理器之间的正确对应。

在连接信号调理器与数据采集卡时,要确保插头与插孔完全插合,并保持连接稳定。

通过仔细检查连接情况,可以避免数据采集中的错误和故障。

操作技巧二:选择合适的采样率采样率是多通道数据采集系统进行数据转换的关键参数之一。

采样率过低会导致数据损失和失真,而采样率过高会增加系统负担和数据存储需求。

因此,在进行数据采集时,要根据实际需要选择合适的采样率。

一般情况下,采样率应调整至能够满足信号特征的最低要求,既能保证数据完整性又节省系统资源。

操作技巧三:进行适当的滤波处理多通道数据采集系统所采集的信号中常常包含大量噪声和干扰。

为了提取出有效信号并减少噪声的影响,需要进行适当的滤波处理。

一种常用的滤波方法是数字滤波器。

通过选择合适的滤波器类型和设置滤波器参数,可以对信号进行低通、高通、带通或带阻滤波,以消除不需要的频率成分。

操作技巧四:合理设置参考电平参考电平在多通道数据采集系统中起着至关重要的作用。

它可以用于校准和标定采集的信号,以提高数据的准确性和可靠性。

在设置参考电平时,首先应选用稳定的参考电压源,并通过校准操作将其与实际电压进行对比调整。

此外,还需根据采集的信号范围和精度需求进行适当的范围分配和调整,以保证准确的数据采集和分析。

操作技巧五:减少电磁干扰电磁干扰是影响多通道数据采集系统性能的常见问题之一。

为了减少电磁干扰对采集信号的影响,可以采取一些措施。

例如,选择低噪声的电源供电,使用屏蔽良好的信号线缆,远离电磁辐射源,保持设备与其他电子设备之间的适当距离等。

振动信号多通道同步整周期数据采集卡设计

振 动信 号 多通 道 同步 整 周 期 数 据 采集 卡 设 计

杨 世 锡 。 , 梁 文 军 , 于保 华

( 1 . 浙 江 大 学 液 压 传 动 及 控 制 国家 重 点 实 验 室

摘要

.

杭州 , 8 1 0 0 2 7 ) ( 2 . 浙 江 大 学 机 械 工 程 学 系 杭 州 , 3 1 0 0息 , 通 过 振 动分 析 得 出机组 当前 的

工作状况, 确定 运 行 和 维 修 计 划[ 2 ; 因此 , 需 要 根 据 转 子振 动信 号 的特点 设计 一款 适用 于转 子振 动信 号 采 集 的高速 、 可 靠 的数据 采集 卡来 满足 这种 需求 。 对 于 汽 轮发 电机 组 这类 大型 旋 转机 械 设 备 , 转

对 汽 轮 发 电 机组 转 子 的振 动 信 号 进 行 整 周 期 采 集 有 利 于 提 高 频 谱 分 析 的精 度 、 提 高设备状 态监测 的水平 。

研 究 了整 周 期 采 集 技 术 , 提 出 了一 种 基 于现 场 可编 程 门 阵 列 ( f i e l d p r o g r a mma b l e g a t e a r r a y , 简称 F P G A) 的 转 子 振 动 信 号 多 通 道 同步 整周 期 数 据 采 集 卡 的设 计 方 案 。 该方案采用 F P G A 技 术设 计 了 基 于 键 相 倍 频 法 的 整 周 期 采 集 控 制算法 , 对 两 片 高 速 A/ D转换芯片进行整 周期采集控制 , 采 用 乒 乓 操 作 的方 式 将 A/ D转 换数据保存 在双 口R AM

片maxl320进行控制ad转换的控制时序采用状该芯片的数字供电电压范围为35v故可以使用态机编程主要状态的作用为复位ad芯片初始与fpga相同的工作电压33v可以免去两者之间化等待ad启动信号等待触发采样信号向ad为了匹配电平而增加的电平转换芯片减小电路开芯片发送采样保持信号等待ad转换完毕信号销使电路更加精简和可靠

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

读 取 P5上 的 高 八 位 数 据 32路 通 道 已 依 次 采 完 ? 否 存 储 器 已 满 ? 否 存 低 八 位 数 据 是 地 址 指 针 指 向 存 储 器 首 单 元 是

输 出 模 拟 通 道 地 址

地 址 指 针 指 向 存 储 器 首 单 元

置 R/C=1

存 储 地 址 加 一

系统软件设计(AD部分采用外部中断版本)

主函数流程图如下

开 始 延 时 50ms 是

初 始 化

存 储 器 已 满 ?

Hale Waihona Puke 延 时 8us否 存 低 八 位 数 据

地 址 指 针 指 向 存 储 器 首 单 元

置 R/C=1 存 储 地 址 加 一 读 取 P4上 的 低 八 位 数 据 模 拟 通 道 地 址 加 一

系统硬件设计

五、片外存储 选用µPD43256B,它是32Kx8的SRAM.

1、P2.0——P2.6作片外RAM 的高7位地址线,P2.7与RAM 的片选端相连输出片选信 号 ——可知,RAM地址为 0000H——7FFFH

2、P0口做数据地支复用线

系统硬件设计

六、USB接口

选用国产芯片CH372,它是一个 USB总线的通用设备接口芯片。在本地端,CH372 具有 8位数据总线和读、写、片选控制线以及中断输出,可以方便地挂接到单片机系统总线上; CH372内置了USB通讯中的底层协议,具有省事的内置固件模式和灵活的外置固件模式。 在内置固件模式下,CH372自动处理默认端点0的所有事务,本地端单片机只要负责数据交换, 所以单片机程序非常简洁。在外置固件模式下,由外部单片机根据需要自行处理各种USB 请求, 从而可以实现符合各种USB 类规范的设备。 本系统采用内置固件模式。 1、P0口做 CH372的八位数据线 2、74HC573的Q0与CH372的控 制端A0相连,控制是向CH372写 命令还是数据(当 A0=1 时可以 写命令,当 A0=0 时可以读写数 据) 3、P2.4,P2.5,P2.6,P2.7分 别与74HC138的的A0,A1,A2 和E3端相连,Y3端与CH372的 片选端CS相连,输出CH372的使 能信号4、可知CH372的地址为 Bxx1H和Bxx0H,此处选择BFF1H 和BFF0H

片外SRAM、 CH372和两个 74HC573无地址重 叠

7

系统硬件设计

8

七、ISP下载电路

本设计选用STC89C52单片机,支持ISP功能。

VCC V3_340 C15 22uf C16 0.1uf C17 0.01uf GND

U23 1 2 3 4 5 6 7 8 9 10 CKO ACT# TXD RXD V3 UD+ UDGND XI XO NOS# Vcc R232 NC RTS# DTR# DCD# RI# DSR# CTS# 20 19 18 17 16 15 14 13 12 11

U18 GND P0.0 P0.1 P0.2 P0.3 P0.4 P0.5 P0.6 P0.7 GND 1 2 3 4 5 6 7 8 9 10 OE D0 D1 D2 D3 D4 D5 D6 D7 GND 74HC573 U19 P2.4 P2.5 P2.6 1 2 3 4 5 6 7 8 A0 VCC A1 Y0 A2 Y1 E1 Y2 E2 Y3 E3 Y4 Y7 Y5 GND Y6 74HC138 16 VCC 15 OE1 14 OE2 13 12 CS 11 10 9 VCC Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 LE 20 VCC 19 Q0 18 Q1 17 Q2 16 Q3 15 Q4 14 Q5 13 Q6 12 Q7 11 ALE

三、I/O扩展

74HC573是74HC373的替代品,引脚分布较规则,利于布线。让LE端始终为高电平,通 过改变输给使能端的信号控制信号的通断。具体电路如图所示。地址为:低八位是 8XXXXH,高八位是9XXXXH,这里取8FFFH和9FFFH。

U21 OE1 D0 D1 D2 D3 D4 D5 D6 D7 GND 1 2 3 4 5 6 7 8 9 10 OE D0 D1 D2 D3 D4 D5 D6 D7 GND 74HC573 VCC Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 LE 20 19 18 17 16 15 14 13 12 11 VCC P0.0 P0.1 P0.2 P0.3 P0.4 P0.5 P0.6 P0.7 VCC OE2 D8 D9 D10 D11 D12 D13 D14 D15 GND 1 2 3 4 5 6 7 8 9 10

系统硬件设计

七、ISP下载电路

U20 LVCC VCC 1 2 3 switch6 6 5 4 LGND GND

ISP下载需要单片机冷启动, 即把电源和地都断开,这里 用一个六角的自锁开关实现, 其中VCC和GND为电源端, LVCC和LGND为单片机的电 源端。如图所示。

系统硬件设计

八、单片机模块电路

数据采集系统方案的确立

——常用系统介绍

3、单A/D多通道同步采集系统

这种方法能保证多路信号的同步采集,也能用于高速采样,而且电路简单,成本 不高,但是各个通道之间容易相互干扰。

本系统采用第一种方案, 即多路非同步数据采集系统

系统硬件设计

一、电源模块

之前:由于7805标准输入电压是10V,我输入的是12V,7805发热严重;

系统主要技术指标

1、输入通道数:32通道 2、信号动态范围:0—5V、0—3V、 0—10V、±5V 3、数据采样速率:2KHZ 4、ADC分辨率:12—16位 5、接口形式:USB2.0

系统设计主要包括的内容

1、数据采集系统方案的确立

2、系统硬件设计

3、系统软件设计

数据采集系统方案的确立

——常用系统介绍

RXD TXD V3_341 D+340 D-340 GND Y3

U24 GND GND GND D+ DVCC USB 6 5 4 3 2 1 GND

D+340 D-340

C18 22p

12M

C19 CH340_T 22p

如图所示是ISP下载电路。 CH340 提供了常用的串口信 号,C17容量为 4700pF到 0.02μF,用于CH340内部电 D 源节点退耦,C16容量为 0.1μF,用于外部电源退耦。 晶体Y3、电容 C18 和 C19 用于时钟振荡电路。Y3 是频 率为12MHz 的石英晶体, C18 和 C19 是容量为22pF 的独石或高频瓷片电容。它 输出的就是TTL电平,无需 再进行电平转换。

系统硬件设计

四、AD转换 选用AD转换芯片ADS7805,它是16位采样AD转换器,内置16位逐次逼近式寄 存器、采样保持器、参考电压、时钟、数字接口、信号调理电路以及三台输出驱 动电路采样频率为100KHZ(两次采样之间间隔10us),+5V单电源供电,模拟 输入范围为-10V—+10V,转换最多在8us内完成,精度也满足要求。 1、P1.5与ADS7805的R/非C 端相连,位操作,控制 ADS7805是进行AD转换还是 输出转换后的数据 2、两个并行I/O扩展芯片用来 接收ADS7805输出的高八位和 低八位数据 3、P2.4,P2.5,P2.6,P2.7 分别与74HC138的的A0,A1, A2和E3端相连,其Y0、Y1端 分别输出I/O扩展口的使能信号, 顾地址为:低八位是8XXXXH ,高八位是9XXXXH,这里取 8FFFH和9FFFH。

由于AD转换至多在8us内完成,所以可在启动转换后延时8us直接读数,ADS7805输出的为补码,补 码转原码由计算机读出数据后转换;存储数据时,从存储器的第一个存储单元开始,将数据依次存入 各个存储单元,先存低八位数据后存高八位数据;数据存储完毕后,修改模拟开关地址和存储单元地 址,以进行下一个通道的信号的AD转换并存储数据;如果数据已经存入最后一个存储单元,则下一 个数据存入第一个存储单元,如此循环下去。

1、多路非同步数据采集系统

这种方法用在被采集的多路信号之间没有严格的时序关系的时候,不适合 用来实现对高速信号的采集,也不能实现多路信号的同步采集。

数据采集系统方案的确立

——常用系统介绍

2、多A/D实现多通道并行采样系统

这种方法用于多个高频高速数据并行采集。该系统需要多片ADC芯片来实现多路 信号并行采集,各路信号基本上不互相干扰,采集速度也有明显的提高,但是由 于使用的芯片较多,导致电路结构复杂,体积庞大,而且价格昂贵。

U15 P1.5 P1.6 P1.7 RST RXD TXD INT0 INT1 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 P1.5 P1.6 P1.7 RST RXD/P3.0 INT2/P4.3 TXD/P3.1 INT0/P3.2 INT1/P3.3 T0/P3.4 T1/P3.5 WR/P3.6 RD/P3.7 XTAL2 XTAL1 GND P4.0 P2.0 P2.1 P2.2 P2.3 P2.4 STC89C52 LVCC SVCC XTAL1 12MHZ K1 R2 200 R3 10K C12 10uf RST C13 47pf C14 47pf Y2 XTAL2 P1.4 P1.3 P1.2 T2EX/P1.1 T2/P1.0 INT3/P4.2 Vcc P0.0 P0.1 P0.2 P0.3 P0.4 P0.5 P0.6 P0.7 P4.6 P4.1 ALE/P4.5 P4.4 P2.7 P2.6 P2.5 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 P1.4 P1.3 P1.2 P1.1 P1.0 LVCC P0.0 P0.1 P0.2 P0.3 P0.4 P0.5 P0.6 P0.7