第3章-4 TMS320F2407DSP芯片的结构

TMS320系列DSP原理、结构及应用

如将信号从时域转化为频域,从模拟信号转换为数字信号等。信号处理 的内容涉及广泛,尤其信号的数字处理为信号处理带来了广阔的前景。

由信号、系统和信号处理的定义,可以清晰地看到它们之间的关系, 即信号分析是基础,系统分析是桥梁,信号处理是手段,系统综合是目的。 信号处理作为手段,贯穿信号分析、系统分析、系统综合的始终。

第一章号处理是利用计算机或专用处理设备,以数字的形式对信号进 行分析、采集、合成、变换、滤波、估算、压缩、识别等加工处理,以便 提取有用的信息并进行有效的传输与应用。与模拟信号处理相比,数字信 号处理具有精确、灵活、抗干扰能力强、可靠性高、体积小、易于大规模 集成等优点。

第一章 绪论

1.1信号处理技术基础——数字信号处理

数字信号处理包括算法研究和实现方法两个方面的内容:

1.算法研究。算法研究是指如何以最小的运算量和存储器的 使用量来完成指定的任务。20世纪60年代出现的快速傅里叶变 换(FFT),使数字信号处理技术发生了革命性的变化。近几年 来,数字信号处理的理论和方法得到了迅速的发展,诸如:语音 与图像的压缩编码、识别与鉴别,信号的调制与解调、加密和解 密,信道的辨识与均衡,智能天线,频谱分析等各种快速算法都 成为研究的热点,并取得了长足的进步,为各种实时处理的应用 提供了算法基础。

第一章 绪论

1.2 DSP芯片概述

1. DSP 芯片的发展概况

DSP 芯片诞生于 20 世纪 70 年代末,至今已经得到了突飞猛进的发 展,并经历了以下三个阶段:

第一阶段,DSP 的雏形阶段(1980 年前后)。 1978 年 AMI公司生产出第一片 DSP 芯片 S2811。 1979 年美国 Intel 公司发布了商用可编程 DSP器件 Intel2920。 代表性器件主要有:Intel2920(Intel)、 PD7720(NEC)、 TMS320C10(TI)、DSP16(AT&T)、S2811(AMI)、ADSP-21 (AD公司)等

三大DSP系列结构之比较

TI公司三大系列DSP芯片内部结构之比较班级:SJ1126 姓名:张晖学号:201120195012摘要:随着数字信号处理技术和集成电路技术的发展,以及数字系统的显著优越性,导致了DSP芯片的产生和迅速发展,DSP技术的地位凸显出来。

在世界上众多的DSP厂商中,德州仪器公司的DSP始终占据着较大的市场份额(45% ~60%),本文概略的介绍目前得到广泛应用的TI三大DSP处理器系列,TMS320C2000、TMS320C5000和TMS320C6000。

关键字:TI DSP正文:一、TMS320系列DSP命名TMS 320 F 2812 PGF A温度范围(缺省为L)前缀L=0 ~70℃TMX=A=-40 ~85℃TMP=Q=-40~125℃TMS=封装形式DSP PGF=176—引脚LQFP320=TMS320系列PAG=64—引脚塑料TQFPPGE=144-引脚塑料TQFPPZ=100-引脚塑料TQFP器件型号工艺C=COMSE=COMS EPROMF=Flash EEPROMLC=Low—voltage COMS(3.3V)VC=Low—voltage COMS(3V)TMS320包括了定点、浮点和多处理器数字信号处理芯片。

主要分为三种不同指令集的三大系列:TMS320C2000、TMS320C5000和TMS320C6000。

TMS320系列中的同一子系列产品具有相同的CPU结构,只是片内存储器和片内外设配置不同,同一子系列产品的软件完全兼容。

二、TMS320C2000系列TMS320C2000是作为优化控制的DS P系列。

TMS320C2000系列DSP集成CPU核和控制外设于一体,提供了高速的ADC和PWM发生器等,集成强大灵活的特定控制接口。

C2000 DSP既具有数字信号处理能力,又具有强大的事件管理能力和嵌入式控制功能,非常实用于工业、汽车、医疗和消费类市场中数字电机控制、数字电源和高级感应技术。

第3章-1 TMS320F2407DSP芯片的结构ppt课件

MUX TRE G M u l ti p l ie r 16*16 PRE G

P r o d u c t s h i ft e r (3 2 b it s )

MUX

CAL U

C

Acc umulat or

Out put sh ifter( 32 bi ts)

输入定标单元:

32位的输入数据定标 移位器把存储器中送来 的16位值调整送至32位 的中央算术逻辑单元 (CALU)。数据调整对 于算术运算、数据定标 和逻辑运算时定标非常 必要。作为程序/数据空 间至CALU间数据通路一 部分。

算术逻辑单元(CALU

输入定标单元 乘单元 中央算术逻辑单元(CALU)

TMS320C24x的CPU与系统结构:

Data write bus(DWEB)

Data read bus(DRDB) Program read bus(PRDB)

MUX

31

16 15

0

I n p u t s h i ft e r (3 2 b i t s )

中央算术逻辑单元主 要组成部分包括:

1、中央算术逻辑单元 (CALU)

2、32位累加器(ACC)

3、输出移位器

C

input shifter

product shifter

M UX

C AL U A cc u m ul a t or

Output shifter(32 bits)

中央算术逻辑单元:

1.实现大部分的算术和逻辑运算功能。大多数 只需1个机器周期。

通用IO脚,极性可编程; CLKOUT/IOPE0:时钟输出或通用IO脚; PDPINTB* :功率驱动保护中断输入,当电机驱动不正常

DSP芯片概述

第2章TMS320C6000 DSP芯片概述本章介绍了TI公司是DSP芯片和DSP芯片的命名规则,并着重介绍了TMS320DM642的器件特性及总体原理框图。

本章的知识要点为理解TMS320DM642的原理框图构成,本章建议安排2个课时进行学习。

DSP芯片概述随着信息技术的高速发展,数字信号处理器(Digital Signal Processor,DSP)的应用范围越来越广,普及率越来越高。

DSP的应用领域主要包括:图形图像领域(如图形变换、图像压缩、图像传输、图像增强、图像识别等)、自动化控制领域(如导航和定位、振动分析、磁盘驱动、激光打印、机器人控制等)、消费电力领域(如智能玩具、扫描仪、机顶盒、VCD/DVD、可视电话、传真机等)、电子通信领域(如蜂窝电话、IP电话、无线调制解调器、数字语音嵌入等)、语音处理领域(如语音综合、语音增强、语音识别、语音编码等)、工业应用领域(如数字控制、机器人技术、在线监控等)、仪器仪表领域(如数字滤波器、函数发生器、瞬时分析仪、频谱分析仪、数据采集仪器等)、医疗器械领域(如诊断设备、助听器、病情监控器、心电图设备、超声设备等)、军事领域(如导弹制导、导航、雷达、保密通信等)。

因此,DSP在当今电子通信类产品中起到了不可或缺的作用。

2.1.1主要类型DSP芯片主要分为以下两大类:(1)专用DSP芯片。

这类芯片被设计和加工成独立的电路模块,只能完成功能单一的任务,它们的使用场合比较特殊,通常应用于高速信号处理环境中,如执行FFT运算、数值滤波运算、卷积运算等,专用DSP芯片通过硬件逻辑实现信号处理算法,而不是采用内部编程的方法,这种机制保证了专用DSP芯片的执行效率、提高了其运算速度,专用DSP芯片在应用中无须程序设计。

只要根据其功能设计外围电路即可。

(2)通用可编程数字信号处理器(Programmable Digital Signal Processor)。

2407的硬件总结

6. 64k的外部sram是用来仿真的,仿真完后可以用来当数据存储器,2407的flash老是有人说容易坏,可是我看了一个帖子,有个家伙没有结外部sram,他就是靠烧flash调试的,他也没说坏,我认为容易坏的原因可能是cmd文件没写对,没有避开40h的密码保护,所以烧了一次就不让烧了。

a. 如果用外部程序flash,现在的flash的速度都不能和2407的内部flash相比,都要等待,这样dsp的速度会慢下来

b. 如果用sram代替flash,用bootload启动,倒是可以

3. 问:R/W干什么用的?本菜鸟认为:既然有了RD#跟WE#,就可以完成读和写了;那么R/W还有什么用呢?

三 JTAG口

照图连吧

四 pll锁相环 时钟

1.低频的时钟倍频上去,时钟会产生jitter,所以要滤波.他的电源是和dsp的core与io电压是分开的

3.JPG (15.01 KB)

2007-11-7 09:32

4.JPG (84.06 KB)

b. 开发板上的3.3v分了支(图表 1),如图P33页。一个是专门给电源引脚用的,注意这里的电源加了bead,图上为dsp3.3v,还有一个3.3v,是给其它方面用的,例如pll锁相电压供电,参考电压供电

1.JPG (32.42 KB)

2007-11-7 09:32

2007-11-7 09:32

2.时钟

a. external reference crystal clock option

这里的crystal,就是无源的晶振,他和2407内部的反向器构成振荡电路

b. external reference oscillator clock option

《DSP控制技术》课程教学大纲

DSP控制技术课程教学大纲DSPContro1Techno1ogy学时数:48其中:实验学时:8学分数:3适用专业:普通本科电气工程与自动化专业一、课程的性质、目的和任务本课程是电气工程与自动化本科专业的的专业选修课。

数字信号处理己发展成一门理论与实践紧密结合的、应用日益广泛的、迅速替代传统模拟信号处理方法的、具有丰富器件支持的先进技术和方法。

DSP 器件是数字信号处理技术的最佳载体。

了解和掌握数字信号处理的实用技术对电气类学生而言,显得越来越重要且迫切。

数字信号处理器是微处理器技术发展的一个重要分支,处理的高速性和高集成度和在信号处理方面的卓越性能,使其在IT业界的用途越来越广。

本课程正是顺应这一发展方向而为电气工程与自动化本科专业学生开设的专业选修课。

本课程的目的是使该专业学生在数字信号处理器件及应用方面具有一定的基础知识,掌握DSP的结构、工作原理、特性、应用及发展方向,使该专业毕业生在工作中具有利用DSP 开发产品和解决实际问题的基本能力。

二、课程教学的基本要求本课程以TMS320F2xx为蓝本,剖析TMS320'C2000系列数字信号处理器的结构、内部资源、运行方式和指令系统、开发系统。

借鉴DSP系统实例,要求学生了解DSP的原理、用途和性能,了解软件集成开发环境的使用,掌握采用DSP进行工程项目开发的过程和软硬件调试工具的使用,熟练掌握使用汇编/C语言编写应用处理程序的方法。

本课程总学时为48学时,3学分,其中课堂教学为40学时,实验教学8学时,在第七学期完成。

三、课程的教学内容、重点和难点第零章绪论(4学时)基本内容:数字信号处理器的特点,DSP器件的发展,DSP器件的特点,DSP与其它微处理器的比较,DSP器件的应用领域,DSP应用系统设计,Mat1ab在DSP应用系统中的作用。

第一节数字信号处理器第二节专用DSP和DSP-IP核第三节通用DSP器件第四节小结基本要求:1. 了解数字信号处理器的特点2. 了解DSP器件的发展,DSP器件的特点;3. 了解DSP器件的应用领域,掌握DSP应用系统设计流程;4. 了解Uat1ab在DSP应用系统中的作用。

DSP课件第二章TMS320LF240x硬件结构

当片内外设产生中断时,CPU响应中断并执行相应的中断服务程序 对片内外设进行操作。

05

TMS320LF240x的电源管理和低功耗

模式

电源管理单元

电源管理单元(PMU)是TMS320LF240x芯片中的一个重要组成部分,负责控制芯 片的电源供应和功耗管理。

PMU包含多个电源域,可独立控制各个电源域的开启和关闭,以实现灵活的功耗管 理。

较

他设备进行数据交换,可配 置为发送或接收模式。

器

比较器用于检测电压或电平 是否达到预设值,输出电平

可配置为高或低,常用于 PWM控制或阈值检测。

看门 狗定 时器

片内外设的访问方式

直接访问

通过特定的寄存器地址直接读写片内外设的控制寄存器和数据寄 存器。

间接访问

通过特定的寄存器地址读写片内外设的控制寄存器来配置片内外设, 再通过数据寄存器进行数据传输。

PMU还具有过压和欠压保护功能,以确保芯片在异常电源条件下能够安全运行。

低功耗模式

TMS320LF240x支持多种低功 耗模式,以便在不需要时降低芯

片功耗。

低功耗模式通过关闭不需要的内 部时钟和电源域来实现功耗降低。

在低功耗模式下,芯片的某些功 能将被禁用,但仍可以响应外部 事件或中断,并在必要时唤醒。

需求。

输入输出电平

02

TMS320LF240x的输入输出电平一般为CMOS电平,能够与

TTL和CMOS电路兼容。

驱动能力

03

TMS320LF240x的驱动能力较强,能够驱动较大规模的外部电

路。

封装形式

• TMS320LF240x的封装形式一般为塑封或陶瓷封装,具体 取决于应用需求和生产厂家。

DSP应用技术教程 部分习题答案

《TMS320C54x DSP应用技术教程》部分习题答案注意:未提供的参考答案习题(因考试为开卷形式,部分在课堂讲过,部分需要自行思考归纳总结或编程),请参考PPT和书上示例,自行解答。

第1章绪论1.简述Digital Signal Processing 和Digital Signal Processor 之间的区别与联系。

答:前者指数字信号处理的理论和方法,后者则指用于数字信号处理的可编程微处理器,简称数字信号处理器。

数字信号处理器不仅具有可编程性,而且其数字运算的速度远远超过通用微处理器,是一种适合于数字信号处理的高性能微处理器。

数字信号处理器已成为数字信号处理技术和实际应用之间的桥梁,并进一步促进了数字信号处理技术的发展,也极大地拓展了数字信号处理技术的应用领域。

2.什么是DSP技术?答:DSP技术是指使用通用DSP处理器或基于DSP核的专用器件,来实现数字信号处理的方法和技术,完成有关的任务。

5.数字信号处理的实现方法有哪些?答:参见P3-4 1.1.3节。

6.DSP的结构特点有哪些?答:哈佛结构和改进的哈佛结构、多总线结构、流水线技术、多处理单元、特殊的DSP指令、指令周期短、运算精度高、硬件配置强。

7.什么是哈佛结构和冯洛伊曼结构?它们有什么区别?答:参见P5-6 1.2.2节。

8.什么是哈佛结构和冯.诺依曼结构?它们有什么区别?答:DSP处理器将程序代码和数据的存储空间分开,各空间有自己独立的地址总线和数据总线,可独立编址和独立访问,可对程序和数据进行独立传输,这就是哈佛结构。

以奔腾为代表的通用微处理器,其程序代码和数据共用一个公共的存储空间和单一的地址和数据总线,取指令和取操作数都是通过一条总线分时进行的,这样的结构称为冯·诺伊曼结构。

采用哈佛结构,可同时取指令和取操作数,并行地进行指令和数据的处理,从而可以大大地提高运算的速度,非常适合于实时的数字信号处理。

而冯·诺伊曼结构当进行高速运算时,取指令和取操作数是分时操作的,这样很容易造成数据传输通道的瓶颈现象,其工作速度较慢。

TMS320LF2407DSP结构、原理及应用

TMS320LF2407 DSP结构、原理及应用实验指导书重庆大学――美国德州仪器公司数字信号处理解决方案实验室2003年8月前言美国TI公司推出的DSP微控制器TMS320LF2407芯片具有低成本、低功耗、高性能的处理能力,是电机数字化控制的升级产品,体现了单芯片微控制器工业的新趋势。

随着数字信号处理这一新学科的飞速发展及教学的需要,特编写了此实验指导书。

DSP理论和技术是目前电子技术和IT领域中的一门基本工程理论与核心技术,它既有较为完整的理论体系,又以最快的速度形成自己的产业。

实际上,数字信号处理是紧紧围绕着理论、实现及应用三方面迅速发展起来的,它以众多的学科为理论基础,其成果又渗透到众多学科,成为理论与实践并重、在高新技术领域中占有重要地位的新兴学科。

DSP器件的出现,为数字电路方法实现工程系统提供了坚实的技术基础。

在数字信号处理的工程领域中,工程实际更关心的是DSP应用技术,所以,检验数字信号处理理论和技术的基本工程标准,就是能否在工程实际中应用先进的理论,将理论变成一种实际应用技术。

作为工程应用技术,其理论意义体现在应用中。

如果不能在工程实际中应用,再好的理论也是没有用的。

因此,对于学生来说,DSP技术的学习,必须以应用为目标,必须在相应的理论基础之上,应用DSP技术。

为此,本实验指导书通过提供一些基本实验帮助学生迅速学会如何应用DSP 技术和方法,从而达到学习DSP应用开发技术的目的。

本书结合编者的开发应用试验,选用TI公司的DSP微控制器TMS320LF2407芯片为实验对象,以Code Composer Studio (CCS)-TMS320集成调试环境、XDS510硬件仿真器以及自制2047实验装置作为该芯片的开发硬件和软件工作平台和工具,为数字信号处理器的开发创建了较好的软、硬件的工作环境,在帮助学生熟悉DSP微控制器TMS320LF2407芯片应用与开发的基本技能和汇编程序调试技巧的基础上,更为方便地应用所学知识并在控制应用系统的产品设计的开发得到充分的展示,以求学生在未来能够顺利地投入到开发产品的工作中,并能够通过各种渠道,如公司产品技术手册和网上查询,以获得最新器件、最佳技术来为设计自己的产品系统服务。

第四章 TMS320系列DSP芯片概述

4.1

1

TMS320C2xx系列 DSP

4.1.2 TMS320F206引脚与兼容性

TMS320F206 的引脚

引脚名

引脚 类型 说明 号 D0~D2 38~41 I/O/ 并行数据总线D15[最高有效位 (MSB)] 到D0[最低有效位(LSB)]。 D3~D6 26~29 Z 多路转换TMS320F206和外部数据 D7~D10 31~34 空间/程序空间或I/O空间之间的数 D11 36 据。当无输出(R/ W 为高)、 RS 保 D12~D15 38~41 持, OFF =0时变成高阻。

大连理工大学出版社

4.1

4.1.3 片内资源

1

位

TMS320C2xx系列 DSP

模式寄存器PMST

大连理工大学出版社

4.1

4.1.3 片内资源

1

位 15~13

TMS320C2xx系列 DSP

寄存器及相关功能说明

状态寄存器ST0

名称 ARP 说明 当前ARx寄存器号,x=0~7

12

11

OV

OVM

算术逻辑单元ALU溢出时为1

溢出模式位,OVM=0时,对溢出不作处理,OVM= 1时,将溢出数据置为最大正数/负数,即饱和

12

CNF

片内RAM设置,CNP=0时,片内双存取RAM的B0块和 B1块映射为数据空间。CNF=1,则B0和B1映射为程序 空间。复位后,CNP=0

测试/控制位,当BIT,BITT, CMPR, NORM指令测的条 件成立时,TC=1, 否则,TC=0。可用于条件跳转、调用 和返回。

大连理工大学出版社

...

...

大连理工大学出版社

TI公司DSP系列概述

Printer Print head control Paper path motor control

Digital Power Supply Provides control, sensing, PFC, and other functions

DSL modems Pooled modems Base station transceivers Wireless LAN Enterprise PBX Speech recognition Multimedia gateway Professional audio Networked camera Machine vision Security identification Industrial scanner High speed printer Advanced encryption

12-Bit ADC

Watchdog

GPIO

Peripheral Bus

McBSP

CAN 2.0B

SCI-A

SCI-B

SPI

Event Managers Ultra-Fast 12-bit ADC 16.7 MSPS Conversion Speed Dual s/h enable simultaneous sampling Auto Sequencer, up to 16 conversions w/o CPU

第二部分:TI DSP概述

DSP芯片产品简介

TI公司的DSP芯片概况 其它公司的DSP芯片概况 TMS320C2000概况

TI公司的DSP芯片概况

经典产品 TMS320C1X、TMS320C25、TMS320C3X/4X、TMS320C5 X、TMS320C8X 目前主流系列 TMS320C2000,用于数字化控制领域 TMS320C5000,用于通信、便携式应用领域 TMS320C6000,音视频技术、通信基站

dsp 第三章2

’C54x存储器操作的各种情况: ③ 执行写单操作数指令 例如:STH

预取指P 加载 PAB 取指F

A,*AR1

译码D 寻址A

;单周期指令, 写单操作数 读数R 执行/写数

通过PB 通过IR 读取指令 指令译码

写地址 数据 加载EAB 写至EB

8

第3章 TMS320C54x的硬件结构

’C54x存储器操作的各种情况: ④ 执行写双操作数指令 例如:DST

i5或NOP a5

i5

X R i5的条件执行 PAB=a5 PB=i5 PB=i5 ;任意单周期,单字指令

T6:XC指令寻址级,求解XC指令的条件。 T4:对XC指令进行取值; T3:XC指令地址a3加载PAB; 注意:① 决定XC指令判断条件的指令应放在i1指令之前; 如果XC指令的判断条件由指令i1和i2的结果给出,则 在T6周期,i1和i2指令还没执行完毕,执行结果不会 若条件满足,则i4和i5指令进入译码级并执行; 会得出错误的判断。 对XC指令的条件判断产生影响。 ② 在条件执行指令前屏蔽所有可能产生的中断或 若不满足,则不对i4和i5指令译码,执行NOP。 其他改变指令规定条件的运算。

1

第3章 TMS320C54x的硬件结构

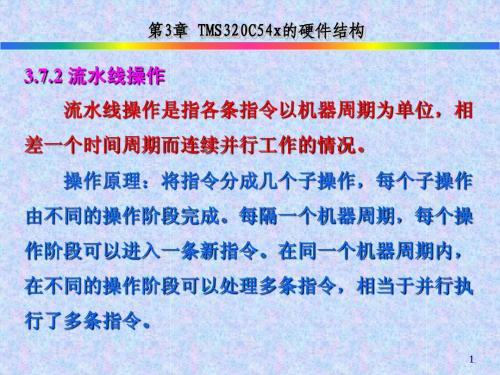

3.7.2 流水线操作 1. 流水线操作的概念

’C54x的流水线操作是由6个操作阶段或操作周

期组成。在任何一个机器周期内,可以有1 ~ 6条不

同的指令在同时工作,每条指令可在不同的周期内

工作在不同的操作阶段。

2

第3章 TMS320C54x的硬件结构

1. 流水线操作的概念 六个操作阶段: ① 预取指P; ③ 译码D; ⑤ 读数R; 流水线结构:

T1 a1,a2 P T2 T4 T5 T6 T7 T8 T9 T10 BF b1 T3 ;四机器周期,两字的无延迟分支转移指令 D A R X

《DSP原理及应用》课件第3章 浮点DSP芯片TMS320VC

内部总线的并行性高性能

程序指令总线可在一个机器周期内取 一个指令字

数据总线在一个周期内可进行两次存 储器操作

3.2 TMS320VC33的硬件结构

2) TMS320VC33的内部结构(续)

存储器和片内I/O设备

`VC33片内的设备和存储器统一编址

外部存储器接口具有32位数据线,24

程序指令总线:指令地址总线

(PADDR)和指令数据总线(PDATA)

数据总线:数据地址总线(DADDR1-2) 数据总线

`VC33内部结构及总线连接

3.2 TMS320VC33的硬件结构

2) TMS320VC33的内部结构(续)

3.2 TMS320VC33的硬件结构

1) TMS320VC33的引脚及其功能 (续)

控制信号 (续)

SHZ#:关闭高阻抗

XF1,XF0:外部标志。用做通用I/O

或支持被互锁的处理器指令

3.2 TMS320VC33的硬件结构

1) TMS320VC33的引脚及其功能 (续)

同步串行口信号

3.1 TMS320VC33的性能指标

1) TMS320VC33 简介(续)

总存储空间:16M×32位

具有程序引导传送功能 具有4个内部译码页码选择信号PAGE0#PAGE3#,可大大简化与I/O及存储器的 接口 外部中断可选择边沿触发方式和电平触 发方式

3.1 TMS320VC33的性能指标

2) TMS320VC33的内部结构(续)

外围设备

时钟有两种产生方法

•

•

片内振荡器:XIN和XOUT外接晶 振,EXTCLK接地 片外直接输入时钟:由EXTCLK 输入,XIN接地,XOUT悬空

DSP理论和实践能力培训-经典

一、DSP入门培训第一章DSP芯片基本结构与特点1 DSP简介1.1 什么是DSP?1.2 为什么要使用DSP?1.3 DSP芯片的发展简史2 DSP芯片的基本结构2.1 DSP的结构特征2.2 DSP与MCU、PC的区别3 TMS320系列DSP产品介绍3.1 C2000系列3.2 C5000系列3.3 C6000系列4 DSP的学习建议第二章DSP2407引脚与内部结构1、DSP2407引脚与内部结构2、TI公司的DSP命名规则3、DSP2407内部包含哪些成分?4、CPU结构5、存储器及存储空间配置第三章DSP最小系统介绍3.1DSP最小系统电源结构与要求3.2晶体振荡器电路3.3JTAG接口3.4片外存储器扩展3.5最小系统其他引脚处理与说明3.6最小系统摸板第一章DSP芯片基本结构与特点1、DSP简介1.1 什么是DSP?从20世纪60年代数字信号处理理论的崛起,到20世纪80年代数字信号处理器的产生,DSP 芯片和技术飞速发展.如今已广泛应用在社会各领域,如汽车,数码相机,MP3和手机都是日常生活中DSP的典型应用.1.2 为什么要使用DSP?传统的信号处理是用电阻、电容、电感、二极管、三极管等分立元件完成的,在模拟电路中不能完全消除误差;而在数字信号处理器中,我们用逻辑电平1、0来表示电路中电压的状态,实时运行和存储数据不存在误差,且工作稳定,可靠。

1.3 DSP芯片的发展简史⑴C2000系列芯片的发展简史在C2000系列中,TI公司最早推出的是16位定点产品,其中TMS320F240是1996年推出的C/F24x系列中第一款带有Flash的DSP.运算速度高达20MIPS.之后TI公司先后推出主频为30MHz的LF/LC240x系列和主频为40MHz的LF/LC240xA系列.★其中C/F24x系列和LF/LC240x系列这2个子系列合称为C24xx系列.在C24xx系列的基础上,推出了F/C281x系列.⑵C2000 DSP的分类比较相同系列中的所有芯片,都有相同的CPU结构,区别在于片内存储器容量大小和片内外设种类的多少不同. C24xx系列中,LF2407A片内存储器容量最大,片内外设最多.⑶F/C281x系列功能简介TMS320X281x是TI公司推出的C2000系列中新一代32位定点数字信号处理芯片.该系列芯片每秒可以执行1.5亿次指令(150MIPS),与TMS320F24x/LF240x的源代码和部分功能相兼容,进一步扩大了TMS320C2000的应用范围.⑷F/C281x与C240x内核的比较F/C281x系列的DSP内核称之为C28x,与此对应,C240x系列的DSP内核称之为C2Xlp. C28x 兼容了C2Xlp.当AMODE=1时, C28x与C2Xlp工作方式完全一样,只不过寻址范围从16位增加到了32位;当AMODE=0时, C28x工作在崭新的模式下.C28x与C2Xlp的主要区别2、DSP芯片的基本结构2.1 DSP的结构特征1) 专用硬件乘法器在通用微处理器件中,乘法是由软件实现的.它实际上是由时钟控制的一连串的<移位-加法>操作,乘法操作需要100个左右的时钟周期.而用DSP来处理,可以使乘法运算在一个单指令周期内完成.2) 采用总线哈拂结构传统的微处理器采用的是冯诺依曼结构:统一的程序和数据空间,共享的程序和数据总线.而DSP采用的总线哈拂结构,可在一个时钟周期内同时读取程序和存取操作,速度大为提高.3)流水线在CPU内,每条指令的执行分为取指,解码和执行3个阶段.流水线处理使得若干条指令的不同执行阶段并行执行,从而提高程序的执行速度.2.2 DSP与MCU、PC的区别MCU的速度较慢;CPU体积较大,功耗较高。

DSP原理及应用第三章

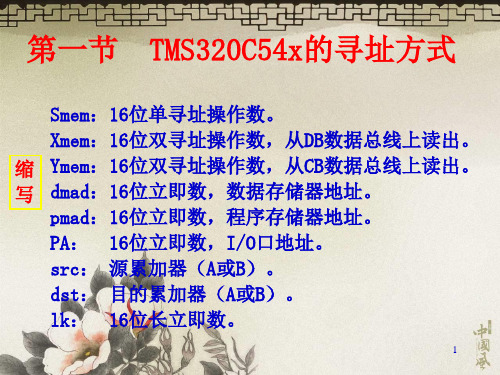

15~8 7 6~0

操作码

I=0

dmad

堆栈指针SP

16位堆栈指针SP

SP+dmad

16位数据 存储器地址 16位SP+dmad 高 9位

dmad

低 7位

15

DP地址的范围是从0~511(29-1),将存储器分成 512页。 7 位 dmad 范围是从 0~127 ,每页有 128 个可以访 问的单元。 以DP为基准的直接寻址是由DP 值确定是 512 页中 的哪一页,由dmad确定是该页中的哪一个单元。 SP 可以指向存储器中的任意一个地址。 dmad 可 以指向当前页中具体的单元,从而允许访问存储器 任意基地址中的连续的128个单元

循环寻址的有效地址计算

循环缓冲区的参数主要包括:长度寄存器 (BK)、有效基地址(EFB)、尾地址(EOB)。 N>32, 则N=6。 例如:缓冲区长度 R=32 , 若 2 BK:定义了循环缓冲区的大小R。大小为R的循环缓冲 缓冲区开始的地址: xxxx xxxx xx00 0000 B 器其地址要始于最低 N位为零的地址。并且 R要满足下 缓冲区长度 N>R 装入循环缓冲长度寄存器BK中。 面的条件: 2R=32 EFB:循环缓冲器的有效基地址(EFB)就是用户选定 的辅助寄存器(ARx)的低N位置 0后所得到的值。 EOB:是通过用BK的低N位代替ARx的低N位得到。

LD

*(BUFFER),A

9

绝对寻址总结

16位地址表示形式: ① 地址符号,如:TABLE; ② 16位数值,如:89AB、1234。 特点:指令中包含一个固定的16位地址,能寻 址所有数据、程序和I/O存储空间,但 运行速度慢,需要较大的存储空间。 用途:用于对速度要求较低的场合。

电压电流调理电路

2常用采样电路设计方案比较配电网静态同步补偿器(DSTATCOM)系统总体硬件结构框图如图2-1所示。

由图2-1可知DSTATCOM的系统硬件大致可以分成三部分,即主电路部分、控制电路部分、以及介于主电路和控制电路之间的检测与驱动电路。

其中采样电路包括3路交流电压、6路交流电流、2路直流电压和2路直流电流、电网电压同步信号。

3路交流电压采样电路即采样电网三相电压信号;6路交流电流采样电路分别为电网侧三相电流和补偿侧三相电流的电流采样信号;2路直流电压和2路直流电流的采样电路DSTATCOM的桥式换流电路的直流侧电压信号和电流信号;电网电压同步信号采样电路即电网电压同步信号。

信号调理TMS320 LF2407ADSP键盘显示电路电压电流信号驱动电路保护电路控制电路检测与驱动电路主电路图2-1 DSTATCOM系统总体硬件结构框图2.1常用电网电压同步采样电路及其特点2.1.1 常用电网电压采样电路1从D-STATCOM的工作原理可知,当逆变器的输出电压矢量与电网电压矢量幅值大小相等,方向相同时,连接电抗器内没有电流流动,而D-STATCOM 工作在感性或容性状态都可由调节以上两矢量的夹角来进行控制,因此,逆变器输出的电压矢量的幅值及方向的调节都是以电网电压的幅值和方向作为参考的,因此,系统电压与电网电压的同步问题就显得尤为重要。

图2-2 同步信号产生电路1从图2-2所示同步电路由三部分组成,第一部分是由电阻、电容组成的RC滤波环节,为减小系统与电网的相位误差,该滤波环节的时间常数应远小于系统的输出频率,即该误差可忽略不计。

其中R5=1K ,C4=15pF,则时间常数错误!未找到引用源。

<<l ms,因此符合设计要求;第二部分由电压比较器LM311构成,实现过零比较;第三部分为上拉箝位电路,之后再经过两个非门,以增强驱动能力,满足TMS320LF2407的输入信号要求[1]。

2.1.2 常用电网电压采样电路2常用电网电压同步信号采样电路2如图2-3所示。

第三章 TI TMS320C2000系列DSP存储器及输入输出空间(“存储器”相关文档)共7张

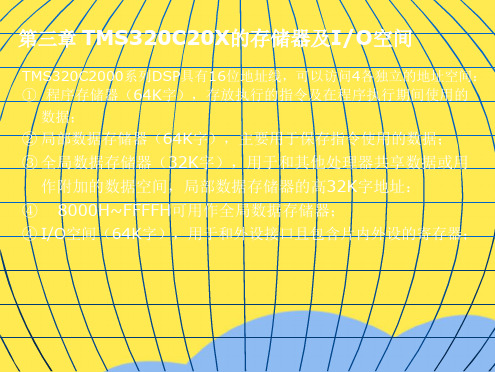

第三章 TMS320C20X的存储器及I/O空间

TMS320C2000系列DSP具有16位地址线,可以访问4各独立的地址空间: ① 程序存储器(64K字),存放执行的指令及在程序执行期间使用的

数据;

② 局部数据存储器(64K字),主要用于保存指令使用的数据; ③ 全局数据存储器(32K字),用于和其他处理器共享数据或用

片内16K flash(1) C全N局F数=1据,存片储内器B0(块3D2KA字RA)M,用于和其他处理器共享数据或用作附加的数据空间,局部数据存储器的高32K字地址: CNF=01保,留片,内CB0N块F=D1A片RA外M 8片0内001H6~KFfFlaFsFhH(0可) M用P作/M全C局=0数据存储器; PON=0,片外4K ROM 800040H~F3FFFhH可用作全局数据存储器; C片N内F=41K,S片AR内ABM0(块PDOANR=A1M) 片CN内F1=61K,片fla内shB(0块1)DARAM CNF=01保,留片,内CB0N块F=D1A片RA外M TMS320F206程序存储器空间映像 CNF=0保留,CNF=1 片外 I8/0O0空0H间~(FF6F4FKH字可)用,作用全于局和数外据设存接储口器且;包含片内外设的寄存器; CNF=0保留,CNF=1 片外 片内16K flash(1) CNF=01保,留片,内CB0N块F=D1A片RA外M

900H~FDFFH FE00H~FEFFH FF00H~FFFFH

片内16K flash(0) MP/MC=0 片内16K flash(1) MP/MC=0 片内 4K SARAM(PON=1) PON=0,片外4K ROM 片外ROM CNF=0保留,CNF=1 片外 CNF=1,片内B0块DARAM CNF=0,片外ROM

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3.7.2 串行通信接口的物理描述(续)

(7)两种唤醒多处理器模式: 空闲线唤醒、位寻址唤醒 (8)半双工或全双工。 (9)双缓冲接收和发送功能。 (10)发送和接收操作均可通过中断或查询操作进 行 (11)非归零格式(NRZ)

主要包括以下部件: (1)发送器-TX: SCITXBUF-发送数据缓冲寄存器,存发送数据。 TXSHF-发送移位寄存器,每次1位送到SCITXD引脚 (2)接收器-RX: RXSHF-接收移位寄存器,每次1位将SCITXD引脚上的数 据移入。 SCIRXBUF-接收数据缓冲寄存器,存RXSHF接收到数据 (3)一个可编程的波特率发生器。 (4)控制和状态寄存器(映射在数据存储器区) 返回首页

返回首页

自动排序器的操作原理(单排序器(16状态,级联))

返回首页

自动排序器的操作原理(双排序器(2个独立的8状态排序器))

返回首页

自动排序器的操作原理

规定排序器的状态如下: 排序器SEQ1:CONV00-CON07 排序器SEQ2:CONV08-CON15 排序器SEQ: CONV00-CON15 CONVnn位为4位长,可指定16通道中的任何一个。 转换触发特性: SEQ1:软件、EVA、外部引脚,仲裁优先级高于SEQ2 SEQ2:软件、EVB,仲裁优先级低于SEQ1 SEQ: 软件、EVA、EVB、外部引脚,无仲裁优先级

返回首页

(1)连续自动排序的模式

以双排序工作方式为例 此模式, SEQ1/SEQ2在一次排序过程中,可对任 意通道的8个转换进行自动排序。 转换结果被保存到8个结果寄存器(SEQ1为 RESULT0-RESULT7,SEQ2为RESULT8- RESULT15)。

返回首页

(1)连续自动排序的模式(续)

返回首页

(2)排序器的启动/停止模式(续)

在这种情况下,MAX CONV1的值被设置为2, 并且ADC模块的输入通道选择排序控制寄存器 (CHSELSEQn)应为:

返回首页

(2)排序器的启动/停止模式(续)

复位和初始化之后,SEQ1等待一个触发源信号。 第一个触发源到来之后,执行通道选择值为 CONV00(I1 )、CONV01(I2 )和CONV02(I3 )的3个转 换,然后,SEQ1在当前状态等待另一个触发源信号 。当第二个触发源到来后25为微秒,ADC模块开始 另外3个转换,通道选择值为CONV03(V1)、 CONV04(V2)和CONV05(V3)。

3.6.1 ADC模块的寄存器

返回首页

3.6.1 ADC模块的寄存器

返回首页

3.6.1 ADC模块的寄存器

返回首页

3.6.1 ADC模块的寄存器

返回首页

3.6.2 ADC转换模块概述

自动排序器的操作原理 2个8状态排序器SEQ1和SEQ2,也可级联成一个16状态 排序器SEQ。 状态:排序器可以执行的自动转换数目。 ADC模块能对一序列转换自动排序。转换结束后,结 果依次保存在RESULT0、RESULT1……中。 用户也可对同一通道进行多次采样,即“过采样”,得 到的采样结果比传统的单采样结果分辨率高。 根据信号处理理论,如果以比输入信号截频高很多的采样频 率采样,并辅以适当的数字滤波器,可以达到比原AD转换器更 高的采样精度,这种技术就是过采样技术.

在一个排序中的转换个数受寄存器MAXCONV中 的一个3位域或4位域控制。它的值在自动排序转 换开始时被自动装载到自动排序寄存器 (AUTO_SEQ_SR)的排序计数器状态域 (SEQCNTR3∼0)。 MAXCONV中的3位域有一个在0∼7范围的值,当 排序器从状态CONV00开始依次进行。 SEQCNTRn位从装载值开始向下计数直到 SEQCNTRn为0。

返回首页

(1)连续自动排序的模式(续)

例:使用SEQ1的双排序模式中的A/D转换。 假设SEQ1要完成7个通道的转换(通道2、3、2、3、6 、7和12经过自动排序后转换),则MAXCONV1的值应 该设置为6,且CHSELSEQn寄存器的设置如下:

返回首页

(1)连续自动排序的模式(续)

一旦转换启动(SOC)触发器被排序器收到后,转换立即开 始。SOC触发器载入在SEQCNTRn位。在CHSELSEQn寄 存器指定的通道已预先决定的顺序进行转换。每个转换结束 后,SEQCNTRn位自动减少1。当SEQCNTRn达到0时,将 根据ADCTRL1寄存器的连续运行(CONT RUN)位状态,发 生以下事情: (1)如果CONT RUN位置1,转换排序自动再次启动( SEQCNTRn重载MAXCONV1中的初始值,且SEQ1状态被 置于CONV00)。在这种情况下,必须确保在下一次转换排 序之前读取结果寄存器。 返回首页

ADC模块的特性(续)

(7)16个存放结果的寄存器(RESULT0∼RESULT15) (8)有多个启动ADC转换的触发源如下: 软件立即启动 EVA事件管理器启动 EVB事件管理器启动 ADC 的SOC引脚启动 (9)EVA和EVB可分别独立地触发SEQ1和SEQ2(仅用 于双排序器模式) (10)有单独的预定标的采样/保持时间 返回首页

3.6.3 输入触发器描述

每一排序器都有一组能被使能或禁止的触发源。

返回首页

3.6.4 ADC时钟预定标

2407A器件的采样和保持(S/H)模块可以调整来适应 输入信号的阻抗的变化,这可以通过改变ADCTR1寄存器中 的ACQ PS3~ ACQ 0位段域和CPS位来实现。模拟到数字的 转换可以被分成两个时间段:

返回首页

(2)排序器的启动/停止模式

在此模式,可实现和多个转换/启动触发器时间上 同步。这种模式和上例基本相同,但是排序器完 成一个转换序列之后,可以在没有复位到初始状 态CONV00情况下,被重触发。因此当一个转换 排序结束后,排序器停留在当前的转换状态。 ADCTRL1寄存器的连续运行位必须设置为0(禁 止)。

3.7.4 SCI模块的寄存器地址

返回首页

3.7.5 可编程的数据格式

串行通信接口可的数据无论是接收还是发送都采 用NRZ(非归零)格式, NRZ包括以下组成部分: • 一个起始位 • 1-8个数据位. • 一个奇偶校验位或无奇偶校验位 • 1-2个停止位 •一个从数据中识别地址的附加位(仅用于地址模式)。

3.7.1 串行通信接口(SCI)

内部有一个串行通信(SCI)接口模块,来实 现与其它外设之间的串行数据通信。波特率 可编程。 SCI的发送器与接收器都是双缓冲的。各自 有工作使能和中断控制。可工作于全双工模 式

返回首页

3.7.2 串行通信接口的物理描述

返回首页

3.7.2 串行通信接口的物理描述(续)

返回首页

(1)空闲线模式

空闲线模式在地址字节前留有一段静空间。该模式 没有一个附加的地址/数据位。,在处理包含多于10 个字节的数据块的情况下,其效率比地址位模式更高。 空闲线模式应用于典型的非多处理器的SCI通信。 在空闲线多处理器协议中(ADDR/IDLE M0DE= 0)。在一个帧之后,十个或者更多的高电平位的交 闲时间表明了一个新的块的开始。

返回首页

(2)排序器的启动/停止模式(续)

在第2个自动转换完成店,ADC的结果寄存器的 值如下 :

返回首页

(2)排序器的启动/停止模式(续)

完成第二个触发源转换后,SEQ1在当前 状态等待另一个触发源到来。用户可以通过软 件复位SEQ1到CONV00,并重复同样的触发 源1、2转换操作。

返回首页

返回首页

3.7.5 可编程的数据格式(续)

数据的基本单位被称作一个字符,为1-8位的字长。 数据的每个字符格式化为1个起始位,1-2个停止位和 可选的奇偶校验位和地址位,如下图所示。 注意:带有格式化信息数据的一个字符称为一个帧。

返回首页

3.7.6 SCI多处理器通信

多处理器通信即一条串行线上只能有一个信息源。 地址字节 信息源发送的数据块的第一个字节包括一个地址字节, 它被所有的接收器读取,但只有地址正确的接收器 才能被紧随地址字节后面的数据字节中断,地址不 正确的接收器不被中断,直到下一个地址字节。 SLEEP位 串行线路上的所有处理器将它们的串行通信接口的 SLEEP位(SClCTL1.2)设置为1,这样当仅在检测到地 址字节时才被中断。当一个处理器读取到的一个数 返回首页

(1)连续自动排序的模式(续)

(2)如果CONT RUN位没有被置位,则排序会停留在过去 的状态(例如CONV06),并且SEQCNTRn继续保持0值。 因为每次SEQCNTRn位达到0时,中断标志会被置1。如 果需要,用户可使用ADCTRL2寄存器的RSTSEQn位,在中 断服务程序(ISR)中手动复位排序器,以便下一次转换启动 时,SEQCNTRn位可以重载MAXCONV1的初始值,且 SEQ1状态被设置为CONV00。 这一特性在排序器的启动/停止操作中很有用。

DSP(芯片)原理与应用

主讲人:杨海柱

第三讲 TMS320F2407DSP芯片的结构

3.1 DSP2407概述 3.2 系统配置和中断 3.3 时钟和低功耗模式 3.4 数字输入输出 3.5 事件管理器 3.6 模数转换ADC模块 3.7 串行通信接口SCI 3.8 串行外设接口SPI 3.9 CAN接口 3.10 看门狗

返回首页

3.6.5 ADC校准

校准模式可以计算ADC模块的零、中值和最大 值的偏置误差。该偏置误差的二进制补码被载入 CALBRATION寄存器(二进制补码操作仅对负误差 有用)。此后,ADC硬件自动将偏置误差加到转换 值上。

返回首页

第三讲 TMS320F2407DSP芯片的结构

3.1 DSP2407概述 3.2 系统配置和中断 3.3 时钟和低功耗模式 3.4 数字输入输出 3.5 事件管理器 3.6 模数转换ADC模块 3.7 串行通信接口SCI 3.8 串行外设接口SPI 3.9 CAN接口 3.10 看门狗