OrCAD图文教程:总线用法

OrCAD图文教程

2. 选中菜单->browse 这里可选浏览parts、 neparts

选择parts,弹出浏览属 性对话框,选择默认即可。 OK,打开工程中用到的所有元件列表窗口。 在该窗口中,双击某一个 元件的reference,则可 以打开原理图相应页面, 同时该元件高亮显示。 如图所示,这样可以方便 的定位某一元件。

修改网络名称,赋给相应电压等级。

浏览命令中其他的命令使用也类似。在 画完原理图后全面检查阶段很有用。

创建元件库

通常在画原理图时,需要自己生成所要用到器件 的元件图形。这时可以建立一个自己的元件库, 不断向其中添加,积累起来,就可以形成自己常 用器件的元件库了,以后用起来会很方便。

创建元件库的方法: 激活工程管理器,

上图中可以设置颜色、字体、网格显示方式、 缩放和滚动方式等等很多选项,看一看试一试 就明白了。在主菜单->option->design template中可以设置题头、字体大小、页面 尺寸、网格尺寸显示打印方式等等。

浏览工程中的各个元素

当原理图画完后,需要对原理图进行查错编辑。 这时就要用到browse命令,浏览整个工程中 的元素。

CS5381,共有24个管脚,管 脚比较少 ,就不用把元件分成 多个部分;按OK按钮,弹出器 件图形窗口 。初始图形很小, 先把图框拉大,图中虚线部分, 然后放置图形实体的边界线, 选右侧工具栏中的那个小方框 即可画出,初步调整大小,能 放下24个脚即可。接下来要添 加管腿了。这时你可以一个一 个的添加,好处是每次添加都 能设定好管脚的属性。也可以 一次添加24个,然后再去一个 一个修改属性。这里一次添加 完所有管脚。

• 这个操作对于查看电源 网络是否没有赋值很方便。 图中VCC_BAR为忘记 赋值的电源网络。出现这 种情况,在DRC检查的时 候,并不报错,但是该电 源网络在pcb中不会和任何电源相连,出现严 重错误。可以在这里方便的查看并修改。

4.2.1 总线和总线分支的放置

总线和总线分支的放置

●放置总线

在原理图中,当两组引脚需要分别进行电气连接时,可用 一组并行导线进行连接。但为了简化电路,一般用总线配合网 络标号来代替并行导线。放置总线只需启动“放置总线”命令, 常用方法有以下几种: 执行菜单命令放置→总线; 单击配线工具条中的“放置总线”; 快捷键P→B。

总线和总线分支的放置

●放置总线

命令启动后,按Tab键,在弹出的总线对话框中可设置其属 性,如图所示:

总线和总线分支的放置

●放置总线

可以设置线宽和线的颜色。 总线设置完毕后,回到放置状态,放置的方法和放置导线 基本相同。在放置时总线不是和引脚直线相连,而应和一组引 脚的连接点保持平行并隔开一段距离,而且总线在转折处应有 45度直角倒角。

orcad教程

orcad教程在这个Orcad教程中,我们将介绍如何使用Orcad工具进行电路设计和模拟。

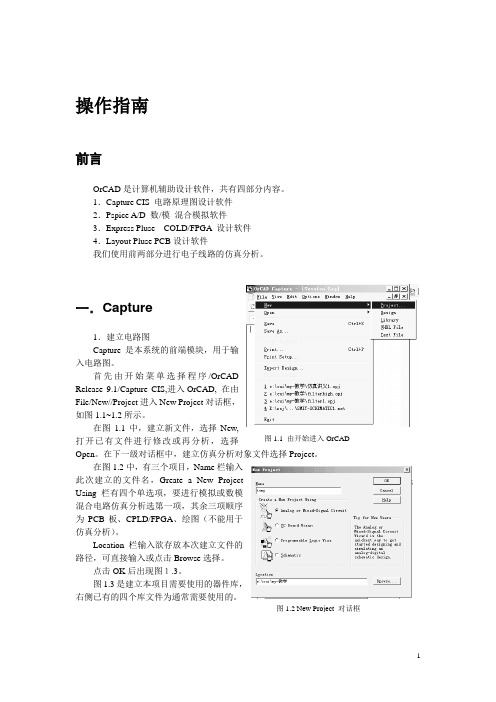

在这个教程中,我们将逐步引导您完成以下几个步骤:1. 创建新项目首先,打开Orcad,并创建一个新的项目。

点击"File",然后选择"New Project"。

在弹出的对话框中,选择一个存储项目的文件夹,并为项目命名。

点击"OK"以继续。

2. 添加原理图接下来,我们将在项目中添加原理图。

点击"Project",然后选择"Add New to Project"。

在弹出的对话框中,选择"Design File"并点击"OK"。

在弹出的对话框中,选择"OrCAD Capture Schematic"并点击"OK"。

现在,您可以开始绘制原理图了。

3. 绘制电路使用Orcad工具绘制您的电路。

您可以添加电源、电阻、电容等元件,并连接它们以完成电路图。

确保为每个元件添加正确的值和标注。

4. 添加模型和库为了模拟和分析电路,您需要为电路中的每个元件添加正确的模型和库。

点击"Place",然后选择"Part"。

在弹出的对话框中,搜索需要的元件,并将其添加到原理图中。

接下来,为每个元件选择正确的模型和库。

5. 进行电路模拟一旦完成了电路的设计和元件的模型添加,您可以开始进行电路模拟了。

点击"PSpice",然后选择"Run"。

在弹出的对话框中,选择模拟的类型和设置,并点击"OK"以开始模拟。

6. 查看和分析结果模拟完成后,您可以查看电路模拟的结果。

点击"PSpice",然后选择"Probe"。

通过选择不同的节点和信号,您可以查看电流、电压等结果并分析电路的行为。

OrCAD操作指南

三.

Prob模块显示窗模拟示波器的显示效果,同时可对图形进行适当的分析。

在显示窗上增加图形。点击后出现下面对话框:

左边栏目选择要显示波形的节点处。右边栏目可选择计算公式。下边栏目列表达式。点击OK按键后,对应节点表达式的波形将显示在屏幕上。用这种办法可得到更多的显示信息。比如可用输入电压比输入电流得到输入阻抗。

噪声分析是计算电路各部分在各点频上的噪声等效为输入噪声源位置上的输入噪声。以此计算出等效输出噪声,结果以文件的形式输出。可在输出文件中查到。

Bias Point:

在分析偏置时,Pspice将电路中的电容开路电感短路,对各信号源取其直流电平值,用迭代法计算电路的直流偏置状态。

在Analysis type栏中选中bias Point,Options栏中选中Save Bias Point,Output file options栏选中Include detailed bias point information for nonlnear controlled sources and semiconductor,就可以进行偏置(直流工作点)分析了。Perform Sensitivity analysis用于直流灵敏度分析,Calculate small-signal DC gain用于计算直流传输特性分析。

傅立叶变换,进行时域分析后选此按键可进行傅立叶变换,结果以频谱显示在屏幕上。

文本标签,在屏幕上设置文本标签。

测试点坐标,测试任意点的坐标。

标注座标值。

*点击菜单栏的window/copy to clipboard可将屏幕显示的图形放入剪贴版,粘贴到word文档中。

Capture BUS线的应用

2. BUS NAME 在平坦式电路中跨 PAGE 连接时, 则需要靠 OFF PAGE 或 PORT 来对 BUS 总线端做连接时。 这时需要注意: BUS Name 或 PORT(OFF PAGE)必须有一个与网络名(Net Alias)相同:如一组线的网络 命名为 D0,D1,D2…D7, 则该 BUS 或 PORT(or OFF PAGE)中至少有一个的名称则要起名 为 D[0..7] ,这时其连接会有以下几种情况,如下将一一列出:

7

二、阶层式电路图中:

BUS (总线)在阶层式电路中,由于需要跨 PAGE,跨 Folder 等,配合 Hierarchical Block 和 Hierarchical Pin 等等,其应用要注意以下事项:

ห้องสมุดไป่ตู้

1. BUS Name 根图(root)和子图中与 Port NAME 及 Net Alias 和 Hierarchical pin 完全一致时:输出正确

其输出的网表(NET LIST)如下: D0; U1.1 D0_547; D1; U1.2 D1_547; D2; U1.3 D2_547; D3; U1.4 D3_547; D4; U1.5 D4_547; D5; U1.6 D5_547;

U2.1 U2.2 U2.3 U2.4 U2.5 U2.6

Net Alias D0, D1...D7,

其输出的网表(NET LIST)如下:其输出的网络名是以 Port Name(or OFF PAGE)为主 DATA0;U2.1 U1.1 DATA1;U2.2 U1.2 DATA2;U2.3 U1.3 DATA3;U2.4 U1.4 DATA4;U2.5 U1.5 DATA5;U2.6 U1.6 ……

《OrCAD图文教程》课件

电路设计与仿真

展示如何在OrCAD中进行电 路设计和进行仿真测试。

印制板设计

演示如何使用OrCAD进行PCB 布局和设计。

常见问题解答

1 常见问题概述

列举和解答OrCAD用户经常遇到的一些常见问题。

2 常见错误和解决方法

提供常见的错误提示及其解决方法,帮助用户迅速解决问题。

3 常见疑问解答

回答用户关于OrCAD软件的常见疑问和困惑。

结束语

M ission

总结OrCAD软件的重要性和应用领域,激发 学习者对电路设计的兴趣。

V is io n

鼓励继续学习和探索OrCAD以及其他相关电 路设计工具。

使用步骤

1

ห้องสมุดไป่ตู้

安装和配置

详细讲解如何正确安装和配置

工程的创建

2

OrCAD软件,并解决常见安装问题。

指导用户如何创建新工程文件,设

置工程参数,以及导入现有工程。

3

环境和工具的介绍

介绍OrCAD开发环境和各种电路设 计工具的功能和用法。

功能演示

元件库的使用

演示如何在OrCAD中使用元 件库进行原理图设计。

《OrCAD图文教程》PPT 课件

本PPT课件为《OrCAD图文教程》提供了全面的软件指导。了解OrCAD的功能 和特点、使用步骤以及功能演示,解决常见问题,并鼓励进一步学习和探索。

软件简介

OrCAD的概述

了解OrCAD软件的背景和基本概念,为后续内容打下基础。

OrCAD的功能和特点

介绍OrCAD具备的强大功能以及在电路设计和仿真方面的特点。

ORCAD小技巧

先把学习ORCAD过程中遇到的问题说一下:1.首先把orcad中常用的快捷键总结一下W-画线B-总线P-放置元气件E-总线接入线J-放置节点X-不连接F-电源N-网络标号G-地T-放置文本Y-折线F10-下页SHIFT+F10上页2.使用ORCAD首先要建立工程,和其他软件类似也可以建立自己的元件库FILE/NEW/LIBRARY,然后就可以在里面设计自己的库了啊, 但是在设计库的时候一般的要求线的类别,如输入,输出,电源,三态等,这些都要对照DATASHEET选择,否则在DRC检查的时候会出现错误!3.有些设计需要多个电源的时候,在orcad库里的元件很多是隐藏电源的,如果你不显示出来的话,系统默认VCC,这样会使设计出错,那么可以用鼠标左键点击元件选中,然后点击右键,选择EDIT PART就可以修改了.4.画原理图的时候网络标号在线的两端最好都标注上,以便在DRC检查的时候可以轻松发现问题,而且可以尽量保证安全啊.5.在画总线的时候,要给总线起名字,而且总线的命名格式是如DIO[0..7]或者DIO[0:7],这样子。

总线的名字一定要写,否则DRC检查不能通过,还有画总先接入线的时候可能需要画很多,那有一种快捷的办法,就是把第一个接入线放好的时候,可以用鼠标左键点击接入线,沿着总线向你想要放的紧挨着的接入线的位置放下,然后点F4就可以轻松的放接入线了,还有其他的有规律的线都可以用这种方法!6.建立新页,一张电路图也许不能够画完所有的电路图,所以就需要分页,这样可以在管理窗口点击.dsn文件的子目录中的schmetics右键点,然后NEW PAGE 就可以了,但是页与页之间一定要用off_page connector符号连接,原则是出来的都用offpageleft-L,进入的用offpageleft-R,而且在同一页的这种标号最好放齐,进来的都放在页面的左边,出去的都放在页面的右边7.画原理图要分模快画,同一模快的放在一块8.相同元件的标号的放置,如果是水平放置的元件把标号和值放在元件两侧,尽量靠近元件,垂直放置的时候,放在一侧上下放置,值在上,标号在下!9.如果在画图的过程中,某些元件需要改动或者删除的话,一定要重新给元件进行标号,那么首先要把标号变成问号的形式,然后用软件的排列可以给元件按照顺序编号10.生成网络表要在管理窗口下,点.dsn的文件,然后点tools/creat netlists,在生成网络表之前一定要把元件的封装添好!以上这些是我在画原理图和学习orcad的软件过程中遇到的问题和总结,拿出来和大家分享。

orcad总线使用要求

orcad总线使用要求

1.总线命名要规范,不能重名或混淆。

2. 总线宽度要根据实际需求进行设置,不能过度浪费或不足。

3. 总线布线要避免交叉、环路等情况,保证信号的正常传输。

4. 总线的起始点和结束点要进行正确的连接,确保数据流向正确。

5. 总线的接口和器件要进行正确的匹配,避免不必要的信号损失或干扰。

6. 总线的信号传输要保证稳定和可靠,不能出现抖动、噪声等问题。

7. 总线的测试和调试要进行充分的验证和确认,确保系统的正常工作。

8. 总线的设计要考虑未来的扩展和升级,保证系统的可持续性。

9. 总线的文档和标注要清晰明确,方便后续的维护和管理。

10. 总线的设计要符合相关的标准和规范,确保符合行业要求。

- 1 -。

orcad 差分总线命名

orcad 差分总线命名

在Orcad中,差分总线的命名通常遵循一定的规则和约定。

首先,差分总线通常用于传输差分信号,这意味着它由一对互补的信号线组成,分别被标记为正和负。

在命名差分总线时,可以采用以下一般约定:

1. 使用“_P”和“_N”后缀,差分信号通常由正和负两部分组成,因此可以使用“_P”和“_N”作为正负信号线的后缀来命名差分总线。

例如,如果差分信号用于传输时钟信号,可以将差分总线命名为“CLK_P”和“CLK_N”。

2. 使用相关信号名称作为前缀,有时候,差分信号可能与特定的信号相关联,因此可以使用相关信号名称作为差分总线的前缀。

例如,如果差分信号用于传输数据信号D0,可以将差分总线命名为“D0_P”和“D0_N”。

3. 保持一致性,在命名差分总线时,应该保持一致性,确保正负信号线的命名方式一致并易于理解。

总的来说,在Orcad中命名差分总线时,应该遵循上述约定并

保持清晰易懂的命名方式,以便于后续的设计和维护工作。

希望这些信息对你有所帮助。

OrCAD Capture BUS Application

◆OrCAD Capture BUS 走线的运用详解一、平坦式电路设计1 .BUS NAME 在平坦式电路中,同一张PAGE 中的BUS 总线及BUS NAME 仅仅是为了方便我们读图使用。

其没有实际的连接意义。

如下图所示,BUS 内的NET 连结还是通过NET 上的Net alias 来完成的。

因此其输出的网表中的NET 也抓取Net Alias 一一对应。

另外:BUS 线在与NET 连接时必须要用Bus entry 与NET 相连后再与BUS 线连接。

直接将NET 与BUS 连接在一起会出现”节点”(junction )表示所有的NET 将为同一NET,即短路在一起。

如上图所示:无论BUSNAME 为何,其输出的网表是以Netalias 的如命名为准。

同时NET 的连接也是通过Net alias 实现的。

2. BUS NAME 在平坦式电路中跨PAGE 连接时,则需要靠OFF PAGE 或PORT 来对BUS 总线端做连接时。

这时需要注意:BUS Name 或PORT(OFF PAGE) 必须有一个与网络名(Net Alias) 相同:如一组线的网络命名为D0,D1,D2…D7, 则该BUS 或PORT(or OFF PAGE )中至少有一个的名称则要起名为D[0..7] ,这时其连接会有以下几种情况,如下将一一列出:1.BUS Name 与PortNAME(orOFFPAGE )及NetAlias 完全一致时,如下图,其输出的网表正确。

Net Alias D0, D1...D7, BUS Name D[0..7] Port Name (or OFF PAGE) D[0..7]其输出的网表(NET LIST)正是我们需要的:D0;U2.1 U1.1D1;U2.2 U1.2D2;U2.3 U1.3D3;U2.4 U1.4D4;U2.5 U1.5D5;U2.6 U1.6……2.BUS Name 与Port NAME(or OFF PAGE )不一致时,但Net Alias 与Port NANE(or OFF PAGE )一致:其抓取以PORT 为主。

ORCAD画原理图步骤及操作讲解

目录目录 (1)第一章基本画原理图流程 (2)1.1 建工程 (2)1.2 放置元件 (2)1.3 总线连接 (2)1.4 一些其他操作 (3)1.5 自动编号与Browse命令 (3)1.6 加封装和批量加封装 (5)1.7检查 (5)1.8生成网表 (5)1.9生成元件清单 (6)1.10* 导出PDF格式 (6)第二章元件库制作 (6)2.1 Homogeneous分裂元件制作 (6)2.2 Hetergeneous分裂元件制作 (6)2.3 在原理图中编号或区分分裂元件 (6)第一章基本画原理图流程1.1 建工程(1)创建原理图工程之前,先简单设置一下。

Options-->Design Template--> 简单设置下项目名称,管理者,纸张大小等基本信息。

(2)创建工程文件File-->New-->Project-->选中Schematic-->ok,然后就可以开始原理图绘制了。

(3)栅格设置Options-->Preferences-->Grid Display-->取消选择Pointer snap to pin后,就可以选任尺寸的区域。

1.2 放置元件Place-->Part-->Add Library-->选择库-->选择元件,即可放置。

说明:(1)软件自带库在安装目录Cadence/SPB16.6/Tools/Capture/library中,比较常用的DISCRETE(电阻电容等常用元件)CAPSYM(电源库)。

(2)Part Search(注意选择路径)。

(3)元件还未放定时,旋转元件,快捷键“R”。

(4)元件的镜像翻转选中元件-->Edit-->Mirror-->选择水平或者垂直翻转。

或者选中元件-->鼠标右键-->选中水平或者垂直翻转。

(5)画线,按住Shift时可以画任意角度的线。

orcad总线使用要求

orcad总线使用要求Orcad总线是电路设计中一个非常重要的部分,它可以实现不同的信号之间进行交互,并在电路中传递信号。

但是,为了顺利使用Orcad总线,需要遵守一些基本规则和使用要求。

1. 命名规则与定义在使用Orcad总线时,需要遵循明确的命名规则和定义,以确保各个信号之间的通信正常进行。

例如,可以将总线命名为“BUS”,在命名时需要合理明确的定义各个信号的名称,避免出现混淆。

2. 确定总线大小在设计过程中,需要确定Orcad总线的大小,即总线需要承载多少个信号,这对于整个电路的性能有着重要的影响。

要根据所需的信号数量来选择合适的总线大小,一般建议在电路设计前进行整体规划。

3. 使用总线标记当多个信号需要使用总线进行通信的时候,需要在总线上添加总线标记,以便于识别总线与信号之间的关系。

在Orcad的PCB编辑工具中,可以通过“PLACE->BUS ENTRY”来添加总线标记,借此实现信号的连接和传输。

4. 使用总线编译器在进行Orcad总线设计时,可以使用Orcad总线编译器来自动生成总线接线。

总线编译器会根据信号的名称、大小、方向等信息,自动计算信号的位置和连接点,并生成最佳的总线接线方案。

这样可以大大节省设计的时间和精力。

5. 避免总线短路在Orcad总线设计中,总线短路是一个常见的问题。

要避免总线短路,可以在设计时合理规划信号的路径,并避免将信号连接到错误的位置上。

在使用总线编译器时,也需要仔细检查每一个信号的连接点,以确保信号传输的正常进行。

总之,Orcad总线的使用需要遵循明确的命名规则和定义,确定合适的总线大小,使用总线标记和总线编译器来管理信号的连接和传输,并避免总线短路等问题。

只有遵守这些基本要求,才能保证Orcad总线在电路设计中发挥出更好的性能。

OrCAD图文教程:总线用法

OrCAD图文教程:总线用法时间:2009-04-27 21:40来源:未知作者:于博士点击:347次1 如何创建总线1)菜单place->bus或者右侧快捷按钮2)原理图内鼠标左键选择总线起点3)移动鼠标画线4)如需要转向,鼠标左键单击页面可转向,默认90度转角。

5)双击左键结束总线2 放置非90度转角总线1)菜单place bus2)按住shift,左键单击选择起点3)拖动鼠标即可画出任意角度总线4)单击左键转方向5)双击左键结束总线3 总线命名命名规则:BUSNAME[0..31]或BUSNAME[0:31]或BUSNAME[0-31]三种形式。

注意BUSNAME和‘[’之间不能有空格,BUSNAME不能以数字结束,不能用BUSNAME00 BUSNAME02这样的名字.放置总线的net alias:a)菜单place ->net alias弹出place net alias对话框b)按照总线命名规则命名,在alias栏中输入,OK。

4总线与信号线连接放置总线入口bus entry,可用菜单place->bus entry或快捷键E或右侧快捷按钮Bus entry悬挂在鼠标上,按R键旋转Bus entry方向。

移动Bus entry与总线相接,单击放置。

按快捷键F4重复放置使用wire把一个引脚和总线一个入口相连。

给wire添加net alias,命名规则如下:如果总线名称为ED[0..31],则wire名称必须是ED0、ED1、ED2……..ED31等这种名字。

注意wire所在网络作为总线的成员,不能有方括号。

按住CTRL键,鼠标选中wire,拖动,连接其他线。

此时,wire上的net alias自动递增。

几点说明:1)总线和wire信号线之间只能通过网络名称实现电气互连。

2)如果不用总线入口,而把wire线直接连到总线上,在连接处也显示连接点,但是这时并没有形成真正的电气连接。

于博士OrCAD图文教程

于博士OrCAD图文教程从于博士个人网上下的于博士网站:/ OrCAD图文教程:快捷键小结时间:2009-03-16 21:13来源:未知作者:网络点击: 6679次ORCAD Capture CIS 快捷键ORCAD Capture CIS 被业界视为最优秀的原理图工具。

这个是原理图设计中的一部分快捷键总结,是从网上找到的,不是很全,以后争取出一份全的。

这份先收藏在这里。

应用环境快捷键说明=========================================CIS Explore Ctrl+Tab 切换到原理图页面而不关闭CIS Explore CIS Explore Ctrl+Shift+Tab 切换到原理图页面而不关闭CIS Explore原理图页面编辑 CTRL+A 全选所有原理图页面编辑 B 放置总线BUS原理图页面编辑 E 放置总线BUS的分支Entry原理图页面编辑 F 放置电源符号原理图页面编辑 G 放置GND符号原理图页面编辑 J 放置连接点原理图页面编辑 N 放置网络别名原理图页面编辑 P 放置元件(从元件库)原理图页面编辑 T 放置文本Text原理图页面编辑 W 放置电气连线原理图页面编辑 Y 放置图形连线原理图页面编辑 X 放置无连接符号原理图页面编辑 F7 记录宏操作原理图页面编辑 F8 回放宏操作原理图页面编辑 F9 配置宏操作元件库编辑(绘图) CTRL+B 跳转至前一个part元件库编辑(绘图) CTRL+N 跳转至后一个part原理图页面及元件库编辑 CTRL+E 编辑属性原理图页面及元件库编辑 CTRL+F 查找原理图页面及元件库编辑 CTRL+T 吸附格点设置原理图页面及元件库编辑 CTRL+Y 重做(恢复)原理图页面及元件库编辑 CTRL+Z 撤销原理图页面及元件库编辑 F4 重复操作原理图页面及元件库编辑 C 以鼠标指针为中心原理图页面及元件库编辑 H 水平镜像原理图页面及元件库编辑 I 放大原理图页面及元件库编辑 O 缩小原理图页面及元件库编辑 R 旋转原理图页面及元件库编辑 V 垂直镜像原理图页面及元件库编辑 E 结束连线、BUS、图形连线orcad 是一个十分受欢迎的原理图设计软件,其他的功能我就不做过多评论了,但原理图设计工具确实很好用,著名的pcb软件cadence allegro SPB系列集成的原理图工具就是这个。

ORCAD使用技巧

1、实际使用中,同一个schematic folder下的page用port是可以实现互连的,对于总线信号的标注,要加注off-page,而且都是有方向的,但方向性不会影响网表的生成,在做DRC 时会有警告。

IC的datasheet一般是从生产商的网站上down的,中文网站中/的资料库较全,可以试试看,引脚的方向是指的type吗,若不做仿真就不用管它。

2、FANOUT布线:延伸焊盘式布线。

为了保证SMD器件的贴装质量,一般遵循在SMD焊盘上不打孔的原则,因此用fanout布线,从SMD器件的焊盘向外延伸一小段布线,再放置VIA,起到在焊盘上打孔的作用。

在LAYOUT PLUS 中,用AUTO/Fanout/Board,实现fanout布线。

先要设置好FANOUT的参数。

在自动布线前要对PCB上各SMD器件先FANOUT布线。

3、现在顶层图上有四个模块,选中任一模块后,按右键选Descend Hierarchy后可进入子图,现在子图已画好,如何在顶层中自动生成PORT?而不用自己一个一个往上加PORT?(子图中已给一些管脚放置了PORT)阶层式电路图的模块PIN脚要自己放置。

选中模块后用place pin快捷菜单。

自动应该不可能。

4、只是想把板框不带任何一层,单独输出gerber文件.该咋整?发现在layout 自带的模板中,有一些关于板框和尺寸的定义,都是在notes层。

所以你也可以在设定板框时,尝试单独将obstacle type 设定为board outline,将obstacle layer设定为notes,当然要在layers对话框里添加上notes层,再单独输出notes层gerber文件5、层次原理图,选中,右键,Descend Hierarchy,出现错误:Unable to descend part.?建议重新设置层级、重新设置属性后就可以了6、层次原理图是什么概念呢?阶层电路就是将经常要用到的原理图(如半加器)作为一个模块,不禁可以是设计版图简洁,而且便于其他设计引用7、有关ORCAD产生DEVICE的问题用ORCAD出DEVICE文件时,它只默认原理图上所显示的元件的PIN连接来出,悬空的PIN在DEVICE里的PINCOUNT没有统计进去,而且确定不了元件PIN 的数量(由于悬空没有显示)这样的话,做封装的时候很容易做错,如果没有DATA SHEET的话。

Candence学习笔记7--第7讲 Cadence原理图中总线的使用方法

第7讲Cadence原理图中总线的使用方法目录1、放置总线 (2)2、放置任意转角的总线 (2)4、把信号连接到总线 (2)5、重复放置与总线连接的信号线 (3)6、总线使用中的注意事项 (4)7、在不同页面之间建立电气连接 (5)8、总结: (6)第7讲总线的使用方法1、放置总线Place--Bus或者快捷键B2、放置任意转角的总线任意走线,走线之前按住shift3、总线命名规则Alias命名规则:baseName[0:N]总线是N+1位,baseName不能以数字结尾;然后将Net Alias放置到总线上。

4、把信号连接到总线信号线通过bus entry和总线相连。

5、重复放置与总线连接的信号线快捷操作:放置1根bus entry线之后,按住F4,可以一直放置bus entry线。

然后将芯片管脚与bus entry相连,在导线上放置net alias快捷操作:重复命名,可以按住ctrl+左键拖动上一根已经命名好的线,这样就能重复命名导线了。

或者按住F4,也能重复上一次动作。

6、总线使用中的注意事项1、总线和信号线之间,它们之间的连接,只能通过net alias这种方式,网络名称的方式连接。

总线名称和信号线名称之间:这两个圈圈处的名字,必须一致。

2、信号线与总线之间,用bus entry的这种方式,连接。

如果Wire与总线直接相连,wire与总线之间实际是没有电气连接的。

总线与总线之间连接,会构成实际的电气连接。

如果两个总线交叉相连,那么系统默认两根线之间是没有电气连接的。

在交叉点处,放置一个junction,两个总线之间就有实际的连接了。

7、在不同页面之间建立电气连接在一个页面中放置Off-page connector,然后在另外一个页面中放置同样名称的off-page Connector。

只要两个页面的off-page connector的名称一样,那么这两个点就已经有电气连接了。

8、总结:理解Cadence软件是使用网络名称建立电气连接的。

PROTEL中画总线的方法

PROTEL中画总线的方法

有部人友会p a d s(p o w e r P C B)以及P R O T E L。

他们在使用过程中比较两个软件的使用方法。

其中最集中的问题是P R O T E L中画总线的问题,只要一提到P A D S和P R O T E L两者的优缺点,大部分人都会说P R O T E L 画总线不好用。

其实不尽然,P R O T E L中画总线很简单,而且画完后不影响网络。

画20条以上速度要比P S D A不相上下。

如果画100条以上的话那P A D S是无论如何都比不上的了。

下面是具体的步骤:

首先画一条线。

在使用快捷键“S”“N”选中网络,如下图

然后用快捷键C T R L+C复制所选的线,并确定基点。

然后再“编辑”菜单里选“特殊粘贴”或者使用快捷键“E”“A”调出特殊粘贴对话框(不能使用工具条上的快捷图标)如图:

看到画红圈的地方吗!一定要选中再点“粘贴阵列”弹出如下对话框:

项目数填写你要复制的总线数(一般是N-1条,N表示你一共有多少条总线)

在“直线队列”中可根据你的实际情况填写。

一般来讲D I P封装的元件管脚间的距离是100m i l。

X,Y,表示你的总线是横排还是竖排。

确认吧!

一下就完了。

效果挺好

检查一下网络,没问题吧,各是各的,决不影响D R C。

ORCAD 原理图设计及后处理

放大缩小:I , O . 导线:W 添加导线名:N 总线:B 总线支线:E 电源、地:F , G. 交点:J 引脚不连接:X 旋转:R 添加文字:T 按Ctrl为复制 F4为重复走线

修改图纸属性

பைடு நூலகம்

纸张大小 格点设置

分页图纸操作

多部分组成的元器件

在Part栏里选择添加的 部分 只要元器件编号名称相 同程序默认为是同一元 件,例如:U1A,U1B… 各个元件的封装要相同

原理图后处理

更新序号

生成网表,PCB

注意事项: 选择这种输出 为最常用方式。 Do not open board file.为 生成PCB后不 打开Allegro.

编辑元器件属性

双击标题栏会自动排序 点击右键,Pivot会更改坐标,横 向变竖向,竖向变横向

CAD中的总线设计与布局 实现串行与并行通信的优化

CAD中的总线设计与布局:实现串行与并行通信的优化设计和布局CAD中的总线是实现串行和并行通信的关键,这对于优化CAD软件的性能和功能至关重要。

在本文中,我们将深入探讨如何设计和布局CAD中的总线,以实现串行和并行通信的优化。

在CAD软件中,总线是指用于在不同组件之间传递数据和控制信号的物理连接。

优化总线设计和布局可以提高CAD软件的响应速度和处理能力,从而提升用户体验和工作效率。

首先,我们需要确定CAD软件中需要进行串行和并行通信的组件。

这些组件可以包括图形处理单元(GPU)、中央处理器(CPU)、内存、外部设备等。

对于每个组件,我们需要确定它们之间传递数据和控制信号的需求和频率。

接下来,我们可以使用一些优化技术来设计和布局CAD中的总线。

一种常见的技术是分段总线设计。

通过将总线划分为多个段,可以减少总线上的冲突和延迟。

每个段可以专门设计以满足特定组件之间的通信需求。

另一种技术是总线宽度匹配。

通过确保总线的宽度与组件之间的数据传输需求相匹配,可以避免数据丢失和传输错误。

总线宽度的匹配还可以提高数据传输速度,从而提升CAD软件的响应速度。

除了分段设计和总线宽度匹配,我们还可以使用分时多路复用技术来优化CAD中的总线布局。

该技术允许多个组件共享同一条总线,以减少硬件成本和复杂性。

通过使用时分多路复用,可以实现不同组件之间的并行通信,从而提高CAD软件的处理能力。

此外,我们还可以考虑使用缓冲区和控制电路来优化CAD中的总线设计。

缓冲区可以用于存储和分发数据,以减轻总线上的压力。

控制电路可以用于协调和管理总线上的数据传输和控制信号,以确保数据和信号的准确性和可靠性。

最后,我们还应该注意总线的布线和电路板设计。

合理的总线布线和电路板设计可以最大程度地减少干扰和信号失真,从而提高CAD软件的性能和稳定性。

总而言之,CAD中的总线设计和布局是实现串行和并行通信优化的重要环节。

通过合理的设计和布局,可以提高CAD软件的响应速度和处理能力,从而提升用户体验和工作效率。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

OrCAD图文教程:总线用法

时间:2009-04-27 21:40来源:未知作者:于博士点击:347次

1 如何创建总线

1)菜单place->bus或者右侧快捷按钮

2)原理图内鼠标左键选择总线起点

3)移动鼠标画线

4)如需要转向,鼠标左键单击页面可转向,默认90度转角。

5)双击左键结束总线

2 放置非90度转角总线

1)菜单place bus

2)按住shift,左键单击选择起点

3)拖动鼠标即可画出任意角度总线

4)单击左键转方向

5)双击左键结束总线

3 总线命名

命名规则:BUSNAME[0..31]或BUSNAME[0:31]或BUSNAME[0-31]三种形式。

注意BUSNAME和‘[’之间不能有空格,BUSNAME不能以数字结束,不能用BUSNAME00 BUSNAME02这样的名字.

放置总线的net alias:

a)菜单place ->net alias弹出place net alias对话框

b)按照总线命名规则命名,在alias栏中输入,OK。

4总线与信号线连接

放置总线入口bus entry,可用菜单place->bus entry或快捷键E或右侧快捷按钮

Bus entry悬挂在鼠标上,按R键旋转Bus entry方向。

移动Bus entry与总线相接,单击放置。

按快捷键F4重复放置

使用wire把一个引脚和总线一个入口相连。

给wire添加net alias,命名规则如下:如果总线名称为ED[0..31],则wire名称必须是ED0、ED1、ED2……..ED31等这种名字。

注意wire所在网络作为总线的成员,不能有方括号。

按住CTRL键,鼠标选中wire,拖动,连接其他线。

此时,wire上的net alias自动递增。

几点说明:

1)总线和wire信号线之间只能通过网络名称实现电气互连。

2)如果不用总线入口,而把wire线直接连到总线上,在连接处也显示连接点,但是这时

并没有形成真正的电气连接。

总线必须通过bus entry和信号线实现互连。

并且总线和信号线都要命名,并符合命名规则。

3)两段总线如果形成T型连接,则自动放置连接点,电气上是互连的。

两段十字形的总

线默认没有连接点,要形成电气互连,必须手动放置连接点。