PT7C4363P中文资料

PT7C4337中文资料

Time Counter .............................................................................................................................................................................. 9 Days of the week Counter ......................................................................................................................................................... 10 Calendar Counter ...................................................................................................................................................................... 10 Alarm Register .......................................................................................................................................................................... 11 Alarm Function ........................................................................................................................................................................... 12 I2C Bus Interface............................................................................................................................................................................. 14 Overview of I2C-BUS .................................................................................................................................................................. 14 System Configuration ................................................................................................................................................................. 14 Starting and Stopping I2C Bus Communications ..................................................................................................................... 15 Slave Address .............................................................................................................................................................................. 17 Maximum Ratings........................................................................................................................................................................... 19 Recommended Operating Conditions ........................................................................................................................................... 19 DC Electrical Characteristics......................................................................................................................................................... 20 AC Electrical Characteristics......................................................................................................................................................... 21 Mechanical Information ................................................................................................................................................................. 22

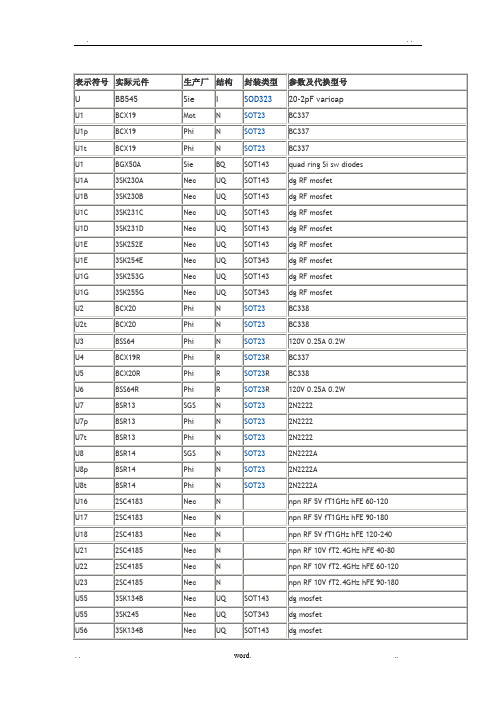

贴片晶体管参数代码查询uvwxyz

BCR133T

Sie

N

SC75

npn dig 50V 0.1A 10k+10k

WCs

BCR133U

Sie

N

SOT457

npn dig 50V 0.1A 10k+10k

WCs

BCR133W

Sie

N

SOT323

npn dig 50V 0.1A 10k+10k

WCs

BCR133S

Sie

DN

SOT363

参数及代换型号

W0F

TSDF1205RW

Tfk

WQ

SOT343

12GHz npn 5mA 4V

W1s

BFT92

Sie

N

SOT23

BFQ51/BFQ76

W1s

BCR10PN

Sie

DP

SOT363

pnp/npn dig 0.1A 10k+10k

W2

TSDF1220RW

Tfk

WQ

SOT343

12GHz npn 6V 20mA

dg RF mosfet

U1E

3SK254E

Nec

UQ

SOT343

dg RF mosfet

U1G

3SK253G

Nec

UQ

SOT143

dg RF mosfet

U1G

3SK255G

Nec

UQ

SOT343

dg RF mosfet

U2

BCX20

Phi

N

SOT23

BC338

U2t

BCX20

Phi

N

SOT23

NPTC021KFXC-RC;NPPC021KFXC-RC;NPPC031KFXC-RC;NPTC031KFXC-RC;NPTC041KFXC-RC;中文规格书,Datasheet资料

80

| 760-744-0125 | toll-free 888-774-3100 | fax 760-744-6081 | info@

/

Sullins Headers

.100”[2.54mm] Contact Centers, Female Header Dip Solder/Right Angle/SMT

MOUNTING STYLE N = No Mounting C = SMT, One Row, pin 1 Left D = SMT, One Row, pin 1 Right P = SMT, 2 Row with guide pins S = SMT, 2 Row without guide pins

NPPC031KFXC-RC PPPC022LJBN-RC NPTC042KFMS-RC NPPC122KFMS-RC NPTC401KFXC-RC NPPC302KFMS-RC NPTC071KFXC-RC NPPC101KFXC-RC NPPC091KFXC-RC NPTC141KFXC-RC NPTC151KFXC-RC NPPC191KFXC-RC NPTC201KFXC-RC NPPC132KFMS-RC NPPC271KFXC-RC NPTC221KFXC-RC NPTC281KFXC-RC NPTC301KFXC-RC NPTC311KFXC-RC NPPC391KFXC-RC NPTC331KFXC-RC NPPC341KFXC-RC NPPC192KFMS-RC NPTC252KFMS-RC NPTC262KFMS-RC NPPC262KFMS-RC NPPC272KFMS-RC NPPC292KFMS-RC NPPC342KFMS-RC NPPC332KFMS-RC NPTC352KFMS-RC NPTC372KFMS-RC NPTC091KFXC-RC NPTC061KFXC-RC NPPC291KFXC-RC NPPC121KFXC-RC NPTC082KFMS-RC NPPC361KFXC-RC NPTC162KFMS-RC NPTC051KFXC-RC NPTC321KFXC-RC

PT7C4337WE中文资料

Crystal: 32.768kHz

Source

External input

1

Oscillator

Oscillator enable/disable

Oscillator fail detect

2

Time

Time display

12-hour 24-hour

Century bit

3

Alarm interrupt

Product Features

Product Description

• Using external 32.768kHz quartz crystal • Supports I2C-Bus's high speed mode (400 kHz) • Includes time (Hour/Minute/Second) and calendar

Control and status register........................................................................................................................................................... 7 Oscillator related bits .............................................................................................................................................................. 7 Square wave frequency selection bits ..................................................................................................................................... 7 Interrupt related bits ................................................................................................................................................................ 8

PT7773A;PT7773C;PT7773N;中文规格书,Datasheet资料

Power Trends, Inc. 27715 Diehl Road, Warrenville, IL 60555 (800) 531-5782 Fax: (630) 393-6902 /powertrends /Ordering InformationPT7773❏ = 0.8 to 3.1 V oltsProgramming InformationVID4=1VID4=0VID3VID2VID1VID0Vout Vout1111 1.6V 0.80V 1110 1.7V 0.85V 1101 1.8V 0.90V 1100 1.9V 0.95V 1011 2.0V 1.00V 1010 2.1V 1.05V 1001 2.2V 1.10V 1000 2.3V 1.15V 0111 2.4V 1.20V 0110 2.5V 1.25V 0101 2.6V 1.30V 0100 2.7V 1.35V 0011 2.8V 1.40V 0010 2.9V 1.45V 0001 3.0V 1.50V 03.1V1.55VLogic 0 = Pin 12 potential (remote sense gnd)Logic 1 = Open circuit (no pull-up resistors)VID3 and VID4 may not be changed while the unit is operating.For dimensions and PC board layout, see Package Style 1020 and 1030•+5V input•5-bit Programmable: 0.8V to 3.1V @32A •High Efficiency•Input V oltage Range: 4.5V to 5.5V•Differential Remote Sense•27-pin SIP PackageFeaturesPower Trends, Inc. 27715 Diehl Road, Warrenville, IL 60555 (800) 531-5782 Fax: (630) 393-6902 /powertrendsPT Series Suffix (PT1234X )Case/PinConfigurationVertical Through-Hole N Horizontal Through-Hole A Horizontal Surface MountCh t t p ://o n e i c.c o m /IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI)reserve the right to make corrections,modifications,enhancements,improvements,and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products andapplications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right,or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications (such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,andacknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic."Only products designated by TI as military-grade meet militaryspecifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products Applications AmplifiersAudioData Converters Automotive DLP®Products Broadband DSPDigital Control Clocks and Timers Medical Interface MilitaryLogicOptical Networking Power Mgmt Security Microcontrollers TelephonyRFIDVideo &Imaging RF/IF and ZigBee®SolutionsWirelessMailing Address:Texas Instruments,Post Office Box 655303,Dallas,Texas 75265Copyright ©2009,Texas Instruments Incorporatedht t p ://o分销商库存信息:TIPT7773A PT7773C PT7773N。

MSK4363资料

-

Volts

-

MHz

-

V/mV

-

100

-

nSec

-

100

-

nSec

-

-

750 µAmps

-

-

0.3

Volts

-

-

0.6

Volts

-

-

0.026

Ω

-

-

2.6

Volts

-

280

-

nSec

-

2

-

µSec

NOTES:

1 Guaranteed by design but not tested. Typical parameters are representative of actual device performance but are for reference only.

(315) 701-6751

FEATURES:

75 Volt Motor Supply Voltage

MIL-PRF-38534 QUALIFIED

10 Amp Output Switch Capability

100% Duty Cycle High Side Conduction Capable

Shoot-Through/Cross Conduction Protection

ABSOLUTE MAXIMUM RATINGS

V+ High Voltage Supply ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ 75V

VIN Current Command Input ○ ○ ○ ○ ○ ○ ○ ○ ○ ○±13.5V

+Vcc ○

pt7c4302时钟芯片规格书

PT7C4302时钟芯片规格书一、产品概述1.1 产品名称:PT7C4302时钟芯片1.2 产品型号:PT7C43021.3 产品功能:PT7C4302是一款宽温工作范围,低成本,实时时钟/日历集成电路(IC)。

它具有秒,分,时,日,月,年,星期和12/24小时模式的实时时钟。

1.4 适用范围:PT7C4302广泛应用于计算机,汽车电子,工业控制系统和家用电器等领域。

二、产品特点2.1 宽温工作范围:-40°C至+85°C2.2 低功耗设计:工作电流仅为1.5μA(最大)2.3 高精度:时钟精度为±2分钟/年(25°C下)2.4 可编程:支持12小时/24小时模式切换,支持闰年计算2.5 封装形式:采用8引脚SOIC(小外形集成线路)封装2.6 通信接口:SPI接口,便于与微处理器或微控制器连接三、产品功能描述3.1 实时时钟功能:PT7C4302在低功耗模式下持续正常工作,能够提供准确的实时时钟功能,包括秒,分,小时,日,月,年和星期等显示。

3.2 闰年计算:PT7C4302内置闰年计算功能,可自动判断闰年和平年。

3.3 电源监控:PT7C4302内置电源监控电路,能够实时监测供电电压,确保时钟芯片在电压不稳定的情况下仍然能够正常工作。

四、产品应用4.1 计算机:PT7C4302可以作为计算机主板的实时时钟芯片,提供精准的时间信息,并支持系统待机和节能模式。

4.2 汽车电子:PT7C4302可用于汽车电子系统中,提供车辆的精准时间信息,并支持车载设备的定时控制功能。

4.3 工业控制系统:PT7C4302适用于工业控制系统中的时间同步和定时功能,确保生产流程的准确控制。

4.4 家用电器:PT7C4302可作为家用电器中的时间显示和定时控制芯片,如微波炉、洗衣机等设备中的时钟显示和定时启动功能。

五、产品性能指标5.1 工作电压范围:2.7V至5.5V5.2 工作温度范围:-40°C至+85°C5.3 存储温度范围:-55°C至+125°C5.4 封装形式:8引脚SOIC封装5.5 通信接口:SPI接口5.6 尺寸:5mm×6mm×1.5mm六、产品包装及贮存6.1 包装形式:PT7C4302采用卷装或者盒装形式,符合RoHS环保要求。

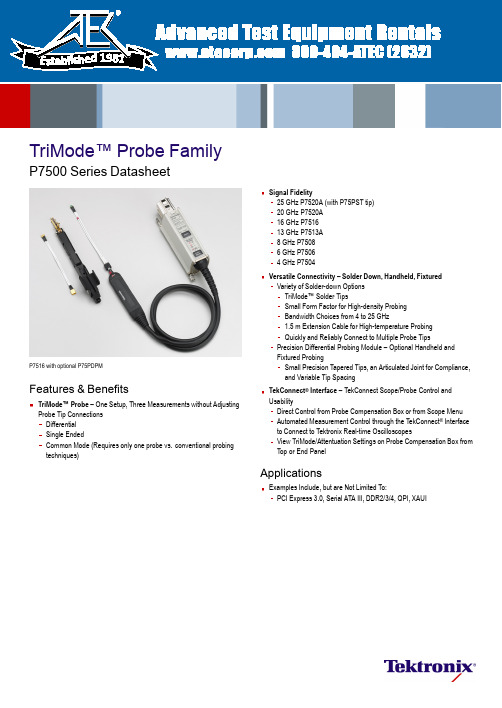

三模式探头系列P7500系列数据表P7516(含可选功能P75PDPM)特点与优势说明书

TriMode™Probe FamilyP7500SeriesDatasheetP7516with optional P75PDPMFeatures &Bene fitsTriMode™Probe –One Setup,Three Measurements without Adjusting Probe Tip Connections Differential Single EndedCommon Mode (Requires only one probe vs.conventional probing techniques)Signal Fidelity25GHz P7520A (with P75PST tip)20GHz P7520A 16GHz P751613GHz P7513A 8GHz P75086GHz P75064GHz P7504Versatile Connectivity –Solder Down,Handheld,Fixtured Variety of Solder-down Options TriMode™Solder TipsSmall Form Factor for High-density Probing Bandwidth Choices from 4to 25GHz1.5m Extension Cable for High-temperature Probing Quickly and Reliably Connect to Multiple Probe TipsPrecision Differential Probing Module –Optional Handheld and Fixtured ProbingSmall Precision Tapered Tips,an Articulated Joint for Compliance,and Variable Tip Spacing TekConnect ®Interface –TekConnect Scope/Probe Control and UsabilityDirect Control from Probe Compensation Box or from Scope Menu Automated Measurement Control through the TekConnect ®Interface to Connect to Tektronix Real-time OscilloscopesView TriMode/Attentuation Settings on Probe Compensation Box from Top or End PanelApplicationsExamples Include,but are Not Limited To:PCI Express 3.0,Serial ATA III,DDR2/3/4,QPI,XAUI1981DatasheetBefore TriMode:1Probe for Differential;2Probes for SE and Common Mode;or 1Probe Soldered and Resoldered 3times;2Probes for Common Mode.TriMode™Probing,Connectivity,and PerformanceTriMode™Probing ArchitectureOne-probe setup makes differential,single ended,and common mode measurements accurately and de finitively.Tektronix is a known leader when it comes to signal fidelity and signalacquisition.Building on our history of market-leading innovations inprobing,After TriMode (P75TLRST):1Probe for Differential,Single Ended,and Common Mode,with only 1setup required.we invented a revolutionary probing architecture called “TriMode™Probing”that de fines the next-generation industry benchmark for usability and signal fidelity.This architecture changes the rules of probing and allows you to work more effectively and ef ficiently.By enabling unique functionality,the P7500Series TriMode probes allow you to switch between differential,single ended,and common mode measurements without moving the probe from its connection points.Improved productivity is achieved by reducing setup time.One setup can be used to make the three different types of measurements all with the press of a button.The TriMode Probe architecture for the P7500Series probes continues the Tektronix tradition of high-bandwidth and low-DUT loading while providing improved connectivity and value.2TriMode™Probe Family —P7500SeriesConnectivity Plus –Solder Down –Handheld –FixturedThe P7500Series TriMode probe architecture offers various levels of connectivity and provides the highest probe fidelity available for real-time oscilloscopes.The multipoint connectivity solutions of the P7500Series include:TriMode Performance Solder Tip The highest-performance solder tip.Up to 25GHzbandwidth.TriMode Long-reach Solder Tip A high performance solder tip with a long reach and very small,low-pro file form factor.Up to 20GHzbandwidth.TriMode Resistor Solder Tip High-performance solder tip with easy-to-solder tip resistors.Up to 18GHzbandwidth.TriMode Extended-resistor Solder Tip Medium-performance solder tip with long easy-to-solder tip resistors.Up to 7GHzbandwidth.3DatasheetTriMode Micro-coax Tip Low-cost,quick-connect solder tips.Up to 4GHzbandwidth.TriMode High-temperature Tip When used with the 1.5m Socket Cable XL,this tip can be used in environments from –55°C to 150°C.Up to 10GHz bandwidth withDSP.Damped Wire Tip Low-cost solder tips ideal for high-density probing.Up to 8GHzbandwidth.Precision Differential Probing Module High-performance handheld probing module.Up to 18GHzbandwidth.Handheld and fixtured probing needs are met using the optional Precision Differential Probing Module (P75PDPM).Its small precision tapered tips,variable articulation of the probe tip,and quick-adjusting variable tip spacing provides the needed flexibility for adapting to vias and other test points of differing sizes from 30mils to 180mils.These precision connectivity tools enable you to access multiple signals on anything from convenient test pads to hard-to-reach,high-density circuitry.4TriMode™Probe Family —P7500SeriesSignal FidelityYou can be con fident in the signal fidelity of your measurements.The innovative new Tektronix differential architecture,coupled with the superior electrical performance of IBM SiGe Technology,provides the bandwidth and fidelity to meet the industry needs of today as well as tomorrow.The P7500Series Probe Architecture provides:Highest bandwidth available –25GHz Excellent step response Low-DUT loading High CMRRDifferential,single ended,or common mode measurements using one probePerformance You Can Count OnDepend on Tektronix to provide you with performance you can count on.In addition to industry-leading service and support,this product comes backed by a one-year warranty as standard.CharacteristicsP7500with P75PDPMTriMode Probe ArchitectureP7520AP7516P7513A P7508P7506P7504Bandwidth (Typical,Probe Only)>20GHz,A-B mode >18GHz,P75PDM,other modes >16GHz >13GHz >8GHz >6GHz >4GHz Rise Time (10-90%)(Typical,Probe Only)<27ps,A-B mode <29ps,other modes <32ps <40ps <55ps <75ps <105ps Rise Time (20-80%)(Typical,Probe Only)<18ps,A-B mode <20ps,other modes<24ps <28ps <35ps <50ps <70ps Attenuation(User Selectable)5X or 12.5X 5X or 12.5X 5X or 12.5X 5X or 12.5X 5X or 12.5X 5X or 12.5X Differential Input Range ±0.625V (5X)±1.6V (12.5X)±0.75V (5X)±1.75V (12.5X)±0.75V (5X)±1.75V (12.5X)±0.75V (5X)±1.75V (12.5X)±0.75V (5X)±1.75V (12.5X)±0.75V (5X)±1.75V (12.5X)Operating Voltage Window+3.7to –2.0V +4.0to –2.0V +4.0to –2.0V +4.0to –2.0V +4.0to –2.0V +4.0to –2.0V Offset Voltage Range+2.5to –1.5V,A-B mode +3.4to –1.8V,other modes +2.5to –1.5V,A-B mode +3.4to –1.8V,other modes +2.5to –1.5V,A-B mode +3.4to –1.8V,other modes +2.5to –1.5V,A-B mode +3.4to –1.8V,other modes +2.5to –1.5V,A-B mode +3.4to –1.8V,other modes +2.5to –1.5V,A-B mode +3.4to –1.8V,other modes DC Input Resistance (Differential)100k ohms 100k ohms 100k ohms 100k ohms 100k ohms 100k ohms Noise<33nV /√Hz (5X)<48nV /√Hz (12.5X)<33nV /√Hz (5X)<48nV /√Hz (12.5X)<33nV /√Hz (5X)<48nV /√Hz (12.5X)<33nV /√Hz (5X)<48nV /√Hz (12.5X)<33nV /√Hz (5X)<48nV /√Hz (12.5X)<33nV /√Hz (5X)<48nV /√Hz (12.5X)CMRR(Differential Mode)>60dB at DC >40dB at 50MHz >30dB at 1GHz >20dB at 10GHz >12dB at 20GHz>60dB at DC >40dB at 50MHz >30dB to 1GHz >20dB to 8GHz >15dB to 16GHz>60dB at DC >40dB at 50MHz >30dB to 1GHz >20dB to 7GHz >15dB to 13GHz>60dB at DC >40dB at 50MHz >30dB at 1GHz >25dB at 4GHz >20dB at 8GHz>60dB at DC >40dB at 50MHz >30dB at 1GHz >25dB at 3GHz >20dB at 6GHz>60dB at DC >40dB at 50MHz >30dB at 1GHz >28dB at 2GHz >25dB at 4GHzNondestructive Input Range ±15V ±15V ±15V ±15V ±15V ±15V Interface TekConnect™TekConnect™TekConnect™TekConnect™TekConnect™TekConnect™Cable Length1meter1meter1.3meters1.3meters1.3meters1.3metersFor additional characteristics,refer to the individual probe Technical Reference Manuals.5DatasheetTypical System Speci ficationsThe typical system speci fications in the table below are achieved using a P7520A probe with a DPO/DSA72504D or DPO/DSA73304D Oscilloscope and a P75PST solder tip.CharacteristicA-B ModeAll Other ModesSystem Bandwidth25GHz >18GHz System Rise Time (10%–90%)<20ps <29ps System Rise Time (20%–80%)<14ps<20psMinimum System Requirements /Instrument CompatibilityP7500Series TriMode Differential Probes are compatible with the DPO/DSA/MSO70000and TDS6000B/C Series TekConnect Oscilloscopes.The chart below shows recommended probe/oscilloscope model combinations.InstrumentBW (Scope)FW VersionRecommended ProbeDPO/DSA73304D 33GHz V6.4.1or higher P7520A DPO/DSA72504D 25GHz V6.4.1or higher P7520A DPO/DSA7200420GHz V3.0or higher P7520A DPO/DSA7160416GHz V3.0or higher P7516DPO/DSA7125412.5GHz V3.0or higher P7513A DPO/DSA708048GHz V3.0or higher P7508DPO/DSA706046GHz V3.0or higher P7506DPO/DSA704044GHzV3.0or higher P7504TDS6000C 12.5GHz,15GHz V5.1.7P7516,P7513A TDS6000B8GHz,6GHzV5.1.3P7508,P750680A03TekConnect Probe Interface V2.3All P7500Series probes RTPA2A TekConnect Probe InterfaceV2.3All P7500Series probesOrdering InformationP7520A TriMode™Differential Probe,20GHz,for TekConnect Interface Oscilloscopes.P7516TriMode™Differential Probe,16GHz,for TekConnect Interface Oscilloscopes.P7513A TriMode™Differential Probe,13GHz,for TekConnect Interface Oscilloscopes.P7508TriMode™Differential Probe,8GHz,for TekConnect Interface Oscilloscopes.P7506TriMode™Differential Probe,6GHz,for TekConnect Interface Oscilloscopes.P7504TriMode™Differential Probe,4GHz,for TekConnect Interface Oscilloscopes.All Include :One-year warranty,plus see Standard Accessories table.Service OptionsOptionDescriptonCA1Single Calibration or Functional Veri fication C3Calibration Service 3Years C5Calibration Service 5YearsD3Calibration Data Report 3Years (with Option C3)D5Calibration Data Report 5Years (with Option C5)G3Complete Care 3Years (includes loaner,scheduled calibration and more)G5Complete Care 5Years (includes loaner,scheduled calibration and more)R3Repair Service 3Years R5Repair Service 5YearsAdditional Service Products Available During Warranty (DW)R3PDW Repair service coverage 3years (includes product warranty period).3-year period starts at time of customer instrument purchaseR5PDWRepair service coverage 5years (includes product warranty period).5-year period starts at time of customer instrument purchase6TriMode™Probe Family —P7500SeriesStandard AccessoriesDescriptionP7520A/P7516P7513A/P7508P7506/P7504Reorder Part Number020-2790-xx(P7516/P7513A/P7508)020-2977-xx (P7506/P7504)The documentation kit contains:Printed Quick Start User Manuals,CD-ROM contains PDFs of basic probe and measurement literature,and the probe manuals (Quick Start User Manual and Technical Reference Manual)1each *11each 1each071-3048-xx (P7520A)Antistatic Wrist Strap1each 006-3415-xx Certi ficate of Traceable Calibration1each 1each 1each Standard with probe Data Calibration Report:Lists themanufacturing test results of your probe at the time of shipment and is included with every probe1each 1each 1eachStandard with probeDC Probe Calibration Fixture1each 067-1821-xx DC Probe Calibration Fixture1each 1each 067-1967-xx 50ΩCoax Cable –Male BNC to Male BNC1each 1each 1each 012-0208-xx 50ΩCoax Cable –Male SMA to Male SMA1each 1each 1each174-1120-xx Solder Tip Ramps (25each)1each (P7520A only)020-3118-xx P7520A/P7516/P7513A/P7508Accessory Box (See contents listing below 1through 7)1)TriMode Long-reach Solder Tip2each 2eachP75TLRST 2)G3PO Bullet Kit (includes 4bullets)1each 013-0359-xx 3)G3PO Bullet Removal Tool1each 003-1896-xx 4)Solder Kit:Solder Spool,Wire Spool1each 1each 020-2754-xx 5)Tape,Adhesive (Strip,10each)1each 1each 006-8237-xx 6)Marker Band Set (2each of 5colors)1each 1each 016-0633-xx 7)Socket Cable1each020-2954-xxP7506/P7504Accessory Box (See contents listing below 1through 6)1)Socket Cable1each 020-2954-xx 2)TriMode Micro-coax Tip4each 020-2955-xx 3)TriMode High-temperature Tip2each 020-2958-xx 4)Solder Kit:Solder Spool,Wire Spool 1each 020-2754-xx 5)Tape,Adhesive (Strip,10each)1each 006-8237-xx 6)Marker Band Set (2each of 5colors)1each016-0633-xx*1P7520A documentation is a printed instruction manual.7DatasheetContact Tektronix:ASEAN /Australasia (65)63563900Austria 0080022554835*Balkans,Israel,South Africa and other ISE Countries +41526753777Belgium 0080022554835*Brazil +55(11)37597627Canada 180********Central East Europe and the Baltics +41526753777Central Europe &Greece +41526753777Denmark +4580881401Finland +41526753777France 0080022554835*Germany 0080022554835*Hong Kong 4008205835India 0008006501835Italy 0080022554835*Japan 81(3)67143010Luxembourg +41526753777Mexico,Central/South America &Caribbean 52(55)56045090Middle East,Asia,and North Africa +41526753777The Netherlands 0080022554835*Norway 80016098People’s Republic of China 4008205835Poland +41526753777Portugal 800812370Republic of Korea 00180082552835Russia &CIS +7(495)7484900South Africa +41526753777Spain 0080022554835*Sweden 0080022554835*Switzerland 0080022554835*Taiwan 886(2)27229622United Kingdom &Ireland 0080022554835*USA 180*********European toll-free number.If not accessible,call:+41526753777Updated 10February 2011For Further Information.Tektronix maintains a comprehensive,constantly expanding collection of application notes,technical briefs and other resources to help engineers working on the cutting edge of technology.Please visit Copyright ©Tektronix,Inc.All rights reserved.Tektronix products are covered by U.S.and foreign patents,issued and rmation in this publication supersedes that in all previously published material.Speci fication and price change privileges reserved.TEKTRONIX and TEK are registered trademarks of Tektronix,Inc.All other trade names referenced are the service marks,trademarks,or registered trademarks of their respective companies.17Aug 201251W-20271-13Optional Tip AccessoriesDescriptionPart NumberTriMode Performance Solder TipP75PST P7500Series Precision Differential Probing ModuleP7500Precision Differential Probing Module Accessory Kit (See 1through 7below)P75PDPM 1)Tip Cable (1ps matched pair,1each)P75TC 2)Probing Module TipProbe Tips Replacement Kit 1Each (Right and left side)P75PMT 3)Accessory Kit;Ground Spring,Large 4Each 016-1998-xx 4)Accessory Kit;Ground Spring,Small 4Each 016-1999-xx 5)Handle,Adapter (Probing Module)367-0545-xx 6)G3PO Separator Tool 003-1897-xx 7)Ground Spring Tool 003-1900-xx TriMode Resistor Solder Tip020-2936-xx TriMode Extended-resistor Solder Tip 020-2944-xx Resistor Replacement Kit 020-2937-xx Solder Tip Ramps,25Each 020-3118-xx Socket Cable 020-2954-xx Socket Cable,XL020-2960-xx TriMode High-temperature Tip 020-2958-xx TriMode Micro-coax Tip 020-2955-xx Damped Wire Tip020-2959-xx Nexus Interposer DDR Solder Tip 020-3022-xx Deskew Fixture 067-1586-xx Probe PositionerPPM100Precision,3Position,Probe Positioner PPM203B 8200Series TekConnect ®Probe Interface 80A03(FW Version ≥2.3)RTSA Series TekConnect ®Probe InterfaceRTPA2A(FW Version ≥2.3)Tektronix is registered to ISO 9001and ISO 14001by SRI Quality SystemRegistrar.Product(s)complies with IEEE Standard 488.1-1987,RS-232-C,and with Tektronix Standard Codes and Formats.。

NT73CS6DC3V中文资料

79

Ambient Temperature Relative Humidity 元器件交易网 Mass

Safety approvals Safety approval Load Dimensions (Unit: mm)

UL&CUR 10A/250VAC 28VDC 6A/277VAC Insulation B-class F-class

CCEE 5A/250VAC

mm 0.3 0.4 0.5 1.0 1.3 1.4 2.0 3.5 6 12 12.2 16.5 19.5

19.5×16.5×16.5

元器件交易网

Features

Superminiature, High power. Low coil power consumption. PC board mounting. Suitable for household appliance, automation system, electronic equipment, instrument and meter, communication facilities and remote control facilities.

Ordering Information

NT73 C S 10

1 2 3 4

DC12V F

5 6 4 Contact Current:5:5A;6:6A;10:10A;12:12A 5 Coil rated Voltage(V):DC:3,4.5,5,6,9,12,24,36,48 6 Resistance Heat Class:NIL:130℃;F:155℃

AP436中文资料

Synchronous Rectifier MOSFET DriverFeatures- V OUT slew-rate minimum 100V/uS @ CL=3000pF - I OUT (sink & source)=1.2 / 0.9 A - Safety considered.- Reduce power system thermal & increase system efficiency.- Pb-free packages: SOT89-5L, SOP-8LApplication- Power Adapter.(50~120W for LCD Monitor & NB…etc.)General DescriptionsThe AP436 is a high-speed controller designed to drive N-channel power MOSFET used as synchronous rectifiers in high current, high frequency fly-back converters. The circuit does not require any ties to the primary side and derives its operating power directly from the secondary. The circuit functions are structured by anticipating transformer output transitions then turns the power MOSFET on or off before the transitions of the transformer to minimize body drain diode conduction and reduce associated losses.Pin Assignment( Top View )GND TABV DC V CCV GND GND V R V OUT SOP-8L GND V CC GNDPin DescriptionsName Description V CC Operating voltage inputV R Reference input voltage V DC Duty cycle input voltageV OUTOutput voltage for driving N channelMOSFETGND GroundOrdering InformationS : SOP-8L Y : SOT89-5LBlank: Tube A : TapingSynchronous Rectifier MOSFET Driver Block DiagramsVDCVROUTVGNDAbsolute Maximum RatingsSymbol Parameter Rating UnitV CC SupplyVoltage 14 V V R Referenceinputvoltage -0.3≦V≦2.5 V V DC Duty cycle input voltage -0.3≦V≦V CC-2.1 VV OUT Output voltage to Ground -0.7 VP D Powerdissipation 1 W T ST Storage temperature range -65 to 150 o CT OP Operating temperature range -40 to +125 o CV OP Operating voltage range 7.2 to 14 VSynchronous Rectifier MOSFET DriverElectrical CharacteristicsUnless otherwise specified, guaranteed for Tj=25OC, V CC =12V.Symbol Parameter Conditions Min. Typ. Max. Units V CC Supply Voltage 7.2 12 14 V I B1 Input Bias Current (Pin V R ) V R =0.7V,V CC =12V -74 -103 -150 uA I B2 Input Bias Current (Pin V DC ) V DC =0.7V,V CC =12V -74 -103 -150 uA V R Reference Pin Voltage Range 0.3 0.7 1.5 V V DCL Minimum Input Signal Voltage -0.3 V V OH Output High Vcc-1.5 V V OL Output LowCL=3000pFR L =2K 0.8 0.9 V V DC Detection Voltage V R V R +6 mV V CM Common Mode Range 0.7 1.5 V I S Supply Current (Average Value) V CC =12V,No Load 5.5 6 mAI SOURCE Sourcing Current (Transient Value) 1250 mAI SINK Sinking Current (Transient Value) V CC =12V,C L =3000pFR L =2K,Cin=47uF,F Vdc =200KHz 900 mA I OP Operation Current (Average Value)14 mA Output Delay Time(Low to High)80 100 nS T PDOutput Delay Time(High to Low) 60100nST ROutput Rise Time (10% ~ 90% Rise Edge)35 100 nS T FOutput Fall Time (10% ~ 90% FallEdge)V CC =12V,C L =3000pFR L =2K,Cin=47uF, F Vdc =60KHz60 100 nS F OP Maximum Operation Frequency 200 KHz P D Power Dissipation SOT89-5L, SOP-8L1WI SD (Icc Shutdown Current)V CC =5V, C L =3000pFR L =2K,Cin=47uF, F Vdc =60KHz0.2 0.43 mASynchronous Rectifier MOSFET DriverTypical Application Circuit(1)(2)Marking Information(1)SOP-8L( Top View )~AP436YY WW (2)SOT89-5LXX : Identification code (See Appendix)Y : Year: 0-9M : Month: A~L(Top View)Appendix Part Number Package Identification CodeAP436 SOT89-5L FMSynchronous Rectifier MOSFET DriverPackage Information(1) Package Type: SOP-8LDimensions In Millimeters Dimensions In InchesSymbolMin. Nom. Max. Min. Nom. Max.A 1.40 1.60 1.75 0.055 0.063 0.069A1 0.10 - 0.25 0.040 - 0.100A2 1.30 1.45 1.50 0.051 0.057 0.059B 0.33 0.41 0.51 0.013 0.016 0.0200.008 0.010C 0.19 0.20 0.25 0.0075D 4.80 5.05 5.30 0.189 0.199 0.209E 3.70 3.90 4.10 0.146 0.154 0.161e - 1.27 - - 0.050 -H 5.79 5.99 6.20 0.228 0.236 0.244L 0.38 0.71 1.27 0.015 0.028 0.050y - - 0.10 - - 0.004θ0O - 8O0O - 8OSynchronous Rectifier MOSFET DriverPackage Information (Continued)(2) Package Type: SOT89-5LDimensions In Millimeters Dimensions In InchesSymbolMin. Nom. Max. Min. Nom. Max.A 4.40 4.50 4.60 0.173 0.177 0.181B 4.05 4.15 4.25 0.159 0.163 0.167C 1.50 1.60 1.70 0.059 0.063 0.067D 1.30 1.40 1.50 0.051 0.055 0.059E 2.40 2.50 2.60 0.094 0.098 0.102F 0.80 - - 0.031 - -G 3.00 Ref. 0.118 Ref.H 1.50 Ref. 0.059 Ref.I 0.40 0.46 0.52 0.016 0.018 0.020J 1.40 1.50 1.60 0.055 0.059 0.063K 0.35 0.39 0.43 0.014 0.015 0.017L 5o Typ. 5o Typ.。

安川变频器GA700技术手冊说明书

使用前安裝和配線起動步驟與試運轉符合國外標準網路通訊故障排除檢查和維護廢棄物處理規格參數一覽表參數的詳細內容資料編號SITP C71061707A安川變頻器GA700高性能型技術手冊型號CIPR-GT70Axxxxxxxx容量範圍200V 級(三相電源用)0.4~110kW400V 級(三相電源用)0.4~355kW為了安全使用本產品,請務必閱讀該使用說明書。

另外,請妥善保管該使用說明書,並將其交至最終使用者手中。

2株式會社安川電機SITP C71061707A安川變頻器GA700技術手冊株式會社安川電機SITP C71061707A 安川變頻器GA700技術手冊3目錄i.前言和一般注意事項 (13)i.1使用前 (14)關於本書中的術語、簡稱...................................................14關於註冊商標 (14)i.2為了安全使用 (15)與安全有關的警語.........................................................15安全注意事項............................................................15警告標誌的內容與位置.. (16)i.3關於保固 (18)關於本產品的適用 (18)1.使用前 (19)1.1安全注意事項......................................................201.2變頻器型號和銘牌的確認 (21)銘牌....................................................................21型號的查閱方法. (21)2.安裝和配線 (25)2.1安全注意事項......................................................262.2安裝環境..........................................................282.3安裝方向和安裝空間的確認...........................................292.4搬運、安裝........................................................31搬運、安裝時的注意事項 (31)2.5發熱量............................................................322.6安裝/拆卸操作器. (35)拆下操作器..............................................................35安裝操作器.. (35)2.7將操作器安裝於控制盤等處 (36)在遠離變頻器的場所操作操作器.............................................36在遠離變頻器的場所安裝操作器 (36)2.8拆卸/安裝外蓋 (41)拆卸/安裝外蓋(步驟A ) (41)2.9變更變頻器的保護構造 (43)安裝保護蓋(步驟A ) (43)2.10安裝方法..........................................................452.11配線.. (48)標準連接圖 (48)2.12主迴路的配線 (51)馬達和主迴路的連接.......................................................51主迴路端子台的排列.......................................................51主迴路端子的功能 (52)電線尺寸和緊鎖力矩 (53)主迴路端子與馬達的配線 (60)主迴路端子間的保護 (63)2.13主迴路端子台的配線步驟 (64)進行主迴路端子台配線(步驟A) (64)2.14控制迴路的配線 (67)控制迴路配線圖 (67)控制迴路端子的功能 (68)控制迴路端子的排列 (70)控制迴路端子台的配線 (71)控制迴路端子台的開關排列 (73)2.15輸入輸出訊號的連接 (74)脈波序列輸出 (74)共射極模式與共集極模式的設定 (74)選擇多功能類比輸入端子A1~A3的輸入訊號 (75)選擇多功能類比輸入端子A3的輸入訊號 (76)選擇多功能類比監視輸出端子FM、AM的輸出訊號 (76)MEMOBUS/Modbus通訊的終端電阻設為ON (76)2.16與外部的聯鎖 (78)2.17安裝制動電阻器 (79)制動電阻器(ERF型)的連接 (79)制動電阻器裝置(LKEB型)的連接 (79)制動裝置(CDBR型)的連接 (79)制動裝置的並聯連接 (80)制動選購品使用注意事項 (80)2.18保護變頻器的配線 (82)配線用斷路器(MCCB)或漏電斷路器(ELCB)的連接 (82)漏電斷路器的連接 (82)2.19保護制動選購品、馬達 (83)在變頻器輸入側安裝電磁接觸器(MC) (83)在變頻器輸出側安裝熱繼電器 (83)2.20改善功率因數 (84)AC電抗器或DC電抗器的連接 (84)2.21開關突波不流出外部 (85)2.22降低雜訊 (86)輸入側(一次側)的雜訊濾波器的連接 (86)輸出側(二次側)的雜訊濾波器的連接 (86)2.23故障時保護變頻器 (88)分路迴路保護 (88)2.24配線檢查表 (91)2.25馬達使用注意事項 (93)用於現有標準馬達 (93)用於同步馬達 (93)用於特殊馬達時的注意事項 (94)動力傳動結構 (94)3.起動步驟與試運轉 (95)3.1安全注意事項 (96)3.2操作器各部分的名稱與功能 (97)LCD顯示器 (98)操作器的指示燈 (99)操作器的模式和選單 (100)3.3LED狀態燈 (102)3.4起動步驟 (103)4株式會社安川電機SITP C71061707A安川變頻器GA700技術手冊流程圖A(透過最低限度的設定變更,連接馬達進行運轉) (103)子流程圖A-1(感應馬達的自動調整和試運轉步驟) (104)子流程圖A-2(PM馬達的自動調整和試運轉步驟) (105)子流程圖A-3(EZ向量控制模式的試運轉步驟) (106)3.5變頻器起動時的確認事項 (108)接通電源前的確認 (108)接通電源後的確認 (108)進行初始設定 (108)3.6操作器的操作方法 (110)HOME畫面的顯示確認與操作 (110)顯示監視 (111)設定常用的監視 (111)顯示常用監視 (112)設定以橫條顯示的監視 (113)以橫條顯示監視 (114)設定以類比指針顯示的監視 (115)以類比指針顯示監視 (116)變更參數的設定值 (117)確認常用參數 (118)將參數儲存作為備份 (119)將備份的參數寫入變頻器 (120)核對操作器的參數和變頻器的參數 (121)確認變更的參數 (122)將變更的參數恢復為出廠設定 (124)顯示故障記錄 (125)進行自動調整 (125)選擇操作器所顯示的語言 (127)設定日期 (128)使用設定引導畫面對參數進行設定 (130)不顯示初始設定畫面 (131)開始登記資料日誌 (132)設定資料日誌的內容 (133)設定背光的自動熄滅 (135)顯示變頻器的資訊 (136)3.7應用程式上自動設定最佳參數(應用程式選擇) (138)3.8自動調整 (140)感應馬達用馬達參數的自動調整 (140)PM馬達用馬達參數的自動調整 (140)EZ調整 (142)控制系統自動調整 (142)進行自動調整前的注意事項 (143)3.9試運轉 (146)空載狀態下的試運轉 (146)用空載進行試運轉 (146)實際負載試運轉 (146)用實際負載進行試運轉 (147)3.10試運轉時的微調(控制性能的調整) (148)無PG V/f控制模式及附PG V/f控制模式 (148)無PG向量控制模式 (148)附PG向量控制模式 (150)無PG高級向量控制模式 (150)PM用無PG向量控制模式 (151)PM用無PG高級向量控制模式 (152)PM用附PG向量控制模式 (152)EZ向量控制模式 (153)3.11試運轉時的確認表 (154)4.符合國外標準 (157)株式會社安川電機SITP C71061707A安川變頻器GA700技術手冊54.1安全注意事項 (158)4.2歐洲標準 (160)低電壓指令 (160)EMC指令 (172)4.3UL標準 (181)安裝場所 (181)主迴路端子的配線 (181)控制迴路端子的低電壓配線 (189)馬達的過載、過熱保護 (190)4.4UL Standards (195)Area of Use (195)Main Circuit Terminal Wiring (195)Low Voltage Wiring for Control Circuit Terminals (211)Drive Motor Overload and Overheat Protection (211)4.5安全輸入 (217)規格 (217)注意事項 (217)安全功能的使用方法 (218)5.網路通訊 (221)5.1安全注意事項 (222)5.2現場總線網路的對應 (223)5.3MEMOBUS/Modbus通訊 (224)主站/從屬站的構成 (224)通訊規格 (224)與PLC間的通訊 (224)透過MEMOBUS/Modbus通訊運轉 (226)通訊時機 (226)資訊格式 (227)指令/回應時的資訊範例 (228)確定指令 (230)自檢 (230)通訊資料一覽 (231)錯誤代碼 (250)6.故障排除 (253)6.1安全注意事項 (254)6.2故障、輕故障、警告、錯誤的種類 (256)6.3故障、輕故障、警告、錯誤代碼一覽 (257)6.4故障 (262)6.5輕故障、警告 (277)6.6參數設定錯誤 (285)6.7自動調整錯誤 (289)6.8備份功能的動作模式顯示和錯誤 (292)6.9故障發生後變頻器的恢復方法 (293)發生故障的同時變頻器電源被切斷時的恢復步驟 (293)發生故障時變頻器電源未被切斷時的恢復步驟 (293)故障重定 (293)6.10操作器上無顯示時的故障排除 (294)無法變更參數的設定 (294)即使輸入運轉指令馬達也不旋轉 (294)馬達旋轉方向與運轉指令相反 (295)馬達只朝一個方向旋轉 (295)馬達異常發熱 (295)無法在操作器選擇希望進行的自動調整 (296)6株式會社安川電機SITP C71061707A安川變頻器GA700技術手冊加速時馬達失速/馬達未依設定值加速、減速 (296)馬達轉速和頻率指令值的設定值相差較大 (296)PM馬達的速度不穩定 (297)馬達振動強烈,無法正常旋轉 (297)即使連接制動選購品,馬達的減速時間也較長 (297)進行制動時垂直軸的負載滑落 (297)運轉變頻器後,其他控制裝置發生誤動作、收音機有雜音 (298)變頻器運轉中漏電斷路器(ELCB)進行不必要的動作 (298)馬達旋轉時機械發出異常聲音 (298)馬達旋轉時機械產生振動或波動 (298)PID輸出故障 (298)由於起動轉矩不足,馬達無法起動 (299)即使變頻器輸出被切斷,馬達仍未完全停止 (299)輸出頻率達不到頻率指令值 (299)馬達的激磁音發生變動 (299)停電恢復後,馬達也不重新起動 (299)7.檢查和維護 (301)7.1安全注意事項 (302)7.2檢查 (304)日常檢查 (304)定期檢查 (304)7.3維護 (306)7.4冷卻風扇、內部空氣攪動風扇的更換 (308)冷卻風扇、內部空氣攪動風扇的使用數量 (308)更換風扇(步驟A) (308)更換風扇(步驟B) (310)更換風扇(步驟C) (311)7.5更換變頻器主體 (314)關於控制迴路端子台 (314)更換變頻器 (314)7.6更換操作器的電池 (318)7.7存放要領 (319)8.廢棄物處理 (321)8.1安全注意事項 (322)8.2關於廢棄物處理的注意事項 (323)9.規格 (325)9.1安全注意事項 (326)9.2重載額定(HD)與輕載額定(ND) (327)9.3各種機型的規格(200V級) (328)9.4各種機型的規格(400V級) (330)9.5通用規格 (333)9.6變頻器的降低額定值 (336)載波頻率的設定和額定電流值 (336)根據海拔高度降低額定值 (338)9.7變頻器外形圖 (339)盤內安裝型(IP20) (339)封閉壁掛型(UL Type1) (341)9.8頂銷孔的外形尺寸(UL Type1) (344)9.9周邊機器和選購品 (345)10.參數一覽表 (349)株式會社安川電機SITP C71061707A安川變頻器GA700技術手冊710.1安全注意事項 (350)10.2參數一覽表的查閱方法 (351)表示控制模式的圖示及用語 (351)10.3參數群組 (352)10.4A:環境設定 (356)A1:環境設定模式 (356)A2:常用參數設定模式 (357)10.5b:應用程式 (358)b1:運轉模式選擇 (358)b2:直流制動/短路制動 (359)b3:速度搜尋 (359)b4:定時功能 (360)b5:PID控制 (361)b6:DWELL功能 (363)b7:DROOP(低下)控制 (364)b8:節能控制 (364)b9:零伺服 (365)10.6C:自動調整 (366)C1:加減速時間 (366)C2:S曲線特性 (366)C3:滑差補償 (367)C4:轉矩補償 (367)C5:速度控制(ASR:Automatic Speed Regulator) (368)C6:載波頻率 (369)10.7d:指令 (370)d1:頻率指令 (370)d2:頻率上限/下限 (371)d3:跳躍頻率 (371)d4:頻率指令保持指令、UP/DOWN指令、UP2/DOWN2指令 (371)d5:轉矩控制 (372)d6:激磁減弱和激磁增強 (372)d7:偏壓頻率 (373)10.8E:馬達參數 (374)E1:馬達1的V/f特性 (374)E2:馬達參數 (375)E3:馬達2的V/f特性 (375)E4:馬達2的參數 (376)E5:PM馬達的參數 (376)E9:EZ向量控制模式的馬達參數 (377)10.9F:選購品 (378)F1:PG選購卡的設定 (378)F2:類比輸入選購卡的設定 (379)F3:數位式輸入選購卡的設定 (380)F4:類比輸出選購卡的設定 (380)F5:數位式輸出選購卡的設定 (381)F6:通訊選購卡的設定 (381)F7:通訊選購卡的設定 (384)10.10H:端子功能選擇 (387)H1:多功能接點輸入 (387)H2:多功能接點輸出 (390)H3:多功能類比輸入 (394)H4:多功能類比輸出 (396)H5:MEMOBUS/Modbus通訊 (397)H6:脈波序列輸入輸出 (398)H7:虛擬輸入輸出功能選擇 (398)10.11L:保護功能 (400)8株式會社安川電機SITP C71061707A安川變頻器GA700技術手冊L1:馬達保護功能 (400)L2:瞬間停電處理 (400)L3:失速防止功能 (401)L4:頻率檢出 (402)L5:故障重試 (403)L6:過轉矩/轉矩不足檢出 (403)L7:轉矩限制 (404)L8:硬體保護 (404)L9:硬體保護2 (406)10.12n:特殊調整 (407)n1:防止波動功能 (407)n2:速度回授檢出控制功能 (407)n3:高滑差制動、過激磁減速 (407)n4:無PG高級向量控制的特殊調整 (408)n5:前饋控制 (408)n6:馬達線間電阻線上變更 (409)n7:EZ向量控制的特殊調整 (409)n8:PM馬達控制 (409)10.13o:操作器相關的設定 (411)o1:操作器的顯示設定 (411)o2:操作器的功能設定 (412)o3:參數的備份功能 (413)o4:維護監視的設定 (413)o5:資料日誌功能 (414)10.14q:DriveWorksEZ參數 (415)q1-01~q8-40:DriveWorksEZ未使用 (415)10.15r:DriveWorksEZ連接參數 (416)r1-01~r1-40:DriveWorksEZ連接參數1~20(高位元/低位元) (416)10.16T:自動調整 (417)T0:自動調整模式 (417)T1:感應馬達的馬達參數自動調整 (417)T2:PM馬達的馬達參數自動調整 (417)T3:控制系統自動調整 (418)T4:EZ調整 (419)10.17U:監視 (420)U1:狀態監視 (420)U2:故障追蹤 (421)U3:故障記錄 (423)U4:維護監視 (423)U5:應用程式監視 (426)U6:控制監視 (426)U8:DriveWorksEZ用的使用者監視 (428)10.18在A1-02[控制模式的選擇]出廠設定發生變更的參數 (429)10.19在E3-01[馬達2的控制模式選擇]出廠設定發生變更的參數 (433)10.20在E1-03[V/f曲線]出廠設定發生變更的參數 (434)10.21在o2-04[變頻器容量選擇]和C6-01[ND/HD選擇]出廠設定發生變更的參數 (436)200V級 (436)400V級 (441)10.22在E5-01[馬達代碼的選擇]出廠設定發生變更的參數 (448)安川製SMRA系列SPM馬達 (448)安川製SSR1系列IPM馬達(遞減轉矩用) (449)安川製SST4系列IPM馬達(固定轉矩用) (457)11.參數的詳細內容 (467)11.1安全注意事項 (468)株式會社安川電機SITP C71061707A安川變頻器GA700技術手冊911.2A:環境設定 (469)A1:環境設定模式 (469)A2:常用參數的設定模式 (484)11.3b:應用程式 (486)b1:運轉模式選擇 (486)b2:直流制動/短路制動 (496)b3:速度搜尋 (498)b4:定時功能 (505)b5:PID控制 (507)b6:DWELL功能 (521)b7:DROOP(低下)控制 (522)b8:節能控制 (523)b9:零伺服 (527)11.4C:自動調整 (528)C1:加減速時間 (528)C2:S曲線特性 (531)C3:滑差補償 (532)C4:轉矩補償 (535)C5:速度控制(ASR:Automatic Speed Regulator) (537)C6:載波頻率 (544)11.5d:指令 (548)d1:頻率指令 (548)d2:頻率上限/下限 (553)d3:跳躍頻率 (554)d4:頻率指令保持指令、UP/DOWN指令、UP2/DOWN2指令 (555)d5:轉矩控制 (559)d6:激磁減弱和激磁增強 (564)d7:偏壓頻率 (564)11.6E:馬達參數 (566)E1:馬達1的V/f特性 (566)E2:馬達參數 (572)E3:馬達2的V/f特性 (574)E4:馬達2的參數 (576)E5:PM馬達的參數 (578)E9:EZ向量控制模式的馬達參數 (581)11.7F:選購卡 (584)F1:PG選購卡的設定 (584)F2:類比輸入選購卡的設定 (589)F3:數位式輸入選購卡的設定 (591)F4:類比輸出選購卡的設定 (594)F5:數位式輸出選購卡的設定 (596)F6、F7:通訊選購卡的設定 (599)11.8H:端子功能選擇 (616)H1:多功能接點輸入 (616)多功能接點輸入的設定值 (619)H2:多功能接點輸出 (635)H2多功能接點輸出參數 (637)多功能接點輸出的設定值 (642)H3:多功能類比輸入 (654)H3:多功能類比輸入參數 (655)多功能類比輸入的設定值 (659)H4:多功能類比輸出 (664)H5:MEMOBUS/Modbus通訊 (667)H6:脈波序列輸出輸出 (670)H7:虛擬輸入輸出功能選擇 (673)11.9L:保護功能 (676)L1:馬達保護功能 (676)10株式會社安川電機SITP C71061707A安川變頻器GA700技術手冊L2:瞬間停電處理 (681)L3:失速防止功能 (688)L4:頻率檢出 (696)L5:故障重試 (698)L6:過轉矩/轉矩不足檢出 (699)L7:轉矩限制 (703)L8:硬體保護 (706)L9:硬體保護2 (713)11.10n:特殊調整 (714)n1:防止波動功能 (714)n2:速度回授檢出抑制功能 (716)n3:高滑差制動、過激磁減速 (716)n4:無PG高級向量控制的特殊調整 (719)n5:前饋控制 (721)n6:馬達線間電阻線上調整 (724)n7:EZ向量控制的特殊調整 (724)n8:PM馬達控制 (725)11.11o:操作器的設定 (732)o1:操作器的顯示設定 (732)o2:操作器的功能設定 (737)o3:參數的備份功能 (739)o4:維護監視的設定 (741)o5:資料日誌功能 (743)11.12T:自動調整 (748)T0:自動調整模式 (748)T1:感應馬達的馬達參數自動調整 (748)T2:PM馬達的馬達參數自動調整 (750)T3:控制系統自動調整 (753)T4:EZ調整 (753)索引 (756)改版履歷 (765)前言和一般注意事項本章對與本產品相關的安全注意事項進行說明。

SA系列NP型三极管参数表

-30

200M

100-500

3CG120A

2SA1029B

HITACHI

硅PNP三极管,低频放大,配对管2SC458/2SC2308

300m

-100m

-30

-30

200M

100-500

3CK14F

2SA103

锗PNP三极管,高频射频放大

60m

-10m

-40

35M

25-250

3AG95A

2SA1030

140M

120-560

2SA1037K

ROHM

硅PNP三极管,一般小信号放大,配对管2SC2412K/2SC4081

200m

-100m

-50

-40

140M

120-560

2SA1038S

ROHM

硅PNP三极管,高压放大,配对管2SC2389S

300m

-50m

-120

-120

140M

180-560

3CG170C

硅PNP三极管,低频功率放大,配对管2SC1847

-50

-40

150M

80-220

3CK10B

2SA100

锗PNP三极管,高频射频放大

60m

-10m

-40

10M

80-300

3AG95A

2SA1001

硅PNP三极管

80

130

3CD10E

2SA1002

硅PNP三极管

120

120

3CD15D

2SA1003

UTC

硅PNP三极管,功率放大,功率开关,配对管2SC2655

900m

op07c

PACKAGING INFORMATIONOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)OP-07DPSR ACTIVE SO PS82000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMOP-07DPSRE4ACTIVE SO PS82000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMOP-07DPSRG4ACTIVE SO PS82000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMOP07CD ACTIVE SOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMOP07CDE4ACTIVE SOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMOP07CDG4ACTIVE SOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMOP07CDR ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMOP07CDRE4ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMOP07CDRG4ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMOP07CP ACTIVE PDIP P850Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeOP07CPE4ACTIVE PDIP P850Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeOP07DD ACTIVE SOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMOP07DDE4ACTIVE SOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMOP07DDG4ACTIVE SOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMOP07DDR ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMOP07DDRE4ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMOP07DDRG4ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMOP07DP ACTIVE PDIP P850Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeOP07DPE4ACTIVE PDIP P850Pb-Free(RoHS)CU NIPDAU N/A for Pkg Type(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan-The planned eco-friendly classification:Pb-Free(RoHS),Pb-Free(RoHS Exempt),or Green(RoHS&no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free(RoHS):TI's terms"Lead-Free"or"Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all6substances,including the requirement that lead not exceed0.1%by weight in homogeneous materials.Where designed to be solderedat high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free(RoHS Exempt):This component has a RoHS exemption for either1)lead-based flip-chip solder bumps used between the die and package,or2)lead-based die adhesive used between the die and leadframe.The component is otherwise considered Pb-Free(RoHS compatible)as defined above.Green(RoHS&no Sb/Br):TI defines"Green"to mean Pb-Free(RoHS compatible),and free of Bromine(Br)and Antimony(Sb)based flame retardants(Br or Sb do not exceed0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.TAPE AND REEL INFORMATION*All dimensions are nominal Device Package Type Package DrawingPinsSPQ Reel Diameter (mm)Reel Width W1(mm)A0(mm)B0(mm)K0(mm)P1(mm)W (mm)Pin1Quadrant OP-07DPSR SOPS 82000330.016.48.2 6.6 2.512.016.0Q1OP07CDR SOICD 82500330.012.4 6.4 5.2 2.18.012.0Q1OP07DDR SOIC D 82500330.012.4 6.4 5.2 2.18.012.0Q1*All dimensions are nominalDevice Package Type Package Drawing Pins SPQ Length(mm)Width(mm)Height(mm) OP-07DPSR SO PS82000346.0346.033.0 OP07CDR SOIC D8*******.5338.120.6 OP07DDR SOIC D8*******.5338.120.6IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDLP®Products Communications and /communicationsTelecomDSP Computers and /computersPeripheralsClocks and Timers /clocks Consumer Electronics /consumer-appsInterface Energy /energyLogic Industrial /industrialPower Mgmt Medical /medicalMicrocontrollers Security /securityRFID Space,Avionics&/space-avionics-defenseDefenseRF/IF and ZigBee®Solutions /lprf Video and Imaging /videoWireless /wireless-appsMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2010,Texas Instruments Incorporated。

74ls373中文资料

型号

tPd

54S373/74S373

7ns

54LS373/74LS373

17ns

PD 525mW 120mW

373 的输出端 O0~O7 可直接与总线相连。

当三态允许控制端 OE 为低电平时,O0~O7 为正常逻辑状态,可用来驱动负载或总

线。当 OE 为高电平时,O0~O7 呈高阻态,即不驱动总线,也不为总线的负载,但

ic中文-17IC中文资料网 - IC中文资料-IC渠道网 IC中文资料 - 电源 - 嵌入式 - 电路图 - 单片机 - 应用方案 - 技术文章

首 页 IC库存 电子资讯 技术资料

IC

非IC

求购信息

PDF 资料

IC库存搜索: 请输入IC型号

搜索

最新搜索: VN2406LZL1 MAX881REUB+T IC42S16400-6TG LTC2230IUP MSR320 HLMP-2700 GS-R405S EPF10K10LI84 …

IC中文资料

型号A开头

型号B 开头

型号C开头

·MCP1316中文资料MCP1317应用MCP1318 MCP1319封装图MC... ·MCP111 中文资料 MCP112 应用 pdf 封装图 管脚说明... ·MCP102中文资料MCP103应用MCP111 MCP121封装图MCP131... ·MCP41010 中文资料 MCP41050 应用 pdf MCP41100 封... ·MCP40D17中文资料 MCP40D18应用 pdf MCP40D19 封装图... ·DS12R885 中文资料 DS12CR887 应用 pdf DS12R887封... ·MAX6972ATJ 中文资料 MAX6973ATJ 应用 pdf 封装图 管脚... ·MCP14E3中文资料MCP14E4 应用 pdf 封装图 MCP14E5管脚说... ·MCP6V06中文资料 MCP6V07应用 pdf 封装图 MCP6V08管脚说... ·MCP6V01中文资料MCP6V02应用 pdf 封装图MCP6V03 管脚说明...

CS4353资料