FPGA中AD转换与显示接口电路设计

第8章 AD和DA转换模块设计

#include<intrins.h> unsigned int a,b; sbit di=P3^7; sbit clock=P3^6; sbit cs=P3^5;

//移位函数头文件 //定义变量 //定义串行输入口 //定义时钟位 //定义片选位

/******************************************/ /* 延时子程序 */ /******************************************/ void delay(unsigned int z) { unsigned int x,y; for(x=z;x>0;x--) for(y=114;y>0;y--); } void _nop_(); //空操作 较短延时 /******************************************/ /* 主程序 */ /******************************************/ void main()

注:Vref+为加到 TLC1543 REF+端的电压,Vref-是加到 REF-端的电压

同时,串口也从DATAOUT端接收前一次转换的结果。它以MSD前导方式 DATAOUT输出,但MSB出现在DATAOUT端的时刻取决于串行接口时序。 TLC1543可以用6种基本串行接口时序方式,这些方式取决于I/0 CLOCK 的速度与CS的工作,如表8-2所示。

A0 A1 A2 A3 A4 A5 A6 A7 A8 GND 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 Vcc EOC I/O CLOCK ADDRESS DATA OUT __ CS REF+ REFA10 A9

FPGA实验报告整理版.doc

目录实验一分频器实验三 ADC0809 模数转换实验实验二七段数码管扫描显示实验四双向移位寄存器实验一分频器一、实验目的1.学习分频器的设计,进一步了解、熟悉和掌握FPGA开发软件Quartus II 的使用方法2.学习Verilog HDL 和VHDL的编程方法3.学会使用Vector Wave功能仿真4.掌握使用多种方法分配管脚二、实验内容编写一个分频器的Verilog 代码和VHDL代码并仿真,编译下载验证三、实验原理在数字电路中,时钟信号的分频是很常见的电路。

分频器除了可以对时钟信号频率做除以二的计算外,分频器同时很类似涟波计数器。

涟波计数器是计数器的一种,它属于异步设计。

因为触发器并非皆由同一个时钟信号同步操作,所以它非常节省电路面积。

本实验要设一个带选择的分频时钟,SEL[1:0]用于选择是几分频。

分频器设原理框图如图1所示:图1 分频器原理图从原理图中可见,核心板的时钟是50MHz ,通过sel[1:0]选择分频数,00:不分频;01:12.5M分频;10:25M四分频;11:50M分频。

采用SW1 ‐SW2 设置分频值,SW3 复位。

LED1为时钟的输出,通过调整SW1 、SW2 ,可以得到不同的闪烁频率。

引脚分配情况如表1所示表1 引脚分布情况四、实验步骤1.新建工程,取名为frediv ,如下图2所示。

图2 新建工程2.新建VHDL设计文件,选择“File|New ”,在New 对话框中选择Device Design Files下的VHDL File,单击OK,完成新建设计文件。

3.在新建设计文件中输入VHDL程序。

4.生成“Symbol ”文件,新建“Block Diagram/Schematic File”文件,在文件中添加刚刚生成的“Symbol ”以及输入输出管脚,最后完整的系统顶层模块图如图3 所示。

图3 顶层模块图5.保存文件,使用qsf或者tcl 进行管脚分配(相应的文件在本工程里面都可以找到)。

FPGA与ADC0809接口电路详解

FPGA与ADC0809接口电路详解注:(1)本程序基于FPGA和vhdl编写有详尽的程序解释和原理分析以及原理图,状态图(2)对于adc0809具体资料可上网查在此不累述一.FPGA与ADC0809的接口电路图原理二.关于ADC0809的说明(重点)(1)ale信号(引脚):高电平时把三个地址信号送入地址锁存器,并经译码器得到地址数据,以选择相应的模拟输入通道。

(2)oe信号(引脚)en使能信号:电平由低变高时,打开数据输出锁存器,将转换数据送到数据总线上(3)eoc信号(引脚):eoc为高电平时完成转换,为低电平时正在转换。

(4)start信号(引脚):要给start线送一个100ns宽的启动正脉冲,start下跳沿时,开始进行A/D转换,在转换期间start以保持低电平。

三.转换状态图对于状态图的真值表未列出 注意对应的注释为vhdl 语句ale<='1';start<='0';en<='0';----eoc='1' ale<='0';start<='0';en<='0';--再次检测数据是否转换完 if eoc='0' then next_state<=st4;else next_state<=st5;器,将数据送入数据总线存器四.ADC0809采样接口电路程序--*********ADC0809采样控制*************--******因为FPGA 的时钟频率为50MHz ,则256分频后,即ADC0809输入时钟为195KHz****** --******对ADC0809进行简单的采样控制,得到的数据进FPGA 送到8个并排的数码管显示***** library ieee;use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; use ieee.std_logic_arith.all; entity PL_AD isport ( d : in std_logic_vector(7 downto 0); --ADC0809输出的采样数据输入FPGA clk,eoc: in std_logic; --clk 为系统时钟,eoc 为ADC0809转换结束信号输入FPGA lock1,start, ale,en: out std_logic; --ADC0809控制信号FPGA 输出信号 abc_in :in std_logic_vector(2 downto 0); --模拟选通信号abc_out :std_logic_vector(2 downto 0);--ADC0809模拟信号选通信号q : out std_logic_vector(7 downto 0));送至8个并排数码管信号FPGA 输出数字信号 end pl_AD;architecture behav of PL_AD istype states is ( st0,st1, st2, st3, st4,st5,st6);--定义状态类型枚举类型signal current_state, next_state:states:=st0;--定义总体两个状态现态和次态并且初值为st0态signal regl :std_logic_vector(7 downto 0);--定义中间寄存器signal lock : std_logic;signal qq:std_logic_vector(7 downto 0);--定义计数器用于分频begincom:process(current_state,eoc) –此进程主要是驱动ADC0809工作即数据转换过程begincase current_state iswhen st0=>next_state<=st1;ale<='0';start<='0';en<='0';--准备when st1=>next_state<=st2;ale<='1';start<='0';en<='0';--三个地址信号送入地址锁存器when st2=>next_state<=st3;ale<='0';start<='1';en<='0';--开始数据转换when st3=> ale<='0';start<='0';en<='0';--检测数据是否转换完if eoc='1' then next_state<=st3;else next_state<=st4;end if;when st4=> ale<='0';start<='0';en<='0';--再次检测数据是否转换完if eoc='0' then next_state<=st4;else next_state<=st5;end if;when st5=>next_state<=st6;ale<='0';start<='0';en<='1'; --打开输出数据锁存器,将数据送入数据总线when st6=>next_state<=st0;ale<='0';start<='0';en<='1';regl<=d;--打开输出数据锁存器,将数据送入寄存器regl when others=> next_state<=st0;ale<='0';start<='0';en<='0';end case;end process;clock:process(clk) --对系统时钟进行分频,得到驱动ADC0809的时钟信号beginif clk'event and clk='1' then qq<=qq+1;if QQ="01111111" THEN lock<='1';--实现分频current_state <=next_state;--在lock上升沿,转换至下一状态elsif qq<="01111111" then lock<='0';end if;end if;end process;q<=regl;--寄存器数据输出即FPGA输出lock1<=lock;abc_out<=abc_in;--模拟选通信号送往ADC0809end behav;注:有错when st3=> ale<='0';start<='0';en<='0';--检测数据是否转换完if eoc='1' then next_state<=st3;else next_state<=st4;end if;when st4=> ale<='0';start<='0';en<='0';--再次检测数据是否转换完if eoc='0' then next_state<=st4;else next_state<=st5;end if;不过我这里的注释好像错了,这两个when合起来才是检测数据是否转换完的。

AD转换器及其接口设计详解

AD转换器及其接口设计详解AD转换器(Analog-to-Digital Converter)是将模拟信号转换为数字信号的电子设备。

它是现代电子系统中常见的组件之一,广泛应用于通信、测量、仪器仪表、音频处理等领域。

在AD转换器的设计中,接口设计是至关重要的,它直接影响着AD转换器的性能和可靠性。

物理接口是指AD转换器与其他外部设备(如微处理器、FPGA等)之间的连接方式和信号传输方式。

常见的物理接口包括并行接口、串行接口、I2C接口、SPI接口等。

在选择物理接口时,需要考虑系统的数据传输速度、数据带宽、线路长度、抗干扰能力等因素。

不同的物理接口有不同的特点和适用场景,因此需要根据具体应用需求选择适合的物理接口。

逻辑接口是指AD转换器与外部设备之间的控制和数据传输逻辑。

常见的逻辑接口包括并行接口、串行接口、I2C接口、SPI接口、USB接口等。

逻辑接口的设计需要考虑控制信号的数量、数据传输的稳定性、响应速度等因素。

同时,还需要考虑系统的复杂度、功耗、成本等方面的要求。

AD转换器的接口设计还需要考虑信号的采样率、分辨率和精度。

采样率是指AD转换器从模拟信号中采集样本的速率,常用单位为样本/秒(SPS),采样率越高,可以保留更多的信号细节。

分辨率是指AD转换器的输出数值的位数,通常以比特(bit)为单位,分辨率越高,可以提供更准确的数字化信号。

精度是指AD转换器输出的数字值与实际模拟信号之间的误差,一般以最大有效位数或最小非零位数表示,精度越高,误差越小。

在AD转换器的接口设计中,还需要考虑芯片的功耗、尺寸和成本等因素。

功耗是指AD转换器在工作过程中所消耗的电能,功耗越低,可以延长系统的电池寿命或减少系统的散热需求。

尺寸是指AD转换器的物理尺寸,尺寸越小,可以降低系统的体积和重量。

成本是指AD转换器的制造成本,成本越低,可以降低系统的总体成本。

总之,AD转换器的接口设计是一个综合考虑多个因素的过程,需要根据具体应用需求选择适当的物理接口、逻辑接口和信号参数。

EDA技术及应用—基于FPGA的电子系统设计:基于Verilog hdl的数字电路设计

10100

1111

15

10101

8421BC 余三码 D码

0000

0011

0001

0100

0010

0101

0011

0110

0100

0111

0101

1000

0110

1001

0111

1010

1000

1011

1001

1100

-

-

-

-

-

-

-

-

-

-

-

-

4位格雷码

0000 0001 0011 0010 0110 0111 0101 0100 1100 1101 1111 1110 1010 1011 1001 1000

4'b0011:a_to_g=7'b1111001; //显示3

4'b0100:a_to_g=7'b0110011; //显示4

4'b0101:a_to_g=7'b1011011; //显示5

4'b0110:a_to_g=7'b1011111; //显示6

4'b0111:a_to_g=7'b1110000; //显示7

4: y= {d[2:0],d[3]}; // rol

5: y= {d[3],d[3:1]}; // asr

6: y= {d[1:0],d[3:2]}; // ror2

7: y= d;

// noshift

default: y = d;

图6-2 基本门电路仿真结果

综合结果如图6-3所示。

图6-3 基本门电路综合结果

2、 三态逻辑电路

基于FPGA的数字直流电压表的设计

基于FPGA的数字直流电压表的设计基于FPGA的数字直流电压表的设计文献综述随着电子技术的发展,当前数字电子系统的设计正朝着速度快、容量大、体积小、重量轻的方向发展。

推动该潮流发展的引擎就是日趋进步和完善的ASIC设计技术[1]。

而数字电压表作为数字电子系统的核心与基础,其设计与开发,已经有多种的类型和款式。

其中以单片机为基础的数字电压表设计和可编程逻辑器件为基础的数字电压表设计为典型,这两种类型的数字电压表各有特点,但是都是要经过AD数模转换器将模拟信号转换成数字信号直接显示在LED上[2]。

一、方案比较基于单片机的数字电压表的实现,依靠的是硬件电路,并通过软件程序的控制,最后对输入模拟信号进行AMD转换,数据处理,驱动数码管显示被测电压。

它的设计包括硬件电路的设计、软件设计两个部分,主要依靠软件来实现功能[3]。

单片机又称单片微控制器,它不是完成某一个逻辑功能的芯片,而是把一个计算机系统集成到一个芯片上。

概括的讲:一块芯片就成了一台计算机。

它的体积小、质量轻、价格便宜、受到了很大的欢迎,可它的不足之处就在于设计繁琐,资源利用率不高,集成化程度不够高等的方面[4]。

基于可编程逻辑器件的数字电压表整个系统可分为三大部分:AD控制模块,BCD码转换模块以及扫描显示模块。

其测量精度高、灵活性和可扩展性好[5]。

可编程逻辑器件主要包括FPGA和CPLD。

FPGA(Field Programmable Gate Array,现场可编程门阵列)基本结构包括可编程的CLB(Configurable Logic Block,可配置逻辑块)阵列组成、可编程的IMO模块与负责CLB之间传输信号的可编程连接点。

CPLD(Complex Programmable Logic Device,复杂可编程逻辑器件)包括逻辑阵列块、IMO控制块、可编程连接阵列。

FPGA与CPLD虽然结构截然不同,但都可以用于复杂的逻辑电路,可使用相同的工具和硬件描述语言(如VHDL,Verilog HDL等)开发设计[6]。

基于FPGA的ADC采集系统的设计_毕业设计论文

基于FPGA的ADC采集系统的设计摘要基于FPGA在高速数据采集方面有单片机和DSP无法比拟的优势,FPGA具有时钟频率高,内部延时小,全部控制逻辑由硬件完成,速度快,效率高,组成形式灵活等特点。

因此,本文研究并开发了一个基于FPGA的数据采集系统。

FPGA的IO口可以自由定义,没有固定总线限制更加灵活变通。

本文中所提出的数据采集系统设计方案,就是利用FPGA作为整个数据采集系统的核心来对系统时序和各逻辑模块进行控制。

依靠FPGA强大的功能基础,以FPGA作为桥梁合理的连接了ADC、显示器件以及其他外围电路,最终实现了课题的要求,达到了数据采集的目的。

关键词FPGA A/D转换AbstractFPGA is better than microcontroller and DSP in high speed data acquisition, FPGA has higher internal clock frequency, smaller delay than DSP,and all the control logic of FPGA is completed by hardware, FPGA has fast speed, high efficiency, and so on. Therefore, this paper introduces and develops a data acquisition system which is based on FPGA.The I/O pin of FPGA can be defined yourself without fixed limit,it’s very flexible. This design of data acquisition system use FPGA as the data acquisition system core to control the timing and the logic control module. Relying on the powerful function of FPGA, FPGA can connect ADC, display devices and other peripheral circuits, finally we can achieve the requirements of the subject, and the purpose of the data collection。

在高速的AD转换中 FPGA承担着不可替代的作用

在高速的AD转换中FPGA承担着不可替代的作用

AD转换,也叫模数转换,是将模拟信号转换为数字信号。

目前包括电脑CPU,ARM,FPGA,处理的信号都只能是数字信号,所以数据信号在进入处理芯片前必须要进行AD转换。

在高速的AD转换中,FPGA以其高速的处理能力,并行的运行结构,丰富的IO资源,往往承担者不可替代的作用。

下面给出一个实际的设计方案。

AD芯片的时钟为25M,FPGA内部系统时钟频率为100M,FPGA内部处理AD数据的处理模块需要8个时钟周期才能处理完一个数据。

根据上述给出的条件,我们可以知道。

按正常思路设计方案,肯定会造成AD数据的丢失,为什么会丢失数据,试想一下,FPGA处理一个数据需要8个时钟周期,才能采集下一个数据,这样算下来AD需要的时钟是12.5M,而给定的AD时钟是25M,所以肯定会漏掉数据。

根据分析,可以采用乒乓操作通过缓存降低数据采样率。

乒乓操作如下图:

具体乒乓操作为什么能够降低数据速率,这里将不做详细介绍。

以上方案可以满足上述处理AD数据的需求。

紧接着继续增加需求条件,要求数据处理需要连续,不能打乱顺序,前面数据的处理会影响后续数据处理。

这样乒乓操作将不适合,具体原因,读者可以自己想一下(乒乓操作会以数据块打乱数据顺序)。

根据上述条件,设计方案需要修改。

可以外加存储器,FPGA片上存储器资源有限。

添加SDRAM提高存储速度和存储量。

继续添加需求,如果AD数据连续不断,那么势必是造成SDRAM溢出。

那么上述设计方。

基于FPGA和高精度ADC的组合导航系统设计

基于FPGA和高精度ADC的组合导航系统设计作者:田育民刘思伟白云超来源:《现代电子技术》2008年第17期摘要:介绍了高精度模数变换(ADC)和现场可编程门阵列(FPGA)在惯性导航系统(INS)与全球定位系统(GPS)构成的组合导航系统中的应用,讨论了运用多片ADC同时对陀螺仪、加速度计等惯性传感器信号进行并行采集,使用FPGA实现对ADC进行时序控制和对采集到的信号进行硬件数字滤波的方案,最后给出了系统测试结果,达到了预期的设计目的。

关键词:组合导航;FPGA;模数转换;OMAP中图分类号:TP391.76 文献标识码:B 文章编号:1004373X(2008)1702803System Design of Integrated Navigation Based on FPGA and ADCTIAN Yumin,LIU Siwei,BAI Yunchao(Xi′an Research Institute of Surveying and Mapping,Xi′an,710054,China)Abstract:This paper introduces high-precision Analog-to-Digital Converter (ADC) and Field Programmable Gates Array (FPGA) application approach in a Inertial Navigation System(INS) and Global Positioning System(GPS) integrated navigation system.It discusses how to utilize AD2151 converter to collect data of multi gyroscope and accelerometer,how to control A/D by FPGA,how to filer the data signal in FPGA.Finally,the test result of system is presented,which meets the design goal so well.Keywords:integrated navigation;FPGA;analog-to-digital converter;OMAP1 引言INS/GPS组合导航系统在军事领域和民用方面的运动载体中得到了广泛应用。

基于FPGA的微型示波器设计

设计应用技术D/AD/A A/D D/A常运行,于此可以判断所得数据是否正确。

因此,在模拟数据输入端口需要设计一个电压衰减电路,降低电压至有效范围之内。

tc模拟输入输入时钟数据输出tcHtcLS 1S2S3S425nsDATA1图4 AD9280时序波形分析3.2 高速DA模块由3PD9780芯片构成的高速DA模块,是一种电流输出数模转换器(Digital to Analog Converter,DAC),是由思瑞浦公司研发的一款以大量P沟道金属氧化物半导体(Positive Channel Metal Oxide Semiconductor,PMOS)电流源阵列组成的芯片。

该阵列被分成32个相等的电流,能够提供高达20 mA的总电流,构成5个最高有效值(Most Significant Bit,MSBs)。

其余的3个MSB也采用了相等加权的电流源,其总和等于一个MSB电流源的7/8。

使用电流源实现上下位有助于保持DAC的高输出阻抗(即>100 kW)。

所有这些电流源都通过PMOS差动电流开关切换到2个输出节点中的一个或另一个。

这些开关是基于一种新的架构,大大提高了失真性能。

由这8个数据输入(MSB)引脚和一个时钟输入引脚组成输入数据,具有8位数据位,且3PD9780芯片支持高达125 MSPS的时钟速率。

3PD9780的工作原理比较简单,只需要输入一个时钟信号,给定合理的参考电压,则会产生差分电流信号。

经过一个7阶低通滤波器,再经过2个AD8066将差分电流信号变为单端信号并放大。

3PD9780的原理如图5所示。

4 软件设计为了搭建微型示波器系统,提出一种不同于其他系统的示波器,极大程度地发挥了FPGA的优势,采用并行模式并创造了多个模块,以达到能够在一个时钟周期内进行多级数据处理的目的,主要分4个层次:数据处理区、驱动层、数据交互区以及用户界面(User Interface,UI)。

软件设计结构如图6所示。

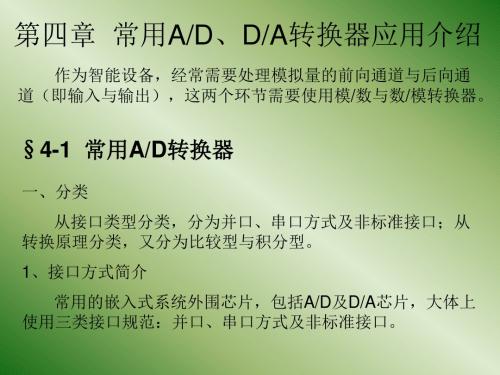

电子设计创新训练(基础)第四章 常用AD、DA转换器应用介绍

此程序仅为一个采样示例, 主函数实际没有使用意义。

(二)8路8位分辨率ADC0809及与MCU的直接I/O接口

1、简介

ADC0809芯片有28条引脚,采用双列直 插式封装,如图3-13所示。下面说明各引脚功 能。IN0~IN7:8路模拟量输入端。2-1~2-8: 8位数字量输出端。ADDA、ADDB、ADDC:3 位地址输入线,用于选通8路模拟输入中的一路。 ALE:地址锁存允许信号,输入,高电平有效。 START: A/D转换启动信号,输入,高电平 有效。 EOC: A/D转换结束信号,输出, 当A/D转换结束时,此端输出一个高电平(转 换期间一直为低电平)。 OE:数据输出允许 信号,输入,高电平有效。当A/D转换结束时, 此端输入一个高电平,才能打开输出三态门, 输出数字量。CLK:时钟脉冲输入端。要求时 钟频率不高于640KHZ(典型500KHZ,转换时 间小于100μs)。 REF(+)、REF(-):基 准电压。 Vcc:电源,单一+5V。GND:地。 图4-13 ADC0809引脚图

图4-8 AD57A的管脚图

A0 :字节地址/短周期,高为8位变换/输出低4位,低为12位变换/输出高8位; STS :变换状态,高为正在变换,低为变换结束.STS总共有三种接法:(1)空着:只 能在启动变换,25 μ s以后读A/D结果;(2)接静态端口线:可用查询方法,待STS为 低后再读A/D变换结果;(3)接外部中断线:可引起中断后,读A/D变换结果; REFIN :基准输入. REFOUT :内部10V基准输出; BIP OFF :双极性方式时,偏置电压输入端(10V基准);

ADC0809的工作过程是:首先输入3位地址,并使ALE=1,将地址存 入地址锁存器中。此地址经译码选通8路模拟输入之一到比较器。START上 升沿将逐次逼近寄存器复位。下降沿启动 A/D转换,之后EOC输出信号变 低,指示转换正在进行。直到A/D转换完成,EOC变为高电平,指示A/ D转换结束,结果数据已存入锁存器,这个信号可用作中断申请。当OE输 入高电平 时,输出三态门打开,转换结果的数字量输出到数据总线上。

基于FPGA的HDMI显示系统的设计与实现

as weU as compiliⅡg and publishing the tiUe and abstract of this th销is,consistent with¨fair

use"as pnscribed in the COpyright Law Of The P∞pIe’s Republic of China.

饮pKcit哆aclmowIedged and included in the Refe阳nc鹤sec伽n at the阻d of this thesis.

魄咖他:喜鹾薹jate:么心生

Copyright Notice

I henin agr∞that the Libnry of ECNU shaU make its copi伪fhely available for

fhmer cop咖g 纽spection.I

agr∞that extens押e

of the thesis缸aHowable oⅡ炒for

鲍hohrly purpos铭,in panicular'storing the cont蛆t of this thesis into聆levant databas馏,

bave HDMI interfIace.Now it becomes one of仕屺standard砒erfhes and is

success觚1y applied t0}、析ile钿.eas.

S硫eⅪLINX invented the mSt FPGA d卸in也c 1980s,FPGA is e妣nsively

Signatllre:

Ⅳ

华东师范大学硕士毕业论文

第一章 绪论

1.1课题的研究背景

1.1.1皿MI的出现背景 随着科学技术的迅速发展,人们的生活水平日益提高。在满足日益丰富的

AD转换与单片机的接口电路(ADC0809)

;设置第0工作区 设置第 工作区 ;采样数据存放首址 ;IN0通道地址 通道地址 ;模拟量通道数 启动A/D转换 ;启动 转换 外部中断0为边沿触发方式 ;外部中断 为边沿触发方式 允许外部中断0中断 ;允许外部中断 中断 开放CPU中断 ;开放 中断

Copyright 2006

ADC 0809

22 21 20 19 18 17 16 15

Copyright 2006

ADC0809的通道选择: 的通道选择: 的通道选择

被选通的通道 IN0 IN1 IN2 IN3 ADDC 0 0 0 0 ADDB 0 0 1 1 ADDA 0 1 0 ቤተ መጻሕፍቲ ባይዱ 被选通的通道 IN4 IN5 IN6 IN7 ADDC 1 1 1 1 ADDB 0 0 1 1 ADDA 0 1 0 1

A/D转换器与单片机的接口技术 转换器与单片机的接口技术

从物理信号到电信号的转换

A/D转换器的作用是将模拟的电信号转换成数字信号。在将 物理量转换成数字量之前,必须先将物理量转换成电模拟 量,这种转换是靠传感器完成的。传感器的种类繁多,如 温度传感器,压力传感器、光传感器、气敏传感器等。 温度传感器:典型的温度传感器有热电偶和热敏电阻。热 电偶是利用热点效应来工作的,室温下的输出电压为毫伏 级的。热敏电阻是一种半导体新型感温元件,具有负的电 阻温度系数,当温度升高时,其电阻减小。 湿度传感器:是利用湿度变化引起其电阻值或电容量变 化原理制成的,即将湿度变化转换成电量变化。

Copyright 2006

ADC0809与51单片机接口 与 单片机接口

ADC0809与单片机接口 与单片机接口

通道地址: 78H~7FH

Copyright 2006

FPGA控制AD转换原理及程序

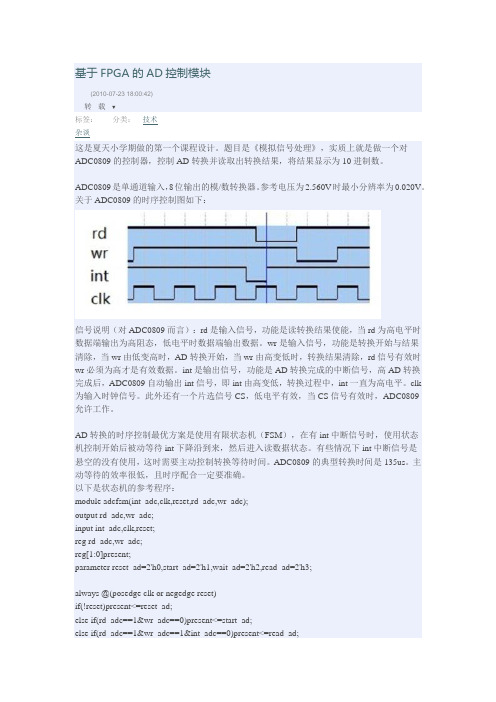

基于FPGA的AD控制模块(2010-07-23 18:00:42)转载▼分类:技术标签:杂谈这是夏天小学期做的第一个课程设计。

题目是《模拟信号处理》,实质上就是做一个对ADC0809的控制器,控制AD转换并读取出转换结果,将结果显示为10进制数。

ADC0809是单通道输入,8位输出的模/数转换器。

参考电压为2.560V时最小分辨率为0.020V。

关于ADC0809的时序控制图如下:信号说明(对ADC0809而言):rd是输入信号,功能是读转换结果使能,当rd为高电平时数据端输出为高阻态,低电平时数据端输出数据。

wr是输入信号,功能是转换开始与结果清除,当wr由低变高时,AD转换开始,当wr由高变低时,转换结果清除,rd信号有效时wr必须为高才是有效数据。

int是输出信号,功能是AD转换完成的中断信号,高AD转换完成后,ADC0809自动输出int信号,即int由高变低,转换过程中,int一直为高电平。

clk 为输入时钟信号。

此外还有一个片选信号CS,低电平有效,当CS信号有效时,ADC0809允许工作。

AD转换的时序控制最优方案是使用有限状态机(FSM),在有int中断信号时,使用状态机控制开始后被动等待int下降沿到来,然后进入读数据状态。

有些情况下int中断信号是悬空的没有使用,这时需要主动控制转换等待时间。

ADC0809的典型转换时间是135us。

主动等待的效率很低,且时序配合一定要准确。

以下是状态机的参考程序:moduleadcfsm(int_adc,clk,reset,rd_adc,wr_adc);outputrd_adc,wr_adc;inputint_adc,clk,reset;regrd_adc,wr_adc;reg[1:0]present;parameterreset_ad=2'h0,start_ad=2'h1,wait_ad=2'h2,read_ad=2'h3;always @(posedgeclk or negedge reset)if(!reset)present<=reset_ad;else if(rd_adc==1&wr_adc==0)present<=start_ad;else if(rd_adc==1&wr_adc==1&int_adc==0)present<=read_ad;else if(rd_adc==1&wr_adc==1)present<=wait_ad;else present<=reset_ad;always @(present)begincase(present)reset_ad:beginrd_adc<=1;wr_adc<=0;endstart_ad:beginrd_adc<=1;wr_adc<=1;endwait_ad:beginrd_adc<=1;wr_adc<=1;endread_ad:beginrd_adc<=0;wr_adc<=1;endendcaseendendmoduleAD转换后的结果为8位二进制数据,即00H~FFH,要输出到数码管上显示,需要将二进制码转换为8421BCD码。

AD转换

ADCDLY 符号

DELAY [15: 0] (1)在正常转换模式、分开的X/Y位置转换模式和 X/Y位置自动(顺序)转换模式的X/Y位置转换延时值。 (2)在等待中断模式:当在此模式按下触笔时,这个 寄存器在几ms时间间隔内产生用于进行X/Y方向自动转 换的中断信号(INT_TC)。 注意:不能使用零位值(0x0000)

双积分式A/D转换图

图5.2.2 (a)双积分式A/D转换器电路结构图

图5.2.2 (b)积分输出波形

3.逐次逼近式A/D转换器原理 逐次逼近式A/D转换器电路结构如图5.2.3所示,其工作过程可与天 平称重物类比,图中的电压比较器相当于天平,被测电压Ux相当于 重物,基准电压Ur相当于电压法码。该方案具有各种规格的按8421 编码的二进制电压法码Ur,根据Ux<Ur和Ux>Ur,比较器有不同的 输出以打开或关闭逐次逼近寄存器的各位。输出从大到小的基准电 压法码,与被测电压Ux比较,并逐渐减小其差值,使之逼近平衡。 当Ux=Ur时,比较器输出为零,相当于天平平衡,最后以数字显示 的平衡值即为被测电压值。 逐次逼近式A/D转换器转换速度快,转换精度较高,对N位A/D转换 只需N个时钟脉冲即可完成,可用于测量微秒级的过渡过程的变化, 是在计算机系统中采用最多的一种A/D转换方法。

2.双积分式A/D转换器原理 双积分式A/D转换器对输入模拟电压和参考电压进行两次积分, 将电压变换成与其成正比的时间间隔,利用时钟脉冲和计数器测 出其时间间隔,完成A/D转换。双积分式A/D转换器主要包括积分 器、比较器、计数器和标准电压源等部件,其电路结构图如图 5.2.2(a)所示。 双积分式A/D转换器的转换过程如下: 首先对输入待测的模拟电压Vi进行固定时间的积分; 然后转换到标准电压VR进行固定斜率的反向积分(定值积分 ), 如图5.2.2(b)所示。反向积分进行到一定时间,便返回起始值。 从图5.2.2(b)中可看出对标准电压VR进行反向积分的时间T2正 比于输入模拟电压,输入模拟电压越大,反向积分回到起始值的 时间T越长,有Vi=(T2/T1)VR。 用标准时钟脉冲测定反向积分时间(如计数器),就可以得到对 应于输入模拟电压的数字量,实现A/D转换。 双积分式A/D转换器具有很强的抗工频干扰能力,转换精度高, 但速度较慢。

AD转换设计中的基本问题整理

AD转换设计中的基本问题整理了解数据转换器错误及参数1.如何选择高速模数转换之前的信号调理器件;如何解决多路模数转换的同步问题?ADC之前的信号调理,最根本的原则就是信号调理引起的噪声和误差要在ADC的1个LSB之内。

根据这个目的,可以需要选择指标合适的运放。

至于多路ADC同步的问题,一般在高速ADC的数据手册中都会有一章来介绍多片同步问题,你可以看一下里面的介绍。

2.在挑选ADC时如何确定内部噪声这个参数?一般ADC都有信噪比SNR或者信纳比SINAD这个参数,SINAD=6.02*有效位数+1.76,您可以根据这个公式来确定您选择的ADC能否符合您的要求.3.如何对流水线结构ADC进行校准?需要校准哪些参数?一般来讲,ADC的offset和gain error会比较容易校准。

只要外接0V和full scale进行采样,然后得到校准系数。

另外,如果需要作温度补偿的话,一般需要加一个温度传感器,然后利用查表的方式来补偿。

4.对ADC和DAC周围的布线有哪些建议?ADC和DAC属于模拟数字混合型器件,在布局布线时最重要的是要注意地分割,即模拟地和数字地的处理问题。

对于高采样率的器件,建议使用一块地。

而低采样率的器件,建议模拟数字地分开,最后在芯片下方连接在一起。

其他的布局布线规范与其他器件的是一样的。

对于具体的器件,一般会有评估板的Layout图可供参考。

5.模数转换器的精度与噪声系数之间有什么必然的联系吗?低速模数转换器的精度用峰峰值分辨率,有效值分辨率来表示。

在ADI一些Sigma-delta ADC的芯片资料里都会列出不同情况下的有效值分辨率指标。

高速模数转换器的精度可用SNR,SNOB来表示,这些指标也可在资料中找到。

但一般ADC的指标中不会有噪声系数(NF)的指标。

6.如果采用了外部模拟切换开关,那么这个开关总是存在一些电阻的,必然引起一些误差,那么我想问一下有没有什么办法能减少这些误差,分别描述一下用硬件的方法与用软件的方法。

基于fpga的ad9268的并口读数据的代码

基于fpga的ad9268的并口读数据的代码1. 引言1.1 概述本文基于FPGA设计了一种并口读取数据的方案,该方案可以与AD9268芯片实现接口通信。

通过该方案,我们可以在FPGA平台上高效地读取AD9268芯片采集的数据。

1.2 文章结构本文共分为五个部分进行阐述。

首先,引言部分将介绍文章的背景和目的。

其次,AD9268简介部分将对AD9268芯片及其功能进行介绍,以及FPGA与AD9268之间接口通信的原理和并口读取数据的需求背景。

然后,在基于FPGA的AD9268并口读取数据设计方案中,将详细说明选择和搭建FPGA硬件平台、设计与实现AD9268数据读取流程、优化技术研究等内容。

随后,在实验与结果分析部分,将展示实验环境搭建与参数设置,并对AD9268并口读取数据性能测试结果进行详细分析,并评估优化方法对性能提升的影响。

最后,在结论与展望部分总结研究成果,并提出存在问题与改进方向以及未来发展趋势展望。

1.3 目的本文旨在针对AD9268芯片,并基于FPGA设计一种高效的并口读取数据的方案。

通过深入研究AD9268芯片的功能,对FPGA与AD9268之间的接口通信原理进行分析,并提出一种针对并口读取数据需求背景下的设计方案。

通过实验和结果分析,验证了该方案的可行性,并从优化方法的角度评估了其对性能提升的影响。

最后,总结研究成果,指出存在问题并提出改进方向,并展望了未来在该领域的发展趋势。

2. AD9268简介:2.1 AD9268芯片功能:AD9268是一款高性能、12位模数转换器(ADC)芯片,采用并行接口与FPGA 进行通信。

它具有较高的分辨率和采样速率,并且适用于广泛的模拟输入信号范围。

该芯片内置了功耗优化的电源管理电路,并提供了多种工作模式,以满足不同应用场景的需求。

2.2 FPGA与AD9268接口通信的原理:在FPGA与AD9268之间建立稳定可靠的通信通道是实现并口读取数据的关键。

基于FPGA的ADC时序设计

基于FPGA的ADC时序设计刘亚亚【摘要】随着机器视觉领域的快速发展,图像实时处理的需求越来越迫切,而软件实现图像处理无法满足实时性的需求,且基于专用集成芯片的实现开发周期过长,开发难度过大.针对此提出一种基于FPGA的ADC时序设计.该设计以现场可编程门阵列(FPGA)为核心,在ISE10.1和ModelSim仿真软件环境下开发,在Xilinx的XC4VSX55硬件平台上实现.最终搭建图像采集与处理系统的平台,很好地实现图像的实时与处理.【期刊名称】《现代计算机(专业版)》【年(卷),期】2016(000)027【总页数】4页(P46-49)【关键词】FPGA;ADC;图像采集;仿真【作者】刘亚亚【作者单位】商洛学院数学与计算机应用学院,商洛726000【正文语种】中文随着现代通信技术的发展,ADC信号的实时采样和有效处理在数字化接收机中起到重要作用[1],FPGA提供逻辑控制,虽然以传统的DSP或单片机作为CPU 的AD采样系统控制简单,但它们不适合完成对复杂的外围电路的逻辑控制,而且软件运行速度较低,而FPGA电路设计易于软件仿真,可同时进行采样控制和信号的处理[2],且能简化硬件电路,提高系统工作速度,缩短产品研发周期。

针对此,基于FPGA的ADC时序设计,能更有效地提高宽带数字化接收技术,更容易硬件实现。

同时该设计还具有比较好的通用性。

1.1 ADC128的时序信号ADC12要正常工作,必需获取好的时序驱动信号,而时序信号的产生需要各种频率的时钟,而系统时钟只有一个,因此,设计时钟产生功能是ADC128时序设计的基础。

该模块主要用来产生内部的全局清零信号和ADC128工作所需的时钟信号。

上电初始时刻需对FPGA进行清零,清除FPGA上电初始时刻的不稳定态以使FPGA避开外围电路的不稳定状态[3-4]。

接着产生系统需要的时钟信号,时钟产生模块(CLK_CTRL)接口框图如图1所示:FPGA工作时钟为40MHz时钟,全局异步上电复位信号和ADC128等各个模块所需的时钟信号如表1所示。

AD转换设计中的基本问题整理

AD转换设计中的基本问题整理1.如何选择高速模数转换之前的信号调理器件;如何解决多路模数转换的同步题目?ADC之前的信号调理,最根本的原则就是信号调理引起的噪声和误差要在ADC的1个LSB之内。

根据这个目的,可以需要选择指标合适的运放。

至于多路ADC同步的题目,一般在高速ADC的数据手册中都会有一章来先容多片同步题目,你可以看一下里面的先容。

2.在挑选ADC时如何确定内部噪声这个参数?一般ADC都有信噪比SNR或者信纳比SINAD这个参数,SINAD=6.02*有效位数+1.76,您可以根据专业这个公式来确定您选择的ADC能否符合您的要求.3.如何对流水线结构ADC进行校准?需要校准哪些参数?一般来讲,ADC的offset和gain error会比较轻易校准。

只要外接0V和full scale进行采样,然后得到校准系数。

另外,假如需要作温度补偿的话,一般需要加一个温度传感器,然后利用查表的方式来补偿。

4.对ADC和DAC四周的布线有哪些建议?ADC和DAC属于模拟数字混合型器件,在布局布线时最重要的是要留意地分割,即模拟地和数字地的处理题目。

对于高采样率的器件,建议使用一块地。

而低采样率的器件,建议模拟数字地分开,最后在芯片下方连接在一起。

其他的布局布线规范与其他器件的是一样的。

对于具体的器件,一般会有评估板的Layout图可供参考。

5.模数转换器的精度与噪声系数之间有什么必然的联系吗?低速模数转换器的精度用峰峰值分辨率,有效值分辨率来表示。

在ADI一些Sigma-delta ADC的芯片资料里都会列出不同情况下的有效值分辨率指标。

高速模数转换器的精度可用SNR,SNOB来表示,这些指标也可在资料中找到。

但一般ADC的指标中不会有噪声系数(NF)的指标。

6.假如采用了外部模拟切换开关,那么这个开关总是存在一些电阻的,必然引起一些误差,那么我想问一下有没有什么办法能减少这些误差,分别描述一下用硬件的方法与用软件的方法。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

FPGA中的AD转换与显示接口电路设计

【摘要】ad转换中的数据采集和显示是生产过程或科学实验中各种物理量进行实时采集、测试的经常需要解决的问题。

可编程逻辑芯片具有高集成度、高可靠性、高速度的特点。

论文运用vhdl

硬件编程语言,通过两段式状态机设计程序,完成常见的ad0809

芯片与可编程逻辑芯片的联接。

将ad转换结果以bcd码形式通过fpga芯片进行显示,实时观测转换进程,给出了bcd码转换流程图,完成相应电路设计,通过quartusii软件进行了仿真,并在开发系统上成功实现功能验证。

【关键词】fpga;ad转换;bcd码显示;接口电路

fpga是大规模可编程器件。

它是利用eda技术进行电子系统设计的载体;硬件描述语言是eda技术进行电子系统设计的主要表达手段,vhdl语言是常用的硬件描述语言之一;软件开发工具quartus ⅱ。

fpga以高速、高可靠性、串并行工作方式等特点在电子设计中广泛应用。

它打破了软硬件之间的界限,加速了产品的开发过程。

1.硬件电路构成

用一片mcs-51芯片、一片fpga芯片、模数转换器adc0809和数模转换器dac0832构成一个数据采集系统,并用fpga实现数据采样、d/a转换输出、有关数据显示的控制、键盘电路。

单片机完成对a/d转换数据运算。

系统的组成框图如图1所示,其功能如下:(1)系统按一定速率采集输入电压ui,经ad0809转换为8位数字量data。

(2)输入数据与通过cpld/fpga采样后输入单片机进行相关运算,最后通过fpga送至dac0832转换为δu。

(3)数据采集和处理均在数据采集系统控制器的管理下有序进行。

工作速率由时钟信号clk的速率决定。

2.ad0809与cpld/fpga接口设计

adc0809在转换开始前由地址锁存允许信号ale 将3 位地址锁入锁存器中以确定转换信号通道。

eoc 为转换结束状态信号,由低电平转为高电平时指示转换结束,此时可读入转换好的8 位数据。

eoc 在低电平时指示正在进行转换。

start 为转换启动信号,上升沿启动。

oe 为数据输出允许高电平有效。

clk 为adc 转换时钟输入端口500khz 左右。

为了达到a/d 器件的最高转换速度,a/d 转换控制器必须包含监测eoc 信号的逻辑,一旦eoc 从低电平变为高电平即可将oe 置为高电平然后传送或显示已转换好的数据

[d0..d7]。

图1所示为ad0809引脚图;图2所示为ad0809时序电路,根据时序电路图通过两段式状态机设计程序完成与cpld/fpga 芯片的连接。

图4为状态机程序仿真结果,表1所示为状态机功能与相应引脚的取值。

表1 ad转换状态机描述

状态实现功能引脚

s0 初始状态,选择1通道模拟信号输入 addc=‘1’,

ale=start=oe=lock=‘0’

s1 通道锁存 ale=‘1’, start=oe=lock=‘0’

s2 启动a/d转换ale=‘1’, start=‘1’,oe=lock=‘0’s3 a/d转换等待状态ale=start=‘0’,oe=lock=‘0’;

if eoc=‘0’保持当前状态不变,继续等待a/d转换。

else 转换结束,进入下一状态

s4 数据输出允许状态a/d转换完毕,开启数据输出允许信号。

ale=‘0’, start=‘0’,oe=‘1’,lock=‘0’

s5 数据锁存状态开启数据锁存信号,将转换结果送锁存器锁存;ale=‘0’, start=‘0’,oe=‘1’,lock=‘1’

s6 延时状态为了保证数据可靠锁存,延时一个时钟状态周期;ale=‘0’, start=‘0’,oe=‘1’,lock=‘1’

其它状态返回到初始状态 ale=start=oe=lock=‘0’

图1 ad0809引脚图图2 ad0809时序图3.bcd码转换电路设计

找到adc0809的基准电压(vref)为5.12 v时,模拟输入电压与输出电压的对应关系,其中最小电压准位是5.12/28=0.2 v。

这样,当由adc0809的d[7..0]收到的数据信号是10000110(即86h)时,高4位1000是2.56 v,而低4位0110是0.12 v,所以最后的电压输出结果是2.56 v+0.12 v=2.68 v。

为了方便后续的电压数据显示,我们应将输出电压表示成12位的bcd码形式。

将d(7..4)转换为对应的12位bcd码h(11..0);将d(3..0)转换为对应的12位bcd码l(11..0)。

如上述的2.56 v是0010 0101 0110,0.12 v是0000 0001 0010,所以相加的结果2.68 v是0010 0110 1000,

因此必须设计一个12位的bcd码加法程序。

二进制bcd码相加时,由最低4位加起,且每4位相加的结果超过1001时,应加0110调整。

bcd码程序转换流程如图3所示。

图3 bcd码转换仿真波形

4.系统电路仿真

ad转换电路与bcd码转换电路构成系统,将ad转换程序和bcd 码程序组合成一个整体程序,通过quartus ii软件生成系统图,如图4所示。

ad转换结果由三位十进制数表示,每位十进制数由四位bcd码表示,总共有12位bcd码输出。

将电路输出bcdout (11..0)分成bcdout(11..8)、bcdout(7..4)和bcdout(3..0)三部分,通过三个进程process分别用vhdl语言编程实现led显示驱动。

对整个系统进行波形仿真,得到仿真波形如图5所示,最后在gw48-ck实训开发系统完成功能验证。

图4系统电路图

图5 系统仿真结果

参考文献:

[1] 潘松、王国栋. vhdl实用教程[m]:成都:电子科技大学出版社2001:334-344.

[2] 王建校.张虹,金印彬.电子系统设计与实践【m].北京:高等教育出版社,2008. [2].

[3] 林敏.vhdl数字系统设计与高层次综合[m].北京:电子工业出版社,2001.

[4] 路而红等编著电子设计自动化应用技术[m].北京:北京希望:高等教育出版社.。