VC5402芯片AD和DA转换接口的设计

TMS320VC5402DSP与串行AD73360AD转换器接口设计(精)

TMS320VC5402 DSP与串行AD73360A/D转换器接口设计摘要:讨论了TI公司的数字信号处理器TMS320VC5402的多通道缓冲串口与串行A/D变换器AD73360的接口设计,详细阐述了两者的硬件接口和软件实现。

关键词:多通道缓冲串口TMS320VC5402DSPAD73360A/D转换器随着对信号处理要求的不断提高以及DSP技术的不断发展,越来越多的工程技术人员开始采用DSP进行系统设计。

美国TI公司的TMS320VC5402(以下简称VC5402)DSP具有运算速度快、功耗小和性价比高的特点,已在个人移动通信、信号与信息处理以及自动控制等领域得到了广泛的应用。

该芯片提供了两个多通道缓冲串行接口(McBSP)与外部设备进行通信。

它与串行A/D变换器构成的信号采集与处理系统具有硬件设计简单、可靠性好的特点。

本文将详细阐述VC5402与AD73360的接口设计。

1VC5402的McBSPVC5402的McBSP是一种同步串行接口,支持多种通信方式和SPI协议,该串口可以根据设计者的不同需求进行配置,使用非常灵活。

它的主要特点如下:全双工的串行通信;连续的发送和接收数据流功能;具有外部时钟输入或内部可编程时钟两种时钟控制方式;可独立编程的发送和接收帧同步;多通道数据传输(最多可达128个通道);可选的数据宽度:8、12、16、20、24或32位;用于数据压缩的μ律和A律压缩扩展;可编程的时钟和帧同步极性。

McBSP包括6个引脚,分别是串行数据发送信号DX、串行数据接收信号DR、发送时钟信号CLKX、接收时钟信号CLKR、发送帧同步信号FSX和接收帧同步信号FSR。

由于McBSP内带有一个可编程的采样和帧同步时钟产生器,所以串口接收、发送时钟和帧同步等信号既可由内部产生,也可以由外部输入。

VC5402的McBSP由23个寄存器进行控制,除了少数几个不能由程序访问之外,一般在串口进行数据通信之前都要对它们进行初始化,部分寄存器是存储器映射寄存器,必须通过子地址的方式进行访问。

TMS320C5402与TLC320AD50C的接口设计

TMS320C5402与TLC320AD50C的接口设计芯片接口设计是一种基于芯片的设备及其电路的连接方式。

在芯片接

口设计中,相关接口被设计成标准的接口,使其可以被多种不同的芯片所

使用。

TMS320C5402与TLC320AD50C是一种典型的芯片接口。

TMS320C5402是一款高性能的DSP芯片,它拥有32位元的指令体系

结构,能够提供强大的计算能力和高效的运算速度。

TMS320C5402具有可

编程的芯片外围电路,可以根据用户的需求进行定制以满足特定应用场景

的要求。

另外,TMS320C5402也提供多种接口,如分立元件接口

(Discrete I/O interface)、RJ45接口(RJ45 interface) 、串口接口(Serial Interface) 、总线接口(Bus Interface)等。

TLC320AD50C是一款高性能的数字音频处理IC。

其内部具有2路数字

音频处理器,各路数字音频处理能力可以达到32位96KHZ的水平,可以

满足用户对数字音频处理高要求的应用。

此外,TLC320AD50C既具有多种

主要32位、24位、16位的数据接口,如I2S、I2C、I2L、SPI等,也具

有可选的数字接口,如TDM、S/PDIF、EIAJ、SCMS等。

因此,为了使TMS320C5402与TLC320AD50C之间的接口更加简洁高效,我们可以采用I2C接口设计。

I2C接口也被称为串行总线接口,是一种可

以在多个芯片之间传递信息的串行接口,具有高带宽、低成本、低电压电

平等特点,适用于多种多台设备的集成。

首先。

TMS320VC5402串行通信接口设计

不可少 。目前 几乎所 有 的 D P都 提供 一个 或多个 串 口, S 然 而, 多数 D P芯 片 提 供 的是 同步 串 口, 实 际 的应 用 中 , S 在

D P要 能够与 外设进 行 异步 串 行 通信 , 与 P S 如 C机进 行 串

Mc S B P串 口工作 于时钟停 止模 式 时与 S I 议兼 容 。 P协 此时, 发送 器 和 接 收 器 在 内 部 得 到 同步 , B P可 作 为 Mc S SI P 的主设 备 或 从 设备 。发 送 时 钟 信 号 ( CL B Kx) 应 于 对 SI P 协议 中 的串行 时 钟 信号 ( C , 送 帧 同步 信 号 对 应 S K) 发 于 从设备 使能 信号 ( C ) / S 。在这 种方 式下 对 接收 时钟 信 号

摘 要 :介 绍 了 TMS 2 C 4 2Mc S 的结 构 及 主 要 特 点 , 出 了通 过 Mc S 30 5 0 B P 给 B P扩 展 成 S I 口与 P P串 C机 及 AT 9 5 8S 1

TMS320VC5402与串行ADDA转换器的接口设计

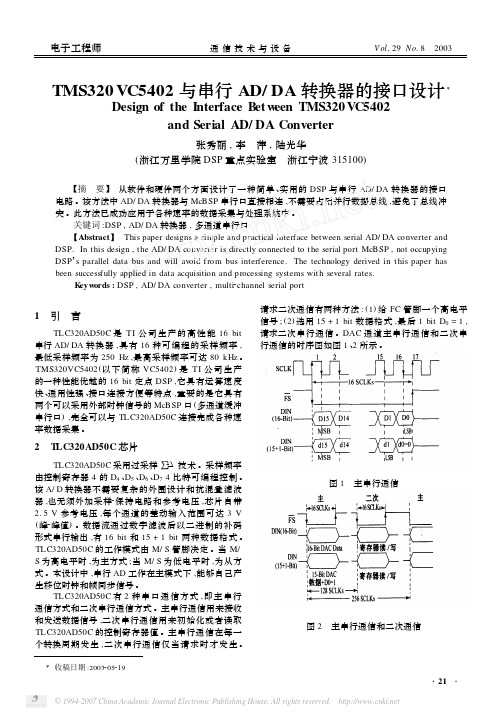

TMS320VC5402与串行AD/DA转换器的接口设计ΞDesign of the Interface B et w een TMS320VC5402and Serial AD/DA Converter张秀丽,李 萍,陆光华(浙江万里学院DSP重点实验室 浙江宁波315100)【摘 要】 从软件和硬件两个方面设计了一种简单、实用的DSP与串行AD/DA转换器的接口电路。

该方法中AD/DA转换器与McBSP串行口直接相连,不需要占用并行数据总线,避免了总线冲突。

此方法已成功应用于各种速率的数据采集与处理系统中。

关键词:DSP,AD/DA转换器,多通道串行口【Abstract】 This paper designs a simple and practical interface between serial AD/DA converter and DSP.In this design,the AD/DA converter is directly connected to the serial port McBSP,not occupying DSP’s parallel data bus and will avoid from bus interference.The technology derived in this paper has been successfully applied in data acquisition and processing systems with several rates.K eyw ords:DSP,AD/DA converter,multi2channel serial port1 引 言TLC320AD50C是TI公司生产的高性能16bit串行AD/DA转换器,具有16种可编程的采样频率,最低采样频率为250Hz,最高采样频率可达80kHz。

TMS320VC5402(以下简称VC5402)是TI公司生产的一种性能优越的16bit定点DSP,它具有运算速度快、通用性强、接口连接方便等特点,重要的是它具有两个可以采用外部时钟信号的McBSP口(多通道缓冲串行口),完全可以与TLC320AD50C连接完成各种速率数据采集。

TMS320VC5402与模拟芯片TLC320AD50C接口设计

TMS320VC5402与模拟芯片TLC320AD50C接口设计目前进展起来的高速数字信号处理器在语音处理系统中得到了广泛应用。

TMS320VC5402是TI公司生产的一种性能价格比较高的16位定点DSP。

它的命令周期为10ns,具有运算速度快、通用性强、接口衔接便利等特点,尤其适合在语音编码和通信中应用。

TLC320AD50C是TI公司生产的Σ-Δ型A/D、D/A音频接口芯片,为V3.4调制解调器以及音频应用提供了通用的模拟接口,可以挺直与TMS320VC5402相连。

本文具体介绍TLC320AD50C与TMS320VC5402的硬件接口衔接和软件设计。

1 TMS320VC5402的McBSPTMS320VC5402有两个McBSP多通道缓存串行口。

McBSP提供了全双工的通信机制,以及双缓存的发送寄存器和三缓存的接收寄存器,允许延续的数据流传输,数据长度可以为8、12、16、20、24、32;同时还提供了A-律和μ-律压扩,多达128个通道的发送和接收。

McBSP通过7个引脚使得一个数据通路和一个控制通路与外部设备相连。

数据经McBSP与外设的通信通过DR和DX引脚传输,控制信号则由CLKX、CLKR、FSX、FSR等四条引脚来实现。

CPU和DMA控制器可以读取DRR?1,2?的数据实现接收,并且可以对DXR?1,2?写入数据实现发送。

接收和发送帧同步脉冲既可以由内部采样速率产生器产生,也可以由外部脉冲源驱动。

当FSR和FSX都为输入时FSXM=FSRM=0,外部脉冲源驱动,McBSP分离在CLKR和CLKX的下降沿检测,且DR的数据也在CLKR 的下降沿举行采样。

而当FSR和FSX都为输出时,则在CLKX和CLKR 的升高沿举行检测。

16-bit的串行口控制寄存器SPCR?1,2?和引脚控制寄存器PCR用来配置串行口;接收控制寄存器RCR?1,2?和发送控制寄存器XCR?1,2?分离设置接收和发送的不同参数,如帧长度、每帧的数据长度等。

VC5402与外部存储器的接口设计

VC5402与外部存储器的接口设计作为DSP 芯片与外界交换数据的重要关口,外扩存储器存储器接口接口的优劣程度直接影响着DSP 的适应性和控制功能,同时,高性能、灵活性强的外部存储器接口也是利用DSP 搭建图像采集处理系统的重要保证。

基于上述原因,本文提出了一种基于CPLD 的VC5402VC5402 存储器扩展方案,此方法具有接口灵活、调试方便的优点。

图像采集处理系统中资源的配置情况为了更方便地了解VC5402 与外部存储器的接口设计,本文首先介绍在设计的图像采集处理系统中VC5402的资源配置状况。

VC5402 有3 个比特位(MP/ MC # ,OVL Y,DROM)共同影响着存储器的结构,用户可以根据需要修改PMST的值来配置存储空间。

本文采用了微处理器模式,设置MP/ MC # = 1 ,片上4 k 字的ROM 不映射到程序区,即ROM 不可访问。

设置OVL Y= 0 ,片内16 k 字的RAM 不映射到程序存储器,使64 k 字的程序存储空间全部配置成外部存储器,利用2 片SRAM(记为SRAM1 ,SRAM2) 存放采集到的图像数据。

DSP 每执行一次复位,都将DROM 清零,在系统中没有改变该比特位的设置, 这样使得数据存储空间的低48 k 字全都对应外部存储器,其中低32 k 字空间映射为外挂FLASH ,用来存放引导程序、中断矢量表和用户代码等内容,其他16 k 字的空间映射为SRAM(记为SRAM3)用来存放数据处理的结果。

对于扩展程序存储空间、扩展数据存储空间所需要的时延可以通过软件编程的方法对DSP 的等待状态寄存器(SWWSR) 进行设置,使之达到最快速度。

这样就避免了使用硬件进行握手通信,简化了接口的设计。

程序存储器的扩展系统中实际采集到的图像数据量大约有1 M ×8 b ,而VC5402 的数据空间只有64 k 字,并且VC5402 内部具有16 k 字的随机存储器和4 k 字的只读存储器,远远不能满足存储要求,因此需要将数据空间扩展到1 MB才能实现图像数据的存储。

数字信号处理芯片TMS320VC5402的语音接口设计

计 算 4 累加 器中数值 的指 数 . 0位 片外可 寻址空 间达到 1M×1 i 片内有 4K×1 i的 R M和 l K×1 i 6bt . 6b t O 6 6bt

的 R M. A 附加 的片 内外设 包括 软件可 编程 等待状 态产生 器 、 可编 程的块交 换 、 内锁 相环 时钟 发生器 、 片 2个 1 6

处理 研 究 ;

崔光照 ( 5 ) 男, 南省 洛 宁县 人 . 1卜 , 河 9 郑州轻 工业 学院教授 , 主要 从事 电器控 制厦 其 可 靠性技 术的 开发 与研究 .

维普资讯

郑 州 轻 工 业 学 院 学 报 c自 然 科 学 版

20 02正

M B P 由分离 的发送 和 接收 通 道组 成 , cS s 每个

M BP 的外部 接 口由 以下 管 脚组 成 : 送参 考 时 cSs 发

钟 B L X, 送数据 B X, 送 帧 同步 B S 接 收 CK 发 D 发 F X, 参考 时 钟 B L R, 收 数 据 B R, 收 帧0 C 4 2芯 片介 绍 MS 2 v 5 o

T 3 0 C 42芯 片是 l 位 定点 D P 采 用增强 的改进 哈 佛结构 , MS2 V 50 6 S, 具有 1 程序 总线 和 3组数 据总线 . 组 4 0 位 的算术 逻辑单元 包括 1 4 个 0位 的桶型移 位 器和 2个 独 立 的 4 0位 累加 器 , 其指 数 编 码器 可 以在单 周 期 内

T S 2 V 50 M 30 C 4 2是 1 公 司推 出的一 款性 价 比很 高 的 l 位 定 点 D P 它具 有 1 8的指令 周 期 、0 IS的运 1 6 S, 0n 10M P 算能力 , 其 适用 于通 信 和语 音处 理 . 开 发语 音 处 理 系统 时 , 会 遇 到语 音 A D, / 尤 在 常 / D A转 换 接 口的 问题 , T C 2 A 5 C是 1 公 司生产 的 一种 A D, / L 30 D 0 1 / D A模 拟 接 口芯 片 , 文 拟介 绍 T C 2 A 5 C与 T 3 0 C 42 本 L 30 D 0 MS2 V 50 的接 口设计方 法 .

片机AD及DA转换接口

数字滤波,就是通过程序对采样信号进行平滑加工,以 提高其有用信号,消除或抑制干扰信号。有多种数字滤波程 序,例如,程序判断滤波程序、中值滤波程序、算术平均滤 波程序、加权平均滤波程序、一阶滞后滤波程序以及复合滤 波程序等。

与模拟滤波相比,数字滤波具有众多优点,所以在现代

测控系统中广泛使用数字滤波。数字滤波不但不需要硬件设

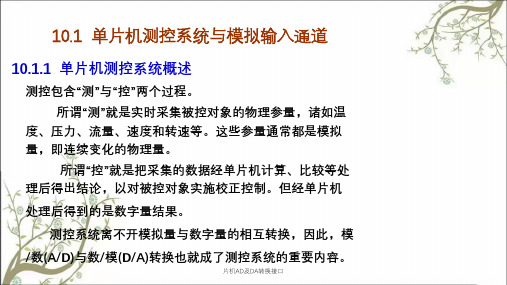

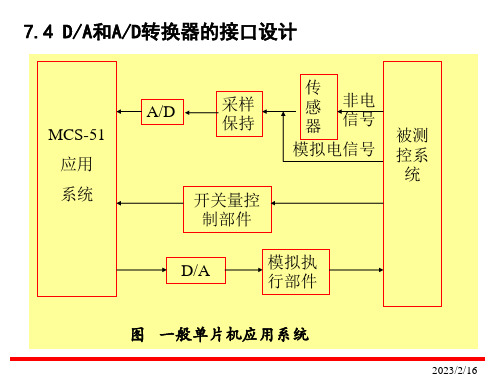

测控系统离不开模拟量与数字量的相互转换,因此,模 /数(A/D)与数/模(D/A)转换也就成了测控系统的重要内容。

片机AD及DA转换接口

10.1.2 模拟输入通道

模拟输入通道的工作从采集信号开始。由于传感器采 集到的模拟信号幅值通常很小,而且连续变化的信号容易受 到干扰,因此,要对传感器采集到的原始信号进行放大、采 样、保持、滤波等处理后,才能送给A/D转换器。这一系列 的处理过程构成了模拟输入通道,如下图。

模拟信号的分时采集,片内有8路模拟选通开关,以及相 应的通道地址锁存与译码电路,转换时间为100 μs左右。 ADC0809的内部逻辑结构如下图所示。

片机AD及DA转换接口

图中多路开关可选通8个模拟通道,允许8路模拟量分 时输入,共用一个A/D转换芯片进行转换。地址锁存与译码 电路完成对A、B、C 3个地址位进行锁存和译码,其译码输 出用于通道选择。8位A/D转换器是逐次逼近式。输出锁存 器用于存放和输出转换得到的数字量。

片机AD及DA转换接口

2、信号引脚 ADC 0809转换器芯片为28引脚,双列直插式(DIP)封装。

1

IN 3

IN 2

28

2 3

IN 4 IN 5

A D C 0809 IN 1 IN 0

27 26

4

IN 6

ADDA

25

单片机原理及应用—DA和AD转换器的接口设计

START: LOOP:

周期

ORG 2000H

MOV R0,#0FEH

MOV A,#data1 MOVX @R0,A ;置矩形波上限电平 LCALL DELAY1 ;调用高电平延时程序 MOV A,#data2

MOVX @R0,A ;置矩形波下限电平

LCALL DELAY2 ;调用低电平延时程序

返 2023/2/16 回

表7-3 ADC0809通道选择表

图7-21 ADC0809的引脚图

返 2023/2/16 回

2. MCS-51单片机与ADC0809的接口

返 2023/2/16 回

3. A/D转换应用举例

• 设有一个8路模拟量输入的巡迥检测系统,使 用中断方式采样数据,并依次存放在外部 RAM的A0H~A7H单元中。采集完一遍以后 即停止采集。其数据采样的初始化程序和中 断服务程序如下:

返 2023/2/16 回

DAC0832的逻辑结构:

返 回

2023/2/16

返 回

2023/2/16

2023/2/16

(两级锁存方式)

2023/2/16

两级锁存方式,故程序中需要两条传送指令才能完成 一个数字量的模拟转换。 如:输入寄存器的地址为FEFFH,DAC寄存器的地址为 FDFFH,则完成一次D/A转换的程序为: MOV A, #DATA MOV DPTR, #0FEFFH MOVX @DPTR, A MOV DPTR, #0FDFFH MOVX @DPTR, A

SJMP LOOP

;重复进行下一个

返 回

2023/2/16

DAC0832 的应用举例

请设计一8031与DAC0832的接口电路,工作于单缓冲方

dsp课程设计(TMS320VC5402 最小系统 存储器扩展设计)

摘要我为我问问我问问问问我我问问问问问我我问一个完整的DSP系统通常是由DSP芯片和其他相应的外围器件构成。

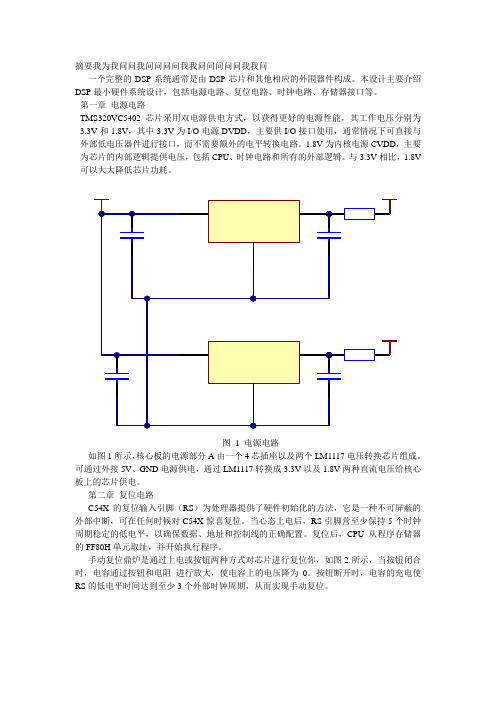

本设计主要介绍DSP最小硬件系统设计,包括电源电路、复位电路、时钟电路、存储器接口等。

第一章电源电路TMS320VC5402芯片采用双电源供电方式,以获得更好的电源性能,其工作电压分别为3.3V和1.8V,其中3.3V为I/O电源DVDD,主要供I/O接口使用,通常情况下可直接与外部低电压器件进行接口,而不需要额外的电平转换电路。

1.8V为内核电源CVDD,主要为芯片的内部逻辑提供电压,包括CPU、时钟电路和所有的外部逻辑。

与3.3V相比,1.8V 可以大大降低芯片功耗。

图 1 电源电路如图1所示,核心板的电源部分A由一个4芯插座以及两个LM1117电压转换芯片组成。

可通过外接5V、GND电源供电,通过LM1117转换成3.3V以及1.8V两种直流电压给核心板上的芯片供电。

第二章复位电路C54X的复位输入引脚(RS)为处理器提供了硬件初始化的方法,它是一种不可屏蔽的外部中断,可在任何时候对C54X惊喜复位。

当心态上电后,RS引脚营至少保持5个时钟周期稳定的低电平,以确保数据、地址和控制线的正确配置。

复位后,CPU从程序存储器的FF80H单元取址,并开始执行程序。

手动复位鼎炉是通过上电或按钮两种方式对芯片进行复位你,如图2所示,当按钮闭合时,电容通过按钮和电阻进行放大,使电容上的电压降为0。

按钮断开时,电容的充电使RS的低电平时间达到至少3个外部时钟周期,从而实现手动复位。

图2 复位电路第三章时钟电路时钟电路用来为TMS320VC5402芯片体制时钟信号,可以利用DSP芯片内部的振荡器构成时钟电路,连接方式如图3所示。

在芯片的X1和X2引脚之间介入夜歌晶体,用于启动内部振荡器。

图3 时钟电路第四章DSP芯片的存储器接口第一节内部存储器TMS320VC5402的芯片设计有丰富的内部快速存储器可以全速运行,达到芯片最高速度。

AD,DA转换接口电路设计

实验报告课程名称单片机原理与应用实验项目A/D、D/A转换接口设计实验仪器Keil 3系别专业班级/学号学生姓名实验日期成绩指导教师实验六 A/D、D/A转换接口设计一、实验目的1. 了解A/D、D/A转换的基本原理;2. 掌握A/D、D/A转换芯片性能及编程方法;3. 掌握单片机系统扩展A/D、D/A转换的基本方法。

二.实验内容1、设计DAC0832与ADC0809与单片机的接线。

2、利用DAC0832,编制程序产生锯齿波。

3、实验台上的电源和地提供模拟量输入,编制程序,利用ADC0809将模拟量转换成数字量,用发光二极管显示。

三、有关说明D/A转换是把数字信号转换成模拟量的变换,从D/A输出的是模拟电压信号。

产生锯齿波只需由A存放的数字量的增减来控制;A/D转换器大致有三类:一是双积分A/D转换器,优点是精度高,抗干扰性好,价格便宜,但速度慢;二是逐次逼近A/D转换器,精度、速度、价格适中;三是并行A/D转换器,速度快,价格也昂贵。

实验用的ADC0809属于第二类,是八位A/D转换器,每采集一次最长需100uS,A/D转换结束后会自动产生EOC信号,可以采用查询EOC信号方式,也可采用EOC中断方式来确定A/D转换是否结束,如果实时性要求不高也可采用软件延时,延时时间大于A/D转换器最长转换时间即可。

四.实验代码(1) D/A转换#include<reg51.h>#define unchar unsigned char#define unint unsigned intsbit A0=P2^0;sbit CS=P2^7;sbit wr=P2^6;void delayms(unchar time){unchar i,j;for(i=time;i--;i>0)for(j=110;j--;j>0);}void main(){unchar i;CS=0;wr=0;P0=0;i=0;while(1){i=i+5;A0=0;P0=i;A0=1;if(i==255)i=0;delayms(50);}}D/A转换效果图(2) A/D转换#include<reg51.h>#define unchar unsigned char #define unint unsigned int sbit wr = P2^0;sbit rd = P2^1;sbit cs = P2^2;void start(){cs=0;wr=0;wr=1;}void delayus(unchar time) {unchar i;for(i=100;i>0;i--);}void main(){while(1){start();delayus();rd=1;rd=0;}}。

TMS320VC5402最小系统原理图设计

TMS320VC5402最小系统原理图设计第一篇:TMS320VC5402最小系统原理图设计TMS320VC5402最小系统原理图设计1.DSP简介1.1 DSP 的应用领域在近20 多年时间里,DSP 芯片的应用已经从军事、航空航天领域扩大到信号处理、通信、雷达、消费等许多领域。

主要应用有信号处理、通信、语音、图形、图像、军事、仪器仪表、自动控制、医疗、家用电器等。

DSP 主要应用市场为3C 领域,占整个市场需求的 90%。

数字蜂窝电话是DSP最为重要的应用领域之一。

由于DSP 具有强大的计算能力,使得移动通信的蜂窝电话重新崛起,并创造了一批诸如GSM、CDMA 等全数字蜂窝电话网。

在Modem 器件中,DSP 更是成效卓著,不仅大幅度提高了传输速率,且具有接收动态图像能力。

另外,可编程多媒体 DSP 是 PC 领域的主流产品。

以XDSL Modem为代表的高速通信技术与MPEG 图像技术相结合,使得高品位的音频和视频形式的计算机数据有可能实现实时交换。

目前的硬盘空间相当大,这主要得益于CDSP(可定制DSP)的巨大作用。

预计在今后的PC 机中,一个 DSP 即可完成全部所需的多媒体处理功能。

DSP 也是消费类电子产品中的关键器件。

由于DSP的广泛应用,数字音响设备的更新换代周期变得非常短暂。

用于图像处理的DSP,一种用于JPEG 标准的静态图像数据处理;另一种用于动态图像数据处理。

1.2 DSP的特点DSP 芯片是模拟信号变换成数字信号以后进行高速实时处理的专用微处理器,其处理速度比最快的 CPU 还快 10-50 倍,具有处理速度高、功能强、性能价格比好以及速度功耗比高等特点,被广泛应用于具有实时处理要求的场合。

DSP 系统以DSP 芯片为基础,具有以下优点。

1.高速性,DSP 运行速度高达 1000MIPS 以上2.编程方便,可编程DSP 可使设计人员在开发过程中灵活方便的对软件进行修改和升级。

TMS320VC5402主机接口引导方案的设计2

TMS320VC5402主机接口引导方案的设计2摘要利用 TI公司生产的 DSP芯片TMS320VC5402 (简称 C5402)所提供的 HPI接口及其功能 ,提出了一种从PC直接将 DSP引导程序下载到DSP芯片的RAM中的方法。

本文还描述了HPI接口的工作原理及C5402的HPI引导方案的接口电路设计 ,给出了 HPI接口的软件设计。

其中 ,只需要在 PC机端对下载程序代码进行一些处理就可以省掉 DSP 下载仿真器以及 DSP芯片的外围下载辅助电路 ,从而只使用了 DSP中的 RAM,提高了处理速度 ,大大地减少了硬件设计的复杂度和开销。

关键词 : TMS320VC5402 HPI 引导程序目录摘要............................................ I 1 TMS320VC5402简介.. (1)1.1 芯片介绍 (1)1.2 几种引导装载方法 (3)2 C5402主机接口的解决方案 (4)3 硬件电路设计 (5)4 TMS320C54x的HPI引导模式的实现 (6)4.1 创建启动代码 (6)4.2 主机对HPI接口的操作 (8)4.3 主机通过HPI引导程序到目标DSP (8)4.4 目标DSP开始执行所下载的代码 (9)4.5 用户初始化程序 (10)5 课程设计体会 (13)参考文献 (14)1 TMS320VC5402简介1.1 芯片介绍TMS320VC5402(以下简称C5402)是德州仪器公司(TI)1999年10月推出的性价比极高(目标价格仅为5美元)的定点数字信号处理器(DSP)。

C5402主要特点如下[1]:·操作速率达100MIPS;·具有先进的多总线结构,三条16位数据存储器总线和一条程序存储器总线;·40位算术逻辑单元(ALU),包括一个40位桶形移位器和两个40位累加器;·一个17×17乘法器和一个40位专用加法器,允许16位带/不带符号的乘法;·整合维特比加速器,用于提高维特比编译码的速度;·单周期正规化及指数译码;·8个辅助寄存器及一个软件栈,允许使用业界最先进的定点DSP C 语言编译器;·数据/程序寻址空间1M×16b it,内置4K×16bit ROM和16K×16bit RAM;·内置可编程等待状态发生器、锁相环(PLL)时钟产生器、两个多通道缓冲串行口、一个8位并行与外部处理器通信的HPI口、2个16位定时器以及6通道DMA控制器;·低功耗,工作电源有3V和1.8V(内核),特别适合电池供电设备。

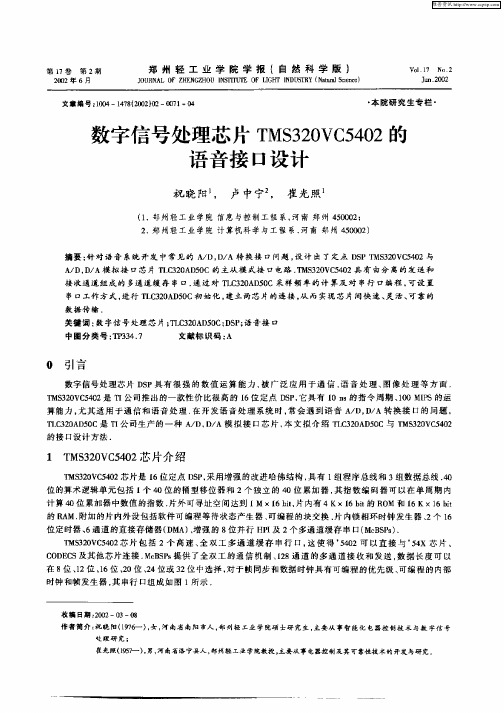

数字信号处理芯片TMS320VC5402的语音接口设计

数字信号处理芯片TMS320VC5402的语音接口设计

祝晓阳;卢中宁;崔光照

【期刊名称】《郑州轻工业学院学报(自然科学版)》

【年(卷),期】2002(017)002

【摘要】针对语音系统开发中常见的A/D,D/A转换接口问题,设计出了定点DSP TMS320VC5402与A/D,D/A模拟接口芯片TLC320AD50C的主从模式接口电路.TMS320VC5402具有由分离的发送和接收通道组成的多通道缓存串口.通过对TLC320AD50C采样频率的计算及对串行口编程,可设置串口工作方式,进行

TLC320AD50C初始化,建立两芯片的连接,从而实现芯片间快速、灵活、可靠的数据传输.

【总页数】4页(P71-74)

【作者】祝晓阳;卢中宁;崔光照

【作者单位】郑州轻工业学院,信息与控制工程系,河南,郑州,450002;郑州轻工业学院,计算机科学与工程系,河南,郑州,450002;郑州轻工业学院,信息与控制工程系,河南,郑州,450002

【正文语种】中文

【中图分类】TP334.7

【相关文献】

1.DSP芯片TMS320VC5402与无线网卡的接口设计 [J], 黄孟波;张宇林

2.TMS320VC5402 DSP与ISD4004语音录放芯片的接口设计及其信息管理 [J],

陈斌;施克仁

3.数字信号处理芯片TMS320C3 1语音接口设计 [J], 高娜娜;焦永革;黄国策

4.高性能数字信号处理芯片TMS320VC5402在汽车防撞警示雷达中的应用 [J], 龙宪惠;刘炜

5.数字信号处理芯片的语音接口设计 [J], 胡春松;曾水平

因版权原因,仅展示原文概要,查看原文内容请购买。

TMS320VC5402与串行AD_DA转换器的接口设计

C"% & " D C H < + F H " 芯片

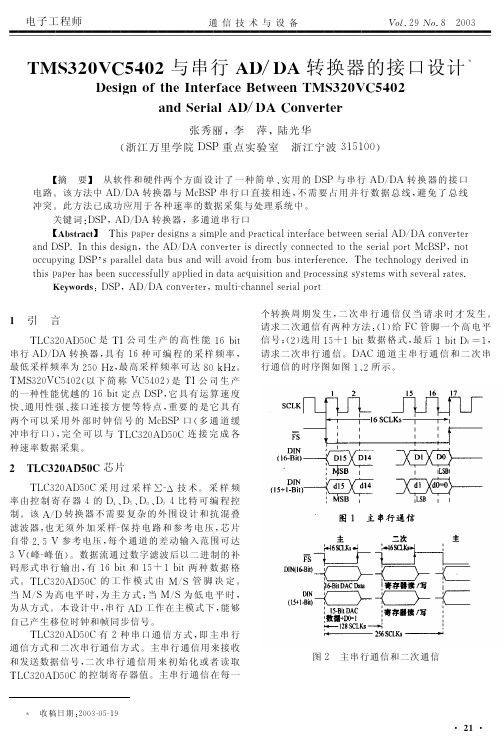

* + ’ % R # G H U # ’采用过采样 * ? # 技 术# 采 样 频 & & & 率由 控 制 寄 存 器 ! 的 H H H H ! U V $! 比特可编程控 制#该 G ! H 转换器 不 需 要 复 杂 的 外 围 设 计 和 抗 混 叠 滤波器 " 也无须 外 加 采 样 保 持 电 路 和 参 考 电 压" 芯片 ? 自带 RF 每个 通 道 的 差 动 输 入 范 围 可 达 U ^ 参考电压 " 峰 峰值 % # 数据流通过数字滤波后以二 进 制 的 补 %^$ ? 码形式串行 输 出 " 有" V; , 8和 " Ua"; , 8两 种 数 据 格 式 #* ! + ’ % R # G H U # ’ 的工作模式由 W Y 管 脚 决 定# 当W ! 为 主 方 式’ 当W ! Y 为高电平 时 " Y 为 低 电 平 时" 为从方式 # 本设计中 " 串行 G 能够 H 工作在主模式下 " 自己产生移位时钟和帧同步信号 # 即主串行 * + ’ % R # G H U # ’ 有 R 种 串 口 通 信 方 式" 通信方式和二次串行通信方式 # 主串行通信用来接收 和发送数据信号 " 二次串行通信用来初始化或者读取 * + ’ % R # G H U # ’ 的控制寄存器值 # 主 串 行 通 信 在 每 一

个转换周 期 发 生 " 二 次 串 行 通 信 仅 当 请 求 时 才 发 生# 请求二次通信有两种方法 ( $ 给N "% ’ 管脚一个 高 电 平 信号 ’ $ % 选用 数 据 格 式 " 最 后 "; " R " Ua"; , 8 , 8H # ]" 请求二次串行 通 信 #H G ’ 通道主串行通信和二次串 行通信的时序图如图 "& R 所示 #

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

目录1 概述 (1)2 芯片介绍 (2)2.1 TMS320VC5402 串口简介 (2)2.2 TLC320AD50C 简介 (2)2.3 TLC320AD50C功能介绍 (3)2.4 AD50的内部结构简图 (3)3 硬件电路设计 (4)3.1整体系统框图设计 (4)3.2 电源模块和复位模块 (5)3.3 时钟模块 (6)3.4 TLC320AD590C与TMS320VC5402接口电路 (6)3.5 TMS320VC5402的存储空间扩展 (7)4 系统软件设计 (8)4.1 AD50的控制时序 (9)4.2 程序流程图 (11)4.3 部分程序代码 (11)5 心得体会 (13)参考文献 (14)1 概述通常,一个典型的DSP系统应包括抗混叠滤波、数据采集A/D转换器、数字信号处理器DSP、D/A转换器和低通滤波器等,其组成框图如图1.1所示。

在许多应用系统中,为了应用DSP卓越的数字信号处理能力,我们必须先将模拟信号进行数字化(A/D转换),再对采样数据进行相应的算法处理,最后经过数字信号模拟化(D/A转换)后输出。

在这些DSP应用系统中的关键问题是怎样十分容易和高效地实现这些转换,因此必然涉及到接口电路的设计。

本文介绍一种单片内集成了ADC通道和DAC通道的模拟接口电路TLC320AD50C(以下简称AD50)与TMS320VC5402缓冲串口的接口的设计实现方法,然后,基于这种接口电路的硬件设计,通过软件编程实现信号的采集与回放。

图1-1 典型的DSP数据处理系统框图TMS320VC5402是TI公司生产的从属于TMS320C54x系列的一个工作灵活、高速、具有较高性价比、低功耗的16位定点通用DSP芯片。

其主要特点包括:采用改进的哈佛结构,1条程序总线(PB),3条数据总线(CB、DB、EB)和4条地址总线(PAB,CAB,DAB,EAB),带有专用硬件逻辑CPU,片内存储器,片内外围专用的指令集,专用的汇编语言工具等。

TMS320VC5402含4K字节的片内ROM和16K字节的双存取R AM,1个HPI (Host Port Interface)接口,2个多通道缓冲单口MCBSP(Multi-Channel Buffered Serial Port),单周期指令执行时间10ns,双电源(1.8V和3.3V)供电,带有符合IEEE1149.1标准的JTAG边界扫描仿真逻辑。

DSP(数字信号处理器)具有强大的数字信号处理能力,在其应用系统中,大多由ADC和DAC通道来完成对模拟信号的数字化处理。

设计了基于一种集成ADC和DAC 于一体的TLC320AD50C模拟接口电路与TMS320VC5402定点DSP接口电路的硬件设计方法,并结合硬件电路实现主从模式下软件的设计。

2 芯片介绍2.1 TMS320VC5402 串口简介McBSP提供了全双工的通信机制,以及双缓存的发送寄存器和三缓存的接收寄存器,允许连续的数据流传输,数据长度可以为8、12、16、20、24、32;同时还提供了A-律和μ-律压扩,多达128个通道的发送和接收。

McBSP串口由数据通道和控制通道组成,它通过7个管脚与外部设备相连,数据发送通过DX,数据接收通过DR,串行口的控制信息从CLKX、CLKR、FSX和FSR获得。

CLKS为外部时钟源。

CPU和DMA控制器通过内部外设总线对McBSP进行访问,从数据接收寄存器DRR[1,2]中读取数据,往数据发送寄存器DXR[1,2]写数据,数据从DR引脚进入DSP,首先存放在接收移位寄存器RSR[1,2]中,当一个完整的字接收完毕后,结果被复制到接收缓冲寄存器RBR[1,2],最后再由RBR[1,2]复制到DRR[1,2]中,供CPU或DMA控制器访问。

写操作与读取相仿,从结构上来看,发送和接收部分是相对独立的,所以可以实现全双工通信。

McBSP的控制设置通过一对寄存器读写来完成,这些控制寄存器控制的工作模式或指示串口的状态信息。

访问某个指定的寄存器时,首先要将相应的控制寄存器的子地址写入子地址控制器SPSA,SPSA驱动复接器,使之与数据控制寄存器SPSD相连。

接入相应子地址寄存器所在的实际物理存储位置,当向SPSD写入数据时,数据送入前面子地址寄存器所指定的内嵌数据存储器,当从SPSD读取数时,也接入所制定的内嵌数据存储器。

2.2 TLC320AD50C 简介美国TI公司的TLC320AD50C是一种具有许多优良特性的模拟接口电路芯片,AD50是TI公司生产的一个16位、音频范围(采样频率为2K~22.05KHZ)、内含抗混叠滤波器和重构滤波器的模拟接口芯片,它集成了16位A/D和D/A转换器,片内还包括一个定时器(调整采样率和帧同步延时)和控制器(调整编程放大增益,锁相环PLL,主从模式)。

2.3 TLC320AD50C功能介绍AD50有28脚的塑料SOP封装(带DW后缀)和48脚的塑料扁平封装(带PT后缀),体积较小,适应于便携设备。

AD50的工作温度范围是0~70℃,单一5V电源供电或5V 和3.3V联合供电,工作时的最大功耗为120 mW。

该芯片可广泛用于各种电路,尤其是应用在DSP领域中。

AD50芯片采用过采样 - 技术,可进行A/D和D/A的高分辨率、低速信号转换。

该器件同时还包括两个串行同步转换电路(用于各自的数据方向),在DAC 之前有一个内插滤波器,而在后面有一个抽取滤波器。

AD50中的可选项和电路配置可以通过串行口进行编程, AD50配置位可进行软件编程,该器件中共有七个数据和控制寄存器可供使用。

其用途如下:寄存器0:空操作(No-Op)寄存器。

寄存器1:Control1寄存器。

该寄存器用以控制软件复位、软件掉电、选择正常或辅助模拟输入、数字反馈的选择、DAC的16位或15位工作方式的选择、监视放大器输出增益的选择及硬件或软件二次通信请求方式的选择等。

寄存器2:Control 2寄存器,用于控制一个抽取FIR滤波器溢出的输出标志、FLAG 的输出值、ALT-DATA输入端使能、为ADC选择16位方式或15位方式及使能模拟反馈。

寄存器3:Control 3寄存器。

它控制FS与FSD之间延迟SCLK的个数;通知主器件有多少从器件将连在一起。

寄存器4:Control 4寄存器,用来控制输入输出放大器增益,采样率为fs=MCLK/(128 N)或MCLK/(512 N)的选择,以及在MCLK输入端使能外部采样时钟和旁路内部PLL等。

寄存器5和寄存器6:保留寄存器,用于工厂测试。

2.4 AD50的内部结构简图图2-1 首次通信与二次通信上图最上面第一通道为模拟信号输入监控通道,第二通道为模拟信号转化为数字信号(A/D)通道,第三通道为数字信号转化为模拟信号(D/A)通道,最下面一路是AD50的工作频率和采样频率控制通道。

本文所述的输入时钟(MCLK)为8.192MHz,A/D与D/A 的采样频率为MCLK/(128*N)Hz(N为AD50C的第4个寄存器4~6位所设)。

TLC320AD50C与 VC5402 串行通信可以分为首次通信和二次通信.在首次通信中,有两种数据传送模式,16位传送模式和 15 + 1 位传送模式,可通过控制寄存器设定.缺省却情况下为15+1位传送模式.若采用 15 + 1 位传送模式,其最低位D0为非数据位,输入DAC数据的D0位为二次通信请求位,输出ADC数据的D0 位为M/S脚的状态位.如果要对控制寄存器编程 ,必须申请二次通信.二次通信只有在发出请求时产生 ,当首次通信中往DIN 写入数据时采用 15 + 1 位模式时 ,可以用D0进行二次通信请求;当首次通信采用 16 位模式时,则必须由 FC 引脚输入信号来产生二次通信请求. 二次通信数据格式如图 4 所示 ,其中D7~D0 为控制寄存器数据 ,D12~D8 为控制寄存器地址 ,D13 = 1 为读控制寄存器数据 ,D13 = 0对控制寄存器写数据. 通过二次通信 ,可实现TLC320AD50C初始化和修改 TLC320AD50C 内部控制寄存器。

图2-2 二次通信格式3 硬件电路设计3.1整体系统框图设计DSP作为主设备,AD50为从设备的连接图如下图所示。

图中AD50的时钟信号由5402的定时器0输出提供,时钟频率可以通过修改定时器0的设置而改变。

AD50的FC引脚连接到C5402的XF引脚,用于控制第二次串行通信。

AD50的DIN和DOUT分别连接C5402的缓冲串口0的DX0和DR0引脚。

AD50的SCLK连接C5402的CLKR0,帧同步信号FS连接C5402缓冲串口的FRX0.图3-1 系统总体框图3.2 电源模块和复位模块TMS320C5402芯片的电源电压有3.3V 和1.8V 两种,其中3.3V 电压供I/O 接口用,1.8V 电源主要供期间内部使用。

电源的产生一般由5V 电源电压产生3.3V 、1.8V ,产生电源的芯片很多,如Maxim 公司的MAX604和,MAX748,TI 公司的TPS72x 和TPS73x 系列,这些芯片又分为线性和开关两种,在设计时应根据实际的需要,如果系统对功耗要求不是很高的情况下,可以使用线性稳压器。

DR0DX0TOUT0CLKR0FRX0XFTMS320VC5402 DOUT DIN MCLK SCLK /FS FC M/~S TLC320 AD50CGND图3-2 电源电路和复位电路复位电路一般有两种,一种是RC复位电路,另一种是采用集成自动监控复位芯片电路。

RC复位电路成本低,在一般情况下能够保证系统的正常复位,但其功耗大,可靠性差,当电源出现瞬态降落时,由于RC的相应速较慢,无法产生符合要求的复位脉冲,另外电阻和电容受环境温度的影响大,给设计也带来一些麻烦,所以我们采用性能全、价格低、可靠性高的集成自动监控复位芯片复位电路。

3.3 时钟模块一般TMS320C54x芯片的时钟电路有两种。

一种是利用芯片内部的振荡器电路与X1、X2/CLK引脚之间连接的一个晶体和两个电容组成并联谐振电路,如图3-3,它可以产生与外加晶体同频率的时钟信号。

电容一般在0~30pf之间选择,它们可以对时钟频率起到微调的作用。

另一种方法是采用封装好的晶体振荡器,将外部时钟源直接输入X2/CLK 引脚,而将X1引脚悬空,如图3-3由于这种方法简单,一般系统设计都采用这种方案。

晶振我们一般采用20M晶振。

图3—3时钟电路3.4 TLC320AD590C与TMS320VC5402接口电路DSP作为主设备,TLC320AD590C为从设备的连接图如下图所示。

图中AD50的时钟信号由5402的定时器0输出提供,时钟频率可以通过修改定时器0的设置而改变。