可编程ASIC技术

可编程ASIC设计实训报告

可编程ASIC设计实训报告1.引言1.1 概述概述:可编程ASIC(Application-Specific Integrated Circuit)设计是一种针对特定应用领域进行定制优化的集成电路设计方法。

与传统的ASIC 设计相比,可编程ASIC设计可以在不改变硬件的情况下,通过重新编程实现不同的功能和逻辑。

在本报告中,我们将介绍可编程ASIC设计的基本概念和原理,以及在实训中搭建设计环境和进行设计实例分析的具体过程和方法。

通过本报告的学习,读者可以深入了解可编程ASIC设计的实践应用,以及进一步掌握ASIC设计的相关技术和方法。

文章结构部分的内容可以包括对整篇文章的组织架构和每个部分的内容概述。

可以介绍文章的逻辑顺序以及每个部分的重点内容和目的。

同时,文章结构部分也可以包括对整篇文章的写作目的和读者对象的介绍。

": , "3.2 成果展示": ,"3.3 展望":请编写文章1.2 文章结构部分的内容1.3 目的目的部分:通过本报告的撰写和实训内容的呈现,旨在让读者了解可编程ASIC设计的基本概念和原理,掌握实训环境搭建的方法和技巧,以及通过设计实例分析进行实际操作,从而提升对可编程ASIC设计的理解和应用能力。

同时,通过总结和成果展示,展示实训成果,激发更多人对可编程ASIC设计领域的兴趣,为未来的发展展望提供参考。

2.正文2.1 可编程ASIC设计简介可编程ASIC(Application Specific Integrated Circuit)是一种专门定制的集成电路,与传统的ASIC相比,可编程ASIC具有更高的灵活性和可编程性。

可编程ASIC设计允许工程师在硅片上实现特定的电路功能,同时又可以根据需求进行修改和重新配置,从而实现多种功能的实现。

可编程ASIC设计的主要特点包括灵活性、可编程性和高性能。

通过使用可编程ASIC,设计人员可以快速构建复杂的数字电路,同时减少电路设计的时间和成本。

可编程ASIC器件分类及特点

可编程ASIC器件分类及特点目前,可编程ASIC 器件已经是一个特别浩大的家族了,生产厂家众多、产品名称各异、制造工艺和结构也不尽相同。

例如,目前生产可编程ASIC 器件的厂家有主要有XILINX、ALTERA、LATTICE、ACTEL、ATMEL、AMD、CYPRESS、INTEL、MOTOROLA、TI(TEXAS INSTRUMENT)等厂家。

各厂家又有不同的系列和产品名称,器件结构和分类更是不同。

目前,常见的可编程ASIC器件有FPGA,CPLD,GAL,PAL,PLA和PROM 等。

由于历史的缘由,对可编程ASIC器件的命名不很规范,可编程ASIC器件有多种分类方法,没有统一的分类标淮。

本节介绍其中几种比较通行的分类方法。

1.编程ASIC器件的集成度分类集成度是集成电路一项很重要的指标,假如从集成密度上分类,可分为低密度可编程ASIC器件和高密度可编程ASIC规律器件。

通常,当PLD中的等效门数超过500门,则认为它是高密度PLD。

假如根据这个标准,PROM、PLA、PAL和GAL器件属于低密度可编程ASIC器件,而CPLD和FPGA属于高密度可编程ASIC器件。

2.从互连结构上分类从互连结构上可将PLD分为确定型和统计型两类。

确定型PLD是指互连结构每次用相同的互连线实现布线,所以线路的时延是可以猜测的,这类PLD的定时特性经常可以从数据手册上查阅而事先确定。

这种基本结构大多为与或阵列的器件,它能有效地实现“积之和”形式的布尔规律函数。

包括简洁PLD器件(PROM,PLA,PAL和GAL)和CPLD。

目前除了FPGA器件外,基本上都属于这一类结构。

确定型PLD是通过修改与有固连内部电路的规律功能来编程.统计型结构的典型代表是FPGA。

它是指设计系统每次执行相同功能,都能给出不同的布线模式,一般无法准确地预知线路的时延。

所以,设计系统必需允许设计者提出约束条件,如关键路径的时延。

统计型结构的可编程ASIC器件主要通过转变内部连线的布线来编程。

ASIC芯片技术和知识介绍

ASIC芯片技术和知识介绍ASIC (Application Specific Integrated Circuit )芯片是专用集成电路,是针对用户对特定电子系统的需求,从根级设计、制造的专有应用程序芯片,其计算能力和计算效率可根据算法需要进行定制,是固定算法最优化设计的产物。

ASIC 芯片模块可广泛应用于人工智能设备、虚拟货币挖矿设备、耗材打印设备、军事国防设备等智慧终端。

在硬件层面,ASIC 芯片由基本硅材料、磷化镓、砷化镓、氮化镓等材料构成。

在物理结构层面,ASIC 芯片模块由外挂存储单元、电源管理器、音频画面处理器、网络电路等IP核拼凑而成。

同一芯片模组可搭载一个或几个功能相同或不同的ASIC 芯片,以满足一种或多种特定需求ASIC 芯片分类(1)根据定制程度不同,ASIC 芯片可被分为全定制ASIC 芯片、半定制ASIC 芯片及可编程ASIC芯片① 全定制ASIC 芯片全定制ASIC 芯片是定制程度最高的芯片之一,研发人员基于不同电路结构设计针对不同功能的逻辑单元,于芯片板搭建模拟电路、存储单元、机械结构。

逻辑单元之间由掩模版连接,ASIC 芯片掩模版也具备高度定制化特点。

全定制化ASIC 芯片设计成本较高,平均每单位芯片模块设计时间超过9 周。

该类芯片通常用于高级应用程序。

相对半定制化ASIC 芯片,全定制化ASIC 芯片在性能、功耗等方面表现优秀。

如应对相同功能,在同种工艺前提下,全定制化ASIC 芯片平均算力输出约为半定制化ASIC 芯片平均算力输出的8 倍,采用24 纳米制程的全定制化ASIC 芯片在性能上优于采用5 纳米制程的半定制化ASIC 芯片。

② 半定制ASIC 芯片构成半定制ASIC 芯片的逻辑单元大部分取自标准逻辑单元库,部分根据特定需求做自定义设计。

相对全定制ASIC 芯片设计成本较低,灵活度较高。

根据标准逻辑单元和自定义逻辑单元数量搭配模式不同,半定制ASIC 芯片可细分为门阵列芯片和标准单元芯片。

可编程ASIC设计及应用_[电子科大]可编程逻辑器件

![可编程ASIC设计及应用_[电子科大]可编程逻辑器件](https://img.taocdn.com/s3/m/9a797c8eec3a87c24028c47a.png)

• •

微米级的含义。 深亚微米:0.35μm以下的工艺称为深亚微米(DSM)。DSM的优 点:

1. 面积缩小; 2. 速度提高;(问题:时序电路中,影响系统速度的因素是什么?) 3. 功耗降低。(问题:电子系统中,影响功耗的因素是什么?)

电子科技大学

9

Outline

• • • • • • • 本部分分析思路 后端知识补充 可编程ASIC器件的分类 可编程ASIC的基本资源 CPLD和FPGA 典型FPGA结构 资源估计实例

电子科技大学

33

CPLD和FPGA结构比较

FPGA CPLD

逻辑块粒度 互连结构 寄存器个数 延时 设计周期 速度 工艺

小 分布式 多 与布局有关 长 单元速度快 SRAM查找表

电子科技大学

大 集总式 少 可以预测 短 系统速度快

EPROM、FLASH ROM

34

FPGA和CPLD性能的选用

• 速度与性能

电子科技大学 29

分段互连型FPGA

• 内部存在多种长度不同的金属连线资源,各 金属连线间通过开关矩阵或逆熔丝编程互连 • 走线灵活,走线延时与布局布线的具体处理 过程有关 • 便于实现快速的局部互连和多级逻辑功能, 但布线复杂

电子科技大学 30

连续互连型FPGA

• 各金属线长度相同,通常是贯穿于整个 芯片的长线来实现功能块间互连 • 连线长度与距离远近无关

• FPGA:现场可编程器件。

电子科技大学

12

Outline

• • • • • • • 本部分分析思路 后端知识补充 可编程ASIC器件的分类 可编程ASIC的基本资源 CPLD和FPGA 典型FPGA结构 资源估计实例

电子科技大学 13

可编程ASIC

4.2 静态RAM

静态RAM可编程技术的例子如图。这是XilinxSRAM配 置单元,由两个交叉耦合反相器组成并采用标准CMOS工艺。 该配置单元驱动芯片上其他晶体管门——开启传输晶体管或 传输门形成连接或者关闭它们使其断开。

优点在于设计者在开发原型时可重新使用芯片,并可用 ISP构建系统。缺点是需要给可编程ASIC持续提供电源,以 使可挥发性的SRAM保存连接信息。或者在每次运行系统时, 从永久性编程的存储器中载入配置数据。SRAM配置单元加 上SRAM单元所驱动的晶体管开关的尺寸也比用在反熔丝技 术中的可编程器件大。

4.3 EPROM和EEPROM工艺

Altera的MAX5000EPLD和xilinx的EPLD都将UV-擦除的 电可编程只读存储器(EPROM)单元用作其编程工艺。 Altera 的EPROM单元如图所示,该EPROM单元几乎和反熔丝一样 大小。

EPROM晶体管除了有另一个浮栅外,看上去就像普通的 MOS管。

4.1.1 金属-金属反熔丝

图示为金属-金属反熔丝。熔丝是钨、钛、硅的合金,其 体电阻率为500μΩcm。 与多晶-扩散反熔丝相比有两个优点。一个是金属反熔丝 直接到金属连线层。而多晶反熔丝连到连线层还需要额外的 空间,并产生附件的寄生电容。第二个优点是直接连到低电 阻金属层更容易用大的编程电流减小反熔丝电阻。

半导体设计中的ASIC技术

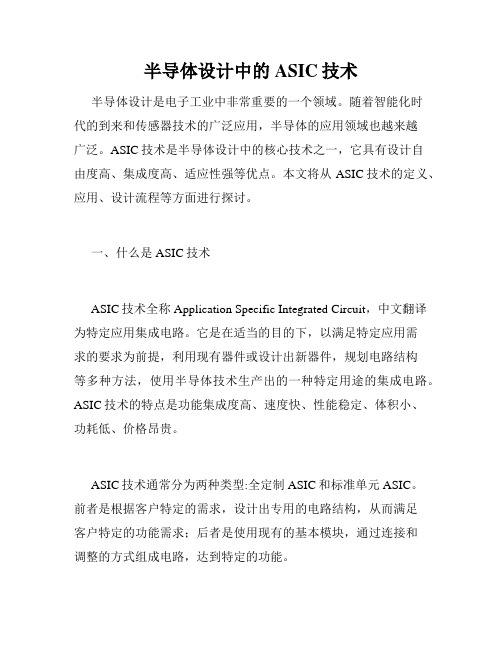

半导体设计中的ASIC技术半导体设计是电子工业中非常重要的一个领域。

随着智能化时代的到来和传感器技术的广泛应用,半导体的应用领域也越来越广泛。

ASIC技术是半导体设计中的核心技术之一,它具有设计自由度高、集成度高、适应性强等优点。

本文将从ASIC技术的定义、应用、设计流程等方面进行探讨。

一、什么是ASIC技术ASIC技术全称Application Specific Integrated Circuit,中文翻译为特定应用集成电路。

它是在适当的目的下,以满足特定应用需求的要求为前提,利用现有器件或设计出新器件,规划电路结构等多种方法,使用半导体技术生产出的一种特定用途的集成电路。

ASIC技术的特点是功能集成度高、速度快、性能稳定、体积小、功耗低、价格昂贵。

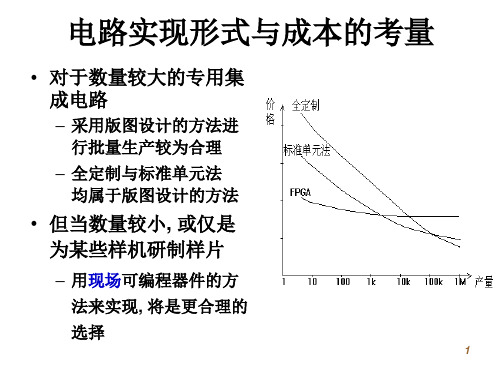

ASIC技术通常分为两种类型:全定制ASIC和标准单元ASIC。

前者是根据客户特定的需求,设计出专用的电路结构,从而满足客户特定的功能需求;后者是使用现有的基本模块,通过连接和调整的方式组成电路,达到特定的功能。

二、ASIC技术的应用领域ASIC技术的应用非常广泛,一般来说,ASIC可以被应用于需要高性能计算和处理的系统中。

例如:工业自动化、汽车电子、医疗、生物、通信、音视频、安防等领域。

下面以智能家居领域为例进行介绍:在智能家居系统中,各种传感器、执行机构等设备需要集成起来,由一个中央控制器进行控制。

这样可以实现智能家居的自动化控制,包括温度、湿度、光照度等环境因素控制,还可以实现家电的遥控、智能化的场景控制以及对家庭安防进行控制。

ASIC技术的应用可以帮助智能家居系统实现高度集成、高准确性和低功耗目标的同时,通过针对特定的应用领域的性能优化提供更强的支撑。

三、ASIC技术的设计流程ASIC技术的设计主要包括前端设计和后端设计两部分。

前端设计主要包括需求分析、电路设计、逻辑验证和电路仿真等流程。

ASIC的电路设计分为数字电路设计和模拟电路设计两个部分,其中模拟电路的设计比数字电路更为复杂。

讲ASIC的可编程器件实现方法

– 组合逻辑输出 – 时序逻辑输出 – 三态输出 – 双向输入/输出

18

可编程器件与现场可编程器件

• 可编程器件家族

– 可编程只读存储器ROM系列 – 可编程逻辑器件PLD系列 – 规模和功能都上了一个档次的CPLD系列 – 现场可编程门阵列FPGA系列

20

FPGA与CPLD的区别

程序存储 资源类型 集成度 使用场合 速度 其他资源 保密性

CPLD 不需要 组合电路资源丰富

低 完成控制逻辑

慢 - 可加密

FPGA SRAM,外挂EEPROM

触发器资源丰富 高

完成比较复杂的算法 快

锁相环 一般不能加密

21

可编程器件与现场可编程器件

• 可编程器件家族

–输入 –输出 –双向 –三态

26

其它辅助元器件和连线

• PIPs -- Programmble Interconnect Points 可编程的内连点

• BIBs -- Bidirectional Interconnect Buffers 双向内连缓冲器

• VLL -- Vertical Long Line 垂直长线, 在垂直方向起快速通道作用

2. 反熔丝(Anti-Fuse)技术

也称熔通技术,这类器件是用逆熔丝作为开关 元件。这些开关元件在未编程时处于开路状态, 编程时,在需要连接处的开关元件两端加上编 程电压将其融通(前页右)。

7

EPROM (可擦除式现场编程)

采用可逆工作机理的“浮栅”雪崩注入MOS电

路

写入1:

衬底接地,D端加高压,雪崩击 穿,隧道效应,浮栅积累正电荷, 形成反型层沟道

可编程ASIC数字系统设计

教学方式

• 自学、讲课和交流 自学、

– 熟练VHDL和自学Verilog语言 (教材1、2) 教材 、 ) – 熟悉常用数字部件的VHDL设计(教材3) (教材 )

• 基本门电路、基本触发器、寄存器、存储器 • 编码器、译码器、选择器、锁存器、比较器、施密特放大器、 移位和循环等 • 加法器、乘法器、A/D和D/A、MCU

VHDL语言设计技术 陈耀和,电子工业出版社, 语言设计技术》 • 1、《VHDL语言设计技术》,陈耀和,电子工业出版社,

2004

• 2、《Verilog 数字系统设计》,夏宇闻,北航出版社,2004。 数字系统设计》 夏宇闻,北航出版社,2004。 • 3、《超大规模集成电路与系统导论》,周润德,电子工业出版社,2004。 超大规模集成电路与系统导论》 周润德,电子工业出版社,2004。 • 4、《集成电路EDA实验教材》,陈弟虎,中山大学出版社,2004。 集成电路EDA实验教材》 陈弟虎,中山大学出版社,2004。 EDA实验教材

数字系统课题设计

• 课题设计目的: 课题设计目的:

– 学会数字系统设计的基本过程和具体方法, 掌握简单 学会数字系统设计的基本过程和具体方法, 数字系统的设计流程, 数字系统的设计流程, –了解数字系统产品的开发过程 , 即项目规划 、 设计与 了解数字系统产品的开发过程,即项目规划、 了解数字系统产品的开发过程 仿真、硬件制做与调试、应用产品或芯片设计; 仿真、硬件制做与调试、应用产品或芯片设计;

数字系统课题设计

• 设计要求: 设计要求:

–具备一个相对完善的数字系统,应具有输入键、输出显示、 具备一个相对完善的数字系统,应具有输入键、输出显示、 具备一个相对完善的数字系统 I/O信号端,选题范围可覆盖控制类(时序或/和过程类) 、 信号端,选题范围可覆盖控制类( 时序或 和过程类) 信号端 和过程类 家电类和微处理(计算、数据处理等) 家电类和微处理(计算、数据处理等); –利用 利用VHDL、Verilog硬件描述语言实现整个数字系统的设计、 硬件描述语言实现整个数字系统的设计、 利用 、 硬件描述语言实现整个数字系统的设计 仿 真 , 并 在 现 有 的 EDA 平 台 上 进 行 证 , 同 时 设 计 下 载 统课题设计

第四章 可编程ASIC

然该器件是反熔丝的,但有时也称其为熔丝型,两种术 语可以互换。

制造工艺和编程电流控制烧断的反熔丝平均电阻,电阻 值变化如图所示。在特殊工艺中,5mA编程电流使烧断的反 熔丝平均电阻约为500Ω。编程电流增加至15mA可使反熔丝 电阻减小至100Ω。反熔丝隔开了FPGA芯片上的互联线,而 编程器烧断反熔丝时便成永久连接。一旦反熔丝编程后,过 程就不可逆了,这是一种OTP技术(而且是抗辐射的)。例如, Actel1010包含112000个反熔丝,但一般只需对Actel芯片上的 约2%的熔丝进行编程。

第四章 可编程ASIC

徐瑞

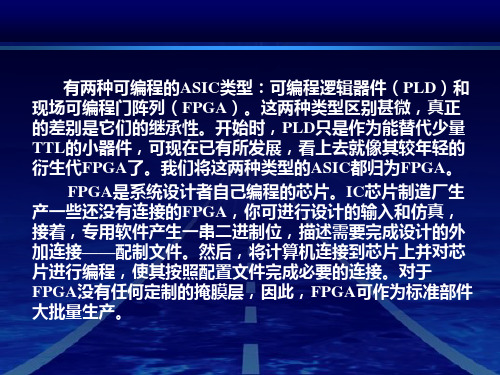

有两种可编程的ASIC类型:可编程逻辑器件(PLD)和 现场可编程门阵列(FPGA)。这两种类型区别甚微,真正 的差别是它们的继承性。开始时,PLD只是作为能替代少量 TTL的小器件,可现在已有所发展,看上去就像其较年轻的 衍生代FPGA了。我们将这两种类型的ASIC都归为FPGA。 FPGA是系统设计者自己编程的芯片。IC芯片制造厂生 产一些还没有连接的FPGA,你可进行设计的输入和仿真, 接着,专用软件产生一串二进制位,描述需要完成设计的外 加连接——配制文件。然后,将计算机连接到芯片上并对芯 片进行编程,使其按照配臵文件完成必要的连接。对于 FPGA没有任何定制的掩膜层,因此,FPGA可作为标准部 件大批量生产。

FPGA深受微系统设计者的喜爱,因为它填补了TTL和 PLD设计与现代复杂且通常又昂贵的ASIC之间的空白。FPGA 用于开发系统原型或小批量生产时非常理想。FPGA供应商不 需要IC制造设备来生产芯片,而是与IC制造厂签约为其生产 部件。他们常通过经销商售出芯片,而自己直接销售设计软件 和必要的编程硬件。 所有的FPGA都有某些共同的要素。他们都有规则化的基 本逻辑单元阵列,并用可编程技术进行配臵。芯片输入和输出 使用与基本逻辑单元不同的专用I/O逻辑单元。可编程互联方 式形成这两种逻辑单元之间的连接。FPGA中的可编程技术决 定了基本逻辑单元的类型和互联方式。由此也决定了输入和输 出电路的设计以及编程方式。 可编程技术可以是永久性,也可以是非永久性的。一下几 节将讨论不同的可编程技术。

asic芯片编程语言

ASIC芯片编程语言是一种专门用于编写ASIC芯片的程序的语言,它与普通的编程语言不同,因为它需要考虑到ASIC芯片的硬件特性和设计规则。

常见的ASIC芯片编程语言包括VHDL、Verilog、SystemVerilog等。

这些语言都有自己的特点和适用范围,需要根据具体的应用场景和需求来选择。

VHDL是一种硬件描述语言,它主要用于描述数字系统的结构和行为,适用于ASIC和FPGA 设计。

VHDL语法严谨、规范,易于阅读、编写和调试,适用于描述复杂数字系统的行为。

它适合于描述算法和逻辑电路,易于移植到不同的硬件平台上。

Verilog是一种面向结构的硬件描述语言,它主要用于描述数字系统的结构和功能,适用于ASIC和FPGA设计。

Verilog语法简洁、易学易用,适合于描述电路模块和系统级设计。

它支持并行执行和组合逻辑,适用于描述大规模数字系统的行为。

SystemVerilog是一种基于Verilog的验证和测试语言,它提供了更多的验证和测试功能,适用于ASIC和FPGA设计。

SystemVerilog支持异常处理、并发结构和并发验证方法,适用于描述复杂数字系统的行为和功能。

它还提供了许多用于验证的测试工具和测试框架,提高了设计的可靠性和可维护性。

除了以上三种语言外,还有一些其他的ASIC芯片编程语言,如C、C++等。

这些语言也可以用于ASIC芯片的设计,但它们需要考虑到硬件的特性和性能,需要进行一些特殊的优化和调整。

总之,ASIC芯片编程语言的选择需要考虑具体的应用场景和需求,不同的语言有不同的特点和适用范围。

在选择语言时,需要根据具体情况进行评估和选择,以获得最佳的设计效果和性能。

asic设计方法知识点

asic设计方法知识点ASIC(Application Specific Integrated Circuit,专用集成电路)是根据特定应用需求进行设计的芯片。

它经过专门的设计和验证,以实现特定功能或任务。

本文将介绍ASIC设计方法的相关知识点,包括设计流程、设计方法和验证技术。

一、设计流程ASIC设计流程是按照一定的步骤进行的,主要包括需求分析、体系结构设计、逻辑设计、物理设计和验证。

下面将对这些步骤进行详细介绍。

1. 需求分析在需求分析阶段,设计人员需要明确ASIC的功能需求和性能指标。

他们与客户进行沟通,并根据客户所述需求进行详细分析。

在这个阶段,定义ASIC的输入输出接口和芯片的整体功能。

2. 体系结构设计体系结构设计是确定ASIC内部模块之间的关系和功能分配。

在这个阶段,设计人员将高层次的功能分解为多个模块,并定义它们之间的通信方式和数据交换。

还可以选择合适的处理器和外围设备。

3. 逻辑设计逻辑设计将体系结构设计的模块进行电路层次的设计。

在这个阶段,设计人员采用HDL(Hardware Description Language)编写硬件描述语言代码,然后进行逻辑综合和布局布线。

逻辑综合将HDL代码转化为逻辑网表,布局布线则将逻辑网表转化为物理布局。

4. 物理设计物理设计主要包括布局、布线和时序优化。

在设计布局时,需要确定各模块的相对位置和布局规则,以满足尺寸和性能要求。

布线阶段用于确定模块之间的互连路径,以及时序优化以确保设计的正确性和性能。

5. 验证验证是整个设计流程中非常重要的一步,确保ASIC设计满足规格要求。

验证可以包括功能仿真、时序仿真、形式验证和硬件验证等。

在验证阶段,设计人员需要使用专业的仿真和验证工具对设计进行验证,并解决可能出现的问题。

二、设计方法ASIC设计方法包括全定制设计、半定制设计和可编程逻辑设计。

下面将分别介绍这三种方法。

1. 全定制设计全定制设计是一种从零开始的设计方法,它提供了最大的灵活性和性能优化。

FPGA和ASIC的概念及区别

FPGA和ASIC的概念,他们的区别?答案:FPGA是可编程ASIC。

ASIC:专用集成电路,它是面向专门用途的电路,专门为一个用户设计和制造的。

根据一个用户的特定要求,能以低研制成本,短、交货周期供货的全定制,半定制集成电路。

与门阵列等其它ASIC(Application Specific IC)相比,它们又具有设计开发周期短、设计制造成本低、开发工具先进、标准产品无需测试、质量稳定以及可实时在线检验等优点。

FPGA与ASIC实现系统设计的比较在当今的电子设备中集成电路的应用已经越来越广泛,几乎涉及到每一种电子设备中。

集成电路按其实现技术可以分为2大类:可编程逻辑器件(包括CPLD和FPGA等)和专用集成电路(ASIC)。

下面我们分别从这2类集成电路的特点和如何使用这2类集成电路来实现我们的设计需求来进行比较,以为我们以后的系统设计提供借鉴。

首先我们以FPGA为代表比较可编程逻辑器件和ASIC,它们最大的区别就是FPGA在不知道使用者的具体需求之前就已经按一定的配置制造好了所有的电路,使用者再根据自己的设计需要选用其中的电路来使用,而ASIC是根据使用者的设计需求来制造其中的电路。

由于以上原因使得这2类集成电路具有如下特点:ASIC由厂家定制,有比较低的单片生产成本,但却有很高的设计成本以及缓慢的上市时间;FPGA则具有高度的灵活性,低廉的设计成本以及适中的器件成本和快速的面世时间。

下面我们分别简单介绍使用ASIC和FPGA实现某一设计的的步骤:要设计并生产一颗ASIC其流程大致如下:首先是系统设计,这其中包括设计好系统的对外接口,系统内部大的模块划分,内部模块之间的接口确定,系统时钟的确定等等。

然后进行进一步的详细设计,这一步包括各个大模块内部的再次模块划分,内部小模块之间的接口确定等。

再下一步是进行RTL级编码,即使用硬件描述语言进行实际的电路的设计,类似于软件业的代码编写。

RTL级编码完成后进行RTL级仿真,如果功能正确那么下一步利用综合工具生成网表和SDF文件然后进行前仿真,如果前仿真没有问题即可进行布局布线,布局布线完成后再次提取网表和SDF文件,利用布局布线后的网表和SDF文件进行后仿真,如果后仿真也没有问题即可进行样片的生产。

可编程ASIC技术及应用

可编程ASIC技术及应用可编程ASIC(Application-Specific Integrated Circuit,即应用特定集成电路)是一种专为特定应用而设计的、定制化的集成电路。

与通用可编程逻辑设备(如FPGA)相比,可编程ASIC用于实现高度特定的应用需求,因此具有更高的性能和更低的功耗。

可编程ASIC的技术在过去几十年中得到了快速发展。

以下是关于可编程ASIC 技术及应用的一些主要内容。

一、可编程ASIC的技术进展:可编程ASIC的技术进展主要包括:1.设计工具的改进:随着VLSI技术的不断发展,可编程ASIC设计工具的功能和性能也得到了明显提升。

设计工具的改进使得设计师能够更加有效地进行设计、验证和调试工作,大大缩短了开发周期。

2.系统级集成设计:可编程ASIC的技术进展使得系统级集成设计得以实现。

通过将多个模块整合到单一芯片上,可实现更高度集成的系统,进一步提升了性能和功耗。

3.低功耗设计:为了满足移动设备等低功耗应用的需求,可编程ASIC技术在低功耗设计方面也取得了显著进展。

新的设计方法和技术被应用于可编程ASIC,以降低功耗,并提供更长的电池寿命。

二、可编程ASIC的应用领域:可编程ASIC的应用广泛涵盖了各个领域,以下是其中一些主要应用领域:1.通信和网络:可编程ASIC被广泛应用于通信和网络设备中,如交换机、路由器、光纤通信设备等。

由于可编程ASIC能够提供高性能、低功耗和高度集成的特性,使其成为这些应用的首选。

2.消费电子产品:可编程ASIC在消费电子产品中应用广泛,如智能手机、平板电脑、数字电视等。

通过采用可编程ASIC芯片,这些设备能够获得更高的性能和更低的功耗。

3.汽车电子:可编程ASIC也逐渐得到汽车电子领域的应用。

它可以用于实现自动驾驶、车载娱乐系统、车联网等功能,提升驾驶体验和安全性能。

4.医疗设备:可编程ASIC在医疗设备中也有广泛的应用,如磁共振成像(MRI)、心脏起搏器等。

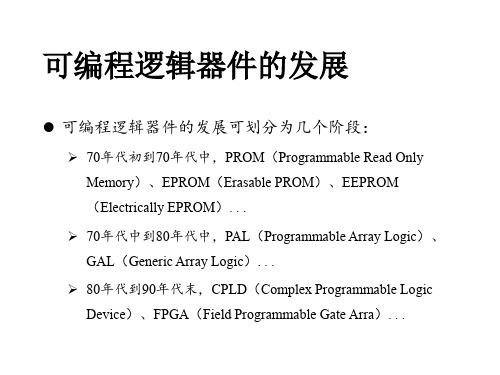

可编程逻辑器件及ASIC简介

CPLD/FPGA

Lattice首先推出了复杂通用逻辑阵列CPLD:

具有可编程的逻辑宏单元MC 采用全铜层等长连接线,可实现复杂的I/O单元互连 可预知电路延迟时间,实现精确的时序逻辑设计 CPLD可完成较复杂、较高速度的逻辑功能,如接口转换、总

线控制等,从而实现人机接口模块、数据采集系统等功能设 计

80年代到90年代末,CPLD(Complex Programmable Logic Device)、FPGA(Field Programmable Gate Arra). . .

基于ROM的组合逻辑

由于ASIC的高成本、长周期的瓶颈,市场首先推出了 基于ROM的组合逻辑设备:

与逻辑函数相对应,能快速实现需要的逻辑 操作简单,无平台要求 工作速度慢 无法实现时序逻辑和大规模逻辑 功耗大,资源浪费较多

未来FPGA的设计者,主要工作是找到适合项目需要的IP库资 源,然后将这些IP整合起来,完成顶层模块设计

FPGA的发展动向

FPGA的动态可重构技术:

随着密度不断提高,FPGA能实现的功能也越来越复杂,全部 逻辑配置需要的时间也变长了,这降低了系统的实时性

FPGA动态重构技术主要是指对于特定结构的FPGA芯片,在 一定的控制逻辑的驱动下,对芯片的全部或部分逻辑资源实 现高速的功能变换,从而实现“按需动态重构”,节省逻辑 资源,提高配置效率

具有几乎完美的现场编程架构,已成为新一代:

FPGA 实现方法 查找表

门规模 数百万门

延时 配置方式

互连结构 成本价格

不可预测

多属于 RAM型 分布式

较高

CPLD 与或阵列 或查找表 数万门

固定 一般为 ROM型 集总式 较低

可编程ASIC器件剖析

三、可编程逻辑器件

3、多路开关方式:利用多路开关的特性,在多 路开关的每个输入接到固定电平或输入信号 时,来实现不同的逻辑功能。 一个二选一开关可以实现的功能: a、b、s做输入信号:f=sa+/sb a、b接0、1,可以做反相器:f=/s s接0或1,可以做缓冲器:f=a|b b接0。可以做2输入与门:f=sa a接0。可以实现一个反相输入与门:f=/sb b接1。可以做2输入或门:f=sa+/s=s+a 4、固定功能方式:即逻辑功能单元可以提供单 个固定功能。

主要内容

EDA技术概述 EDA设计流程 可编程逻辑器件 硬件描述语言

二、EDA设计流程

EDA设计特点:自顶向下设计。 芯片设计流程

系统描述

功能设计

系统描述:从系统层次对芯片进行规划, 包括芯片的功能、功耗、大小尺寸、成 本和工艺等。 功能设计:使用相关硬件语言或电路图 输入等方式描述系统的行为特性,得到 系统的时序图、子模块图或状态机等。 逻辑设计:用EDA工具进行仿真验证、 并进行综合和优化。

5 边界扫描技术 BST:边界扫描测试,实现 在片(ON-CHIP)印刷板测 试和器件测试。由联合测试 活动组织JTAG提出,IEEE 规定了测试标准。 IEEE 1149.1 TDI:测试数据输入; TMS:测试模式选择; TCKБайду номын сангаас边界扫描时钟; TDO:测试数据输出。 一般芯片具有ISP功能时, 其编程引脚与JTAG引脚共 用。

系统描述

功能设计

逻辑设计

电路设计 版图设计 芯片制作 封装测试

主要内容

EDA技术概述 EDA设计流程 可编程逻辑器件 硬件描述语言

可编程ASIC设计及应用核心语法与基础电路设计课件

End u_and2;

Architecture behv of u_and2 is

Begin

c <= a and b;

End behv;

电子科技大学

程序例子 u1

a

Library ieee;

Use ieee.std_logic_1164.all;

b

c

Entity u_and2 is

PEABonreccrdgthi<(unibc=ta_e:a:a:cnoitiannudunr2stsed;tstddbbt_d_e;l_lhoolvgogigioccif;c;u);_and2结绝成一际感is构大;条上信体多“就号描数光是为述情秃一右。况”个边下的所pro由信有ce号信psrso赋号,ce值。其ss实构敏

程序结构

• Library …;-- 库,包等的说明 • Entity …;-- 实体说明 • Architecture…;-- 结构体描述

电子科技大学

程序例子 u1

a

Library ieee;

Use ieee.std_logic_1164.all;

b

c

Entity u1 is

Port( a : in std_logic;

b

c

Entity u1 is

Port( a : in std_logic; b : in std_logic; c : out std_logic);

End u1; Architecture behv of u1 is

表示使用 ieee库。这是最 常用的库说明,绝大多数 的VHDL代码都使用这个 库。

ELSIF (input(2)=‘0’) then y<=“10”;

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

可编程ASIC技术组合电路模块一、采用不同的描述方式设计本章中的组合电路模块,并综合。

1. 基本组合电路①门级结构描述module gate_1(F,A,B,C,D);input A,B,C,D;output F;nand(F1,A,B);and(F2,B,C,D);or(F,F1,F2);endmodule综合后RTL视图:②数据流描述module gate_1(F,A,B,C,D);input A,B,C,D;output F;assign F = (~(A&B))|(B&C&D);endmodule综合后RTL视图:③行为描述module gate_1(F,A,B,C,D);input A,B,C,D;output F;reg F;always @(A or B or C or D)beginF=(~(A&B))|(B&C&D);endendmodule综合后RTL视图:2. 三态门描述①门级结构描述module tri_1(in,en,out);input in,en;output out;tri out;bufif1 b1(out,in,en);endmodule综合后RTL视图:②数据流描述module tri_1(in,en,out);input in,en;output out;assign out = en?in:1'bZ;endmodule综合后RTL视图:③行为描述module tri_1(in,en,out);input in,en;output out;reg out;always @(in,en)beginif(en)out = in;elseout = 1'bZ;endendmodule综合后RTL视图:3. 3-8译码器①门级描述module decoder_38(out,in);output[7:0] out;input[2:0] in;// 3 to 8 decoderor(out[0],in[2],in[1],in[0]);or(out[1],in[2],in[1],~in[0]);or(out[2],in[2],~in[1],in[0]);or(out[3],in[2],~in[1],~in[0]);or(out[4],~in[2],in[1],in[0]);or(out[5],~in[2],in[1],~in[0]);or(out[6],~in[2],~in[1],in[0]);or(out[7],~in[2],~in[1],~(in[0]));endmodule综合后RTL视图:②数据流描述module decoder_38(out,in);output[7:0] out;input[2:0] in;wire[7:0] out;assign out[0]=in[2]|in[1]|in[0];assign out[1]=in[2]|in[1]|(~in[0]);assign out[2]=in[2]|(~in[1])|in[0];assign out[3]=in[2]|(~in[1])|(~in[0]);assign out[4]=(~in[2])|in[1]|in[0];assign out[5]=(~in[2])|in[1]|(~in[0]);assign out[6]=(~in[2])|(~in[1])|in[0];assign out[7]=(~in[2])|(~in[1])|(~in[1]);endmodule综合后RTL视图:③行为描述module decoder_38(out,in);output[7:0] out;input[2:0] in;reg[7:0] out;always @(in)begincase(in)3'd0: out=8'b11111110;3'd1: out=8'b11111101;3'd2: out=8'b11111011;3'd3: out=8'b11110111;3'd4: out=8'b11101111;3'd5: out=8'b11011111;3'd6: out=8'b10111111;3'd7: out=8'b01111111;endcaseendendmodule综合后RTL视图:4. 奇偶校验位产生器①门级描述module parity(even_bit,odd_bit,input_bus);output even_bit,odd_bit;input[7:0] input_bus;xor XR1(r1,input_bus[1],input_bus[0]);xor XR2(r2,input_bus[3],input_bus[2]);xor XR3(r3,input_bus[5],input_bus[4]);xor XR4(r4,input_bus[7],input_bus[6]);xor XR5(r5,r2,r1);xor XR6(r6,r4,r3);xor XR7(r7,r6,r5);not N1(odd_bit,r7);not N2(even_bit,odd_bit);endmodule综合后RTL视图:②数据流描述module parity(even_bit,odd_bit,input_bus);output even_bit,odd_bit;input[7:0] input_bus;assign odd_bit = ~(^input_bus);assign even_bit = ~odd_bit;endmodule综合后RTL视图:③行为描述module parity(even_bit,odd_bit,input_bus);output even_bit,odd_bit;input[7:0] input_bus;reg odd_bit,even_bit;always @(input_bus)beginodd_bit = ~(^input_bus);endalways @(input_bus)begineven_bit = ~odd_bit;endendmodule综合后RTL视图:5. 4选1 MUX①门级结构描述module mux4_1(out,in0,in1,in2,in3,sel);output out;input in0,in1,in2,in3;input[1:0] sel;not (sel1_n,sel[1]);not (sel0_n,sel[0]);and (g1,sel1_n,sel0_n);and (out0,g1,in0); //in0and (g2,sel1_n,sel[0]);and (out1,g2,in1); //in1and (g3,sel[1],sel0_n);and (out2,g3,in2); //in2and (g4,sel[1],sel[0]);and (out3,g4,in3); //in3or (res1,out2,out1);or (res2,out4,out3);or (out,res2,res1); //outendmodule综合后RTL视图:②数据流描述module mux4_1(out,in0,in1,in2,in3,sel);output out;input in0,in1,in2,in3;input[1:0] sel;assign out = (~sel[1]&~sel[0]&in0)|(~sel[1]&sel[0]&in1)|(sel[1]&~sel[0]&in2)|(sel[1]&sel[0]&in3);endmodule综合后RTL视图:③行为描述module mux4_1(out,in0,in1,in2,in3,sel);output out;input in0,in1,in2,in3;input[1:0] sel;reg out;always @(in0 or in1 or in2 or in3 or sel)beginif(sel==2'b00)out=in0;else if(sel==2'b01)out=in1;else if(sel==2'b10)out=in2;elseout=in3;endendmodule综合后RTL视图:时序电路模块二、采用不同的描述方式设计本章中的时序电路模块,并综合。

1. D-FF designs(基本D触发器)①门级结构描述module dffx (d,clk,q,qbar);input d,clk;output q,qbar;nandnd1 (d1_n,d,d2),nd2 (d1,d1_n,d2_n),nd3 (d2,clk,d1_n,d2_n),nd4 (d2_n,clk,d1),nd5 (qbar,d2,q),nd6 (q,qbar,d2_n);endmodule综合后RTL视图:②数据流描述module dffx(d,clk,q,qbar);input d,clk;output q,qbar;wire d1,d2,d1_n,d2_n;assign d1_n = ~(d&d2);assign d1 = ~(d1_n&d2_n);assign d2_n = ~(clk&d1);assign d2 = ~(clk&d1_n&d2_n);assign qbar = ~(d2&q);assign q = ~(qbar&d2_n);endmodule综合后RTL图:③行为描述module dffx3(q,d,clk);output q;input d,clk;reg q;always @(posedge clk)beginq <= d;endendmodule综合后RTL视图:2. 带异步清0、异步置1的D触发器①门级描述module dffx1 (d,clk,q,qbar,set,reset);input d,clk,set,reset;output q,qbar;not (set_n,set);not(reset_n,reset);nandnd1 (d1_n,d,d2),nd2 (d1,d1_n,d2_n),nd3 (d2,clk,d1_n,d2_n),nd4 (d2_n,clk,d1),nd5 (qbar,d2,q,reset_n),nd6 (q,qbar,d2_n,set_n);endmodule综合后RTL视图:②数据流描述module dffx1(d,clk,q,qbar,set,reset);input d,clk,set,reset;output q,qbar;assign d1_n = ~(d&d2);assign d1 = ~(d1_n&d2_n);assign d2_n = ~(clk&d1);assign d2 = ~(clk&d1_n&d2_n);assign qbar = ~(d2&q&(~reset));assign q = ~(qbar&d2_n&(~set));endmodule综合后RTL视图:③行为描述module dff1(q, qn, d, clk, set, reset);input d, clk, set, reset;output q, qn;reg q, qn;always @(posedge clk or negedge set or negedge reset)beginif (!reset)beginq <= 0; // clearqn <= 1;endelse if (!set)beginq <= 1; // setqn <= 0;endelsebeginq <= d;qn <= ~d;endendendmodule综合后RTL视图:3. 带同步清0、同步置1的D触发器①门级描述module dffx2(q,qn,d,clk,set,reset);input d, clk, set, reset;output q, qn;nandnd1 (d1_n,d,d2),nd2 (d1,d1_n,d2_n),nd3 (d2,clk,d1_n,d2_n),nd4 (d2_n,clk,d1),nd5 (r_cp,clk,reset),nd6 (s_cp,clk,set),nd7 (qbar,d2,q,r_cp),nd8 (q,qbar,d2_n,s_cp);endmodule综合后RTL视图:②数据流描述module dffx2(q,qn,d,clk,set,reset);input d,clk,set,reset;output q,qn;wire r_cp,s_cp;assign d1_n = ~(d&d2);assign d1 = ~(d1_n&d2_n);assign d2_n = ~(clk&d1);assign d2 = ~(clk&d1_n&d2_n);assign r_cp = ~(reset&clk);assign s_cp = ~(set&clk);assign qn = ~(d2&q&r_cp);assign q = ~(qn&d2_n&s_cp);endmodule综合后RTL视图:③行为级描述module dffx2(q, qn, d, clk, set, reset);input d, clk, set, reset;output q, qn;reg q, qn;always @(posedge clk)beginif (reset)beginq <= 0;qn <= 1;end //clear,high enableelse if (set)beginq <= 1;qn <= 0;end //set,high enableelsebeginq<= d;qn<=~d;endendendmodule综合后RTL视图:4. 8位数据锁存器①门级描述module latch_8(qout,data,clk);output[7:0] qout;input[7:0] data;input clk;andad1(qout[0],data[0],clk),ad2(qout[1],data[1],clk),ad3(qout[2],data[2],clk),ad4(qout[3],data[3],clk),ad5(qout[4],data[4],clk),ad6(qout[5],data[5],clk),ad7(qout[6],data[6],clk),ad8(qout[7],data[7],clk);endmodule综合后RTL视图:②数据流描述module latch_8(qout,data,clk);output[7:0] qout;input[7:0] data;input clk;assign qout[0]= data[0]&clk;assign qout[1]= data[1]&clk;assign qout[2]= data[2]&clk;assign qout[3]= data[3]&clk;assign qout[4]= data[4]&clk;assign qout[5]= data[5]&clk;assign qout[6]= data[6]&clk;assign qout[7]= data[7]&clk;endmodule综合后RTL视图:③行为描述module latch_8(qout,data,clk);output[7:0] qout;input[7:0] data;input clk;reg[7:0] qout;always @(clk or data)beginif(clk)qout <= data;endendmodule综合后RTL视图:5. 8位数据寄存器①门级描述module reg8(out_data,in_data,clk,clr);output[7:0] out_data;input[7:0] in_data;input clk,clr;wire[7:0] out_data;wire[7:0] qb;dffx_clk dfx_ck0(.d(in_data[0]),.clk(clk),.q(out_data[0]),.qbar(qb[0]));dffx_clk dfx_ck1(.d(in_data[1]),.clk(clk),.q(out_data[1]),.qbar(qb[1]));dffx_clk dfx_ck2(.d(in_data[2]),.clk(clk),.q(out_data[2]),.qbar(qb[2]));dffx_clk dfx_ck3(.d(in_data[3]),.clk(clk),.q(out_data[3]),.qbar(qb[3]));dffx_clk dfx_ck4(.d(in_data[4]),.clk(clk),.q(out_data[4]),.qbar(qb[4]));dffx_clk dfx_ck5(.d(in_data[5]),.clk(clk),.q(out_data[5]),.qbar(qb[5]));dffx_clk dfx_ck6(.d(in_data[6]),.clk(clk),.q(out_data[6]),.qbar(qb[6]));dffx_clk dfx_ck7(.d(in_data[7]),.clk(clk),.q(out_data[7]),.qbar(qb[7]));endmodule//dffx with clk(positive edge enable)module dffx_clk (d,clk,q,qbar);input d,clk;output q,qbar;wire d_q1;wire d_qbar1;wire clk_n;assign clk_n = ~clk;dffx_en d_m1(.dat(d),.en(clk),.q(d_q1),.qbar(d_qbar1));dffx_en d_m2(.dat(d_q1),.en(clk_n),.q(q),.qbar(qbar));endmodule//gate control D_latchmodule dffx_en(dat,en,q,qbar);input dat,en;output q,qbar;wire x1,x2;wire q,qbar;not (dat_n,dat);nandnd1 (x1,dat,en),nd2 (x2,dat_n,en),nd3 (q,x1,qbar),nd4 (qbar,q,x2);endmodule综合后RTL视图:②数据流描述module reg8(out_data,in_data,clk,clr);output[7:0] out_data;input[7:0] in_data;input clk,clr;wire[7:0] out_data;wire[7:0] qb;dffx_clk dfx_ck0(.d(in_data[0]),.clk(clk),.q(out_data[0]),.qbar(qb[0]));dffx_clk dfx_ck1(.d(in_data[1]),.clk(clk),.q(out_data[1]),.qbar(qb[1]));dffx_clk dfx_ck2(.d(in_data[2]),.clk(clk),.q(out_data[2]),.qbar(qb[2]));dffx_clk dfx_ck3(.d(in_data[3]),.clk(clk),.q(out_data[3]),.qbar(qb[3]));dffx_clk dfx_ck4(.d(in_data[4]),.clk(clk),.q(out_data[4]),.qbar(qb[4]));dffx_clk dfx_ck5(.d(in_data[5]),.clk(clk),.q(out_data[5]),.qbar(qb[5]));dffx_clk dfx_ck6(.d(in_data[6]),.clk(clk),.q(out_data[6]),.qbar(qb[6]));dffx_clk dfx_ck7(.d(in_data[7]),.clk(clk),.q(out_data[7]),.qbar(qb[7]));endmodule//dffx with clk(positive edge enable) module dffx_clk (d,clk,q,qbar);input d,clk;output q,qbar;wire d_q1;wire d_qbar1;wire clk_n;assign clk_n = ~clk;dffx_en d_m1(.dat(d),.en(clk),.q(d_q1),.qbar(d_qbar1));dffx_en d_m2(.dat(d_q1),.en(clk_n),.q(q),.qbar(qbar)); endmodule//gate control D_latchmodule dffx_en(dat,en,q,qbar);input dat,en;output q,qbar;wire x1,x2;wire q,qbar;assign dat_n = ~dat;assign x1 = ~(dat&en);assign x2 = ~(dat_n&en);assign q = ~(x1&qbar);assign qbar = ~(q&x2);endmodule综合后RTL视图:③行为级描述module reg8(out_data,in_data,clk,clr);output[7:0] out_data;input[7:0] in_data;input clk,clr;reg[7:0] out_data;always @(posedge clk or posedge clr)begin if(clr)out_data <= 0;elseout_data <= in_data;endendmodule综合后RTL视图:6. 可变模加法/减法计数器①门级描述module updown_count(d,clk,clear,load,up_down,qd);input[7:0] d;input clk,clear,load,up_down;output[7:0] qd;wire[7:0] j;wire[7:0] k;wire[7:0] sd_n;wire[7:0] xd_n;wire[7:0] rd_n;wire[7:0] qd_n;wire clear_n;not (clear_n,clear);not (up_down_n,up_down);nandsd1 (sd_n[0],load,d[0]),sd2 (sd_n[1],load,d[1]),sd3 (sd_n[2],load,d[2]),sd4 (sd_n[3],load,d[3]),sd5 (sd_n[4],load,d[4]),sd6 (sd_n[5],load,d[5]),sd7 (sd_n[6],load,d[6]),sd8 (sd_n[7],load,d[7]);nandrd1 (xd_n[0],sd_n[0],load),rd2 (xd_n[1],sd_n[1],load),rd3 (xd_n[2],sd_n[2],load),rd4 (xd_n[3],sd_n[3],load),rd5 (xd_n[4],sd_n[4],load),rd6 (xd_n[5],sd_n[5],load),rd7 (xd_n[6],sd_n[6],load),rd8 (xd_n[7],sd_n[7],load);andad1 (rd_n[0],xd_n[0],clear_n),ad2 (rd_n[1],xd_n[1],clear_n),ad3 (rd_n[2],xd_n[2],clear_n),ad4 (rd_n[3],xd_n[3],clear_n),ad5 (rd_n[4],xd_n[4],clear_n),ad6 (rd_n[5],xd_n[5],clear_n),ad7 (rd_n[6],xd_n[6],clear_n),ad8 (rd_n[7],xd_n[7],clear_n);//JK Trigernot (j[0],0);not (k[0],0);wire[7:1] patA;wire[7:1] patB;andadp1 (patA[1],qd[0],up_down), adp2 (patB[1],qd_n[0],up_down_n), adp3 (patA[2],patA[1],qd[1]),adp4 (patB[2],patB[1],qd_n[1]), adp5 (patA[3],patA[2],qd[2]),adp6 (patB[3],patB[2],qd_n[2]), adp7 (patA[4],patA[3],qd[3]),adp8 (patB[4],patB[3],qd_n[3]), adp9 (patA[5],patA[4],qd[4]),adp10 (patB[5],patB[4],qd_n[4]), adp11 (patA[6],patA[5],qd[5]),adp12 (patB[6],patB[5],qd_n[5]), adp13 (patA[7],patA[6],qd[6]),adp14 (patB[7],patB[6],qd_n[6]);ororp1 (j1,patA[1],patB[1]),orp2 (j2,patA[2],patB[2]),orp3 (j3,patA[3],patB[3]),orp4 (j4,patA[4],patB[4]),orp5 (j5,patA[5],patB[5]),orp6 (j6,patA[6],patB[6]),orp7 (j7,patA[7],patB[7]); jk_tri jkm0(.j(j[0]),.k(j[0]),.clk(clk),.sd_n(sd_n[0]),.rd_n(rd_n[0]),.q(qd[0]),.qbar(qd_n[0])); jk_tri jkm1(.j(j[1]),.k(j[1]),.clk(clk),.sd_n(sd_n[1]),.rd_n(rd_n[1]),.q(qd[1]),.qbar(qd_n[1])); jk_tri jkm2(.j(j[2]),.k(j[2]),.clk(clk),.sd_n(sd_n[2]),.rd_n(rd_n[2]),.q(qd[2]),.qbar(qd_n[2])); jk_tri jkm3(.j(j[3]),.k(j[3]),.clk(clk),.sd_n(sd_n[3]),.rd_n(rd_n[3]),.q(qd[3]),.qbar(qd_n[3])); jk_tri jkm4(.j(j[4]),.k(j[4]),.clk(clk),.sd_n(sd_n[4]),.rd_n(rd_n[4]),.q(qd[4]),.qbar(qd_n[4]));jk_tri jkm5(.j(j[5]),.k(j[5]),.clk(clk),.sd_n(sd_n[5]),.rd_n(rd_n[5]),.q(qd[5]),.qbar(qd_n[5]));jk_tri jkm6(.j(j[6]),.k(j[6]),.clk(clk),.sd_n(sd_n[6]),.rd_n(rd_n[6]),.q(qd[6]),.qbar(qd_n[6]));jk_tri jkm7(.j(j[7]),.k(j[7]),.clk(clk),.sd_n(sd_n[7]),.rd_n(rd_n[7]),.q(qd[7]),.qbar(qd_n[7])); endmodulemodule jk_tri(j,k,clk,sd_n,rd_n,q,qbar);input j,k,clk,sd_n,rd_n;output q,qbar;wire ss,rr;andnd1 (ss,j,qbar),nd2 (rr,k,q);SR_ms srms1(.s(ss),.r(rr),.clk(clk),.sd_n(sd_n),.rd_n(rd_n),.q(q),.qbar(qbar)); endmodulemodule SR_ms(s,r,clk,sd_n,rd_n,q,qbar);input s,r,clk,sd_n,rd_n;output q,qbar;wire q,qbar;wire clk_n;not (clk_n,clk);wire qm,qm_bar;//SR triger: master_slaveSR sr1(.s(s),.r(r),.cp(clk_n),.sd_n(sd_n),.rd_n(rd_n),.q(qm),.qbar(qm_bar));SR sr2(.s(qm),.r(qm_bar),.cp(clk),.sd_n(sd_n),.rd_n(rd_n),.q(q),.qbar(qbar));endmodule//SR trigermodule SR(s,r,cp,sd_n,rd_n,q,qbar);input s,r,cp,sd_n,rd_n;output q,qbar;wire x1,x2;nandnd1 (x1,r,cp,sd_n),nd2 (x2,s,cp,rd_n),nd3 (qbar,q,x1,rd_n),nd4 (q,qbar,x2,sd_n);endmodule综合后RTL视图:②数据流描述module updown_count(d,clk,clear,load,up_down,qd);input[7:0] d;input clk,clear,load,up_down;output[7:0] qd;wire[7:0] j;wire[7:0] sd_n;wire[7:0] rd_n;wire[7:0] qd_n;wire down;wire up,clear_n;assign up = up_down;assign down = ~up_down;assign load_n = ~load;// jk signalassign j[0] = 1;assign j[1] = (qd[0]&up) |(~qd[0]&down);assign j[2] = (qd[0]&qd[1]&up)|((~qd[0])&(~qd[1])&down);assign j[3] = (qd[0]&qd[1]&qd[2]&up)|((~qd[0])&(~qd[1])&(~qd[2])&down);assign j[4] = (qd[0]&qd[1]&qd[2]&qd[3]&up)|((~qd[0])&(~qd[1])&(~qd[2])&(~qd[3])&down);assign j[5] = (qd[0]&qd[1]&qd[2]&qd[3]&qd[4]&up)|((~qd[0])&(~qd[1])&(~qd[2])&(~qd[3])&(~qd[4])&down);assign j[6] = (qd[0]&qd[1]&qd[2]&qd[3]&qd[4]&qd[5]&up)|((~qd[0])&(~qd[1])&(~qd[2])&(~qd[3])&(~qd[4])&(~qd[5])&down); assign j[7] = (qd[0]&qd[1]&qd[2]&qd[3]&qd[4]&qd[5]&qd[6]&up) |((~qd[0])&(~qd[1])&(~qd[2])&(~qd[3])&(~qd[4])&(~qd[5])&(~qd[6])&down);//sd valueassign sd_n[0] = ~(d[0]&load_n);assign sd_n[1] = ~(d[1]&load_n);assign sd_n[2] = ~(d[2]&load_n);assign sd_n[3] = ~(d[3]&load_n);assign sd_n[4] = ~(d[4]&load_n);assign sd_n[5] = ~(d[5]&load_n);assign sd_n[6] = ~(d[6]&load_n);assign sd_n[7] = ~(d[7]&load_n);//rd valueassign rd_n[0] = (~(sd_n[0]&load_n))&clear_n;assign rd_n[1] = (~(sd_n[1]&load_n))&clear_n;assign rd_n[2] = (~(sd_n[2]&load_n))&clear_n;assign rd_n[3] = (~(sd_n[3]&load_n))&clear_n;assign rd_n[4] = (~(sd_n[4]&load_n))&clear_n;assign rd_n[5] = (~(sd_n[5]&load_n))&clear_n;assign rd_n[6] = (~(sd_n[6]&load_n))&clear_n;assign rd_n[7] = (~(sd_n[7]&load_n))&clear_n;jk_tri jkm0(.j(j[0]),.k(j[0]),.clk(clk),.sd_n(sd_n[0]),.rd_n(rd_n[0]),.q(qd[0]),.qbar(qd_n[0]));jk_tri jkm1(.j(j[1]),.k(j[1]),.clk(clk),.sd_n(sd_n[1]),.rd_n(rd_n[1]),.q(qd[1]),.qbar(qd_n[1])); jk_tri jkm2(.j(j[2]),.k(j[2]),.clk(clk),.sd_n(sd_n[2]),.rd_n(rd_n[2]),.q(qd[2]),.qbar(qd_n[2])); jk_tri jkm3(.j(j[3]),.k(j[3]),.clk(clk),.sd_n(sd_n[3]),.rd_n(rd_n[3]),.q(qd[3]),.qbar(qd_n[3])); jk_tri jkm4(.j(j[4]),.k(j[4]),.clk(clk),.sd_n(sd_n[4]),.rd_n(rd_n[4]),.q(qd[4]),.qbar(qd_n[4])); jk_tri jkm5(.j(j[5]),.k(j[5]),.clk(clk),.sd_n(sd_n[5]),.rd_n(rd_n[5]),.q(qd[5]),.qbar(qd_n[5])); jk_tri jkm6(.j(j[6]),.k(j[6]),.clk(clk),.sd_n(sd_n[6]),.rd_n(rd_n[6]),.q(qd[6]),.qbar(qd_n[6])); jk_tri jkm7(.j(j[7]),.k(j[7]),.clk(clk),.sd_n(sd_n[7]),.rd_n(rd_n[7]),.q(qd[7]),.qbar(qd_n[7])); endmodulemodule jk_tri(j,k,clk,sd_n,rd_n,q,qbar);input j,k,clk,sd_n,rd_n;output q,qbar;wire ss,rr;assign ss = j&qbar;assign rr = k&q;SR_ms srms1(.s(ss),.r(rr),.clk(clk),.sd_n(sd_n),.rd_n(rd_n),.q(q),.qbar(qbar)); endmodulemodule SR_ms(s,r,clk,sd_n,rd_n,q,qbar);input s,r,clk,sd_n,rd_n;output q,qbar;wire q,qbar;wire clk_n;not (clk_n,clk);wire qm,qm_bar;//SR triger: master_slaveSR sr1(.s(s),.r(r),.cp(clk_n),.sd_n(sd_n),.rd_n(rd_n),.q(qm),.qbar(qm_bar));SR sr2(.s(qm),.r(qm_bar),.cp(clk),.sd_n(sd_n),.rd_n(rd_n),.q(q),.qbar(qbar));endmodule//SR trigermodule SR(s,r,cp,sd_n,rd_n,q,qbar);input s,r,cp,sd_n,rd_n;output q,qbar;wire x1,x2;assign x1 = ~(r&cp&sd_n);assign x2 = ~(s&cp&rd_n);assign qbar = ~(q&x1&rd_n);assign q = ~(qbar&x2&sd_n);endmodule综合后RTL视图:③行为描述module updown_count(d,clk,clear,load,up_down,qd);input[7:0] d;input clk,clear,load,up_down;output[7:0] qd;reg[7:0] cnt;assign qd=cnt;always @ (posedge clk)beginif(!clear)cnt = 8'h00; //clear,low enableelse if(load)cnt = d; //set,high enableelse if(up_down)cnt = cnt+1; //countelsecnt=cnt-1; //discountendendmodule综合后RTL视图:功能模块设计1.十进制计数器设计设计一个带同步复位的十进制计数器,编辑波形激励文件测试程序。