S-100-3中文资料

OC-3中文资料

OC-3中⽂资料Headquarters :No. 669, Sec. 4 Chung Hsing RoadFeaturesCompliant with 155 Mbps ATM and SONET OC-3SDH STM-1 (S1.1) Industry standard 1×9 footprint SC duplex connector Single power supply 3.3 VDifferential LVPECL inputs and outputsCompatible with solder and aqueous wash processes Class 1 laser product complies with EN 60825-1 DescriptionThe TS3-0155-32S-P1-X transceivers utilizing 1310 nm MQW laser diodes are fully compliance to the 155 Mbps ATM and SONET OC-3 SDH STM-1 standard, anddesigned in industry standard 1×9 package with SC duplex connector. The transmitter section is a class 1 laser which is compliant to International Safety Standard EN 60825-1.Ordering InformationPART NUMBER INPUT/OUTPUTSIGNAL DETECTVOLTAGE TEMPERATURE TS3-0155-32S-P1 DC/DC LVPECL 3.3 V 0°C to 70 °C TS3-0155-32S-P1-E DC/DC LVPECL3.3 V40°C to 85°CAbsolute Maximum RatingsPARAMETER SYMBOL MIN MAX UNITS NOTEStorage Temperature T S ?40 85°CSupply V oltage Vcc ?0.5 6.0 V Input V oltage V IN ?0.5Vcc VOutput Current I o --- 50 mA Operating Current I OP --- 400 mA Soldering Temperature T SOLD--- 260 °C10 seconds on leadsHeadquarters :No. 669, Sec. 4 Chung Hsing RoadOperating EnvironmentPARAMETER SYMBOL MIN MAX UNITS NOTEAmbient Operating Temperature(TS3-0155-32S-P1)T AMB 0 70°C Ambient Operating Temperature (TS3-0155-32S-P1-E) T AMB ?40 85°CSupply V oltageVcc3.1 3.5 VTransmitter Electro-optical Characteristics(Vcc = 3.1 V to 3.5 V , TS3-0155-32S-P1: T A = 0°C to 70°C, TS3-0155-32S-P1-E: T A = ?40°C to 85°C)PARAMETER SYMBOL MIN TYP . MAX UNITS NOTEData RateB 50 155 200 Mb/sOutput Optical Power 9/125 µm fiber Pout ?15---8dBm AverageExtinction Ratio ER8.2 --- --- dB Center Wavelength λC 1261 1310 1360 nm Spectral Width (RMS) ?λ --- --- 4 nm Rise/Fall Time (10?90%) T r , f --- 1 2 nsOutput EyeCompliant with Telcordia GR-253-CORE Issue 3 and ITU-T recommendation G-957Power Supply Current I CC --- --- 140 mA Note 1 Data Input Current-Low I IL ?350--- --- µAData Input Current-HighI IH --- --- 350 µATransmitter Data Input V oltage-High V IH ? V CC ?1.1 --- ?0.74 V Note 2 Transmitter Data Input V oltage-LowV IL ? V CC2.0---1.58V Note 2Transmitter Data Input DifferentialV oltage V DIFF 0.3 --- 1.6 VNote 2Note 1: Not including the terminations.Note 2: These inputs are compatible with 10K, 10KH and 100K ECL and PECL input.Headquarters :No. 669, Sec. 4 Chung Hsing RoadReceiver Electro-optical Characteristics(Vcc = 3.1 V to 3.5 V , TS3-0155-32S-P1: T A = 0°C to 70°C, TS3-0155-32S-P1-E: T A = ?40°C to 85°C)PARAMETER SYMBOLMIN TYP . MAX UNITS NOTE Data RateB 50 155 200 Mb/sOptical Input Power-maximum P IN 0 --- --- dBm Note 1 Optical Input Power-minimum (Sensitivity)P IN--- --- ?34dBm Note 1Operating Center Wavelength λC 1100 --- 1600 nmSignal Detect-Asserted P A --- --- ?34 dBm AverageSignal Detect-Deasserted P D ?47--- --- dBm AverageSignal Detect-Hysteresis P A ? P D 1.0 --- --- dB Signal Detect Assert Time T SD + --- --- 100 µs Signal Detect Desssert Time T SD ? --- --- 100 µsSignal Detect Output voltage-High V OH ? V CC ?1.1 --- ?0.74 V Note 2 Signal Detect Output voltage-Low V OL ? V CC2.0---1.58V Note 2Power Supply CurrentI CC --- --- 100 mA Note 3 Data Output Rise, Fall Time (10?90%) T r, f --- 1 2 nsData Output V oltage-High V OH ? V CC ?1.1 --- ?0.74 V Note 2 Data Output V oltage-LowV OL ? V CC2.0---1.58V Note 2Note 1: The input data is at 155.52 Mbps, 223?1 PRBS data pattern with 72 “1”s and 72 “0”s inserted per the ITU-T recommendation G .958 Appendix 1. The receiver is guaranteed to provide output data with Bit Error Rate (BER) better than or equal to 1×10?10.Note 2: These outputs are compatible with 10K, 10KH and 100K ECL and PECL input. Note 3: The current exclude the output load current.Headquarters :No. 669, Sec. 4 Chung Hsing RoadTransmitter SectionThe transmitter section consists of a 1310 nm InGaAsP laser in an eye safe optical subassembly (OSA) which mates to the fiber cable. The laser OSA is driven by a LD driver IC which converts differential input LVPECL logic signals into an analog laser driving current. Receiver SectionThe receiver utilizes an InGaAs PIN photodiode mounted together with a trans-impedance preamplifier IC in an OSA. This OSA is connected to a circuit providing post-amplification quantization, and optical signal detection. Receiver Signal DetectSignal Detect is a basic fiber failure indicator. This is a single-ended LVPECL output. As the input optical power is decreased, Signal Detect will switch from high to low (deassert point) somewhere between sensitivity and the no light input level. As the input optical power is increased from very low levels, Signal Detect will switch back from low to high (assert point). The assert level will be at least 1.0 dB higher than the deassert level.Headquarters :No. 669, Sec. 4 Chung Hsing RoadEye DiagramTransmitter ReceiverSignal pattern: PRBS 23Signal pattern: PRBS 23 Input Power: ?35 dBmHeadquarters :No. 669, Sec. 4 Chung Hsing RoadPIN SYMBOL DESCRIPTION1 RX GNDReceiver Signal Ground.Directly connect this pin to the receiver ground plane. 2 RD +RD+ is an open-emitter output circuit.Terminate this high-speed differential LVPECL output with standard LVPECL techniques at the follow-on device input pin. (See recommended circuit schematic) 3RD ?RD – is an open-emitter output circuit.Terminate this high-speed differential LVPECL output with standard LVPECL techniques at the follow-on device input pin. (See recommended circuit schematic) 4SDSignal Detect.Normal optical input levels to the receiver result in a logic “1” output, V OH , asserted. Low input optical levels to the receiver result in a fault condition indicated by a logic “0” output V OL , deasserted Signal Detect is a single-ended LVPECL output. SD can be terminated with LVPECL techniques via 50 ?toV CCR ? 2 V. Alternatively, SD can be loaded with a 180 ? resistor to RX GND to conserve electrical power with small compromise to signal quality. If Signal Detect output is not used, leave it open-circuited. This Signal Detect output can be used to drive a LVPECL input on an upstream circuit,such as, Signal Detect input or Loss of Signal-bar. 5 V CCR Receiver Power Supply.Provide +3.3 Vdc via the recommended receiver power supply filter circuit. Locate the power supplyfilter circuit as close as possible to the V CCR pin. 6 V CCT Transmitter Power Supply.Provide +3.3 Vdc via the recommended transmitter power supply filter circuit. Locate the power supplyfilter circuit as close as possible to the V CCT pin. 7 TD ?Transmitter Data In-Bar.Terminate this high-speed differential LVPECL input with standard LVPECL techniques at the transmitter input pin. (See recommended circuit schematic) 8 TD +Transmitter Data In.Terminate this high-speed differential LVPECL input with standard LVPECL techniques at the transmitter input pin. (See recommended circuit schematic) 9TX GND Transmitter Signal Ground.Directly connect this pin to the transmitter signal ground plane. Directly connect this pin to thetransmitter ground plane.Headquarters :No. 669, Sec. 4 Chung Hsing RoadIn order to get proper functionality, a recommended circuit is provided in above recommended circuit schematic. When designing the circuit interface, there are a few fundamental guidelines to follow.(1) The differential data lines should be treated as 50 ? Micro strip or strip line transmission lines. This will help to minimize the parasitic inductance and capacitance effects. Locate termination at the received signal end of the transmission line. The length of these lines should be kept short and of equal length.(2) For the high speed signal lines, differential signals should be used, not single-ended signals, and these differential signals need to be loaded symmetrically to prevent unbalanced currents which will cause distortion in the signal.(3) Multi layer plane PCB is best for distribution of V CC , returning ground currents, forming transmission lines and shielding, Also, it is important to suppress noise from influencing the fiber-optic transceiver performance, especially the receiver circuit. (4) A separate proper power supply filter circuits shown in Figure for the transmitter and receiver sections. These filter circuits suppress Vcc noise over a broad frequency range, this prevents receiver sensitivity degradation due to V CC noise. (5) Surface-mount components are recommended. Use ceramic bypass capacitors for the 0.1 µF capacitors and a surface-mount coil inductor for 1 µH inductor. Ferrite beads can be used to replace the coil inductors when using quieter V CC supplies, but a coil inductor is recommended over a ferrite bead. All power supply components need to be placed physically next to the V CC pins of the receiver and transmitter.(6) Use a good, uniform ground plane with a minimum number of holes to provide a low-inductance ground current return for the power supply currents.Headquarters :No. 669, Sec. 4 Chung Hsing Roadmust be completely remove from the module. The transceiver is supplied with a process plug to prevent contamination during wave solder and aqueous rinse as well as during handling, shipping or storage.Solder fluxes should be water-soluble, organic solder fluxes. Recommended cleaning and degreasing chemicals for these transceivers are alcohol’s (methyl, isopropyl, isobutyl), aliphatics (hexane, heptane) and other chemicals, such as soap solution or naphtha. Do not use partially halogenated hydrocarbons for cleaning/degreasing.Headquarters :No. 669, Sec. 4 Chung Hsing RoadHeadquarters :No. 669, Sec. 4 Chung Hsing RoadRegulatory ComplianceFEATURE TEST METHOD PERFORMANCEElectrostatic discharge (ESD) to the electrical pinsMIL-STD-883D Method 3015.7 Class 1(>1 kV) – Human Body Model Electromagnetic interference (EMI)FCC Class B EN55022 Class BThe transceiver is mounded on a circuit card without a chassis enclosure at frequencies up to 1000 MHz. Margins will be dependent on customer’s board and chassis designs.Immunity Variation of IEC801-3 Typically show no measurable effect from a 10 V/mfiled swept from 30 MHz to 1000 MHz applied tothe transceiver without a chassis enclosure.FDA 21 CFR 1040.10 and 1040.11 Class 1FDA Accession Number: 0012715-01Eye safetyEN 60825-1:1994+A11EN 60950: 1992+A1+A2+A3+A4+A11EN 60825-2: 1994+A1TUV certificated Number: R 3-50005227Note : All information contained in this document is subject to change without notice.。

100S-D中文资料

230 — — KF

240 T A KA

277 — T —

380… 400 N — —

415 B — —

440 G N —

480 — B —

500 M — —

550 C — —

600 — C —

Electronic Coil w/PLC Interface ➋ 100S-D95… 100S-D250 100S-D300… 100S-D420 100S-D630… 100S-D860

元器件交易网

Contactors & Control Relays

Safety Contactors

100S-D Specifications Conformity to Standards

IEC 60947-4 IEC 60947-4 Annex F IEC 60947 Type “2” Coordination CSA 22.2 No. 14 UL 508

V DC DC DC

24 EZJ — —

48…72 EZY EZY —

110…130 EZD EZD ED

ቤተ መጻሕፍቲ ባይዱ

200…255 EZA EZA EA

➊ The N.C. contacts meet IEC 60947-4 Annex F requirements to mirror contact performance. The N.C. mirror contacts are wired in series or parallel and must

V 50/60 Hz 50/60 Hz 50/60 Hz

24 EJ — —

42… 64 EY EY —

100 EP EP EP

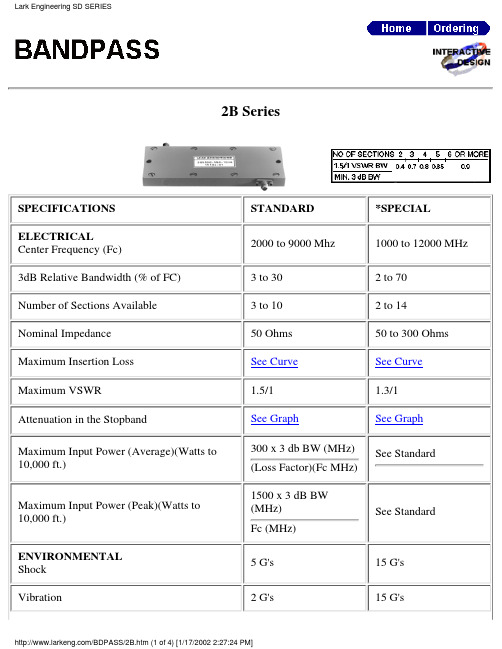

2Bxxxx-xxx-3BD中文资料

2B SeriesSPECIFICATIONS STANDARD *SPECIAL ELECTRICALCenter Frequency (Fc)2000 to 9000 Mhz 1000 to 12000 MHz 3dB Relative Bandwidth (% of FC) 3 to 30 2 to 70Number of Sections Available 3 to 10 2 to 14Nominal Impedance 50 Ohms 50 to 300 Ohms Maximum Insertion Loss See Curve See Curve Maximum VSWR 1.5/1 1.3/1Attenuation in the StopbandSee GraphSee Graph Maximum Input Power (Average)(Watts to 10,000 ft.)300 x 3 db BW (MHz)(Loss Factor)(Fc MHz)See StandardMaximum Input Power (Peak)(Watts to 10,000 ft.)1500 x 3 dB BW (MHz)Fc (MHz)See StandardENVIRONMENTAL Shock 5 G's 15 G's Vibration2 G's15 G'sHumidity90% relative100% relative Altitude Unlimited UnlimitedTemperature Range (Operating)-25 to + 50 degreescelsius-54 to + 100 degreescelsiusTemperature Range (Non-Operating)-54 to + 70 degreescelsius-62 to +150 degreescelsiusMECHANICALApproximate Weight in oz.1.7 x L x W 1.0 x L x WMounting Provisions See below Consult FactoryINSERTION LOSS:The Maximum Insertion Loss atcenter frequency is equal to :LF x (N + 0.5) / % 3 dB BW + 0.1Where:LF= Loss Factor, N= Number ofSections% 3dB BW:3dB BW (MHz) x 100divided byCenter Frequency (MHz)Example:A 5 section 2B with a centerfrequencey of 5000 MHz and a 3dBBW of 500 MHz would have,.08 x 5.5 /10 = 4.4 /10 = 0.44 + 0.1= 0.5 dbMECHANICAL SPECIFICATIONSL Dimension = 1.5 inch = (0.5 x No. of Sections) Approx.W Dimension = 2950 / Fc (MHz) + 0.6 inch Approx.Connectors Available On 2B Series:Lark Code Type C DIM.Inches & MM Lark Code Type C DIM.Inches & MM A SMA JACK .375 & 9.5*G N JACK .736 & 18.7BSMA PLUG.507 & 12.9*HN PLUG.819 & 20.8Lark Engineering SD SERIES元器件交易网*C TNC JACK .750 & 19.1S SPECIAL*D TNC PLUG.844 & 21.4* Not recommended for use with this SeriesThe size shown is a standard used by Lark to facilitate a low cost, easily reproducible unit. Should you require another size, please submit all of your requirements-both electrical and mechanical. This will enable Lark Engineering to quote theoptimum design for your application.Lark Engineering SD SERIES元器件交易网STOPBAND SPECIFICATIONSThe graphs on the following pages define the normal specification limits on attenuation Lark bandpass filter series 2B, 3B, and 4B. The minimum level of attenuation in dB is shown as a "number of 3dB bandwidths from centerfrequency".Since the frequency characteristics vary for differing bandwidths, it is necessary to establish specifications for each bandwidth of filter. The different graphs represent various 3dB percentage bandwidths. Intermediate values should be interpolated. The 3dB percentage bandwidth is defined as follows:3dB Bandwidth (MHz) x 100divided byCenter Frequency (MHz)The exact relationship is as follows:1. 3dB Bandwidths From Center Frequency= Rejection Frequency (Mhz) -Center Frequency (Mhz) divided by 3dB Bandwidth (Mhz)Example:Given:2. Center Frequency = 5000 MHz Minimum 3dB Bandwidth = 500 MHzNumber of Sections = 5Find: Minimum attenuation levels at 4250 MHz and 5800 MHz.3dB BW's from Fc = 4250 - 5000 / 500 = - 1.5and 5800 - 5000 / 500 = + 1.6The answer can be read directly from the 10% graph. Using the 5 section curve at the point -1.5 (4250 MHz) we find the minimum level of attenuation is 40dB.At +1.6 (5800 MHz) the minimum level of attenuation is 50dB.For special requirements, please contact our Application EngineeringDepartment.STOPSP3.HTM元器件交易网STOPBAND SPECIFICATIONSSTOPBAND SPECIFICATIONSSTOPSP3.HTM元器件交易网STOPBAND SPECIFICATIONS。

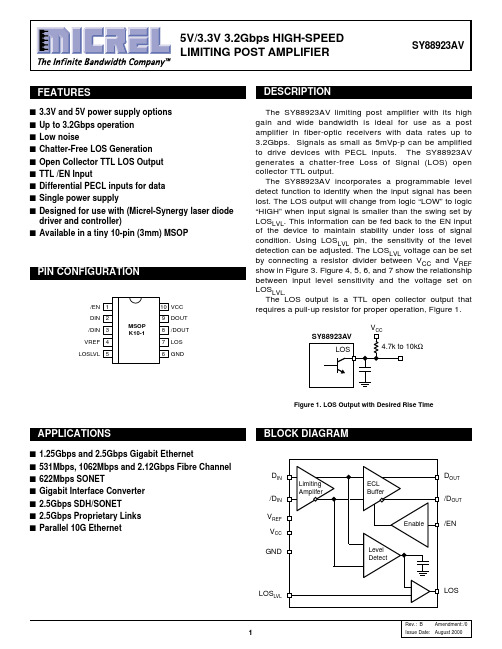

SY88923AV资料

s 3.3V and 5V power supply options s Up to 3.2Gbps operation s Low noises Chatter-Free LOS Generation s Open Collector TTL LOS Output s TTL /EN Inputs Differential PECL inputs for data s Single power supplysDesigned for use with (Micrel-Synergy laser diode driver and controller)s Available in a tiny 10-pin (3mm) MSOPThe SY88923AV limiting post amplifier with its high gain and wide bandwidth is ideal for use as a post amplifier in fiber-optic receivers with data rates up to 3.2Gbps. Signals as small as 5mVp-p can be amplified to drive devices with PECL inputs. The SY88923AV generates a chatter-free Loss of Signal (LOS) open collector TTL output.The SY88923AV incorporates a programmable level detect function to identify when the input signal has been lost. The LOS output will change from logic “LOW” to logic “HIGH” when input signal is smaller than the swing set by LOS LVL . This information can be fed back to the EN input of the device to maintain stability under loss of signal condition. Using LOS LVL pin, the sensitivity of the level detection can be adjusted. The LOS LVL voltage can be set by connecting a resistor divider between V CC and V REF show in Figure 3. Figure 4, 5, 6, and 7 show the relationship between input level sensitivity and the voltage set on LOS LVL.The LOS output is a TTL open collector output that requires a pull-up resistor for proper operation, Figure 1.s 1.25Gbps and 2.5Gbps Gigabit Ethernets 531Mbps, 1062Mbps and 2.12Gbps Fibre Channel s 622Mbps SONETs Gigabit Interface Converter s 2.5Gbps SDH/SONETs 2.5Gbps Proprietary Links sParallel 10G EthernetFigure 1. LOS Output with Desired Rise TimeΩV /EN DIN /DIN VREF LOSLVL VCC DOUT /DOUT LOS GNDGND/ENLOSD IN /D IN V REF V CC LOS LVLD OUT /D OUTMICREL-SYNERGY3250 SCOTT BOULEVARD SANTA CLARA CA 95054USA TEL + 1 (408) 980-9191 FAX + 1 (408) 914-7878 WEB This information is believed to be accurate and reliable, however no responsibility is assumed by Micrel for its use nor for any infringement of patents or other rights of third parties resulting from its use. No license is granted by implication or otherwise under any patent or patent right of Micrel Inc.© 2000 Micrel Incorporated。

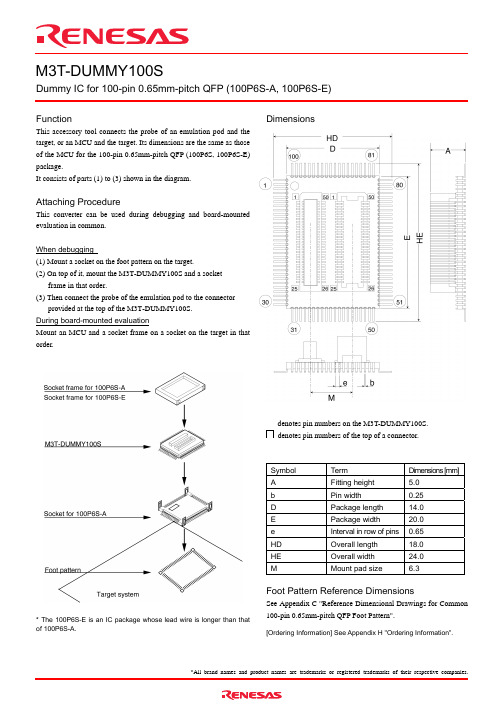

M3T-DUMMY100S中文资料

M3T-DUMMY100S

Dummy IC for 100-pin 0.65mm-pitch QFP (100P6S-A, 100P6S-E)

Function

This accessory tool connects the probe of an emulation pod and the target, or an MCU and the target. Its dimensions are the same as those of the MCU for the 100-pin 0.65mm-pitch QFP (100P6S, 100P6S-E) package. It consists of parts (1) to (3) shown in the diagram.

100-pin 0.65mm-pitch QFP Foot Pattern".

[Ordering Information] See Appendix H "Ordering Information".

*All brand names and product names are trademarks or registered trademarks of their respective companies.

Dimensions [mm] 5.0 0.25 14.0 20.0 0.65 18.0 24.0 6.3

Foot Pattern RefeБайду номын сангаасence Dimensions

See Appendix C "Reference Dimensional Drawings for Common

* The 100P6S-E is an IC package whose lead wire is longer than that of 100P6S-A.

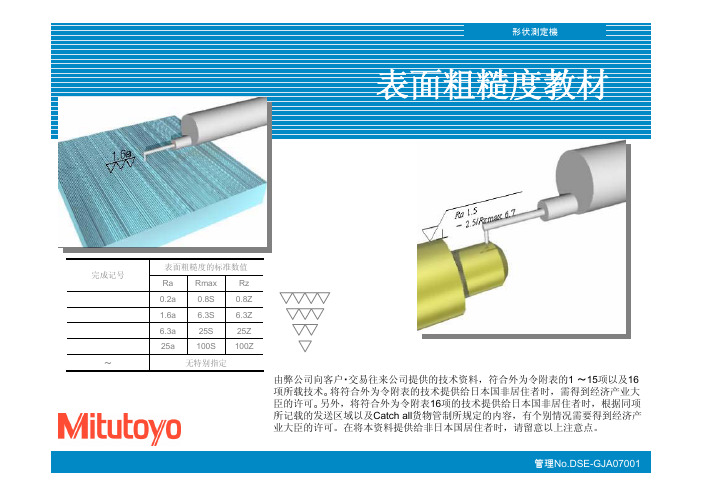

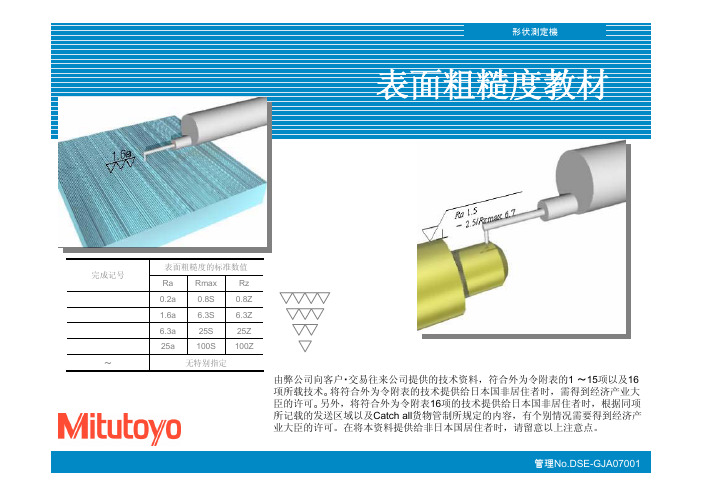

表面粗糙度学习资料 中文

表面粗糙度教材

完成记号 ~

表面粗糙度的标准数值

Ra

Rmax

Rz

0.2a

0.8S

0.8Z

1.6a

6.3S

6.3Z

6.3a

25S

25Z

25a

100S 100Z

无特别指定

由弊公司向客户・交易往来公司提供的技术资料,符合外为令附表的1 ~15项以及16 项所载技术。将符合外为令附表的技术提供给日本国非居住者时,需得到经济产业大 臣的许可。另外,将符合外为令附表16项的技术提供给日本国非居住者时,根据同项 所记载的发送区域以及Catch all货物管制所规定的内容,有个别情况需要得到经济产 业大臣的许可。在将本资料提供给非日本国居住者时,请留意以上注意点。

信息不全的图纸举例

100

φ 30.0 φ 30.0 φ 30.0

+0.2

φ30

-0.1

上・下面的真直度 如何

上・下面的平行度 如何

信息不全的图纸举例

适用的形体

公差的种类

记号

真直度的公差

单独形体

形状公差

平面度公差 真圆度公差 圆柱度公差

单独形体以及

线的轮廓度公差

关连形体

面的轮廓度公差

适用的形体 关连形体

9

最近与表面粗糙度有关的JIS

JIS B 0601:2001

(旧JIS B 0601:1994 表面粗糙度-定义及表示) 【改正】

产品几何量技术规范(GPS).表面结构:轮廓法.术语、定义和表面结构参数

ISO 4287:1997

Geometrical Product Specifications(GPS)-Surface texture: Profile method-Terms, definitions and surface texture

RSS100N03中文资料

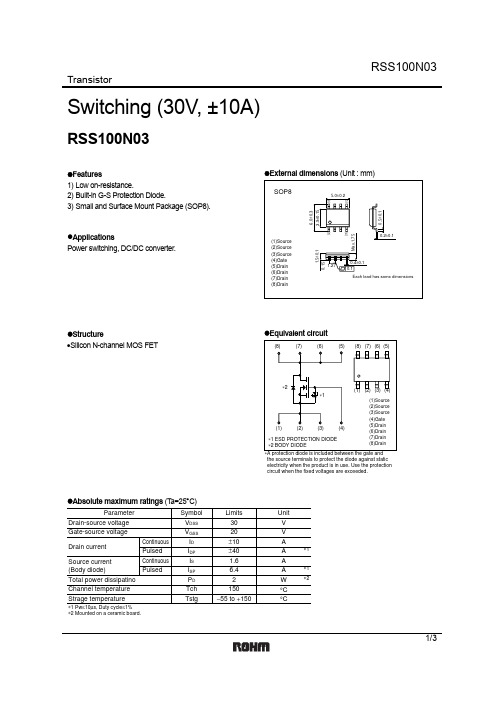

Transistor1/3Switching (30V, ±10A)RSS100N03z Features1) Low on-resistance.2) Built-in G-S Protection Diode.3) Small and Surface Mount Package (SOP8).z ApplicationsPower switching, DC/DC converter.z External dimensions (Unit : mm)z Structure•Silicon N-channel MOS FET z Equivalent circuitthe source terminals to protect the diode against static electricity when the product is in use. Use the protection circuit when the fixed voltages are exceeded.z Absolute maximum ratings (T a=25°C)∗1∗1∗2ParameterV V DSS Symbol 30V V GSS 20A I D ±10A I DP ±40A I S 1.6A I SP 6.4W P D 2°C Tch 150°CTstg −55 to +150Limits Unit Drain-source voltage Gate-source voltage Drain current Total power dissipatino Channel temperature Strage temperatureContinuous Pulsed Continuous Source current (Body diode)Pulsed∗1 Pw ≤10µs, Duty cycle ≤1%∗2 Mounted on a ceramic board.Transistor2/3z Thermal resistance (T a=25°C)°C / WRth (ch-a)62.5ParameterSymbol Limits Unit Channel to ambient∗ Mounted on a ceramic board.∗z Electrical characteristics (T a=25°C)z Body diode characteristics (Source-Drain Characteristics) (T a=25°C)Forward voltageV SD −− 1.2V I S=6.4A, V GS =0VParameterSymbol Min.Typ.Max.Unit Conditions∗Pulsed∗z Electrical characteristic curvesDRAIN-SOURCE VOLTAGE : V DS (V)C A P A C I T A N C E : C (p F )Fig.1 Typical Capacitancevs. Drain-Source VoltageDRAIN CURRENT : I D (A)S W I T C H I N G T I M E : t (n s )Fig.2 Switching CharacteristicsTOTAL GATE CHARGE : Qg (nC)G A T E -S O U R C E V O L T A G E : V G S (V )Fig.3 Dynamic Input CharacteristicsTransistor3/3GATE-SOURCE VOLTAGE : V GS (V)D R A I N C U R RE N T : I D (A )Fig.4 Typical Transfer CharacteristicsGATE-SOURCE VOLTAGE : V GS (V)S T A T I C D R A I N -S O U R C E O N -S T A T E R E S I S T A N C E : R D S (o n ) (m Ω)Fig.5 Static Drain-SourceOn-State Resistance vs. Gate-Source VoltageSOURCE-DRAIN VOLTAGE : V SD (V)S O U R C E C U R R E N T : I s (A )Fig.6 Source Current vs.Source-Drain VoltageDRAIN CURRENT : I D (A)1101001000S T A T I C D R A I N -S O U R C E O N -S T A T E R E S I S TA N C E : R D S (o n ) (m Ω)Fig.7 Static Drain-SourceOn-State Resistance vs. Drain Current (Ι)DRAIN CURRENT : I D (A)S T A T I C D R A I N -S O U R C E O N -S T A T E R E S I S T A N C E : R D S (o n ) (m Ω)Fig.8 Static Drain-SourceOn-State Resistance vs. Drain Current (ΙΙ)DRAIN CURRENT : I D (A)S T A T I C D R A I N -S O U R C E O N -S T A T E R E S I S T A N C E : R D S (o n ) (m Ω)Fig.9 Static Drain-SourceOn-State Resistance vs. Drain Current (ΙΙΙ)AppendixAbout Export Control Order in JapanProducts described herein are the objects of controlled goods in Annex 1 (Item 16) of Export Trade ControlOrder in Japan.In case of export from Japan, please confirm if it applies to "objective" criteria or an "informed" (by MITI clause)on the basis of "catch all controls for Non-Proliferation of Weapons of Mass Destruction.Appendix1-Rev1.0。

HQxxxx-xxx-3AA中文资料

HQ SeriesSPECIFICATIONS STANDARD*SPECIAL ELECTRICALCenter Frequency (Fc)100 to 1000 Mhz80 to 1400 MHz 3dB Relative Bandwidth (% of FC) 4 to 40 4 to 50 Number of Sections Available 3 to 8 2 to 10 Nominal Impedance50 Ohms50 to 75 Ohms Maximum Insertion Loss See Curve See Curve Maximum VSWR 1.5/1 1.3/1 Attenuation in the Stopband See Graph See GraphMaximum Input Power (Average)(Watts to10,000 ft.)500 x 3dB BW (MHz)(Loss Factor)(Fc MHz)See StandardMaximum Input Power (Peak)(Watts to10,000 ft.)300 x 3dB BW (MHz)Fc (MHz)2,000ENVIRONMENTALShock15 G's25 G's Vibration 5 G's10 G's Humidity90% relative100% relativeINSERTION LOSS:The Maximum Insertion Loss at center frequency is equal to :LF x (N + 0.5) / % 3 dB BW + 0.2 Where:LF= Loss Factor, N= Number of Sections% 3dB BW:3dB BW (MHz) x 100divided byCenter Frequency (MHz) Example:A 3 section HQ with a center frequency of 400 MHz and a 3dB BW of 40 MHz would have,1.5 x 3.5 / 10 = 5.25 / 10 = 0.525 0.525 + 0.2 = 0.8 dBConnectors Available on HQ Series:Lark Code Type C DIM.Inches & MMLarkCodeType C DIM.Inches & MMA SMA JACK.800 & 20.3G N JACK 1.625 & 41.3B SMA PLUG.855 & 22.5H N PLUG 1.585 & 40.3C TNC JACK 1.350 & 34.3L SOLDER MPINAXIAL.625 & 15.9D TNC PLUG 1.280 & 32.5*M SOLDER PINRADIAL.625 & 15.9E BNC JACK 1.350 & 34.3S SPECIALF BNC PLUG 1.280 & 32.5*Not recommended for use with this series.LENGTH:The approximate length of a Lark HQ series filter can be determined by the formula:( 0.5 N + 2 / %BW ) x LC = LWhere N is the number of sections used, % BW is:3dB BW (MHz) x 100divided byCENTER FREQUENCY (MHz)LC is the length constant at the specified center frequency, L is the dimension between theconnectors; C1 and C2 are the connector lengths as shown above. All of the length information given here is approximate. Exact length specifications must be quoted by the factory. If a special length is needed,please submit all of your requirements - both electrical and mechanical. This will enable Lark Engineering to quote the optimum design for your application.Example:A 3 section HQ with a center frequency of 400 MHz a 3dB BW of 40 MHz and SMA jack input and output connectors would be:(1.5 + 0.2) x 1.38 = 2.35 + C1 + C2In most cases, the L dimension is rounded to the nearest 1/4 inch which in this instance would be 2.25inches and the O.A.L. is:2.25 + .800 + .800 =3.85 inches.To convert inches to millimeters multiply x 25.40.Lark Engineering HQ SERIES元器件交易网STOPBAND ATTENUATIONThe graph on the following pages defines the normal specification limits on attenuation Lark bandpass filter series HP, HQ, SF, and SM. The minimum level of attenuation in dB is shown as a "number of 3dB bandwidths from center frequency".Since the frequency characteristics vary for differing bandwidths, it is necessary to establishspecifications for each bandwidth of filter. The different graphs represent various 3dB percentage bandwidths. Intermediate values should be interpolated. The 3dB percentage bandwidth is defined asfollows:STOPATT5.HTM元器件交易网As the 3dB bandwidth is exactly 10% of the center frequency, the answer can be read directly from the 10% graph. Using the 5 section curve at the point -1.5 (255 MHz) we find the minimum level of attenuation is 36dB. At +1.6 (348 MHz) the minimum level of attenuation is 48dB.For special requirements, please contact our Application Engineering Department.STOPBAND ATTENUATIONSTOPBAND ATTENUATIONSTOPATT5.HTM元器件交易网STOPBAND ATTENUATIONSTOPBAND ATTENUATIONSTOPBAND ATTENUATION。

SMP100-xxxH225中文资料

®

SMP100-xxx SMP100-xxxH225

TRISIL TM

FEATURES BIDIRECTIONAL CROWBAR PROTECTION VOLTAGE RANGE : FROM 8V to 320V REPETITIVE PEAK PULSE CURRENT: IPP = 100 A (10/1000 µs) HOLDING CURRENT: IH = 150mA or 225mA LOW LEAKAGE CURRENT: IR = 2 µA max DESCRIPTION The SMP100 series are transient surge arrestors used for the protection of sensitive telecom equipment. MAIN APPLICATIONS Any sensitive equipment requiring protection against lightning strikes : ANALOG AND DIGITAL LINE CARDS MAIN DISTRIBUTION FRAMES TERMINALS AND TRANSMISSION EQUIPMENT GAS-TUBE REPLACEMENT BENEFITS NO AGEING AND NO NOISE IF DESTROYED, THE SMP100 FALLS INTO SHORT CIRCUIT,STILLENSURINGPROTECTION BOARD SPACE SAVING COMPLIES WITH THE FOLLOWING STANDARDS: CCITT K20 VDE0433 VDE0878 IEC-1000-4-5 FCC Part 68, lightning surge type A FCC Part 68, lightning surge type B BELLCORE TR-NWT-001089 First level BELLCORE TR-NWT-001089 Second level CNET l31-24

S-350-5中文资料

SPECIFICATIONMODELDC VOLTAGERATED CURRENTCURRENT RANGERATED POWER OUTPUT VOLTAGE ADJ. RANGELINE REGULATIONLOAD REGULATIONSETUP, RISE TIMEHOLD UP TIME(Typ.)VOLTAGE RANGEFREQUENCY RANGEEFFICIENCY(Typ.) INPUTINRUSH CURRENT(Typ.)LEAKAGE CURRENTSAFETY& EMC WITHSTAND VOLTAGE ISOLATION RESISTANCE WORKING TEMP. WORKING HUMIDITY STORAGE TEMP., HUMIDITY TEMP. COEFFICIENT VIBRATIONMTBFDIMENSIONOTHERSNOTE PACKINGOVERLOADOVER VOLTAGEAC CURRENT(Typ.)200ms, 50ms at full load20ms at full load90 ~ 132VAC / 180 ~ 264VAC by switch 254 ~ 370VDC47 ~ 63Hz73%76%74%79%78%81%82%83%83%6.5A/115VAC 4A/230VAC50A/115VAC 50A/230VAC<3.5mA/ 240VAC105 ~ 135%rated output power5.75 ~6.75V9.4 ~ 10.9V13.8 ~ 16.2V15.5 ~ 18.2V18 ~ 21V27.6 ~ 32.4V33.7 ~ 39.2V40.5 ~ 46.5V57.6 ~ 67.2VProtection type :Constant current limiting, recovers automatically after fault condition is removedProtection type :Hiccup mode, recovers automatically after fault condition is removedI/P-O/P:1.5KVAC I/P-FG:1.5KVAC O/P-FG:0.5KVACI/P-O/P, I/P-FG, O/P-FG:100M Ohms/500VDC-10 ~ +60(Refer to output load derating curve)20 ~ 90% RH non-condensingRTH355FAN ON,45FAN OFF,80output shutdown (5 ~ 7.5V)RTH365FAN ON,55FAN OFF,80output shutdown (12 ~ 15V)RTH370FAN ON,60FAN OFF,85output shutdown (24 ~ 48V)-20 ~ +85, 10 ~ 95% RH0.03%/(0 ~ 5010 ~ 500Hz, 2G 10min./1cycle, 60min. each along X,Y, Z axes234.3K hrs min. MIL-HDBK-217F (25)215*115*50mm (L*W*H)1.07Kg; 12pcs/13.5Kg/0.92CUFT1. All parameters NOT specially mentioned are measured at 230VAC input, rated load and 25of ambient temperature.2. Ripple & noise are measured at 20MHz of bandwidth by using a 12" twisted pair-wire terminated with a 0.1uf & 47uf parallel capacitor.3. Tolerance : includes set up tolerance, line regulation and load regulation.5V7.5V12V13.5V15V24V27V36V48V50A40A29A25.8A23.2A14.6A13A9.7A7.3A0 ~ 50A0 ~ 40A0 ~ 29A0 ~ 25.8A0 ~ 23.2A0 ~ 14.6A0 ~ 13A0 ~ 9.7A0 ~ 7.3A250W300W348W348.3W348W350.4W351W349.2W350.4W150mVp-p150mVp-p150mVp-p150mVp-p150mVp-p150mVp-p200mVp-p240mVp-p240mVp-p4.5 ~5.6V6 ~ 9V10 ~ 13.2V12 ~ 15V13.5 ~ 18V20 ~ 26.4V26 ~ 32V32 ~ 40V41 ~ 56V2.0% 2.0% 1.0% 1.0% 1.0% 1.0% 1.0% 1.0% 1.0%0.5%0.5%0.5%0.5%0.5%0.5%0.5%0.5%0.5%1.0% 1.0%0.5%0.5%0.5%0.5%0.5%0.5%0.5%AC input range selectable by switchProtections: Short circuit / Overload / Over voltageForced air cooling by built-in DC fanPWM control and regulatedBuilt-in cooling Fan ON-OFF control100% full load burn-in testFixed switching frequency at 25KHzLow cost1 year warrantyFeatures :RIPPLE & NOISE (max.)Note.2VOLTAGE TOLERANCE Note.3PROTECTION ENVIRONMENTS-350-5S-350-7.5S-350-12S-350-13.5S-350-15S-350-24S-350-27S-350-36S-350-48 FAN ON/OFF CONTROLFUNCTIONMechanical SpecificationDerating Curve Static Characteristics (24V)Case No. 912C Unit:mmAMBIENT TEMPERATURE ()INPUT VOLTAGE (VAC) 60HzL O A D (%)20406080100-100102030405060(HORIZONTAL)S-350-24~48VS-350-5~15V8016085170901809519010020010521011022011523012024012525013026030032250282002415020100165012258O U T P U T V O L T A G E (V )O U T P U T R I P P L E (m V p -p )Ta=25fosc : 25KHzBlock DiagramEMI FILTERRECTIFIERS&FILTERPOWER SWITCHINGCONTROLON/OFF FAN FANI/PFG230115FILTER&RECTIFIERS+V -VDRIVERPWM CONTROLO.C.P.O.V.P.Terminal Pin No.AssignmentPin No.Pin No.14~6327~9Assignment Assignment AC/L DC OUTPUT -V FGAC/N DC OUTPUT +VAir flow direction117.521532.532.527.58281534671359.596-M4 L=6mm5025150C L5-M3 L=3mm154-M4 L=5mm 177.515047.536.55050.5101159532.51612 max.+V ADJ.LED。

S-100中文资料

SPECIFICATIONS-100-3S-100-5S-100-7.5S-100-10S-100-12S-100-15S-100-18S-100-24S-100-27S-100-36S-100-48MODELDC VOLTAGE RATED CURRENT CURRENT RANGE RATED POWEROUTPUTVOLTAGE ADJ. RANGE LINE REGULATION LOAD REGULATION SETUP, RISE TIME HOLD UP TIME (Typ.)VOLTAGE RANGE FREQUENCY RANGEEFFICIENCY (Typ.)INPUTINRUSH CURRENT (Typ.)LEAKAGE CURRENTSAFETY STANDARDSSAFETY &EMCWORKING TEMP.WORKING HUMIDITYSTORAGE TEMP., HUMIDITYTEMP. COEFFICIENTVIBRATIONMTBFDIMENSION OTHERSNOTEPACKINGOVERLOADAC CURRENT (Typ.)3V 5V 7.5V 10V 12V 15V 18V 24V 27V 36V 48V 20A 20A 13.6A 10A 8.5A 6.7A 5.6A 4.5A 3.7A 2.7A 2A 0 ~ 20A 0 ~ 20A 0 ~ 13.6A 0 ~ 10A0 ~ 8.5A 0 ~ 6.7A 0 ~ 5.6A 0 ~ 4.5A 0 ~ 3.7A 0 ~ 2.7A 0 ~ 2A 60W100W102W100W102W100.5W100.8W108W99.9W97.2W96W100mVp-p 100mVp-p 100mVp-p 100mVp-p 100mVp-p 100mVp-p 100mVp-p 100mVp-p 100mVp-p 100mVp-p 100mVp-p 2.85 ~ 3.3V 4.75 ~ 5.5V 6.75 ~ 8.25V 9 ~ 11V 10.8 ~ 13.2V 13.5 ~ 16.5V 16.2 ~ 19.8V 21.6 ~ 26.4V 26 ~ 32V 32.4 ~ 39.6V 43.2 ~ 52.8V2.0% 2.0% 1.0% 1.0%1.0% 1.0% 1.0% 1.0% 1.0% 1.0% 1.0%0.5%0.5%0.5%0.3%0.3%0.3%0.3%0.3%0.3%0.3%0.3%0.2%0.2%0.2%0.2%0.5%0.5%0.5%0.2%0.2%0.2%0.2%200ms, 80ms at full load 24ms at full load85 ~ 132VAC/180 ~ 264VAC selected by switch 255 ~ 370VDC 47 ~ 63Hz 70%78%80%80%81%81%82%84%84%84%84%1.9A/115VAC 0.96A/230VACCOLD START 27A/115VAC 54A/230VAC <1mA / 240VAC105 ~ 150%rated output power (130 ~ 180% of rated output power for S-100-5, S-100-36 ; 150 ~ 200% of rated output power for S-100-7.5 )Protection type : Shut down o/p voltage, re-power on to recover Design refer to UL1012-10 ~ +60(Refer to output load derating curve)20 ~ 90% RH non-condensing-20 ~ +85, 10 ~ 95% RH0.03%/(0 ~ 5010 ~ 500Hz, 2G 10min./1cycle, 60min. each along X,Y, Z axes 322.4K hrs min. MIL-HDBK-217F (25)199*98*38mm (L*W*H)0.62Kg; 20pcs/13.6Kg/0.8CUFT1. All parameters NOT specially mentioned are measured at 230VAC input, rated load and 25of ambient temperature.2. Ripple & noise are measured at 20MHz of bandwidth by using a 12" twisted pair-wire terminated with a 0.1uf & 47uf parallel capacitor.3. Tolerance : includes set up tolerance, line regulation and load regulation.Design refer to FCC Part15 J Conduction Class BAC input range selectable by switch Protections: Short circuit / Overload Cooling by free air convection 100% full load burn-in testFixed switching frequency at 25KHz Low cost High reliability 1 year warrantyFeatures :RIPPLE & NOISE (max.)Note.2VOLTAGE TOLERANCE Note.3EMI CONDUCTION & RADIATION ENVIRONMENT PROTECTION WITHSTAND VOLTAGEISOLATION RESISTANCE I/P-O/P:1.5KVAC I/P-FG:1.5KVAC O/P-FG:0.5KVACI/P-O/P, I/P-FG, O/P-FG:100M Ohms/500VDCMechanical SpecificationDerating CurveStatic Characteristics (24V)Case No. 902 Unit:mmAMBIENT TEMPERATURE ()INPUT VOLTAGE (V) 60HzO U T P U T V O L T A G E (V )O U T P U T R I P P L E (m V p -p )(HORIZONTAL)(VERTICAL)-10-1000102030405045605520406080100L O A D (%)S-100-7.5S-100-3.3,5S-100-12~48801608517090951801001901052001102101152201202301252402501302602832242016128Ta=2550100200150250300350Block Diagramfosc : 25KHzEMI FILTER RECTIFIERS230115&FILTERPOWER SWITCHINGFILTER&RECTIFIERS+V -VI/PFGDRIVERPWM CONTROLO.C.P.Terminal Pin No.AssignmentPin No.Pin No.124,536,7Assignment Assignment DC OUTPUT -V DC OUTPUT +VFGAC/L AC/N 3.59919776.5190221574.57654328.2112019957.5129.58085.5983.54-M33.5189.5183-M33.528.538。

AVS10CB-AVS10CBI-AVS100CB中文资料

0.89 Vreg

4.6

V

0.7 Vreg

0.3 Vreg

650

mV

+ 10

µA

VSWON (pin 8)

Low Threshold of Trip Point (switching-on of triac triggering) (3)

VSWOFF (pin 8)

High Threshold of Trip Point (switching-off of triac triggering) (3)

Min. - 12 VSS - 0.5 - 40 - 60

0

Max. 0.5 0.5 + 40 + 150 + 70

TRIAC AVS10CB / AVS10CBI / AVS100CB Tj = +25°C (unless otherwise specified)

Symbol

Parameter

VDRM

ITM = 11A (tp = 10ms, Tj = 25°C)

VDRM rated Gate open

Tj = 25°C AVS10/AVS100 Tj = 110°C AVS10 Tj = 700°C AVS100

Min. 0.2

Max.

Unit

V

1.75

V

10

µA

500

µA

500

µA

CONTROLLER AVS2ACP08 Toper = 25°C (unless otherwise specified)

TRIAC

.HIGH EFFICIENCY AND SAFETY SWITCHING .UNINSULATED PACKAGE :

SM-3中文资料

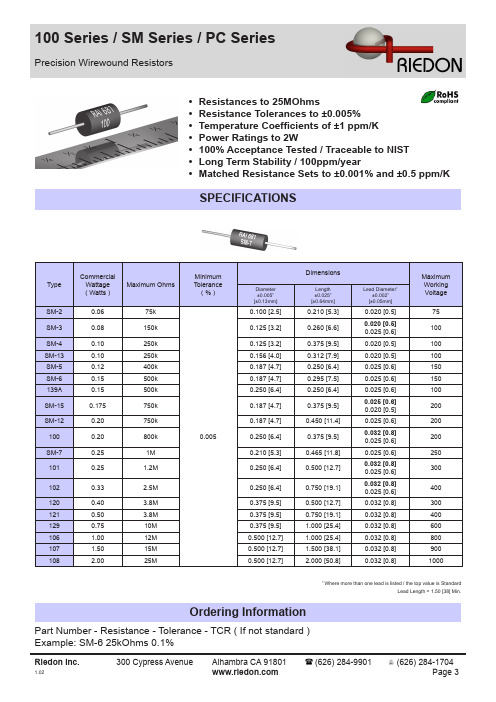

SM-2 SM-3 SM-4 SM-13 SM-5 SM-6 139A SM-15 SM-12 100 SM-7 101 102 120 121 129 106 107 108

75k 150k 250k 250k 400k 500k 500k 750k 750k 800k 1M 1.2M 2.5M 3.8M 3.8M 10M 12M 15M 25M 0.005

SM-8 SM-9 SP5086 SP5232

0.140 [3.6] 0.150 [3.8] 0.102 [2.6] 0.160 [4.1]

0.250 [6.4] 0.270 [6.9] 0.320 [8.1] 0.525 [13.3]

0.270 [6.9] 0.540 [13.7] 0.300 [7.6] 0.585 [14.9]

Diameter ±0.005” [±0.13mm] Length ±0.025” [±0.64mm] Lead Diameter ±0.002” [±0.05mm]

1

Lead Spacing ±0.015” [±0.4mm]

Maximum Working Voltage 150 150 150 150 300 400

SPECIFICATIONS

Type

Commercial Wattage ( Watts ) 0.06 0.08 0.10 0.10 0.12 0.15 0.15 0.175 0.20 0.20 0.25 0.25 0.33 0.40 0.50 0.75 1.00 1.50 2.00

Maximum Ohms

100PC 130PC 131PC 101PC 120PC 104PC

0.250 [6.4] 0.250 [6.4] 0.250 [6.4] 0.250 [6.4] 0.375 [9.5] 0.500 [12.7]

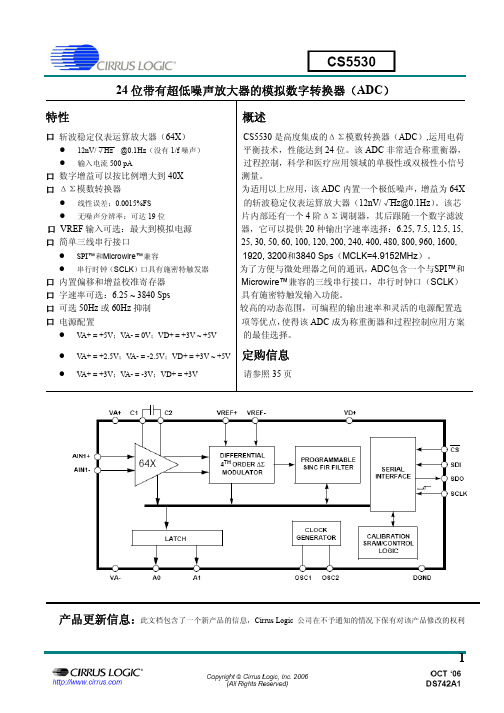

CS5530中文资料

表面粗糙度学习资料 中文

parameters

JIS B0632:2001

【制定】

产品几何量技术规范 ( GPS) –表面结构:轮廓法.相位校正过滤器的计量特征

ISO 11562:1996

Geometrical Product Specifications(GPS)-Surface texture: Profile method-Metrological characteristics of phase

JIS B 0659-1:2002

【制定】

产品几何量技术规范(GPS).表面结构:轮廓法.测量标准.第1部分:标准片

ISO 5436-1:2000

Geometrical Product Specifications(GPS)-Surface texture: Profile method;Measurement standards Part1: Material measures

6

什么是表面粗糙度

• 物体的表面,通常用光滑或者粗糙等来表示其各种凹凸。

• 在工业产品上这种不规则的凹凸会给外观品质,产品寿命,机械效率 等各种性能带来影响,将这些粗糙以及光滑的程度明确地数值化的就 是粗糙度。

1.6a

研削 Ra1.6

JIS B601:1970

JIS B0031:2003

表面结构的图案表示

姿势公差 位置公差 跳动公差

公差的种类

记号

平行度公差

直角度公差

倾斜度公差

位置度公差

同轴度公差以及同心度公差

对称度公差

圆周跳动公差

全跳动公差

φB φA

外侧圆柱φA的轴心位置

内侧圆柱φB的轴心位置

外侧圆柱φA的轴线 内侧圆柱φB的轴线

S-1131资料

Rev.3.0_01

HIGH RIPPLE-REJECTION LOW DROPOUT MIDDLE OUTPUT CURRENT CMOS VOLTAGE REGULATOR

S-1131 Series

The S-1131 Series is a positive voltage regulator with a low dropout voltage, high output voltage accuracy, and low current consumption developed based on CMOS technology. A built-in low on-resistance transistor provides a low dropout voltage and large output current, and a built-in overcurrent protector prevents the load current from exceeding the current capacitance of the output transistor. An ON/OFF circuit ensures a long battery life, and small SOT-89-3, SOT-89-5 and 6-Pin HSON(A) packages realize high-density mounting.

*1. Attention should be paid to the power dissipation of the package when the output current is large.

Applications

• Power supply for DVD and CD-ROM drives • Power supply for battery-powered devices • Power supply for personal communication devices • Power supply for note PCs

AQY214S中文资料

Footprint

Approx. 70%

2. Tape and reel

The device comes standard in a tape and reel (1,000 pcs./reel) to facilitate automatic insertion machines.

3. Controls low-level analog signals PhotoMOS relays feature extremely low closed-circuit offset voltage to enable control of low-level analog signals without distortion. 4. Low-level off state leakage current In contrast to the SSR with an off state leakage current of several milliamperes, the PhotoMOS relay features a very small off state leakage current of typ. 100 pA (AQY214S) even with the rated load voltage of 400 V.

3.0

2.5

2.0

1.5

AQY212S

DS2482S-100+中文资料

General DescriptionThe DS2482-100 is an I 2C-to-1-Wire ®bridge device that interfaces directly to standard (100kHz max) or fast (400kHz max) I 2C masters to perform bidirectional pro-tocol conversion between the I 2C master and any downstream 1-Wire slave devices. Relative to any attached 1-Wire slave device, the DS2482-100 is a 1-Wire master. Internal, factory-trimmed timers relieve the system host processor from generating time-critical 1-Wire waveforms, supporting both standard and over-drive 1-Wire communication speeds. To optimize 1-Wire waveform generation, the DS2482-100 performs slew-rate control on rising and falling 1-Wire edges and provides additional programmable features to match drive characteristics to the 1-Wire slave environment.Programmable, strong pullup features support 1-Wire power delivery to 1-Wire devices such as EEPROMs and sensors. The DS2482-100 combines these features with an output to control an external MOSF ET for enhanced strong pullup application. The I 2C slave address assignment is controlled by two binary address inputs, resolving potential conflicts with other I 2C slave devices in the system.ApplicationsFeatures♦I 2C Host Interface Supports 100kHz and 400kHz I 2C Communication Speeds♦1-Wire Master IO with Selectable Active or Passive 1-Wire Pullup♦Provides Reset/Presence, 8-Bit, Single-Bit, and 3-Bit 1-Wire IO Sequences♦Standard and Overdrive 1-Wire Communication Speeds♦Slew-Controlled 1-Wire Edges♦Selectable 1-Wire Slave Presence-Pulse Falling Edge Masking to Control Fast Edges on the 1-Wire Line♦Strong 1-Wire Pullup Provided by an Internal Low-Impedance Signal Path♦PCTLZ Output to Optionally Control an External MOSFET for Stronger Pullup Requirements♦Two Address Inputs for I 2C Address Assignment ♦Operating Range: 2.9V to 5.5V, -40°C to +85°C ♦8-Pin (150 mils) SO and 9-Bump WLP PackagesDS2482-100Single-Channel 1-Wire Master________________________________________________________________Maxim Integrated Products1Rev 7; 8/08For pricing, delivery, and ordering information,please contact Maxim Direct at 1-888-629-4642,or visit Maxim’s website at .Pin Configurations appear at end of data sheet.PrintersMedical InstrumentsIndustrial Sensors Cell Phones, PDAsOrdering Information+Denotes a lead-free/RoHS-compliant package.T/T&R = Tape and reel.PART TEMP RANGE PIN-PACKAGEDS2482S-100+ -40°C to +85°C 8 SO (150 mils) DS2482S-100+T&R -40°C to +85°C 8 SO (150 mils) DS2482X-100+T -40°C to +85°C9 WLP (2.5k pieces)Typical Operating Circuit1-Wire is a registered trademark of Maxim Integrated Products, Inc.D S 2482-100Single-Channel 1-Wire Master 2_______________________________________________________________________________________ABSOLUTE MAXIMUM RATINGSELECTRICAL CHARACTERISTICSStresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.Voltage Range on Any Pin Relative to Ground.........-0.5V to +6V Maximum Current into Any Pin..........................................±20mA Operating Temperature Range ...........................-40°C to +85°CJunction Temperature......................................................+150°C Storage Temperature Range.............................-55°C to +125°C Soldering Temperature...........................Refer to the IPC/JEDECJ-STD-020 Specification.DS2482-100Single-Channel 1-Wire Master_______________________________________________________________________________________3ELECTRICAL CHARACTERISTICS (continued)D S 2482-100Single-Channel 1-Wire Master 4_______________________________________________________________________________________threshold V IL1may not be reached in the available time. With overdrive speed, the capacitive load on the 1-Wire bus must not exceed 300pF.Note 3:Active pullup guaranteed to turn on between V IL1(MAX)and V IH1(MIN).Note 4:Active or resistive pullup choice is configurable.Note 5:Except for t F1, all 1-Wire timing specifications and t APUOT are derived from the same timing circuit. Therefore, if one of these parameters is found to be off the typical value, it is safe to assume that all these parameters deviate from their typi-cal value in the same direction and by the same degree.Note 6:These values apply at full load, i.e., 1nF at standard speed and 0.3nF at overdrive speed. For reduced load, the pulldown slew rate is slightly faster.Note 7:Fall time high-to-low (t F1) is derived from PD SRC , referenced from 0.9 x V CC to 0.1 x V CC .Note 8:Presence-pulse masking only applies to standard speed.Note 9:All I 2C timing values are referred to V IH(MIN)and V IL(MAX)levels.Note 10:Applies to SDA, SCL, AD0 and AD1.Note 11:The input/output pins of the DS2482-100 do not obstruct the SDA and SCL lines if V CC is switched off.Note 12:The DS2482-100 provides a hold time of at least 300ns for the SDA signal (referred to the V IH(MIN)of the SCL signal) to bridge the undefined region of the falling edge of SCL.Note 13:The maximum t HD:DAT need only be met if the device does not stretch the low period (t LOW ) of the SCL signal.Note 14:A fast-mode I 2C bus device can be used in a standard-mode I 2C bus system, but the requirement t SU:DAT ≥250ns must then be met. This is automatically the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line t R(MAX)+ t SU:DAT = 1000 +250 = 1250ns (according to the standard-mode I 2C bus specification) before the SCL line is released.Note 15:C B —Total capacitance of one bus line in pF. If mixed with high-speed-mode devices, faster fall times according to I 2C-Bus Specification Version 2.1are allowed.Note 16:I 2C communication should not take place for the max t OSCWUP time following a power-on reset.ELECTRICAL CHARACTERISTICS (continued)DS2482-100Single-Channel 1-Wire Master_______________________________________________________________________________________5Figure 1. Block DiagramD S 2482-100Single-Channel 1-Wire Master 6_______________________________________________________________________________________Detailed DescriptionThe DS2482-100 is a self-timed 1-Wire master that sup-ports advanced 1-Wire waveform features including standard and overdrive speeds, active pullup, strong pullup for power delivery, and presence-pulse masking.The active pullup affects rising edges on the 1-Wire side. The strong pullup function uses the same pullup transistor as the active pullup, but with a different con-trol algorithm. In addition, the strong pullup activates the PCTLZ pin, controlling optional external circuitry to deliver additional power beyond the capabilities of the on-chip pullup transistor. Once supplied with command and data, the input/output controller of the DS2482-100performs time-critical 1-Wire communication functions such as reset/presence-detect cycle, read-byte, write-byte, single-bit R/W, and triplet for ROM Search, without requiring interaction with the host processor. The host obtains feedback (completion of a 1-Wire function,presence pulse, 1-Wire short, search direction taken)through the Status Register and data through the Read Data Register. The DS2482-100 communicates with a host processor through its I 2C bus interface in standard mode or in fast mode. The logic state of two address pins determines the I 2C slave address of the DS2482-100,allowing up to four devices operating on the same bus segment without requiring a hub. See Figure 1 for a block diagram.Device RegistersThe DS2482-100 has three registers that the I 2C host can read: Configuration, Status, and Read Data. These registers are addressed by a read pointer. The position of the read pointer, i.e., the register that the host reads in a subsequent read access, is defined by the instruc-tion the DS2482-100 executed last. To enable certain 1-Wire features, the host has read and write access to the Configuration Register.Configuration RegisterThe DS2482-100 supports four 1-Wire features that are enabled or selected through the Configuration Register.These features are:•Active Pullup (APU)•Presence-Pulse Masking (PPM)•Strong Pullup (SPU)•1-Wire Speed (1WS)These features can be selected in any combination.While APU, PPM, and 1WS maintain their state, SPU returns to its inactive state as soon as the strong pullup has ended.After a device reset (power-up cycle or initiated by the Device Reset command), the Configuration Register reads 00h. When writing to the Configuration Register,the new data is accepted only if the upper nibble (bits 7to 4) is the one’s complement of the lower nibble (bits 3to 0). When read, the upper nibble is always 0h.Active Pullup (APU)The APU bit controls whether an active pullup (con-trolled slew-rate transistor) or a passive pullup (R WPU resistor) is used to drive a 1-Wire line from low to high.When APU = 0, active pullup is disabled (resistor mode). Active pullup should be selected if the 1-Wire line has a substantial length (several 10m) or if there is a large number (approximately 20 or more) of devices connected to a 1-Wire line. The active pullup does not apply to the rising edge of a presence pulse or a recovery after a short on the 1-Wire line.The circuit that controls rising edges (F igure 2) oper-ates as follows: At t 1, the pulldown (from DS2482-100or 1-Wire slave) ends. F rom this point on, the 1-Wire bus is pulled high through R WPU internal to the DS2482-100. V CC and the capacitive load of the 1-Wire line determine the slope. In case that active pullup is disabled (APU = 0), the resistive pullup continues, as represented by the solid line. With active pullup enabled (APU = 1), and when at t 2the voltage has reached a level between V IL1(MAX)and V IH1(MIN), the DS2482-100 actively pulls the 1-Wire line high, applying a controlled slew rate as represented by the dashed line. The active pullup continues until t APUOT is expired at t 3. F rom that time on the resistive pullup continues.See the Strong Pullup (SPU)section for a way to keep the pullup transistor conducting beyond t 3.DS2482-100Single-Channel 1-Wire Master_______________________________________________________________________________________7Presence-Pulse Masking (PPM)The PPM bit controls whether the DS2482-100 masks the leading edge (falling) of presence pulses. When PPM = 0, masking is disabled. Presence-pulse masking applies only to standard 1-Wire speed (1WS = 0); this bit has no function if 1WS = 1 (overdrive speed).Presence-pulse masking can improve the performance of large 1-Wire networks because it prevents the fast falling edge of a presence pulse generated by a 1-Wire slave device from propagating through the network andbeing reflected. Reflections can cause glitches in the network that, in turn, can cause slave devices to lose synchronization with the 1-Wire master.Figure 3 shows the timing references for the presence-pulse masking. If enabled (PPM = 1), the DS2482-100begins pulling the 1-Wire line low at t PPM1after the reset low time t RSTL is expired. The pulldown ends at t PPM2, at which a 1-Wire slave, if present, is pulling the 1-Wire line low. The falling edge of the presence-pulse mask is slew-rate controlled.Figure 2. Rising Edge PullupFigure 3. Presence-Pulse MaskingD S 2482-100Single-Channel 1-Wire Master8_______________________________________________________________________________________Strong Pullup (SPU)The SPU bit is used to activate the strong pullup func-tion prior to a 1-Wire Write Byte or 1-Wire Single Bit command. Strong pullup is commonly used with 1-Wire EEPROM devices when copying scratchpad data to the main memory or when performing an SHA-1 computa-tion and with parasitically powered temperature sen-sors or A/D converters. The respective device data sheets specify the location in the communications pro-tocol after which the strong pullup should be applied.The SPU bit must be set immediately prior to issuing the command that puts the 1-Wire device into the state where it needs the extra power. The strong pullup uses the same internal pullup transistor as the active pullup feature. For cases where the internal strong pullup has insufficient strength, the PCTLZ pin can be used to con-trol an external p-channel MOSFET to supply additional power beyond the drive capability of the DS2482-100 to the 1-Wire line. See the ΔV STRPU parameter in the Electrical Characteristics to determine if the internal strong pullup is sufficient given the current load on the device.If SPU is 1, the DS2482-100 treats the rising edge of the time slot in which the strong pullup starts as if the active pullup was activated. However, in contrast to the active pullup, the strong pullup, i.e., the internal pullup transis-tor, remains conducting, as shown in Figure 4, until one of three events occurs: the DS2482-100 receives a command that generates 1-Wire communication (thetypical case); the SPU bit in the Configuration Register is written to 0; or the DS2482-100 receives the Device Reset command. As long as the strong pullup is active,the PCTLZ output is low. When the strong pullup ends,the SPU bit is automatically reset to 0. Using the strong pullup feature does not change the state of the APU bit in the Configuration Register.1-Wire Speed (1WS)The 1WS bit determines the timing of any 1-Wire com-munication generated by the DS2482-100. All 1-Wire slave devices support standard speed (1WS = 0),where the transfer of a single bit (t SLOT in Figure 4) is completed within 65µs. Many 1-Wire devices can also communicate at a higher data rate, called overdrive speed. To change from standard to overdrive speed, a 1-Wire device needs to receive an Overdrive-Skip ROM or Overdrive-Match ROM command, as explained in the 1-Wire device data sheets. The change in speed occurs immediately after the 1-Wire device has received the speed-changing command code. The DS2482-100 must take part in this speed change to stay synchronized. This is accomplished by writing to the Configuration Register with the 1WS bit as 1 imme-diately after the 1-Wire Byte command that changes the speed of a 1-Wire device. Writing to the Configuration Register with the 1WS bit as 0, followed by a 1-Wire Reset command, changes the DS2482-100 and any 1-Wire devices on the active 1-Wire line back to stan-dard speed.Figure 4. Low-Impedance Pullup TimingDS2482-100Single-Channel 1-Wire Master_______________________________________________________________________________________9Status RegisterThe read-only Status Register is the general means for the DS2482-100 to report bit-type data from the 1-Wire side, 1-Wire busy status, and its own reset status to the host processor. All 1-Wire communication commands and the Device Reset command position the read pointer at the Status Register for the host processor to read with minimal protocol overhead. Status information is updated during the execution of certain commands only. Details are given in the description of the various status bits that follow.1-Wire Busy (1WB)The 1WB bit reports to the host processor whether the 1-Wire line is busy. During 1-Wire communication 1WB is 1; once the command is completed, 1WB returns to its default 0. Details on when 1WB changes state and for how long it remains at 1 are found in the Function Commands section.Presence-Pulse Detect (PPD)The PPD bit is updated with every 1-Wire Reset com-mand. If the DS2482-100 detects a presence pulse from a 1-Wire device at t MSP during the presence-detect cycle, the PPD bit is set to 1. This bit returns to its default 0 if there is no presence pulse or if the 1-Wire line is shorted during a subsequent 1-Wire Reset command.Short Detected (SD)The SD bit is updated with every 1-Wire Reset com-mand. If the DS2482-100 detects a logic 0 on the 1-Wire line at t SI during the presence-detect cycle, the SD bit is set to 1. This bit returns to its default 0 with a subsequent 1-Wire Reset command provided that the short has been removed. If SD is 1, PPD is 0. The DS2482-100 cannot distinguish between a short and a DS1994 or DS2404 signaling a 1-Wire interrupt. For this reason, if a DS2404 or DS1994 is used in the applica-tion, the interrupt function must be disabled. The inter-rupt signaling is explained in the respective 1-Wire device data sheets.Logic Level (LL)The LL bit reports the logic state of the active 1-Wire line without initiating any 1-Wire communication. The 1-Wire line is sampled for this purpose every time the Status Register is read. The sampling and updating of the LL bit takes place when the host processor has addressed the DS2482-100 in read mode (during the acknowledge cycle), provided that the read pointer is positioned at the Status Register.Device Reset (RST)If the RST bit is 1, the DS2482-100 has performed an internal reset cycle, either caused by a power-on reset or from executing the Device Reset command. The RST bit is cleared automatically when the DS2482-100 exe-cutes a Write Configuration command to restore the selection of the desired 1-Wire features.Single Bit Result (SBR)The SBR bit reports the logic state of the active 1-Wire line sampled at t MSR of a 1-Wire Single Bit command or the first bit of a 1-Wire Triplet command. The power-on default of SBR is 0. If the 1-Wire Single Bit command sends a 0bit, SBR should be 0. With a 1-Wire Triplet command,SBR could be 0 as well as 1, depending on the response of the 1-Wire devices connected. The same result applies to a 1-Wire Single Bit command that sends a 1 bit.Triplet Second Bit (TSB)The TSB bit reports the logic state of the active 1-Wire line sampled at t MSR of the second bit of a 1-Wire Triplet command. The power-on default of TSB is 0.This bit is updated only with a 1-Wire Triplet command and has no function with other commands.Branch Direction Taken (DIR)Whenever a 1-Write Triplet command is executed, this bit reports to the host processor the search direction that was chosen by the third bit of the triplet. The power-on default of DIR is 0. This bit is updated only with a 1-Wire Triplet command and has no function with other commands. F or additional information, see the description of the 1-Wire Triplet command and Application Note 187: 1-Wire Search Algorithm .D S 2482-100Single-Channel 1-Wire MasterFunction CommandsThe DS2482-100 understands eight function com-mands that fall into four categories: device control, I 2C communication, 1-Wire setup, and 1-Wire communica-tion. The feedback path to the host is controlled by a read pointer, which is set automatically by each func-tion command for the host to efficiently access relevant information. The host processor sends these com-mands and applicable parameters as strings of one or two bytes using the I 2C interface. The I 2C protocol requires that each byte be acknowledged by the receiving party to confirm acceptance or not be acknowledged to indicate an error condition (invalid code or parameter) or to end the communication. See the I 2C Interface section for details of the I 2C protocol including acknowledge.The function commands are as follows:1) Device Reset 5) 1-Wire Single Bit 2) Set Read Pointer 6) 1-Wire Write Byte 3) Write Configuration 7) 1-Wire Read Byte 4) 1-Wire Reset8) 1-Wire TripletDS2482-100Single-Channel 1-Wire MasterD S 2482-100Single-Channel 1-Wire MasterFigure 5. 1-Wire Reset/Presence-Detect CycleDS2482-100Single-Channel 1-Wire MasterFigure 6. Write-Zero Time SlotFigure 7. Write-One and Read-Data Time SlotD S 2482-100Single-Channel 1-Wire MasterDS2482-100Single-Channel 1-Wire MasterD S 2482-100Single-Channel 1-Wire Master I 2C InterfaceGeneral CharacteristicsThe I 2C bus uses a data line (SDA) plus a clock signal (SCL) for communication. Both SDA and SCL are bidi-rectional lines, connected to a positive supply voltage through a pullup resistor. When there is no communica-tion, both lines are high. The output stages of devices connected to the bus must have an open drain or open collector to perform the wired-AND function. Data on the I 2C bus can be transferred at rates of up to 100kbps in standard mode and up to 400kbps in fast mode. The DS2482-100 works in both modes.A device that sends data on the bus is defined as a transmitter, and a device receiving data is defined as a receiver. The device that controls the communication is called a master. The devices that are controlled by the master are slaves. To be individually accessed, each device must have a slave address that does not conflict with other devices on the bus.Data transfers can be initiated only when the bus is not busy. The master generates the serial clock (SCL), con-trols the bus access, generates the START and STOP conditions, and determines the number of data bytes transferred between START and STOP (Figure 8). Data is transferred in bytes with the most significant bit beingtransmitted first. After each byte follows an acknowledge bit to allow synchronization between master and slave.Slave AddressThe slave address to which the DS2482-100 responds is shown in Figure 9. The logic state at the address pins AD0 and AD1 determines the value of the address bits A0 and A1. The address pins allow the device to respond to one of four possible slave addresses. The slave address is part of the slave address/control byte.The last bit of the slave address/control byte (R/W )defines the data direction. When set to 0, subsequent data flows from master to slave (write access); when set to 1, data flows from slave to master (read access).Figure 8. I 2C Protocol OverviewFigure 9. DS2482-100 Slave AddressDS2482-100 Single-Channel 1-Wire MasterI2C Definitions The following terminology is commonly used to describe I2C data transfers. The timing references are defined in Figure 10.Bus Idle or Not Busy: Both SDA and SCL are inac-tive and in their logic-high states.START Condition: To initiate communication with a slave, the master must generate a START condition.A START condition is defined as a change in state ofSDA from high to low while SCL remains high.STOP Condition: To end communication with a slave, the master must generate a STOP condition. A STOP condition is defined as a change in state of SDA from low to high while SCL remains high.Repeated START Condition: Repeated STARTs are commonly used for read accesses to select a spe-cific data source or address to read from. The mas-ter can use a repeated START condition at the end of a data transfer to immediately initiate a new data transfer following the current one. A repeated START condition is generated the same way as a normal START condition, but without leaving the bus idle after a STOP condition.Data Valid: With the exception of the START and STOP condition, transitions of SDA can occur only during the low state of SCL. The data on SDA must remain valid and unchanged during the entire high pulse of SCL plus the required setup and hold time (t HD:DAT after the falling edge of SCL and t SU:DAT before the rising edge of SCL; see Figure 10). There is one clock pulse per bit of data. Data is shifted into the receiving device during the rising edge of SCL. When finished with writing, the master must release the SDA line for a sufficient amount of setup time (minimum t SU:DAT+ t R in Figure 10) before the next rising edge of SCL to start reading. The slave shifts out each data bit on SDA at the falling edge of the previous SCL pulse and the data bit is valid at the rising edge of the current SCL pulse. The master generates all SCL clock pulses, including those needed to read from a slave.Acknowledge:Typically a receiving device, when addressed, is obliged to generate an acknowledge after the receipt of each byte. The master must gen-erate a clock pulse that is associated with this acknowledge bit. A device that acknowledges must pull SDA low during the acknowledge clock pulse in such a way that SDA is stable low during the high period of the acknowledge-related clock pulse plus the required setup and hold time (t HD:DAT after the falling edge of SCL and t SU:DAT before the rising edge of SCL).Not Acknowledged by Slave:A slave device may be unable to receive or transmit data, for example, because it is busy performing some real-time func-tion. In this case, the slave device does not acknowl-edge its slave address and leaves the SDA line high.A slave device that is ready to communicate acknowledges at least its slave address. However,Figure 10. I2C Timing DiagramD S 2482-100Single-Channel 1-Wire Mastersome time later the slave may refuse to accept data,possibly because of an invalid command code or parameter. In this case, the slave device does not acknowledge any of the bytes that it refuses and leaves SDA high. In either case, after a slave has failed to acknowledge, the master first should gener-ate a repeated START condition or a STOP condition followed by a START condition to begin a new data transfer.Not Acknowledged by Master:At some time when receiving data, the master must signal an end of data to the slave device. To achieve this, the master does not acknowledge the last byte that it has received from the slave. In response, the slave releases SDA, allowing the master to generate the STOP condition.Writing to the DS2482-100To write to the DS2482-100, the master must accessthe device in write mode, i.e., the slave address must be sent with the direction bit set to 0. The next byte to be sent is a command code, which, depending on the command, may be followed by a command parameter.The DS2482-100 acknowledges valid command codes and expected/valid command parameters. Additional bytes or invalid command parameters are never acknowledged.Reading from the DS2482-100To read from the DS2482-100, the master must access the device in read mode, i.e., the slave address must be sent with the direction bit set to 1. The read pointer determines the register that the master reads from. The master can continue reading the same register over and over again, without having to readdress the device,e.g., to watch the 1WB changing from 1 to 0. To read from a different register, the master must issue the Set Read Pointer command and then access the DS2482-100 again in read mode.I 2C Communication ExamplesSee Tables 4 and 5 for the I 2C communication legend and data direction codes.Table 5. Data Direction CodesDS2482-100Single-Channel 1-Wire MasterI 2C Communication Examples (continued)D S 2482-100Single-Channel 1-Wire MasterI 2C Communication Examples (continued)DS2482-100Single-Channel 1-Wire Master______________________________________________________________________________________21I 2C Communication Examples (continued)D S 2482-100Single-Channel 1-Wire Master 22______________________________________________________________________________________Applications InformationSDA and SCL Pullup ResistorsSDA is an open-drain output on the DS2482-100 that requires a pullup resistor to realize high-logic levels.Because the DS2482-100 uses SCL only as input (no clock stretching), the master can drive SCL either through an open-drain/-collector output with a pullup resistor or a push-pull output.Pullup Resistor R P SizingAccording to the I 2C specification, a slave device must be able to sink at least 3mA at a V OL of 0.4V. This DC condition determines the minimum value of the pullup resistor as:R P(MIN)= (V CC - 0.4V)/3mA With an operating voltage of 5.5V, the minimum value for the pullup resistor is 1.7k Ω. The “MINIMUM R P ” line in F igure 12 shows how the minimum pullup resistor changes with the operating voltage.F or I 2C systems, the rise time and fall time are mea-sured from 30% to 70% of the pullup voltage. The maxi-mum bus capacitance, C B , is 400pF. The maximum risetime must not exceed 1000ns at standard speed and 300ns at fast speed. Assuming maximum rise time, the maximum resistor value at any given capacitance C B is calculated as:R PMAXS = 1000ns/[C B x ln(7/3)] (standard speed)R PMAXF = 300ns/[C B x ln(7/3)] (fast speed)F or a bus capacitance of 400pF , the maximum pullup resistor values are 2.95k Ωat standard speed and 885Ωat fast speed. A value between 1.7k Ωand 2.95k Ωmeets all requirements at standard speed.Because an 885Ωpullup resistor, as would be required to meet the rise time specification at fast speed and 400pF bus capacitance, is lower than R P(MIN)at 5.5V, a different approach is necessary. The “MAX LOAD AT MIN R P FAST MODE” line in Figure 12 is generated by first calculating the minimum pullup resistor at any given operating voltage (“MINIMUM R P ” line) and then calculating the respective bus capacitance that yields a 300ns rise time.Only for pullup voltages of 3V and lower can the maximum permissible bus capacitance of 400pF be maintained. AI 2C Communication Examples (continued)。

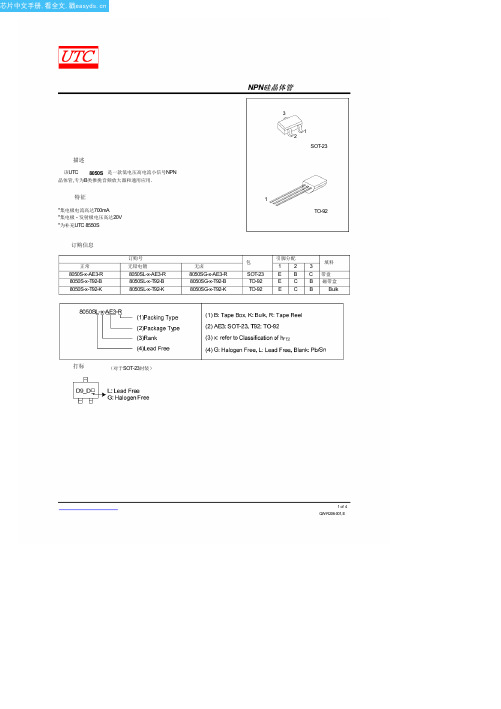

8050S中文资料(Unisonic Technologies)中文数据手册「EasyDatasheet - 矽搜」

打标

(对于SOT-23封装)

1 of 4 QW-R206-001,E

芯片中文手册,看全文,戳

8050S

绝对最大额定值

NPN硅晶体管

(TA = 25°C,除非另有规定)

参数

符号

集电极基极电压

VCBO

集电极 - 发射极电压

VCEO

发射极基极电压

VEBO

电气特性ta25c除非另有规定参数集电极基击穿电压集电极发射极击穿电压发射基地击穿电压集电极截止电流发射极截止电流dc电流增益注集电极发射极饱和电压基地发射极饱和电压基地发射极饱和电压当前增益带宽产品输出电容符号bvcbobvceobvebocob测试条件1mhzmin3020typ最大单位ua100na4001001204005121010090mhzpfh分类fe2qwr206001e芯片中文手册看全文戳easydscn8050s电流增益带宽产品f兆赫集电极电流ic毫安集电极电流ic毫安典型特征饱和电压mvdc电流增益h电容cobpfnpn硅晶体管硅晶体管qwr206001e芯片中文手册看全文戳easydscn8050snpn硅晶体管硅晶体管设备故障不承担任何责任额定数值例如最大额定值工作环境范围或其他参数任何产品规格和描述或此处包含所有utc产品上市

订购号 无铅电镀

8050SL-x-AE3-R 8050SL-x-T92-B 8050SL-x-T92-K

无卤

8050SG-x-AE3-R 8050SG-x-T92-B 8050SG-x-T92-K

3

1 2

SOT-23

1 TO-92

包

SOT-23 TO-92 TO-92

引脚分配

12 EB EC EC

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

SPECIFICATION

S-100-3S-100-5S-100-7.5S-100-10S-100-12S-100-15S-100-18S-100-24S-100-27S-100-36S-100-48MODEL

DC VOLTAGE RATED CURRENT CURRENT RANGE RATED POWER

OUTPUT

VOLTAGE ADJ. RANGE LINE REGULATION LOAD REGULATION SETUP, RISE TIME HOLD UP TIME (Typ.)VOLTAGE RANGE FREQUENCY RANGE

EFFICIENCY (Typ.)INPUT

INRUSH CURRENT (Typ.)LEAKAGE CURRENT

SAFETY STANDARDS

SAFETY &EMC

WORKING TEMP.

WORKING HUMIDITY

STORAGE TEMP., HUMIDITY

TEMP. COEFFICIENT

VIBRATION

MTBF

DIMENSION OTHERS

NOTE

PACKING

OVERLOAD

AC CURRENT (Typ.)

3V 5V 7.5V 10V 12V 15V 18V 24V 27V 36V 48V 20A 20A 13.6A 10A 8.5A 6.7A 5.6A 4.5A 3.7A 2.7A 2A 0 ~ 20A 0 ~ 20A 0 ~ 13.6A 0 ~ 10A

0 ~ 8.5A 0 ~ 6.7A 0 ~ 5.6A 0 ~ 4.5A 0 ~ 3.7A 0 ~ 2.7A 0 ~ 2A 60W

100W

102W

100W

102W

100.5W

100.8W

108W

99.9W

97.2W

96W

100mVp-p 100mVp-p 100mVp-p 100mVp-p 100mVp-p 100mVp-p 100mVp-p 100mVp-p 100mVp-p 100mVp-p 100mVp-p 2.85 ~ 3.3V 4.75 ~ 5.5V 6.75 ~ 8.25V 9 ~ 11V 10.8 ~ 13.2V 13.5 ~ 16.5V 16.2 ~ 19.8V 21.6 ~ 26.4V 26 ~ 32V 32.4 ~ 39.6V 43.2 ~ 52.8V

2.0% 2.0% 1.0% 1.0%

1.0% 1.0% 1.0% 1.0% 1.0% 1.0% 1.0%0.5%0.5%0.5%0.3%0.3%0.3%0.3%0.3%

0.3%

0.3%

0.3%

0.2%0.2%0.2%0.2%0.5%

0.5%

0.5%

0.2%

0.2%

0.2%

0.2%

200ms, 80ms at full load 24ms at full load

85 ~ 132VAC/180 ~ 264VAC selected by switch 255 ~ 370VDC 47 ~ 63Hz 70%

78%

80%

80%

81%

81%

82%

84%

84%

84%

84%

1.9A/115VAC 0.96A/230VAC

COLD START 27A/115VAC 54A/230VAC <1mA / 240VAC

105 ~ 150%rated output power (130 ~ 180% of rated output power for S-100-5, S-100-36 ; 150 ~ 200% of rated output power for S-100-7.5 )Protection type : Shut down o/p voltage, re-power on to recover Design refer to UL1012

-10 ~ +60(Refer to output load derating curve)20 ~ 90% RH non-condensing

-20 ~ +85

, 10 ~ 95% RH

0.03%/(0 ~ 50

10 ~ 500Hz, 2G 10min./1cycle, 60min. each along X,Y, Z axes 322.4K hrs min. MIL-HDBK-217F (25)

199*98*38mm (L*W*H)

0.62Kg; 20pcs/13.6Kg/0.8CUFT

1. All parameters NOT specially mentioned are measured at 230VAC input, rated load and 25of ambient temperature.

2. Ripple & noise are measured at 20MHz of bandwidth by using a 12" twisted pair-wire terminated with a 0.1uf & 47uf parallel capacitor.

3. Tolerance : includes set up tolerance, line regulation and load regulation.

Design refer to FCC Part15 J Conduction Class B

AC input range selectable by switch Protections: Short circuit / Overload Cooling by free air convection 100% full load burn-in test

Fixed switching frequency at 25KHz Low cost High reliability 1 year warranty

Features :

RIPPLE & NOISE (max.)Note.2VOLTAGE TOLERANCE Note.3EMI CONDUCTION & RADIATION ENVIRONMENT PROTECTION WITHSTAND VOLTAGE

ISOLATION RESISTANCE I/P-O/P:1.5KVAC I/P-FG:1.5KVAC O/P-FG:0.5KVAC

I/P-O/P, I/P-FG, O/P-FG:100M Ohms/500VDC

Mechanical Specification

Derating Curve

Static Characteristics (24V)

Case No. 902 Unit:mm

AMBIENT TEMPERATURE ()INPUT VOLTAGE (V) 60Hz

O U T P U T V O L T A G E (V )

O U T P U T R I P P L E (m V p -p )

(HORIZONTAL)(VERTICAL)-10-1000

10203040

5045605520

4060

80100L O A D (%)

S-100-7.5

S-100-3.3,5

S-100-12~48

80160851709095180100190105200110210115220120230125240250130260

2832

242016128

Ta=25

50

100200150250300350

Block Diagram

fosc : 25KHz

EMI FILTER RECTIFIERS

230115&FILTER

POWER SWITCHING

FILTER

&RECTIFIERS

+V -V

I/P

FG

DRIVER

PWM CONTROL

O.C.P.

Terminal Pin No.Assignment

Pin No.Pin No.124,53

6,7

Assignment Assignment DC OUTPUT -V DC OUTPUT +V

FG

AC/L AC/N 3.59

9

197

7

6.5

190

22

157

4.5

7

65

4

3

28.2

1

120

199

57.5

12

9.5

80

85.5

98

3.5

4-

M

3

3.5

18

9.5

18

3-M

3

3.528.5

38。