SN65MLVD201中文资料

SN65DP141 DisplayPort线性转接驱动器说明书

SN65DP141 DisplayPort 线性转接驱动器1 特性•支持 VESA DisplayPort 1.4a 、2.0 和 eDP 1.4•四通道线性转接驱动器,支持高达 12Gbps 的数据速率,包括 DisplayPort RBR 、HBR 、HBR2、HBR3 和 UHBR10•与协议无关•透明呈现 DP 链路训练•与在链路上的位置无关,适用于源端、接收端和电缆应用•6GHz 时模拟均衡为 15dB •输出线性动态范围:1200mV •带宽:>20 GHz•6GHz 时的回波损耗优于 16dB • 2.5V 或 3.3V ±5% 单电源选项•低功耗,2.5V V CC 时每通道 80mW •GPIO 或 I 2C 控制2 应用•平板电脑•笔记本电脑•台式机•扩展坞3 说明SN65DP141 是一款与协议无关的异步、低延迟、四通道线性均衡器,该器件经过优化适用于高达 12Gbps 的数据速率并且可对电路板走线和电缆所产生的损耗进行补偿。

该器件透明呈现 DisplayPort (DP) 链路训练,这使得 DP 发送设备和接收设备能够执行有效的链路训练,克服了传统 aux snooping 转接驱动器的缺点。

此外,该器件与位置无关。

它可置于源设备、电缆或接收设备内,从而为总体链路预算有效提供负损耗 分量。

SN65DP141 内的线性均衡在与接收器搭配使用时还可提高链路裕度,从而实现判决反馈均衡 (DFE)。

SN65DP141 支持采用 I 2C 和 GPIO 配置对均衡、增益、动态范围进行独立通道控制。

(1)(1)如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

GPU DP141DP141Copyright © 2016, Texas Instruments Incorporated简化版原理图Table of Contents1 特性...................................................................................12 应用...................................................................................13 说明...................................................................................14 Revision History ..............................................................25 Pin Configuration and Functions ...................................36 Specifications ..................................................................56.1 Absolute Maximum Ratings........................................56.2 ESD Ratings...............................................................56.3 Recommended Operating Conditions.........................56.4 Thermal Information....................................................66.5 Electrical Characteristics.............................................66.6 Switching Characteristics............................................86.7 Switching Characteristics, I 2C Interface......................96.8 Typical Characteristics..............................................107 Parameter Measurement Information ..........................118 Detailed Description ......................................................158.1 Overview...................................................................158.2 Functional Block Diagram.. (15)8.3 Feature Description...................................................168.4 Device Functional Modes..........................................178.5 Register Maps...........................................................189 Application and Implementation ..................................249.1 Application Information.............................................249.2 Typical Application....................................................2410 Power Supply Recommendations ..............................2611 Layout ...........................................................................2711.1 Layout Guidelines...................................................2711.2 Layout Example......................................................2812 Device and Documentation Support ..........................2912.1 接收文档更新通知...................................................2912.2 支持资源..................................................................2912.3 Trademarks.............................................................2912.4 Electrostatic Discharge Caution..............................2912.5 术语表.....................................................................2913 Mechanical, Packaging, and OrderableInformation (29)4 Revision History注:以前版本的页码可能与当前版本的页码不同Changes from Revision B (September 2021) to Revision C (December 2021)Page•Changed the I2C_EN pin Type from internal pull-up to internal pull-down ........................................................3Changes from Revision A (October 2016) to Revision B (September 2021)Page•更新了整个文档中的表格、图和交叉参考的编号格式.........................................................................................1•将特性从:“支持 VESA DisplayPort 1.3 和 eDP 1.4”更新为:“支持 VESA DisplayPort 1.4a 、2.0 和 eDP 1.4”...................................................................................................................................................................1•将特性从“包括 DisplayPort RBR 、HBR 、HBR2 和 HBR3”更新为“包括 DisplayPort RBR 、HBR 、HBR2、HBR3 和 UHBR10”...........................................................................................................................................1•Updated the DP bit rates from: RBR to HBR3 (1.6 Gbps, 2.7 Gbps, 5.4 Gbps and 8.1 Gbps ... to: RBR toUHBR10 (1.6 Gbps, 2.7 Gbps, 5.4 Gbps, 8.1 Gbps and 10.0 Gbps … in the Overview section......................15•Updated Operating data rate from HBR3 (8.1 Gbps) to UHBR10 (10 Gbps)...................................................24Changes from Revision * (February 2016) to Revision A (October 2016)Page•Replaced 图 9-2 (25)SN65DP141ZHCSEQ7C – FEBRUARY 2016 – REVISED DECEMBER 20215 Pin Configuration and FunctionsThermalPadV C C1IN0_P P W D #2IN0_N R X _G A I N3VCC E Q _M O D E /_A D D 24IN1_P E Q 0/A D D 05IN1_N E Q 1/A D D 16VCC 7VCC OUT0_P 8IN2_P 9IN2_N V C COUT0_N VCC OUT1_P OUT1_N VCC VCC OUT2_P OUT2_N VCC OUT3_P OUT3_NV C CV C CVCC IN3_P IN3_NS D AD R V _P K #/S C LI 2C _E NT X _D C _G A I N /C SR E X T1011121314151617181920212223242526272829303132333435363738It is required for the thermal pad to be soldered to ground for better thermal performance.图 5-1. RLJ Package 38 Pins (WQFN) Top ViewSN65DP141ZHCSEQ7C – FEBRUARY 2016 – REVISED DECEMBER 2021SN65DP141ZHCSEQ7C – FEBRUARY 2016 – REVISED DECEMBER (1)I = input, O = output6 Specifications6.1 Absolute Maximum Ratings(1)(2)(1)Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated underRecommended Operating Conditions . Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.(2)All voltage values, except differential I/O bus voltages, are with respect to network ground terminal.6.2 ESD Ratings(1)JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.(2)JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. .6.3 Recommended Operating ConditionsSN65DP141ZHCSEQ7C – FEBRUARY 2016 – REVISED DECEMBER 2021SN65DP141ZHCSEQ7C – FEBRUARY 2016 – REVISED DECEMBER 6.4 Thermal Information(1)For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics applicationreport, SPRA953.6.5 Electrical Characteristics6.5 Electrical Characteristics (continued)SN65DP141ZHCSEQ7C – FEBRUARY 2016 – REVISED DECEMBER 2021SN65DP141ZHCSEQ7C – FEBRUARY 2016 – REVISED DECEMBER 6.6 Switching Characteristics(1)Rise and Fall measurements include board and channel effects of the test environment, refer to 图 7-1 and 图 7-3.(2)t SK(O) is the magnitude of the time difference between the channels.(3)t SK(PP) is the magnitude of the difference in propagation delay times between any specified terminals of two devices when both devicesoperate with the same(4)All noise sources added.6.7 Switching Characteristics, I 2C InterfaceSN65DP141ZHCSEQ7C – FEBRUARY 2016 – REVISED DECEMBER 20216.8 Typical Characteristics−45−40−35−30−25−20−15−10−5002468101214Frequency (GHz)A m p l i t u d e (dB )图 6-1. Differential Input Return Loss−70−60−50−40−30−20−1002468101214Frequency (GHz)A m p l i t u d e (dB )图 6-2. Differential to Common Mode Conversion−40−35−30−25−20−15−10−5002468101214Frequency (GHz)A m p l i t u d e (dB )图 6-3. Differential Output Return Loss −45−40−35−30−25−20−15−10−5002468101214Frequency (GHz)A m p l i t u d e (dB )图 6-4. Common Mode Output Return LossSN65DP141ZHCSEQ7C – FEBRUARY 2016 – REVISED DECEMBER 20217 Parameter Measurement InformationCopyright © 2016, Texas Instruments Incorporated图 7-1. Common Mode Output Voltage Test Circuit图 7-2. Propagation Delay Input to Output图 7-3. Output Rise and Fall TimesOUTxOUT y图 7-4. Output Inter-Pair Skew0V图 7-5. V (pre) and V (post) (test pattern is 1111111100000000 (8-1s, 8-0s))CHARACTERIZATION TEST CHANNEL图 7-6. Receive Side Performance Test Circuit图 7-7. Transmit Side Performance Test CircuitIN-Copyright © 2016, Texas Instruments Incorporated图 7-8. Equivalent Input CircuitINCopyright © 2016, Texas Instruments Incorporated图 7-9. 3-Level Input Biasing Network图 7-10. Two – Wire Serial Interface Data Transfer图 7-11. Two – Wire Serial Interface Timing Diagram8 Detailed Description8.1 OverviewThe SN65DP141 is an asynchronous, protocol-agnostic, low latency, four-channel linear equalizer optimized for use up to 12 Gbps. The characteristics of this device make it transparent to DisplayPort (DP) link training. It supports all the available DP bit rates from RBR to UHBR10 (1.6 Gbps, 2.7 Gbps, 5.4 Gbps, 8.1 Gbps, and 10.0 Gbps respectively). Additionally, the SN65DP141 is configurable to a trace or cable mode, and hence improves its performance depending on the type of channel it is being used. Its transparency to the DP link training makes the SN65DP141 a position independent device, suitable for source/sink or cable applications, effectively providing a negative loss component to the overall link budget, in order to compensate the signal degradation over the channel.The SN65DP141 is configurable by means of I 2C and GPIOs, allowing independent channel control for activation, equalization, gain, and dynamic range.8.2 Functional Block DiagramGNDIN[3:0]_P DRV_PK#/SCLSDA VOD/CS GAININ[3:0]_NCopyright © 2016, Texas Instruments Incorporated8.3 Feature Description8.3.1 DC and AC Independent Gain ControlBesides the functional block diagram, the behavior of the SN65DP141 can be described as it is shown in 图 8-1; where the input stage first applies a DC gain (0 dB or –6 dB) and then equalizes the signal, which is driven to the output stage where the SN65DP141 applies an output DC gain (0 dB or 6 dB).TX_GAIN(TX_DC_GAIN)EQUALIZATION(EQ_AC_GAIN)RX_GAIN(EQ_DC_GAIN)0dB or -6dB Up to 15dB0dB or 6dB图 8-1. DP141 Signal Chain Gain Control8.3.2 Two-Wire Serial Interface and Control LogicThe SN65DP141 uses a 2-wire serial interface for digital control. The two circuit inputs, SDA and SCL, are driven, respectively, by the serial data and serial clock from a microcontroller, for example. The SDA and SCK pins require external 10 kΩ pull-ups to VCC.The 2-wire interface allows write access to the internal memory map to modify control registers and read access to read out control and status signals. The SN65DP141 is a slave device only which means that it cannot initiate a transmission itself; it always relies on the availability of the SCK signal for the duration of the transmission. The master device provides the clock signal as well as the START and STOP commands. The protocol for a data transmission is as follows:1.START command2.7 bit slave address (0000ADD [2:0]) followed by an eighth bit which is the data direction bit (R/W). A zeroindicates a WRITE and a 1 indicates a READ. The ADD [2:0] address bits change with the status of the ADD2, ADD1, and ADD0 device pins, respectively. If the pins are left floating or pulled down, the 7 bit slave address is 0000000.3.8-bit register address4.8-bit register data word5.STOP commandRegarding timing, the SN65DP141 is I2C compatible. The typical timing is shown in 图 7-11 and a complete data transfer is shown in 图7-10. Parameters for these figures are defined in the I2C Interface section of the Switching Characteristics.8.3.3 Bus IdleBoth SDA and SCL lines remain HIGH8.3.4 Start Data TransferA change in the state of the SDA line, from HIGH to LOW, while the SCL line is HIGH, defines a START condition (S). Each data transfer is initiated with a START condition.8.3.5 Stop Data TransferA change in the state of the SDA line from LOW to HIGH while the SCL line is HIGH defines a STOP condition (P). Each data transfer is terminated with a STOP condition; however, if the master still wishes to communicate on the bus, it can generate a repeated START condition and address another slave without first generating a STOP condition.8.3.6 Data TransferThe number of data bytes transferred between a START and a STOP condition is not limited and is determined by the master device. The receiver acknowledges the transfer of data.8.3.7 AcknowledgeEach receiving device, when addressed, is obliged to generate an acknowledge bit. The transmitter releases the SDA line and a device that acknowledges must pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge clock pulse. Setup and hold times must be taken into account. When a slave-receiver doesn’t acknowledge the slave address, the data line must be left HIGH by the slave. The master can then generate a STOP condition to abort the transfer. If the slave-receiver does acknowledge the slave address but some time later in the transfer cannot receive any more data bytes, the master must abort the transfer. This is indicated by the slave generating the not acknowledge on the first byte to follow. The slave leaves the data line HIGH and the master generates the STOP condition.8.4 Device Functional Modes8.4.1 TRACE and CABLE Equalization ModesThe SN65DP141 is optimized for both trace and cable application at its input. The device pin EQ_MODE sets the EQ gain curve profile suitable for these two use cases.8.4.2 Control ModesThe SN65DP141 features two control modes: GPIO and I2C, and the selection between these two modes is by means of the I2C_EN terminal, which activates the GPIO when tied to LOW; otherwise, the I2C mode is active due to its internal pull-up resistance.8.4.3 GPIO MODEDevice Pins RX_GAIN, EQ1 and EQ0 determines receiver DC and AC gain as shown in 表 8-1 and 表 8-2.8.4.4 I2C Mode8.5 Register Maps8.5.1 Register 0x00 (General Device Settings) (offset = 00000000) [reset = 00000000]LEGEND: R/W = Read/Write; R = Read only; -n = value after reset8.5.2 Register 0x01 (Channel Enable) (offset = 00000000) [reset = 00000000]LEGEND: R/W = Read/Write; R = Read only; -n = value after reset8.5.3 Register 0x02 (Channel 0 Control Settings) (offset = 00000000) [reset = 00000000]LEGEND: R/W = Read/Write; R = Read only; -n = value after reset8.5.4 Register 0x03 (Channel 0 Enable Settings) (offset = 00000000) [reset = 00000000]LEGEND: R/W = Read/Write; R = Read only; -n = value after reset8.5.5 Register 0x05 (Channel 1 Control Settings) (offset = 00000000) [reset = 00000000]LEGEND: R/W = Read/Write; R = Read only; -n = value after reset8.5.6 Register 0x06 (Channel 1 Enable Settings) (offset = 00000000) [reset = 00000000]LEGEND: R/W = Read/Write; R = Read only; -n = value after resetSN65DP141ZHCSEQ7C – FEBRUARY 2016 – REVISED DECEMBER 2021SN65DP141ZHCSEQ7C – FEBRUARY 2016 – REVISED DECEMBER 8.5.7 Register 0x08 (Channel 2 Control Settings) (offset = 00000000) [reset = 00000000]LEGEND: R/W = Read/Write; R = Read only; -n = value after reset8.5.8 Register 0x09 (Channel 2 Enable Settings) (offset = 00000000) [reset = 00000000]LEGEND: R/W = Read/Write; R = Read only; -n = value after reset8.5.9 Register 0x0B (Channel 3 Control Settings) (offset = 00000000) [reset = 00000000]LEGEND: R/W = Read/Write; R = Read only; -n = value after reset8.5.10 Register 0x0C (Channel 3 Control Settings) (offset = 00000000) [reset = 00000000]LEGEND: R/W = Read/Write; R = Read only; -n = value after resetSN65DP141ZHCSEQ7C – FEBRUARY 2016 – REVISED DECEMBER 20219 Application and Implementation备注以下应用部分中的信息不属于TI 器件规格的范围,TI 不担保其准确性和完整性。

SN65ELT22中文资料

FEATURESPIN ASSIGNMENTAPPLICATIONS DESCRIPTIONVCCGND QQQ1Q1DD1SN65ELT22............................................................................................................................................................................................SLLS924–DECEMBER20085-V Dual TTL-to-Differential PECL Translator• 1.1-ns(max)Propagation Delay•Operating Range:V CC=4.2V to5.7V with D or DGK PACKAGE GND=0V(TOP VIEW)•<50-ps(typ)Output-to-Output Skew•Built-In Temperature Compensation•Drop-In Compatible to the MC10ELT22,MC100ELT22•Data and Clock Transmission Over Backplane•Signaling Level Conversion for Clock or DataThe SN65ELT22is a dual TTL-to-differential PECLtranslator.It operates on+5-V supply and groundonly.The output is undetermined when the inputs areTable1.Pin Descriptionsleft floating.The low output skew makes the devicean ideal solution for clock or data signal translation.PIN FUNCTIONThe SN65ELT22is housed in an industry standard D,D1TTL inputsSOIC-8package and is also available in an optional Q,Q0,Q1,Q1PECL outputsTSSOP-8package.V CC Positive supplyGND GroundORDERING INFORMATION(1)PART NUMBER PART MARKING PACKAGE LEAD FINISHSN65ELT22D SN65ELT22SOIC NiPdAuSN65ELT22DGK SN65ELT22SOIC-TSSOP NiPdAu(1)Leaded device options are not initially available;contact a sales representative for further detailsPlease be aware that an important notice concerning availability,standard warranty,and use in critical applications of TexasInstruments semiconductor products and disclaimers thereto appears at the end of this data sheet.ABSOLUTE MAXIMUM RATINGS (1)POWER DISSIPATION RATINGSTHERMAL CHARACTERISTICSKEY ATTRIBUTESSN65ELT22SLLS924–DECEMBER These devices have limited built-in ESD protection.The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.PARAMETERCONDITIONSVALUE UNIT Absolute PECL mode supply voltage,V CC GND =0V 6V Input voltage,V IN GND =0V GND +0.025<V IN <V CC –0.025V Continuous 50Output currentmA Surge100Operating temperature range –40to 85°C Storage temperature range –65to 150°C(1)Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device.These are stress ratings only and functional operation of the device at these or any conditions beyond those indicated under recommended operating conditions is not implied.Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.POWER RATINGTHERMAL RESISTANCE,DERATING FACTORPOWER RATINGCIRCUIT BOARDJUNCTION-TO-AMBIENTPACKAGET A <25°C T A >25°C T A =85°C MODELNO AIRFLOW(mW)(mW/°C)(mW)Low-K 7191397288SOIC High-K 8401198336Low-K 4692135188SOIC-TSSOPHigh-K5271895211PARAMETERMINTYP MAXUNIT SOIC 79θJB Junction-to-board thermal resistance °C/W SOIC-TSSOP 120SOIC 98θJCJunction-to-case thermal resistance°C/WSOIC-TSSOP74CHARACTERISTICS VALUE Moisture sensitivity levelLevel 1Flammability rating (oxygen index:28to 34)UL 94V-0at 0.125inHuman body model4kV Electrostatic dischargeCharge device model 2kV Machine model200VMeets or exceeds JEDEC Spec EIA/JESD78latchup testPECL DC CHARACTERISTICS TTL DC CHARACTERISTICS AC CHARACTERISTICS SN65ELT22............................................................................................................................................................................................SLLS924–DECEMBER2008At V CC=5.0V,GND=0.0V(unless otherwise noted)(1)(2)T A=–40°C T A=25°C T A=85°C PARAMETER TEST CONDITIONS UNITMIN TYP MAX MIN TYP MAX MIN TYP MAXI CC Power supply current17.32018.22019.422mA V OH High-level output voltage See(3)391539544120391539584120391539614120mV V OL Low-level output voltage See(3)317032363380317032313380317032293380mV (1)The device meets the specifications after thermal balance has been established when mounted in a socket or printed circuit board withmaintained transverse airflow greater than500lfpm.Electrical parameters are assured only over the declared operating temperature range.Functional operation of the device exceeding these conditions is not implied.Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.(2)Input and output parameters vary1:1with V CC.V CC can vary+0.7V/–0.8V.(3)Outputs are terminated through a50-Ωresistor to V CC–2.0V.At V CC=4.2V to5.7V,T A=–40°C to85°C(unless otherwise noted)(1)PARAMETER TEST CONDITIONS MIN TYP MAX UNIT I IH High-level input current V IN=2.7V,V IN=(V CC–0.025)V20µAI IHH High-level input current V IN=V CC20µAI IL Low-level input current V IN=0.5V,V IN=(GND+0.025)V–200µAV IK Input clamp diode voltage I IN=–18mA–1.2VV IH High-level input voltage 2.0Vcc–0.025VV IL Low-level input voltage GND+0.0250.8V (1)The device meets the specifications after thermal balance has been established when mounted in a socket or printed circuit board withmaintained transverse airflow greater than500lfpm.Electrical parameters are assured only over the declared operating temperature range.Functional operation of the device exceeding these conditions is not implied.Device specification limit values are applied individually under normal operating conditions and not valid simultaneouslyAt V CC=4.2V to5.7V,GND=0.0V(unless otherwise noted)(1)T A=–40°C T A=25°C T A=85°C PARAMETER TEST CONDITIONS UNITMIN TYP MAX MIN TYP MAX MIN TYP MAX Max switchingf MAX frequency(2),500490470MHzsee Figure5t PLH0.60.83 1.10.60.84 1.10.60.85 1.1 Propagation delay time 1.5V to50%nst PHL0.50.90.50.90.50.9 Within device skew See(3)259025902590t SKEW ps Device-to-device skew See(4)251002510025100Random clock jittert JITTER0.50.50.5ps (RMS)t r/t f Output rise/fall times Q(20%–80%)0.7 1.10.7 1.10.7 1.1ns (1)The device meets the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuitboard with maintained transverse airflow greater than500lfpm.Electrical parameters are assured only over the declared operating temperature range.Functional operation of the device exceeding these conditions is not implied.Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.(2)Maximum switching frequency measured at output amplitude of300mV pp.(3)Measured between outputs under the identical transitions and conditions on any one device.(4)Device-to-device skew for identical transitions at identical V CC levels.Typical Termination for Output DriverV = V - 2 VTTTT CCINSN65ELT22SLLS924–DECEMBER Figure 1.Typical Termination for DriverFigure 2.Output Propagation DelayFigure 3.Output Rise and Fall TimesINHigher [(t - t ), (t - t )]PLH1PLH0PLH1PLH0010020030040050060070080090010000100200300400600f –Frequency –MHzO u t p u t A m p l i t u d e –m V500SN65ELT22 ............................................................................................................................................................................................SLLS924–DECEMBER 2008Figure 4.Device SkewFigure 5.Output Amplitude vs.FrequencyPACKAGING INFORMATIONOrderable Device Status (1)Package Type Package DrawingPins Package Qty Eco Plan (2)Lead/Ball Finish MSL Peak Temp (3)SN65ELT22D ACTIVE SOIC D 875Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN65ELT22DGK ACTIVE MSOP DGK 880Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN65ELT22DGKR ACTIVE MSOP DGK 82500Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN65ELT22DRACTIVESOICD82500Green (RoHS &no Sb/Br)CU NIPDAULevel-1-260C-UNLIM(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan -The planned eco-friendly classification:Pb-Free (RoHS),Pb-Free (RoHS Exempt),or Green (RoHS &no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free (RoHS):TI's terms "Lead-Free"or "Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all 6substances,including the requirement that lead not exceed 0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free (RoHS Exempt):This component has a RoHS exemption for either 1)lead-based flip-chip solder bumps used between the die and package,or 2)lead-based die adhesive used between the die and leadframe.The component is otherwise considered Pb-Free (RoHS compatible)as defined above.Green (RoHS &no Sb/Br):TI defines "Green"to mean Pb-Free (RoHS compatible),and free of Bromine (Br)and Antimony (Sb)based flame retardants (Br or Sb do not exceed 0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge andbelief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.PACKAGE OPTION ADDENDUM2-Jan-2009TAPE AND REEL INFORMATION*All dimensions are nominalDevicePackage Type Package Drawing Pins SPQReel Diameter (mm)Reel Width W1(mm)A0(mm)B0(mm)K0(mm)P1(mm)W (mm)Pin1Quadrant SN65ELT22DGKR MSOP DGK 82500330.012.4 5.3 3.4 1.48.012.0Q1SN65ELT22DRSOICD82500330.012.46.45.22.18.012.0Q1*All dimensions are nominalDevice Package Type Package Drawing Pins SPQ Length(mm)Width(mm)Height(mm) SN65ELT22DGKR MSOP DGK82500346.0346.029.0 SN65ELT22DR SOIC D8*******.0346.029.0IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI)reserve the right to make corrections,modifications,enhancements,improvements,and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products andapplications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right,or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications (such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,andacknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic."Only products designated by TI as military-grade meet militaryspecifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:ProductsApplications AmplifiersAudio Data ConvertersAutomotive DLP®ProductsBroadband DSPDigital Control Clocks and TimersMedical InterfaceMilitary LogicOptical Networking Power MgmtSecurity MicrocontrollersTelephony RFIDVideo &Imaging RF/IF and ZigBee®Solutions Wireless Mailing Address:Texas Instruments,Post Office Box 655303,Dallas,Texas 75265Copyright ©2009,Texas Instruments Incorporated 元器件交易网。

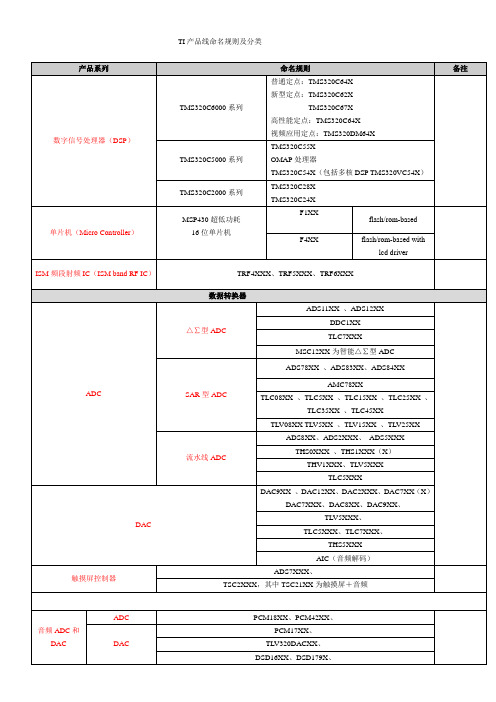

TI产品线命名规则及分类

TI产品线命名规则及分类

补充:

1、MSP430系列产品品种较多,先来了解下TI公司对MSP430的命名规则

2、TI产品命名规则

TI产品命名规则:SN54LS×××/HC/HCT/或SNJ54LS/HC/HCT中的后缀说明:

1、SN或SNJ表示TI品牌

2、SN军标,带N表示DIP封装,带J表示DIP(双列直插),带D表示表贴,带W表示宽体

3、SNJ军级,后面代尾缀F或/883表示已检验过的军级。

CD54LS×××/HC/HCT:

1、无后缀表示普军级

2、后缀带J或883表示军品级

CD4000/CD45××:

1、后缀带BCP或BE属军品

2、后缀带BF属普军级

3、后缀带BF3A或883属军品级

TL×××:

1、后缀CP普通级IP工业级后缀带D是表贴

2、后缀带MJB、MJG或带/883的为军品级

3、TLC表示普通电压TLV低功耗电压

TMS320系列归属DSP器件,MSP430F微处理器

BB产品命名规则:

前缀ADS模拟器件,后缀U表贴,P是DIP封装,带B表示工业级;前缀INA、XTR、PGA等表示高精度运放后缀U表贴,P 代表DIP,PA表示高精度。

LVDS

LVDS2010-08-25 21:41:18| 分类:论文| 标签:|字号大中小订阅今天接到了一个TI的电路(SN65LVDT352)要求测试,以前没有接触过,今天在网上收集点资料, 拿来和大家分享.以后可能会用的上这种器件.LVDS:Low Voltage Differential Signaling,低电压差分信号。

LVDS传输支持速率一般在155Mbps(大约为77MHZ)以上。

LVDS是一种低摆幅的差分信号技术,它使得信号能在差分PCB线对或平衡电缆上以几百Mbps 的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗。

IEEE在两个标准中对LVDS信号进行了定义。

ANSI/TIA/EIA-644中,推荐最大速率为655Mbps,理论极限速率为1.923Mbps。

1.1 LVDS信号传输组成LVDS信号传输一般由三部分组成:差分信号发送器,差分信号互联器,差分信号接收器。

差分信号发送器:将非平衡传输的TTL信号转换成平衡传输的LVDS信号。

通常由一个IC来完成,如:DS90C031差分信号接收器:将平衡传输的LVDS信号转换成非平衡传输的TTL信号。

通常由一个IC来完成,如:DS90C032差分信号互联器:包括联接线(电缆或者PCB走线),终端匹配电阻。

按照IEEE规定,电阻为100欧。

我们通常选择为100,120欧。

1.2 LVDS信号电平特性LVDS物理接口使用1.2V偏置电压作为基准,提供大约400mV摆幅。

LVDS驱动器由一个驱动差分线对的电流源组成(通常电流为3.5mA),LVDS接收器具有很高的输入阻抗,因此驱动器输出的电流大部分都流过100Ω的匹配电阻,并在接收器的输入端产生大约350mV 的电压。

电流源为恒流特性,终端电阻在100――120欧姆之间,则电压摆动幅度为:3.5mA * 100 =350mV ;3.5mA * 120 = 420mV 。

LVDS与PECL(光收发器使用的电平)电平变化。

SN65LVDS048PWR中文资料

PACKAGING INFORMATIONOrderable Device Status (1)Package Type Package DrawingPins Package Qty Eco Plan (2)Lead/Ball FinishMSL Peak Temp (3)SN65LVDS048D OBSOLETE SOIC D 16TBD Call TI Call TI SN65LVDS048DR OBSOLETE SOIC D 16TBD Call TI Call TI SN65LVDS048PW OBSOLETE TSSOP PW 16TBD Call TI Call TI SN65LVDS048PWROBSOLETETSSOPPW16TBDCall TICall TI(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan -The planned eco-friendly classification:Pb-Free (RoHS)or Green (RoHS &no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free (RoHS):TI's terms "Lead-Free"or "Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all 6substances,including the requirement that lead not exceed 0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Green (RoHS &no Sb/Br):TI defines "Green"to mean Pb-Free (RoHS compatible),and free of Bromine (Br)and Antimony (Sb)based flame retardants (Br or Sb do not exceed 0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracyof such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.PACKAGE OPTION ADDENDUM30-Mar-2005Addendum-Page 1IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. T o minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements. Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetwork Microcontrollers Security /securityTelephony /telephonyVideo & Imaging /videoWireless /wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright 2005, Texas Instruments Incorporated。

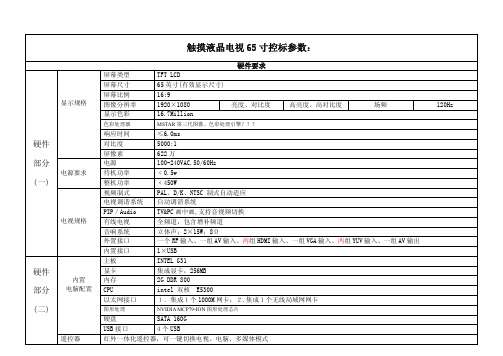

65红外触摸电视控标参数

对多余的误操作可以用撤销进行恢复。也可以相反操作。

1.更改背景颜色,颜色可以由用户自定义。2.使用纹理作为背景,各种格子如田字格、拼音格、五线谱等等教学格式。3.可以用图 背景、纹理

片文件作为背景。

保存 截图

批注模式

模式(一)

全屏模式 窗口模式 桌面鼠标 模式 打印

一键切换到电脑桌面

1.打印预览;2.打印整个文件所有页面

发送电子 邮件

将当前文件所有页面内容作为 ibd、PPT 或 PDF 等格式文件,然后当做邮件的附件进行发送

模式(二)

操作

多点 触控

快捷键

演示功能

1.聚光灯:用于演示的全屏聚光效果; 2.帘幕:遮挡全屏大部分区域的帘幕; 3.放大镜:可进一步设置放大效果的放大镜,可以放大电脑内所有软件和文档; 4.录像:不仅可以录制电子白板软件的操作,还可以录制电脑内其他软件的操作,而且接上麦克风还可以将语音录制下来,存为 avi 视频文件进行保存,便于今后播放;

鼠标双击 快速双击白板同一点

双指 双手

漫游操作 双手可放大、缩小、旋转图形

可两人同时在上面书写。此项为选项。非标准配置。

屏幕显示快捷键,包涵最常用的功能,便于快速选择功能进行操作

教学资源库

支持开放式,适合中学各学科教学用途的资源,并可增加内容和扩展学科资源。

特别要求

每台机器都要安装好适用的 Windows 平台和具有上述功能的触控软件。触摸屏生产厂家通过 ISO9000、ISO14000 认证,必须提 供证书复印件。 触摸屏产品必须通过 CE、FCC、ROHS 认证(须提供认证证书复印件),自主创新产品认证,国家高新技术企业。 软件部分必须具有独立知识产权,需提供产品底层控制软件著作权证书,软件著作权证书 ,加盖制造商公章。

各种线驱动器接收器的正确选择

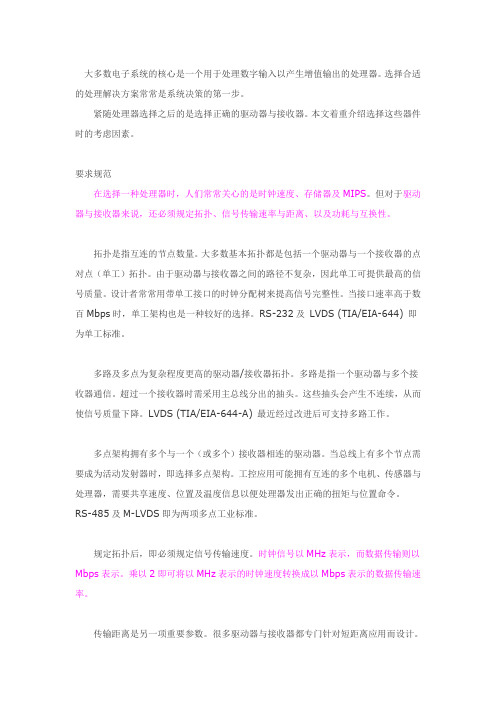

大多数电子系统的核心是一个用于处理数字输入以产生增值输出的处理器。

选择合适的处理解决方案常常是系统决策的第一步。

紧随处理器选择之后的是选择正确的驱动器与接收器。

本文着重介绍选择这些器件时的考虑因素。

要求规范在选择一种处理器时,人们常常关心的是时钟速度、存储器及MIPS。

但对于驱动器与接收器来说,还必须规定拓扑、信号传输速率与距离、以及功耗与互换性。

拓扑是指互连的节点数量。

大多数基本拓扑都是包括一个驱动器与一个接收器的点对点(单工)拓扑。

由于驱动器与接收器之间的路径不复杂,因此单工可提供最高的信号质量。

设计者常常用带单工接口的时钟分配树来提高信号完整性。

当接口速率高于数百Mbps时,单工架构也是一种较好的选择。

RS-232及LVDS (TIA/EIA-644) 即为单工标准。

多路及多点为复杂程度更高的驱动器/接收器拓扑。

多路是指一个驱动器与多个接收器通信。

超过一个接收器时需采用主总线分出的抽头。

这些抽头会产生不连续,从而使信号质量下降。

LVDS (TIA/EIA-644-A) 最近经过改进后可支持多路工作。

多点架构拥有多个与一个(或多个)接收器相连的驱动器。

当总线上有多个节点需要成为活动发射器时,即选择多点架构。

工控应用可能拥有互连的多个电机、传感器与处理器,需要共享速度、位置及温度信息以便处理器发出正确的扭矩与位置命令。

RS-485及M-LVDS即为两项多点工业标准。

规定拓扑后,即必须规定信号传输速度。

时钟信号以MHz表示,而数据传输则以Mbps表示。

乘以2即可将以MHz表示的时钟速度转换成以Mbps表示的数据传输速率。

传输距离是另一项重要参数。

很多驱动器与接收器都专门针对短距离应用而设计。

这些限制源自于所采用的信号传输(单端比差分)、电压电平与接收器的共模电压范围。

信号传输速率与传输距离之间存在着倒数关系。

对于大多数器件来说,信号传输速率会随距离增加而减小。

这种倒数关系是由于存在符号间干扰(ISI)。

SN65LVDS150PW资料

PACKAGING INFORMATIONOrderable Device Status (1)Package Type Package Drawing Pins Package Qty Eco Plan (2)Lead/Ball Finish MSL Peak Temp (3)SN65LVDS150PW ACTIVE TSSOP PW 2850None CU NIPDAU Level-2-220C-1YEAR SN65LVDS150PWRACTIVETSSOPPW282000NoneCU NIPDAULevel-2-220C-1YEAR(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan -May not be currently available -please check /productcontent for the latest availability information and additional product content details.None:Not yet available Lead (Pb-Free).Pb-Free (RoHS):TI's terms "Lead-Free"or "Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all 6substances,including the requirement that lead not exceed 0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Green (RoHS &no Sb/Br):TI defines "Green"to mean "Pb-Free"and in addition,uses package materials that do not contain halogens,including bromine (Br)or antimony (Sb)above 0.1%of total product weight.(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDECindustry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing orchemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.PACKAGE OPTION ADDENDUM11-Feb-2005Addendum-Page 1IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. T o minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements. Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetwork Microcontrollers Security /securityTelephony /telephonyVideo & Imaging /videoWireless /wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright 2005, Texas Instruments Incorporated。

UM-BUS总线传输系统的建模与仿真

UM-BUS总线传输系统的建模与仿真摘要: UM-BUS(动态可重构高速串行总线)是一种基于故障实时检测和动态重构的新型多通道高速串行总线。

UM-BUS总线的传输介质为屏蔽双绞线,传输通道采用MLVDS (TIA/EIA-899-2002)信号传送方式,能够支持多个节点设备直接连接。

基于传输线理论,采用Hyperlynx建立了UM-BUS总线物理线路的电阻隔离型、电容隔离型、阻容隔离型3种传输模型,并对仿真眼图及实测眼图进行了分析,确定了UM-BUS总线物理链路模型,为进一步研究UM-BUS总线传输系统提供了支持。

关键词:建模;仿真;眼图;动态可重构高速串行总线;Hyperlynx0 引言动态可重构高速串行总线(UM-BUS)是一种基于故障实时检测和动态重构的新型多通道高速串行总线。

该总线具有线路动态检错功能,能够实时检测总线系统线路状况,并能根据线路状况将通信数据动态均衡地分配到健康的传输线路上,实现了通信线路冗余容错与高速传输的有机统一。

UM-BUS总线采用多点低电压差分信号(Multipoint-Low-Voltage Differential Signaling,M-LVDS)传输技术[1],这种传输方式可满足多节点直接连接的需求,提高信号的传输速度和信号的抗噪能力。

UM-BUS总线采用100 Ω屏蔽双绞线作为传输介质,信息传输速率为100 Mb/s。

然而UM-BUS总线传输系统在传输信号时,信号波形易发生畸变,对传输质量有很大的影响[2]。

因此,应寻找合适的传输链路模型和参数来提高总线信号传输的可靠性。

本文在Hyperlynx中对UM-BUS总线的物理层进行建模,搭建3种耦合链路模型:电阻型链路模型、电容型链路模型、电阻电容型链路模型,将以上这3种模型进行建模仿真分析与实际测量,确定电阻电容型链路模型是传输质量最优的链路模型,对UM-BUS 总线起到全面的故障隔离的作用,波形畸变较小,误码率较低,提高了UM-BUS总线的可靠性。

SN65220DBVR中文资料

DBV-6PW-8P-8PACKAGING INFORMATIONOrderable Device Status (1)Package Type Package Drawing Pins Package Qty Eco Plan (2)Lead/Ball Finish MSL Peak Temp (3)SN65220DBVR ACTIVE SOT-23DBV 63000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN65220DBVT ACTIVE SOT-23DBV 6250Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN65220YZBR ACTIVE DSBGA YZB 43000None Call TI Level-1-260C-UNLIM SN65220YZBT ACTIVE DSBGA YZB 4250None Call TI Level-1-260C-UNLIM SN65240P ACTIVE PDIP P 850Pb-Free (RoHS)CU NIPDAU Level-NC-NC-NC SN65240PW ACTIVE TSSOP PW 8150None CU NIPDAU Level-1-220C-UNLIM SN65240PWR ACTIVE TSSOP PW 82000None CU NIPDAU Level-1-220C-UNLIM SN75240P ACTIVE PDIP P 850Pb-Free (RoHS)CU NIPDAU Level-NC-NC-NC SN75240PW ACTIVE TSSOP PW 8150None CU NIPDAU Level-1-220C-UNLIM SN75240PWLE OBSOLETE TSSOP PW 8None Call TI Call TISN75240PWR ACTIVE TSSOP PW 82000None CU NIPDAU Level-1-220C-UNLIM SN75240PWRG4PREVIEWTSSOPPW82000NoneCall TICall TI(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan -May not be currently available -please check /productcontent for the latest availability information andadditional product content details.None:Not yet available Lead (Pb-Free).Pb-Free (RoHS):TI's terms "Lead-Free"or "Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all 6substances,including the requirement that lead not exceed 0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Green (RoHS &no Sb/Br):TI defines "Green"to mean "Pb-Free"and in addition,uses package materials that do not contain halogens,including bromine (Br)or antimony (Sb)above 0.1%of total product weight.(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDECindustry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.PACKAGE OPTION ADDENDUM1-Mar-2005Addendum-Page 1IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. T o minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements. Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetwork Microcontrollers Security /securityTelephony /telephonyVideo & Imaging /videoWireless /wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright 2005, Texas Instruments Incorporated。

CAN总线远程传输可靠性的设计方法和实现

CAN总线远程传输可靠性的设计方法和实现2010-06-29 16:55:02 作者:杜洪亮张培仁王亮崔军辉来源:电子技术关键字:CAN总线C8051F040可靠性远程0 引言现场总线能同时满足过程控制和制造业自动化的需求,成为工业数据总线领域最为活跃的技术之一。

CAN(Controller Area Network,即控制器局域网)现场总线以其多主方式,报文自动过滤重发、极低的误码率和高通讯速率等特点,在各种低成本、高抗干扰的多机远程监控系统中得到广泛应用。

CAN总线属于总线式带同步位的串行通信网络,由于采用了许多新技术以及独特的设计,与一般的通信总线相比,CAN总线在远距离数据通信上具有突出的可靠性、实时性和灵活性。

CAN的直接通信距离最远可达lOkm(通信速率5Kbps以下),通信速率最高可达lMbps(通信距离最长40m)。

但在实际的远程传输过程中,通信数据受许多因素的影响,致使传输的波形失真,达不到预期的效果。

本文针对CAN总线远程传输的可靠性进行了设计与分析。

1 远程CAN总线传输可靠性的主要影响因素(1)工作环境电磁干扰的影响。

(2)传输介质分布电容和电阻的影响。

(3)远近端阻抗不匹配的影响。

(4)接收同步位端的相位变化和幅值变化的影响。

(5)传送波特率位时钟设计的影响。

(6)没有发送和接收帧的节点之问高阻状态性的漏电对CAN总线的影响。

(7)对总线短路和断路监测处理的影响。

2 远程CAN总线传输可靠性的设计方法系统运行在复杂的电磁空问里,有外界的各种电磁场变化,也有系统内部各个元器件之间的电磁干扰。

尤其工作现场的电磁场环境是最容易干扰系统的可靠性。

因此系统数据传输过程采用屏蔽双绞线,它综合了屏蔽线和双绞线两者的优点,是较理想的信号传输线,即可以抑制静电干扰,也可以抑制电磁感应干扰,从而提高系统的可靠性。

元器件是构成系统的基础,选择集成化程度高,抗干扰能力强,功耗又小的电子元器件尤为重要。

SN65LVDS1

Copyright © 1999–2006, Texas Instruments Incorporated

SN65LVDS1 SN65LVDS2 SN65LVDT2

SLLS373H – JULY 1999 – REVISED JULY 2006

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

Bus pins (A, B, Y, Z)

Machine-model electrostatic discharge, MM ESD(4)

Field-induced-charge device model electrostatic discharge, FCDM ESD(5)

Continuous total pesigned for Signaling Rates (1) up to: – 630 Mbps Drivers

– 400 Mbps Receivers

• Operates From a 2.4-V to 3.6-V Supply • Available in SOT-23 and SOIC Packages • Bus-Terminal ESD Exceeds 9 kV • Low-Voltage Differential Signaling With

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

一种基于MLVDS的SPI通信链路设计

3 结语

SPI作为一种常用的串行通信标准,众多的MCU中均 内置SP I接口,在层出不穷的嵌入式系统中不可避免地面 临与其他通信系统兼容的应用需求, 因此通过软件方法 拓展SPI接口的应用具有重要的意义。本文基于MLVDS链 路层标准的SPI总线接口提出的软件处理方法可以很好地 解决连续时钟时序下的SPI半双工通信,灵活、稳定和实时 性要求满足设计需要, 而且在硬件实现上简单可靠, 并且 兼容传统非连续时钟应用场合,可应用于后续类SP I通信 总线的工业或者航天嵌入式系统中。

14

钱小东 宣浩 葛鹏:一种基于 ML VD S 的 SPI 通信链路设计

2021年第 6 期

2.1 初始化流程 (1)使能所使用的GPIO引脚时钟功能,并设置SPI1相关 引脚为复用功能; (2)通过配置SPI1_CR1寄存器初始化SPI1,分别设置为 半双工串行收方式, 从机模式, 8 位数据格式, 同步串行时 钟在空闲状态设为低电平, 并在串行同步时钟有效的第 一个跳变沿采样数据, 从机节点选择( N S S ) 引脚设置为软 件控制, SP I 波特率预分频值选择2 , 数据传输顺序高字节 在前且M SB 位在前, CR C 校验多项式设为7 。初始化操作 之后禁用SPI1并不使能SPI1接收中断; (3)根据硬件设计,使用PE4作为SPI通信片选信号,使 能PE4引脚时钟并配置为输入模式,随后开启SYSCFG时 钟,并设置PE4口与EXIT4中断线映射,然后设置中断线4 上的中断模式为任意电平( 上升沿或下降沿) 触发, 并使能 中断线。最后, 设置中断分组并使能中断。 2.2 外部中断服务程序 外部中断服务处理过程主要是判断中断线4 发生中断 的跳边沿类型,如果是下降沿中断,则说明SPI主机节点片 选本从机节点并开始发送控制命令,所以立即使能SPI1时 钟,启动SPI1并使能SPI1接收中断RXNE;如果是上升沿中 断,则说明SPI通信结束,此时执行上述步骤(2)中的SPI1初 始化流程, 将内置的S P I 1 硬核资源恢复初始态。 2.3 SPI1接收中断服务程序 根据SPI初始化配置,在片选信号低电平有效期间,每 8 个时钟的最后一个采样时钟边沿出现时, R X N E 位将置 1 , 产生中断, 移位寄存器中接收的数据字节被拷贝到接 收缓冲区中,读取SP I_DR 寄存器将SPI接收中断标志位 (RXNE)清零。SPI接收中断服务程序中读取接收缓冲区中

SN65MLVD206B具有IECESD保护的多点LVDS…

DE D RE RA B Y ZCopyright © 2016,Texas Instruments IncorporatedDE D RE RA BCopyright © 2016,Texas Instruments IncorporatedProductFolder OrderNow TechnicalDocuments Tools &SoftwareSupport &CommunitySN65MLVD206BZHCSFW6–DECEMBER 2016SN65MLVD206B 具有IEC ESD 保护的多点LVDS 线路驱动器和接收器(收发器)1特性•符合M-LVDS 标准TIA/EIA-899,适用于多点数据交换•低压差分30Ω至55Ω线路驱动器和接收器,适用于高达200Mbps 的信号传输速率(1)、高达100MHz 的时钟频率–1类接收器整合了25mV 迟滞(201B 和203B )–2类接收器可提供一个偏移阈值来检测开路和空闲总线条件(206B 和207B )•总线I/O 保护–>±8kV HBM–>±8kV IEC 61000-4-2接触放电•可控的驱动器输出电压转换时间可改进信号质量•-1V 至3.4V 共模电压范围允许在2V 接地噪声下传输数据•总线引脚在禁用或V CC ≤1.5V 时具有高阻抗•提供100Mbps 器件(SN65MLVD200B ,202B ,204B ,205B )•是SN65MLVD201、203、206和207的改进替代方案(1)线路的信号传输速率是指每秒钟的电压转换次数,单位为bps (每秒比特数)2应用•低功耗、高速和短行程可替代TIA/EIA-485•背板或电缆连接的多点数据和时钟传输•蜂窝基站•局端交换机•网络交换机和路由器3说明SN65MLVD201B 、SN65MLVD203B 、SN65MLVD206B 、SN65MLVD207B 器件均为多点低压差分(M-LVDS)线路驱动器和接收器,它们均经过优化,支持的信号传输速率可高达200Mbps 。

SN65DSI84-Q1汽车用单通道MIPIDSILVDS

TFT LCD DisplayCopyright © 2016, Texas Instruments IncorporatedProduct Folder Order Now Technical Documents Tools &SoftwareSupport &CommunitySN65DSI84-Q1ZHCSFS1–DECEMBER 2016SN65DSI84-Q1汽车用单通道MIPI ®DSI 转双链路LVDS 桥接器1特性•适用于汽车电子应用•具有符合AEC-Q100标准的下列结果:–器件温度等级2:-40°C 至105°C 的环境运行温度范围–器件人体放电模式(HBM)静电放电(ESD)分类等级3A–器件组件充电模式(CDM)ESD 分类等级C6•实现了MIPI D-PHY 版本1.00.00物理层前端和显示屏串行接口(DSI)版本1.02.00•单通道DSI 接收器每通道可配置1、2、3或4条D-PHY 数据信道,每条信道的运行速率高达1Gbps•支持RGB666和RGB888格式的18bpp 与24bpp DSI 视频流•适合60fps WUXGA 1920×1200分辨率(18bpp 和24bpp 颜色),以及60fps 1366×768分辨率(18bpp 和24bpp 颜色)•针对单链路或双链路LVDS 的输出配置•支持单通道DSI 转单链路LVDS 的操作模式•双链路或单链路模式下LVDS 输出时钟范围为25MHz 到154MHz•LVDS 像素时钟可由自由运行持续D-PHY 时钟或外部基准时钟(REFCLK)供源• 1.8V 主V CC 电源•低功耗特性包括关断模式、低LVDS 输出电压摆幅、共模以及MIPI 超低功耗状态(ULPS)支持•针对简化印刷电路板(PCB)走线的LVDS 通道交换(SWAP),LVDS 引脚顺序反向特性•采用64引脚10mm ×10mm HTQFP (PAP)封装PowerPAD™IC 封装2应用•集成显示屏的信息娱乐系统主机•具有远程显示屏的信息娱乐系统主机•后座信息娱乐系统•混合动力汽车仪表板•便携式导航设备(PND)•导航•工业人机界面(HMI)和显示屏3说明SN65DSI84-Q1DSI 转LVDS 桥接器具有一个单通道MIPI D-PHY 接收器前端配置,此配置中在每个通道上具有4条信道,每条信道的运行速率为1Gbps ,最大输入带宽为4Gbps 。

马疱疹病毒l型gB糖蛋白线性B细胞表位的预测与鉴定

Copyright©博看网. All Rights Reserved.

%)H(

中!国!畜!牧!兽!医

)) 卷 !

表#!根据预测的 ) 细胞表位合成的寡聚核苷酸链

F0A58#!^5*?+,:258+1*;836,1783*3022+.;*,?1+178E.8;*21*+,+-)28558E*1+E83

LVd!%的诊断 在 马 疱 疹 病 毒 防 制 中 有 重 要 的 作用!随着 LVd!%的防 制 措 施 的 实 施!流 行 区 的 感 染率明显下降&常规的免疫学检测方法多为检测阳 性血清!成分复杂 且 成 本 较 高& 同 时!由 于 8; 糖 蛋 白分子质量大!制备 表 达 并 保 持 该 蛋 白 的 天 然 构 象 较困难!因此!可选择该蛋 白 表 位 作 为 研 究 对 象 & )%0* 本研究利用生物 信 息学综合预测 ; 细 胞表 位!将 预 测的表位合成'表 达 及 纯 化!能 被 LVd!% 阳 性 血 清 所识别!为进一步表 位 疫 苗 的 设 计 和 新 型 诊 断 试 剂 的研发奠定基础&

4A31.021$W73D9S"NXMDM$43"9#653"$,9;,3EE36$9#63D$-8;8EN,#65#93$-#Z3TS$-373563D[$5SD 9N63% "LVd!%#X$972$#$-Z#54M9$,D!M-"D3E3,936$9#63DX7$,77M"6#93-9$ME"$M8-#D9$,[MES3' W73aPIZ5M843-9D#Z8;8EN,#65#93$-X353653"$,93"2N65#93M-#ZaPIC9M5D#Z9XM53'C,533-! $-86#93-9$ME;,3EE36$9#63DMZ9356M5M43935,#46M5$D#-!9739M5839;,3EE36$9#63DX353D3E3,93"! ,E#-3"M-"3F653DD3"'W733F653DD3"ZSD$#-65#93$-DD35[$,3"MDM-M-9$83- X353SD3"9#53M,9 X$973TS$-373563D[$5SD6#D$9$[3D35S4 9#D,533-M-"$"3-9$ZNM-9$83-$,36$9#63D'W7353DSE9D D7#X3"97M9M,,#5"$-89#653"$,9$[3M-"M-MEND$D!973M53MD#ZM4$-#M,$"Z5#4(9#%&!0*9#*0! 1*9#(1!/09#AH!%%%9#%0&!%109#%((!%/*9#%H& 4$879238;8EN,#65#93$-;,3EE36$9#63D' C3[3-36$9#63DX353DS,,3DDZSEEN,E#-3"$-9#M65#.M5N#9$,3F653DD$#-[3,9#5!M-",#-Z$543"2N aPID3TS3-,$-8'IZ9353F653DD$#-M-"6S5$Z$,M9$#-!`3D935-2E#99$-8 XMD635Z#543"9#"393,9 973M-9$83-!X7$,7,#SE"2353,#8-$Y3"2N3TS$-373563D[$5SD6#D$9$[3D35M';$#$-Z#54M9$,D93,7! -#E#8NM-" 4#E3,SEM52$#E#8N93,7-$TS3D X353SD3"9#DS,,3DDZSEEND,533-Z$[36#93-9$ME;,3EE 36$9#63D!X7$,765#[$"3"973Z#S-"M9$#-Z#5973"$M8-#D$D#ZLVd!%M-""3D$8-#Z97336$9#63 [M,,$-3' B86C+.;3$;!,3EE36$9#63(M-9$83-$,36$9#63653"$,9$#-(65#.M5N#9$,3F653DD$#-($"3-9$Z$,M9$#-

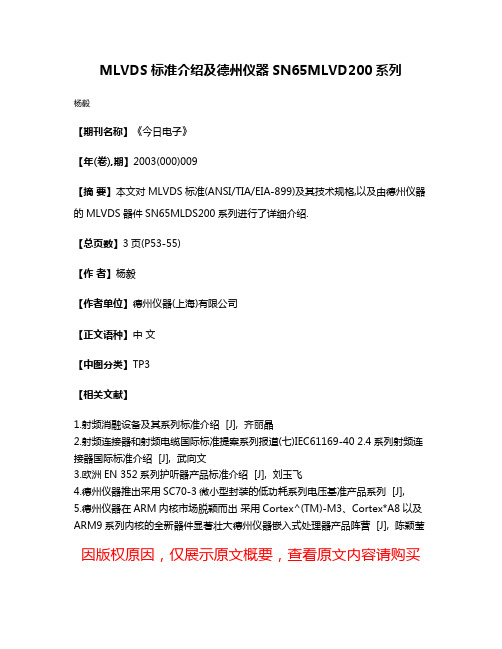

MLVDS标准介绍及德州仪器SN65MLVD200系列

MLVDS标准介绍及德州仪器SN65MLVD200系列

杨毅

【期刊名称】《今日电子》

【年(卷),期】2003(000)009

【摘要】本文对MLVDS标准(ANSI/TIA/EIA-899)及其技术规格,以及由德州仪器的MLVDS器件SN65MLDS200系列进行了详细介绍.

【总页数】3页(P53-55)

【作者】杨毅

【作者单位】德州仪器(上海)有限公司

【正文语种】中文

【中图分类】TP3

【相关文献】

1.射频消融设备及其系列标准介绍 [J], 齐丽晶

2.射频连接器和射频电缆国际标准提案系列报道(七)IEC61169-40 2.4系列射频连接器国际标准介绍 [J], 武向文

3.欧洲EN 352系列护听器产品标准介绍 [J], 刘玉飞

4.德州仪器推出采用SC70-3微小型封装的低功耗系列电压基准产品系列 [J],

5.德州仪器在ARM内核市场脱颖而出采用Cortex^(TM)-M3、Cortex*A8以及ARM9系列内核的全新器件显著壮大德州仪器嵌入式处理器产品阵营 [J], 陈颖莹

因版权原因,仅展示原文概要,查看原文内容请购买。

特校65寸液晶一体机参数

台

1

2

计算机主机

1、1L小型机箱电脑主机;电源在机箱外单独供电。

2、主机:处理器: 不低于Core i3-4160/1L小型机箱/H81主板/内存:4G DDR3 1600MHz /硬盘容量:500G, SATAⅢ /外围设备接口:前置1*USB2.0+1*USB3.0、1*MIC + 1*耳机、1*SD Card;后置2*USB2.0+1*USB3.0、1*耳机/MIC COMBO接口、1*RJ45、1*VGA、1*DP

★17、软件支持3D模型导入,可直接插入通用的dae,obj,fbx格式的3D模型,实现模型360度翻转,重点标记并时刻保持关联功能。

18、软件打开后,可设定背景透明,方便老师在任意屏幕表面上使用白板软件提供的工具进行操作,如书写文字、绘制图形等。用户添加的内容实际上都添加到了当前的白板软件的页面上。方便需要频繁切换白板软件和计算机中其它软件的老师进行操作。

2、腔体分左右两边,一边安装电路和固定电脑主机,电脑主机须用螺丝等材料固定,一边腔体放置各种课堂教学需使用的多媒体设备(如无线键盘、鼠标等),拉开后可以作简易的操作平台。两边腔体防尘防盗带锁(两个锁钥匙是否通用按照学校实际需要确定,教学和维护确保互不干扰)。提供6位电源插座一个。

3、安装在交互式电视一体机下部,固定在墙体,安装方式为:在箱体背面板四角由四个8*100mm的膨胀螺栓固定,要求安装牢固、安全可靠(也可根据用户要求安装)。

8、提供中国质量认证中心颁发的中国节能产品认证证书(2级能效及以上);并提供入围第十六期节能产品政府采购清单证明;

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

元器件交易网

SN65MLVD201, SN65MLVD203 SN65MLVD206, SN65MLVD207

SLLS558A – DECEMBER 2002 – JUNE 2003

MULTIPOINT-LVDS LINE DRIVER AND RECEIVER

D Bus Pins High Impedance When Disabled or

VCC ≤ 1.5 V

D 100-MΒιβλιοθήκη ps Devices Available

(SN65MLVD200, 202, 204, 205)

APPLICATIONS D Low-Power High-Speed Short-Reach

Copyright 2002 – 2003, Texas Instruments Incorporated

元器件交易网 SN65MLVD201, SN65MLVD203

SN65MLVD206, SN65MLVD207

SLLS558A – DECEMBER 2002 – JUNE 2003

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

D Backplane or Cabled Multipoint Data and

Clock Transmission

D Cellular Base Stations D Central-Office Switches D Network Switches and Routers DESCRIPTION

D Power Up/Down Glitch Free D Controlled Driver Output Voltage Transition

Times for Improved Signal Quality

D –1 V to 3.4 V Common-Mode Voltage Range

Allows Data Transfer With 2 V of Ground Noise

ORDERING INFORMATION

PART NUMBER SN65MLVD201D SM65MLVD203D SN65MLVD206D SM65MLVD207D FOOTPRINT SN75176 SN75ALS180 SN75176 SN75ALS180 RECEIVER TYPE Type 1 Type 1 Type 2 Type 2 PACKAGE MARKING MF201 MLVD203 MF206 MLVD207

Alternative to TIA/EIA-485

LOGIC DIAGRAM (POSITIVE LOGIC)

SN65MLVD201, SN65MLVD206 DE D RE R 3 4 2 1 6 7 A B D DE RE R SN65MLVD203, SN65MLVD207 5 4 3 2 12 11 A B 9 10 Y Z

FEATURES D Low-Voltage Differential 30-Ω to 55-Ω Line D Type-1 Receivers Incorporate 25 mV of

Hysteresis Drivers and Receivers for Signaling Rates(1) Up to 200 Mbps

RECOMMENDED OPERATING CONDITIONS

MIN Supply voltage, VCC High-level input voltage, VIH Low-level input voltage, VIL Voltage at any bus terminal VA, VB, VY or VZ Magnitude of differential input voltage, VID Operating free-air temperature, TA 3 2 GND –1.4 0.05 –40 NOM 3.3 MAX UNIT 3.6 VCC 0.8 3.8 VCC 85 V V V V V °C

D Type-2 Receivers Provide an Offset

(100 mV) Threshold to Detect Open-Circuit and Idle-Bus Conditions

D Meets or Exceeds the M-LVDS Standard

TIA/EIA-899 for Multipoint Data Interchange

Electrostatic discharge

(1) Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. (2) All voltage values, except differential I/O bus voltages, are with respect to network ground terminal. (3) Tested in accordance with JEDEC Standard 22, Test Method A114–A. (4) Tested in accordance with JEDEC Standard 22, Test Method C101.

ABSOLUTE MAXIMUM RATINGS

over operating free-air temperature range unless otherwise noted(1) SN65MLVD201, 203, 206, AND 207 Supply voltage range(2), VCC D, DE, RE Input In ut voltage range A, B (201, 206) A, B (203, 207) R O t t voltage Output lt range Y, Z, A, or B H Human B Body d M Model d l(3) Charged-Device Model(4) Continuous power dissipation Storage temperature range A, B, Y, and Z All pins All pins –0.5 V to 4 V –0.5 V to 4 V –1.8 V to 4 V –4 V to 6 V –0.3 V to 4 V –1.8 V to 4 V ±8 kV ±2 kV ±1500 V See Dissipation Rating Table –65°C to 150°C