AD408M166RBB-5中文资料

3845B中文资料

TOP-SIDE MARKING TL2842BP TL2843BP TL2844BP TL2845BP 2842B

2843B

2844B

2845B

TL2842B

TL2843B

TL2844B

TL2845B TL3842BP TL3843BP TL3844BP TL3845BP 3842B

3843B

3844B

元器件交易网

TL284xB, TL384xB HIGH-PERFORMANCE CURRENT-MODE PWM CONTROLLERS

SLVS610A – AUGUST 2006 – REVISED SEPTEMBER 2006

FEATURES

• Low Start-Up Current (<0.5 mA) • Trimmed Oscillator Discharge Current • Current Mode Operation to 500 kHz • Automatic Feed-Forward Compensation • Latching PWM for Cycle-by-Cycle Current

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

TL2842BD-8

Reel of 2500

mini smd 可编程数字AD型热释电红外传感器S22-P340R 使用说明书

MINI SMD 可编程数字AD 型热释电红外传感器Mini SMD Programmable AD Pyroelectric Infrared SensorsS22-P340R 使用说明书V1.2森霸传感科技股份有限公司Senba Sensing Technology Co.,Ltd.森霸传感科技股份有限公司1.企业及产品概况:1.1体系认证●ISO14001认证公司获得ISO14001认证,在遵守国家环保法的基础上,通过采取各种改进措施,实现企业可持续性发展。

●ISO 9001认证公司获得国际标准化机构(ISO)的品质保证标准-即“ISO 9001”的认证。

1.2关于欧盟ROHS指令ROHS指令:欧盟提出的“关于在电子电气设备中限制使用某些有害物质的指令2011/65/EC”,公司生产的所有产品均符合欧盟ROHS指令。

1.3产品型号及检测原理1.3.1产品规格型号:本产品为SMD 数字AD 型双元热释电红外传感器,产品型号为S22-P340R ,版本号为V1.2,若使用产品超出了产品列举的应用范围,请及时咨询产品应用或销售工程师。

1.3.2产品探测原理:传感器核心部件由热释电探测敏感元、红外滤光片和芯片IC三部分组成,其中探测敏感元为双元结构。

是一款用于低功耗运动检测的红外热释电传感器(PIR)。

利用MCU进行通信,当S22-P340R 进行连续运动传感时,MCU不需要激活,它只在检测到运动时才激活外部MCU。

运动检测结果通过输出中断信号发出。

运动检测的算法是可编程的,可以通过外部MCU配置来改变。

PIR信号在芯片上转换为一个14位的数字值,然后进入运动算法检测单元。

所有的信号处理都是数字化的,可支持运动检测结果输出和原始数据输出。

2.非商业用途说明森霸传感科技股份有限公司(以下简称森霸)免费授权用户非商业性使用本产品说明书,并为用户提供产品变更和咨询服务。

若要进行商业性的销售、复制、散发或其他商业活动,须事先获取森霸的书面授权和许可。

MM24512-BN5T中文资料

1/24February 2005M24512512 Kbit Serial I²C Bus EEPROMFEATURES SUMMARY■Two-Wire I 2C Serial Interface Supports 400kHz Protocol ■Supply Voltage Ranges:– 1.8V to 5.5V (M24512 − R)– 2.5V to 5.5V (M24512 − W)■Write Control Input■BYTE and PAGE WRITE (up to 128 Bytes)■RANDOM and SEQUENTIAL READ Modes ■Self-Timed Programming Cycle ■Automatic Address Incrementing ■Enhanced ESD/Latch-Up Protection ■More than 100,000 Erase/Write Cycles ■More than 40-Year Data RetentionTable 1. M24512 devicesReference Part Number M24512M24512 − W M24512 − RM24512TABLE OF CONTENTSFEATURES SUMMARY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1Table 1.M24512 devices. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Figure 1.Packages. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Figure 2.Logic Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4 Table 2.Signal Names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4 Power On Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4 Figure 3.DIP, SO and TSSOP Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4SIGNAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5Serial Clock (SCL). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5 Serial Data (SDA) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5 Chip Enable (E0, E1, E2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5 Write Control (WC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5 Figure 4.Maximum R P Value versus Bus Parasitic Capacitance (C) for an I2C Bus. . . . . . . . . . . .5 Figure 5.I2C Bus Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6 Table 3.Device Select Code. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6 Table 4.Most Significant Byte. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6 Table 5.Least Significant Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6DEVICE OPERATION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7Start Condition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7 Stop Condition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7 Acknowledge Bit (ACK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7 Data Input. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7 Memory Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7 Table 6.Operating Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7 Figure 6.Write Mode Sequences with WC=1 (data write inhibited). . . . . . . . . . . . . . . . . . . . . . . . .8 Write Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 Byte Write. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 Page Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9 Figure 7.Write Mode Sequences with WC=0 (data write enabled) . . . . . . . . . . . . . . . . . . . . . . . . .9 Figure 8.Write Cycle Polling Flowchart using ACK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10 Minimizing System Delays by Polling On ACK. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10 Figure 9.Read Mode Sequences. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11 Read Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11 Random Address Read. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11 Current Address Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11 Sequential Read. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12 Acknowledge in Read Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12INITIAL DELIVERY STATE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12MAXIMUM RATING. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13 Table 7.Absolute Maximum Ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .132/24M24512DC AND AC PARAMETERS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14Table 8.Operating Conditions (M24512 – W). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14 Table 9.Operating Conditions (M24512 – R) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14 Table 10.AC Measurement Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14 Figure 10.AC Measurement I/O Waveform. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14 Table 11.Input Parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15 Table 12.DC Characteristics (M24512 – W). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15 Table 13.DC Characteristics(1) (M24512 – R) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15 Table 14.AC Characteristics (M24512 – W). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16 Table 15.AC Characteristics(1) (M24512 – R) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16 Figure 11.AC Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17PACKAGE MECHANICAL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18Figure 12.PDIP8 – 8 pin Plastic DIP, 0.25mm lead frame, Package Outline . . . . . . . . . . . . . . . . .18 Table 16.PDIP8 – 8 pin Plastic DIP, 0.25mm lead frame, Package Mechanical Data. . . . . . . . . .18 Figure 13.SO8W – 8 lead Plastic Small Outline, 208 mils body width, Package Outline . . . . . . . .19 Table 17.SO8W – 8 lead Plastic Small Outline, 208 mils body width, Package Mechanical Data.19 Figure 14.SO8N – 8 lead Plastic Small Outline, 150 mils body width, Package Outline. . . . . . . . .20 Table 18.SO8N – 8 lead Plastic Small Outline, 150 mils body width, Package Mechanical Data .20 Figure 15.TSSOP8 – 8 lead Thin Shrink Small Outline, Package Outline . . . . . . . . . . . . . . . . . . .21 Table 19.TSSOP8 – 8 lead Thin Shrink Small Outline, Package Mechanical Data. . . . . . . . . . . .21PART NUMBERING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22 Table 20.Ordering Information Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22REVISION HISTORY. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23 Table 21.Document Revision History. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .233/24M245124/24SUMMARY DESCRIPTIONThese I 2C-compatible electrically erasable pro-grammable memory (EEPROM) devices are orga-nized as 64K x 8 bits.Table 2. Signal NamesI 2C uses a two-wire serial interface, comprising a bi-directional data line and a clock line. The devic-es carry a built-in 4-bit Device Type Identifier code (1010) in accordance with the I 2C bus definition.The device behaves as a slave in the I 2C protocol,with all memory operations synchronized by the serial clock. Read and Write operations are initiat-ed by a Start condition, generated by the bus mas-ter. The Start condition is followed by a Device Select Code and Read/Write bit (RW) (as de-scribed in Table 3.), terminated by an acknowl-edge bit.When writing data to the memory, the device in-serts an acknowledge bit during the 9th bit time,following the bus master’s 8-bit transmission.When data is read by the bus master, the bus master acknowledges the receipt of the data byte in the same way. Data transfers are terminated by a Stop condition after an Ack for Write, and after a NoAck for Read.Power On ResetIn order to prevent data corruption and inadvertent Write operations during Power-up, a Power On Reset (POR) circuit is included. At Power-up, the device will not respond to any command until V CC has reached the Power On Reset threshold volt-age (this threshold is lower than the V CC min oper-ating voltage defined in Tables 8 and 9). In the same way, as soon as V CC drops from the normal operating voltage, below the Power On Reset threshold voltage, the device stops to respond to any command.Prior to selecting and issuing commands to the memory, a valid and stable V CC voltage must be applied. This voltage must remain stable and valid until the end of the transmission of the command and, for a Write instruction, until the completion of the internal write cycle (t W ).sions, and how to identify pin-1.E0, E1, E2Chip Enable SDA Serial Data SCL Serial Clock WC Write Control V CC Supply Voltage V SSGroundM24512 SIGNAL DESCRIPTIONSerial Clock (SCL).This input signal is used to strobe all data in and out of the device. In applica-tions where this signal is used by slave devices to synchronize the bus to a slower clock, the bus master must have an open drain output, and a pull-up resistor must be connected from Serial Clock (SCL) to V CC. (Figure 4. indicates how the value of the pull-up resistor can be calculated). In most applications, though, this method of synchro-nization is not employed, and so the pull-up resis-tor is not necessary, provided that the bus master has a push-pull (rather than open drain) output. Serial Data (SDA).This bi-directional signal is used to transfer data in or out of the device. It is an open drain output that may be wire-OR’ed with other open drain or open collector signals on the bus. A pull up resistor must be connected from Se-rial Data (SDA) to V CC. (Figure 4. indicates how the value of the pull-up resistor can be calculated).Chip Enable (E0, E1, E2).These input signals are used to set the value that is to be looked for on the three least significant bits (b3, b2, b1) of the 7-bit Device Select Code. These inputs must be tied to V CC or V SS, to establish the Device Select Code. When not connected (left floating), these in-puts are read as Low (0,0,0).Write Control (WC).This input signal is useful for protecting the entire contents of the memory from inadvertent write operations. Write opera-tions are disabled to the entire memory array when Write Control (WC) is driven High. When uncon-nected, the signal is internally read as V IL, and Write operations are allowed.When Write Control (WC) is driven High, Device Select and Address bytes are acknowledged, Data bytes are not acknowledged.25/24M245122Table 3. Device Select CodeDevice Type Identifier1Chip Enable Address2RW b7b6b5b4b3b2b1b0 Device Select Code1010E2E1E0RW Note: 1.The most significant bit, b7, is sent first.2.E0, E1 and E2 are compared against the respective external pins on the memory device.Table 4. Most Significant Byte Table 5. Least Significant Byteb15 b14 b13 b12 b11 b10 b9 b8b7 b6 b5 b4 b3 b2 b1 b0 6/247/24M24512DEVICE OPERATIONThe device supports the I 2C protocol. This is sum-marized in Figure 5.. Any device that sends data on to the bus is defined to be a transmitter, and any device that reads the data to be a receiver.The device that controls the data transfer is known as the bus master, and the other as the slave de-vice. A data transfer can only be initiated by the bus master, which will also provide the serial clock for synchronization. The M24512 device is always a slave in all communication.Start ConditionStart is identified by a falling edge of Serial Data (SDA) while Serial Clock (SCL) is stable in the High state. A Start condition must precede any data transfer command. The device continuously monitors (except during a Write cycle) Serial Data (SDA) and Serial Clock (SCL) for a Start condition,and will not respond unless one is given.Stop ConditionStop is identified by a rising edge of Serial Data (SDA) while Serial Clock (SCL) is stable and driv-en High. A Stop condition terminates communica-tion between the device and the bus master. A Read command that is followed by NoAck can be followed by a Stop condition to force the device into the Stand-by mode. A Stop condition at the end of a Write command triggers the internal Write cycle.Acknowledge Bit (ACK)The acknowledge bit is used to indicate a success-ful byte transfer. The bus transmitter, whether it be bus master or slave device, releases Serial Data (SDA) after sending eight bits of data. During the 9th clock pulse period, the receiver pulls SerialData (SDA) Low to acknowledge the receipt of the eight data bits.Data InputDuring data input, the device samples Serial Data (SDA) on the rising edge of Serial Clock (SCL).For correct device operation, Serial Data (SDA)must be stable during the rising edge of Serial Clock (SCL), and the Serial Data (SDA) signal must change only when Serial Clock (SCL) is driv-en Low.Memory AddressingTo start communication between the bus master and the slave device, the bus master must initiate a Start condition. Following this, the bus master sends the Device Select Code, shown in Table 3.(on Serial Data (SDA), most significant bit first).The Device Select Code consists of a 4-bit Device Type Identifier, and a 3-bit Chip Enable “Address”(E2, E1, E0). To address the memory array, the 4-bit Device Type Identifier is 1010b.Up to eight memory devices can be connected on a single I 2C bus. Each one is given a unique 3-bit code on the Chip Enable (E0, E1, E2) inputs.When the Device Select Code is received, the de-vice only responds if the Chip Enable Address is the same as the value on the Chip Enable (E0, E1,E2) inputs.The 8th bit is the Read/Write bit (RW). This bit is set to 1 for Read and 0 for Write operations.If a match occurs on the Device Select code, the corresponding device gives an acknowledgment on Serial Data (SDA) during the 9th bit time. If the device does not match the Device Select code, it deselects itself from the bus, and goes into Stand-by mode.Table 6. Operating ModesNote: 1.X = V IH or V IL .ModeRW bit WC 1Bytes Initial SequenceCurrent Address Read 1X 1START, Device Select, RW = 1Random Address Read 0X 1START, Device Select, RW = 0, Address 1X reSTART, Device Select, RW = 1Sequential Read 1X ≥ 1Similar to Current or Random Address Read Byte Write 0V IL 1START, Device Select, RW = 0Page WriteV IL≤ 128START, Device Select, RW = 0M245128/24Write OperationsFollowing a Start condition the bus master sends a Device Select Code with the Read/Write bit (RW) reset to 0. The device acknowledges this, as shown in Figure 7., and waits for two address bytes. The device responds to each address byte with an acknowledge bit, and then waits for the data byte.Writing to the memory may be inhibited if Write Control (WC) is driven High. Any Write instruction with Write Control (WC) driven High (during a pe-riod of time from the Start condition until the end of the two address bytes) will not modify the memory contents, and the accompanying data bytes are not acknowledged, as shown in Figure 6..Each data byte in the memory has a 16-bit (two byte wide) address. The Most Significant Byte (Ta-ble 4.) is sent first, followed by the Least Signifi-cant Byte (Table 5.). Bits b15 to b0 form the address of the byte in memory.When the bus master generates a Stop condition immediately after the Ack bit (in the “10th bit” time slot), either at the end of a Byte Write or a Page Write, the internal Write cycle is triggered. A Stop condition at any other time slot does not trigger the internal Write cycle.After the Stop condition, the delay t W , and the suc-cessful completion of a Write operation, the de-vice’s internal address counter is incremented automatically, to point to the next byte address af-ter the last one that was modified.During the internal Write cycle, Serial Data (SDA)is disabled internally, and the device does not re-spond to any requests.Byte WriteAfter the Device Select code and the address bytes, the bus master sends one data byte. If the addressed location is Write-protected, by Write Control (WC) being driven High, the device replies with NoAck, and the location is not modified. If, in-stead, the addressed location is not Write-protect-M24512ed, the device replies with Ack. The bus master terminates the transfer by generating a Stop con-dition, as shown in Figure 7.Page WriteThe Page Write mode allows up to 128 bytes to be written in a single Write cycle, provided that they are all located in the same ’row’ in the memory: that is, the most significant memory address bits (b15-b7) are the same. If more bytes are sent than will fit up to the end of the row, a condition known as ‘roll-over’ occurs. This should be avoided, as data starts to become overwritten in an implemen-tation dependent way.The bus master sends from 1 to 128 bytes of data, each of which is acknowledged by the device if Write Control (WC) is Low. If Write Control (WC) is High, the contents of the addressed memory loca-tion are not modified, and each data byte is fol-lowed by a NoAck. After each byte is transferred, the internal byte address counter (the 7 least sig-nificant address bits only) is incremented. The transfer is terminated by the bus master generat-ing a Stop condition.9/24M2451210/24Minimizing System Delays by Polling On ACK During the internal Write cycle, the device discon-nects itself from the bus, and writes a copy of the data from its internal latches to the memory cells.The maximum Write time (t w ) is shown in Table 14., but the typical time is shorter. To make use of this, a polling sequence can be used by the bus master.The sequence, as shown in Figure 8., is:–Initial condition: a Write cycle is in progress.–Step 1: the bus master issues a Start condition followed by a Device Select Code (the first byte of the new instruction).–Step 2: if the device is busy with the internal Write cycle, no Ack will be returned and the bus master goes back to Step 1. If the device has terminated the internal Write cycle, it responds with an Ack, indicating that the device is ready to receive the second part of the instruction (the first byte of this instruction having been sent during Step 1).Note: 1.The seven most significant bits of the Device Select Code of a Random Read (in the 1st and 4th bytes) must be identical.Read OperationsRead operations are performed independently of the state of the Write Control (WC) signal.After the successful completion of a Read opera-tion, the device’s internal address counter is incre-mented by one, to point to the next byte address. Random Address ReadA dummy Write is first performed to load the ad-dress into this address counter (as shown in Fig-ure 9.) but without sending a Stop condition. Then, the bus master sends another Start condition, and repeats the Device Select Code, with the Read/ Write bit (RW) set to 1. The device acknowledges this, and outputs the contents of the addressed byte. The bus master must not acknowledge the byte, and terminates the transfer with a Stop con-dition.Current Address ReadFor the Current Address Read operation, following a Start condition, the bus master only sends a De-vice Select Code with the Read/Write bit (RW) set to 1. The device acknowledges this, and outputs the byte addressed by the internal address counter. The counter is then incremented. The bus master terminates the transfer with a Stop condi-tion, as shown in Figure 9., without acknowledging the byte.11/24Sequential ReadThis operation can be used after a Current Ad-dress Read or a Random Address Read. The bus master does acknowledge the data byte output,and sends additional clock pulses so that the de-vice continues to output the next byte in sequence. To terminate the stream of bytes, the bus master must not acknowledge the last byte, and must generate a Stop condition, as shown in Figure 9. The output data comes from consecutive address-es, with the internal address counter automatically incremented after each byte output. After the last memory address, the address counter ‘rolls-over’, and the device continues to output data from memory address 00h.Acknowledge in Read ModeFor all Read commands, the device waits, aftereach byte read, for an acknowledgment during the 9th bit time. If the bus master does not drive SerialData (SDA) Low during this time, the device termi-nates the data transfer and switches to its Stand-by mode.INITIAL DELIVERY STATEThe device is delivered with all bits in the memory array set to 1 (each byte contains FFh).12/2413/24MAXIMUM RATINGStressing the device outside the ratings listed in Table 7. may cause permanent damage to the de-vice. These are stress ratings only, and operation of the device at these, or any other conditions out-side those indicated in the Operating sections of this specification, is not implied. Exposure to Ab-solute Maximum Rating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and other relevant quality documents.Table 7. Absolute Maximum RatingsNote: pliant with JEDEC Std J-STD-020C (for small body, Sn-Pb or Pb assembly), the ST ECOPACK ® 7191395 specification, andthe European directive on Restrictions on Hazardous Substances (RoHS) 2002/95/EU2.AEC-Q100-002 (compliant with JEDEC Std JESD22-A114A, C1=100pF, R1=1500Ω, R2=500Ω)Symbol ParameterMin.Max.Unit T A Ambient Operating Temperature –40125°C T STG Storage Temperature–65150°C T LEAD Lead Temperature during Soldering See note (1)°C V IO Input or Output range –0.50 6.5V V CC Supply Voltage–0.50 6.5V V ESDElectrostatic Discharge Voltage (Human Body model) 2–40004000V14/24DC AND AC PARAMETERSThis section summarizes the operating and mea-surement conditions, and the DC and AC charac-teristics of the device. The parameters in the DC and AC Characteristic tables that follow are de-rived from tests performed under the Measure-ment Conditions summarized in the relevant tables. Designers should check that the operating conditions in their circuit match the measurement conditions when relying on the quoted parame-ters.Table 8. Operating Conditions (M24512 – W)Table 9. Operating Conditions (M24512 – R)Table 10. AC Measurement ConditionsSymbol ParameterMin.Max.Unit V CC Supply Voltage2.5 5.5V T AAmbient Operating Temperature–4085°CSymbol ParameterMin.Max.Unit V CC Supply Voltage1.8 5.5V T AAmbient Operating Temperature–4085°CSymbol ParameterMin.Max.Unit C LLoad Capacitance 100pF Input Rise and Fall Times 50ns Input Levels0.2V CC to 0.8V CC V Input and Output Timing Reference Levels0.3V CC to 0.7V CCV15/24Table 11. Input ParametersNote: 1.T A = 25 °C, f = 400 kHz2.Sampled only, not 100% tested.3.E2,E1,E0: Input impedance when the memory is selected (after a Start condition).Table 12. DC Characteristics (M24512 – W)Note: 1.When the device is selected (after a START condition), the Ei inputs have a different input impedance, as defined in Table 11.Table 13. DC Characteristics (1) (M24512 – R)Note: 1.The information contained in Table 13. is related to the new M24512 (process letter “A”) and is subject to change without previousnotice.Symbol Parameter (1,2)Test ConditionMin.Max.Unit C IN Input Capacitance (SDA)8pF C IN Input Capacitance (other pins)6pF Z L (3)Input Impedance (E2, E1, E0, WC)V IN < 0.3V CC 30k ΩZ H (3)Input Impedance (E2, E1, E0, WC)V IN > 0.7V CC 500k Ωt NSPulse width ignored(Input Filter on SCL and SDA)Single glitch100nsSymbol ParameterTest Condition Min.Max.Unit I LI Input Leakage Current (SCL, SDA, E0, E1, E2)V IN = V SS or V CCdevice in Standby mode (1)± 2µA I LO Output Leakage Current V OUT = V SS or V CC, SDA in Hi-Z± 2µA I CCSupply CurrentV CC = 2.5V, f c =400kHz (rise/fall time < 30ns)1mA V CC = 5.5V, f c =400kHz (rise/fall time < 30ns)2mA I CC1Stand-by Supply Current V IN = V SS or V CC , V CC = 2.5V 2µA V IN = V SS or V CC , V CC = 5.5V5µA V IL Input Low Voltage (SCL, SDA, WC)–0.450.3V CC V V IH Input High Voltage (SCL, SDA, WC)0.7V CCV CC +1V V OLOutput Low VoltageI OL = 2.1mA, V CC = 2.5V0.4VSymbol ParameterTest Condition Min.Max.Unit I LI Input Leakage Current (SCL, SDA, E2, E1, E0)V IN = V SS or V CCdevice in Stand-by mode ± 2µA I LO Output Leakage Current V OUT = V SS or V CC, SDA in Hi-Z ± 2µA I CC Supply Current V CC =1.8V, f c = 400kHz (rise/fall time <30ns)1mA I CC1Standby Supply Current V IN = V SS or V CC , V CC = 1.8V2µA V IL Input Low Voltage –0.450.3V CC V V IH Input High Voltage 0.7V CC V CC +1V V OLOutput Low VoltageI OL = 0.7mA, V CC = 1.8V0.2VTable 14. AC Characteristics (M24512 – W)Symbol Alt.Parameter Min.Max.Unitf C f SCL Clock Frequency400kHzt CHCL t HIGH Clock Pulse Width High600ns t CLCH t LOW Clock Pulse Width Low1300ns t CH1CH2t R Clock Rise Time300ns t CL1CL2t F Clock Fall Time300nst DH1DH2 (2)t R SDA Rise Time20300ns t DL1DL2 (2)t F SDA Fall Time20300ns t DXCX t SU:DAT Data In Set Up Time100ns t CLDX t HD:DAT Data In Hold Time0ns t CLQX t DH Data Out Hold Time200ns t CLQV (3)t AA Clock Low to Next Data Valid (Access Time)200900ns t CHDX (1)t SU:STA Start Condition Set Up Time600ns t DLCL t HD:STA Start Condition Hold Time600ns t CHDH t SU:STO Stop Condition Set Up Time600ns t DHDL t BUF Time between Stop Condition and Next Start Condition1300ns t W t WR Write Time 5 or 10(4)ms Note: 1.For a reSTART condition, or following a Write cycle.2.Sampled only, not 100% tested.3.To avoid spurious START and STOP conditions, a minimum delay is placed between SCL=1 and the falling or rising edge of SDA.4.For M24512 devices whose package marking shows the process letter “A” t W(max) = 5ms whereas for M24512 devices whosepackage marking shows the process letter “V” t W(max) = 10msTable 15. AC Characteristics(1) (M24512 – R)Symbol Alt.Parameter Min.Max.Unitf C f SCL Clock Frequency400kHzt CHCL t HIGH Clock Pulse Width High600ns t CLCH t LOW Clock Pulse Width Low1300nst DL1DL2 (3)t F SDA Fall Time20300ns t DXCX t SU:DAT Data In Set Up Time100ns t CLDX t HD:DAT Data In Hold Time0ns t CLQX t DH Data Out Hold Time200nst CLQV (4)t AA Clock Low to Next Data Valid (Access Time)200900nst CHDX (2)t SU:STA Start Condition Set Up Time600ns t DLCL t HD:STA Start Condition Hold Time600ns t CHDH t SU:STO Stop Condition Set Up Time600ns t DHDL t BUF Time between Stop Condition and Next Start Condition1300ns t W t WR Write Time10ms Note: 1.The information contained in Table 15. is related to the new M24512 (process letter “A”) and is subject to change without previous notice.2.For a reSTART condition, or following a Write cycle.3.Sampled only, not 100% tested.4.To avoid spurious START and STOP conditions, a minimum delay is placed between SCL=1 and the falling or rising edge of SDA. 16/24。

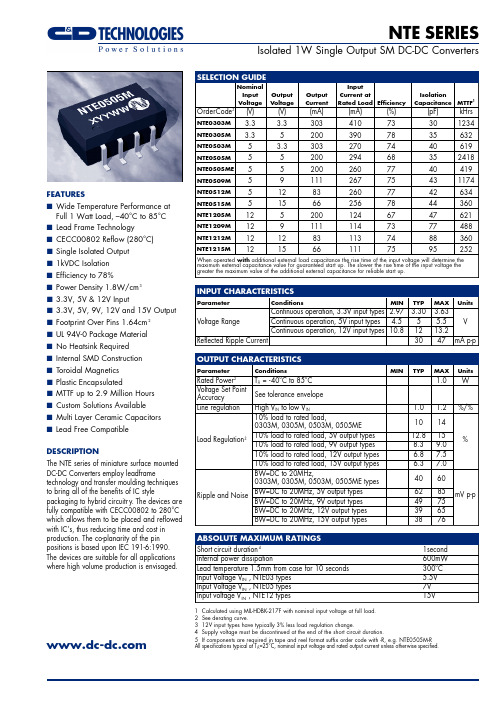

NTE0505M中文资料

Reflected Ripple Current

TYP 3.30

5 12 30

MAX Units 3.63 5.5 V 13.2

47 mA p-p

OUTPUT CHARACTERISTICS

Parameter

Conditions

Rated Power2

Voltage Set Point Accuracy

元器件交易网

NTE SERIES

Isolated 1W Single Output SM DC-DC Converters

FEATURES s Wide Temperature Performance at

Full 1 Watt Load, –40°C to 85°C s Lead Frame Technology s CECC00802 Reflow (280°C) s Single Isolated Output s 1kVDC Isolation s Efficiency to 78% s Power Density 1.8W/cm3 s 3.3V, 5V & 12V Input s 3.3V, 5V, 9V, 12V and 15V Output s Footprint Over Pins 1.64cm 2 s UL 94V-0 Package Material s No Heatsink Required s Internal SMD Construction s Toroidal Magnetics s Plastic Encapsulated s MTTF up to 2.9 Million Hours s Custom Solutions Available s Multi Layer Ceramic Capacitors s Lead Free Compatible

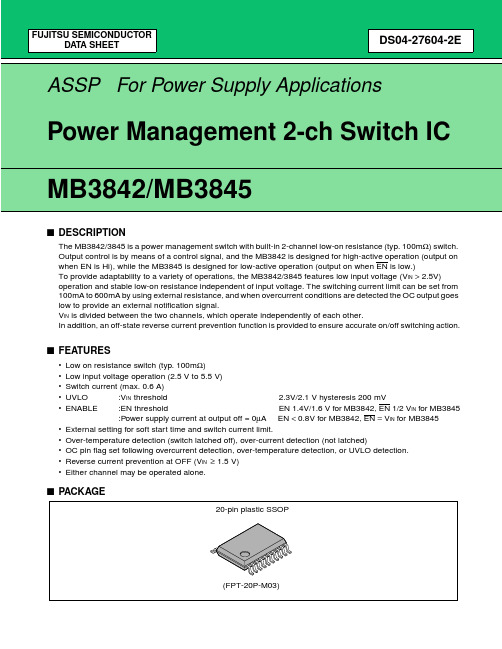

MB3845资料

s RECOMMENDED OPERATING CONDITIONS

Parameter

Symbol

Condition

Min.

Value Typ.

Max.

Input voltage ENABLE voltage

VIN

—

VEN

VEN ≤ VIN

2.5

5.0

5.5

0

—

5.5

Switch current

ISW

Control signal input pin. Set “L” to turn switch on, “H” to turn off. At “H” level = VIN, the chip is in STBY state and current consumption is less than 1µA. Normally used as CMOS inverter input, so that recommended use is “L” level at GND +0.5V or less, and “H” level is VIN -0.5V or greater.

Slow start setting pin. Used to adjust the switch on/off timing. Add external capacitance to delay operation. Leave open when not in use. In open mode voltages up to 12 V are present. Care should be taken in mounting to prevent leakage current generation because high impedance is required.

MB40166中文资料

R-2R RESISTOR NETWORK

24 VOUT

15 28

D.GND

17 26

A.GND

16 27

VCCD

18 25

VCCA

23

COMP

Note : The circuits within the dotted lines above are different for MB40166 and MB40176.

– Clamp capacitor is connected between these pins.

–

I A/D conversion clock input.

O Analog signal output.

I Digital signal input. (DD1: MSB, DD6: LSB)

Phase compensation capacitor is connected. – Insert a capacitor of 1 µF or more between this pin and

VINA

-0.5 to VCCA +0.5

V

Storage Temperature

TSTG

-55 to +125

°C

NOTE:

Permanent device damage may occur if the above Absolute Maximum Ratings are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

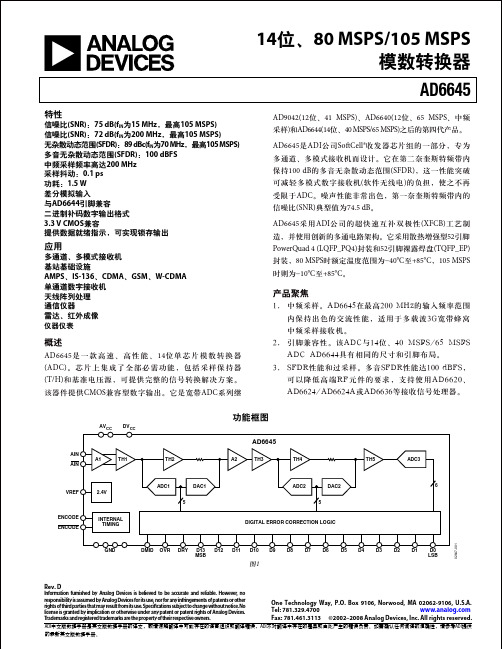

AD6645中文说明手册

应用

多通道、多模式接收机 基站Байду номын сангаас础设施 AMPS、IS-136、CDMA、GSM、W-CDMA 单通道数字接收机 天线阵列处理 通信仪器 雷达、红外成像

仪器仪表

产品聚焦

1. 中频采样。AD6645在最高200 MHz的输入频率范围 内保持出色的交流性能,适用于多载波3G宽带蜂窝 中频采样接收机。 2. 引脚兼容性。该ADC与14位、40 MSPS/65 MSPS ADC AD6644具有相同的尺寸和引脚布局。 3. SFDR性能和过采样。多音SFDR性能达100 dBFS, 可以降低高端RF元件的要求,支持使用AD6620、 AD6624/AD6624A或AD6636等接收信号处理器。

ADC1 VREF 2.4V 5 ENCODE ENCODE

DAC1

ADC2 5

DAC2

6

INTERNAL TIMING

DIGITAL ERROR CORRECTION LOGIC

GND

DMID

OVR

DRY

D13 MSB

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0 LSB

图1

Rev. D

修订历史

2008年10月—修订版C至修订版D 增加TQFP_EP封装 .................................................................... 通篇 重命名“热特性”和“热阻”部分 ...................................................... 7 增加表6;重新排序 ........................................................................ 7 移动“等效电路”部分 ..................................................................... 14 移动“术语”部分 .............................................................................. 15 更改表9 ............................................................................................ 20 更改“外形尺寸”.............................................................................. 24 更改“订购指南”.............................................................................. 24 2006年12月—修订版B至修订版C 更新格式 ...................................................................................... 通篇 更改“技术规格”................................................................................ 3 更改“抖动考虑”部分 ..................................................................... 19 更改表8“物料清单” ....................................................................... 20 更改图43“评估板原理图” ............................................................ 21 更改图44和图46 ............................................................................. 22 更新“外形尺寸”.............................................................................. 23 更改“订购指南”.............................................................................. 23

SUB75P05-08中文资料

30

0 0 20 40 60 80 100

0 0 20 40 60 80 100 120

ID – Drain Current (A)

ID – Drain Current (A)

Capacitance

12000 20

Gate Charge

V GS – Gate-to-Source Voltage (V)

元器件交易网

SUP/SUB75P05-08

New Product

Vishay Siliconix

P-Channel 55-V (D-S), 175_C MOSFET

PRODUCT SUMMARY

V(BR)DSS (V)

–55

rDS(on) (W)

0.008

ID (A)

–75a

120 TC = –55_C g fs – Transconductance (S) 90 25_C 125_C r DS(on)– On-Resistance ( W ) 0.06

On-Resistance vs. Drain Current

0.05

0.04

60

0.03

0.02 VGS = 4.5 V 0.01 VGS = 10 V

Source-Drain Diode Ratings and Characteristics (TC = 25_C)b

Continuous Current Pulsed Current Forward Voltagea Reverse Recovery Time Peak Reverse Recovery Current Reverse Recovery Charge Is ISM VSD trr IRM(REC) Qrr IF = –75 A, di/dt = 100 A/ms 75 A di/d A/ IF = –75 A, VGS = 0 V –1.1 60 2.2 0.176 –75 A –240 –1.3 120 3.5 0.21 V ns A mC

AD408M182VBB-5中文资料

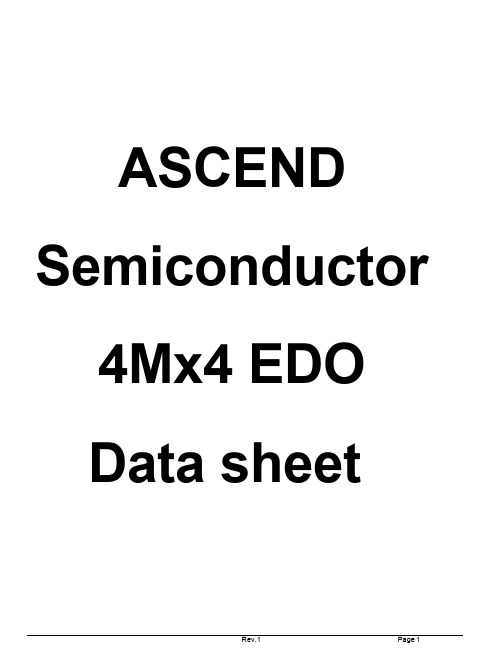

ASCEND Semiconductor 4Mx4 EDO Data sheetDescriptionThe device CMOS Dynamic RAM organized as 4,194,304 words x 4 bits with extended data out access mode. It is fabricated with an advanced submicron CMOS technology and designed to operate from a single 3.3V oniy power supply. Low voltage operation is more suitable to be used on battery backup, portable elec-tronic application. lt is packaged in JEDEC standard 26/24-pin plastic SOJ or TSOP(II).Features• Single 3.3V(%) only power supply • High speed t RAC acess time: 50/60ns • Low power dissipation- Active mode : 432/396 mW (Mas) - Standby mode: 0.54 mW (Mas)• Extended - data - out(EDO) page mode access • I/O level: CMOS level (Vcc = 3.3V)• 2048 refresh cycle in 32 ms(Std.) or 128 ms(S-version)• 4 refresh modesh: - RAS only refresh- CAS - before - RAS refresh - Hidden refresh - Self-refresh(S-version)10±Pin Name FunctionA0-A10Address inputs- Row address - Column address - Refresh address DQ1~DQ4Data-in / data-out RAS Row address strobe CAS Column address strobe WE Write enable OE Output enable Vcc Power (+ 3.3V)VssGroundVCC 1DQ12DQ23DQ34DQ45VCC6891011 NC 12 WE 13A0 A117 A218 A319VSS RAS CAS OE A8A7A6A5A4VSSAD404M42VSPin Description Pin Configuration21222324 2526151416 A1026/24-PIN 300mil Plastic SOJA9VCC 1DQ12DQ23DQ34DQ45VCC6891011 NC 12 WE 13A0 A117 A218 A319VSS RAS CAS OE A8A7 A6A5 A4VSSAD404M42VT212223242526151416 A1026/24-PIN 300mil Plastic TSOP (ll)A9A0-A10A0-A10A0-A10WECASNO. 2 CLOCK GENERATORCOLUMN ADDRESS BUFFERS (11)REFRESH CONTROLLERREFRESH COUNTERBUFFERS (11)ADDRESS ROW NO. 1 CLOCK GENERATORA0RASA1A2A3A4A5A6A7A8CONTROLLOGICDATA-IN BUFFERDATA-OUT BUFFEROEDQ1.DQ4.COLUMN DECODER2048SENSE AMPLIFIERSI/O GATING2048x42048x2048x4MEMORY ARRAY2048R O W D E C O D E RVcc VssBlock DiagramA9A10TRUTH TABLENotes: 1. EARLY WRITE only.FUNCTIONRASCAS WE OE ADDRESSESDQ SNotesROW COL STANDBY H X X X X High-Z READL L H L ROW COL Data-Out WRITE: (EARLY WRITE )L L L X ROW COL Data-lnREAD WRITE L L ROW COL Data-Out,Data-ln EDO-PAGE-MODE READ1st Cycle L H L ROW COL Data-Out 2nd CycleL H L n/a COL Data-Out EDO-PAGE MODE WRITE1st CycleL L X ROW COL Data-In 2nd Cycle L L Xn/a COL Data-InEDO-PAGE-MODEREAD-WRITE 1st Cycle L ROW COL Data-Out, Data-In 2nd Cycle L n/a COL Data-Out, Data-In HIDDEN REFRESHREAD L H L ROW COL Data-Out WRITEL L X ROW COL Data-In 1RAS-ONLY REFRESH L H X X ROW n/a High-Z CBR REFRESHLHXXXHigh-ZH X →H L →L H →H L →H L →H L →H L →H L →H L →L H →H L →H L →L H→L H L →→L H L→→H L→Absolute Maximum RatingsRecommended DC Operating ConditionsCapacitanceTa = 25°C, V CC = 3.3V%, f = 1MHz Note: 1. Capacitance measured with effective capacitance measuring method. 2. RAS, CAS = V IH to disable Dout.ParameterSymbol Value Unit Voltage on any pin relative to Vss V T -0.5 to + 4.6V Supply voltage relative to Vss V CC -0.5 to + 4.6V Short circuit output current I OUT 50mA Power dissipation P D 1.0WOperating temperature T OPT 0 to + 70°C Storage temperatureT STG-55 to + 125°CParameter/Condition Symbol3.3 Volt VersionUnitMinTyp MaxSupply VoltageV CC 3.0 3.33.6V Input High Voltage, all inputs V IH 2.0-V CC + 0.3V Input Low Voltage, all inputsV IL-0.3-0.8VParameterSymbol Typ Max Unit Note Input capacitance (Address)C I1 -5pF 1Input capacitance (RAS, CAS, OE, WE)C I2-7pF 1Output capacitance(Data-in, Data-out)C I/O-7pF1, 210±DC Characteristics :(T a = 0 to 70°C, V CC = + 3.3V%, V SS = 0V)Parameter Symbol Test Conditions AD404M42V Unit Notes-5-6Min Max Min MaxOperating current I CC1RAS cyclingCAS, cyclingt RC = min-120-110mA1, 2Standby Current LowpowerS-versionI CC2LVTTL interfaceRAS, CAS = V IHDout = High-Z-0.5-0.5mACMOS interfaceRAS, -0.2VDout = High-Z-0.15-0.15mAStandardpowerversionLVTTL interfaceRAS, CAS = V IHDout = High-Z-2-2mACMOS interfaceRAS,-0.2VDout = High-Z-0.5-0.5mARAS- only refresh current I CC3RAS cycling, CAS = V IHt RC = min-120-110mA1, 2 EDO page mode current I CC4t PC = min-90-80mA1, 3CAS- before- RAS refresh current I CC5t RC = minRAS, CAS cycling-120-110mA1, 2Self- refresh current (S-Version)I CC8 - 550 - 55010±CAS V CC≥CAS V CC≥t RASS100µs≥µADC Characteristics :(T a = 0 to 70°C , V CC = +3.3V %, V SS = 0V)Notes:1. I CC is specified as an average current. It depends on output loading condition and cycle rate when the device is selected. I CC max is specified at the output open condition.2. Address can be changed once or less while RAS = V IL .3. For I CC4, address can be changed once or less within one EDO page mode cycle time.Parameter Symbol Test Conditions AD404M42VUnitNotes-5-6Min MaxMin MaxInput leakage current I LI + 0.3V -55-55Output leakage current I LO + 0.3V Dout = Disable -55-55Output high Voltage V OH I OH = -2mA 2.4- 2.4-V Output low voltage V OLI OL = +2mA-0.4-0.4V10±0V Vin V CC ≤≤µA 0V Vout V CC ≤≤µAAC Characteristics(T a = 0 to + 70°C , V cc = 3.3V %, V ss = 0V) *1, *2, *3, *4Test conditions• Output load: one TTL Load and 100pF (V CC = 3.3V %)• Input timing reference levels:V IH = 2.0V, V IL = 0.8V (V CC = 3.3V %)• Output timing reference levels:V OH = 2.0V, V OL = 0.8V10±10±10±Read, Write, Read- Modify- Write and Refresh Cycles (Common Parameters)ParameterSymbol AD404M42V UnitNotes-5-6Min MaxMin MaxRandom read or write cycle time t RC 84-104-ns RAS precharge timet RP 30-40-ns CAS precharge time in normal mode t CPN 10-10-ns RAS pulse width t RAS 50100006010000ns 5CAS pulse width t CAS 8100001010000ns 6Row address setup time t ASR 0-0-ns Row address hold time t RAH 8-10-ns Column address setup time t ASC 0-0-ns 7Column address hold time t CAH 8-10-ns RAS to CAS delay timet RCD 12371445ns 8RAS to column address delay time t RAD 10251230ns 9Column address to RAS lead time t RAL 25-30-ns RAS hold time t RSH 8-10-ns CAS hold timet CSH 38-40-ns CAS to RAS precharge time t CRP 5-5-ns 10OE to Din delay time t OED 12-15-ns Transition time (rise and fall)t T 150150ns 11Refresh periodt REF -32-32ms Refresh period (S- Version)t REF -128-128ms CAS to output in Low- Z t CLZ 0-0-ns CAS delay time from Din t DZC 0-0-ns OE delay time from Dint DZO-0-nsRead CycleWrite Cycle Parameter SymbolAD404M42V Unit Notes-5-6Min Max Min MaxAccess time from RAS t RAC-50-60ns12 Access time from CAS t CAC-14-15ns13, 14 Access time from column address t AA-25-30ns14, 15 Access time from OE t OEA-12-15nsRead command setup time t RCS0-0-ns7 Read command hold time to CAS t RCH0-0-ns10, 16 Read command hold time to RAS t RRH0-0-ns16 Output buffer turn-off time t OFF012015ns17 Output buffer turn-off time from OE t OEZ012015ns17Parameter SymbolAD404M42V Unit Notes -5-6Min Max Min MaxWrite command setup time t WCS0-0-ns7, 18 Write command hold time t WCH8-10-nsWrite command pulse width t WP8-10-nsWrite command to RAS lead time t RWL13-15-nsWrite command to CAS lead time t CWL8-10-nsData-in setup time t DS0-0-ns19 Data-in hold time t DH8-10-ns19 WE to Data-in delay t WED10-10-nsRead- Modify- Write CycleRefresh Cycle Parameter SymbolAD404M42V Unit Notes-5-6Min Max Min MaxRead-modify- write cycle time t RWC108-133-nsRAS to WE delay time t RWD64-77-ns18 CAS to WE dealy time t CWD26-32-ns18 Column address to WE delay time t AWD39-47-ns18 OE hold time from WE t OEH8-10-nsParameter SymbolAD404M42VUnit Notes -5-6Min Max Min MaxCAS setup time (CBR refresh) t CSR5-5-nsCAS hold time (CBR refresh)t CHR8-10-ns10 RAS precharge to CAS hold time t RPC5-5-ns7 RAS pulse width (self refresh)t RASS100-100-RAS precharge time (self refresh)t RPS90-110-nsCAS hold time (CBR self refresh)t CHS-50--50-nsWE setup time t WSR0-0-nsWE hold time t WHR10-10-nsµsEDO Page Mode CycleEDO Page Mode Read Modify Write CycleParameterSymbol AD404M42VUnit Notes-5-6Min MaxMin MaxEDO page mode cycle timet PC 20-25-ns EDO page mode CAS precharge time t CP 10-10-ns EDO page mode RAS pulse width t RASP 5010560105ns 20Access time from CAS precharge t CPA -30-35ns 10, 14RAS hold time from CAS precharge t CPRH 30-35-ns OE high hold time from CAS high t OEHC 5-5-ns OE high pulse widtht OEP 10-10-ns Data output hold time after CAS low t COH 5-5-ns Output disable delay from WEt WHZ 310310ns WE pulse width for output disable whenCAS hight WPZ7-7-nsParameterSymbol AD404M42V Unit Notes -5-6Min MaxMin MaxEDO page mode read- modify- write cycle CAS precharge to WE delay timet CPW 45-55-ns 10EDO page mode read- modify- write cycle timet PRWC56-68-nsNotes :1. AC measurements assume t T = 2ns.2. An initial pause of 100 is required after power up, and it followed by a minimum of eightinitialization cycles (RAS - only refresh cycle or CAS - before - RAS refresh cycle). If the internal refresh counter is used, a minimun of eight CAS - before - RAS refresh cycles are required.3. In delayed write or read-modify-write cycles, OE must disable output buffer prior to applying data to the device.4. All the V CC and V SS pins shall be supplied with the same voltages.5. t RAS (min) = t RWD (min)+t RWL (min)+t T in read-modify-write cycle.6. t CAS (min) = t CWD (min)+t CWL (min)+t T in read-modify-write cycle.7. t ASC (min), t RCS (min), t WCS (min), and t RPC are determined by the falling edge of CAS .8. t RCD (max) is specified as a reference point only, and t RAC (max) can be met with the t RCD (max) limit.Otherwise, t RAC is controlled exclusively by t CAC if t RCD is greater than the specified t RCD (max) limit. 9. t RAD (max) is specified as a reference point only, and t RAC (max) can be met with the t RAD (max) limit.Otherwise, t RAC is controlled exclusively by t AA if t RAD is greater than the specified t RAD (max) limit. 10. t CRP , t CHR , t RCH , t CPA and t CPW are determined by the rising edge of CAS .11. V IH (min) and V IL (max) are reference levels for measuring timing or input signals. Therefore, transitiontime is measured between V IH and V IL .12. Assumes that t RCD tRCD (max) and t RAD t RAD (max). If t RCD or t RAD is greater than the maximum recommended value shown in this table, t RAC exceeds the value shown. 13. Assumes that (max) and (max).14. Access time is determined by the maximum of t AA , t CAC , t CPA . 15. Assumes that (max) and (max). 16. Either t RCH or t RRH must be satisfied for a read cycle.17. t OFF (max) and t OEZ (max) define the time at which the output achieves the open circuit condition (highimpedance). t OFF is determined by the later rising edge of RAS or CAS.18. t WCS , t RWD , t CWD , and t AWD are not restrictive operating parameters. They are included in the datasheet as electrical characteristics only. If (min), the cycle is an early write cycle and the data out will remain open circuit (high impedance) throughout the entire cycle. If (min),(min), (min) and (min), the cycle is a read-modify-write and the data output will contain data read from the selected cell. If neither of the above sets of conditions is satisfied, the condition of the data output (at access time) is indeterminate.19. These parameters are referenced to CAS separately in an early write cycle and to WE edge in adelayed write or a read-modify-write cycle.20. t RASP defines RAS pulse width in EDO page mode cycles.µs ≤≤t RCD t RCD ≥t RADt RAD ≤t RCD t RCD ≤t RAD t RAD ≥t WCS t WCS ≥t RWD t RWD ≥t CWDt CWD ≥t AWD t AWD ≥t CPW t CPW≥Timing Waveforms• Read Cyclet RC t RASt RPtCRPtCPNtRRHtRCHt OEZ t OFF tOEA tCACt AAtRACt CLZD OUTtRCS t ASR tRAH tASC tCAH tRAD t RALtCAStRSH tRCDt TtCSHRASCASADDRESSWEDQ1~DQ4Note : = don’t care OEt OFFRowColumn= Invalid Dout•Early Write CycletRC t RASt RPt WCHt DSt DHt WCS t RALtCAStRSH tRCDt TtCSHRASCASWEDQ1~DQ4tCRPtASRtRAH tASCtCAH ADDRESSColumnRowtCPND INtRADt RAL• Delayed Write CycletRC t RASt RPt RWL t RCSt CAStRSH tRCDt TtCSHRASCAStASR tRAH tCAHADDRESSColumnRow tASC D INDQ1~DQ4WEtCRPtCPNt DHt DSt OEHt OEDOEt DSOPENt WPt CWL• Read - Modify - Write CycletRWC t RASt RPtRWDt WPtRADtRWL tCAStCWL tRCDt TtCPNRASCASWEtCRP t ASRtRAHtASCtCAHADDRESS Column RowDQ1~DQ4t DHt DSOEtRCStAWD tCWD D INt OEDt OEHt OEZt OEA t CAC t RACt AADQ1~DQ4D OUTOPENtDZCtDZO• EDO Page Mode Read CycletRASPtCPRHt RCStCAStRSH tRCDt OEAtCSHRASCAStASRtRAHtCAHADDRESStCASWEtCRPt CPOEDQ1~DQ4OPENtOEPD OUT 1t PCt CPtCAStCPNtCRPtRADtCAHtASCt ASCtCAHt ASCt RAL Row Column 1t OEAt OEHCtRRH tRCHt RACt AAt AAt AA t CPA t CPA t OEZt OFFt OFFt CACt OEZt CAC t CACt COHD OUT NWE OE Column 2Column N Rowt RPD OUT 2• EDO Page Mode Early Write CycletRASPtRPt WCSt CAStRSH tRCDRASCAStASRtRAHtCAHADDRESStCASWEt CPDQ1~DQ4t PCt CPt CAStCPNtCRP tCAH tASCtASC tCAH tASC Row Column 1t DS WE Column 2Column Nt WCH t WCS t WCH t WCS t WCHt DH t DS t DH t DS t DHD IN 1D IN 2D IN Nt TtCSH• EDO Page Mode Read-Early-Write Cyclet RASPtCPRHt RCStCAStRSH tRCDt OEAtCSHRASCAStASRtRAHtCAHADDRESStCASWEtCRPt CPOEDQ1~DQ4OPENtWEDt PCt CPtCAStCPNtCRPtRADtRAHtASCt ASCtCAHt ASCt RAL Row Column 1tWCStRCHt RACt AAt AAt CPA t DHt WHZt CACt CACt COHWE OE Column 2Column N Rowt RPt CAL tWCHDataDoutput 2Data Input NDataDoutput 1t DStCSH• EDO Page Mode Read-Modify-Write Cyclet RASPt CPRHt RCStCASt WP RASCASt ASRtRAHtCAHADDRESSt CASWEtRCDCPDQ1~DQ4tPRWCt CPtCAStCRPtRADtCAHtASCt ASCtCAH tASC Row Column 1tRWLtRCSt OEDt DZOt CAC WE OEt RPt RAL D OUT 2D OUT ND OUT 1tTt Column NColumn 2Column 1tRWD tAWD tCWDtCWLtRCStCWDtAWD tCPW tCWL tCPW tAWD tCWDtCWL t OEDt OEDt OEHt OEHt OEHt CAC t CAC t OEA t AAt RACt OEZt OEAt AA t CPAt OEZt OEAt AA t CPAt OEZ t DSt DHt WP t DSt DHt WP t DSt DHOPENOPENOPEN D IN 1D IN ND IN 2DQ1~DQ4t DZCt DZOt DZCt DZCt DZO• Read Cycle with WE Controlled Disablet WPZt RCStCAStRCDt TtCSHRASCASt ASRtRAHtCAHADDRESSColumnRow tASCD DQ1~DQ4WEt OEZt DSt WHZOEt RCH t OEA t CACt AAt RACt CLZOUTtRADRASADDRESSt RC t CRPt ASRt RAHt Tt RPCROWt OFFCAS t RASt RPOPENt CRPDQ1~DQ4RASt CSRt WSRt RPt T t RPCt OFFCAS t RASt RPOPENt CRPDQ1~DQ4t RPCt CHRt RASt RPt RCt RCt CHRt CSRt WHRt WSRt WHRWECAS-Before-RAS Refresh CycleRASWEt RPCt OFFt CSRt CHSt WSRCASt RASS t RPSOPENDQ1~DQ4t WHRHigh lmpedance• Hidden Refresh Cyclet RPt RASRASt RCDt CRPADDRESSWEt CHRt CASt RSHt RAHt ASRt ASCt CAHt RAL ROW t RCHt OEZCASDQ1~DQ4t Tt RCSD t RASt RASt RPt RPt RC t RCt RCt RADt RRHt OFF t OFFt OEA t CACt AAt RACCOlumnOUTOE(READ)(REFRESH)(REFRESH)Ordering informationAD404M42VSA-5• AD• Ascend Memory Product • 40 • Device Type• 4M4 • Density and Organization • 2• Refresh Rate, 2: 2K Refresh • V• T: 5V, V: 3.3V• S • Package Type (S : SOJ, T : TSOP II)• A• Version• 5• Speed (5: 50 ns, 6: 60 ns)Part Number Access time PackageAD404M42VSA-5AD404M42VSA-6AD404M42VTA-5AD404M42VTA-650 ns 60 ns 50 ns 60 ns300mil 26/24-Pin Plastic SOJTSOP IIPackaging information • 300 mil, 26/24-Pin Plastic SOJ• 300 mil, 26/24-Pin TSOP II。

AD8005中文资料

TMIN to TMAX Offset Drift +Input Bias Current TMIN to TMAX –Input Bias Current Input Bias Current Drift (± ) Open-Loop Transimpedance INPUT CHARACTERISTICS Input Resistance Input Capacitance Input Common-Mode Voltage Range Common-Mode Rejection Ratio OUTPUT CHARACTERISTICS Output Voltage Swing Output Current Short Circuit Current POWER SUPPLY Quiescent Current Power Supply Rejection Ratio OPERATING TEMPERATURE RANGE

元器件交易网

a

FEATURES Ultralow Power 400 A Power Supply Current (4 mW on ؎5 VS) Specified for Single Supply Operation High Speed 270 MHz, –3 dB Bandwidth (G = +1) 170 MHz, –3 dB Bandwidth (G = +2) 280 V/ s Slew Rate (G = +2) 28 ns Settling Time to 0.1%, 2 V Step (G = +2) Low Distortion/Noise –63 dBc @ 1 MHz, V O = 2 V p-p –50 dBc @ 10 MHz, VO = 2 V p-p 4.0 nV/√Hz Input Voltage Noise @ 10 MHz Good Video Specifications (RL = 1 k⍀, G = +2) Gain Flatness 0.1 dB to 30 MHz 0.11% Differential Gain Error 0.4؇ Differential Phase Error APPLICATIONS Signal Conditioning A/D Buffer Power-Sensitive, High-Speed Systems Battery Powered Equipment Loop/Remote Power Systems Communication or Video Test Systems Portable Medical Instruments PRODUCT DESCRIPTION

M393T5166AZA-CC中文资料

DDR2 Registered SDRAM MODULE 240pin Registered Module based on 1Gb A-die72-bit ECCINFORMATION IN THIS DOCUMENT IS PROVIDED IN RELATION TO SAMSUNG PRODUCTS,AND IS SUBJECT TO CHANGE WITHOUT NOTICE.NOTHING IN THIS DOCUMENT SHALL BE CONSTRUED AS GRANTING ANY LICENSE,EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE,TO ANY INTELLECTUAL PROPERTY RIGHTS IN SAMSUNG PRODUCTS OR TECHNOLOGY. ALL INFORMATION IN THIS DOCUMENT IS PROVIDEDON AS "AS IS" BASIS WITHOUT GUARANTEE OR WARRANTY OF ANY KIND.1. For updates or additional information about Samsung products, contact your nearest Samsung office.2. Samsung products are not intended for use in life support, critical care, medical, safety equipment, or similarapplications where Product failure couldresult in loss of life or personal or physical harm, or any military ordefense application, or any governmental procurement to which special terms or provisions may apply.* Samsung Electronics reserves the right to change products or specification without notice.Table of Contents1.0 DDR2 Registered DIMM Ordering Information (4)2.0 Features (4)3.0 Address Configuration (4)4.0 Pin Configurations (Front side/Back side) (5)5.0 Pin Description (6)6.0 Input/Output Function Description (7)7.0 Functional Block Diagram (8)7.1 1GB, 128Mx72 Module (M393T2863AZ3/M393T2863AZA) (8)7.2 2GB, 256Mx72 Module (M393T5663AZ3/M393T5663AZA) (9)7.3 2GB, 256Mx72 Module (M393T5660AZ3/M393T5660AZA) (10)7.4 4GB, 512Mx72 Module (M393T5168AZ0/M393T5166AZA) (11)8.0 Absolute Maximum DC Ratings (12)9.0 AC & DC Operating Conditions (12)9.1 Operating Temperature Condition (13)9.2 Input DC Logic Level (13)9.3 Input AC Logic Level (13)9.4 AC Input Test Conditions (13)10.0 IDD Specification Parameters Definition (14)11.0 Operating Current Table(1-1) (15)11.1 M393T2863AZ3/M393T2863AZA : 1GB(128Mx8 *9) Module (15)11.2 M393T5663AZ3/M393T5663AZA : 2GB(128Mx8 *18) Module (15)11.3 M393T5660AZ3/M393T5660AZA : 2GB(256Mx4 *18) Module (16)11.4 M393T5168AZ0/M393T5166AZA : 4GB(st.512Mx4 *18) Module (16)12.0 Input/Output Capacitance (17)13.0 Electrical Characteristics & AC Timing for DDR2-667/533/400 (18)13.1 Refresh Parameters by Device Density (18)13.2 Speed Bins and CL, tRCD, tRP, tRC and tRAS for Corresponding Bin (18)13.3 Timing Parameters by Speed Grade (18)14.0 Physical Dimensions (20)14.1 128Mbx8 based 128Mx72 Module(1 Rank) (M393T2863AZ3/M393T2863AZA) (20)14.2 128Mbx8/256Mbx4 based 256Mx72 Module(2/1 Ranks)(M393T5663AZ3/M393T5663AZA/ M393T5660AZ3/M393T5660AZA) (21)14.3 st.512Mbx4 based 512Mx72 Module(2 Ranks) (M393T5168AZ0/M393T5166AZA) (22)15.0 240 Pin DDR2 Registered DIMM Clock Topology (23)Revision HistoryRevision Month Year History1.0July2005 - Initial Release1.1Aug.2005 - Revised IDD Current Values1.2Sep.2005 - Revised the Ordering InformationDDR2 Registered DIMM Ordering InformationPart Number Density Organization Component Composition Number of Rank Parity Register Height M393T2863AZ3-CD5/CC1GB128Mx72128Mx8(K4T1G084QA)*9EA1X30mm M393T2863AZA-CE6/D5/CC1GB128Mx72128Mx8(K4T1G084QA)*9EA1O30mm M393T5663AZ3-CD5/CC2GB256Mx72128Mx8(K4T1G084QA)*18EA2X30mm M393T5663AZA-CE6/D5/CC2GB256Mx72128Mx8(K4T1G084QA)*18EA2O30mm M393T5660AZ3-CD5/CC2GB256Mx72256Mx4(K4T1G044QA)*18EA1X30mm M393T5660AZA-CE6/D5/CC2GB256Mx72256Mx4(K4T1G044QA)*18EA1O30mm M393T5168AZ0-CD5/CC4GB512Mx72st.512Mx4(K4T2G064QA)*18EA2X30mm M393T5166AZA-CE6/D5/CC4GB512Mx72st.512Mx4(K4T2G264QA)*18EA2O30mm Note: “Z” of Part number(11th digit) stand for Lead-free products.Note: “3” of Part number(12th digit) stand for Dummy Pad PCB products.Note: "A" of Part number(12th digit) stand for Parity Register products.Features•Performance rangeE6(DDR2-667)D5(DDR2-533)CC(DDR2-400)UnitSpeed@CL3400400400MbpsSpeed@CL4533533400MbpsSpeed@CL5667533-MbpsCL-tRCD-tRP5-5-54-4-43-3-3CK•JEDEC standard 1.8V ± 0.1V Power Supply•V DDQ = 1.8V ± 0.1V•200 MHz f CK for 400Mb/sec/pin, 267MHz f CK for 533Mb/sec/pin, 333MHz f CK for 667Mb/sec/pin•8Banks•Posted CAS•Programmable CAS Latency: 3, 4, 5•Programmable Additive Latency: 0, 1 , 2 , 3 and 4•Write Latency(WL) = Read Latency(RL) -1•Burst Length: 4 , 8(Interleave/nibble sequential)•Programmable Sequential / Interleave Burst Mode•Bi-directional Differential Data-Strobe (Single-ended data-strobe is an optional feature)•Off-Chip Driver(OCD) Impedance Adjustment•On Die Termination with selectable values(50/75/150 ohms or disable)•PASR(Partial Array Self Refresh)•Average Refresh Period 7.8us at lower than a T CASE 85°C, 3.9us at 85°C < T CASE < 95 °C- support High Temperature Self-Refresh rate enable feature•Serial presence detect with EEPROM•DDR2 SDRAM Package: 68ball FBGA - 256Mx4/128Mx8, 56ball BGA - st.512Mbx4•All of Lead-free products are compliant for RoHSNote: For detailed DDR2 SDRAM operation, please refer to Samsung’s Device operation & Timing diagram..Address ConfigurationOrganization Row Address Column Address Bank Address Auto Precharge 256Mx4(1Gb) based Module A0-A13A0-A9, A11BA0-BA2A10128Mx8(1Gb) based Module A0-A13A0-A9BA0-BA2A10NC = No Connect, RFU = Reserved for Future Use1. RESET (Pin 18) is connected to both OE of PLL and Reset of register.2. The Test pin (Pin 102) is reserved for bus analysis probes and is not connected on normal memory modules (DIMMs)3. NC/Err_Out ( Pin 55) and NC/Par_In (Pin 68) are for optional function to check address and command parity.4. CKE1,S1 Pin is used for double side Registered DIMM.Pin Front Pin Back Pin Front Pin Back Pin Front Pin Back Pin Front Pin Back 1V REF 121V SS 31DQ19151V SS 61A4181V DDQ 91V SS 211DM5/DQS142V SS 122DQ432V SS 152DQ2862V DDQ 182A392DQS5212NC/DQS143DQ0123DQ533DQ24153DQ2963A2183A193DQS5213V SS 4DQ1124V SS 34DQ25154V SS 64V DD184V DD94V SS 214DQ465V SS 125DM0/DQS935V SS 155DM3/DQS12KEY95DQ42215DQ476DQS0126NC/DQS936DQS3156NC/DQS1265V SS 185CK096DQ43216V SS 7DQS0127V SS 37DQS3157V SS 66V SS 186CK097V SS 217DQ528V SS 128DQ638V SS 158DQ3067V DD 187V DD 98DQ48218DQ539DQ2129DQ739DQ26159DQ3168NC/Par_In 188A099DQ49219V SS 10DQ3130V SS 40DQ27160V SS 69V DD 189V DD 100V SS 220RFU 11V SS 131DQ1241V SS 161CB470A10/AP 190BA1101SA2221RFU 12DQ8132DQ1342CB0162CB571BA0191V DDQ 102NC(TEST)222V SS 13DQ9133V SS 43CB1163V SS 72V DDQ 192RAS 103V SS 223DM6/DQS1514V SS 134DM1/DQS1044V SS 164DM8/DQS1773WE 193S0104DQS6224NC/DQS1515DQS1135NC/DQS1045DQS8165NC/DQS1774CAS 194V DDQ 105DQS6225V SS 16DQS1136V SS 46DQS8166V SS 75V DDQ 195ODT0106V SS 226DQ5417V SS 137RFU 47V SS 167CB676S14196A13107DQ50227DQ5518RESET 138RFU 48CB2168CB777ODT1197V DD 108DQ51228V SS 19NC 139V SS 49CB3169V SS 78V DDQ 198V SS 109V SS 229DQ6020V SS 140DQ1450V SS 170V DDQ 79V SS 199DQ36110DQ56230DQ6121DQ10141DQ1551V DDQ 171CKE1480DQ32200DQ37111DQ57231V SS 22DQ11142V SS 52CKE0172V DD 81DQ33201V SS 112V SS 232DM7/DQS1623V SS 143DQ2053V DD 173NC 82V SS 202DM4/DQS13113DQS7233NC/DQS1624DQ16144DQ2154BA2174NC 83DQS4203NC/DQS13114DQS7234V SS 25DQ17145V SS 55NC/Err_Out 175V DDQ 84DQS4204V SS 115V SS 235DQ6226V SS 146DM2/DQS1156V DDQ 176A1285V SS 205DQ38116DQ58236DQ6327DQS2147NC/DQS1157A11177A986DQ34206DQ39117DQ59237V SS 28DQS2148V SS 58A7178V DD 87DQ35207V SS 118V SS 238VDDSPD 29V SS 149DQ2259V DD 179A888V SS 208DQ44119SDA 239SA030DQ18150DQ2360A5180A689DQ40209DQ45120SCL240SA190DQ41210V SS Pin Configurations (Front side/Back side)* The VDD and VDDQ pins are tied to the single power-plane on PCB.Pin Name DescriptionPin Name Description CK0Clock Inputs, positive line ODT0~ODT1On die termination CK0Clock inputs, negative line DQ0~DQ63Data Input/OutputCKE0, CKE1Clock Enables CB0~CB7Data check bits Input/Output RAS Row Address Strobe DQS0~DQS8Data strobesCAS Column Address Strobe DQS0~DQS8Data strobes, negative line WE Write Enable DM(0~8), DQS(9~17)Data Masks / Data strobes (Read)S0, S1Chip Selects DQS9~DQS17Data strobes (Read), negative line A0~A9, A11~A13Address InputsRFU Reserved for Future Use A10/AP Address Input/Autoprecharge NC No ConnectBA0~BA2DDR2 SDRAM Bank AddressTEST Memory bus test tool(Not Connect and Not Useable on DIMMs)SCL Serial Presence Detect (SPD) Clock Input V DD Core Power SDA SPD Data Input/Output V DDQ I/O Power SA0~SA2SPD addressV SS GroundPar_In Parity bit for the Address and Control bus V REF Input/Output Reference Err_Out Parity error found in the Address and Control bus V DDSPDSPD PowerRESETRegister and PLL control pinPin DescriptionSymbol Type DescriptionCK0Input Positive line of the differential pair of system clock inputs that drives input to the on-DIMM PLL.CK0Input Negative line of the differential pair of system clock inputs that drives the input to the on-DIMM PLL.CKE0~CKE1Input Activates the SDRAM CK signal when high and deactivates the CK signal when low. By deactivating the clocks, CKE low initiates the Power Down mode, or the Self Refresh mode.S0~S1Input Enables the associated SDRAM command decoder when low and disables decoder when high. When decoder is dis-abled, new commands are ignored but previous operations continue.These input signals also disable all outputs (except CKE and ODT) of the register(s) on the DIMM when both inputs are high.ODT0~ODT1Input I/O bus impedance control signals.RAS, CAS, WE Input When sampled at the positive rising edge of the clock, CAS, RAS, and WE define the operation to be executed by the SDRAM.V REF Supply Reference voltage for SSTL_18 inputsV DDQ Supply Isolated power supply for the DDR SDRAM output buffers to provide improved noise immunity BA0~BA2Input Selects which SDRAM bank of eight is activated.A0~A9,A10/APA11~A13Input During a Bank Activate command cycle, Address defines the row address.During a Read or Write command cycle, Address defines the column address. In addition to the column address, AP is used to invoke autoprecharge operation at the end of the burst read or write cycle. If AP is high, autoprecharge is selected and BA0, BA1, BA2 defines the bank to be precharged. If AP is low, autoprecharge is disabled. During a Precharge com-mand cycle, AP is used in conjunction with BA0, BA1, BA2 to control which bank(s) to precharge. If AP is high, all banks will be precharged regardless of the state of BA0 or BA1 or BA2. If AP is low, BA0 and BA1 and BA2 are used to define which bank to precharge.DQ0~63,CB0~CB7In/Out Data and Check Bit Input/Output pinsDM0~DM8Input Masks write data when high, issued concurrently with input data. Both DM and DQ have a write latency of one clock once the write command is registered into the SDRAM.V DD, V SS Supply Power and ground for the DDR SDRAM input buffers and core logicDQS0~DQS17In/Out Positive line of the differential data strobe for input and output data.DQS0~DQS17In/Out Negative line of the differential data strobe for input and output data.SA0~SA2Input These signals are tied at the system planar to either V SS or V DDSPD to configure the serial SPD EEPROM address range.SDA In/Out This bidirectional pin is used to transfer data into or out of the SPD EEPROM. A resistor must be connected from the SDA bus line to V DDSPD to act as a pullup.SCL Input This signal is used to clock data into and out of the SPD EEPROM. A resistor may be connected from the SCL bus time to V DDSPD to act as a pullup.V DDSPD Supply Serial EEPROM positive power supply (wired to a separate power pin at the connector which supports from 1.7 Volt to 3.6 Volt operation).RESET Input The RESET pin is connected to the RST pin on the register and to the OE pin on the PLL. When low, all register outputs will be driven low and the PLL clocks to the DRAMs and register(s) will be set to low level (The PLL will remain synchro-nized with the input clock )Par_In Input Parity bit for the Address and Control bus. ( “1 “ : Odd, “0 “ : Even) Err_Out Input Parity error found in the Address and Control busTEST In/Out Used by memory bus analysis tools (unused on memory DIMMs) Input/Output Function Description(populated as 1 rank of x8 DDR2 SDRAMs)1GB, 128Mx72 Module (M393T2863AZ3/M393T2863AZA)RS0DQS0DQS0DM0/DQS9NC/DQS9DM/ RDQS NU/RDQSCS DQS DQSDQ0 DQ1 DQ2 DQ3 DQ4 DQ5 DQ6 DQ7I/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D0DQS1DQS1DM1/DQS10 NC/DQS10DM/ RDQS NU/RDQSCS DQS DQSDQ8 DQ9 DQ10 DQ11 DQ12 DQ13 DQ14 DQ15I/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D1DQS2DQS2DM2/DQS11 NC/DQS11DM/ RDQS NU/RDQSCS DQS DQSDQ16 DQ17 DQ18 DQ19 DQ20 DQ21 DQ22 DQ23I/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D2DQS3DQS3DM3/DQS12 NC/DQS12DM/ RDQS NU/RDQSCS DQS DQSDQ24 DQ25 DQ26 DQ27 DQ28 DQ29 DQ30 DQ31I/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D3DQS8DQS8DM8/DQS17 NC/DQS17DM/ RDQS NU/RDQSCS DQS DQSCB0 CB1 CB2 CB3 CB4 CB5 CB6 CB7I/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D8DQS4DQS4DM4/DQS13NC/DQS13DM/RDQSNU/RDQSCS DQS DQSDQ32DQ33DQ34DQ35DQ36DQ37DQ38DQ39I/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D4DQS5DQS5DM5/DQS14NC/DQS14DM/RDQSNU/RDQSCS DQS DQSDQ40DQ41DQ42DQ43DQ44DQ45DQ46DQ47I/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D5DQS6DQS6DM6/DQS15NC/DQS15DM/RDQSNU/RDQSCS DQS DQSDQ48DQ49DQ50DQ51DQ52DQ53DQ54DQ55I/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D6DQS7DQS7DM7/DQS16NC/DQS16DM/RDQSNU/RDQSCS DQS DQSDQ56DQ57DQ58DQ59DQ60DQ61DQ62DQ63I/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D7A0Serial PDA1A2SA0SA1SA2SCL SDAV SS D0 - D8V DD/V DDQ D0 - D8D0 - D8VREFV DDSPD Serial PDWPNotes :1. DQ-to-I/O wiring may be changed within a byte.2. DQ/DQS/DM/CKE/S relationships must be maintained as shown.3. Unless otherwise noted, resister values are 22 Ohms1:1REGISTERRSTS0*BA0-BA2A0-A13RASCASWECKE0ODT0RESETPCK7PCK7RSO-> CS : DDR2 SDRAMs D0-D8RBA0-RBA2 -> BA0-BA2 : DDR2 SDRAMs D0-D8RA0-RA13 -> A0-A13 : DDR2 SDRAMs D0-D8RRAS -> RAS : DDR2 SDRAMs D0-D8RCAS -> CAS : DDR2 SDRAMs D0-D8RWE -> WE : DDR2 SDRAMs D0-D8RCKE0 -> CKE : DDR2 SDRAMs D0-D8RODT0 -> ODT0 : DDR2 SDRAMs D0-D8PLLOECK0CK0RESETPCK0-PCK6, PCK8, PCK9 -> CK : DDR2 SDRAMs D0-D8PCK0-PCK6, PCK8, PCK9 -> CK : DDR2 SDRAMs D0-D8PCK7 -> CK : RegisterPCK7 -> CK : Register* S0 connects to DCS and VDD connects to CSR on the register.Functional Block DiagramSignals for Address and Command Parity Function (M393T2863AZA)V SSV SS PAR_IN C0C1PPOQERR Err_Out RegisterPAR_IN100K ohmsThe resistors on Par_In, A13, A14, A15, BA2 and the signal line of Err_Out refer to the section: "Register Options for Unused Address inputs"RS0DQS0DQS0DM0/DQS9NC/DQS9DM/RDQS NU/RDQSCS DQS DQSDQ0DQ1DQ2DQ3DQ4DQ5DQ6DQ7I/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D0DQS1DQS1DM1/DQS10NC/DQS10DM/RDQS NU/RDQSCS DQS DQSDQ8DQ9DQ10DQ11DQ12DQ13DQ14DQ15I/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D1DQS2DQS2DM2/DQS11NC/DQS11DM/RDQS NU/RDQSCS DQS DQSDQ16DQ17DQ18DQ19DQ20DQ21DQ22DQ23I/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D2DQS3DQS3DM3/DQS12NC/DQS12DM/RDQS NU/RDQSCS DQS DQSDQ24DQ25DQ26DQ27DQ28DQ29DQ30DQ31I/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D3DQS8DQS8DM8/DQS17NC/DQS17DM/RDQS NU/RDQSCS DQS DQSCB0CB1CB2CB3CB4CB5CB6CB7I/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D8DQS4DQS4DM4/DQS13NC/DQS13DM/RDQS NU/RDQSCS DQS DQSDQ32DQ33DQ34DQ35DQ36DQ37DQ38DQ39I/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D4DQS5DQS5DM5/DQS14NC/DQS14DM/RDQS NU/RDQSCS DQS DQSDQ40DQ41DQ42DQ43DQ44DQ45DQ46DQ47I/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D5DQS6DQS6DM6/DQS15NC/DQS15DM/RDQS NU/RDQSCS DQS DQSDQ48DQ49DQ50DQ51DQ52DQ53DQ54DQ55I/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D6DQS7DQS7DM7/DQS16NC/DQS16DM/RDQS NU/RDQSCS DQS DQSDQ56DQ57DQ58DQ59DQ60DQ61DQ62DQ63I/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D7DM/RDQS NU/RDQSCS DQS DQSI/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D9DM/RDQS NU/RDQSCS DQS DQSI/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D10DM/RDQS NU/RDQSCS DQS DQSI/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D11DM/RDQS NU/RDQSCS DQS DQSI/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D12DM/RDQS NU/RDQSCS DQS DQSI/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D17DM/RDQS NU/RDQSCS DQS DQSI/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D13DM/RDQS NU/RDQSCS DQS DQSI/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D14DM/RDQS NU/RDQSCS DQS DQSI/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D15DM/RDQS NU/RDQSCS DQS DQSI/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D16RS1A0Serial PDA1A2SA0SA1SA2SCLSDAV SSD0 - D17V DD /V DDQ D0 - D17D0 - D17VREF V DDSPDSerial PD WP Notes :1. DQ-to-I/O wiring may be changed per nibble.2. Unless otherwise noted, resister values are 22 Ohms3. RS0 and RS1 alternate between the back and front sides of the DIMM1:2R E G I S T E RRSTS1*BA0-BA2A0-A13RAS CAS WE CKE0CKE1RESET**PCK7**PCK7**RS1-> CS : DDR2 SDRAMs D9-D17RBA0-RBA2 -> BA0-BA2: DDR2 SDRAMs D0-D17RA0-RA13 -> A0-A13 : DDR2 SDRAMs D0-D17RRAS -> RAS : DDR2 SDRAMs D0-D17RCAS -> CAS : DDR2 SDRAMs D0-D17RWE -> WE : DDR2 SDRAMs D0-D17RCKE0 -> CKE : DDR2 SDRAMs D0-D8RCKE1 -> CKE : DDR2 SDRAMs D9-D17P L LOECK0CK0RESETPCK0-PCK6, PCK8, PCK9 -> CK : DDR2 SDRAMs D0-D17PCK0-PCK6, PCK8, PCK9 -> CK : DDR2 SDRAMs D0-D17PCK7 -> CK : Register PCK7 -> CK : RegisterODT0ODT1RODT0 -> ODT0 : DDR2 SDRAMs D0-D8RODT1 -> ODT1 : DDR2 SDRAMs D9-D17S0*RSO-> CS : DDR2 SDRAMs D0-D8(populated as 2 rank of x8 DDR2 SDRAMs)2GB, 256Mx72 Module (M393T5663AZ3/M393T5663AZA)* S0 connects to DCS and S0 connects to CSR on a Register,S1 connects to DCS and S0 connects to CSR on another Register.** RESET, PCK7 and PCK7 connects to both Registers. Other signals connect to one of two Registers.Signals for Address and Command Parity Function (M393T5663AZA)V SS V DDPAR_IN C0C1PPO QERRRegister APAR_IN 100K ohmsThe resistors on Par_In, A13, A14, A15, BA2 and the signal line of Err_Out refer to the section: "Register Options for Unused Address inputs"V DD V DDC0C1PPO QERRErr_OutRegister BPAR_INVSSRS0DQS0DQS0DM CS DQS DQSDQ0 DQ1 DQ2 DQ3I/O 0I/O 1I/O 2I/O 3D0DM0/DQS9NC/DQS9DM CS DQS DQSDQ4DQ5DQ6DQ7I/O 0I/O 1I/O 2I/O 3D9DQS1DQS1DM CS DQS DQSDQ8 DQ9 DQ10 DQ11I/O 0I/O 1I/O 2I/O 3D1DM1/DQS10NC/DQS10DM CS DQS DQSDQ12DQ13DQ14DQ15I/O 0I/O 1I/O 2I/O 3D10DQS2DQS2DM CS DQS DQSDQ16 DQ17 DQ18 DQ19I/O 0I/O 1I/O 2I/O 3D2DM2/DQS11NC/DQS11DM CS DQS DQSDQ20DQ21DQ22DQ23I/O 0I/O 1I/O 2I/O 3D11DQS3DQS3DM CS DQS DQSDQ24 DQ25 DQ26 DQ27I/O 0I/O 1I/O 2I/O 3D3DM3/DQS12NC/DQS12DM CS DQS DQSDQ28DQ29DQ30DQ31I/O 0I/O 1I/O 2I/O 3D12DQS5DQS5DM CS DQS DQSDQ40 DQ41 DQ42 DQ43I/O 0I/O 1I/O 2I/O 3D5DM5/DQS14NC/DQS14DM CS DQS DQSDQ44DQ45DQ46DQ47I/O 0I/O 1I/O 2I/O 3D14DQS4DQS4DM CS DQS DQSDQ32 DQ33 DQ34 DQ35I/O 0I/O 1I/O 2I/O 3D4DM4/DQS13NC/DQS13DM CS DQS DQSDQ36DQ37DQ38DQ39I/O 0I/O 1I/O 2I/O 3D13DQS6DQS6DM CS DQS DQSDQ48 DQ49 DQ50 DQ51I/O 0I/O 1I/O 2I/O 3D6DM6/DQS15NC/DQS15DM CS DQS DQSDQ52DQ53DQ54DQ55I/O 0I/O 1I/O 2I/O 3D15DQS8DQS8DM CS DQS DQSCB0 CB1 CB2 CB3I/O 0I/O 1I/O 2I/O 3D8DM8/DQS17NC/DQS17DM CS DQS DQSCB4CB5CB6CB7I/O 0I/O 1I/O 2I/O 3D17DQS7DQS7DM CS DQS DQSDQ56 DQ57 DQ58 DQ59I/O 0I/O 1I/O 2I/O 3D7DM7DQS16NC/DQS16DM CS DQS DQSDQ60DQ61DQ62DQ63I/O 0I/O 1I/O 2I/O 3D16A0Serial PDA1A2SA0SA1SA2SCL SDAV SS D0 - D17V DD/V DDQ D0 - D17D0 - D17VREFV DDSPD Serial PDWPNotes :1. DQ-to-I/O wiring may be changed per nibble.2. Unless otherwise noted, resister values are 22 Ohms 1:2REGISTERRSTS0*BA0-BA2A0-A13RASCASWECKE0ODT0RESET**PCK7** PCK7**RSO-> CS : DDR2 SDRAMs D0-D17RBA0-RBA2 -> BA0-BA2 : DDR2 SDRAMs D0-D17RA0-RA13 -> A0-A13 : DDR2 SDRAMs D0-D17RRAS -> RAS : DDR2 SDRAMs D0-D17RCAS -> CAS : DDR2 SDRAMs D0-D17RWE -> WE : DDR2 SDRAMs D0-D17RCKE0 -> CKE : DDR2 SDRAMs D0-D17RODT0 -> ODT0 : DDR2 SDRAMs D0-D17PLLOECK0CK0RESETPCK0-PCK6, PCK8, PCK9 -> CK : DDR2 SDRAMs D0-D8PCK0-PCK6, PCK8, PCK9 -> CK : DDR2 SDRAMs D0-D8PCK7 -> CK : RegisterPCK7 -> CK : Register(populated as 1 rank of x4 DDR2 SDRAMs)2GB, 256Mx72 Module (M393T5660AZ3/M393T5660AZA)* S0 connects to DCS of Register1, CSR of Register2. CSR of reg-ister 1 and DCS of register 2 connects to VDD.** RESET, PCK7 and PCK7 connects to both Registers. Other sig-nals connect to one of two Registers.Signals for Address and Command Parity Function (M393T5660AZA)V SSV DDPAR_INC0C1PPOQERRRegister APAR_IN100K ohmsThe resistors on Par_In, A13, A14, A15, BA2 and thesignal line of Err_Out refer to the section: "RegisterOptions for Unused Address inputs"V DDV DDC0C1PPOQERR Err_OutRegister BPAR_IN(populated as 2 rank of x4 DDR2 SDRAMs)A0Serial PDA1A2SA0SA1SA2SCLSDAV SSD0 - D35V DD /V DDQ D0 - D35D0 - D35VREF V DDSPDSerial PD WP P L LOECK0CK0RESET PCK0-PCK6, PCK8, PCK9 -> CK : DDR2 SDRAMs D0-D35PCK0-PCK6, PCK8, PCK9 -> CK : DDR2 SDRAMs D0-D35PCK7 -> CK : Register PCK7 -> CK : Register1:2R E G I S T E RRSTS1*BA0-BA2A0-A13RAS CAS WE CKE0CKE1RESET**PCK7**PCK7**RS1-> CS : DDR2 SDRAMs D18-D35RBA0-RBA2 -> BA0-BA2 : DDR2 SDRAMs D0-D35RA0-RA13 -> A0-A13 : DDR2 SDRAMs D0-D35RRAS -> RAS : DDR2 SDRAMs D0-D35RCAS -> CAS : DDR2 SDRAMs D0-D35RWE -> WE : DDR2 SDRAMs D0-D35RCKE0 -> CKE : DDR2 SDRAMs D0-D17RCKE1 -> CKE : DDR2 SDRAMs D18-D35ODT0ODT1RODT0 -> ODT0 : DDR2 SDRAMs D0-D17RODT1 -> ODT1 : DDR2 SDRAMs D18-D35S0*RSO-> CS : DDR2 SDRAMs D0-D174GB, 512Mx72 Module (M393T5168AZ0/M393T5166AZA)* S0 connects to DCS and S0 connects to CSR on a Register,S1 connects to DCS and S0 connects to CSR on another Register.** RESET, PCK7 and PCK7 connects to both Registers. Other signals connect to one of two Registers.VSS RS0DQS0DQS0DMCSDQS DQSDQ0DQ1DQ2DQ3I/O 0I/O 1I/O 2I/O 3D0DM0/DQS9NC/DQS9DMCSDQS DQSDQ4DQ5DQ6DQ7I/O 0I/O 1I/O 2I/O 3D9DQS1DQS1DM CS DQS DQS DQ8DQ9DQ10DQ11I/O 0I/O 1I/O 2I/O 3D1DM1/DQS10NC/DQS10DM CS DQS DQS DQ12DQ13DQ14DQ15I/O 0I/O 1I/O 2I/O 3D10DQS2DQS2DM CS DQS DQS DQ16DQ17DQ18DQ19I/O 0I/O 1I/O 2I/O 3D2DM2/DQS11NC/DQS11DM CS DQS DQS DQ20DQ21DQ22DQ23I/O 0I/O 1I/O 2I/O 3D11DQS3DQS3DM CS DQS DQS DQ24DQ25DQ26DQ27I/O 0I/O 1I/O 2I/O 3D3DM3/DQS12NC/DQS12DM CS DQS DQS DQ28DQ29DQ30DQ31I/O 0I/O 1I/O 2I/O 3D12DQS5DQS5DM CS DQS DQS DQ40DQ41DQ42DQ43I/O 0I/O 1I/O 2I/O 3D5DM5/DQS14NC/DQS14DM CS DQS DQS DQ44DQ45DQ46DQ47I/O 0I/O 1I/O 2I/O 3D14DQS4DQS4DM CS DQS DQS DQ32DQ33DQ34DQ35I/O 0I/O 1I/O 2I/O 3D4DM4/DQS13NC/DQS13DM CS DQS DQS DQ36DQ37DQ38DQ39I/O 0I/O 1I/O 2I/O 3D13DQS6DQS6DM CS DQS DQS DQ48DQ49DQ50DQ51I/O 0I/O 1I/O 2I/O 3D6DM6/DQS15NC/DQS15DM CS DQS DQS DQ52DQ53DQ54DQ55I/O 0I/O 1I/O 2I/O 3D15DQS8DQS8DM CS DQS DQS CB0CB1CB2CB3I/O 0I/O 1I/O 2I/O 3D8DM8/DQS17NC/DQS17DM CS DQS DQS CB4CB5CB6CB7I/O 0I/O 1I/O 2I/O 3D17DQS7DQS7DM CS DQS DQS DQ56DQ57DQ58DQ59I/O 0I/O 1I/O 2I/O 3D7DM7DQS16NC/DQS16DM CS DQS DQS DQ60DQ61DQ62DQ63I/O 0I/O 1I/O 2I/O 3D16DM/CSDQS DQSI/O 0I/O 1I/O 2I/O 3D18DM/CS DQS DQS I/O 0I/O 1I/O 2I/O 3D19DM/CS DQS DQS I/O 0I/O 1I/O 2I/O 3D20DM CS DQS DQS I/O 0I/O 1I/O 2I/O 3D21DM CS DQS DQS I/O 0I/O 1I/O 2I/O 3D23DM CS DQS DQS I/O 0I/O 1I/O 2I/O 3D22DM CS DQS DQS I/O 0I/O 1I/O 2I/O 3D24DM CS DQS DQS I/O 0I/O 1I/O 2I/O 3D26DM CS DQS DQS I/O 0I/O 1I/O 2I/O 3D25DMCSDQS DQSI/O 0I/O 1I/O 2I/O 3D27DM CS DQS DQSI/O 0I/O 1I/O 2I/O 3D28DM CS DQS DQSI/O 0I/O 1I/O 2I/O 3D29DM CS DQS DQSI/O 0I/O 1I/O 2I/O 3D30DM CS DQS DQSI/O 0I/O 1I/O 2I/O 3D32DM CS DQS DQSI/O 0I/O 1I/O 2I/O 3D31DM CS DQS DQSI/O 0I/O 1I/O 2I/O 3D33DM CS DQS DQSI/O 0I/O 1I/O 2I/O 3D35DM CS DQS DQSI/O 0I/O 1I/O 2I/O 3D34RS1Signals for Address and Command The resistors on Par_In, A13, A14, A15, BA2and the signal line of Err_Out refer to the sec-tion: "Register Options for Unused Address inputs"PAR_INErr_Out100K ohmsV SS V DDC0C1PPO QERRRegister A1PAR_INV DD V DDC0C1PPO QERRRegister B1PAR_INV SS V DDC0C1PPO QERRRegister A2PAR_INV DD V DDC0C1PPO QERRRegister B2PAR_INParity Function (M393T5166AZA)Register A1 and A2 share the a part of Add/Cmd input signal set.Register B1 and B2 share the rest part of Add/Cmd input signal set.Recommended DC Operating Conditions (SSTL - 1.8)Note : There is no specific device V DD supply voltage requirement for SSTL-1.8 compliance. However under all conditions V DDQ must be less than or equalto V DD .1. The value of V REF may be selected by the user to provide optimum noise margin in the system. Typically the value of V REF is expected to be about 0.5 x V DDQ of the transmitting device and V REF is expected to track variations in V DDQ .2. Peak to peak AC noise on V REF may not exceed +/-2% V REF (DC).3. V TT of transmitting device must track V REF of receiving device.4. AC parameters are measured with V DD , V DDQ and V DDL tied together.Symbol ParameterRatingUnits NotesMin.Typ. Max.V DD Supply Voltage 1.7 1.8 1.9V V DDL Supply Voltage for DLL 1.7 1.8 1.9V 4V DDQ Supply Voltage for Output 1.7 1.8 1.9V 4V REF Input Reference Voltage 0.49*V DDQ 0.50*V DDQ0.51*V DDQ mV 1,2V TTTermination VoltageV REF -0.04V REFV REF +0.04V3 Note :1. Stresses greater than those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.2. Storage Temperature is the case surface temperature on the center/top side of the DRAM. For the measurement conditions, please refer to JESD51-2standard.Symbol ParameterRating Units Notes V DD Voltage on V DD pin relative to V SS - 1.0 V ~ 2.3 V V 1V DDQ Voltage on V DDQ pin relative to V SS - 0.5 V ~ 2.3 V V 1V DDL Voltage on V DDL pin relative to V SS - 0.5 V ~ 2.3 V V 1V IN, V OUT Voltage on any pin relative to V SS - 0.5 V ~ 2.3 V V1T STGStorage Temperature-55 to +100°C 1, 2AC & DC Operating ConditionsAbsolute Maximum DC Ratings。

AD408M166RCA-5中文资料