0201超小封装ESD保护器件

esd器件选用大全

ESD保护器件选型建议ESD保护器件的分类ESD保护元件应该保持在不动作状态,同时不会对电子系统的功能造成任何影响,这可以通过维持低电流以及足以在特定数据传输速率下维持数据完整性的低电容值来达成。

而在ESD 应力冲击或者说大电流冲击条件下,ESD 保护元件的第一个要求就是必须能够正常工作,要有够低的电阻以便能够限制受保护点的电压;其次,必须能够快速动作,这样才能使上升时间低于纳秒的ESD 冲击上升时间。

众所周知,对于电子系统而言,它必须能够在IEC 61000-4-2 标准测试条件下存续。

ESD器件一般有以下几种:1、以硅技术为代表的过ESD器件,如瞬态电压抑制器TVS管2、以陶瓷技术为代表的ESD器件,如多层压敏电阻MLV, 金属氧化物压敏电阻MOV等3、以聚合物技术为代表的ESD器件在这几种保护元件中,压敏电阻在低电压时,呈现出高电阻,其中的每个小型二极管两端的电压都相当低,同时电流也相当小;而在较高电压时,其中的独立二极管开始导通,同时压敏电阻的电阻会下降。

从表1 中我们也可以看出压敏电阻为双向保护元件。

压敏电阻采用的是物理吸收原理,每经过一次ESD 事件,材料就会受到一定的物理损伤,形成无法恢复的漏电通道;而且,要达到更好的吸收效果,就要使用更多的材料,使其体积增加,进而限制了在今天小型化产品当中的应用。

而对于带导电粒子的聚合物而言,在正常电压下,这些材料拥有相当高的电阻,但当发生ESD 冲击时,导电粒子间的小间隙会成为突波音隙阵列,从而形成低电阻路径。

瞬态电压抑制器(TVS)则为采用标准与齐纳二极管特性设计的硅芯片元件。

TVS元件主要针对能够以低动态电阻承载大电流的要求进行优化,由于TVS 元件通常采用集成电路(IC)方式生产,因此我们可以看到各种各样的单向、双向及以阵列方式排列的单芯片产品。

压敏电阻介绍压敏电阻器简称VSR,是一种对电压敏感的非线性过电压保护半导体元件。

普通电阻器遵守欧姆定律,而压敏电阻器的电压与电流则呈特殊的非线性关系。

ESD保护器件的主要特性参数分析(精)

TVS二极管是专门设计用于吸收ESD能量并且保护系统免遭ESD损害的固态元件。如果应用得当,TVS二极管将限制跨在被保护器件上的电压刚好高过额定工作电压,但是却远低于破坏阈值电压。

TVS相关参数Leabharlann 处理瞬时脉冲对器件损害的最好办法是将瞬时电流从敏感器件引开。TVS二极管在线路板上与被保护线路并联,当瞬时电压超过电路正常工作电压后,TVS二极管便发生雪崩,提供给瞬时电流一个超低电阻通路,其结果是瞬时电流通过二极管被引开,避开被保护器件,并且在电压恢复正常值之前使被保护回路一直保持截止电压。当瞬时脉冲结束以后,TVS二极管自动回复高阻状态,整个回路进入正常电压。许多器件在承受多次冲击后,其参数及性能会发生退化,而只要工作在限定范围内,二极管将不会发生损坏或退化。

因为利用先进工艺技术制造的IC电路里氧化层比较薄,栅极氧化层更易受到损害。这意味着较高的箝位电压将在被保护IC器件上产生较高的应变电压,并且增加了失效的概率。

很多保护元件都被设计成可吸收大量的能量,由于元件结构或设计上的原因也导致其具有很高的箝位电压。由于变阻器的箝位电压太高,他们不能够提供有效的ESD保护。此外,由于变阻器的高电容他们也不能给高速数据线路提供保护。TVS二极管正是为解决此问题而产生的,它已成为保护便携电子设备的关键性技术。

esd保护器件和电路保护原理

esd保护器件和电路保护原理电子设备在日常使用和维护过程中,往往会遇到静电放电(ESD)的问题。

由于ESD的高能量特性,如果不加以有效的保护措施,会对设备的电路产生严重破坏。

因此,ESD保护器件和电路保护原理成为了电子设备设计中重要的考虑因素之一。

一、ESD保护器件为了有效地保护电子设备免受ESD的危害,研发出了各种ESD保护器件。

这些器件通常是使用低电阻材料和特殊的设计来吸收或分散ESD所带来的能量,从而保护设备电路的完整性。

以下介绍几种常见的ESD保护器件。

1. 二极管二极管是一种常用的ESD保护器件。

它可以承受较高的电压,并具有快速响应的特性。

当输入电压超过二极管的正向电压阈值时,二极管开始导通电流,从而分散和吸收ESD能量。

由于其简单性和有效性,二极管被广泛应用于各种电子设备中。

2. 金属氧化物半导体场效应管(MOSFET)MOSFET是另一种常见的ESD保护器件。

它具有低电阻和高响应速度的特点,能够有效地吸收和分散ESD的能量。

MOSFET通常用于高速信号线的保护,如USB接口和以太网端口。

3. 电磁继电器电磁继电器是一种特殊的ESD保护器件,主要用于对电路进行隔离和保护。

它通过电磁感应原理来控制电路的开关状态,从而保护设备免受ESD损害。

电磁继电器常用于高压和高功率电路的保护。

二、电路保护原理除了使用ESD保护器件外,设计合理的电路保护方案也是预防ESD引起的损害的重要手段。

下面介绍几种常见的电路保护原理。

1. 地线设计良好的地线设计可以有效地减少ESD放电路径上的电阻和电压。

将设备的地线与ESD保护器件连接,可以将ESD的能量引流到地线上,从而保护电路不受损害。

地线还可以起到隔离和屏蔽的作用,避免外部ESD对设备的影响。

2. 前端过滤器在电子设备的输入端加入前端过滤器可以有效地降低外部ESD噪声对电路的影响。

前端过滤器通常采用滤波器和瞬态电压抑制器,用于滤除高频噪声和抑制ESD波形。

泰科电子推出业界最小的0201封装

A C A 0 8 ae s :16 P C S2 0 .P s ( ) 24—16 27

4 高明伦 . o 下 一代 集成 电路 主 流 设 计 N C:

技 术. 电子 学 ,0 6 微 20

5 “ t t【I e i e Ha d o k Sr i I D vc n b o ”.Al a C — a) mr o p a in。 0 7 rt o 2 0.

5 2

纂戚 躐遗 : 诋

第8 第 期 2 1 卷

处理 器软 核 , 解 码算 法 同样 适 用 于其 他 片 上 多 但 核处 理器 架 构 。同 时 , 片上 多核 处 理器 架 构 的任 务分解 优 化方 法 , 于其 他运 行 于 多核 处 理 器架 对

型 芯片 实现技 术研 究. 士论文.07 博 20

核 数越 多 、 并行 度 越 高 时 , 采用 N C结 构 可 以提 O 供最 好性 能 。对 于不 同的应 用 , 体选 择 哪 种 通 具 讯 结构 , 本文具 有一 定的借鉴 作用 , 当然还 要依 赖

于系统需 求 和更详 细 的测试 。 参考 文献

6 D. a b n. . rc l n,P G2 0 I T u ma M Ma el J l 0 0,m— e i E

《 集成电路通讯》 编辑部 摘

器 、 D 和数 码 相 机 等 便 携 式 电子 产 品 提 供 保 护和 提 高 其 可 靠 性 。 这 些 S S 器 件 的实 际 P A ED 大 小 仅 为 0 6 mmO 3 m0 3 m, 设 计 师 们 在 空 间 受 限 的 应 用 中 提 供 了 灵 活 性 。 .0 . r .r a a 为

布式 共享 总线结 构 可 以提 供 较好 性 能 , 该 结 构 但 在后 端设 计时 , 分布式 总线 布局是个 挑 战。

几种ESD器件的特性及选型原则

ESD器件ESD器件概述ESD保护元件的作用是转移来自敏感元件的ESD应力,使电流流过保护元件而非敏感元件,同时维持敏感元件上的低电压;ESD保护元件还应具有低泄漏和低电容特性,不会降低电路功能;不会对高速信号造成损害,在多重应力作用下保护元件的功能不会下降。

瞬态电压抑制器(TVS)、压敏电阻和聚合物是近几年发展起来的几种专用ESD保护元件。

其中前两种元件均采用电压钳位的方式进行保护,采用带导电粒子的聚合物则是采用消弧(crowbar)保护策略。

压敏电阻和聚合物支持双向保护,但TVS可支持单向或双向保护。

传统的压敏电阻虽然在成本上具有一定优势,但它存在的一个最大问题是体积太大,无法满足手持设备的封装要求。

事实上,与压敏电阻相比,基于硅材料的TVS和聚合物材料ESD具有更好的钳制性能、更低的泄漏和更长的使用寿命。

高分子聚合物和TVS在多重应力下仍然可保持强大的性能,而压敏电阻则会随着使用次数的增多性能下降。

TVS技术利用的是半导体的钳位原理,在经受瞬时高压时,会立即将能量释放出去,而压敏电阻采用的是物理吸收原理,因此每经过一次ESD事件,材料就会受到一定的物理损伤,形成无法恢复的漏电通道。

“TVS技术的原理就好像传统的打太极,可以轻松释放掉能量而不是直接与之对抗”。

这样做的好处是器件不会受到损害,基本上没有寿命限制。

从现场展示的TVS与压敏电阻的钳制电压曲线来看,TVS器件可以在极短时间内将输入的大电压钳制到5至6伏的水平,而压敏电阻的曲线则下降得非常缓慢,并且无法达到TVS 器件的效果。

这表明TVS器件在响应时间和钳制性能方面均优于压敏电阻。

几种ESD器件的比较1、普通二极管,只能起到箝制电压的作用,不能响应高达几百兆频率的ESD脉冲。

2、压敏电阻/热敏电阻/PTC,压敏电阻抗一次ESD脉冲后特性就会改变,而ESD 保护器件抗几万次也不会改变特性。

3、压敏电阻能承受更大的浪涌电流,而且其体积越大所能承受的浪涌电流越大,最大可达几十kA到上百kA;但压敏电阻的非线性特性较差,大电流时限制电压较高,低电压时漏电流较大。

ESD基础知识

2023-11-07•esd概述•esd基本原理•esd器件类型•esd电路保护元件•esd设计原则目•esd在电子系统中的应用•esd的未来发展趋势及挑战录01 esd概述esd定义能源服务认证(ESCO)ESCO认证是指对ESCO所提供的能源服务进行审核和评估,以确保其符合相关标准和要求。

ESCO服务ESCO服务包括能源审计、能源管理、能源效率改造、能源供应等服务。

能源服务公司(ESCO)ESCO是提供能源审计、能源管理、能源效率改造等服务的企业。

esd的重要性降低能源成本ESCO能够为企业提供能源效率改造和优化方案,从而降低企业的能源成本,提高企业的竞争力。

保护环境ESCO所提供的能源服务能够有效地减少能源消耗和排放,从而减少对环境的污染和破坏。

提高能源效率通过ESCO提供的能源服务,可以有效地提高能源效率,降低能源消耗,减少能源浪费。

esd的应用场景工业领域ESCO可以为工业领域提供全面的能源服务,包括能源审计、能源管理、能源效率改造等,帮助企业提高能源效率、降低能源成本、保护环境。

建筑领域ESCO可以为建筑领域提供建筑能源审计、节能诊断、节能改造等服务,帮助建筑企业降低能源消耗、减少能源浪费、提高建筑能效。

公共机构ESCO可以为政府机构、学校、医院等公共机构提供能源管理、节能改造等服务,帮助公共机构提高能源效率、降低能源成本、保护环境。

02 esd基本原理电容是存储电荷的物理元件,其大小由电极面积、间距和介质决定。

定义工作原理类型在交流电作用下,电容器的电荷会不断充放电,形成电流。

电容包括铝电解电容、钽电解电容、陶瓷电容等。

03电容020103类型电感包括空芯电感、磁芯电感、铁氧体电感等。

01定义电感是存储磁场能量的物理元件,其大小由线圈的匝数、直径和线圈的材料决定。

02工作原理当电流通过线圈时,会产生磁场,从而感应出电动势,阻碍电流的变化。

1 2 3电阻是导体对电流的阻碍作用,其大小由导体的长度、截面积和材料决定。

0201&01005元件组装工艺研究

0201&01005元件组装工艺研究随着表面贴装技术越来越成熟,人们不断要求缩小电子产品的尺寸和重量。

由于主动和被动元件尺寸的缩小以及印刷电路板技术的改进,出现了提及更小、重量更轻、性能更加优良的终端产品。

目前还在进一步研究继续缩小元件尺寸,使得设计者能更小的印刷电路板实现预定功能,0603 和0402元件的广泛使用已有多年,这些元件能够在批量应用中有很高的装配良率。

最近,0201/01005元件已经进行系统装配,在手机、数码像机、无线蓝牙等产品中得以应用。

0201元件约为0402元件尺寸的四分之一,而01005元件则约为0201元件尺寸的四分之一。

较小尺寸的元件可能会降低装配工艺的稳健性。

这类细小元件的装配比其它元件在工艺材料的选择、设计、工艺的控制方面更具敏感性。

由于本身的尺寸非常小,它的尺寸公差对装配工艺也会产生非常显著的影响。

所以,细小元件的装配工艺不同于其它元件,需要更加精确的控制。

贴装细小元件的关键因素包括贴片机的定位系统,取料过程控制,贴片机的影像系统,和对贴片过程的控制。

除了这些因素之外,还有一些不容忽视的地方,如送料器的精度,元件包装的误差和元件本身的误差,吸嘴的材料设计等等,都是在装配之前需要综合考虑的,本文我们主要讨论的是细小元件的贴片控制工艺。

SMT片式贴装零件发展趋势一、片式零件发展趋势电子消费品的小型化发展趋势使得电子零件从80年代的1210、1206缩小到90年代末期的0805、0603和0402,再到目前的0201和01005零件,变化主要动力来源于市场对于小型化低成本高性能产品的需求。

0201元件在和重量上比0402轻75%,占用板面空间小66%,01005元件无论重量和占用板面的空间更加微型,用这种细小片状零件可以大大降低手持式或可携式消费电子产品的尺寸、重量和体积。

二、常用片状零件尺寸介绍0805 0603 0402 0201 01005长(mm) 2.0 1.6 1.0 0.6 0.4宽(mm) 1.2 0.8 0.5 0.3 0.2细小片式(0201&01005)零件组装工艺一、PCB板设计这类细小元件的装配比其它元件在工艺材料的选择、设计、工艺的控制方面更具敏感性。

0603超小尺寸压敏电阻 - Sunlord Electronics

EXPERT IN PASSIVE PARTS0603超小尺寸压敏电阻超小尺寸,适用高密度设计高性能,优良的ESD抑制能力2011.8EXPERT IN PASSIVE PARTS 目录0603压敏电阻基本特性超小尺寸适合高密度封装高性能,优良的ESD抑制能力0603压敏电阻描述产品编号参数描述性能范围和型号对照0603压敏在电路中的应用如何选择压敏电阻器0603压敏电阻的应用手机中的应用1/11EXPERT IN PASSIVE PARTS2/11由于整机的小型化、多功能化,要求电子元件也小型化,例如高端智能手机、耳机、话筒、数据卡等产品都趋向于使用更小尺寸的被动器件。

针对这种需求,我司推出0603(0201)尺寸的压敏电阻,相比1005(0402)尺寸,可以有效减小PCB 占用面积,进一步实现整机小型化。

超小尺寸适合高密度封装78.4640.3±0.050.3±0.050.6±0.05SDV0603//0.5±0.150.5±0.151.0±0.15SDV1005体积缩小率(%)面积缩小率(%)T (mm )W (mm )L (mm )型号EXPERT IN PASSIVE PARTS3/11高性能,优良的ESD 抑制能力SDV0603压敏电阻电性能(与SDV1005比较)158331~3826SDV1005158331~3826SDV06032405~1022~2818SDV10051405~1022~2818SDV060312400.5~2100~16026SDV100512400.5~2100~16014SDV06033~102012~5011~169SDV10051~52012~5011~169SDV06033~101812~5010~145.5SDV10051~51812~5010~145.5SDV0603Peak Current 8/20μS (A )Max. Clamping Voltage (V)Cp(pF) @ 1MHz V1mA (V)Max. Vdc (V)型号EXPERT IN PASSIVE PARTS4/11高性能,优良的ESD 抑制能力SDV0603压敏电阻电性能(与同行型号比较)//0.6~0.95.85.0(Fwd )SESD0201TYCO (TVS )1015.6308.56(Fwd )SP1005-01W Littefuse (TVS )13918125.5CT0201S EPCOS 1~5/8.5~1806.8~273.7~16EZJPZV Panasonic 1~1014~2325~706.8~123.5~7.5AVRM0603TDK //4~7012.8~255.5~10AVLC-01AMOTECH 1~518~580.5~5010~385.5~26SDV0603SUNLORD Peak Current 8/20μS (A )Max. Clamping Voltage (V)Cp(pF) @ 1MHZ V 1mA (V)Max. Vdc (V)型号公司EXPERT IN PASSIVE PARTS 目录0603压敏电阻基本特性超小尺寸适合高密度封装高性能,优良的ESD抑制能力0603压敏电阻描述产品编号参数描述性能范围和型号对照0603压敏在电路中的应用如何选择压敏电阻器0603压敏电阻的应用手机中的应用5/11EXPERT IN PASSIVE PARTS6/11SDV 0603E090 C150 N PT F ①②③④⑤⑥⑦⑧⑨产品编号②尺寸代号(L ×W) (mm)0603 [0201] 0.6×0.3①类型SDV 片式压敏电阻器④最大直流工作电压Example Nominal Value 5R5 5.5V 090 9V⑧包装T 盘装⑤电容@1MHzExample Nominal Value C150 15pF C151 150pF⑥电容公差N ±30%Y +100/-50%G Maximum ③特征代号A 过电压用E ESD 防护用H 高速信号线用S 特殊要求⑦端头代号P Ni, Sn 电镀⑨无有害物质产品FEXPERT IN PASSIVE PARTS7/11参数描述V DC 直流工作电压(使用参数)压敏电阻器在最高操作温度下使用时的最大持续直流工作电压,被用来作为测试漏电流的对应电压点. 该电压总是比压敏电压小. V AC 交流工作电压(使用参数)压敏电阻器在最高操作温度下使用时的最大持续正弦交流工作电压。

ESD知识介绍

感谢您的观看

THANKS

挑战

ESD防护产品的发展也面临着一些挑战,如技术门槛高、研 发周期长、市场竞争激烈等。此外,消费者对ESD防护产品 的认知度还需要进一步提高,需求也需要进一步挖掘。

06

esd防护前沿技术

材料的研发进展

01

02

03

高分子材料

研发具有高导电性、高弹 性、高耐久性的高分子材 料,用于制作ESD防护器 件。

esd保护器件的型号对照

根据不同的应用场景和需求, ESD保护器件分为多种型号, 如二极管、场效应管、气体放

电管等。

不同型号的ESD保护器件具有 不同的参数特性和适用场景, 需要根据具体需求进行选择。

各生产商均会提供其ESD保护 器件的型号对照表,以方便客

户进行选择和使用。

04

esd保护方案的应用

国外市场现状

全球ESD防护产品市场已经进入快速发展阶段,越来越多的企业开始重视ESD防护,投入更多的研发 资源和市场资源。在国外,消费者对ESD防护产品的认知度相对较高,需求量也较大。

esd防护产品的市场发展趋势

技术创新

随着技术的不断发展,ESD防护产品将不断进行技术创新,提高 产品的性能和可靠性,满足客户更高的需求。

esd保护方案的实施步骤

风险评估

对生产过程中可能 出现的ESD事故进行 风险评估,识别出 高风险环节和薄弱 环节。

制定方案

根据风险评估结果 ,制定针对性的ESD 保护方案,明确保 护目标、措施、责 任人等。

方案审批

ESD保护方案需经过 相关部门审批,确 保方案的可行性和 有效性。

方案实施

按照审批通过的ESD 保护方案,各部门 分工合作,落实各 项措施。

优恩半导体新品0201系列TVS管

UN Semiconductor unsemi 优恩半导体新品0201系列TVS 管

优恩半导体新推出0201/DFN0603封装尺寸ESD 静电保护器ESD05V02D-C,ESD05V 02D-C 是低电容TVS 阵列,封装尺寸小、体积小、漏电流低、结电容低。

该0201封装系列产品经过特别设计,用于ESD 保护和低级别的电涌保护,由于其封装小,非常适用于便携式电子产品的ESD 防护,从而帮助电路设计人员降低成本、节约电路板空间,可以通过IE C61000-4-2国际标准。

特性:

工作电压:5V

钳位电压:12V

漏电流:100nA

结电容:6pF 可通过IEC61000-4-2标准

优势:

封装尺寸小,可以满足可携式电子产品轻薄小巧对于组件封装的严苛要求,易于小的电路板空间设计,从而节省了PCB 占用和成本。

体积小,从而帮助电路设计人员降低成本、节约印刷电路板(PCB)空间,以达到在PCB 设计上兼具高聚集度及高度弹性的优势。

漏电流小,对信号的影响小。

业界领先的ESD 保护,满足IEC61000-4-2标准,为工程师带来更多的设计空间和更高的终端产品可靠性。

支持保护充满微型芯片的现代电子设备所需的低箝位电压。

应用领域:

可穿戴设备

笔记本、PC 机、服务器

手机及配件

个人数字助理(PDA's) 医疗设备

产品外观:。

HCPL-0201中文资料

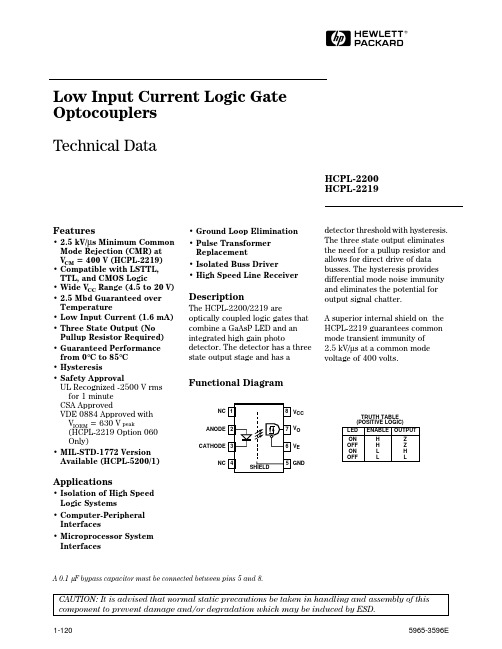

1-120Low Input Current Logic Gate Optocouplers Technical DataHCPL-2200HCPL-2219CAUTION: It is advised that normal static precautions be taken in handling and assembly of this component to prevent damage and/or degradation which may be induced by ESD.Features• 2.5 kV/µs Minimum Common Mode Rejection (CMR) at V CM = 400 V (HCPL-2219)• Compatible with LSTTL,TTL, and CMOS Logic• Wide V CC Range (4.5 to 20V)• 2.5 Mbd Guaranteed over Temperature• Low Input Current (1.6 mA)• Three State Output (No Pullup Resistor Required)• Guaranteed Performance from 0°C to 85°C • Hysteresis• Safety ApprovalUL Recognized -2500 V rms for 1 minute CSA ApprovedVDE 0884 Approved with V IORM = 630 V peak(HCPL-2219 Option 060Only)• MIL-STD-1772 Version Available (HCPL-5200/1)Applications• Isolation of High SpeedLogic Systems• Computer-Peripheral Interfaces• Microprocessor System InterfacesFunctional Diagram• Ground Loop Elimination • Pulse Transformer Replacement• Isolated Buss Driver• High Speed Line ReceiverDescriptionThe HCPL-2200/2219 areoptically coupled logic gates that combine a GaAsP LED and an integrated high gain photodetector. The detector has a three state output stage and has adetector threshold with hysteresis.The three state output eliminates the need for a pullup resistor and allows for direct drive of data busses. The hysteresis provides differential mode noise immunity and eliminates the potential for output signal chatter.A superior internal shield on the HCPL-2219 guarantees common mode transient immunity of 2.5kV/µs at a common mode voltage of 400 volts.A 0.1 µF bypass capacitor must be connected between pins 5 and 8.NC ANODE CATHODE NC GNDV CC V O TRUTH TABLE (POSITIVE LOGIC)LED ON OFF ON OFF ENABLE H H L LV E OUTPUT Z Z H L 5965-3596EHV FV CCV OGNDV EThe Electrical and SwitchingCharacteristics of the HCPL-2200/2219 are guaranteed overthe temperature range of 0°C to85°C and a V CC range of 4.5 voltsto 20 volts. Low I F and wide V CCrange allow compatibility withTTL, LSTTL, and CMOS logic andresult in lower power consump-tion compared to other highspeed optocouplers. Logic signalsare transmitted with a typicalpropagation delay of 160 nsec.Selection GuideNotes:1. HCPL-2200/2219 devices include output enable/disable functionality.2. Minimum CMR of 10 kV/µs with V CM = 1000 V can be achieved with input current, I F, of 5 mA.Ordering InformationSpecify Part Number followed by Option Number (if desired).Example:HCPL-2219#XXX060 = VDE 0884 V IORM = 630 Vpeak Option*300 = Gull Wing Surface Mount Option500 = Tape and Reel Packaging OptionOption data sheets available. Contact your Hewlett-Packard sales representative or authorized distributor for information.*For HCPL-2219 only.SchematicThe HCPL-2200/2219 are usefulfor isolating high speed logicinterfaces, buffering of input andoutput lines, and implementingisolated line receivers in highnoise environments.1-121DIMENSIONS IN MILLIMETERS AND (INCHES).*MARKING CODE LETTER FOR OPTION NUMBERS."V" = OPTION 060OPTION NUMBERS 300 AND 500 NOT MARKED.0.254+ 0.076- 0.051(0.010+ 0.003)- 0.002)Package Outline Drawings8-Pin DIP Package8-Pin DIP Package with Gull Wing Surface Mount Option 300(0.025 ± 0.005)1.080 ± 0.320MAX.(0.100)BSCDIMENSIONS IN MILLIMETERS (INCHES).LEAD COPLANARITY = 0.10 mm (0.004 INCHES).+ 0.076- 0.051+ 0.003)- 0.002)1-1221-123Note: Use of nonchlorine activated fluxes is highly recommended.Maximum Solder Reflow Thermal Profile240TIME – MINUTEST E M P E R A T U R E – °C220200180160140120100806040200260Regulatory InformationThe HCPL-2200/2219 have been approved by the following organizations:ULRecognized under UL 1577,Component Recognition Program, File E55361.CSAApproved under CSA Component Acceptance Notice #5, File CA 88324.VDEApproved according to VDE0884/06.92. (HCPL-2219 Option 060 Only)Insulation and Safety Related SpecificationsParameter Symbol Value Units Conditions Min. External Air Gap L(IO1)7.1mm Measured from input terminals to output terminals,(External Clearance)shortest distance through air.Min. External L(IO2)7.4mm Measured from input terminals to output terminals,Tracking Path shortest distance path along body .(External Creepage)Minimum Internal 0.08mm Through insulation distance, conductor to conductor,Plastic Gap usually the direct distance between the photoemitter (Internal Clearance)and photodetector inside the optocoupler cavity .Tracking Resistance CTI 200V DIN IEC 112/VDE 0303 Part 1(Comparative Tracking Index)Isolation Group IIIa Material Group (DIN VDE 0110, 1/89, Table 1)Option 300 - surface mount classification is Class A in accordance with CECC 00802.VDE 0884 Insulation Related Characteristics (HCPL-2219 OPTION 060 ONLY)*Refer to the front of the optocoupler section of the current catalog, under Product Safety Regulations section, (VDE 0884), for a detailed description.Note: Isolation characteristics are guaranteed only within the safety maximum ratings which must be ensured by protective circuits in application.1-124Absolute Maximum Ratings(No Derating Required up to 70°C)Parameter Symbol Min.Max.Units Note Storage Temperature T S-55125°COperating Temperature T A-4085°C1 Average Forward Input Current I F(AVG)10mAPeak Transient Input Current I F(TRAN) 1.0A(≤1 µs Pulse Width, 300 pps)Reverse Input Voltage V R5VAverage Output Current I O25mASupply Voltage V CC020VThree State Enable Voltage V E-0.520VOutput Voltage V O-0.520VTotal Package Power Dissipation P T210mW1 Lead Solder Temperature260°C for 10 sec., 1.6 mm below seating planeSolder Reflow Temperature Profile See Package Outline Drawings sectionRecommended Operating ConditionsParameter Symbol Min.Max.UnitsPower Supply Voltage V CC 4.520VEnable Voltage High V EH 2.020VEnable Voltage Low V EL00.8VForward Input Current I F(ON) 1.6*5mAForward Input Current I F(OFF)–0.1mAOperating Temperature T A085[1]°CFan Out N4TTL Loads*The initial switching threshold is 1.6 mA or less. It is recommended that 2.2 mA beused to permit at least a 20% CTR degradation guardband.1-125Electrical SpecificationsFor 0°C ≤T A[1]≤85°C, 4.5 V ≤V CC≤20 V, 1.6 mA ≤I F(ON)≤5 mA, 2.0 V ≤V EH≤20 V,0.0 V ≤V EL≤ 0.8 V, 0 mA ≤I F(OFF)≤0.1 mA. All Typicals at T A = 25°C, V CC = 5 V, I F(ON) = 3 mA unless otherwise specified. See Note 7.1-1261-127Switching Specifications (AC)For 0°C ≤T A [1] ≤ 85°C, 4.5 V ≤V CC ≤20 V, 1.6 mA ≤I F(ON) ≤5 mA, 0.0 mA ≤I F(OFF) ≤0.1 mA.All Typicals at T A = 25°C, V CC = 5 V, I F(ON) = 3 mA unless otherwise specified.Parameter Sym.Device Min.UnitsTest ConditionsFig.Note Logic High |CM H |I F = 1.6 mA116Common Mode V CC = 5 V Transient T A = 25°CImmunity Logic Low|CM L |V F = 0 V 116Common Mode V CC = 5 V Transient T A = 25°CImmunityHCPL-22001,000 V/µs |V CM | = 50 VHCPL-22192,500 V/µs |V CM | = 400 V HCPL-22001,000 V/µs |V CM | = 50 V HCPL-22192,500 V/µs|V CM | = 400 VPackage CharacteristicsParameterSym.Min.Typ.Max.UnitsTest Conditions Fig.NoteInput-Output Momentary V ISO 2500V rmsRH ≤50%, t = 1 min.,3, 8Withstand Voltage*T A = 25°CInput-Output Resistance R I-O 1012ΩV I-O = 500 VDC3Input-Output CapacitanceC I-O0.6pFf = 1 MHz, V I-O = 0 VDC3*The Input-Output Momentary Withstand Voltage is a dielectric voltage rating that should not be interpreted as an input-output continuous voltage rating. For the continuous voltage rating refer to the VDE 0884 Insulation Characteristics Table (if applicable), your equipment level safety specification or HP Application Note 1074 entitled “Optocoupler Input-Output Endurance Voltage,” publication number 5963-2203E.1-128OLINPUT I V OFigure 2. Typical Logic High Output Current vs. Temperature.Figure 3. Output Voltage vs. Forward Input Current.Figure 4. Typical Input Diode Forward Characteristic.Figure 1. Typical Logic Low Output Voltage vs. Temperature.Notes:1. Derate total package power dissipa-tion, P T , linearly above 70°C free air temperature at a rate of 4.5mW/°C.2. Duration of output short circuit time should not exceed 10 ms.3. Device considered a two-terminal device: pins 1, 2, 3, and 4 shorted together and pins 5, 6, 7, and 8shorted together.4. The t PLH propagation delay ismeasured from the 50% point on the leading edge of the input pulse to the 1.3 V point on the leading edge of the output pulse. The t PHL propagation delay is measured from the 50% point on the trailing edge of the input pulse to the 1.3 V point on the trailing edge of the output pulse.5. When the peaking capacitor is omitted,propagation delay times may increase by 100 ns.6. CM L is the maximum rate of rise of the common mode voltage that can besustained with the output voltage in the logic low state (V O < 0.8 V). CM H is the maximum rate of fall of the common mode voltage that can beI O H – H I G H L E V E L O U T P U T C U R R E N T – m AT A – TEMPERATURE – °C I F – F O R W A R D C U R R E N T – m A0.001V F – FORWARD VOLTAGE – V1.010000.010.110100sustained with the output voltage in the logic high state (V O > 2.0 V).7. Use of a 0.1 µF bypass capacitor connected between pins 5 and 8 is recommended.8. In accordance with UL1577, eachoptocoupler is proof tested by applying an insulation test voltage ≥3000 V rms for one second (leakage detection current limit, I I-O ≤5 µA). This test is performed before the 100% production test for partial discharge (Method b)shown in the VDE 0884 Insulation Characteristics Table, if applicable.Figure 5. Test Circuit for t PLH , t PHL , t r , and t f .V O L – L O W L E V E L O U T P U T V O L T A G E – VT A – TEMPERATURE – °CV O – O U T P U T V O L T A G E – VI F – INPUT CURRENT – mAΩARE INCLUDED IN C 1 AND C 2.D 2D 3D 4R II F (ON)2.15 k Ω1.6 mA 1.10 k Ω3 mA681 Ω5 mA ALL DIODES ARE 1N916 OR 1N3064.1-129INPUT V EOUTPUT V O 1.5 VOUTPUT V OΩNODED 2D 3D 4Figure 10. Typical Rise, Fall Time vs.Temperature.Figure 8. Typical Logic Low Enable Propagation Delay vs. Temperature.Figure 9. Typical Logic High Enable Propagation Delay vs. Temperature.Figure 7. Test Circuit for t PHZ , t PZH , t PLZ , and t PZL .Figure 6. Typical Propagation Delays vs. Temperature.T p – E N A B L E P RO P A G A T I O N D E L A Y – n sT A – TEMPERATURE – °C t P – E N A B L EP R O P A G A T I O N D E L A Y – n sT A – TEMPERATURE – °C 15020050100t P – P R O P A G A T I O N D E L A Y – n s50T A – TEMPERATURE – °C200250100150t r , t f – R I S E , F A L L T I M E – n sT A – TEMPERATURE – °C120408010020601-130V CC150 VOUTPUT V O* SEE NOTE 6.0 V V OHV OLV O (MAX.)*V O (MIN.)*SWITCH AT A: I F = 1.6 mA SWITCH AT B: I F = 0 mAV CMFigure 11. Test Circuit for Common Mode Transient Immunity and Typical Waveforms.Figure 13. Recommended LSTTL to LSTTL Circuit.Figure 15. Recommended LED Drive Circuit.Figure 12. Thermal Derating Curve,Dependence of Safety Limiting Value with Case Temperature per VDE 0884.Figure 14. LSTTL to CMOS Interface Circuit.Figure 16. Series LED Drive with Open Collector Gate (4.7 k Ω Resistor Shunts I OH from the LED).*The 120 pF capacitor may be omitted in applications where 500 ns propagation delay is sufficient.O RV FFO U T P U T P O W E R – P S , I N P U T C U R R E N T – I S0T S – CASE TEMPERATURE – °C400600800200100300500700DATA INPUT V CC2(+5 V)V DATAOUTPUTV CCDATA INPUT V DATA OUTPUT15 V 20 V3.83 K 5.11 K元器件交易网。

ESD5311Z-2TR DFN0603-2L 0201双向电压5V结电容0.25PF超低电容管

ESD5311Z1-Line, Bi-directional, Ultra-low CapacitanceTransient Voltage SuppressorDescriptionsThe ESD5311Z is an ultra-low capacitance TVS (Transient Voltage Suppressor) designed to protect high speed data interfaces. It has been specifically designed to protect sensitive electronic components which are connected to data and transmission lines from over-stress caused by ESD (Electrostatic Discharge).The ESD5311Z incorporates one pair of ultra-low capacitance steering diodes plus a TVS diode.The ESD5311Z may be used to provide ESD protection up to ±20kV (contact discharge) according to IEC61000-4-2, and withstand peak pulse current up to 4A (8/20μs) according to IEC61000-4-5.The ESD5311Z is available in DFN0603-2L package. Standard products are Pb-free and Halogen-free.Features●Stand-off voltage: 5V Max.●Transient protection for each line according toIEC61000-4-2 (ESD): ±20kV (contact discharge)IEC61000-4-4 (EFT): 40A (5/50ns)IEC61000-4-5 (surge): 4 A (8/20μs)●Ultra-low capacitance: C J = 0.25pF typ.●Ultra-low leakage current: I R < 1nA typ.●Low clamping voltage: V CL = 21V typ. @ I PP = 16A (TLP) ●Small packageApplications●USB 2.0 and USB 3.0 ●HDMI 1.3 and HDMI 1.4 ●SATA and eSATA●DVI●IEEE 1394●PCI Express●Portable Electronics●NotebooksDFN0603-2L (Bottom View)Pin configurationD = Device code* = Month codeMarking (Top View)Order informationPin1Pin2Pin1Pin2354371306.35.409.645 0 1 5 8Absolute maximum ratingsElectrical characteristics (T A=25 o C, unless otherwise noted)Notes:1) TLP parameter: Z0= 50Ω, t p = 100ns, t r = 2ns, averaging window from 60ns to 80ns. R DYN is calculated from 4A to16A.2) Contact discharge mode, according to IEC61000-4-2.3) Non-repetitive current pulse, according to IEC61000-4-5.Typical characteristics (T A=25o C, unless otherwise noted)8/20μs waveform per IEC61000-4-5Clamping voltage vs. Peak pulse currentNon-repetitive peak pulse power vs. Pulse timeContact discharge current waveform per IEC61000-4-2Capacitance vs. Reverse voltagePower derating vs. Ambient temperature 11010010001101001000Peakpulsepower(W)Pulse time (μs)025507510012515020406080100%ofRatedpowerTA- Ambient temperature (o C)VC-Clampingvoltage(V)IPP- Peak pulse current (A)Current(%)C J-Junctioncapacitance(pF)RPeakpulsecurrent(%)ESD clamping(+8kV contact discharge per IEC61000-4-2)TLP MeasurementESD clamping(-8kV contact discharge per IEC61000-4-2)T L P c u r r e n t (A )TLP voltage (V)PACKAGE OUTLINE DIMENSIONSDFN0603-2LTOP VIEW BOTTOM VIEWSIDE VIEWRecommended PCB Layout (Unit: mm)SymbolDimensions in MillimetersMin. Typ. Max.A 0.230.300.34A1 0.000.030.05A3 0.10Ref.D 0.550.600.67E 0.250.300.37b 0.100.150.20L 0.200.240.30e 0.40RefNotes:This recommended land pattern is for referencepurposes only. Please consult your manufacturinggroup to ensure your PCB design guidelines are met.TAPE AND REEL INFORMATIONReel DimensionsTape DimensionsQuadrant Assignments For PIN1 Orientation In TapeQ1Q2Q4Q3Q1Q2Q4Q3RD Reel DimensionW Overall width of the carrier tape 1 P1Pitch between successive cavity centersPin1 Pin1 QuadrantUser Direction of Feed7inch13inch2mm 4mm 8mm Q1Q2Q3Q48mm 12mm 16mm。

ESD保护器件的主要特性参数分析及典型应用

ESD保护器件的主要特性参数分析及典型应用ESD保护器件是一种用于保护电子设备和电路免受静电放电损害的电子元件。

它们可以在电路中实现静电放电的引流和吸收,减小对IC器件的损害,提高系统的可靠性。

下面将对ESD保护器件的主要特性参数进行分析,并介绍其典型应用。

1. 静电放电等级 (ESD Rating):静电放电等级是ESD保护器件能够承受的最大静电放电能量。

该等级通常以KV表示,例如4KV。

ESD保护器件的静电放电等级决定了其能够保护器件免受不同程度静电放电的能力。

2. 保护电流 (Clamping Voltage):保护电流是指ESD保护器件在正常工作状态下对电路传导的最大电流。

当静电放电事件发生时,ESD保护器件能够引导其中大部分能量,并将其吸收释放。

保护电流的大小取决于ESD保护器件的设计和制造工艺。

3. 响应时间 (Response Time):响应时间是指ESD保护器件在检测到静电放电事件时,从无状态到达保护状态的时间。

较低的响应时间意味着ESD保护器件能更快地响应和吸收静电放电能量,从而减小对IC器件的损害。

4. 工作电流 (Operating Current):工作电流是指ESD保护器件在正常工作状态下的最大电流。

它通常取决于ESD保护器件的结构和材料。

典型应用:1.数字电路保护:ESD保护器件可以用于保护数字电路中的IC器件,如芯片、微控制器和FPGA等,免受静电放电损坏。

在数字电路中,静电放电可能导致芯片损坏、数据丢失或系统崩溃,使用ESD保护器件可以有效减小这些风险。

2.通信设备保护:ESD保护器件可以应用于通信设备中的接口和接口电路,如USB、HDMI、以太网和UART等。

这些接口通常需要与外部设备进行连接,而外部设备中的静电放电可能会对接口电路造成损坏,使用ESD保护器件可以防止这种损坏。

3.功率电子保护:ESD保护器件还可以应用于功率电子设备和电路中。

例如电源适配器、电池管理系统和电机驱动器等。

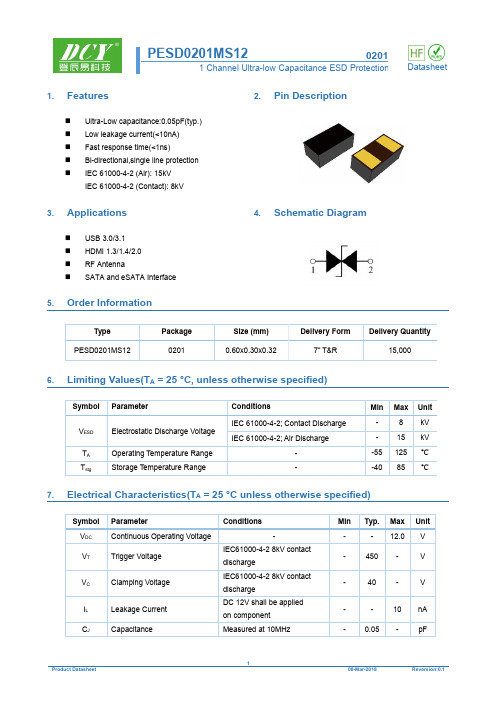

PESD0201MS12超低电容高分子ESD静电保护二极管TVS厂家DCY品牌推荐

1.Features2.Pin Description⏹Ultra-Low capacitance:0.05pF(typ.)⏹Low leakage current(<10nA)⏹Fast response time(<1ns)⏹Bi-directional,single line protection⏹IEC61000-4-2(Air):15kVIEC61000-4-2(Contact):8kV3.Applications4.Schematic Diagram⏹USB3.0/3.1⏹HDMI1.3/1.4/2.0⏹RF Antenna⏹SATA and eSATA Interface5.Order InformationType Package Size(mm)Delivery Form Delivery Quantity PESD0201MS1202010.60x0.30x0.327”T&R15,0006.Limiting Values(T A=25°C,unless otherwise specified)Symbol Parameter Conditions Min Max UnitV ESD Electrostatic Discharge Voltage IEC61000-4-2;Contact Discharge-8kV IEC61000-4-2;Air Discharge-15kVT A Operating Temperature Range--55125℃T stg Storage Temperature Range--4085℃7.Electrical Characteristics(T A=25°C unless otherwise specified)Symbol Parameter Conditions Min Typ.Max Unit V DC Continuous Operating Voltage---12.0VV T Trigger Voltage IEC61000-4-28kV contactdischarge-450-VV C Clamping Voltage IEC61000-4-28kV contactdischarge-40-VI L Leakage Current DC12V shall be appliedon component--10nAC J Capacitance Measured at10MHz-0.05-pF8.Typical CharacteristicsFig.1Typical ESD Response(IEC 61000-4-2,8kV contact discharge )Fig.2Typical Device Capacitance VS.FrequencyFig.3HDMI 1.4Mask at 3.4Gbps Fig.4USB 3.0Mask at 5.0GbpsFig.5HDMI 2.0Mask at 6.0GbpsTime (ns)9.ESD Protection for Signal LineThe PESD is designed for the protection of one bidirectional data line from ESD damage.⏹Place the PESD as close to the input terminal or connector as possible.⏹Minimize the path length between the PESD and the protected signal line.⏹Use ground planes whenever possible.PESD0201MS1210.Package DimensionL2Recommended Solder Pad Footprint*Sizes in mmNotes :This solder pad layout is for reference purposes only.11.Soldering ParametersFIG.5: Reflow conditionT e m p e r a t u r eT T TReflow ConditionPb-Free AssemblyPre-heat-Temperature Min (T s(min))+150°C -Temperature Max(T s(max))+200°C -Time (Min to Max)(ts)60-180secs.Average ramp up rate (Liquid us Temp (T L )to peak)3°C/sec.Max T s(max)to T L -Ramp-up Rate 3°C/sec.Max Reflow-Temperature(T L )(Liquid us)+217°C -Temperature(t L )60-150secs.Peak Temp (T p )+260(+0/-5)°C Time within 5°C of actual Peak Temp (t p )30secs.Max Ramp-down Rate6°C/sec.Max xTime 25°C to Peak Temp (T P )8min.Max Do not exceed+260°C。

超小型贴片元件(0201)的装配及工艺特征

超小型贴片元件(0201)的装配及工艺特征2004年第12期福建电脑33超小型贴片元件(o2o~)的装配及工艺特征冯俊牟志平陈杰(安徽建筑工业学院计算机与信息工程系,安徽合肥,230022)【摘要】本文主要介绍基于SMT表面贴装技术的超小型贴片元件(D20j)X-艺,包括它的工艺特征分析,应用难点及其技术工艺的推动方案,并以SMT工艺制作了编码控制接I:/.【关键词】SMT表面贴装技术,超小型贴片元件,模板印刷,回流焊接1引言自上个世纪五十年代发明印刷电路板(PCB,printedcircuitt~rd)后,人们对电子产品的小型化提出更新更高的要求,电子元件,PCB及其装配设备技术就始终在朝着SMT的方向发展.SMT的普遍应用发生在八十年代初期,1206(3216)电阻与电容是最流行的贴装元件.一两年之后,0805(2125)就替代了1206成为SMT贴装的最普遍的元件包装.在此期间,机器与元件都得到迅速发展.在机器变得更快更灵活的同时,0603(1608)元件,0402(1608)包装的相继出现,给PCB装配的各方面都提出了更高的要求.为了使机器能更准确地送出零件,装配设备技术发展的重点是元件的送料器(feed日).此外锡膏(solderpaste)印刷也变得更加关键一模板(stencil)厚度与锡膏网孔成为越来越重要的工艺考虑因素.这些影响因素使得0402包装几乎用了五年时间才在工业中被广泛应用.现在更小的0201包装已经开始普及.由于尺寸,重量和功率消耗的需求,许多电路板需要将更小的元件和技术结合到其产品中去,因此0201贴装得到了快速发展.可以想象高精度的0201工艺在应用中必然有很多难点,而分析这些难点,找出0201的工艺特征也就是本论文的主要目的.20201的准确贴装2.1主要的困难0201的使用带来了更高的元件密度,也使得贴装作业的难度增大了一个数量级.0201元件要求采用较小的焊盘尺寸来防止焊锡污迹,接纳无焊脚焊接.对于密度高的PCB,贴装精度直接影响回流焊接后的装配缺陷数量,例如,贴装偏移会增加锡桥,锡珠,元件竖立和元件对不准焊盘的几率.根据资料显示,对于标准焊盘,y<0.075mm,x<0.075mm的贴装偏移基本上对缺陷没有影响.可是,当偏移增加到<0. 1mm时,缺陷水平就会上升到超过5000ppm.此外,贴装操作涉及的不止其本身,它还包括吸取的可靠性,元件视觉识别系统的准确性和贴装的可重复性.还有一个很关键的问题是焊盘的设计,在这我们推荐一种行之有效的方法,见表一.表一0201焊盘设计推荐0201焊盘尺寸下限上限过程效果长度尺寸0.010"0.012"改进"墓碑"宽度尺寸0.016"0.018"焊盘间隔()0.020"0.022"改进焊锡结珠焊盘间隔()0.008"0.010"由于吸嘴的轴向运动会产生一个水平的力,将会造成元件的偏移,有可能增加高密度贴装的锡桥.因为当使用无焊脚焊盘时,元件会将锡膏从零件下挤出.因此,可以将超程定义为使得元件和PCB之间的间隙小于焊锡颗粒大小,也就是说,贴装系统必须将该间隙控制在40—60urn.另一个起作用的因素是板的支撑,没有支撑元件可能从过高的高度落下或被压人锡注:拳文受蓟【安擞建筑工业学院]贵助(项目缟号:2002yq006)膏中.为了准确地控制行程,板的支撑系统必须为板的拱形提供足够的纠正.下面所说的吸取位置公差就是描述吸嘴行程的参数.2.2吸取位置公差因为传统贴装设备在Y轴上没有控制,所以使得公差难以控制,从而连贯性难以保证.为了保持生产系统的连贯性,吸嘴必须能够在三个方向上移动,即沿x,Y和z轴移动.同时, 既保证将元件对中吸嘴,又必须确保贴装精度在公差范围之内.显然,这对于0201来说,其公差精度要求与其他零件相比更高.有研究表明,如果要确保0201贴装成功,有必要将吸嘴Y方向的精度控制在±0.07mm以内,X方向的精度在±0.1mm 以内,z方向的精度在±0.1mm内;为了补偿z轴,贴装设备必须具有增设实时的反馈检测机构装置,测量每个元件的厚度, 从而达到0.1mm的目标值.但从实际来看,在保证贴片机精度的前提下,还有一些其它问题需要解决.2.3元件在锡膏上的运动0201贴装的另一个重要问题是在某些情况下,0201元件由于焊接过程中锡膏融化所产生的表面张力不均而无法停留在其原本贴装的位置,也就是说,即使贴片机做到了万无一失, 0201元件最终在PCB板上的位置仍然有可能不准确.根据试验表明,对于Y方向3d的贴装精度,板上小于0.05mm超程的元件有时将会向短边方向滑行超过60uln.并且还发现当0201元件只是贴装在助焊剂上时,元件没有发生因超程产生的滑移,但是在锡膏上就会发生.经仔细对比试验数据后,发现当锡膏颗粒大小大于20um 时,元件就会或多或少的出现偏移,这是因为颗粒在焊盘上分布不均.由于元件贴装时间仅仅是几毫秒,所以任何不平的表面都可能造成零件偏斜或运动.这也是热风焊锡均涂(HAs1.)板不适用于0201贴装的原因.显然:锡膏的颗粒直径也是影响贴装的精度的关键之一.3问题的关键使0201获得准确贴装,主要由以下几个关键因素决定:(1)元件送料器工作台送料器(foder)I作台必须精密加工,保证单个送料器可重复定位,并且采用双轨线性移动导轨与高分辨率半封闭循环伺服系统相结合.这样,只需作微小的调节就可保证元件尽可能地靠近中心吸取.(2)元件送料器元件送料器不论元件高度和元件位置可能出现的大量变化,都必须保证吸取位置维持可重复性.用于送料器的定位机构必须精确耐用.应选用强度高,重量轻的材料,以允许人机工程上的操作,以保证元件料带(ca一日tape)的精密,可重复的送出.(3)送料器驱动链轮驱动链轮轮齿的形状,锥度和长度会极大地影响到送料器定位料带的能力.(下转第36页)福建电脑2004年第12期()函数.(2)为注册的iptables_match变量赋初值.(3)实现ink()函数..ink()调用register.match()注册赋值后的iptables_match.当Iptables命令中第一次使用该Match时, Iptables主程序会自动加载该Match的动态链接库,并执行其中的一init().编写完一个Match的核外部分后,需要以下步骤把它与Iptables集成在一起:(1)把源程序文件放入Iptables根目录下的extensions子目录.(2)编辑extensions目录的Makefile文件,在PFExT'SLIB宏中加上该Match的名字.(3)执行make和makeinstall命令,进行编译和安装.设计Match的核外部分,取名为SnortIptables.在其parse()函数中,依据用户指定的接收端口号,启动一个守护进程,该进程接收远程Snort发来的响应命令,调用API函数system()设置本地的过滤规则.函数ink(),hdp(),finaLcheck(),print()和save()与联动的实现没有直接的关系,就不再详细介绍了.对数据结构iptables-match的赋值如下所示:staticstructiptables~nmtchSnortlpt~les={NULL..SnortIptables.IIrrABLES- VERSION.tPT.ALIGN(slzeoffstructiptSnortIptable~info)),ItrF_ALIGN(sizeoffstructiptSnortIptable~irdo)).&help.&ink.&parse.&fin&check.&print.&save.opt s}4.4安全性NeffilterAptables和Snort的联动能够互补对方的不足,提高网络的整体安全防御能力.Snort检测到入侵活动后,向[HTH]参考文献[I]MartyRoezch.Snort源代码[EB/OL].http..//..NetfilterAptables发送信息设置过滤规则,切断入侵的渠道.这样不但实现动态防火墙的功能,而且能够抵御基于协议和服务的攻击,同时,Snort也具备响应非面向连接的入侵.另外,Snort通过设置Netfilter/ipmbles的过滤规则,减少流人其所在子网的网络流量,以对抗拒绝服务攻击.虽然这样会限制网络流量,但是考虑到入侵检测系统是失效即开放(l_Open)的设备,从安全角度来看,这种限制措施是值得的.防火墙和入侵检测系统的联动,会给黑客提供进行拒绝服务攻击的机会.黑客通过构造源地址是合法用户IP地址的攻击包,使联动功能在防火墙中设置过滤掉来自合法用户数据包的规则.另外,大量的无用规则也会使防火墙的性能下降.在版本2.2以后的Linux内核中有一种防止IP欺骗的很有效的内核技术叫作源地址验证(SauceAddressV eilfication).这项功能被开启以后,内核依据事先设置好的路由表,检测所有流入系统的报文的源地址,来查看这些报文是否与其源网络接口匹配,那些与源地址不匹配的报文将被丢弃.文献[4]中提供了开启源地址验证功能的Shell代码.5结束语安全产品之间的联动可以实现优势互补,提高系统的整体安全防御能力.本文基于联动的思想,给出了Linux平台下防火墙Netfilter以ptables和网络入侵检测系统Snort联动的实现方案,解决了单独使用防火墙或入侵检测系统出现的一些安全问题,提高了网络系统的安全性.但是,针对联动的拒绝服务攻击的隐患仍然会不同程度的存在.同时,由于联动设置的过滤规则是临时性的,所以,定时删除过滤规则可以避免防火墙性能的下降.[2】张悦连.Snort规则及规则处理模块分析[J】.河北科技大学,2003,第24卷(第4期):44—47.[3]赵之茵.Snort入侵检测系统规则描述语言的分析[J].吉林工学院(自然科学版),2002,第23卷(第3期):04一O8.[4]张翔.开放源代码入侵检测系统一一Snort的研究[J].计算机应用,2002,第22卷(第ll期):96—97.[5]丁志芳.Snort规则的分析[J].三峡大学(自然科学版),2002,第24卷(第5期):419—422.【6JRustyRu.~filter-hacking—HOWTO[FA3/OL].filter.og/dct'urnenmtion{【)/netfilter—hacking—HOWTO.html【7JRustyRussel1.iptablez1.2.9源代码lEB/OL1.http://www.iptables.啪.[8]曾汉平.Linux防火墙技术研究[J].武汉理工大学(交通科学与工程版),2002,第26卷(第1期):120—122.[9]张惠卿.在Linux下用iptables构建防火墙[J].中国数据通信,2002,第8期:55—58. [10】ToxenB.Lin安全:入侵防范,检测和恢复[M].北京:机械工业出版社,2002,93—94.(上接第33页)(4)吸取头真空吸嘴(nozzle)应能适应在吸取贴装元件期间因机械运动引起的冲击,以补偿锡膏高度上的微小变化,减少元件破裂的危险.吸嘴必须能够在其夹具内自由移动.因此.在选择吸嘴材料时,必须考虑材料的硬度,加工公差和热特性等,以保证精度.(5)吸嘴设计对于0201元件而言,吸嘴设计不同与其它元件.因为0201元件的体积非常小,如要吸取0.6xO.3inln的元件.吸嘴外径就不能大于0.40mm.所以要求吸嘴的设计应尽量加大真空的接触表面积,同时还应有一个不会干涉高密度布局的外形.为保证精度以维持吸取的高可靠性,0201元件的吸嘴轴由直线型设计改为锥型,增加了吸嘴强度,并使吸嘴具一定的抗弯能力.另外,吸嘴还必须高度耐磨,耐腐.因为元件表面的有机物对吸嘴的腐蚀作用会由于小的接触面积而更加严重.吸参考文献【1]ScottWischoffer.02O1装配.从难关到常规装配2002【2]BrianJ.LewisandPaulHouston.02O1技术推动工艺解决方案2003.6【3】l~mlalF.Baldwin,PaulHouston.高效率的02Ol工艺特征2003.9【4JDaveKalen.如何准确地贴装02O1元件1999.4【5]夏建丰回流焊温度分布曲线图电子工艺技术[6】约翰.希罗.约翰.马尔波尤夫怎样设定锡膏回漉测试曲线cIPC嘴设计的改进也可为提高贴装精度提供部分的解决方法. (6)吸嘴轴(nozzleshaft)装配过压(overdrive)也会造成定位精度变化.过压是由于贴装头上下运动的惯性造成的,如果吸嘴和吸嘴轴不在一条直线上,就会产生抖动(wl)现象.即过压.它取决于运动速度,吸嘴重量和元件重量,可以通过吸嘴与吸嘴轴装配直接对中,来消除过压现象.直接对中能减少与元件吸取和贴装有关的负面因素的数量.4结论对于0201元件贴装,目前的贴装工艺区域在3时X*Y大约为75*75tan.当达到6的贴装可靠性时,X*Y必须减少到50*50tan.最新的高速贴装设备已达66*66tan,实际标准偏差大约为35--45tan.随着0201元件得到更加广泛地使用和制造工艺精度提高,其贴装的准确性将会进一步提高.。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

0201封装的超小型ESD保护器件

上海英联电子科技有限公司徐宁杨永华一、前言

ESD被认为是电子产品质量最大的潜在杀手,影响产品的可靠性,静电防护也就成为电子产品质量控制的一项重要内容。

最有效的ESD保护方法是设备的连接器或端口处放置外部保护元件。

0201尺寸的硅基ESD器件比上一代0402型的器件大约缩小了70%,能够为手机、MP3播放器、PDA和数码相机等便携式电子产品提供保护和提高其可靠性。

上海英联电子推出的UM5051/5052是一款低容值(12pF)的ESD保护器件,实际大小仅为0.6mm x 0.3mm x 0.3mm,为设计师们在空间受限的应用中提供了灵活性。

双向保护消除了在PCB板上安装时的方向限制,而且也不会损失负电平信号。

二、UM5051/5052的重要参数

英联的UM5051、UM5052具有低漏电流、低容值、低钳位电压等特点,DFN的封装可以有效的降低抛料率,降低成本,增加贴片效率。

0201的超小封装,其ESD抗冲击性能达到了IEC 61000-4-2 (ESD) ±30kV (空气)和±25kV(接触)的标准。

主要参数如表1所示:

表1 特性参数表

为方便理解参数,图1为单向ESD保护管的特性曲线图。

图 1 单向ESD保护管特性曲线图图 2 ESD放电波形图

1、击穿电压V BR (Reverse Breakdown Voltage): 在指定测试电流下ESD保护管发生雪崩击穿时的电压,它是ESD保护管最小的击穿电压。

为了满足IEC61000-4-2标准,ESD保护管必须达到可以处理最小8kV(接触)和15kV(空气)的冲击,有的半导体生产厂商在自己的产品上使用了更高的抗冲击标准。

上海英联电子的UM5051、UM5052,达到了IEC 61000-4-2 (ESD) ±30kV (空气)和±25kV(接触)的标准。

2、反向关断电压V RWM(Reverse Peak Working Voltage)和反向漏电流I D(Reverse Leakage Current):指 ESD保护管最大连续工作的直流或脉冲电压。

UM5051/UM5052的V RWM值为5V,可以保护工作电压为5V的芯片。

其反向漏电流小于1μA,对产品的功耗几乎没有影响。

峰值电压为V C。

图 3 ESD钳位电压波形图

时,C必须<10pF。

不同速率传输信号的容值选取请参照下图。

图 4 ESD保护器件容值选取参考图护方案选择。

图5为实物图和封装图。

图 5 0201实物图和封装图

Clamp Voltage @ Ipp=5A

Surge Current

Clamp Voltage

11.5V

1、单向保护

下图为单向保护示意图,当干扰脉冲信号超过V RWM时,超过的部分被释放掉。

V

接口IC

V RWM

图 6 单向保护示意图

单向ESD保护管UM5051的反向端接被保护的线路,正向端接地。

释放掉反向端输入的超过V RWM的ESD脉冲,使得脉冲高压不能进入到IC,从而起到保护IC的作用。

2、双向保护

双向ESD保护管一端接要保护的线路,一端接地,无论来自反向还是来自正向的脉冲均被释放,更有效地保护了IC。

下图为双向ESD保护器件UM5052的双向保护示意图。

V

V RWM

-V RWM

图7 双向保护示意图

四、ESD应用举例

1、手机SIM卡线路保护

2、便携产品音频数据线路保护

便携类产品以体积小备受消费者喜爱,在音频数据线路保护方面,英联推出的UM5052单路双向ESD保护管,0201的超小封装为设计师在有限的布板空间中提供了灵活性。

由于音频信号传输速率比较低,因此对器件电容的要求不太高,100pF左右都是可以接受的。