CAT28F010TR-70T中文资料

AM28F010资料

s Write and erase voltage 12.0 V ±5% s Latch-up protected to 100 mA

from –1 V to VCC +1 V

s Flasherase™ Electrical Bulk Chip-Erase — One second typical chip-erase

AMD’s Flash technology combines years of EPROM and EEPROM experience to produce the highest levels of quality, reliability, and cost effectiveness. The Am28F010 electrically erases all bits simultaneously using Fowler-Nordheim tunneling. The bytes are programmed one byte at a time using the EPROM programming mechanism of hot electron injection.

AMD’s Flash technology reliably stores memory contents even after 10,000 erase and program cycles. The AMD cell is designed to optimize the erase and programming mechanisms. In addition, the combination of advanced tunnel oxide processing and low internal electric fields for erase and programming operations produces reliable cycling. The Am28F010 uses a 12.0 V ± 5% VPP high voltage input to perform the Flasherase and Flashrite algorithms.

CNY70中文资料

Dimensions of CNY70 in mm95 11345www.vishay.Document Number 83751Ozone Depleting Substances Policy StatementIt is the policy of Vishay Semiconductor GmbH to1.Meet all present and future national and international statutory requirements.2.Regularly and continuously improve the performance of our products, processes, distribution and operatingsystems with respect to their impact on the health and safety of our employees and the public, as well as their impact on the environment.It is particular concern to control or eliminate releases of those substances into the atmosphere which are known as ozone depleting substances (ODSs).The Montreal Protocol (1987) and its London Amendments (1990) intend to severely restrict the use of ODSs and forbid their use within the next ten years. Various national and international initiatives are pressing for an earlier ban on these substances.Vishay Semiconductor GmbH has been able to use its policy of continuous improvements to eliminate the use of ODSs listed in the following documents.1.Annex A, B and list of transitional substances of the Montreal Protocol and the London Amendments respectively2.Class I and II ozone depleting substances in the Clean Air Act Amendments of 1990 by the EnvironmentalProtection Agency (EPA) in the USA3.Council Decision 88/540/EEC and 91/690/EEC Annex A, B and C (transitional substances) respectively. Vishay Semiconductor GmbH can certify that our semiconductors are not manufactured with ozone depleting substances and do not contain such substances.We reserve the right to make changes to improve technical design and may do so without further notice. Parameters can vary in different applications. All operating parameters must be validated for each customer application by the customer. Should the buyer use Vishay Telefunken products for any unintended or unauthorized application, the buyer shall indemnify Vishay Telefunken against all claims, costs, damages, and expenses, arising out of, directly or indirectly, any claim of personal damage, injury or death associated with such unintended or unauthorized use.Vishay Semiconductor GmbH, P.O.B. 3535, D-74025 Heilbronn, GermanyTelephone: 49 (0)7131 67 2831, Fax number: 49 (0)7131 67 2423Document Number 83751。

AT281x 说明书 RevC0

2

AT2818/2816A/2816B/2817A/2817/810A 用户手册

安全须知 警告

危险:当你发现有以下不正常情形发生,请立即终止操作并断开电源线。立刻与安柏科技销售部联

仪器操作异常。 操作中仪器产生反常噪音、异味、烟或闪光。 操作过程中,仪器产生高温或电击。 电源线、电源开关或电源插座损坏。 杂质或液体流入仪器。

®

标志和文字是常州安柏精密仪器有限公司的商标或注册商标。

有限担保和责任范围

常州安柏精密仪器有限公司(以下简称 Applent)保证您购买的每一台 AT2818/2816A/2816B/2817A/2817/810A 在质量和 计量上都是完全合格的。此项保证不包括保险丝以及因疏忽、误用、污染、意外或非正常状况使用造成的损坏。本项保证仅 适用于原购买者,并且不可转让。 自发货之日起,Applent 提供玖拾(90)天保换和贰年免费保修,此保证也包括 VFD 或 LCD。玖拾天保换期内由于使 用者操作不当引起的损坏,保换条款终止。贰年包修期内由于使用者操作不当而引起仪器损坏,维修费用由用户承担。贰年 后直到仪表终生,Applent 将以收费方式提供维修。对于 VFD 或 LCD 的更换,其费用以当前成本价格收取。 如发现产品损坏,请和 Applent 取得联系以取得同意退回或更换的信息。之后请将此产品送销售商进行退换。请务必说 明产品损坏原因,并且预付邮资和到目的地的保险费。对保修期内产品的维修或更换,Applent 将负责回邮的运输费用。对 非保修产品的修理,Applent 将针对维修费用进行估价,在取得您的同意的前提下才进行维修,由维修所产生的一切费用将 由用户承担,包括回邮的运输费用。 本项保证是 Applent 提供唯一保证,也是对您唯一的补偿,除此之外没有任何明示或暗示的保证(包括保证某一特殊目 的的适应性) ,亦明确否认所有其他的保证。Applent 或其他代理商并没有任何口头或书面的表示,用以建立一项保证或以任 何方式扩大本保证的范围。凡因对在规格范围外的任何原因而引起的特别、间接、附带或继起的损坏、损失(包括资料的损 失) ,Applent 将一概不予负责。如果其中某条款与当地法规相抵触或由于某些司法不允许暗示性保证的排除或限制,以当地 法规为主,因此该条款可能不适用于您。但该条款的裁定不影响其他条款的有效性和可执行性。 中华人民共和国 江苏省 常州安柏精密仪器有限公司 二〇〇九年十月 Rev.A3

RMC70系列一-和两轴运动控制器说明书

The RMC70 Base module includes CPU, communications, and one or two motion axes. Up to four Expansion modules can be added (e.g. analog inputs and DI/O).FeaturesCommand-based—minimal program development and The din-rail mountable RMC75Base module is just 3.22” x 5.00”Motion Control…and More.p.2Printed in USA 6/11EXP70-AP2RMC70 Series Ordering InformationRMC70 Base ModuleCPU ModuleR MC75E = RMC75 with Ethernet communications and USB monitor port ................................ p. 6 RMC75P = RMC75 with PROFIBUS-DP communications and RS-232 monitor port .................... p. 6 RMC75S = RMC75 with serial RS-232/485 communications and RS-232 monitor port ............. p .7Axis ModuleAA1 = Analog input (±10 V or 4-20 mA), ±10 V analog control output, 1 axis ............................ p .9 AA2 = Analog input (±10 V or 4-20 mA), ±10 V analog control output, 2 axes ........................... p .9 MA1 = Magnetostrictive (Start/Stop, PWM) or SSI input, ±10 V analog control output, 1 axis .. p .10 MA2 = Magnetostrictive (Start/Stop, PWM) or SSI input, ±10 V analog control output, 2 axes . p .10 QA1 = Quadrature encoder input (5 V differential), ±10 V analog control output, 1 axis .......... p .11 QA2 = Quadrature encoder input (5 V differential), ±10 V analog control output, 2 axes ......... p .11RMC70 Expansion ModulesExpansion ModuleA2 = 2 analog reference inputs (±10 V or 4-20 mA) ............................................................. p .13 AP2 = 2 analog inputs (±10 V or 4-20 mA) for position-pressure and position-force control.... p .13 D8 = 8 discrete I/O, 12-24 VDC, software configurable ....................................................... p .14 Q1 = ½–axis quadrature reference input (5 V differential) .................................................. p .15Mounting Dimensions ........................................... p . 18Voltage-to-Current Converters................................. p . 19 Cable Assemblies .................................................. p . 19 Terminal Blocks ..................................................... p . 19RMC75E-MA2Ethernet communications with 2 axes ofmagnetostrictive (Start/Stop or PWM) or SSI feedback. RMC75P-QA1PROFIBUS communications with 1 axis of quadrature encoder feedback. EXP70-D8 8 discrete I/OCompany ProfileDelta Computer Systems, Inc. manufactures motion controllers, color sensors, and other industrial controls providing high-performance automation solutions to a wide range of industries.RMC75E-MA1RMCTools Features Motion Control…and More. p.3Printed in USA 6/11RMC70 Control FeaturesThe RMC70 provides an extensive set of motion commands and programming capability for quick and easy yet flexible motion control for virtually every motion application.SClosed Loop ControlFull PID loop control with velocity, acceleration and jerk feed forwards for precise synchronized motion. Directional gain factors support fluid power control. SPosition ControlSPoint-to-Point moves S S-curvesS Speed at Position S GearingS Cyclic Sinusoidal Motion S Splines S CamsS Move VelocityS Rotary motion with support for incremental andabsolute SVelocity ControlSVelocity control with position feedback S Velocity control with velocity feedback SPressure and Force ControlSLinear or S-curve Ramps S GearingS Cyclic Sinusoidal Profile S Splines S Cams SForce ControlLoad cell or differential force.SPosition-Pressure and Position-Force Control STransition seamlessly between position control and pressure or force control.S Pressure or Force Limit – limit the pressure orforce during a position or velocity move. SActive DampingFor high-performance control of pneumatics and difficult systems.SOpen Loop ControlSeamless transition from open loop to closed loop and vice versa. Ramp the Control Output smoothly between two values, or ramp the Control Output down as the position approaches the final position, for hard-to-control systems.SQuick MoveMove in open loop and stop in closed loop for fast, smooth motion with accurate stops.SUser ProgramsPrograms are easy-to-understand sequences of commands. Run multiple programs simultaneously to handle axis commands and machine control functions.SPreScan TableCyclic task for immediate response to internal conditions or external events, such as discrete inputs, error conditions, etc.SVariablesRecipes and other user parameters can be stored for use by user programs.SMathematical ExpressionsExpressions provide flexible programming capability for advanced calculations and machine control sequences.SPlotsPlot any register in the RMC70, up to 16 registers per plot, sampled down to the control loop resolution. Event LogSpeeds troubleshooting by recording events such as parameter changes, commands, errors, and communications.SClosed Loop stopsRamp speed to zero at specified rate and hold position.SOpen Loop stopsRamp output voltage to zero at specified rate. SMulti-axis (group) stopsA fault on one axis halts multiple axes when configured as a group.SAutoStopsThe response of axes to each fault type is easily configurable.RMC75E CPU ModuleRMC75P CPU ModuleRMC75S CPU Module Motion Control…and More. p.5| Delta Computer Systems, Inc. | Battle Ground, WA USA 98604 | Tel: 360.254.8688 | Fax: 360.254.5435 | |p.6Motion Control…and More.p.7| Delta Computer Systems, Inc. | Battle Ground, WA USA 98604 | Tel: 360.254.8688 | Fax: 360.254.5435 | |p.8MA1 Axis ModuleAA2 Axis ModuleQA1 Axis ModuleMotion Control…and More.p.9| Delta Computer Systems, Inc. | Battle Ground, WA USA 98604 | Tel: 360.254.8688 | Fax: 360.254.5435 | |p.10Motion Control…and More.p.11| Delta Computer Systems, Inc. | Battle Ground, WA USA 98604 | Tel: 360.254.8688 | Fax: 360.254.5435 | |p.12Up to four Expansion modules (Exp70) can be added to an RMC70 motion controller to bring additional capabilities to the controller. Thetransducers.The A2 generates a 10 VDC exciter output, which eliminates a precision power source in some potentiometer applications. This low noise reference also provides the accuracyfollowing characteristics:S Voltage: r10 VS Current: 4-20 mAEach 16-bit input of the AP2 can be Motion Control…and More. p.13| Delta Computer Systems, Inc. | Battle Ground, WA USA 98604 | Tel: 360.254.8688 | Fax: 360.254.5435 | |p.14output common, all inputs must be the same polarity, and all outputs must be the same polarity, but inputs need not be the samepolarity as outputs. That is, outputs can switch high side or low side, and the inputs can be operated with either polarity signals.allows up to 64 slave axes to be electronically geared to one master quadrature signal. Motion Control…and More. p.15Printed in USA 6/11RMC70 Series WiringN ote: For detailed wiring diagrams, see the RMC70 Startup Guide or the RMCTools help.Ethernet (RJ-45)Twisted pair cable CAT5, CAT5e or CAT6, UTP or STP conforming to IEEE 802.3 for 100BASE-T must be used.Power Terminal BlockPin Label Function1 +24Vdc PS +24 VDC power2 PS Return Isolated power common3 Case Chassis groundMonitor Port (USB “B” Connector)Accepts a standard USB cable to communicate with a PC running RMCTools.PROFIBUS-DPStandard PROFIBUS-DP cabling must be used.Power Terminal BlockPin LabelFunction1 +24Vdc PS +24 VDC power2 PS Return Isolated power common3 CaseChassis groundMonitor PortAccepts a null-modem DB-9 female-to-female cable tocommunicate with a PC running RMCTools.RS-232 (DB-9)Pin Function2 Received data3 Transmitted data 5 Serial common 7 Request to Send (RTS) 8 Clear to Send (CTS)RS-485 Terminal BlockPin Label Function1 + T/R Tx/ Rx B (+)2 Trm Jpr Jumper to +T/R for termination3 - T/R Tx/ Rx A (-)4 SCmn Isolated serial common5 Bias Jumper Jumper to SCmn for bias6 CaseChassis groundPower (shared connector with RS-485)Pin Label Function 6 Case Chassis ground 7 +24Vdc PS +24 VDC power 8 PS Return Isolated power commonMonitor PortAccepts a null-modem DB-9 female-to-female cable tocommunicate with a PC running RMCTools.One connector per axis:Pin Label Function 1 + Fault InFault Input (12-24 VDC)2 - Fault In3 + Enable OutEnable Output (12-24 VDC)4 - Enable Out5 Control OutControl Output (±10 V)6 Common MDT SSI7 + Int/Clock + Interrogate + Clock8 - Int/Clock - Interrogate - Clock9 Common Common Common 10 + Ret/Data + Return + Data 11 - Ret/Data - Return - Data 12 Case Chassis groundNote: Pins 6 and 9 are electrically the same.One connector per axis:PinLabelFunction1 + Fault InFault Input (12-24 VDC)2 - Fault In3 + Enable OutEnable Output (12-24 VDC)4 - Enable Out5 Control OutControl Output (±10 V)6 Common7 + Anlg InAnalog input(For 4-20 mA, jumper pins 7 and 8)8 Jmpr for 4- 20mA9 - Anlg In 10 Common Analog common11+ 10Vdc Exciter Exciter output for use withpotentiometers12 Case Chassis ground Note: Pins 6 and 10 are electrically the same.Wiring continuedN ote: For detailed wiring diagrams, see the RMC70 Startup Guide or the RMCTools help.One connector per axis:PinLabelFunction1 A- A- from encoder (5 V signal)2 A+ A+ from encoder (5 V signal)3 B- B- from encoder (5 V signal)4 B+ B+ from encoder (5 V signal) 5 n/c No connection6 RegY/NegLim- Registration Y orNegative Limit (12-24 VDC) 7 RegY/NegLim+8 RegX/PosLim- Registration X orPositive Limit (12-24 VDC) 9 RegX/PosLim+10 n/c No connection 11 n/c No connection 12 Control OutControl Output (±10 V)13 Common 14 Z- Index pulse from encoder(5 V signals) 15 Z+16 Cmn Common17 n/c No connection 18 Home-Home Input (12-24 VDC)19 Home+ 20 - Fault InFault Input (12-24 VDC)21 + Fault In 22 n/c No connection 23 n/c No connection 24 - Enable OutEnable Output25 + Enable OutNote: Pins 13 and 16 are electrically the same.Pin LabelFunction110V Exciter+Exciter output for use with potentiometers2 Anlg Cmn Isolated analog common3 Input 0+ Analog input 0 (For 4-20mA, jumper pins 3and 4) 4 Jumper for 4-20mA5 Input 0-6 Anlg Cmn Isolated analog common7 Input 1+ Analog input 1 (For 4-20mA, jumper pins 7and 8) 8 Jumper for 4-20mA 9 Input 1-10 Case Chassis GroundNote: Pins 2 and 6 are electrically the same.Pin LabelFunction1 Input 0+Analog input 0(For 4-20 mA, jumper pins 1 and 2)2Jumper for4-20mA3 Input 0-4 Anlg Cmn Isolated analog common5 Input 1+Analog input 1(For 4-20 mA, jumper pins 5 and 6)6Jumper for4-20mA7 Input 1- 8 Case Chassis groundPinLabelFunction1 Output Cmn Common to one side of all outputs2 I/O 0 Input or output 03 I/O 1 Input or output 14 I/O 2 Input or output 25 I/O 3 Input or output 36 I/O 4 Input or output 47 I/O 5 Input or output 58 I/O 6 Input or output 69 I/O 7Input or output 710Input CmnCommon to one side of all inputsPin Label Function 1 Reg In+ High-speed registration orhome input 2 Reg In-3 A+Encoder A Input(to enable termination,jumper pins 3 and 4*)4 Jumper forTermination*5 A-6 Cmn Common7 B+Encoder B Input(to enable termination,jumper pins 7 and 8*)8 Jumper forTermination*9 B- 10 Case Chassis ground * Use either both jumpers or no jumpers.Printed in USA 6/11Drawings are not at 1:1 scale.RMC70 Series DimensionsAccessoriesDelta's voltage-to-current converters are designed for converting a voltage drive output to a current drive output in order to control a servo valve. Delta offers several voltage-to-current converters to fit your needs. The maximum output current is adjustable in increments of 10 mA up to the maximum output current range.PartNumber Description Output Current Range*PowerSupplyVC21242-channel voltage-to-current converter ±100 mA per channel 24 VDCVC2100 2-channel voltage-to-current converter ±100 mA per channel ±15 VDCVC2100-HS 2-channel voltage-to-current converter –high speed**±100 mA per channel ±15 VDCVC2124 VC2100 VC2100-HS* Channels can be connected in parallel to provide higher current. For example, two ±100 mA channels connected in parallel will provide ±200 mA.** M ost hydraulic control applications do not require the high-speed converter.Delta 's provides cable assemblies for certain products. The table below lists the available cables:Cable Part No Cable DescriptionRMC-CB-QUAD-01-06 6 ft long, for QA module. 1 DB25 to 3 individual pig-tailed cablesfor drive, encoder, and limits.RMC-CB-QUAD-01-10 10 ft long, for QA module. 1 DB25 to 3 individual pig-tailed cablesfor drive, encoder, and limits.RMC-CB-QUAD-01-15 15 ft long, for QA module. 1 DB25 to 3 individual pig-tailed cablesfor drive, encoder, and limits.RMC-CB-QUAD-01-20 20 ft long, for QA module. 1 DB25 to 3 individual pig-tailed cablesfor drive, encoder, and limits.Custom lengths are available per request. A drawing of RMC-CB-QUAD-01-xx is available on the Downloads page of Delta’s website at /dloads.All RMCs ship with connectors. Connectors are also available for order individually from Delta. The table below lists the available connectors. These parts are also available from connector manufacturers Amphenol Pcd or WECO using thesepart numbers.Connector Part NoConnector Description For ModulesELFT03260E RMC70 3-pin Terminal Block RMC75E, RMC75PELFT08260 RMC70 8-pin Terminal Block RMC75S, AP2ELFT10260 RMC70 10-pin Terminal Block A2, D8ELFT12260 RMC70 12-pin Terminal Block AA, MA p.19| Delta Computer Systems, Inc. | Battle Ground, WA USA 98604 | Tel: 360.254.8688 | Fax: 360.254.5435 | |Printed in USA 6/11。

伊林思H820 系列3G 4G 路由器规格说明书

H820系列3G/4G路由器规格说明书产品概述H820系列路由器是伊林思科技有限公司基于无线网络需求,采用最新硬件系统平台,使用Linux软件系统引用最新技术研发出来的一款全新的,性能更为优异的物联网无线通信路由器产品。

采用工业级设计标准,它主要应用于行业用户的数据传输业务。

该产品采用高性能的32位嵌入式处理器,内嵌完备的TCP/IP协议栈,同时提供RS串口和10/100M以太网接口。

集成IO端子座,提供串口或者GPIO接口。

串口分别提供RS-232、RS-485、TTL电平接口的透明传输模式,支持的VPN 通信功能,采用IPSec/PPTP/L2TP/GRE/OpenVPN等VPN技术,企业级VPN隧道技术和防火墙技术,保证高安全性行业的数据安全,支持自动在线检测,实时动态刷新网络状态,保持链路畅通,产品以性能稳定、体积小、易于安装嵌入、抵抗环境能力强等优点,深受用户欢迎。

支持WEB/Telnet/Console/TR069/NMS管理系统等多种配置方式,其中用户面对的是WEB图形化管理配制界面,管理方便简单。

该产品已广泛应用于物联网产业链中的M2M/IoT行业,如物流快递柜、充电桩、金融、邮政、智能电网、智能交通、智能家居、智能建筑、环保监测、消防监控、安防监控、水利监测、公共安全、广告发布、供应链自动化、工业自动化、工业控制、地震监测、气象监测、数字化医疗、遥感勘测、仪表监测、农业、林业、水务、煤矿、石化等领域。

行业应用公共服务:物流快递柜、充电桩金融:银行储蓄点机房监控,移动性证券交易和信息查询,ATM机通信:电信机房动力环境监控,通信维护人员线路资料查询交通:GPRS/SMS/GPS 机动车辆监控调度系统;银行运钞车,邮政运输车监控调度公安:公安、110、交警车辆监控调度,公安移动性数据(身份证、犯罪档案等)查询,交警移动通信数据(车辆、司机档案等)查询热力:热力系统实时监控和维护电力:电力系统城市中电网实时监控和自动补偿,远程自动抄表;铁塔监控等;公司:移动办公及管理,其他外勤人员移动性数据查询工业:工业遥感,遥测,遥控信息回报气象:气象数据采集与传输水利:水文监测生活:煤气调压站实时数据采集自动控制,自来水;快递柜;污水管道,闸门、泵站与水厂实时监控维护电子商务:支持B2B、B2C的电子商务和电子支付、股票交易等监控: 视频监控, CCTV>>| 主要功能特性项目内容支持多种网络灵活选择全网通支持中国联通、中国电信、中国移动、中国广电等2G/3G/4G网络工业级应用设计采用高性能工业级无线模块;采用高性能工业级32位通讯处理器;支持低功耗模式,包括休眠模式、定时上下线、模式和定时开关机模式;采用金属外壳,保护等级IP30。

P28F010-90资料

元器件交易网

28F010/28F020

E

CONTENTS

PAGE PAGE 4.5 DC Characteristics—28F020—TTL/NMOS Compatible—Commercial Products .......... 22 4.6 DC Characteristics—28F010—CMOS Compatible—Commercial Products .......... 24 4.7 DC Characteristics—28F020—CMOS Compatible—Commercial Products .......... 25 4.8 DC Characteristics—28F010—TTL/NMO Compatible—Extended Temperature Products ................................................... 27 4.9 DC Characteristics—28F020—TTL/NMO Compatible—Extended Temperature Products ................................................... 29 4.10 DC Characteristics—28F010—CMOS Compatible—Extended Temperature Products ................................................... 31 4.11 DC Characteristics—28F020—CMOS Compatible—Extended Temperature Products ................................................... 32 4.12 AC Characteristics—28F010—Read-Only Operation—Commercial and Extended Temperature Products .............................. 35 4.13 AC Characteristics—28F020—Read Only Operations—Commercial and Extended Temperature Products .............................. 36 4.14 AC Characteristics—28F010— Write/Erase/Program Only Operation— Commercial and Extended Temperature Products ................................................... 38 4.15 AC Characteristics—28F020— Write/Erase/Program Only Operation— Commercial and Extended Temperature Products ................................................... 39 4.16 AC Characteristics—28F010—Alternative CE#-Controlled Write—Commercial and Extended Temperature ............................. 44 4.17 AC Characteristics—28F020—Alternate CE# Controlled Writes—Commercial and Extended Temperature Products .............. 45 4.18 Erase and Programming Performance ..... 46 5.0 ORDERING INFORMATION ......................... 47 6.0 ADDITIONAL INFORMATION....................... 47

ENC28J60_cn中文手册

2

20

3

19

4 ENC28J60 18

5

17

6

16

7

15

8 9 1011121314

VDDOSC

OSC2 OSC1 VSSOSC VSSPLL VDDPLL VDDRX

2006 Microchip Technology Inc.

高级信息

DS39662A_CN 第 1 页

ENC28J60

目录

1.0 概述 ... 2.0 外部连接 ... 3.0 存储器构成 ... 4.0 串行外设接口 (SPI) ... 5.0 以太网概述 ... 6.0 初始化 ... 7.0 发送和接收数据包 ... 8.0 接收过滤器 ... 9.0 双工模式配置和协商 ... 10.0 流量控制 ... 11.0 复位 ... 12.0 中断 ... 13.0 直接存储器访问控制器 ... 14.0 掉电 ... 15.0 内置自测试控制器 ... 16.0 电气特性 ... 17.0 封装信息 ... 索引 ... 客户支持 ... 系统信息和升级热线 ... 读者反馈表 ... 产品标识体系 ...

... 3 .. 5 .. 11 . 25 .. 31 . 33 . 39 .. 47 ... 53 ... 55 . 59 . 65 .. 75 . 77 . 79 ... 83 ... 89 .. 95 . 97 . 97 ... 98 .. 99

致客户

我们旨在提供᳔佳文档供客户正确使用 Microchip 产品。为此,我们将不断改进出版物的内容和质量,使之更好地满足您的要求。 出版 物的质量将随新文档及更新版本的推出而得到提升。 如果您对本出版物有任何问题和建议,请通过电子邮件联系我公司 TRC 经理,电子邮件地址为 CTRC@,或将本 数据手册 后附的 《读者反馈表》传真到 86-21-5407 5066。我们期待您的反馈。

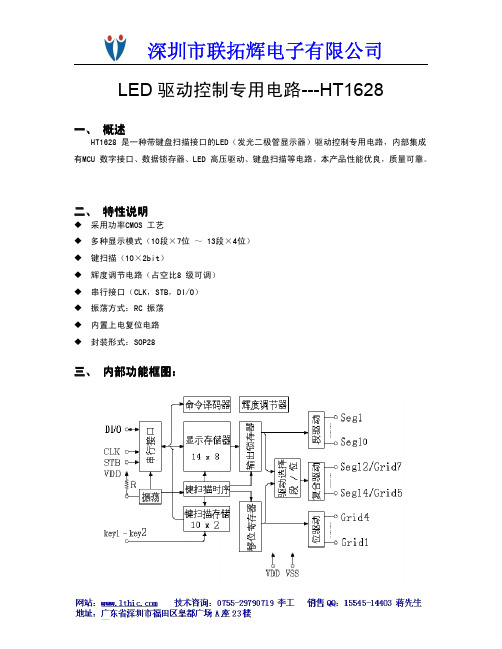

HT1628中文资料

LED驱动控制专用电路---HT1628一、概述HT1628是一种带键盘扫描接口的LED(发光二极管显示器)驱动控制专用电路,内部集成有MCU数字接口、数据锁存器、LED高压驱动、键盘扫描等电路。

本产品性能优良,质量可靠。

二、特性说明�采用功率CMOS工艺�多种显示模式(10段×7位~13段×4位)�键扫描(10×2bit)�辉度调节电路(占空比8级可调)�串行接口(CLK,STB,DI/O)�振荡方式:RC振荡�内置上电复位电路�封装形式:SOP28三、内部功能框图:四、管脚定义:管脚功能定义:五、显示寄存器地址和显示模式:该寄存器存储通过串行接口从外部器件传送到HT1628的数据,地址分配如下:六、键扫描和键扫数据寄存器:为10×3bit,如下所示:键扫数据储存地址如下所示,用读指令读取,读从低位开始:七、指令说明:指令用来设置显示模式和LED驱动器的状态。

在STB下降沿后由DIN输入的第一个字节作为一条指令。

如果在指令或数据传输时STB被置为高电平,串行通讯被初始化,并且正在传送的指令或数据无效(之前传送的指令或数据保持有效)。

(1)显示模式设置:该指令用来设置选择段和位的个数(4~7位,10~13段)。

当指令执行时,显示被强制终止,同时键扫描也停止。

要重新显示,显示开/关指令“ON”必需被执行,但当相同模式被设置时,则上述情况并不发生。

上电时,设置模式为4位,14段。

(2)数据设置:该指令用来设置数据写和读(3)地址设定:该指令用来设置显示寄存器的地址。

如果地址设为0EH或更高,数据被忽略,直到有效地址被设定。

上电时,地址设为00H。

(4)显示控制:上电时,设置为脉冲宽度为1/16,显示关。

上电时,键扫停止。

八、串行数据传输格式:数据接收(写数据)数据读取:因为DOUT管脚为N管开漏输出,所以该脚要连接一个外部上拉电阻(1KΩ到10KΩ)**:读取数据时,从串行时钟CLK的第8个上升沿开始设置指令到CLK下降沿读数据之间需要一个等待时间tWAIT(最小1μS)。

CSC-280系列数字式保护(测控)装置说明书(0SF.451.069)_V2.0

2.7

ห้องสมุดไป่ตู้

输出触点容量............................................................................................................................ 4

2.8

装置主要技术参数.................................................................................................................... 4

1.1

适用范围 ................................................................................................................................... 1

1.2

装置主要特点............................................................................................................................ 1

技术支持

电话:010-62986668 传真:010-62981900

重要提示

感谢您使用北京四方继保自动化股份有限公司的产品。为了安全、 正确、高效地使用本装置,请您务必注意以下重要提示:

1) 本说明书仅适用于 CSC-280 系列数字式保护(测控)装置。 2) 请仔细阅读本说明书,并按照说明书的规定调整、测试和操作。如

3.6

人机接口(MMI) ................................................................................................................... 7

MX28F160C3TTC-70G资料

MX28F160C3T/B16M-BIT [1M x16] CMOS SINGLE VOLTAGE3V ONLY FLASH MEMORY- Word write suspend to read- Sector erase suspend to word write- Sector erase suspend to read register report•Automatic sector erase, word write and sector lock/unlock configuration •Status Reply- Detection of program and erase operation comple-tion.- Command User Interface (CUI)- Status Register (SR)•Data Protection Performance- Include boot sectors and parameter and main sectors to be locked/unlocked•100,000 minimum erase/program cycles •Common Flash Interface (CFI)•128-bit Protection Register- 64-bit Unique Device Identifier - 64-bit User-Programmable•Latch-up protected to 100mA from -1V to VCC+1V •Package type:- 48-pin TSOP (12mm x 20mm)- 48-ball CSP (8mm x 6mm)FEATURES•Bit Organization: 1,048,576 x 16•Single power supply operation- VCC=VCCQ=2.7~3.6V for read, erase and program operation- VPP=12V for fast production programming - Operating temperature:-40°C~85°C •Fast access time : 70/90/110ns •Low power consumption- 9mA typical active read current, f=5MHz- 18mA typical program current (VPP=1.65~3.6V)- 21mA typical erase current (VPP=1.65~3.6V)- 7uA typical standby current under power saving mode•Sector architecture- Sector structure : 4Kword x 2 (boot sectors), 4Kword x 6 (parameter sectors), 32Kword x 31 (main sectors)- Top/Bottom Boot•Auto Erase and Auto Program- Automatically program and verify data at specified address- Auto sector erase at specified sector •Automatic Suspend EnhanceGENERAL DESCRIPTIONThe MX28F160C3T/B is a 16-mega bit Flash memory organized as 1M words of 16 bits. The 1M word of data is arranged in eight 4Kword boot and parameter sectors,and thirty-one 32K word main sectors which are indi-vidually erasable. MXIC's Flash memories offer the most cost-effective and reliable read/write non-volatile random access memory. The MX28F160C3T/B is packaged in 48-pin TSOP and 48-ball CSP . It is designed to be re-programmed and erased in system or in standard EPROM programmers.fast as 70ns, allowing operation of high-speed micropro-cessors without wait states.MXIC's Flash memories augment EPROM functionality with in-circuit electrical erasure and programming. The MX28F160C3T/B uses a command register to manage this functionality. The command register allows for 100%TTL level control inputs and fixed power supply levels during erase and programming, while maintaining maxi-mum EPROM compatibility.MXIC Flash technology reliably stores memory contents even after 100,000 erase and program cycles. The MXICMX28F160C3T/Bmechanisms. In addition, the combination of advanced tunnel oxide processing and low internal electric fields for erase and program operations produces reliable cy-cling. The MX28F160C3T/B uses a 2.7V~3.6V VCC sup-ply to perform the High Reliability Erase and auto Pro-gram/Erase algorithms.The highest degree of latch-up protection is achieved with MXIC's proprietary non-epi process. Latch-up pro-tection is proved for stresses up to 100 milliamps on address and data pin from -1V to VCC + 1V.The dedicated VPP pin gives complete data protection when VPP< VPPLK.A Command User Interface (CUI) serves as the inter-face between the system processor and internal opera-tion of the device. A valid command sequence written to the CUI initiates device automation. An internal Write State Machine (WSM) automatically executes the algo-rithms and timings necessary for erase, word write and sector lock/unlock configuration operations.A sector erase operation erases one of the device's 32K-word sectors typically within 1.0s, 4K-word sectors typi-cally within 0.5s independent of other sectors. Each sec-tor can be independently erased minimum 100,000 times. Sector erase suspend mode allows system software to suspend sector erase to read or write data from any other sector.Writing memory data is performed in word increments of the device's 32K-word sectors typically within 0.8s and 4K-word sectors typically within 0.1s. Word program sus-pend mode enables the system to read data or execute code from any other memory array location.MX28F160C3T/B features with individual sectors lock-ing by using a combination of bits thirty-nine sector lock-bits and WP, to lock and unlock sectors.The status register indicates when the WSM's sector erase, word program or lock configuration operation is done.The access time is 70/90/110ns (tELQV) over the oper-ating temperature range (-40°C to +85°C) and VCC sup-ply voltage range of 2.7V~3.6V.MX28F160C3T/B's power saving mode feature substan-tially reduces active current when the device is in static mode (addresses not switching). In this mode, the typi-cal ICCS current is 7uA (CMOS) at 3.0V VCC.As CE and RP are at VCC, ICC CMOS standby mode is enabled. When RP is at GND, the reset mode is enabled which minimize power consumption and provide data write protection.A reset time (tPHQV) is required from RP switching high until outputs are valid. Similarly, the device has a wake time (tPHEL) from RP-high until writes to the CUI are recognized. With RP at GND, the WSM is reset and the status register is cleared.MX28F160C3T/BMX28F160C3T/BMX28F160C3T/BTable 1. Pin DescriptionSymbol Type Description and FunctionA0-A19input Address inputs for memory address. Data pin float to high-impedance when the chip isdeselected or outputs are disable. Addresses are internally latched during a write orerase cycle.DQ0-DQ15input/output Data inputs/outputs: Inputs array data on the second CE and WE cycle during a pro-gram command. Data is internally latched. Outputs array and configuration data. Thedata pin float to tri-state when the chip is de-selected.CE input Chip Enable : Activates the device's control logic, input buffers, and sense amplifiers.CE high de-selects the memory device and reduce power consumption to standbylevel. CE is active low.RP input Reset/Deep Power Down: when RP=VIL, the device is in reset/deep power down mode,which drives the outputs to High Z, resets the WSM and minimizes current level.When RP=VIH, the device is normal operation. When RP transitions from VIL to VIH,the device defaults to the read array mode.WE input Write Enable: to control write to CUI and array sector. WE=VIL becomes active. Thedata and addresses are latched on the rising edge of the second WE pulse.VPP input/supply Program/Erase Power Supply:(1.65V~3.6V or 11.4V~12.6V)Lower VPP<VPPLK, to protect any contents against Program and Erase Command.Set VPP=VCC for in-system Read, Program and Erase Operation.Raise VPP to 12V±5% for faster program and erase in a production environment.OE input Output enable: gates the device's outputs during a real cycle.WP input Write Protect: When WP is VIL, the sectors marked Lock Down can't be unlockedthrough software. When WP is VIH, the lock down mechanism is disable and sectorspreviously locked down are now locked and can be unlocked and locked through soft-ware. After WP goes low, any sectors previously marked lock down revert to that state. VCC supply Device power supply: (2.7V~3.6V).VCCQ input I/O Power Supply: supplies for input/output buffers. (VCCQ must be tied to VCC) GND supply Ground voltage: all the GND pin shall not be connected.MX28F160C3T/BSECTOR STRUCTURE (TOP)Sector Sector Size Address Range (h)Boot Sector 04K Word FF000 ~ FFFFFBoot Sector 14K Word FE000 ~ FEFFFParameter Sector 04K Word FD000 ~ FDFFFParameter Sector 14K Word FC000 ~ FCFFFParameter Sector 24K Word FB000 ~ FBFFFParameter Sector 34K Word FA000 ~ FAFFFParameter Sector 44K Word F9000 ~ F9FFFParameter Sector 54K Word F8000 ~ F8FFFMain Sector 032K Word F0000 ~ F7FFFMain Sector 132K Word E8000 ~ EFFFFMain Sector 232K Word E0000 ~ E7FFFMain Sector 332K Word D8000 ~ DFFFFMain Sector 432K Word D0000 ~ D7FFFMain Sector 532K Word C8000 ~ CFFFFMain Sector 632K Word C0000 ~ C7FFFMain Sector 732K Word B8000 ~ BFFFFMain Sector 832K Word B0000 ~ B7FFFMain Sector 932K Word A8000 ~ AFFFFMain Sector 1032K Word A0000 ~ A7FFFMain Sector 1132K Word98000 ~ 9FFFFMain Sector 1232K Word90000 ~ 97FFFMain Sector 1332K Word88000 ~ 8FFFFMain Sector 1432K Word80000 ~ 87FFFMain Sector 1532K Word78000 ~ 7FFFFMain Sector 1632K Word70000 ~ 77FFFMain Sector 1732K Word68000 ~ 6FFFFMain Sector 1832K Word60000 ~ 67FFFMain Sector 1932K Word58000 ~ 5FFFFMain Sector 2032K Word50000 ~ 57FFFMain Sector 2132K Word48000 ~ 4FFFFMain Sector 2232K Word40000 ~ 47FFFMain Sector 2332K Word38000 ~ 3FFFFMain Sector 2432K Word30000 ~ 37FFFMain Sector 2532K Word28000 ~ 2FFFFMain Sector 2632K Word20000 ~ 27FFFMain Sector 2732K Word18000 ~ 1FFFFMain Sector 2832K Word10000 ~ 17FFFMain Sector 2932K Word08000 ~ 0FFFFMX28F160C3T/BSECTOR STRUCTURE (BOTTOM)Sector Sector Size Address Range (h)Boot Sector 04K Word00000 ~ 00FFFBoot Sector 14K Word01000 ~ 01FFFParameter Sector 04K Word02000 ~ 02FFFParameter Sector 14K Word03000 ~ 03FFFParameter Sector 24K Word04000 ~ 04FFFParameter Sector 34K Word05000 ~ 05FFFParameter Sector 44K Word06000 ~ 06FFFParameter Sector 54K Word07000 ~ 07FFFMain Sector 032K Word08000 ~ 0FFFFMain Sector 132K Word10000 ~ 17FFFMain Sector 232K Word18000 ~ 1FFFFMain Sector 332K Word20000 ~ 27FFFMain Sector 432K Word28000 ~ 2FFFFMain Sector 532K Word30000 ~ 37FFFMain Sector 632K Word38000 ~ 3FFFFMain Sector 732K Word40000 ~ 47FFFMain Sector 832K Word48000 ~ 4FFFFMain Sector 932K Word50000 ~ 57FFFMain Sector 1032K Word58000 ~ 5FFFFMain Sector 1132K Word60000 ~ 67FFFMain Sector 1232K Word68000 ~ 6FFFFMain Sector 1332K Word70000 ~ 77FFFMain Sector 1432K Word78000 ~ 7FFFFMain Sector 1532K Word80000 ~ 87FFFMain Sector 1632K Word88000 ~ 8FFFFMain Sector 1732K Word90000 ~ 97FFFMain Sector 1832K Word98000 ~ 9FFFFMain Sector 1932K Word A0000 ~ A7FFFMain Sector 2032K Word A8000 ~ AFFFFMain Sector 2132K Word B0000 ~ B7FFFMain Sector 2232K Word B8000 ~ BFFFFMain Sector 2332K Word C0000 ~ C7FFFMain Sector 2432K Word C8000 ~ CFFFFMain Sector 2532K Word D0000 ~ D7FFFMain Sector 2632K Word D8000 ~ DFFFFMain Sector 2732K Word E0000 ~ E7FFFMain Sector 2832K Word E8000 ~ EFFFFMain Sector 2932K Word F0000 ~ F7FFFMX28F160C3T/B2 PRINCIPLES OF OPERATIONThe product includes an on-chip WSM to manage sec-tor erase, word write and lock-bit configuration functions.After initial device power-up or return from reset mode (see section on Bus Operations), the device defaults to read array mode. Manipulation of external memory con-trol pins allow array read, standby and output disable operations.Status register and identifier codes can be accessed through the CUI independent of the VPP voltage. All functions associated with altering memory contents -sector erase, word write, sector lock/unlock, status and identifier codes - are accessed via the CUI and verified through the status register.Commands are written using standard microprocessor write timings. The CUI contents serve as input to the WSM, which controls the sector erase, word write and sector lock/unlock. The internal algorithms are regulated by the WSM, including pulse repetition, internal verifica-tion and margining of data. Addresses and data are in-ternally latched during write cycles. Address is latched at falling edge of CE and data latched at rising edge of WE. Writing the appropriate command outputs array data, accesses the identifier codes or outputs status register data.Interface software that initiates and polls progress of sector erase, word write and sector lock/unlock can be stored in any sector. This code is copied to and executed from system RAM during flash memory updates. After successful completion, reads are again possible via the Read Array command. Sector erase suspend allows system software to suspend a sector erase to read/write data from/to sectors other than that which is suspend. Word write suspend allows system software to suspend a word write to read data from any other flash memory array location.With the mechanism of sector lock, memory contents cannot be altered due to noise or unwanted operation. When RP=VIH and VCC<VLKO (lockout voltage), any data write alteration can be failure. During read opera-tion, if write VPP voltage is below VPPLK, then hard-ware level data protection is achieved. With CUI's two-step command sequence sector erase, word write or sector lock/unlock, software level data protection is 3 BUS OPERATIONThe local CPU reads and writes flash memory in-sys-tem. All bus cycles to or from the flash memory conform to standard microprocessor bus cycles.3.1 ReadInformation can be read from any sector, configuration codes or status register independent of the VPP volt-age. RP can be at VIH.The first task is to write the appropriate read mode com-mand (Read Array, Read Configuration, Read Query or Read Status Register) to the CUI. Upon initial device power-up or after exit from reset, the device automati-cally resets to read array mode. In order to read data, control pins set for CE, OE, WE, RP and WP must be driven to active. CE and OE must be active to obtain data at the outputs. CE is the device selection control. OE is the data output (DQ0-DQ15) control and active drives the selected memory data onto the I/O bus, WE must be VIH, RP must be VIH, WP must be at VIL or VIH.3.2 Output DisableWith OE at a logic-high level (VIH), the device outputs are disabled. Output pins (DQ0-DQ15) are placed in a high-impedance state.3.3 StandbyCE at a logic-high level (VIH) places the device in standby mode which substantially reduces device power consumption. DQ0~DQ15 outputs are placed in a high-impedance state independent of OE. If deselected dur-ing sector erase, word write or sector lock/unlock, the device continues functioning, and consuming active power until the operation completes.3.4 ResetAs RP=VIL, it initiates the reset mode. The device en-ters reset/deep power down mode. However, the data stored in the memory has to be sustained at least 100nsMX28F160C3T/Band output high impedance state.In read modes, RP-low deselects the memory, places output drivers in a high-impedance state and turns off all internal circuits. RP must be held low for a minimum of 100ns. Time tPHQV is required after return from reset mode until initial memory access outputs are valid. Af-ter this wake-up interval tPHEL or tPHWL, normal op-eration is restored. The CUI is reset to read array mode and status register is set to 80H. Sector lock bit is set at lock status.During sector erase, word write or sector lock/unlock modes, RP-low will abort the operation. Memory con-tents being altered are no longer valid; the data may be partially erased or written.In addition, CUI will go into either array read mode or erase/write interrupted mode. When power is up and the device reset subsequently, it is necessary to read sta-tus register in order to assure the status of the device. Recognizing status register (SR.7~0) will assure if the device goes back to normal reset and enters array read mode.3.5 Read Configuration CodesThe read configuration codes operation outputs the manu-facturer code, device code, sector lock configuration codes, and the protection register. Using the manufac-turer and device codes, the system CPU can automati-cally match the device with its proper algorithms. The sector lock codes identify locked and unlocked sectors.3.6 WriteWriting commands to the CUI enable reading of device data and identifier codes. They also control inspection and clearing of the status register. When VCC=2.7V-3.6V and VPP within VPP1 or VPP2 range, the CUI addition-ally controls sector erase, word write and sector lock/ unlock.The Sector Erase command requires appropriate com-mand data and an address within the sector to be erased. The Full Chip Erase command requires appropriate com-mand data and an address within the device. The Word Write command requires the command and address of mands require the command and address within the de-vice or sector within the device (Sector Lock) to be locked. The Clear Sector Lock-Bits command requires the command and address within the device.The CUI does not occupy an addressable memory loca-tion. It is written when WE and CE are active (whichever goes high first). The address and data needed to ex-ecute a command are latched on the rising edge of WE or CE. Standard microprocessor write timings are used.MX28F160C3T/B4 COMMAND DEFINITIONSThe flash memory has four read modes: read array, readconfiguration, read status, read query, and two writemodes: program, erase. These read modes are acces-sible independent of the VPP voltage. But write modesare disable during VPP<VPPLK. Placing VPP on VPP1/2 enables successful sector erase, word write and sec-tor lock/unlock.Device operations are selected by writing specific com-mands into the CUI. T able 3 defines these commands.Table 2. Bus OperationMode Notes RP CE OE WE DQ0~DQ15Read1,2VIH VIL VIL VIH DOUTOutput Disable2VIH VIL VIH VIH High ZStandby2VIH VIH X X High ZReset2VIL X X X High ZWrite2,3,4,5VIH VIL VIH VIL DINNotes:1.Refer to DC Characteristics for VPPLK, VPP1, VPP2 voltage.2.X can be VIL or VIH for pin and addresses.3.RP at GND±0.2 to ensure the lowest power consumption.4.Refer to Table 3 for valid DIN during a write operation.5.To program or erase the lockable sectors holds WP at VIH.MX28F160C3T/BTable 3. Command Definition (1)Command Bus Notes First Bus Cycle Second Bus CycleCycles Operation Address Data Operation Address DataRequired(1)(2)(3)(1)(2)(3) Read Array1Write X FFHRead Configuration> 22,4Write X90H Read IA ID Read Query22,7Write X98H Read QA QD Read Status Register23Write X70H Read X SRD Clear Status Register13Write X50HSector Erase/Confirm2Write X20H Write SA D0H Word Write22,5Write X40H/10H Write WA WD Program/Erase Suspend1Write X B0HProgram/Erase Resume1Write X D0HSector Lock2Write X60H Write SA01H Sector Unlock26Write X60H Write SA D0H Lock-Down Sector2Write X60H Write SA2FH Protection Program2Write X C0H Write P A PDNotes:1.Bus operation are defined in Table 2 and referred to AC Timing Waveform.2.X=Any address within device.IA=ID-Code Address (refer to Table 4).ID=Data read from identifier code.SA=Sector Address within the sector being erased.WA=Address of memory location to be written.WD=Data to be written at location WA.PA=Program Address, PD=Program DataQA=Query Address, QD=Query Data.3.Data is latched from the rising edge of WE or CE (whichever goes high first)SRD=Data read from status register, see T able 6 for description of the status register bits.4.Following the Read Configuration codes command, read operation access manufacturer, device codes, sectorlock/unlock codes, see chapter 4.2.5.Either 40H or 10H command is recognized by the WSM as word write setup.6.The sector unlock operation simultaneously clear all sector lock.7.Read Query Command is read for CFI query information.MX28F160C3T/B4.1 Read Array CommandUpon initial device power-up and after exit from reset mode, the device defaults to read array mode. This op-eration is also initiated by writing the Read Array com-mand. The device remains enabled for reads until an-other command is written. Once the internal WSM has started a sector erase, word write or sector lock con-figuration the device will not recognize the Read Array command until the WSM completes its operation unless the WSM is suspended via a Sector Erase Suspend or Word Write Suspend command. If RP=VIL device is in read Read Array command mode, this read operation no longer requires VPP . The Read Array command func-tions independently of the VPP voltage and RP can be VIH.4.2 Read Configuration Codes CommandThe configuration code operation is initiated by writing the Read Configuration Codes command (90H). To re-turn to read array mode, write the Read Array Command (FFH). Following the command write, read cycles from addresses shown in T able 4 retrieve the manufacturer,device, sector lock configuration codes and the protec-tion register(see Table 4 for configuration code values).T o terminate the operation, write another valid command.Like the Read Array command, the Read Configuration Codes command functions independently of the VPP voltage and RP can be VIH. Following the Read Configu-ration Codes command, the information is shown:CodeAddress Data (A19-A0)(DQ15-DQ0)Manufacturer Code00000H00C2H Device Code(Top/Bottom)00001H 88C2/88C3H Sector Lock Configuration XX002H LocK - Sector is unlocked DQ0=0- Sector is locked DQ0=1- Sector is locked-down DQ1=1Protection Register Lock 80PR-LK Protection Register81-88PRTable 4: ID Code4.3 Read Status Register CommandCUI writes read status command (70H). The status reg-ister may be read to determine when a sector erase,word write or lock-bit configuration is complete and whether the operation completed successfully. (refer to table 6) It may be read at any time by writing the Read Status Register command. After writing this command,all subsequent read operations output data from the sta-tus register until another valid command is written. The status register contents are latched on the falling edge of CE or OE, whichever occurs last. CE or OE must toggle to VIH before further reads to update the status register latch. The Read Status Register command func-tions independently of the VPP voltage. RP can be VIH.4.4 Clear Status Register CommandStatus register bits SR.5, SR.4, SR.3 or SR.1 are set to "1"s by the WSM and can only be reset by the Clear Status Register command (50H). These bits indicate various failure conditions (see Table 6). By allowing sys-tem software to reset these bits, several operations (such as cumulatively erasing multiple sectors or writing sev-eral words in sequence) may be performed. The status register may be polled to determine if an error occurred during the sequence.T o clear the status register, the Clear Status Register command (50H) is written on CUI. It functions indepen-dently of the applied VPP Voltage. RP can be VIH. This command is not functional during sector erase or word write suspend modes.MX28F160C3T/B4.5 Sector Erase CommandErase is executed one sector at a time and initiated by a two-cycle command. A sector erase setup is first writ-ten (20H), followed by a sector erase confirm (D0H). This command sequence requires appropriate sequencing and an address within the sector to be erased. Sector pre-conditioning, erase, and verify are handled internally by the WSM. After the two-cycle sector erase sequence is written, the device automatically outputs status register data when read (see Figure 8). The CPU can detect sec-tor erase completion by analyzing the output data of the status register bit SR.7.When the sector erase is complete, status register bit SR.5 should be checked. If a sector erase error is de-tected, the status register should be cleared before sys-tem software attempts corrective actions. The CUI re-mains in read status register mode until a new com-mand is issued.This two-step command sequence of set-up followed by execution ensures that sector contents are not acciden-tally erased. An invalid sector Erase command sequence will result in both status register bits SR.4 and SR.5 being set to "1". Also, reliable sector erasure can only occur when 2.7V~3.6V and VPP=VPP1/2. In the absence of this high voltage, sector contents are protected against erasure. If sector erase is attempted while VPP<VPPLK SR.3 and SR.5 will be set to "1". T o successfully erase the boot sector, the corresponding sector lock-bit must be clear first. In parameter and sectors case, it must be cleared the corresponding sector lock-bit. If sector erase is attempted when the excepting above sector being locked conditions, SR.1 and SR.5 will be set to "1". Sec-tor erase is not functional.4.6 Word Write CommandWord write is executed by a two-cycle command se-quence. Word write setup (standard 40H or alternate 10H) is written, followed by a second write that specifies the address and data. The WSM then takes over, controlling the word write and write verify algorithms internally. Af-ter the word write sequence is written, the device auto-matically outputs status register data when read (see Figure 6). The CPU can detect the completion of the word write event by analyzing the status register bit SR.7. When word write is complete, status register bit SR.4should be checked. If word write error is detected, the status register should be cleared. The internal WSM verify only detects errors for "1"s that do not successfully write to "0"s. The CUI remains in read status register mode until it receives another command.Reliable word writes can only occur when VCC=2.7V~3.6V and VPP=VPP1/2. If VPP is not within acceptable limits, the WSM doesn't execut the program command. If word write is attempted while VPP<VPPLK, status register bits SR.3 and SR.4 will be set to "1". Successful word write requires for boot sector that WP is VIH the corresponding sector lock-bit be cleared. In parameter and main sectors case, it must be cleared the corresponding sector lock-bit. If word write is at-tempted when the excepting above sector being clocked conditions, SR.1 and SR.4 will be set to "1". Word write is not functional.4.7 Sector Erase Suspend CommandThe Sector Erase Suspend command (50H) allows sec-tor-erase interruption to read or word write data in an-other sector of memory. Once the sector erase process starts, writing the Sector Erase Suspend command re-quests that the WSM suspend the sector erase sequence at a predetermined point in the algorithm. The device outputs status register data when read after the Sector Erase Suspend command is written. Polling status reg-ister bits SR.7 and SR.6 can determine when the sector erase operation has been suspended (both will be set to "1"). Specification tWHRH2/tEHRH2 defines the sector erase suspend latency.When Sector Erase Suspend command is written to the CUI, if sector erase was finished, the device would be placed read array mode. Therefore, after Sector Erase Suspend command is written to the CUI, Read Status Register command (70H) has to be written to CUI, then status register bit SR.6 should be checked if/when the device is in suspend mode.At this point, a Read Array command can be written to read data from sectors other than that which is sus-pended. A Word Write commands sequence can also be issued during erase suspend to program data in other sectors. Using the Word Write Suspend command (see Section 4.9), a word write operation can also be sus-pended. During a word write operation with sector erase suspended, status register bit SR.7 will return to "0".MX28F160C3T/BHowever, SR.6 will remain "1" to indicate sector erase suspend status.The only other valid commands while sector erase is suspended are Read Status Register, Read Configura-tion, Read Query, Program Setup, Program Resume, Sector Lock, Sector Unlock, Sector Lock-Down and sec-tor erase Resume. After a Sector Erase Resume com-mand is written to the flash memory, the WSM will con-tinue the sector erase process. Status register bits SR.6 and SR.7 will automatically be cleared. After the Erase Resume command is written, the device automatically outputs status register data when read (see Figure 9). VPP must remain at VPP1/2 while sector erase is sus-pended. RP must also remain at VIH (the same RP level used for sector erase). Sector cannot resume until word write operations initiated during sector erase suspend has completed.If the time between writing the Sector Erase Resume command and writing the Sector Erase Suspend com-mand is shorter than 15ms and both commands are writ-ten repeatedly, a longer time is required than standard sector erase until the completion of the operation.4.8 Word Write Suspend CommandThe Word Write Suspend command allows word write interruption to read data in other flash memory locations. Once the word write process starts, writing the Word Write Suspend command requests that the WSM sus-pend the Word write sequence at a predetermined point in the algorithm. The device continues to output status register data when read after the Word Write Suspend command is written. Polling status register bits SR.7 and SR.2 can determine when the word write operation has been suspended (both will be set to "1"). Specification tWHRH1/tEHRH1 defines the word write suspend latency. When Word Write Suspend command write to the CUI, if word write was finished, the device places read array mode. Therefore, after Word Write Suspend command write to the CUI, Read Status Register command (70H) has to be written to CUI, then status register bit SR.2 should be checked for if/when the device is in suspend mode.At this point, a Read Array command can be written to read data from locations other than that which is sus-pended. The only other valid commands while word write is suspended are Read Status Register Read Configura-tion, Read Query and Word Write Resume. After Word Write Resume command is written to the flash memory, the WSM will continue the Word write process. Status register bits SR.2 and SR.7 will automatically be cleared. After the Word Write Resume command is written, the device automatically outputs status register data when read (see Figure 7). VPP must remain at VPP1/2 while in word write suspend mode. RP must also remain at VIH (the same RP level used for word write).If the time between writing the Word Write Resume com-mand and writing the Word Write Suspend command is short and both commands are written repeatedly, a longer time is required than standard word write until the comple-tion of the operation.。

CC72004

CC72004

4×2×23AWG UTP CAT6 250MHz HSYVInstallation Cable

CC72004

单位

305m/箱

适用建筑物数字通信用水平对绞电缆

带宽级别250MHz

性能符合ANSI/TIA-568-C.2、YD/T1019六类标准

物理机械特性:

●线规:23AWG

●绝缘层:高密度聚烯烃(HDPE),厚度:0.2mm

●外护套:聚氯乙烯(PVC),厚度:0.5mm

● 线缆外径:6.0±0.5mm

●骨芯结构:十字骨芯

●线缆颜色:灰色(RAL7035)

●毛重:13Kg(305m/轴)

●最大承受拉力:100N

●安装温度:5至+40℃

●工作温度:-15至+60℃

电气性能:

●最大电容:≤5.6nF/100m

●最大直流电阻:≤9.38Ω/100m

认证:

●符合RoHS欧盟环保认证

订货信息:

中文描述

6类4对非屏蔽双绞线

订货型号

北京市首批自主创新产品

北京东方通科技发展有限公司

70

东方通应用集成中间件软件V3.0

北京东方通科技发展有限公司

71

组合移动式集装箱检查系统

清华同方威视技术股份有限公司

72

铁路集装货物安全检查系统

清华同方威视技术股份有限公司

73

车载移动式集装检查系统

清华同方威视技术股份有限公司

74

北京中电华大电子设计有限责任公司

104

直流直流系列变换器模块电源

北京新雷能有限责任公司

105

MINIPCI无线网卡LHWT0101T

北京六合万通微电子技术有限公司

106

CARDBUS无线网卡LHWT1101T

北京六合万通微电子技术有限公司

107

龙芯信富宝(GS-T-01)

北京神州龙芯集成电路设计有限公司

北京地拓科技发展有限公司

79

SuperMap 网络地理信息系统开发平台

北京超图地理信息技术有限公司

80

SuperMap Objects大型全组件式地理信息系统开发平台

北京超图地理信息技术有限公司

81

七号信令集中监测系统

北京中创信测科技股份有限公司

82

北斗一号信息服务系统

北京北斗星通导航技术股份有限公司

北京牡丹联友电子工程有限公司

北京久其软件股份有限公司

28

久其CI综合信息管理平台软件

北京久其软件股份有限公司

29

RedOffice中文贰仟办公软件V3.0

北京红旗中文贰仟软件技术有限公司

30

美髯公信息资源目录管理系统软件V1.0

北京美髯公科技发展有限公司

29F040-70资料