XC6115A046中文资料

XC610101A016MR资料

* The dissipation pad for the USP-6C package should be solder-plated in recommended mount pattern and metal masking so as to enhance mounting strength and heat release. If the pad needs to be connected to other pins, it should be connected to the VSS (No.5) pin.

V IN 6 V SS 5 RESETB 4

1 MRB 2 RESET 3 NC

VIN 6 VSS 5 RESET 4

1 WD 2 MRB 3 NC

USP-6C (BOTTOM VIEW)

USP-6C (BOTTOM VIEW)

USP-6C (BOTTOM VIEW)

USP-6C (BOTTOM VIEW)

Reset Output (VDFL: Low Level When Detected) Ground Manual Reset Watchdog Power Input Reset Output (VDFH: High Level When Detected)

2/27

元器件交易网

PIN ASSIGNMENT

PIN NUMBER XC6101, XC6102 XC6103 XC6104, XC6105 XC6106, XC6107 PIN NAME XC6111, XC6112 XC6113 XC6114, XC6115 XC6116, XC6117 SOT-25 USP-6C SOT-25 USP-6C SOT-25 USP-6C SOT-25 USP-6C 1 2 3 4 5 4 5 2 1 6 2 3 4 5 1 5 2 1 6 4 1 2 4 5 3 4 5 1 6 2 1 2 4 5 3 4 5 1 6 2 RESETB VSS MRB WD VIN RESET FUNCTION

Z056A中文资料

Type No.

Nominal Zener Voltage VZ @ I ZT

(V)

Test Current IZT

(mA)

Maximum Zener Impedance ZZT @ I ZT ZZK @ I ZK IZK

(Ω) (Ω) (mA)

Maximum Reverse Leakage Current IR @ V R

Page 2 of 2

Rev. 04 : May 29, 2006

43 47 51 56 62 68 75 82 91 100 110 120 130 150 160 180 190 200

2.75 2.40 2.23 2.00 1.83 1.65 1.50 1.37 1.25 1.12 1.00 0.95 0.88 0.75 0.70 0.62 0.57 0.55

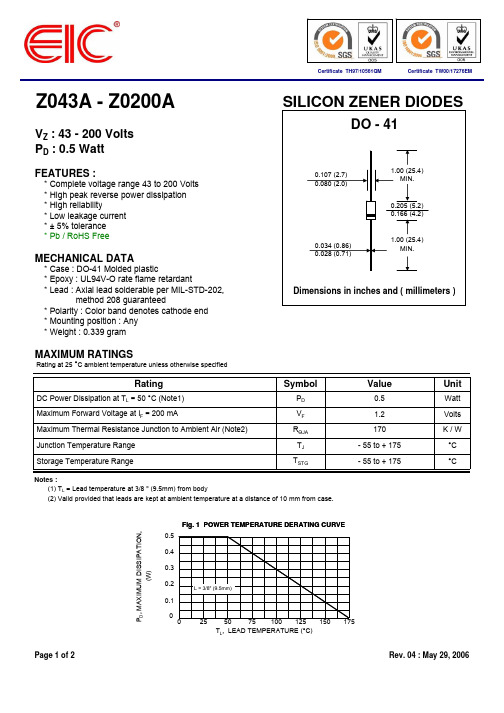

Notes : (1) TL = Lead temperature at 3/8 " (5mm) from body

Symbol

PD VF RӨJA TJ TSTG

Value

0.5 1.2 170 - 55 to + 175 - 55 to + 175

Unit

Watt Volts K/W °C °C

元器件交易网

Certificate TH97/10561QM

Certificate TW00/17276EM

Z043A - Z0200A

VZ : 43 - 200 Volts PD : 0.5 Watt

FEATURES :

* Complete voltage range 43 to 200 Volts * High peak reverse power dissipation * High reliability * Low leakage current * ± 5% tolerance * Pb / RoHS Free

XC6116D644中文资料

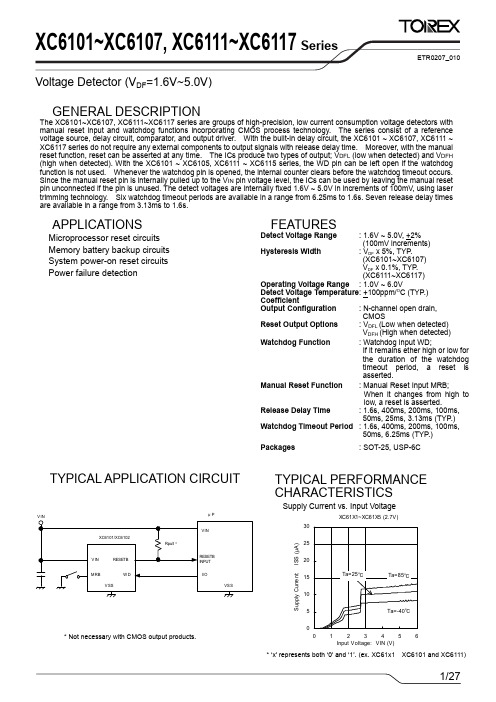

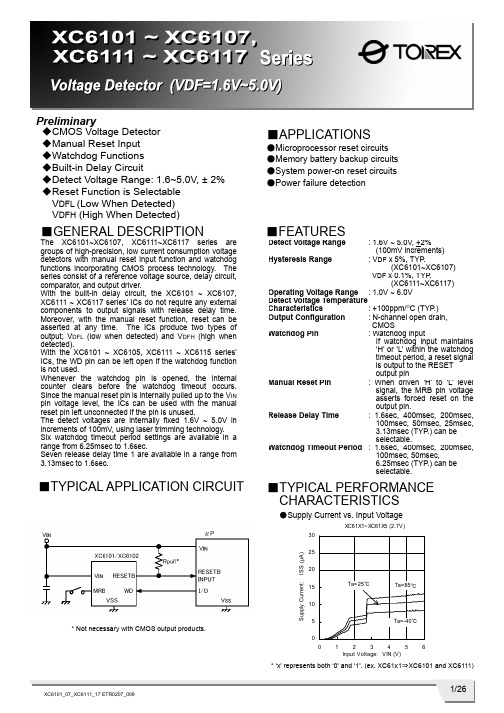

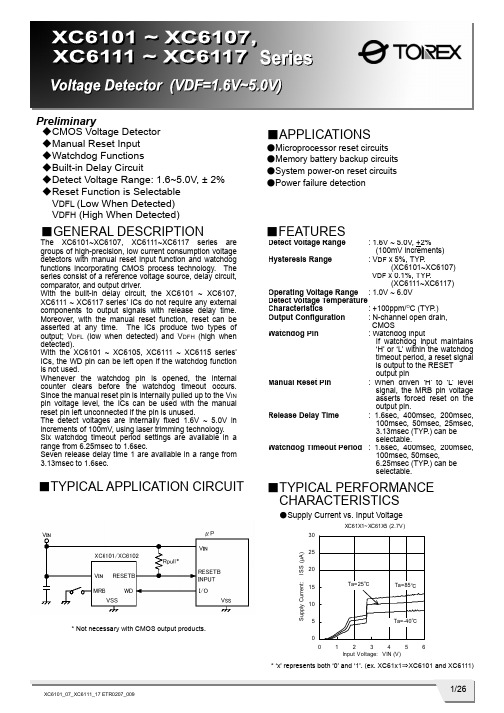

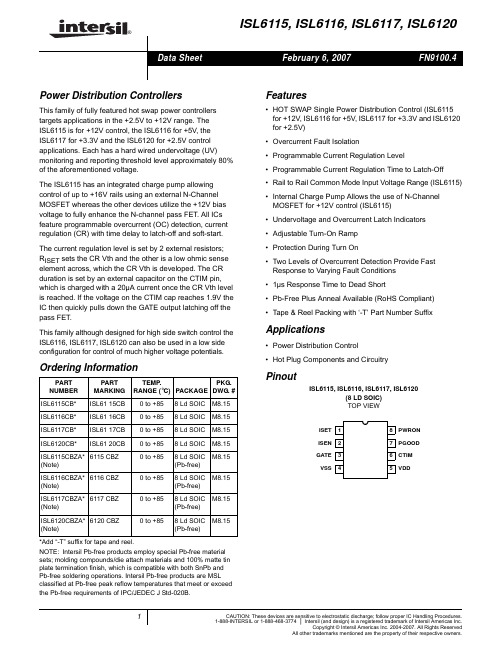

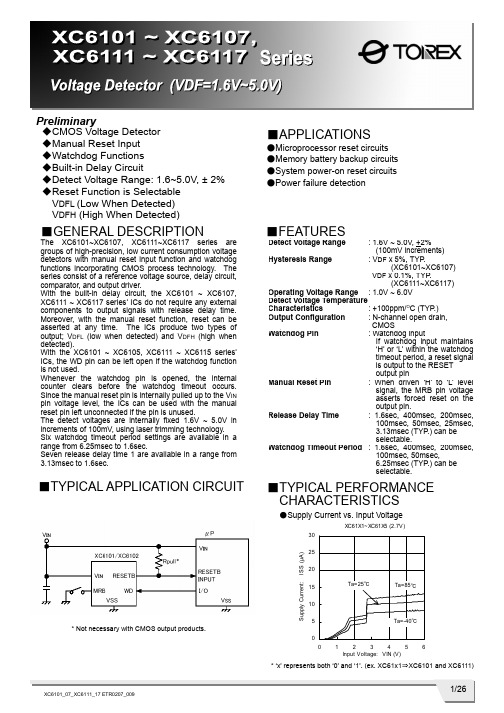

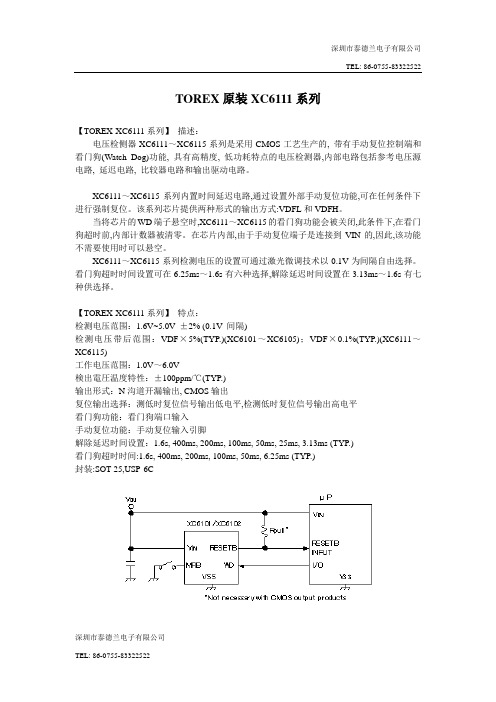

1/26XC6101_07_XC6111_17 ETR0207_009Preliminary◆CMOS Voltage Detector◆Manual Reset Input ◆Watchdog Functions ◆Built-in Delay Circuit ◆Detect Voltage Range: 1.6~5.0V, ± 2% ◆Reset Function is Selectable V DFL (Low When Detected) V DFH (High When Detected)■GENERAL DESCRIPTION The XC6101~XC6107, XC6111~XC6117 series aregroups of high-precision, low current consumption voltage detectors with manual reset input function and watchdog functions incorporating CMOS process technology. The series consist of a reference voltage source, delay circuit, comparator, and output driver.With the built-in delay circuit, the XC6101 ~ XC6107, XC6111 ~ XC6117 series’ ICs do not require any external components to output signals with release delay time. Moreover, with the manual reset function, reset can be asserted at any time. The ICs produce two types of output; V DFL (low when detected) and V DFH (high when detected).With the XC6101 ~ XC6105, XC6111 ~ XC6115 series’ ICs, the WD pin can be left open if the watchdog function is not used. Whenever the watchdog pin is opened, the internal counter clears before the watchdog timeout occurs. Since the manual reset pin is internally pulled up to the V IN pin voltage level, the ICs can be used with the manual reset pin left unconnected if the pin is unused.The detect voltages are internally fixed 1.6V ~ 5.0V in increments of 100mV, using laser trimming technology. Six watchdog timeout period settings are available in a range from 6.25msec to 1.6sec. Seven release delay time 1 are available in a range from 3.13msec to 1.6sec.■APPLICATIONS●Microprocessor reset circuits●Memory battery backup circuits ●System power-on reset circuits ●Power failure detection■TYPICAL APPLICATION CIRCUIT* Not necessary with CMOS output products.■FEATURESDetect Voltage Range: 1.6V ~ 5.0V, +2% (100mV increments)Hysteresis Range : V DF x 5%, TYP .(XC6101~XC6107)V DF x 0.1%, TYP .(XC6111~XC6117)Operating Voltage Range : 1.0V ~ 6.0V Detect Voltage Temperature Characteristics : +100ppm/O C (TYP .) Output Configuration : N-channel open drain,CMOSWatchdog Pin : Watchdog inputIf watchdog input maintains ‘H’ or ‘L’ within the watchdog timeout period, a reset signal is output to the RESET output pinManual Reset Pin : When driven ‘H’ to ‘L’levelsignal, the MRB pin voltage asserts forced reset on theoutput pin.Release Delay Time : 1.6sec, 400msec, 200msec,100msec, 50msec, 25msec, 3.13msec (TYP .) can be selectable.Watchdog Timeout Period : 1.6sec, 400msec, 200msec,100msec, 50msec,6.25msec (TYP .) can be selectable.■TYPICAL PERFORMANCE CHARACTERISTICS ●Supply Current vs. Input Voltage* ‘x’ represents both ‘0’ and ‘1’. (ex. XC61x1⇒XC6101 and XC6111)2/26XC6101~XC6107, XC6111~XC6117 SeriesPIN NUMBERXC6101, XC6102 XC6103 XC6104, XC6105XC6106, XC6107XC6111, XC6112 XC6113 XC6114, XC6115XC6116, XC6117SOT-25 USP-6C SOT-25 USP-6C SOT-25 USP-6C SOT-25USP-6CPIN NAMEFUNCTION1 4 - - 1 4 1 4 R ESETB Reset Output(V DFL : Low Level When Detected)2 5 2 5 2 5 2 5 V SSGround3 2 3 2 - -4 1 M RB ManualReset 4 1 4 1 4 1 - - WDWatchdog5 6 5 6 5 6 5 6 V IN Power Input - - 1 4 3 2 3 2 RESETReset Output (V DFH: High Level When Detected)■PIN CONFIGURATION SOT-25 (TOP VIEW)MRBV IN WD RESETBV SSMRBWD RESETV SSV IN RESETWD RESETBV SS V IN SOT-25 (TOP VIEW)RESETMRB RESETBV SS V IN SOT-25 (TOP VIEW) ■PIN ASSIGNMENT●SOT-25XC6101, XC6102 SeriesXC6111, XC6112 SeriesSOT-25 (TOP VIEW)XC6103 & XC6113 SeriesXC6104, XC6105 Series XC6114, XC6115 SeriesXC6106, XC6107 Series XC6116, XC6117 Series●USP-6CXC6101, XC6102 Series XC6111, XC6112 SeriesXC6103 & XC6113 SeriesXC6104, XC6105 Series XC6114, XC6115 SeriesXC6106, XC6107 Series XC6116, XC6117 SeriesUSP-6C (BOTTOM VIEW)USP-6C (BOTTOM VIEW)USP-6C (BOTTOM VIEW)USP-6C (BOTTOM VIEW)* The dissipation pad for the USP-6C package should be solder-plated in recommended mount pattern and metal masking so as to enhance mounting strength and heat release. If the pad needs to be connected to other pins, it should be connected to the V SS pin.3/26XC6101 ~ XC6107, XC6111~ XC6117SeriesRESET OUTPUTSERIES WATCHDOGMANUAL RESET V DFL (RESETB)V DFH (RESET)XC6101 XC6111 Available Available CMOS - XC6102XC6112AvailableAvailableN-channel open drain-XC6103 XC6113 Available Available - CMOS XC6104 XC6114 Available Not AvailableCMOS CMOS XC6105 XC6115 Available Not Available N-channel open drain CMOS XC6106 XC6116 Not Available AvailableCMOSCMOS XC6107XC6117Not AvailableAvailableN-channel open drainCMOSDESIGNATORDESCRIPTIONSYMBOLDESCRIPTION0 : V DF x 5% (TYP .) with hysteresis ① Hysteresis Range1 : V DF x 0.1% (TYP .) without hysteresis② Functions and Type of Reset Output1 ~ 7: Watchdog and manual functions, and reset output type as per Selection Guide in the above chartA : 3.13msec (TYP .)B : 25msec (TYP .) C: 50msec (TYP .) D : 100msec (TYP .) E : 200msec (TYP .) F : 400msec (TYP .) ③ Release Delay Time * H : 1.6sec (TYP .)0 : No WD timeout period forXC6106, XC6107, XC6116, XC6117 Series 1: 6.25msec (TYP .) 2 : 50msec (TYP .) 3 : 100msec (TYP .) 4 : 200msec (TYP .) 5 : 400msec (TYP .) ④ Watchdog Timeout Period6: 1.6sec (TYP .) ⑤⑥ Detect Voltage 16 ~ 50: Detect voltageex.) 4.5V: ⑤⇒4, ⑥⇒5M : SOT-25 ⑦ Package E : USP-6C R : Embossed tape, standard feed ⑧ Device OrientationL: Embossed tape, reverse feed* Please set the release delay time shorter than or equal to the watchdog timeout period. ex.) XC6101D427MR or XC6101D327MR■PRODUCT CLASSIFICATION ●Selection Guide ●Ordering Information XC61①②③④⑤⑥⑦⑧4/26XC6101~XC6107, XC6111~XC6117 Series■PACKAGING INFORMATION●SOT-25●USP-6C5/26XC6101 ~ XC6107, XC6111~ XC6117Series④ Represents production lot number0 to 9 and A to Z and inverted 0 to 9 and A to Z repeated. (G, I, J, O, Q, W expected.) * ‘X’ represents both ‘0’ and ‘1’. (ex. XC61X1⇒XC6101 and XC6111)■MARKING RULE●SOT-25①②③④SOT-25 (TOP VIEW)6/26XC6101~XC6107, XC6111~XC6117 Series① Represents product series② Represents release delay time MARK RELEASE DELAY TIME PRODUCT SERIES A 3.13msec XC61XxAxxxxx B 25msec XC61XxBxxxxx C 50msec XC61XxCxxxxx D 100msec XC61XxDxxxxx E 200msec XC61XxExxxxx F 400msec XC61XxFxxxxx H 1.6sec XC61XxHxxxxx③ Represents watchdog timeout period MARK WATCHDOG TIMEOUT PERIOD PRODUCT SERIES 0 XC61X6, XC61X7 series XC61Xxx0xxxx 1 6.25msec XC61Xxx1xxxx 2 50msec XC61Xxx2xxxx 3 100msec XC61Xxx3xxxx 4 200msec XC61Xxx4xxxx 5 400msec XC61Xxx5xxxx 6 1.6sec XC61Xxx6xxxx④⑤ Represents detect voltage MARK④ ⑤DETECT VOLTAGE (V)PRODUCT SERIES3 3 3.3 XC61Xxxx33xx 5 0 5.0XC61Xxxx50xx⑥ Represents production lot number0 to 9 and A to Z repeated. (G, I, J, O, Q, W excepted.)* No character inversion used. ** ‘X’ represents both ‘0’ and ‘1’. (ex. XC61X1⇒XC6101 and XC6111)MARK PRODUCT SERIES MARK PRODUCT SERIES 3 XC6101xxxxxx 8 XC6111xxxxxx 4 XC6102xxxxxx 9 XC6112xxxxxx 5 XC6103xxxxxx A XC6113xxxxxx 6 XC6104xxxxxx B XC6114xxxxxx 7 XC6105xxxxxx C XC6115xxxxxx 3 XC6106xxxxxx 8 XC6116xxxxxx 4 XC6107xxxxxx 9 XC6117xxxxxx■MARKING RULE (Continued)●USP-6CUSP-6C (TOP VIEW)7/26XC6101 ~ XC6107, XC6111~ XC6117Series■BLOCK DIAGRAMS●XC6101, XC6111 Series●XC6102, XC6112 Series●XC6103, XC6113 Series8/26XC6101~XC6107, XC6111~XC6117 Series■BLOCK DIAGRAMS (Continued)●XC6107, XC6117 Series●XC6106, XC6116 Series●XC6105, XC6115 Series●XC6104, XC6114 Series9/26XC6101 ~ XC6107, XC6111~ XC6117SeriesPARAMETERSYMBOL RATINGSUNITSV INV SS -0.3 ~ 7.0 VM RBV SS -0.3 ~ V IN +0.3 VInput Voltage WD V SS -0.3 ~ 7.0V Output Current I OUT 20 mACMOS Output RESETB/RESET V SS -0.3 ~ V IN +0.3Output Voltage N-ch Open Drain Output RESETB V SS -0.3 ~ 7.0VSOT-25 250Power Dissipation USP-6C Pd 100mWOperational Temperature Range Topr -40 ~ +85 OCStorage Temperature Range Tstg -40 ~ +125 OC■ABSOLUTE MAXIMUM RATINGSTa = 25O C10/26XC6101~XC6107, XC6111~XC6117 SeriesNOTE:*1: XC6101~XC6107 (with hysteresis) *2: XC6111~XC6117 (without hysteresis)*3: ‘X’ represents both ‘0’ and ‘1’. (ex. XC61X1⇒XC6101 and XC6111) *4: V DF(T): Setting detect voltage*5: If only “V DF ” is indicated, it represents both V DFL (low when detected) and V DFH (high when detected).PARAMETERSYMBOLCONDITIONSMIN.TYP .MAX. UNITS CIRCUITDetect Voltage V DFL V DFHV DF(T)× 0.98V DF(T) V DF(T)× 1.02 V 1 Hysteresis Range XC6101~XC6107 (*1) V HYS V DF × 0.02V DF × 0.05 V DF× 0.08 V 1Hysteresis Range XC6111~XC6117 (*2) V HYS 0 V DF × 0.001 V DFx 0.01V 1V IN =V DF(T)×0.9V - 5 11 V IN =V DF(T)×1.1V- 10 16 XC61X1/XC61X2/XC61X3XC61X4/XC61X5 (*3)(The MRB & the WD Pin: No connection) V IN =6.0V - 1218 V IN =V DF(T)×0.9V - 4 10 V IN =V DF(T)×1.1V - 8 14 Supply Current I SS XC61X6/XC61X7 (*3)(The MRB Pin: No connection)V IN = 6.0V - 1016 µA 2Operating Voltage V IN 1.0 - 6.0 V 1VIN = 1.0V 0.15 0.5 -V IN =2.0V (V DFL(T)> 2.0V) 2.0 2.5 - V IN =3.0V (V DFL(T) >3.0V) 3.0 3.5 -N-ch.V DS = 0.5V V IN =4.0V (V DFL(T) >4.0V) 3.5 4.0 - 3 V DFL Output Current (RESETB) I RBOUTCMOS,P-chV DS = 0.5V V IN = 6.0V - - 1.1 -0.8 mA 4 N-chV DS = 0.5VV IN =6.0V 4.4 4.9 - 3V IN =1.0V - - 0.08 - 0.02 V IN =2.0V (V DFH(T)> 2.0V)- - 0.50 - 0.30 V IN =3.0V (V DFH(T)>3.0V)- - 0.75 - 0.55V DFHOutput Current (RESET) I ROUT P-ch. V DS = 0.5V V IN =4.0V (V DFH(T)>4.0V)- - 0.95 - 0.75 mA 4Temperature Characteristics △V DF / △Topr ・V DF -40OC < Topr < 85 O C - +100 - ppm / O C12 3.13 5 13 25 3825 50 75 60 100 140 120 200 280 240 400 560Release Delay Time(V DF <1.8V)T DR Time until V IN is increased from1.0V to2.0Vand attains to the release time level,and the Reset output pin inverts.960 1600 2240 ms 5 2 3.13 5 13 25 38 25 50 7560 100 140 120 200 280 240 400 560 Release Delay Time(V DF >1.9V)T DRTime until V IN is increased from1.0V to (V DF x1.1V) and attains to the releasetime level,and the Reset output pin inverts. 960 1600 2240ms 5 Detect Delay Time T DFTime until V IN is decreased from 6.0V to 1.0V and attains to the detect voltage level, and the Reset output pin detectswhile the WD pin left opened.- 3 30 µs 5V DFL /V DFH CMOS Output Leak CurrentI LEAK V IN =6.0V, RESETB=6.0V (V DFL ) V IN =6.0V, RESET=0V (V DFH )- 0.01 - µA 3V DFL N-ch Open DrainOutput Leak CurrentI LEAKV IN =6.0V, RESETB=6.0V-0.010.10µA 3■ELECTRICAL CHARACTERISTICS●XC6101~XC6107, XC6111~XC6117 SeriesTa = 25O CSeriesPARAMETERSYMBOL CONDITIONS MIN.TYP . MAX. UNITS CIRCUIT3.13 6.25 9.38 25 50 7560 100 140 120 200 280240 400 560 Watchdog Timeout Period (V DF <1.8V)T WDTime until V IN increases form1.0V to2.0V andthe Reset output pin is released to go into the detection state. (WD=V SS )960 1600 2240 ms 6 3.13 6.25 9.38 25 50 75 60 100 140 120 200 280240 400 560 Watchdog Timeout Period (V DF >1.9V)T WDTime until V IN increases form1.0V to (V DF x1.1V)and the Reset output pin is released to go into the detection state. (WD=V SS )960 1600 2240 ms 6 WatchdogMinimum Pulse Width T WDIN V IN =6.0V,Apply pulse from 6.0V to 0Vto the WD pin. 300 - - ns 7 Watchdog High Level VoltageV WDH V IN =V DF x 1.1V ~ 6.0V V IN x 0.7- 6 V 7 Watchdog Low Level Voltage V WDL V IN =V DF x 1.1V ~ 6.0V0 - V IN x 0.3 V 7 V IN =6.0V, V WD =6.0V (Avg. when peak )- 12 19Watchdog Input Current I WD V IN =6.0V, V WD =0V (Avg. when peak) - 19 -12 -µA 8 Watchdog Input ResistanceR WDV IN =6.0V, V WD =0V, R WD =V IN / |I WD |315500880k Ω8PARAMETERSYMBOL CONDITIONS MIN.TYP . MAX.UNITS CIRCUITMRBHigh Level VoltageV MRH V IN =V DF x1.1V ~ 6.0V 1.4 - V IN 9MRBLow Level VoltageV MRL V IN =V DF x1.1V ~ 6.0V-0.35 V9MRBPull-up Resistance R MR V IN =6.0V, MRB=0V, R MR =V IN / |I MRB | 1.6 2.4 3.0 M Ω 10 MRB Minimum Pulse Width (*3) XC6101~XC6105 XC6111~XC6115 T MRINV IN =6.0V,Apply pulse from 6.0V to 0V tothe MRB pin 2.8 - -MRB Minimum Pulse Width (*4) XC6106, XC6107 XC6116, XC6117T MRIN V IN =6.0V,Apply pulse from 6.0V to 0V tothe MRB pin1.2 - -µs11●XC6101 ~ XC6103, XC6106 ~ XC6107, XC6111 ~ XC6113, XC6116 ~ XC6117 Series NOTE:*1: V DF(T): Setting detect voltage *2: If only “V DF ” is indicated, it represents both V DFL (low when detected) and V DFH (high when detected). *3: Watchdog function is available. *4: Watchdog function is not available.Ta = 25O CTa = 25O C ■ELECTRICAL CHARACTERISTICS (Continued)●XC6101~XC6105, XC6111~XC6115 Series■OPERATIONAL EXPLANATIONThe XC6101~XC6107, XC6111~XC6117 series compare, using the error amplifier, the voltage of the internal voltage reference source with the voltage divided by R1, R2 and R3 connected to the V IN pin. The resulting output signal from the error amplifier activates the watchdog logic, manual reset logic, delay circuit and the output driver. When the V IN pin voltage gradually falls and finally reaches the detect voltage, the RESETB pin output goes from high to low in the case of the V DFL type ICs, and the RESET pin output goes from low to high in the case of the V DFH type ICs.<RESETB / RESET Pin Output Signal>* V DFL (RESETB) type - output signal: Low when detected.The RESETB pin output goes from high to low whenever the V IN pin voltage falls below the detect voltage, or whenever the MRB pin is driven from high to low. The RESETB pin remains low for the release delay time (T DR) after the V IN pin voltage reaches the release voltage. If neither rising nor falling signals are applied to the WD pin within the watchdog timeout period, the RESETB pin output remains low for the release delay time (T DR), and thereafter the RESET pin outputs high level signal. * V DFH (RESET) type – output signal: High when detected.The RESET pin output goes from low to high whenever the V IN pin voltage falls below the detect voltage, or whenever the MRB pin is driven from high to low. The RESET pin remains high for the release delay time (T DR) after the V IN pin voltage reaches the release voltage. If neither rising nor falling signals are applied to the WD pin within the watchdog timeout period, the V OUT pin output remains high for the release delay time (T DR), and thereafter the RESET pin outputs low level signal.<Hysteresis>When the internal comparator output is high, the NMOS transistor connected in parallel to R3 is turned ON, activating the hysteresis circuit. The difference between the release and detect voltages represents the hysteresis range, as shown by the following calculations:V DF (detect voltage) = (R1+R2+R3) x Vref(R2+R3)V DR (release voltage) = (R1+R2) x Vref(R2)V HYS (hysteresis range)=V DR-V DF (V)V DR > V DF* Detect voltage (V DF) includes conditions of both V DFL (low when detected) and V DFH (high when detected).* Please refer to the block diagrams for R1, R2, R3 and Vref.Hysteresis range is selectable from V DF x 0.05V (XC6101~XC6107) or V DF x 0.001V (XC6111~XC6117).<Watchdog (WD) Pin>The XC6101~XC6107, XC6111~XC6117 series use a watchdog timer to detect malfunction or “runaway” of the microprocessor. If neither rising nor falling signals are applied from the microprocessor within the watchdog timeout period, the RESETB/RESET pin output maintains the detection state for the release delay time (T DR), and thereafter the RESET/RESETB pin output returns to the release state (Please refer to the FUNCTION CHART). The timer in the watchdog is then restarted. Six watchdog timeout period settings are available in 1.6sec, 400msec, 200msec, 100msec, 50msec, 6.25msec.<MRB Pin>Using the MRB pin input, the RESET/RESETB pin signal can be forced to the detection state. When the MRB pin is driven from high to low, the RESETB pin output goes from high to low in the case of the V DFL type ICs, and the RESET pin output goes from low to high in the case of the V DFH type. Even after the MRB pin is driven back high, the RESET/RESETB pin output maintains the detection state for the release delay time (T DR). Since the MRB pin is internally pulled up to the V IN pin voltage level, leave the MRB pin open if unused (Please refer to the FUNCTION CHART). A diode, which is an input protection element, is connected between the MRB pin and V IN pin. Therefore, if the MRB pin is applied voltage that exceeds V IN, the current will flow to V IN through the diode. Please use this IC within the stated maximum ratings (V SS -0.3 ~ V IN+0.3) on the MRB pin.<Release Delay Time>Release delay time (T DR) is the time that elapses from when the V IN pin reaches the release voltage, or when the watchdog timeout period expires with no rising signal applied to the WD pin, until the RESET/RESETB pin output is released from the detection state. Seven release delay time (T DR) watchdog timeout period settings are available in 1.6sec, 400msec, 200msec, 100msec, 50msec, 25msec, 3.13msec.<Detect Delay Time>Detect Delay Time (T DF) is the time that elapses from when the V IN pin voltage falls to the detect voltage until the RESET/ RESETB pin output goes into the detection state.Series■TIMING CHARTS●CMOS Output●T DF (CMOS Output)VINVDFL LevelGNDVIN Level VDFL Level GNDVIN x 0.1V■NOTES ON USE1. Please use this IC within the stated maximum ratings. Operation beyond these limits may cause degrading or permanent damage to the device.2. When a resistor is connected between the V IN pin and the input, the V IN voltage drops while the IC is operating and a malfunction may occur as a result of the IC’s through current. For the CMOS output products, the V IN voltage drops while the IC is operating and malfunction may occur as a result of the IC’s output current. Please be careful with using the XC6111~XC6117 series (without hysteresis).3. In order to stabilize the IC’s operations, please ensure that the V IN pin’s input frequency’s rise and fall times are more than 1 µ sec/V.4. Noise at the power supply may cause a malfunction of the watchdog operation or the circuit. In such case, please strength the line between V IN and the GND pin and connect about 0.22µF of a capacitor between the V IN pin and the GND pin.5. Protecting against a malfunction while the watchdog time out period, an ignoring time (no reaction time) occurs to the rise and fall times. Referring to the figure below, the ignoring time (no reaction time) lasts for 900µsec at maximum.GNDGNDGNDVIN Pin Wave FormWD Pin Wave FormRESETB Pin Wave Form (VDFL)SeriesPIN NAMELOGIC CONDITIONSH V IN >V DF +V HYS V IN L V IN <V DF H MRB>1.40V MRBL MRB<0.35V H When keeping W D >V WDH more than T WD L When keeping W D <V WDL more than T WD L → H V WDL → V WDH , T WDIN >300nsec WDH → L V WDH →V WDH , T WDIN >300nsecV IN MRB WD RESETB (*2) H HH LRepeat detect and release (H →L →H)H OpenH L → HH H or Open H → L H HLL *1 LV IN MRB WD RESETB (*3) H HH LRepeat detect and release (L →H →L)H OpenH L → HH H or Open H → L L HLL *1 HV IN WD RESETB (*2) RESET (*3) H HH L Repeat detect and release (H →L →H)Repeat detect and release (L →H →L)H OpenH L → HH H → L H L HL*1 L HV IN MRB RESETB (*2)RESET (*3)H H or Open H LH LL L H■PIN LOGIC CONDITIONSNOTE:*1: If only “V DF ” is indicated, it represents both V DFL (low when detected) and V DFH (high when detected).*2: For the details of each parameter, please see the electrical characteristics. V DF : Detect VoltageV HYS : Hysteresis RangeV WDH : WD High Level Voltage V WDL: WD Low Level Voltage T WDIN : WD Pulse Width T WD : WD Timeout Period■FUNCTION CHART●XC6103/XC61113 Series●XC6104/XC61114, XC6105/XC6115 Series●XC6106/XC61116, XC6107/XC6117 Series●XC6101/XC61111, XC6102/6112 Series*1: Including all logic of WD (WD=H, L, L →H, H →L, OPEN). *2: When the RESETB is High, the circuit is in the release state. When the RESETB is Low, the circuit is in the detection state. *3: When the RESET is High, the circuit is in the release state. When the RESET is Low, the circuit is in the detection state.■TEST CIRCUITSCircuit 1Circuit 2Circuit 3Circuit 4Series ■TEST CIRCUITS (Continued)Circuit 5Circuit 6Circuit 7■TEST CIRCUITS (Continued)Circuit 8Circuit 9Circuit 10Circuit 11Series■TYPICAL PERFORMANCE CHARACTERISTICS(1.1) Supply Current vs. Input Voltage(1.2) Supply Current vs. Input Voltage■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)(2) Detect, Release Voltage vs. Ambient Temperature(1.2) Supply Current vs. Input Voltage (Continued)Series■TYPICAL PERFORMANCE CHARACTERISTICS (Continued) (3-1) Output Voltage vs. Input Voltage (V DFL ) (3.1) Detect, Release Voltage vs. Input Voltage (V DFL )(3.2) Detect, Release Voltage vs. Input Voltage (V DFH )■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)(4) N-ch Driver Output Current vs. V DSSeries(6) P-ch Driver Output Current vs. Input Voltage 1■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)(8) Release Delay Time vs. Ambient Temperature(7) P-ch Driver Output Current vs. Input Voltage 2■TYPICAL PERFORMANCE CHARACTERISTICS (Continued) (10) Release Delay Time vs. Input Voltage(11) Watchdog Timeout Period vs. Input VoltageSeries■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)(14) MRB Low Level Voltage vs. Ambient Temperature(15) MRB High Level Voltage vs. Ambient Temperature* ‘X’ represents both ‘0’ and ‘1’. (ex. XC61X1⇒XC6101 and XC6111)。

XC6112F022资料

1/26XC6101_07_XC6111_17 ETR0207_009Preliminary◆CMOS Voltage Detector◆Manual Reset Input ◆Watchdog Functions ◆Built-in Delay Circuit ◆Detect Voltage Range: 1.6~5.0V, ± 2% ◆Reset Function is Selectable V DFL (Low When Detected) V DFH (High When Detected)■GENERAL DESCRIPTION The XC6101~XC6107, XC6111~XC6117 series aregroups of high-precision, low current consumption voltage detectors with manual reset input function and watchdog functions incorporating CMOS process technology. The series consist of a reference voltage source, delay circuit, comparator, and output driver.With the built-in delay circuit, the XC6101 ~ XC6107, XC6111 ~ XC6117 series’ ICs do not require any external components to output signals with release delay time. Moreover, with the manual reset function, reset can be asserted at any time. The ICs produce two types of output; V DFL (low when detected) and V DFH (high when detected).With the XC6101 ~ XC6105, XC6111 ~ XC6115 series’ ICs, the WD pin can be left open if the watchdog function is not used. Whenever the watchdog pin is opened, the internal counter clears before the watchdog timeout occurs. Since the manual reset pin is internally pulled up to the V IN pin voltage level, the ICs can be used with the manual reset pin left unconnected if the pin is unused.The detect voltages are internally fixed 1.6V ~ 5.0V in increments of 100mV, using laser trimming technology. Six watchdog timeout period settings are available in a range from 6.25msec to 1.6sec. Seven release delay time 1 are available in a range from 3.13msec to 1.6sec.■APPLICATIONS●Microprocessor reset circuits●Memory battery backup circuits ●System power-on reset circuits ●Power failure detection■TYPICAL APPLICATION CIRCUIT* Not necessary with CMOS output products.■FEATURESDetect Voltage Range: 1.6V ~ 5.0V, +2% (100mV increments)Hysteresis Range : V DF x 5%, TYP .(XC6101~XC6107)V DF x 0.1%, TYP .(XC6111~XC6117)Operating Voltage Range : 1.0V ~ 6.0V Detect Voltage Temperature Characteristics : +100ppm/O C (TYP .) Output Configuration : N-channel open drain,CMOSWatchdog Pin : Watchdog inputIf watchdog input maintains ‘H’ or ‘L’ within the watchdog timeout period, a reset signal is output to the RESET output pinManual Reset Pin : When driven ‘H’ to ‘L’levelsignal, the MRB pin voltage asserts forced reset on theoutput pin.Release Delay Time : 1.6sec, 400msec, 200msec,100msec, 50msec, 25msec, 3.13msec (TYP .) can be selectable.Watchdog Timeout Period : 1.6sec, 400msec, 200msec,100msec, 50msec,6.25msec (TYP .) can be selectable.■TYPICAL PERFORMANCE CHARACTERISTICS ●Supply Current vs. Input Voltage* ‘x’ represents both ‘0’ and ‘1’. (ex. XC61x1⇒XC6101 and XC6111)2/26XC6101~XC6107, XC6111~XC6117 SeriesPIN NUMBERXC6101, XC6102 XC6103 XC6104, XC6105XC6106, XC6107XC6111, XC6112 XC6113 XC6114, XC6115XC6116, XC6117SOT-25 USP-6C SOT-25 USP-6C SOT-25 USP-6C SOT-25USP-6CPIN NAMEFUNCTION1 4 - - 1 4 1 4 R ESETB Reset Output(V DFL : Low Level When Detected)2 5 2 5 2 5 2 5 V SSGround3 2 3 2 - -4 1 M RB ManualReset 4 1 4 1 4 1 - - WDWatchdog5 6 5 6 5 6 5 6 V IN Power Input - - 1 4 3 2 3 2 RESETReset Output (V DFH: High Level When Detected)■PIN CONFIGURATION SOT-25 (TOP VIEW)MRBV IN WD RESETBV SSMRBWD RESETV SSV IN RESETWD RESETBV SS V IN SOT-25 (TOP VIEW)RESETMRB RESETBV SS V IN SOT-25 (TOP VIEW) ■PIN ASSIGNMENT●SOT-25XC6101, XC6102 SeriesXC6111, XC6112 SeriesSOT-25 (TOP VIEW)XC6103 & XC6113 SeriesXC6104, XC6105 Series XC6114, XC6115 SeriesXC6106, XC6107 Series XC6116, XC6117 Series●USP-6CXC6101, XC6102 Series XC6111, XC6112 SeriesXC6103 & XC6113 SeriesXC6104, XC6105 Series XC6114, XC6115 SeriesXC6106, XC6107 Series XC6116, XC6117 SeriesUSP-6C (BOTTOM VIEW)USP-6C (BOTTOM VIEW)USP-6C (BOTTOM VIEW)USP-6C (BOTTOM VIEW)* The dissipation pad for the USP-6C package should be solder-plated in recommended mount pattern and metal masking so as to enhance mounting strength and heat release. If the pad needs to be connected to other pins, it should be connected to the V SS pin.3/26XC6101 ~ XC6107, XC6111~ XC6117SeriesRESET OUTPUTSERIES WATCHDOGMANUAL RESET V DFL (RESETB)V DFH (RESET)XC6101 XC6111 Available Available CMOS - XC6102XC6112AvailableAvailableN-channel open drain-XC6103 XC6113 Available Available - CMOS XC6104 XC6114 Available Not AvailableCMOS CMOS XC6105 XC6115 Available Not Available N-channel open drain CMOS XC6106 XC6116 Not Available AvailableCMOSCMOS XC6107XC6117Not AvailableAvailableN-channel open drainCMOSDESIGNATORDESCRIPTIONSYMBOLDESCRIPTION0 : V DF x 5% (TYP .) with hysteresis ① Hysteresis Range1 : V DF x 0.1% (TYP .) without hysteresis② Functions and Type of Reset Output1 ~ 7: Watchdog and manual functions, and reset output type as per Selection Guide in the above chartA : 3.13msec (TYP .)B : 25msec (TYP .) C: 50msec (TYP .) D : 100msec (TYP .) E : 200msec (TYP .) F : 400msec (TYP .) ③ Release Delay Time * H : 1.6sec (TYP .)0 : No WD timeout period forXC6106, XC6107, XC6116, XC6117 Series 1: 6.25msec (TYP .) 2 : 50msec (TYP .) 3 : 100msec (TYP .) 4 : 200msec (TYP .) 5 : 400msec (TYP .) ④ Watchdog Timeout Period6: 1.6sec (TYP .) ⑤⑥ Detect Voltage 16 ~ 50: Detect voltageex.) 4.5V: ⑤⇒4, ⑥⇒5M : SOT-25 ⑦ Package E : USP-6C R : Embossed tape, standard feed ⑧ Device OrientationL: Embossed tape, reverse feed* Please set the release delay time shorter than or equal to the watchdog timeout period. ex.) XC6101D427MR or XC6101D327MR■PRODUCT CLASSIFICATION ●Selection Guide ●Ordering Information XC61①②③④⑤⑥⑦⑧4/26XC6101~XC6107, XC6111~XC6117 Series■PACKAGING INFORMATION●SOT-25●USP-6C5/26XC6101 ~ XC6107, XC6111~ XC6117Series④ Represents production lot number0 to 9 and A to Z and inverted 0 to 9 and A to Z repeated. (G, I, J, O, Q, W expected.) * ‘X’ represents both ‘0’ and ‘1’. (ex. XC61X1⇒XC6101 and XC6111)■MARKING RULE●SOT-25①②③④SOT-25 (TOP VIEW)6/26XC6101~XC6107, XC6111~XC6117 Series① Represents product series② Represents release delay time MARK RELEASE DELAY TIME PRODUCT SERIES A 3.13msec XC61XxAxxxxx B 25msec XC61XxBxxxxx C 50msec XC61XxCxxxxx D 100msec XC61XxDxxxxx E 200msec XC61XxExxxxx F 400msec XC61XxFxxxxx H 1.6sec XC61XxHxxxxx③ Represents watchdog timeout period MARK WATCHDOG TIMEOUT PERIOD PRODUCT SERIES 0 XC61X6, XC61X7 series XC61Xxx0xxxx 1 6.25msec XC61Xxx1xxxx 2 50msec XC61Xxx2xxxx 3 100msec XC61Xxx3xxxx 4 200msec XC61Xxx4xxxx 5 400msec XC61Xxx5xxxx 6 1.6sec XC61Xxx6xxxx④⑤ Represents detect voltage MARK④ ⑤DETECT VOLTAGE (V)PRODUCT SERIES3 3 3.3 XC61Xxxx33xx 5 0 5.0XC61Xxxx50xx⑥ Represents production lot number0 to 9 and A to Z repeated. (G, I, J, O, Q, W excepted.)* No character inversion used. ** ‘X’ represents both ‘0’ and ‘1’. (ex. XC61X1⇒XC6101 and XC6111)MARK PRODUCT SERIES MARK PRODUCT SERIES 3 XC6101xxxxxx 8 XC6111xxxxxx 4 XC6102xxxxxx 9 XC6112xxxxxx 5 XC6103xxxxxx A XC6113xxxxxx 6 XC6104xxxxxx B XC6114xxxxxx 7 XC6105xxxxxx C XC6115xxxxxx 3 XC6106xxxxxx 8 XC6116xxxxxx 4 XC6107xxxxxx 9 XC6117xxxxxx■MARKING RULE (Continued)●USP-6CUSP-6C (TOP VIEW)7/26XC6101 ~ XC6107, XC6111~ XC6117Series■BLOCK DIAGRAMS●XC6101, XC6111 Series●XC6102, XC6112 Series●XC6103, XC6113 Series8/26XC6101~XC6107, XC6111~XC6117 Series■BLOCK DIAGRAMS (Continued)●XC6107, XC6117 Series●XC6106, XC6116 Series●XC6105, XC6115 Series●XC6104, XC6114 Series9/26XC6101 ~ XC6107, XC6111~ XC6117SeriesPARAMETERSYMBOL RATINGSUNITSV INV SS -0.3 ~ 7.0 VM RBV SS -0.3 ~ V IN +0.3 VInput Voltage WD V SS -0.3 ~ 7.0V Output Current I OUT 20 mACMOS Output RESETB/RESET V SS -0.3 ~ V IN +0.3Output Voltage N-ch Open Drain Output RESETB V SS -0.3 ~ 7.0VSOT-25 250Power Dissipation USP-6C Pd 100mWOperational Temperature Range Topr -40 ~ +85 OCStorage Temperature Range Tstg -40 ~ +125 OC■ABSOLUTE MAXIMUM RATINGSTa = 25O C10/26XC6101~XC6107, XC6111~XC6117 SeriesNOTE:*1: XC6101~XC6107 (with hysteresis) *2: XC6111~XC6117 (without hysteresis)*3: ‘X’ represents both ‘0’ and ‘1’. (ex. XC61X1⇒XC6101 and XC6111) *4: V DF(T): Setting detect voltage*5: If only “V DF ” is indicated, it represents both V DFL (low when detected) and V DFH (high when detected).PARAMETERSYMBOLCONDITIONSMIN.TYP .MAX. UNITS CIRCUITDetect Voltage V DFL V DFHV DF(T)× 0.98V DF(T) V DF(T)× 1.02 V 1 Hysteresis Range XC6101~XC6107 (*1) V HYS V DF × 0.02V DF × 0.05 V DF× 0.08 V 1Hysteresis Range XC6111~XC6117 (*2) V HYS 0 V DF × 0.001 V DFx 0.01V 1V IN =V DF(T)×0.9V - 5 11 V IN =V DF(T)×1.1V- 10 16 XC61X1/XC61X2/XC61X3XC61X4/XC61X5 (*3)(The MRB & the WD Pin: No connection) V IN =6.0V - 1218 V IN =V DF(T)×0.9V - 4 10 V IN =V DF(T)×1.1V - 8 14 Supply Current I SS XC61X6/XC61X7 (*3)(The MRB Pin: No connection)V IN = 6.0V - 1016 µA 2Operating Voltage V IN 1.0 - 6.0 V 1VIN = 1.0V 0.15 0.5 -V IN =2.0V (V DFL(T)> 2.0V) 2.0 2.5 - V IN =3.0V (V DFL(T) >3.0V) 3.0 3.5 -N-ch.V DS = 0.5V V IN =4.0V (V DFL(T) >4.0V) 3.5 4.0 - 3 V DFL Output Current (RESETB) I RBOUTCMOS,P-chV DS = 0.5V V IN = 6.0V - - 1.1 -0.8 mA 4 N-chV DS = 0.5VV IN =6.0V 4.4 4.9 - 3V IN =1.0V - - 0.08 - 0.02 V IN =2.0V (V DFH(T)> 2.0V)- - 0.50 - 0.30 V IN =3.0V (V DFH(T)>3.0V)- - 0.75 - 0.55V DFHOutput Current (RESET) I ROUT P-ch. V DS = 0.5V V IN =4.0V (V DFH(T)>4.0V)- - 0.95 - 0.75 mA 4Temperature Characteristics △V DF / △Topr ・V DF -40OC < Topr < 85 O C - +100 - ppm / O C12 3.13 5 13 25 3825 50 75 60 100 140 120 200 280 240 400 560Release Delay Time(V DF <1.8V)T DR Time until V IN is increased from1.0V to2.0Vand attains to the release time level,and the Reset output pin inverts.960 1600 2240 ms 5 2 3.13 5 13 25 38 25 50 7560 100 140 120 200 280 240 400 560 Release Delay Time(V DF >1.9V)T DRTime until V IN is increased from1.0V to (V DF x1.1V) and attains to the releasetime level,and the Reset output pin inverts. 960 1600 2240ms 5 Detect Delay Time T DFTime until V IN is decreased from 6.0V to 1.0V and attains to the detect voltage level, and the Reset output pin detectswhile the WD pin left opened.- 3 30 µs 5V DFL /V DFH CMOS Output Leak CurrentI LEAK V IN =6.0V, RESETB=6.0V (V DFL ) V IN =6.0V, RESET=0V (V DFH )- 0.01 - µA 3V DFL N-ch Open DrainOutput Leak CurrentI LEAKV IN =6.0V, RESETB=6.0V-0.010.10µA 3■ELECTRICAL CHARACTERISTICS●XC6101~XC6107, XC6111~XC6117 SeriesTa = 25O CSeriesPARAMETERSYMBOL CONDITIONS MIN.TYP . MAX. UNITS CIRCUIT3.13 6.25 9.38 25 50 7560 100 140 120 200 280240 400 560 Watchdog Timeout Period (V DF <1.8V)T WDTime until V IN increases form1.0V to2.0V andthe Reset output pin is released to go into the detection state. (WD=V SS )960 1600 2240 ms 6 3.13 6.25 9.38 25 50 75 60 100 140 120 200 280240 400 560 Watchdog Timeout Period (V DF >1.9V)T WDTime until V IN increases form1.0V to (V DF x1.1V)and the Reset output pin is released to go into the detection state. (WD=V SS )960 1600 2240 ms 6 WatchdogMinimum Pulse Width T WDIN V IN =6.0V,Apply pulse from 6.0V to 0Vto the WD pin. 300 - - ns 7 Watchdog High Level VoltageV WDH V IN =V DF x 1.1V ~ 6.0V V IN x 0.7- 6 V 7 Watchdog Low Level Voltage V WDL V IN =V DF x 1.1V ~ 6.0V0 - V IN x 0.3 V 7 V IN =6.0V, V WD =6.0V (Avg. when peak )- 12 19Watchdog Input Current I WD V IN =6.0V, V WD =0V (Avg. when peak) - 19 -12 -µA 8 Watchdog Input ResistanceR WDV IN =6.0V, V WD =0V, R WD =V IN / |I WD |315500880k Ω8PARAMETERSYMBOL CONDITIONS MIN.TYP . MAX.UNITS CIRCUITMRBHigh Level VoltageV MRH V IN =V DF x1.1V ~ 6.0V 1.4 - V IN 9MRBLow Level VoltageV MRL V IN =V DF x1.1V ~ 6.0V-0.35 V9MRBPull-up Resistance R MR V IN =6.0V, MRB=0V, R MR =V IN / |I MRB | 1.6 2.4 3.0 M Ω 10 MRB Minimum Pulse Width (*3) XC6101~XC6105 XC6111~XC6115 T MRINV IN =6.0V,Apply pulse from 6.0V to 0V tothe MRB pin 2.8 - -MRB Minimum Pulse Width (*4) XC6106, XC6107 XC6116, XC6117T MRIN V IN =6.0V,Apply pulse from 6.0V to 0V tothe MRB pin1.2 - -µs11●XC6101 ~ XC6103, XC6106 ~ XC6107, XC6111 ~ XC6113, XC6116 ~ XC6117 Series NOTE:*1: V DF(T): Setting detect voltage *2: If only “V DF ” is indicated, it represents both V DFL (low when detected) and V DFH (high when detected). *3: Watchdog function is available. *4: Watchdog function is not available.Ta = 25O CTa = 25O C ■ELECTRICAL CHARACTERISTICS (Continued)●XC6101~XC6105, XC6111~XC6115 Series■OPERATIONAL EXPLANATIONThe XC6101~XC6107, XC6111~XC6117 series compare, using the error amplifier, the voltage of the internal voltage reference source with the voltage divided by R1, R2 and R3 connected to the V IN pin. The resulting output signal from the error amplifier activates the watchdog logic, manual reset logic, delay circuit and the output driver. When the V IN pin voltage gradually falls and finally reaches the detect voltage, the RESETB pin output goes from high to low in the case of the V DFL type ICs, and the RESET pin output goes from low to high in the case of the V DFH type ICs.<RESETB / RESET Pin Output Signal>* V DFL (RESETB) type - output signal: Low when detected.The RESETB pin output goes from high to low whenever the V IN pin voltage falls below the detect voltage, or whenever the MRB pin is driven from high to low. The RESETB pin remains low for the release delay time (T DR) after the V IN pin voltage reaches the release voltage. If neither rising nor falling signals are applied to the WD pin within the watchdog timeout period, the RESETB pin output remains low for the release delay time (T DR), and thereafter the RESET pin outputs high level signal. * V DFH (RESET) type – output signal: High when detected.The RESET pin output goes from low to high whenever the V IN pin voltage falls below the detect voltage, or whenever the MRB pin is driven from high to low. The RESET pin remains high for the release delay time (T DR) after the V IN pin voltage reaches the release voltage. If neither rising nor falling signals are applied to the WD pin within the watchdog timeout period, the V OUT pin output remains high for the release delay time (T DR), and thereafter the RESET pin outputs low level signal.<Hysteresis>When the internal comparator output is high, the NMOS transistor connected in parallel to R3 is turned ON, activating the hysteresis circuit. The difference between the release and detect voltages represents the hysteresis range, as shown by the following calculations:V DF (detect voltage) = (R1+R2+R3) x Vref(R2+R3)V DR (release voltage) = (R1+R2) x Vref(R2)V HYS (hysteresis range)=V DR-V DF (V)V DR > V DF* Detect voltage (V DF) includes conditions of both V DFL (low when detected) and V DFH (high when detected).* Please refer to the block diagrams for R1, R2, R3 and Vref.Hysteresis range is selectable from V DF x 0.05V (XC6101~XC6107) or V DF x 0.001V (XC6111~XC6117).<Watchdog (WD) Pin>The XC6101~XC6107, XC6111~XC6117 series use a watchdog timer to detect malfunction or “runaway” of the microprocessor. If neither rising nor falling signals are applied from the microprocessor within the watchdog timeout period, the RESETB/RESET pin output maintains the detection state for the release delay time (T DR), and thereafter the RESET/RESETB pin output returns to the release state (Please refer to the FUNCTION CHART). The timer in the watchdog is then restarted. Six watchdog timeout period settings are available in 1.6sec, 400msec, 200msec, 100msec, 50msec, 6.25msec.<MRB Pin>Using the MRB pin input, the RESET/RESETB pin signal can be forced to the detection state. When the MRB pin is driven from high to low, the RESETB pin output goes from high to low in the case of the V DFL type ICs, and the RESET pin output goes from low to high in the case of the V DFH type. Even after the MRB pin is driven back high, the RESET/RESETB pin output maintains the detection state for the release delay time (T DR). Since the MRB pin is internally pulled up to the V IN pin voltage level, leave the MRB pin open if unused (Please refer to the FUNCTION CHART). A diode, which is an input protection element, is connected between the MRB pin and V IN pin. Therefore, if the MRB pin is applied voltage that exceeds V IN, the current will flow to V IN through the diode. Please use this IC within the stated maximum ratings (V SS -0.3 ~ V IN+0.3) on the MRB pin.<Release Delay Time>Release delay time (T DR) is the time that elapses from when the V IN pin reaches the release voltage, or when the watchdog timeout period expires with no rising signal applied to the WD pin, until the RESET/RESETB pin output is released from the detection state. Seven release delay time (T DR) watchdog timeout period settings are available in 1.6sec, 400msec, 200msec, 100msec, 50msec, 25msec, 3.13msec.<Detect Delay Time>Detect Delay Time (T DF) is the time that elapses from when the V IN pin voltage falls to the detect voltage until the RESET/ RESETB pin output goes into the detection state.Series■TIMING CHARTS●CMOS Output●T DF (CMOS Output)VINVDFL LevelGNDVIN Level VDFL Level GNDVIN x 0.1V■NOTES ON USE1. Please use this IC within the stated maximum ratings. Operation beyond these limits may cause degrading or permanent damage to the device.2. When a resistor is connected between the V IN pin and the input, the V IN voltage drops while the IC is operating and a malfunction may occur as a result of the IC’s through current. For the CMOS output products, the V IN voltage drops while the IC is operating and malfunction may occur as a result of the IC’s output current. Please be careful with using the XC6111~XC6117 series (without hysteresis).3. In order to stabilize the IC’s operations, please ensure that the V IN pin’s input frequency’s rise and fall times are more than 1 µ sec/V.4. Noise at the power supply may cause a malfunction of the watchdog operation or the circuit. In such case, please strength the line between V IN and the GND pin and connect about 0.22µF of a capacitor between the V IN pin and the GND pin.5. Protecting against a malfunction while the watchdog time out period, an ignoring time (no reaction time) occurs to the rise and fall times. Referring to the figure below, the ignoring time (no reaction time) lasts for 900µsec at maximum.GNDGNDGNDVIN Pin Wave FormWD Pin Wave FormRESETB Pin Wave Form (VDFL)SeriesPIN NAMELOGIC CONDITIONSH V IN >V DF +V HYS V IN L V IN <V DF H MRB>1.40V MRBL MRB<0.35V H When keeping W D >V WDH more than T WD L When keeping W D <V WDL more than T WD L → H V WDL → V WDH , T WDIN >300nsec WDH → L V WDH →V WDH , T WDIN >300nsecV IN MRB WD RESETB (*2) H HH LRepeat detect and release (H →L →H)H OpenH L → HH H or Open H → L H HLL *1 LV IN MRB WD RESETB (*3) H HH LRepeat detect and release (L →H →L)H OpenH L → HH H or Open H → L L HLL *1 HV IN WD RESETB (*2) RESET (*3) H HH L Repeat detect and release (H →L →H)Repeat detect and release (L →H →L)H OpenH L → HH H → L H L HL*1 L HV IN MRB RESETB (*2)RESET (*3)H H or Open H LH LL L H■PIN LOGIC CONDITIONSNOTE:*1: If only “V DF ” is indicated, it represents both V DFL (low when detected) and V DFH (high when detected).*2: For the details of each parameter, please see the electrical characteristics. V DF : Detect VoltageV HYS : Hysteresis RangeV WDH : WD High Level Voltage V WDL: WD Low Level Voltage T WDIN : WD Pulse Width T WD : WD Timeout Period■FUNCTION CHART●XC6103/XC61113 Series●XC6104/XC61114, XC6105/XC6115 Series●XC6106/XC61116, XC6107/XC6117 Series●XC6101/XC61111, XC6102/6112 Series*1: Including all logic of WD (WD=H, L, L →H, H →L, OPEN). *2: When the RESETB is High, the circuit is in the release state. When the RESETB is Low, the circuit is in the detection state. *3: When the RESET is High, the circuit is in the release state. When the RESET is Low, the circuit is in the detection state.■TEST CIRCUITSCircuit 1Circuit 2Circuit 3Circuit 4Series ■TEST CIRCUITS (Continued)Circuit 5Circuit 6Circuit 7■TEST CIRCUITS (Continued)Circuit 8Circuit 9Circuit 10Circuit 11Series■TYPICAL PERFORMANCE CHARACTERISTICS(1.1) Supply Current vs. Input Voltage(1.2) Supply Current vs. Input Voltage■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)(2) Detect, Release Voltage vs. Ambient Temperature(1.2) Supply Current vs. Input Voltage (Continued)Series■TYPICAL PERFORMANCE CHARACTERISTICS (Continued) (3-1) Output Voltage vs. Input Voltage (V DFL ) (3.1) Detect, Release Voltage vs. Input Voltage (V DFL )(3.2) Detect, Release Voltage vs. Input Voltage (V DFH )■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)(4) N-ch Driver Output Current vs. V DSSeries(6) P-ch Driver Output Current vs. Input Voltage 1■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)(8) Release Delay Time vs. Ambient Temperature(7) P-ch Driver Output Current vs. Input Voltage 2■TYPICAL PERFORMANCE CHARACTERISTICS (Continued) (10) Release Delay Time vs. Input Voltage(11) Watchdog Timeout Period vs. Input VoltageSeries■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)(14) MRB Low Level Voltage vs. Ambient Temperature(15) MRB High Level Voltage vs. Ambient Temperature* ‘X’ represents both ‘0’ and ‘1’. (ex. XC61X1⇒XC6101 and XC6111)。

XC6106C016资料

1/26XC6101_07_XC6111_17 ETR0207_009Preliminary◆CMOS Voltage Detector◆Manual Reset Input ◆Watchdog Functions ◆Built-in Delay Circuit ◆Detect Voltage Range: 1.6~5.0V, ± 2% ◆Reset Function is Selectable V DFL (Low When Detected) V DFH (High When Detected)■GENERAL DESCRIPTION The XC6101~XC6107, XC6111~XC6117 series aregroups of high-precision, low current consumption voltage detectors with manual reset input function and watchdog functions incorporating CMOS process technology. The series consist of a reference voltage source, delay circuit, comparator, and output driver.With the built-in delay circuit, the XC6101 ~ XC6107, XC6111 ~ XC6117 series’ ICs do not require any external components to output signals with release delay time. Moreover, with the manual reset function, reset can be asserted at any time. The ICs produce two types of output; V DFL (low when detected) and V DFH (high when detected).With the XC6101 ~ XC6105, XC6111 ~ XC6115 series’ ICs, the WD pin can be left open if the watchdog function is not used. Whenever the watchdog pin is opened, the internal counter clears before the watchdog timeout occurs. Since the manual reset pin is internally pulled up to the V IN pin voltage level, the ICs can be used with the manual reset pin left unconnected if the pin is unused.The detect voltages are internally fixed 1.6V ~ 5.0V in increments of 100mV, using laser trimming technology. Six watchdog timeout period settings are available in a range from 6.25msec to 1.6sec. Seven release delay time 1 are available in a range from 3.13msec to 1.6sec.■APPLICATIONS●Microprocessor reset circuits●Memory battery backup circuits ●System power-on reset circuits ●Power failure detection■TYPICAL APPLICATION CIRCUIT* Not necessary with CMOS output products.■FEATURESDetect Voltage Range: 1.6V ~ 5.0V, +2% (100mV increments)Hysteresis Range : V DF x 5%, TYP .(XC6101~XC6107)V DF x 0.1%, TYP .(XC6111~XC6117)Operating Voltage Range : 1.0V ~ 6.0V Detect Voltage Temperature Characteristics : +100ppm/O C (TYP .) Output Configuration : N-channel open drain,CMOSWatchdog Pin : Watchdog inputIf watchdog input maintains ‘H’ or ‘L’ within the watchdog timeout period, a reset signal is output to the RESET output pinManual Reset Pin : When driven ‘H’ to ‘L’levelsignal, the MRB pin voltage asserts forced reset on theoutput pin.Release Delay Time : 1.6sec, 400msec, 200msec,100msec, 50msec, 25msec, 3.13msec (TYP .) can be selectable.Watchdog Timeout Period : 1.6sec, 400msec, 200msec,100msec, 50msec,6.25msec (TYP .) can be selectable.■TYPICAL PERFORMANCE CHARACTERISTICS ●Supply Current vs. Input Voltage* ‘x’ represents both ‘0’ and ‘1’. (ex. XC61x1⇒XC6101 and XC6111)2/26XC6101~XC6107, XC6111~XC6117 SeriesPIN NUMBERXC6101, XC6102 XC6103 XC6104, XC6105XC6106, XC6107XC6111, XC6112 XC6113 XC6114, XC6115XC6116, XC6117SOT-25 USP-6C SOT-25 USP-6C SOT-25 USP-6C SOT-25USP-6CPIN NAMEFUNCTION1 4 - - 1 4 1 4 R ESETB Reset Output(V DFL : Low Level When Detected)2 5 2 5 2 5 2 5 V SSGround3 2 3 2 - -4 1 M RB ManualReset 4 1 4 1 4 1 - - WDWatchdog5 6 5 6 5 6 5 6 V IN Power Input - - 1 4 3 2 3 2 RESETReset Output (V DFH: High Level When Detected)■PIN CONFIGURATION SOT-25 (TOP VIEW)MRBV IN WD RESETBV SSMRBWD RESETV SSV IN RESETWD RESETBV SS V IN SOT-25 (TOP VIEW)RESETMRB RESETBV SS V IN SOT-25 (TOP VIEW) ■PIN ASSIGNMENT●SOT-25XC6101, XC6102 SeriesXC6111, XC6112 SeriesSOT-25 (TOP VIEW)XC6103 & XC6113 SeriesXC6104, XC6105 Series XC6114, XC6115 SeriesXC6106, XC6107 Series XC6116, XC6117 Series●USP-6CXC6101, XC6102 Series XC6111, XC6112 SeriesXC6103 & XC6113 SeriesXC6104, XC6105 Series XC6114, XC6115 SeriesXC6106, XC6107 Series XC6116, XC6117 SeriesUSP-6C (BOTTOM VIEW)USP-6C (BOTTOM VIEW)USP-6C (BOTTOM VIEW)USP-6C (BOTTOM VIEW)* The dissipation pad for the USP-6C package should be solder-plated in recommended mount pattern and metal masking so as to enhance mounting strength and heat release. If the pad needs to be connected to other pins, it should be connected to the V SS pin.3/26XC6101 ~ XC6107, XC6111~ XC6117SeriesRESET OUTPUTSERIES WATCHDOGMANUAL RESET V DFL (RESETB)V DFH (RESET)XC6101 XC6111 Available Available CMOS - XC6102XC6112AvailableAvailableN-channel open drain-XC6103 XC6113 Available Available - CMOS XC6104 XC6114 Available Not AvailableCMOS CMOS XC6105 XC6115 Available Not Available N-channel open drain CMOS XC6106 XC6116 Not Available AvailableCMOSCMOS XC6107XC6117Not AvailableAvailableN-channel open drainCMOSDESIGNATORDESCRIPTIONSYMBOLDESCRIPTION0 : V DF x 5% (TYP .) with hysteresis ① Hysteresis Range1 : V DF x 0.1% (TYP .) without hysteresis② Functions and Type of Reset Output1 ~ 7: Watchdog and manual functions, and reset output type as per Selection Guide in the above chartA : 3.13msec (TYP .)B : 25msec (TYP .) C: 50msec (TYP .) D : 100msec (TYP .) E : 200msec (TYP .) F : 400msec (TYP .) ③ Release Delay Time * H : 1.6sec (TYP .)0 : No WD timeout period forXC6106, XC6107, XC6116, XC6117 Series 1: 6.25msec (TYP .) 2 : 50msec (TYP .) 3 : 100msec (TYP .) 4 : 200msec (TYP .) 5 : 400msec (TYP .) ④ Watchdog Timeout Period6: 1.6sec (TYP .) ⑤⑥ Detect Voltage 16 ~ 50: Detect voltageex.) 4.5V: ⑤⇒4, ⑥⇒5M : SOT-25 ⑦ Package E : USP-6C R : Embossed tape, standard feed ⑧ Device OrientationL: Embossed tape, reverse feed* Please set the release delay time shorter than or equal to the watchdog timeout period. ex.) XC6101D427MR or XC6101D327MR■PRODUCT CLASSIFICATION ●Selection Guide ●Ordering Information XC61①②③④⑤⑥⑦⑧4/26XC6101~XC6107, XC6111~XC6117 Series■PACKAGING INFORMATION●SOT-25●USP-6C5/26XC6101 ~ XC6107, XC6111~ XC6117Series④ Represents production lot number0 to 9 and A to Z and inverted 0 to 9 and A to Z repeated. (G, I, J, O, Q, W expected.) * ‘X’ represents both ‘0’ and ‘1’. (ex. XC61X1⇒XC6101 and XC6111)■MARKING RULE●SOT-25①②③④SOT-25 (TOP VIEW)6/26XC6101~XC6107, XC6111~XC6117 Series① Represents product series② Represents release delay time MARK RELEASE DELAY TIME PRODUCT SERIES A 3.13msec XC61XxAxxxxx B 25msec XC61XxBxxxxx C 50msec XC61XxCxxxxx D 100msec XC61XxDxxxxx E 200msec XC61XxExxxxx F 400msec XC61XxFxxxxx H 1.6sec XC61XxHxxxxx③ Represents watchdog timeout period MARK WATCHDOG TIMEOUT PERIOD PRODUCT SERIES 0 XC61X6, XC61X7 series XC61Xxx0xxxx 1 6.25msec XC61Xxx1xxxx 2 50msec XC61Xxx2xxxx 3 100msec XC61Xxx3xxxx 4 200msec XC61Xxx4xxxx 5 400msec XC61Xxx5xxxx 6 1.6sec XC61Xxx6xxxx④⑤ Represents detect voltage MARK④ ⑤DETECT VOLTAGE (V)PRODUCT SERIES3 3 3.3 XC61Xxxx33xx 5 0 5.0XC61Xxxx50xx⑥ Represents production lot number0 to 9 and A to Z repeated. (G, I, J, O, Q, W excepted.)* No character inversion used. ** ‘X’ represents both ‘0’ and ‘1’. (ex. XC61X1⇒XC6101 and XC6111)MARK PRODUCT SERIES MARK PRODUCT SERIES 3 XC6101xxxxxx 8 XC6111xxxxxx 4 XC6102xxxxxx 9 XC6112xxxxxx 5 XC6103xxxxxx A XC6113xxxxxx 6 XC6104xxxxxx B XC6114xxxxxx 7 XC6105xxxxxx C XC6115xxxxxx 3 XC6106xxxxxx 8 XC6116xxxxxx 4 XC6107xxxxxx 9 XC6117xxxxxx■MARKING RULE (Continued)●USP-6CUSP-6C (TOP VIEW)7/26XC6101 ~ XC6107, XC6111~ XC6117Series■BLOCK DIAGRAMS●XC6101, XC6111 Series●XC6102, XC6112 Series●XC6103, XC6113 Series8/26XC6101~XC6107, XC6111~XC6117 Series■BLOCK DIAGRAMS (Continued)●XC6107, XC6117 Series●XC6106, XC6116 Series●XC6105, XC6115 Series●XC6104, XC6114 Series9/26XC6101 ~ XC6107, XC6111~ XC6117SeriesPARAMETERSYMBOL RATINGSUNITSV INV SS -0.3 ~ 7.0 VM RBV SS -0.3 ~ V IN +0.3 VInput Voltage WD V SS -0.3 ~ 7.0V Output Current I OUT 20 mACMOS Output RESETB/RESET V SS -0.3 ~ V IN +0.3Output Voltage N-ch Open Drain Output RESETB V SS -0.3 ~ 7.0VSOT-25 250Power Dissipation USP-6C Pd 100mWOperational Temperature Range Topr -40 ~ +85 OCStorage Temperature Range Tstg -40 ~ +125 OC■ABSOLUTE MAXIMUM RATINGSTa = 25O C10/26XC6101~XC6107, XC6111~XC6117 SeriesNOTE:*1: XC6101~XC6107 (with hysteresis) *2: XC6111~XC6117 (without hysteresis)*3: ‘X’ represents both ‘0’ and ‘1’. (ex. XC61X1⇒XC6101 and XC6111) *4: V DF(T): Setting detect voltage*5: If only “V DF ” is indicated, it represents both V DFL (low when detected) and V DFH (high when detected).PARAMETERSYMBOLCONDITIONSMIN.TYP .MAX. UNITS CIRCUITDetect Voltage V DFL V DFHV DF(T)× 0.98V DF(T) V DF(T)× 1.02 V 1 Hysteresis Range XC6101~XC6107 (*1) V HYS V DF × 0.02V DF × 0.05 V DF× 0.08 V 1Hysteresis Range XC6111~XC6117 (*2) V HYS 0 V DF × 0.001 V DFx 0.01V 1V IN =V DF(T)×0.9V - 5 11 V IN =V DF(T)×1.1V- 10 16 XC61X1/XC61X2/XC61X3XC61X4/XC61X5 (*3)(The MRB & the WD Pin: No connection) V IN =6.0V - 1218 V IN =V DF(T)×0.9V - 4 10 V IN =V DF(T)×1.1V - 8 14 Supply Current I SS XC61X6/XC61X7 (*3)(The MRB Pin: No connection)V IN = 6.0V - 1016 µA 2Operating Voltage V IN 1.0 - 6.0 V 1VIN = 1.0V 0.15 0.5 -V IN =2.0V (V DFL(T)> 2.0V) 2.0 2.5 - V IN =3.0V (V DFL(T) >3.0V) 3.0 3.5 -N-ch.V DS = 0.5V V IN =4.0V (V DFL(T) >4.0V) 3.5 4.0 - 3 V DFL Output Current (RESETB) I RBOUTCMOS,P-chV DS = 0.5V V IN = 6.0V - - 1.1 -0.8 mA 4 N-chV DS = 0.5VV IN =6.0V 4.4 4.9 - 3V IN =1.0V - - 0.08 - 0.02 V IN =2.0V (V DFH(T)> 2.0V)- - 0.50 - 0.30 V IN =3.0V (V DFH(T)>3.0V)- - 0.75 - 0.55V DFHOutput Current (RESET) I ROUT P-ch. V DS = 0.5V V IN =4.0V (V DFH(T)>4.0V)- - 0.95 - 0.75 mA 4Temperature Characteristics △V DF / △Topr ・V DF -40OC < Topr < 85 O C - +100 - ppm / O C12 3.13 5 13 25 3825 50 75 60 100 140 120 200 280 240 400 560Release Delay Time(V DF <1.8V)T DR Time until V IN is increased from1.0V to2.0Vand attains to the release time level,and the Reset output pin inverts.960 1600 2240 ms 5 2 3.13 5 13 25 38 25 50 7560 100 140 120 200 280 240 400 560 Release Delay Time(V DF >1.9V)T DRTime until V IN is increased from1.0V to (V DF x1.1V) and attains to the releasetime level,and the Reset output pin inverts. 960 1600 2240ms 5 Detect Delay Time T DFTime until V IN is decreased from 6.0V to 1.0V and attains to the detect voltage level, and the Reset output pin detectswhile the WD pin left opened.- 3 30 µs 5V DFL /V DFH CMOS Output Leak CurrentI LEAK V IN =6.0V, RESETB=6.0V (V DFL ) V IN =6.0V, RESET=0V (V DFH )- 0.01 - µA 3V DFL N-ch Open DrainOutput Leak CurrentI LEAKV IN =6.0V, RESETB=6.0V-0.010.10µA 3■ELECTRICAL CHARACTERISTICS●XC6101~XC6107, XC6111~XC6117 SeriesTa = 25O CSeriesPARAMETERSYMBOL CONDITIONS MIN.TYP . MAX. UNITS CIRCUIT3.13 6.25 9.38 25 50 7560 100 140 120 200 280240 400 560 Watchdog Timeout Period (V DF <1.8V)T WDTime until V IN increases form1.0V to2.0V andthe Reset output pin is released to go into the detection state. (WD=V SS )960 1600 2240 ms 6 3.13 6.25 9.38 25 50 75 60 100 140 120 200 280240 400 560 Watchdog Timeout Period (V DF >1.9V)T WDTime until V IN increases form1.0V to (V DF x1.1V)and the Reset output pin is released to go into the detection state. (WD=V SS )960 1600 2240 ms 6 WatchdogMinimum Pulse Width T WDIN V IN =6.0V,Apply pulse from 6.0V to 0Vto the WD pin. 300 - - ns 7 Watchdog High Level VoltageV WDH V IN =V DF x 1.1V ~ 6.0V V IN x 0.7- 6 V 7 Watchdog Low Level Voltage V WDL V IN =V DF x 1.1V ~ 6.0V0 - V IN x 0.3 V 7 V IN =6.0V, V WD =6.0V (Avg. when peak )- 12 19Watchdog Input Current I WD V IN =6.0V, V WD =0V (Avg. when peak) - 19 -12 -µA 8 Watchdog Input ResistanceR WDV IN =6.0V, V WD =0V, R WD =V IN / |I WD |315500880k Ω8PARAMETERSYMBOL CONDITIONS MIN.TYP . MAX.UNITS CIRCUITMRBHigh Level VoltageV MRH V IN =V DF x1.1V ~ 6.0V 1.4 - V IN 9MRBLow Level VoltageV MRL V IN =V DF x1.1V ~ 6.0V-0.35 V9MRBPull-up Resistance R MR V IN =6.0V, MRB=0V, R MR =V IN / |I MRB | 1.6 2.4 3.0 M Ω 10 MRB Minimum Pulse Width (*3) XC6101~XC6105 XC6111~XC6115 T MRINV IN =6.0V,Apply pulse from 6.0V to 0V tothe MRB pin 2.8 - -MRB Minimum Pulse Width (*4) XC6106, XC6107 XC6116, XC6117T MRIN V IN =6.0V,Apply pulse from 6.0V to 0V tothe MRB pin1.2 - -µs11●XC6101 ~ XC6103, XC6106 ~ XC6107, XC6111 ~ XC6113, XC6116 ~ XC6117 Series NOTE:*1: V DF(T): Setting detect voltage *2: If only “V DF ” is indicated, it represents both V DFL (low when detected) and V DFH (high when detected). *3: Watchdog function is available. *4: Watchdog function is not available.Ta = 25O CTa = 25O C ■ELECTRICAL CHARACTERISTICS (Continued)●XC6101~XC6105, XC6111~XC6115 Series■OPERATIONAL EXPLANATIONThe XC6101~XC6107, XC6111~XC6117 series compare, using the error amplifier, the voltage of the internal voltage reference source with the voltage divided by R1, R2 and R3 connected to the V IN pin. The resulting output signal from the error amplifier activates the watchdog logic, manual reset logic, delay circuit and the output driver. When the V IN pin voltage gradually falls and finally reaches the detect voltage, the RESETB pin output goes from high to low in the case of the V DFL type ICs, and the RESET pin output goes from low to high in the case of the V DFH type ICs.<RESETB / RESET Pin Output Signal>* V DFL (RESETB) type - output signal: Low when detected.The RESETB pin output goes from high to low whenever the V IN pin voltage falls below the detect voltage, or whenever the MRB pin is driven from high to low. The RESETB pin remains low for the release delay time (T DR) after the V IN pin voltage reaches the release voltage. If neither rising nor falling signals are applied to the WD pin within the watchdog timeout period, the RESETB pin output remains low for the release delay time (T DR), and thereafter the RESET pin outputs high level signal. * V DFH (RESET) type – output signal: High when detected.The RESET pin output goes from low to high whenever the V IN pin voltage falls below the detect voltage, or whenever the MRB pin is driven from high to low. The RESET pin remains high for the release delay time (T DR) after the V IN pin voltage reaches the release voltage. If neither rising nor falling signals are applied to the WD pin within the watchdog timeout period, the V OUT pin output remains high for the release delay time (T DR), and thereafter the RESET pin outputs low level signal.<Hysteresis>When the internal comparator output is high, the NMOS transistor connected in parallel to R3 is turned ON, activating the hysteresis circuit. The difference between the release and detect voltages represents the hysteresis range, as shown by the following calculations:V DF (detect voltage) = (R1+R2+R3) x Vref(R2+R3)V DR (release voltage) = (R1+R2) x Vref(R2)V HYS (hysteresis range)=V DR-V DF (V)V DR > V DF* Detect voltage (V DF) includes conditions of both V DFL (low when detected) and V DFH (high when detected).* Please refer to the block diagrams for R1, R2, R3 and Vref.Hysteresis range is selectable from V DF x 0.05V (XC6101~XC6107) or V DF x 0.001V (XC6111~XC6117).<Watchdog (WD) Pin>The XC6101~XC6107, XC6111~XC6117 series use a watchdog timer to detect malfunction or “runaway” of the microprocessor. If neither rising nor falling signals are applied from the microprocessor within the watchdog timeout period, the RESETB/RESET pin output maintains the detection state for the release delay time (T DR), and thereafter the RESET/RESETB pin output returns to the release state (Please refer to the FUNCTION CHART). The timer in the watchdog is then restarted. Six watchdog timeout period settings are available in 1.6sec, 400msec, 200msec, 100msec, 50msec, 6.25msec.<MRB Pin>Using the MRB pin input, the RESET/RESETB pin signal can be forced to the detection state. When the MRB pin is driven from high to low, the RESETB pin output goes from high to low in the case of the V DFL type ICs, and the RESET pin output goes from low to high in the case of the V DFH type. Even after the MRB pin is driven back high, the RESET/RESETB pin output maintains the detection state for the release delay time (T DR). Since the MRB pin is internally pulled up to the V IN pin voltage level, leave the MRB pin open if unused (Please refer to the FUNCTION CHART). A diode, which is an input protection element, is connected between the MRB pin and V IN pin. Therefore, if the MRB pin is applied voltage that exceeds V IN, the current will flow to V IN through the diode. Please use this IC within the stated maximum ratings (V SS -0.3 ~ V IN+0.3) on the MRB pin.<Release Delay Time>Release delay time (T DR) is the time that elapses from when the V IN pin reaches the release voltage, or when the watchdog timeout period expires with no rising signal applied to the WD pin, until the RESET/RESETB pin output is released from the detection state. Seven release delay time (T DR) watchdog timeout period settings are available in 1.6sec, 400msec, 200msec, 100msec, 50msec, 25msec, 3.13msec.<Detect Delay Time>Detect Delay Time (T DF) is the time that elapses from when the V IN pin voltage falls to the detect voltage until the RESET/ RESETB pin output goes into the detection state.Series■TIMING CHARTS●CMOS Output●T DF (CMOS Output)VINVDFL LevelGNDVIN Level VDFL Level GNDVIN x 0.1V■NOTES ON USE1. Please use this IC within the stated maximum ratings. Operation beyond these limits may cause degrading or permanent damage to the device.2. When a resistor is connected between the V IN pin and the input, the V IN voltage drops while the IC is operating and a malfunction may occur as a result of the IC’s through current. For the CMOS output products, the V IN voltage drops while the IC is operating and malfunction may occur as a result of the IC’s output current. Please be careful with using the XC6111~XC6117 series (without hysteresis).3. In order to stabilize the IC’s operations, please ensure that the V IN pin’s input frequency’s rise and fall times are more than 1 µ sec/V.4. Noise at the power supply may cause a malfunction of the watchdog operation or the circuit. In such case, please strength the line between V IN and the GND pin and connect about 0.22µF of a capacitor between the V IN pin and the GND pin.5. Protecting against a malfunction while the watchdog time out period, an ignoring time (no reaction time) occurs to the rise and fall times. Referring to the figure below, the ignoring time (no reaction time) lasts for 900µsec at maximum.GNDGNDGNDVIN Pin Wave FormWD Pin Wave FormRESETB Pin Wave Form (VDFL)SeriesPIN NAMELOGIC CONDITIONSH V IN >V DF +V HYS V IN L V IN <V DF H MRB>1.40V MRBL MRB<0.35V H When keeping W D >V WDH more than T WD L When keeping W D <V WDL more than T WD L → H V WDL → V WDH , T WDIN >300nsec WDH → L V WDH →V WDH , T WDIN >300nsecV IN MRB WD RESETB (*2) H HH LRepeat detect and release (H →L →H)H OpenH L → HH H or Open H → L H HLL *1 LV IN MRB WD RESETB (*3) H HH LRepeat detect and release (L →H →L)H OpenH L → HH H or Open H → L L HLL *1 HV IN WD RESETB (*2) RESET (*3) H HH L Repeat detect and release (H →L →H)Repeat detect and release (L →H →L)H OpenH L → HH H → L H L HL*1 L HV IN MRB RESETB (*2)RESET (*3)H H or Open H LH LL L H■PIN LOGIC CONDITIONSNOTE:*1: If only “V DF ” is indicated, it represents both V DFL (low when detected) and V DFH (high when detected).*2: For the details of each parameter, please see the electrical characteristics. V DF : Detect VoltageV HYS : Hysteresis RangeV WDH : WD High Level Voltage V WDL: WD Low Level Voltage T WDIN : WD Pulse Width T WD : WD Timeout Period■FUNCTION CHART●XC6103/XC61113 Series●XC6104/XC61114, XC6105/XC6115 Series●XC6106/XC61116, XC6107/XC6117 Series●XC6101/XC61111, XC6102/6112 Series*1: Including all logic of WD (WD=H, L, L →H, H →L, OPEN). *2: When the RESETB is High, the circuit is in the release state. When the RESETB is Low, the circuit is in the detection state. *3: When the RESET is High, the circuit is in the release state. When the RESET is Low, the circuit is in the detection state.■TEST CIRCUITSCircuit 1Circuit 2Circuit 3Circuit 4Series ■TEST CIRCUITS (Continued)Circuit 5Circuit 6Circuit 7■TEST CIRCUITS (Continued)Circuit 8Circuit 9Circuit 10Circuit 11Series■TYPICAL PERFORMANCE CHARACTERISTICS(1.1) Supply Current vs. Input Voltage(1.2) Supply Current vs. Input Voltage■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)(2) Detect, Release Voltage vs. Ambient Temperature(1.2) Supply Current vs. Input Voltage (Continued)Series■TYPICAL PERFORMANCE CHARACTERISTICS (Continued) (3-1) Output Voltage vs. Input Voltage (V DFL ) (3.1) Detect, Release Voltage vs. Input Voltage (V DFL )(3.2) Detect, Release Voltage vs. Input Voltage (V DFH )■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)(4) N-ch Driver Output Current vs. V DSSeries(6) P-ch Driver Output Current vs. Input Voltage 1■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)(8) Release Delay Time vs. Ambient Temperature(7) P-ch Driver Output Current vs. Input Voltage 2■TYPICAL PERFORMANCE CHARACTERISTICS (Continued) (10) Release Delay Time vs. Input Voltage(11) Watchdog Timeout Period vs. Input VoltageSeries■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)(14) MRB Low Level Voltage vs. Ambient Temperature(15) MRB High Level Voltage vs. Ambient Temperature* ‘X’ represents both ‘0’ and ‘1’. (ex. XC61X1⇒XC6101 and XC6111)。

MPXA6115AC6U中文资料

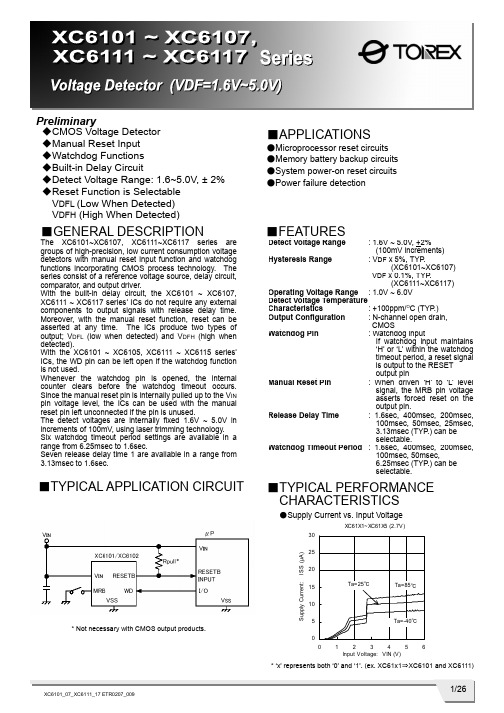

MPXA6115A Rev 3, 01/2007Freescale Semiconductor Technical Data© Freescale Semiconductor, Inc., 2007. All rights reserved.High Temperature AccuracyIntegrated Silicon Pressure Sensor for Measuring Absolute Pressure, On-Chip Signal Conditioned, Temperature Compensated and CalibratedThe MPXA6115A/MPXH6115A series sensor integrates on-chip, bipolar op amp circuitry and thin film resistor networks to provide a high output signal and temperature compensation. The small form factor and high reliability of on-chip integration make the pressure sensor a logical and economical choice for the system designer.The MPXA6115A/MPXH6115A series piezoresistive transducer is a state-of-the-art, monolithic, signal conditioned, silicon pressure sensor. This sensor combines advanced micromachining techniques, thin film metallization, and bipolar semiconductor processing to provide an accurate, high level analog output signal that is proportional to applied pressure.Figure 1 shows a block diagram of the internal circuitry integrated on a pressure sensor chip.Features •Improved Accuracy at High Temperature•Available in Small and Super Small Outline Packages • 1.5% Maximum Error over 0° to 85°C•Ideally suited for Microprocessor or Microcontroller-Based Systems •Temperature Compensated from -40° to +125°C•Durable Thermoplastic (PPS) Surface Mount PackageTypical Applications •Aviation Altimeters •Industrial Controls•Engine Control/Manifold Absolute Pressure (MAP)•Weather Station and Weather Reporting Device BarometersORDERING INFORMATIONDevice TypeOptionsCase No.MPX Series Order No.Packing OptionsDevice MarkingSMALL OUTLINE PACKAGE Basic Element Absolute, Element Only 482MPXA6115A6U Rails MPXA6115A Absolute, Element Only 482MPXA6115A6T1Tape & ReelMPXA6115A Ported ElementAbsolute, Axial Port 482A MPXA6115AC6U Rails MPXA6115A Absolute, Axial Port482AMPXA6115AC6T1Tape & ReelMPXA6115ASUPER SMALL OUTLINE PACKAGE Basic Element Absolute, Element Only 1317MPXH6115A6U Rails MPXH6115A Absolute, Element Only 1317MPXH6115A6T1Tape & ReelMPXH6115A Ported ElementAbsolute, Axial Port 1317A MPXH6115AC6U Rails MPXH6115A Absolute, Axial Port1317A MPXH6115AC6T1Tape & ReelMPXH6115AMPXA6115A MPXH6115A SERIESINTEGRATED PRESSURE SENSOR 15 TO 115 kPA (2.2 TO 16.7 psi)0.2 TO 4.8 V OUTPUTSMALL OUTLINE PACKAGEPIN NUMBERS (1)1.Pins 1, 5, 6, 7, and 8 are internal device connections. Do not connect to external circuitry or ground. Pin 1 is denoted by the notch in the lead.1N/C 5N/C 2V S6N/C 3GND 7N/C 4V OUT8N/CSUPER SMALL OUTLINE PACKAGEPIN NUMBERS (1)1.Pins 1, 5, 6, 7, and 8 are internal device connections. Do not connect to external circuitry or ground. Pin 1 is denoted by the notch in the lead1N/C 5N/C 2V S 6N/C 3GND 7N/C 4V OUT8N/CSensorsMPXA6115A Figure 1. Fully Integrated Pressure Sensor SchematicTable 1. Maximum Ratings (1)1.Exposure beyond the specified limits may cause permanent damage or degradation to the device.RatingSymbol Value Units Maximum Pressure (P1 > P2)P max 400kPa Storage Temperature T stg -40° to +125°°C Operating TemperatureT A -40° to +125°°C Output Source Current @ Full Scale Output (2)2.Maximum Output Current is controlled by effective impedance from V out to Gnd or V out to V S in the application circuit.I o +0.5mAdc Output Sink Current @ Minimum Pressure Offset (2)I o --0.5mAdcPins 1, 5, 6, 7, and 8 are NO CONNECTSSensing ElementV OUTV SGain Stage #2GNDand Ground Reference Shift CircuitryThin Film Temperature CompensationandGain Stage #1SensorsMPXA6115ATable 2. Operating Characteristics (V S = 5.0 Vdc, T A = 25°C unless otherwise noted, P1 > P2)CharacteristicSymbol Min Typ Max Unit Pressure Range P OP 15—115kPa Supply Voltage (1)V S 4.75 5.0 5.25Vdc Supply CurrentI o - 6.010mAdc Minimum Pressure Offset (2)(0 to 85°C)@ V S = 5.0 Volts V off 0.1330.2000.268VdcFull Scale Output (3)(0 to 85°C)@ V S = 5.0 Volts V FSO 4.633 4.700 4.768VdcFull Scale Span (4)(0 to 85°C)@ V S = 5.0 Volts V FSS 4.433 4.500 4.568VdcAccuracy (5)(0 to 85°C)———±1.5%V FSS Sensitivity V/P —45.9—mV/kPa Response Time (6)t R — 1.0—ms Warm-Up Time (7)——20—ms Offset Stability (8)——±0.25—%V FSS1.Device is ratiometric within this specified excitation range.2.Offset (V off ) is defined as the output voltage at the minimum rated pressure.3.Full Scale Output (V FSO ) is defined as the output voltage at the maximum or full rated pressure.4.Full Scale Span (V FSS ) is defined as the algebraic difference between the output voltage at full rated pressure and the output voltage at the minimum rated pressure.5.Accuracy is the deviation in actual output from nominal output over the entire pressure range and temperature range as a percent of span at 25°C due to all sources of error including the following:•Linearity:Output deviation from a straight line relationship with pressure over the specified pressure range.•Temperature Hysteresis:Output deviation at any temperature within the operating temperature range, after the temperature is cycled toand from the minimum or maximum operating temperature points, with zero differential pressure applied.•Pressure Hysteresis:Output deviation at any pressure within the specified range, when this pressure is cycled to and from minimumor maximum rated pressure at 25°C.•TcSpan:Output deviation over the temperature range of 0° to 85°C, relative to 25°C.•TcOffset:Output deviation with minimum pressure applied, over the temperature range of 0° to 85°C, relative to 25°C.6.Response Time is defined as the time for the incremental change in the output to go from 10% to 90% of its final value when subjected to a specified step change in pressure.7.Warm-up Time is defined as the time required for the product to meet the specified output voltage after the pressure has been stabilized.8.Offset Stability is the product's output deviation when subjected to 1000 cycles of Pulsed Pressure, Temperature Cycling with Bias Test.SensorsMPXA6115A Figure 2. Cross Sectional Diagram SSOP (Not to Scale).Figure 3. Typical Application Circuit (Output Source Current Operation)Figure 4. Output versus Absolute PressureFigure 2 illustrates the absolute sensing chip in the basic Super Small Outline chip carrier (Case 1317).Figure 3 shows a typical application circuit (output source current operation).Figure 4 shows the sensor output signal relative to pressure input. Typical minimum and maximum outputcurves are shown for operation over 0 to 85×C temperature range. The output will saturate outside of the rated pressure range.A fluorosilicone gel isolates the die surface and wire bonds from the environment, while allowing the pressure signal to be transmitted to the silicon diaphragm. The MPXA6115A/MPXH6115A series pressure sensor operatingcharacteristics, internal reliability and qualification tests are based on use of dry air as the pressure media. Media other than dry air may have adverse effects on sensor performance and long-term reliability. Contact the factory for information regarding media compatibility in your application.Wire Bond Stainless Steel CapThermoplasticCaseDie BondSealed Vacuum ReferenceFluoro Silicone Gel Die CoatLead FrameAbsolute ElementP1DieV S Pin 2+5.0 VGND Pin 3V out Pin 4MPXA6115A MPXH6115Ato ADC100 nF51 K47 pFO u t p u t (V o l t s )5.04.54.03.53.0Pressure (ref: to sealed vacuum) in kPaMAXMIN51015202530354045505560657075808590951001052.52.01.51.00.5110Transfer Function:V out = V s * (.009*P-.095) ± Error V S = 5.0 Vdc TEMP = 0 to 85ºC115120TYPSensorsMPXA6115ATransfer Function (MPXA6115A/MPXH6115A)Nominal Transfer Value:Vout = VS x (0.009 x P - 0.095)± (Pressure Error x Temp. Factor x 0.009 x VS)VS = 5.0 ± 0.25 VdcTemperature Error BandMPXA6115A/MPXH6115A SERIESBreak Points Temp Multiplier - 4030 to 8511251.75Temperature in Cº4.03.02.00.01.0-40-2020406014012010080Temperature Error FactorNOTE: The Temperature Multiplier is a linear response from 0ºC to -40ºC and from 85ºC to 125ºCPressure Error BandError Limits for Pressure3.02.01.0-1.0-2.0-3.00.020Pressure (in kPa)P r e s s u r e E r r o r (k P a )15 to 115 (kPa)±1.5 (kPa)406080100120Pressure Error (Max)SensorsMPXA6115A MINIMUM RECOMMENDED FOOTPRINT FOR SMALL AND SUPER SMALL PACKAGESSurface mount board layout is a critical portion of the total design. The footprint for the semiconductor package must be the correct size to ensure proper solder connection interface between the board and the package. With the correct pad geometry, the packages will self-align when subjected to asolder reflow process. It is always recommended to fabricate boards with a solder mask layer to avoid bridging and/or shorting between solder pads, especially on tight tolerances and/or tight layouts.Figure 5. SOP Footprint (Case 482)Figure 6. SSOP Footprint (Case 1317 and 1317A)0.66016.760.060 TYP 8X 1.520.100 TYP 2.540.3007.62inch mm0.100 TYP 8X 2.540.027 TYP 8X 0.690.053 TYP 8X 1.35inch mm0.3879.830.1503.810.0501.27TYPPACKAGE DIMENSIONSCASE 482-01ISSUE OSMALL OUTLINE PACKAGECASE 482A-01ISSUE ASMALL OUTLINE PACKAGEMPXA6115A SensorsMPXA6115A PACKAGE DIMENSIONSSensorsPACKAGE DIMENSIONSMPXA6115A SensorsMPXA6115A PACKAGE DIMENSIONSSensorsPACKAGE DIMENSIONSMPXA6115A SensorsMPXA6115A PACKAGE DIMENSIONSSensorsHow to Reach Us:Home Page:Web Support:/supportUSA/Europe or Locations Not Listed: Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot RoadTempe, Arizona 85284+1-800-521-6274 or +1-480-768-2130 /supportEurope, Middle East, and Africa:Freescale Halbleiter Deutschland GmbHTechnical Information CenterSchatzbogen 781829 Muenchen, Germany+44 1296 380 456 (English)+46 8 52200080 (English)+49 89 92103 559 (German)+33 1 69 35 48 48 (French)/supportJapan:Freescale Semiconductor Japan Ltd.HeadquartersARCO Tower 15F1-8-1, Shimo-Meguro, Meguro-ku,Tokyo 153-0064Japan0120 191014 or +81 3 5437 9125support.japan@Asia/Pacific:Freescale Semiconductor Hong Kong Ltd.Technical Information Center2 Dai King StreetTai Po Industrial EstateTai Po, N.T., Hong Kong+800 2666 8080@For Literature Requests Only:Freescale Semiconductor Literature Distribution Center P.O. Box 5405Denver, Colorado 802171-800-441-2447 or 303-675-2140Fax: 303-675-2150 LDCForFreescaleSemiconductor@ Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. “Typical” parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals”, must be validated for each customer application by customer’s technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part. Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.© Freescale Semiconductor, Inc. 2007. All rights reserved.MPXA6115A。

XC6103D540中文资料