LMK03806BISQXNOPB;LMK03806BISQNOPB;中文规格书,Datasheet资料

三菱FX系列PLC特殊功能寄存器M指令代码详细功能介绍之欧阳语创编

M8000:上电接通M8001:上电断开M8002:初始化脉冲(首次扫描接通)M8003:初始化脉冲(首次扫描断开)M8004:错误发生(FX3UC时M8060,M8061,M8064,M8065,M8066,M8067其中哪一个ON时动作;FX3UC 以外M8060,M8061,M8063,M8064,M8065,M8066,M8067其中哪一个ON时动作)M8005:电池电压降低(电池电压异常降低时动作)M8006:电池电压降低锁存(电池电压异常降低时动作保持)M8007:瞬间停止检测(当M8007为ON的时间小于D8008,PLC将继续运行)M8008:停电检测(当M8008电源关闭时,M8000也关闭)M8009:DC24V故障M8011:10ms时钟脉冲M8012:100ms时钟脉冲M8013:1s时钟脉冲M8014:1min时钟脉冲M8015:内存实时脉冲(计时停止以及预先装置)M8016:内存实时脉冲(显示停止,时刻读出显示的停止)M8017:内存实时脉冲(补正,±30s补正)M8018:内存实时脉冲(安装,安装检测)M8019:内存实时脉冲错误M8020:零位标志,加减演算结果为0M8021:借位标志,演算结果成为最大的负数值以下时M8022:进位标志,进位发生在ADD(FNC20)指令期间或当数据移位操作的结果发生溢出时。

M8023:小数点演算标志,ON:进行浮点运算。

M8024:BMOV方向指定,转送方向替换,数据从终点到源的方向转送。

M8029:指令结束,DSW(FNC72)等等的动作结束时动作M8030:电池LED消灯指令,当驱动M8030时,及时电池电压降低,PLC面板的LED也不会点亮。

M8031:非锁存内存全部清除M8032:锁存内存全部清除M8033:内存保持停止,ON时内存保持,当PLC从RUN→STOP,图像存储或者数据存储的内容保持原来状态。

M8034:所有输出禁止M8035:强制RUN模式M8036:强制RUN指令M8037:强制STOP指令M8038: ON时,通讯参数被设定;在FX2、FX2C里,作为RAM文件寄电器全部删除动作。

MAX038资料中文

高频信号发生器_______________概述MAX038是一种只需极少外围电路就能实现高 频、高精度输出三角波、锯齿波、正弦波、方波 和脉冲波的精密高频函数发生器芯片。

内部提供 的2.5V 基准电压和一个外接电阻和电容可以控制 输出频率范围在0.1Hz 到20MHz 。

占空比可在较大 的范围内由一个±2.3V的线性信号控制变化,便 于进行脉冲宽度调制和产生锯齿波。

频率调整和 频率扫描可以用同样的方式实现。

占空比和频率 控制是独立的。

通过设置2个TTL 逻辑地址引脚合适的逻辑电 平,能设定正弦波,方波或三角波的输出。

所有 波形的输出都是峰-峰值为±2VP -P 的信号。

低阻 抗输出能力可以达到±20mA。

____________________________性能o 频率调节范围:0.1Hz 到20MHzo 三角波, 锯齿波, 正弦波, 方波和脉冲波 o 频率和占空比独立可调 o 频率扫描范围:350:1 o 可控占空比:15%到85% o 低阻抗输出缓冲器: 0.1Ω o 低失真正弦波: 0.75% o 低温度漂移: 200ppm/°C______________型号信息TTL 逻辑地址引脚SYNC 从内部振荡器输出占 空比固定为50%的信号,不受其它波占空比的影 响,从而同步系统中其它振荡器。

内部振荡器 允许被连接着相位检波器输入端(PDI )的外部 TTL 时钟同步。

型号 MAX038CPP MAX038CWP MAX038C/D MAX038EPP MAX038EWP工作温度 0°C 到 +70°C 0°C 到 +70°C 0°C 到 +70°C -40°C 到 +85°C -40°C 到 +85°C引脚--封装 20 Plastic DIP 20 SO Dice* 20 Plastic DIP 20 SO.__________________应用精密函数信号发生器 压控振荡器 频率调制器*Contact factory for dice specifications.__________________引脚图脉宽调制器 锁相环 频率合成器FSK 发生器(正弦波和方波)________________________________________________________________ Maxim Integrated Products1For free samples & the latest literature: , or phone 1-800-998-8800. For small orders, phone 408-737-7600 ext. 3468MAX038高频信号发生器图1. 内部结构及基本工作电路_______________ 详细说明MAX038是一种高频函数信号发生器,它可以使 用最少的外部元件而产生低失真正弦波,三角波, 锯齿波,方波(脉冲波)。

MAX038中文

MAX038芯片中文资料及在波形发生器中的应用(1)简介:波形发生器的应用范围很广。

在分析检测设备、超声设备、医疗设备及通讯设备中广泛应用。

函数发生器作为信号激励源,其参数精度是设计时应考虑的重要因素 ...波形发生器的应用范围很广。

在分析检测设备、超声设备、医疗设备及通讯设备中广泛应用。

函数发生器作为信号激励源,其参数精度是设计时应考虑的重要因素。

常用的波形产生电路有RC震荡电路、LC震荡电路、文氏震荡电路以及由555芯片构成的震荡电路等,但这些震荡电路由于核心芯片、选频及限幅元件特性的限制,在幅频精度方面或多或少的存在着不稳定或实现电路复杂等情况。

如果需要实现波形变换、幅频大小调整以及提高幅频的稳定度,设计的外围电路将会变得更为复杂。

由MAX038设计组成的波形产生电路能够输出幅频精度很高且易于调整的波形信号,在电路参数要求苛刻的工作场合能够得到较好的应用。

1 芯片功能介绍1.1 MAX038芯片的性能特点MAX038CPP芯片采用20引脚DIP封装,引脚图如图1所示。

各引脚功能简述如下:REF:芯片内部2.5 V参考电压输出;GND:模拟地;A1,A0:输出波形选择,TTL/CMOS兼容;COSC:内部震荡器外接电容;FADJ,DADJ:输出频率、占空比调节;IIN:震荡频率控制器电流输入;PDI,PDO:内部鉴相器输入、输出;SYNC:同步信号输出,允许内部震荡器与外电路同步;DGND,DV+:内部数字电路电源;V+,V-:MAX038电源(+5 V,-5 V);OUT:波形输出端。

MAX038芯片附加少许外围电路就能够产生三角波、锯齿波、正弦波、方波、矩形脉冲波形。

该芯片具有如下的功能特点:(1)输出频率范围:0.1~20 MHz,最高可达40 MHz:(2)输出波形占空比(15%~85%)独立可调,占空比可由DADJ端调整,如果DADJ 端接地,则输出占空比为50%;(3)具有低输出阻抗的输出缓冲器,输出阻抗的典型值为0.1 Ω;(4)备有TTL兼容的独立同步信号SYNC(方波输出,固定占空比为50%),方便组建频率合成器系统;(5)低温度漂移。

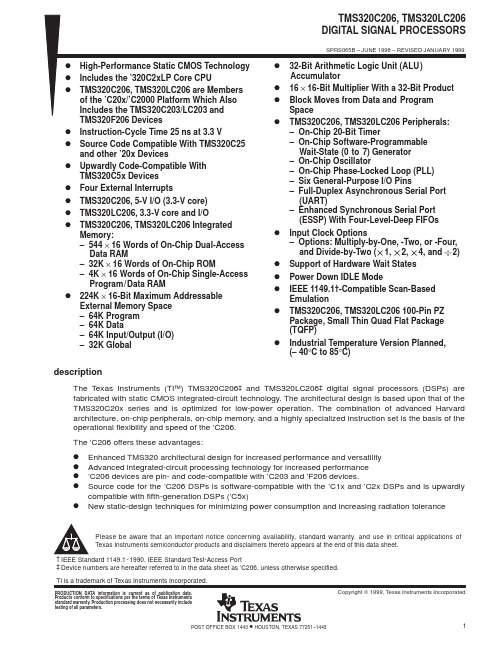

TMS320C206PZ80资料

D D D D

D D D D D D

32-Bit Arithmetic Logic Unit (ALU ) Accumulator 16 × 16-Bit Multiplier With a 32-Bit Product Block Moves from Data and Program Space TMS320C206, TMS320LC206 Peripherals: – On-Chip 20-Bit Timer – On-Chip Software-Programmable Wait-State (0 to 7) Generator – On-Chip Oscillator – On-Chip Phase-Locked Loop (PLL) – Six General-Purpose I/O Pins – Full-Duplex Asynchronous Serial Port (UART) – Enhanced Synchronous Serial Port (ESSP) With Four-Level-Deep FIFOs Input Clock Options – Options: Multiply-by-One, -Two, or -Four, and Divide-by-Two ( 1, 2, 4, and 2) Support of Hardware Wait States Power Down IDLE Mode IEEE 1149.1†-Compatible Scan-Based Emulation TMS320C206, TMS320LC206 100-Pin PZ Package, Small Thin Quad Flat Package (TQFP) Industrial Temperature Version Planned, (– 40°C to 85°C)

Modicon TM3AM6产品数据手册说明书

i s c l a i me r : T h i s d o c u m e n t a t i o n i s n o t i n t e n d e d a s a s u b s t i t u t ef o r a n d i s n o t t o b e u s e d f o r d e t e r m i n i ng s u i t a b i l i t y o r r e l i a b i l i t y o f th e s e p r o d u c t s f o r s p e ci f i c u s e r a p p l i c a t i o n sMainRange of productModicon TM3Product or component typeInput/Output analog module Range compatibility Modicon M251Modicon M241Modicon M221Analogue input number 4Analogue input type Current, analogue input range: 4...20 mACurrent, analogue input range: 0...20 mAVoltage, analogue input range: 0...10 VVoltage, analogue input range: - 10...10 VAnalogue output number 2Analogue output type4...20 mA current0...20 mA current0...10 V voltage- 10...10 V voltage ComplementaryAnalogue input resolution11 bits + sign 12 bits Permissible continuous overload13 V voltage 40 mA current Input impedance<= 50 Ohm current >= 1 MOhm voltage Analogue output resolution11 bits + sign 12 bits LSB value 2.44 mV, analogue input: 0...10 V voltage4.88 mV, analogue input: - 10...10 V voltage4.88 µA, analogue input: 0...20 mA current3.91 µA, analogue input:4...20 mA currentLoad type ResistiveLoad impedance ohmic1 kOhm voltage300 Ohm currentOutput ripple20 mVCross talk<= 1 LSB[Us] rated supply voltage24 V DCSupply voltage limits20.4...28.8 VType of cable<= 30 m twisted shielded pairs cable for input/output circuitCurrent consumption45 mA at 5 V DC (no load) via bus connector55 mA at 5 V DC (full load) via bus connector55 mA at 24 V DC (no load) via external supply100 mA at 24 V DC (full load) via external supplyLocal signalling 1 LED green for PWRElectrical connection10 x 1.5 mm² removable screw terminal block with pitch 3.81 mm adjustment for inputs10 x 1.5 mm² removable screw terminal block with pitch 3.81 mm adjustment for inputs, outputs andsupplyInsulation500 V AC between output and internal logic500 V AC between input and internal logic1500 V AC between input and supply1500 V AC between output and supplyMarking CESurge withstand 1 kV for power supply with common mode protection conforming to EN/IEC 61000-4-50.5 kV for power supply with differential mode protection conforming to EN/IEC 61000-4-51 kV for I/O with common mode protection conforming to EN/IEC 61000-4-50.5 kV for I/O with differential mode protection conforming to EN/IEC 61000-4-5Mounting support Top hat type TH35-15 rail conforming to IEC 60715Top hat type TH35-7.5 rail conforming to IEC 60715Plate or panel with fixing kitHeight90 mmDepth70 mmWidth23.6 mmProduct weight0.11 kgEnvironmentStandards EN/IEC 61131-2EN/IEC 61010-2-201Resistance to electrostatic discharge 4 kV on contact conforming to EN/IEC 61000-4-28 kV in air conforming to EN/IEC 61000-4-2Resistance to electromagnetic fields10 V/m at 80 MHz...1 GHz conforming to EN/IEC 61000-4-33 V/m at 1.4 GHz...2 GHz conforming to EN/IEC 61000-4-31 V/m at2 GHz...3 GHz conforming to EN/IEC 61000-4-3Resistance to magnetic fields30 A/m at 50...60 Hz conforming to EN/IEC 61000-4-8Resistance to fast transients 1 kV I/O conforming to EN/IEC 61000-4-4Resistance to conducted disturbances, induced by radio frequency fields 10 V at 0.15...80 MHz conforming to EN/IEC 61000-4-63 V at spot frequency (2, 3, 4, 6.2, 8.2, 12.6, 16.5, 18.8, 22, 25 MHz) conforming to Marine specification (LR, ABS, DNV, GL)Electromagnetic emission Radiated emissions, test level: 40 dBμV/m QP class A (10 m at 30...230 MHz) conforming to EN/IEC55011Radiated emissions, test level: 47 dBμV/m QP class A (10 m at 230 MHz...1 GHz) conforming to EN/IEC 55011Immunity to microbreaks10 msAmbient air temperature for operation-10...55 °C (horizontal installation)-10...35 °C (vertical installation)2Offer Sustainability Sustainable offer statusGreen Premium product RoHS (date code: YYWW)Compliant - since 1415 - Schneider Electric declaration of conformity Schneider Electric declaration of conformity REAChReference not containing SVHC above the threshold Reference not containing SVHC above the threshold Product environmental profile Available Product environmental Product end of life instructionsAvailableEnd of life manual(*)8.5 mm/0.33 in when the clamp is pulled out.Incorrect Mounting(1)Install a mounting strip Mounting Hole LayoutWiring Diagram (Current / Voltage)(*)Type T fuse (1)Current/Voltage analog output device (2)Current/Voltage analog input device。

奥索凌阳方案适用屏编码和驱动对照

奥索凌阳方案适用屏编码和驱动对照奥索凌阳方案适用屏编码和驱动对照2011-10-4 08:27阅读(26)转载自风的味道2.8寸屏:5408B----FPCHL2401 07CV05408------H2801 FPCHL2401.14A SXD0017 2401QQ AO24QN029325------12N 17N 154000 SAT28S01A05 SXD0002 SAT24000 37H 12A05 2803 HW240320F-2L-0A-20 HJ2810AO-AOFPC 0000000024-0019325C----3225LS2088A SAT28009A05 DST280AU006 4N 88N V029325B----LS24XD 22N 17N9320------19E TS028HA 1N 07N 9N SR779028-AO DST28014L037 CMS21019331-----FTM280F17N 17E FTM280F6W 7N 6E FTM280F10E 7NV 8Q 8A18 21N FPC2802-VO TTPHJ07NVO1289-----JS28ND603C-FPC WST240320S280AV02 1298-----SK001V02 HL2802 36B 10N M30111A197 CMS2101-03A SX2.8C98-4_3-37C T28-A T28-B FPC4218-V0123225-----AU28 036 SXD0006 001 7C SAT2400 12A FPC2803-VO 28A03-VO 12A05 KK240037 0039-C 280NP04-04 3728E SX2.8T28-4_3-37H SXD0001PNL9328------T-0028-A61505V---LS28XD 21N 21E 07NVO A18 FPC1A0027-01-A SYM280T01-A093116----15400053909335IH----24008C18 0367781-----21VO 24N 11N 4N 10N 18V2 FPC-TTHJ07CVO CM012 81-36A 8B26 SY280CM0204535-----SXD00179331LG----Q365205----17V0 YSD FPC 28A03-V0 18V21505C----2.4TE8347-----46E FPC-FTM280C05N 61N 80E TP65K9320LG----SAT28008A18 8K1304 KFM529B21 SR7790928-A061505W----SAT28008A18-Q337502----16N 13N 16E 17E 13E 12N SXD00651297----SAT28009A1161505U-FTM----B21 FPA-SH9873-01A_56-PCB RO61505R(3062主控上用)S6D04M0----TF28001A68070-----NT4PTM3728B MHJ101V1 ZBH028GT-01 SXD00688347D-----ZBH028GT-06 FPC-FTM280C58W-008367-----ZBH028GT-02V18230----XY-2405-HSD10-V2 LC2803.1R61509----QXD028-1000-FB9328LG----07V9338-----91N TFT028E001 EY028CMIL-001-V029335LG----LS28003ILI9320----826709341-----T-280A03-B-16 YQ24TM41-36CLCM0154------2805-PR112-V22.4屏5408-----A024QN025408B----FPCHL2401 SAT24001005 NOATS-V019325-----FPC-S2 TM240320C1NFWCWC FP-29325C----25N3225----Q36 154002660 FTP240F17N FTP240F22N 8C 24N 25W V1 66N 3624A9328----SPT-024-0061298----SK001V02 10N M30111A1978347----FTP240C61N 46E 5N FTP240C65N 3624F 240C29N 240C09N M403A1079325B----22N LS24XD FPC-JTBJ05JUO1505C----XY-2.4TE-V161580----FTP240H25N FTO240HO 32N 04N 25N9335HY----AST24011C19 091110S61505BOE----AST24011C19L LS-100810背面7781----24N 11N 81-36A61505W----LS24Q35 24036095205----53F F240253F 17V09320----01-1D FPC-FTS240W01 JC T24-E T24-A29340----T24BDHJ71V1 240A28-A-16 40-36A 134 240A37-A FPC-FTM240C179N-00S6D04H0----36PIN SXD0066HX8230------LC32002.1 XY-2405 HSDIO-V34535------SXD00249341-----YQ24TM41-36C T-240A82-D-16261卡屏的屏驱动----32063.5寸ST2102----KR035PA5S VT320240S70-A350TMT035---15400T4500 HW320 158000300 S805037535C R0HS 3.5_FPC_10FTS350----735M2 SN570 FMFU-2F 413450017002 513450006002LQ035----8501显示屏编号与屏驱动对应表1 排线丝印侧面丝印驱动IC2 024-22V1 93203 24WIT36-FPC01 93204 1540001660 TS024HAADD04-00 5408B5 1540002660 9325C6 24008C05-V1 93257 AF240B-36B V1.0 AL240EI-3501 77878 AF-240B-2V4.1 AL-240B-S1 77879 AF283E1-37A V1.2 9320-2.810 AF240E1-36C V1.0 778511 AF240E1-36C V2.0 778512 AF283P3-37A V1.0 9325-2.813 CMS2101-03A 080815 080918-2801A背光片 540814 CMS2101-03A 080815 CMS2101 HCT003-280-41F背光片1298CMT304-1(1)-08 8 30 5408B15 CMS2101-3 932516 FPC-FTS240F01 FTS240H03 150517 FPC-FTS240D03 129818 FPC-FTS240D14 129819 FPC-FTP240CO9N FTS240B03 834720 FPC-FTS240W01 FTP240W47N 129821 FPC-FTM280P04N M30111A150 9325C-2.822 FPC-FTM280C05N 8347-2.823 FPC-FTM280F01N FTM280F01N-00 9320-2.824 FPC-FTM280F06W FPC-FTM280F06N-00 090313(背面)933125 FPC-FTM280F07N R61505-2.826 FPC-FTM280C13N 932527 FPC-FTM280P05N M403A486 9325C28 FPC-Y80032 V01 N0711-14-04 9325-2.829 FTP240D10N-01 0703 129830 FTP240D24N-00 090307 778131 FPC-FTP280P05N FTP280P14N-01背面 778132 FTP240W17N-03 080807 9325B33 FG0280FLW-0802-1 8347-2.834 FPC_HL_2401 540835 HL2801 5408-2.836 HL2402B 5408B CMO37 HL2402A 5409B CMO38 LDH240*320F08M 778539 LS2288A 6813-2.840 M30111A116 129841 M30111A059 932542 MFC-S07024 V02 834743 MT321TLLKJ-13 排线接口不同 9320B-2.844 SX-2.4CPT-9325 9325B45 SAT28009A5 9325C-2.846 STA28008A18 9331-2.847 XJ2402-V01 834748 XD028-V01 9325-2.849 XSY LL240-003-081024 R61505(2.4)50 ZCT-24FPC-S1 778551 ZCT-24FPC-S2 9325xp024cp25-36v0 9325hw240320f-0j-0c-10 9325m403a545 1298hw240400f-3a 5420ygg000240ns04-03 9325zc24t04m 9320kfm281e01 9320truly-c tft8k1081fpc-a1-e 9320cf024lgg31-36av1 9320huaruit-0033-a-fpc 9325huaruit-0012-b 9325af240B-36b 7787af-283e1-37av1.2 9320GIANTPLUS KFM281E01-1D 9320 GIANTPLUS KFM281E01-1B 9320CF024LGG31-36AV1 9320 GIANTPLUS KFM281101-1A 9320JLST24PV25-36A 9325ZC24T02 9325DST280CPT003 9325 2.8寸 13SX-2.8CPT-932502 9325 2.8寸 13BX280V003(B0XIANTICH) 9325 2.8寸 13NT4SGP3T28A 5408B 2.8寸 10NT4SGP3T28A AU9325 2.8寸 17NT4PC36728A-BL AU9325 2.8寸 17FPC-TGG000280NP04-07 9325 2.8寸 24LEB-DO428000028C1 9325 2.8寸 24CMS210-03 9325 2.8寸 12HW240320F-2D-0B-10 9325 2.8寸 12HW240320F-2D-0B-20 9325 触摸 13SAT28009A05 9325 2.8寸 13LS2288A 9325 2.8寸 13LS2289A 1505 2.8C寸 9LS2288A 9328 2.8寸 13FPC-FTP280P04N-00 9325 2.8C寸 13FPC-FTM280F0TN-00 61505 2.8寸 27FPC-FTPM280F09N-01、FTM240D17N-00 61505 2.8寸 27 FPC-FTM280F06W-00(FTM280F06N-00) 9331 2.8寸 32NTSAU3624A 5408B 2.4寸 10NT4SHY3624A 3225+HY 2.4寸 35024HAADD04 9325 2.4寸 13FPC-T240BQC 9325 2.4寸 13AF240E3-36D 9325 2.4寸 13(AL240E1-3S01) 9325 2.4寸SX-TGS240STCPYB00-00 7785 2.4寸 15(TGS240STCP-8V1,LDH240X320F008M)SX-2.4CPT-9325 9325 2.4寸 18(SX-TGS2.4CPT)FPC-FTS240D03-02 1298 2.4寸 6(FTP240D10N-02) 9325 2.4寸 13SX-TGS24C98-4:3-36B 1298 2.4寸 6FPC-BKS2401 1298 2.4寸 6SAT24009C05 9325 2.4寸 13SAT24009C05L 9325 2.4寸 13(18)KTM377A01-1A 1298 2.4寸 6SAT24009C05 9325 2.4寸 13TGG000240NS04-03 9325 2.4寸 18(13)(LCM-TGG000240NS04-03)FPC-TTHJ05E00XA 9325 2.4寸 27 (FECHTKONCPT24-9325)24008CIT-Q29 1505 2.4寸 37 1540003250(FMARK) 9325 2.4寸 26 T-0033-B(HUARUI) 9325 2.4寸 26T-0053-A 1297 2.4寸 30T-0033-B 68B(CPT) 2.4寸 26T-0012-B(T-0024-A) 9325 2.4寸 18 (T-0059-A)T-0028-A(HUARUI) 9325 2.8寸2X-GT009BL 7783 2.4寸 25JLST24IH81-36A 7781 2.4寸 25JST24TM25-36A 9328 2.4寸 13SX24C98-413-36B 1298 2.4寸 6(SX-TGS240SDCPET00-00)CF024LCD87-36AVO 7787 2.4寸 4AF240B-36B V1.0 7787 2.4寸 4凌达所有屏 9320 1T-0030 9320 2.4寸 1KT240FC-003B 9320 2.4寸 1FPC-FTS240W01 9320 2.4寸 1FPC1032 9320 2.4寸 124WIT36-FPC01 9320 2.4寸 1FPC-FTS240F01 1505 2.4寸PF240320F-2C-OA-30 8347 2.4寸FPC24T49-A1 9325 2.4寸FPC-TGG000280NP04-07 9325 2.8寸TSA24002C05 9325 2.4寸ST24TM25-36A V1.0 9325 2.4寸FPC-0047A2 9320 2.4寸排线丝印侧面丝印驱动ICAF240B-36B V1.0 :AL240EI-3501 7787AF-240B-2V4.1 : AL-240B-S1 7787AF283E1-37A V1.2 9320-2.8AF240E1-36C V1.0 7785AF240E1-36C V2.0 7785AF283P3-37A V1.0 9325-2.8FPC-FTS240F01 FTS240H03 1505FPC-FTS240D03 1298FPC-FTS240D14 1298FPC-FTP240CO9N FTS240B03 8347FPC-FTM280C05N 8347-2.8FPC-FTM280F01N FTM280F01N-00 9320-2.8 FPC-Y80032 V01 N0711-14-04 9325-2.8 FTP240D10N-01 0703 1298FTP240W17N-03 080807 9325BJLST24PV25-36A V1.0 9325T-0033-B 9325024-22V1 9320FPC_HL_2401 5408HL2801 5408-2.8MFC-S07024 V02 8347MFC-S07001 V04 932024WIT36-FPC01 9320MFC-M240702-A 9320XJ2402-V01 8347XD028-V01 9325-2.8ZCT-24FPC-S1 7785ZCT-24FPC-S2 9325LDH240*320F08M 77851540001660 TS024HAADD04-00 5408B1540002660 9325C24008C05-V1 9325MT321TLLKJ-13 排线接口不同 9320B-2.8SX-2.4CPT-9325 9325BCMS2101-3 9325CMS2101-03A 080815 080918-2801A背光片 540834 M30111A116 1298HW240320F-oj-oc-10 9325FPC24T49-A1 9325ZCT-24FPC-S2 9325NOAIS NT4SAU3624A V01 5408CMS057-2 @ HX(8347)T028 0741Z HL240HYF 0803 7787Hantech HR24F11#02 7787JYD-G5060 GWIL36S03240A-A恻边号GXBL240-019LL240-003 08031141 9325FPC-Y80030 V01 恻边号yxd02436l09 je-c068(b) 9320FPC-Y80030 V01 9320M30111A055 8347M403A107 8347DM2432003-001 这个是2.8的,37线,驱动9320FPC24T49-A1 2.4 9325AF240E1-36B V2.0 7785FPC-Q90044-1 2.8 9325QD -24034Bo-1 2.4 9325NOAIS NT4SAU36 24A V01JLST24CP25-36A 2.4 9325板号:MP-763C-SL V1.1 2005.12.16上位屏CM50011ACT6-01AL 2006/03/06 20针1.5寸元件排列:由上到下整齐一行:C11-C7-C5-C12-R1-R2-C1-C6-C2-C3-C21-C22-C23-C31-C4-C0-D1可代换下位屏:CD50006ACT6-27PIN 2005/10/24 27针元件排列:由上到下整齐一行:RL-CVLCD-CVB0A-CVB1A(这是个利用同尺寸不同针数进行的代换)板号:SD008-V2 2006-07-25-MDLU (ROCKCHIPS 2606A)原屏:CMT027 V1.0 2006-08-09 29针可用屏:FPC-S95012-1 V01 SZSUCCESS 06.01 29针板号:JR040_MAIN_V3.1 2007.04.17 (2608a JXD858)原屏:TFT-2.4-S3D 36PIN IL9320可用屏:DZX2.4-S2 V06 (2608A JXD859)资源:GAUO GASP29P03200-002-A-FPC SA VER 1.3(即屏侧边的标记)板号:SG243 V2 0703140941P2原屏:GIANTPLUS KFM281E01-1D可用:CF024LGG31-36AV1(36P,2.4')可用:GIANTPLUS KFM281E01-1B可用:TRULY-C TFT8K1081FPC-A1-E适用机型:纽曼K8 (2.0版)-ANYKA-AK3225。

Modicon TM3AM6模块说明书

Radiated emissions, test level: 40 dBμV/m QP class A (10 m at 30...230 MHz) conforming to EN/IEC 55011 Radiated emissions, test level: 47 dBμV/m QP class A (10 m at 230 MHz...1 GHz) conforming to EN/IEC 55011

Analogue input number Analogue input type

Analogue output number Analogue output type

Modicon TM3

Input/output analog module

Modicon M221 Modicon M241 Modicon M251

Load type Load impedance ohmic Stabilisation time Conversion time Sampling duration Absolute accuracy error Temperature drift Repeat accuracy Non-linearity Output ripple Cross talk [Us] rated supply voltage Supply voltage limits Type of cable Current consumption

1/4

The information provided in this documentation contains general descriptions and/or technical characteristics of the performance of the products contained herein. This documentation is not intended as a substitute for and is not to be used for determining suitability or reliability of these products for specific user applications. It is the duty of any such user or integrator to perform the appropriate and complete risk analysis, evaluation and testing of the products with respect to the relevant specific application or use thereof. Neither Schneider Electric Industries SAS nor any of its affiliates or subsidiaries shall be responsible or liable for misuse of the information contained herein.

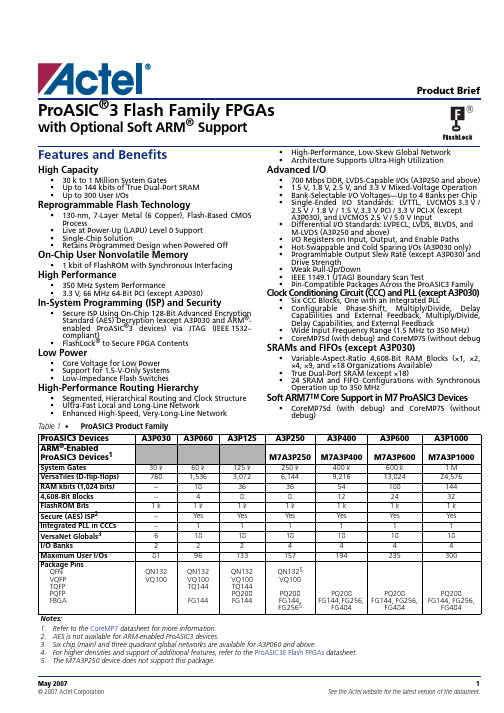

A3P060中文资料

ProASIC3 Devices

ARM-Enabled ProASIC3 Devices

A3P030 A3P060 A3P125

A3P250 3

A3P400 3

M7A3P250 3, 4 M7A3P400 3 I/O Type

A3P600 M7A3P600

A3P1000 M7A3P1000

Single-Ended I/O Single-Ended I/O Single-Ended I/O Single-Ended I/O2 Differential I/O Pairs Single-Ended I/O2 Differential I/O Pairs Single-Ended I/O2 Differential I/O Pairs Single-Ended I/O2 Differential I/O Pairs

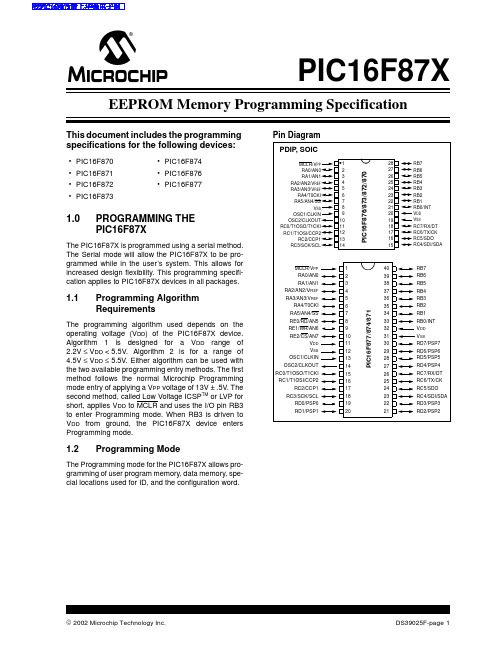

PIC16F873

2002 Microchip Technology Inc.DS39025F-page 1MPIC16F87XThis document includes the programming specifications for the following devices:1.0PROGRAMMING THEPIC16F87XThe PIC16F87X is programmed using a serial method.The Serial mode will allow the PIC16F87X to be pro-grammed while in the user’s system. This allows for increased design flexibility. This programming specifi-cation applies to PIC16F87X devices in all packages.1.1Programming Algorithm RequirementsThe programming algorithm used depends on the operating voltage (V DD ) of the PIC16F87X device.Algorithm 1 is designed for a V DD range of 2.2V ≤V DD <5.5V. Algorithm 2 is for a range of 4.5V ≤V DD ≤5.5V. Either algorithm can be used with the two available programming entry methods. The first method follows the normal Microchip Programming mode entry of applying a V PP voltage of 13V ± .5V. The second method, called Low Voltage ICSP TM or LVP for short, applies V DD to MCLR and uses the I/O pin RB3to enter Programming mode. When RB3 is driven to V DD from ground, the PIC16F87X device enters Programming mode.1.2Programming ModeThe Programming mode for the PIC16F87X allows pro-gramming of user program memory, data memory, spe-cial locations used for ID, and the configuration word.•PIC16F870•PIC16F874•PIC16F871•PIC16F876•PIC16F872•PIC16F877•PIC16F873EEPROM Memory Programming SpecificationPIC16F87XDS39025F-page 22002 Microchip Technology Inc.PIN DESCRIPTIONS (DURING PROGRAMMING): PIC16F87XPin Name During ProgrammingFunction Pin TypePin DescriptionRB3PGM I Low voltage ICSP programming input if LVP configuration bit equals 1RB6CLOCK I Clock input RB7DATA I/O Data input/output MCLR V TEST MODEP*Program Mode Select V DD V DD P Power Supply V SSV SSPGroundLegend:I = Input, O = Output, P = Power*In the PIC16F87X, the programming high voltage is internally generated. To activate the Programming mode, high voltage needs to be applied to the MCLR input. Since the MCLR is used for a level source, this means that MCLR does not draw any significant current.PIC16F87X2.0PROGRAM MODE ENTRY2.1User Program Memory MapThe user memory space extends from 0x0000 to 0x1FFF (8K). In Programming mode, the program memory space extends from 0x0000 to 0x3FFF, with the first half (0x0000-0x1FFF) being user program memory and the second half (0x2000-0x3FFF) being configuration memory. The PC will increment from 0x0000 to 0x1FFF and wrap to 0x0000, 0x2000 to 0x3FFF and wrap around to 0x2000 (not to 0x0000). Once in configuration memory, the highest bit of the PC stays a ‘1’, thus always pointing to the configuration memory. The only way to point to user program mem-ory is to reset the part and re-enter Program/Verify mode, as described in Section2.4.In the configuration memory space, 0x2000-0x200F are physically implemented. However, only locations 0x2000 through 0x2007 are available. Other locations are reserved. Locations beyond 0x200F will physically access user memory (see Figure2-1).2.2Data EEPROM MemoryThe EEPROM data memory space is a separate block of high endurance memory that the user accesses using a special sequence of instructions. The amount of data EEPROM memory depends on the device and is shown below in number of bytes.The contents of data EEPROM memory have the capa-bility to be embedded into the HEX file.The programmer should be able to read data EEPROM information from a HEX file and conversely (as an option), write data EEPROM contents to a HEX file, along with program memory information and configura-tion bit information.The 256 data memory locations are logically mapped starting at address 0x2100. The format for data mem-ory storage is one data byte per address location, LSB aligned.2.3ID LocationsA user may store identification information (ID) in four ID locations. The ID locations are mapped in [0x2000 : 0x2003]. It is recommended that the user use only the four Least Significant bits of each ID location. In some devices, the ID locations read out in an unscrambled fashion after code protection is enabled. For these devices, it is recommended that ID location is written as “11 1111 1000 bbbb” where ‘bbbb’ is ID information. In other devices, the ID locations read out normally, even after code protection. To understand how the devices behave, refer to Table5-1.To understand the scrambling mechanism after code protection, refer to Section4.0.Device# of BytesPIC16F87064PIC16F87164PIC16F87264PIC16F873128PIC16F874128PIC16F876256PIC16F8772562002 Microchip Technology Inc.DS39025F-page 3PIC16F87XDS39025F-page 4 2002 Microchip Technology Inc.PIC16F87X2.4Program/Verify ModeThe Program/Verify mode is entered by holding pins RB6 and RB7 low, while raising MCLR pin from V IL to V IHH (high voltage). In this mode, the state of the RB3 pin does not effect programming. Low voltage ICSP Programming mode is entered by raising RB3 from V IL to V DD and then applying V DD to MCLR. Once in this mode, the user program memory and the configuration memory can be accessed and programmed in serial fashion. The mode of operation is serial, and the mem-ory that is accessed is the user program memory. RB6 and RB7 are Schmitt Trigger Inputs in this mode.The sequence that enters the device into the Program-ming/Verify mode places all other logic into the RESET state (the MCLR pin was initially at V IL). This means that all I/O are in the RESET state (high impedance inputs).The normal sequence for programming is to use the load data command to set a value to be written at the selected address. Issue the begin programming com-mand followed by read data command to verify, and then increment the address.A device RESET will clear the PC and set the address to 0. The “increment address” command will increment the PC. The “load configuration” command will set the PC to 0x2000. The available commands are shown in Table2-2.2.4.1LOW VOLTAGE ICSPPROGRAMMING MODELow voltage ICSP Programming mode allows a PIC16F87X device to be programmed using V DD only. However, when this mode is enabled by a configuration bit (LVP), the PIC16F87X device dedicates RB3 to control entry/exit into Programming mode.When LVP bit is set to ‘1’, the low voltage ICSP pro-gramming entry is enabled. Since the LVP configura-tion bit allows low voltage ICSP programming entry in its erased state, an erased device will have the LVP bit enabled at the factory. While LVP is ‘1’, RB3 is dedi-cated to low voltage ICSP programming. Bring RB3 to V DD and then MCLR to V DD to enter programming mode. All other specifications for high voltage ICSP™apply.To disable low voltage ICSP mode, the LVP bit must be programmed to ‘0’. This must be done while entered with High Voltage Entry mode (LVP bit = 1). RB3 is now a general purpose I/O pin.2.4.2SERIAL PROGRAM/VERIFYOPERATIONThe RB6 pin is used as a clock input pin, and the RB7 pin is used for entering command bits and data input/output during serial operation. To input a com-mand, the clock pin (RB6) is cycled six times. Each command bit is latched on the falling edge of the clock, with the Least Significant bit (LSb) of the command being input first. The data on pin RB7 is required to have a minimum setup and hold time (see AC/DC specifications), with respect to the falling edge of the clock. Commands that have data associated with them (read and load) are specified to have a minimum delay of 1 µs between the command and the data. After this delay, the clock pin is cycled 16 times with the first cycle being a START bit and the last cycle being a STOP bit. Data is also input and output LSb first.Therefore, during a read operation, the LSb will be transmitted onto pin RB7 on the rising edge of the sec-ond cycle, and during a load operation, the LSb will be latched on the falling edge of the second cycle. A min-imum 1 µs delay is also specified between consecutive commands.All commands are transmitted LSb first. Data words are also transmitted LSb first. The data is transmitted on the rising edge and latched on the falling edge of the clock. To allow for decoding of commands and reversal of data pin configuration, a time separation of at least 1µs is required between a command and a data word (or another command).The commands that are available are:2.4.2.1Load ConfigurationAfter receiving this command, the program counter (PC) will be set to 0x2000. By then applying 16 cycles to the clock pin, the chip will load 14-bits in a “data word,” as described above, to be programmed into the configuration memory. A description of the memory mapping schemes of the program memory for normal operation and Configuration mode operation is shown in Figure2-1. After the configuration memory is entered, the only way to get back to the user program memory is to exit the Program/Verify Test mode by taking MCLR low (V IL).2.4.2.2Load Data for Program Memory After receiving this command, the chip will load in a 14-bit “data word” when 16 cycles are applied, as described previously. A timing diagram for the load data command is shown in Figure6-1.Note:The OSC must not have 72 osc clockswhile the device MCLR is between V IL andV IHH.2002 Microchip Technology Inc.DS39025F-page 5PIC16F87XDS39025F-page 62002 Microchip Technology Inc.2.4.2.3Load Data for Data MemoryAfter receiving this command, the chip will load in a 14-bit “data word ” when 16 cycles are applied. How-ever, the data memory is only 8-bits wide, and thus,only the first 8-bits of data after the START bit will be programmed into the data memory. It is still necessary to cycle the clock the full 16 cycles in order to allow the internal circuitry to reset properly. The data memory contains up to 256 bytes. If the device is code pro-tected, the data is read as all zeros.2.4.2.4Read Data from Program MemoryAfter receiving this command, the chip will transmit data bits out of the program memory (user or configu-ration) currently accessed, starting with the second ris-ing edge of the clock input. The RB7 pin will go into Output mode on the second rising clock edge, and it will revert back to Input mode (hi-impedance) after the 16th rising edge. A timing diagram of this command is shown in Figure 6-2.2.4.2.5Read Data from Data MemoryAfter receiving this command, the chip will transmit data bits out of the data memory starting with the sec-ond rising edge of the clock input. The RB7 pin will go into Output mode on the second rising edge, and it will revert back to Input mode (hi-impedance) after the 16th rising edge. As previously stated, the data memory is 8-bits wide, and therefore, only the first 8-bits that are output are actual data.2.4.2.6Increment AddressThe PC is incremented when this command is received. A timing diagram of this command is shown in Figure 6-3.2.4.2.7Begin Erase/Program CycleA load command must be given before every begin programming command. Programming of the appro-priate memory (test program memory, user program memory or data memory) will begin after this command is received and decoded. An internal timing mechanism executes an erase before write. The user must allow for both erase and programming cycle times for program-ming to complete. No “end programming ” command is required.2.4.2.8Begin ProgrammingA load command must be given before every begin programming command. Programming of the appro-priate memory (test program memory, user program memory or data memory) will begin after this command is received and decoded. An internal timing mechanism executes a write. The user must allow for program cycle time for programming to complete. No “end pro-gramming ” command is required.This command is similar to the ERASE/PROGRAM CYCLE command, except that a word erase is not done. It is recommended that a bulk erase be per-formed before starting a series of programming only cycles.Note:The Begin Program operation must take place at 4.5 to 5.5 V DD range.TABLE 2-2:COMMAND MAPPING FOR PIC16F87XCommandMapping (MSB … LSB)Data Voltage Range Load ConfigurationX X 00000, data (14), 0 2.2V - 5.5V Load Data for Program Memory X X 00100, data (14), 0 2.2V - 5.5V Read Data from Program Memory X X 01000, data (14), 02.2V - 5.5V Increment AddressX X 0110 2.2V - 5.5V Begin Erase Programming Cycle 0010002.2V - 5.5V Begin Programming Only Cycle 011000 4.5V - 5.5V Load Data for Data Memory X X 00110, data (14), 0 2.2V - 5.5V Read Data from Data Memory X X 01010, data (14), 0 2.2V - 5.5V Bulk Erase Setup1000001 4.5V - 5.5V Bulk Erase Setup21114.5V -5.5VPIC16F87X2.5Erasing Program and DataMemoryDepending on the state of the code protection bits, pro-gram and data memory will be erased using different procedures. The first set of procedures is used when both program and data memories are not code pro-tected. The second set of procedures must be used when either memory is code protected. A device pro-grammer should determine the state of the code pro-tection bits and then apply the proper procedure to erase the desired memory.2.5.1ERASING NON-CODE PROTECTEDPROGRAM AND DATA MEMORY When both program and data memories are not code protected, they must be individually erased using the following procedures. The only way that both memories are erased using a single procedure is if code protec-tion is enabled for one of the memories. These proce-dures do not erase the configuration word or ID locations.Procedure to bulk erase program memory:1.Execute a Load Data for Program Memory com-mand (000010) with a ’1’ in all locations(0x3FFF)2.Execute a Bulk Erase Setup1 command(000001)3.Execute a Bulk Erase Setup2 command(000111)4.Execute a Begin Erase/Programming command(001000)5.Wait 8ms6.Execute a Bulk Erase Setup1 command(000001)7.Execute a Bulk Erase Setup2 command(000111)Procedure to bulk erase data memory:1.Execute a Load Data for Data Memory com-mand (000011) with a ’1’ in all locations(0x3FFF)2.Execute a Bulk Erase Setup1 command(000001)3.Execute a Bulk Erase Setup2 command(000111)4.Execute a Begin Erase/Programming command(001000)5.Wait 8ms6.Execute a Bulk Erase Setup1 command(000001)7.Execute a Bulk Erase Setup2 command(000111)2.5.2ERASING CODE PROTECTEDMEMORYFor the PIC16F87X devices, once code protection is enabled, all protected program and data memory loca-tions read all ’0’s and further programming is disabled. The ID locations and configuration word read out unscrambled and can be reprogrammed normally. The only procedure to erase a PIC16F87X device that is code protected is shown in the following procedure. This method erases program memory, data memory, configuration bits and ID locations. Since all data within the program and data memory will be erased when this procedure is executed, the security of the data or code is not compromised.1.Execute a Load Configuration command(000000) with a ’1’ in all locations (0x3FFF)2.Execute Increment Address command(000110) to set address to configuration wordlocation (0x2007)3.Execute a Bulk Erase Setup1 command(000001)4.Execute a Bulk Erase Setup2 command(000111)5.Execute a Begin Erase/Programming command(001000)6.Wait 8ms7.Execute a Bulk Erase Setup1 command(000001)8.Execute a Bulk Erase Setup2 command(000111)2002 Microchip Technology Inc.DS39025F-page 7PIC16F87XDS39025F-page 82002 Microchip Technology Inc.FIGURE 2-1:FLOW CHART - PIC16F87X PROGRAM MEMORY (2.2V ≤V DD < 5.5V)STARTSet V DD = V DDPLoad Data Wait All Locations Done?Verify all LocationsData Correct?DONEIncrement Address CommandReport VerifyErrorNoNoCommandBeginErase/ProgrammingCommandtera + tprogPIC16F87X2002 Microchip Technology Inc.DS39025F-page 9PIC16F87XDS39025F-page 10 2002 Microchip Technology Inc.3.0CONFIGURATION WORDThe PIC16F87X has several configuration bits. These bits can be set (reads ‘0’), or left unchanged (reads ‘1’), to select various device configurations.3.1Device ID WordThe device ID word for the PIC16F87X is located at 2006h.TABLE 3-1:DEVICE ID VALUEDeviceDevice ID ValueDev Rev PIC16F87000 1101 000x xxxx PIC16F87100 1101 001x xxxx PIC16F87200 1000 111x xxxx PIC16F87300 1001 011x xxxx PIC16F87400 1001 001x xxxx PIC16F87600 1001 111x xxxx PIC16F87700 1001 101x xxxxREGISTER 3-1:CONFIG: CONFIGURATION WORD FOR PIC16F873/874/876/877(ADDRESS 2007h)U-0U-0U-0U-0U-0U-0U-0R/P-1U-0R/P-1R/P-1R/P-1R/P-1R/P-1 CP1CP0RESV—WRT CPD LVP BODEN CP1CP0PWRTE WDTE F0SC1F0SC0 bit 13bit 0bit 13-12 bit 5-4CP1:CP0: FLASH Program Memory Code Protection bits(2) 4K Devices:11 = Code protection off10 = 0F00h to 0FFFh code protected01 = 0800h to 0FFFh code protected00 = 0000h to 0FFFh code protected8K Devices:11 = Code protection off10 = 1F00h to 1FFFh code protected01 = 1000h to 1FFFh code protected00 = 0000h to 1FFFh code protectedbit 11Reserved: Set to ‘1’ for normal operationbit 10Unimplemented: Read as ‘1’bit 9WRT: FLASH Program Memory Write Enable bit1 =Unprotected program memory may be written to by EECON control0 =Unprotected program memory may not be written to by EECON controlbit 8CPD: Data EE Memory Code Protection bit1 =Code protection off0 =Data EE memory code protectedbit 7LVP: Low Voltage ICSP Programming Enable bit1 =RB3/PGM pin has PGM function, low voltage programming enabled0 =RB3 is digital I/O, HV on MCLR must be used for programmingbit 6BODEN: Brown-out Reset Enable bit(2)1 =BOR enabled0 =BOR disabledbit 3PWRTE: Power-up Timer Enable bit1 =PWRT disabled0 =PWRT enabledbit 2WDTE: Watchdog Timer Enable bit1 =WDT enabled0 =WDT disabledbit 1-0FOSC1:FOSC0: Oscillator Selection bits11 =RC oscillator10 =HS oscillator01 =XT oscillator00 =LP oscillatorNote1:Enabling Brown-out Reset automatically enables Power-up Timer (PWRT), regardless of the value of bit PWRTE. Ensure the Power-up Timer is enabled any time Brown-out Reset is enabled.2:All of the CP1:CP0 pairs have to be given the same value to enable the code protection scheme listed.Legend:R = Readable bit P = Programmable bit U = Unimplemented bit, read as ‘0’- n = Value when device is unprogrammed u = Unchanged from programmed stateREGISTER 3-2:CONFIG: CONFIGURATION WORD FOR PIC16F870/871/872 (ADDRESS 2007h) U-0U-0U-0U-0U-0U-0U-0R/P-1U-0R/P-1R/P-1R/P-1R/P-1R/P-1 CP1CP0RESV—WRT CPD LVP BODEN CP1CP0PWRTE WDTE F0SC1F0SC0 bit 13bit 0bit 13-12 bit 5-4CP1:CP0: FLASH Program Memory Code Protection bits(2) 11 =Code protection off10 =Not supported01 =Not supported00 =0000h to 07FFh code protectedbit 11Reserved: Set to ‘1’ for normal operationbit 10Unimplemented: Read as ‘1’bit 9WRT: FLASH Program Memory Write Enable bit1 =Unprotected program memory may be written to by EECON control0 =Unprotected program memory may not be written to by EECON controlbit 8CPD: Data EE Memory Code Protection bit1 =Code protection off0 =Data EE memory code protectedbit 7LVP: Low Voltage ICSP Programming Enable bit1 =RB3/PGM pin has PGM function, low voltage programming enabled0 =RB3 is digital I/O, HV on MCLR must be used for programmingbit 6BODEN: Brown-out Reset Enable bit(2)1 =BOR enabled0 =BOR disabledbit 3PWRTE: Power-up Timer Enable bit1 =PWRT disabled0 =PWRT enabledbit 2WDTE: Watchdog Timer Enable bit1 =WDT enabled0 =WDT disabledbit 1-0FOSC1:FOSC0: Oscillator Selection bits11 =RC oscillator10 =HS oscillator01 =XT oscillator00 =LP oscillatorNote1:Enabling Brown-out Reset automatically enables Power-up Timer (PWRT), regardless of the value of bit PWRTE. Ensure the Power-up Timer is enabled any time Brown-out Reset is enabled.2:All of the CP1:CP0 pairs have to be given the same value to enable the code protection scheme listed.Legend:R = Readable bit P = Programmable bit U = Unimplemented bit, read as ‘0’- n = Value when device is unprogrammed u = Unchanged from programmed state4.0EMBEDDING THE CONFIGURATION WORD AND ID INFORMATION IN THEHEX FILETo allow portability of code, the programmer is required to read the configuration word and ID locations from the HEX file when loading the HEX file. If configuration word information was not present in the HEX file, then a simple warning message may be issued. Similarly, while saving a HEX file, configuration word and ID information must be included. An option to not include this information may be provided.Specifically for the PIC16F87X, the EEPROM data memory should also be embedded in the HEX file (see Section2.2).Microchip Technology Inc. feels strongly that this feature is important for the benefit of the end customer.5.0CHECKSUM COMPUTATION Checksum is calculated by reading the contents of the PIC16F87X memory locations and adding up the opcodes, up to the maximum user addressable loca-tion, e.g., 0x1FF for the PIC16F87X. Any carry bits exceeding 16-bits are neglected. Finally, the configura-tion word (appropriately masked) is added to the checksum. Checksum computation for each member of the PIC16F87X devices is shown in Table5-1.The checksum is calculated by summing the following:•The contents of all program memory locations •The configuration word, appropriately masked •Masked ID locations (when applicable)The Least Significant 16 bits of this sum are the checksum.The following table describes how to calculate the checksum for each device. Note that the checksum cal-culation differs depending on the code protect setting. Since the program memory locations read out differ-ently depending on the code protect setting, the table describes how to manipulate the actual program mem-ory values to simulate the values that would be read from a protected device. When calculating a checksum by reading a device, the entire program memory can simply be read and summed. The configuration word and ID locations can always be read.Note that some older devices have an additional value added in the checksum. This is to maintain compatibil-ity with older device programmer checksums.TABLE 5-1:CHECKSUM COMPUTATIONDeviceCodeProtectChecksum*BlankValue0x25E6 at 0and maxaddressPIC16F870OFF SUM[0x0000:0x07FFF] + CFGW & 0x3BFF0x33FF0xFFCD ALL CFGW & 0x3BFF + SUM_ID0x3FCE0x0B9C PIC16F871OFF SUM[0x0000:0x07FFF] + CFGW & 0x3BFF0x33FF0xFFCD ALL CFGW & 0x3BFF + SUM_ID0x3FCE0x0B9C PIC16F872OFF SUM[0x0000:0x07FFF] + CFGW & 0x3BFF0x33FF0xFFCD ALL CFGW & 0x3BFF + SUM_ID0x3FCE0x0B9C PIC16F873OFF SUM[0x0000:0x0FFF] + CFGW & 0x3BFF0x2BFF0xF7CD 0x0F00 : 0xFFF SUM[0x0000:0x0EFF] + CFGW & 0x3BFF +SUM_ID0x48EE0xFAA30x0800 : 0xFFF SUM[0x0000:0x07FF] + CFGW & 0x3BFF + SUM_ID0x3FDE0xF193 ALL CFGW & 0x3BFF + SUM_ID0x37CE0x039C PIC16F874OFF SUM[0x0000:0x0FFF] + CFGW & 0x3BFF0x2BFF0xF7CD 0x0F00 : 0xFFF SUM[0x0000:0x0EFF] + CFGW & 0x3BFF +SUM_ID0x48EE0xFAA30x0800 : 0xFFF SUM[0x0000:0x07FF] + CFGW & 0x3BFF + SUM_ID0x3FDE0xF193 ALL CFGW & 0x3BFF + SUM_ID0x37CE0x039C PIC16F876OFF SUM[0x0000:0x1FFF] + CFGW & 0x3BFF0x1BFF0xE7CD 0x1F00 : 0x1FFF SUM[0x0000:0x1EFF] + CFGW & 0x3BFF +SUM_ID0x28EE0xDAA30x1000 : 0x1FFF SUM[0x0000:0x0FFF] + CFGW & 0x3BFF + SUM_ID0x27DE0xD993 ALL CFGW & 0x3BFF + SUM_ID0x27CE0xF39C PIC16F877OFF SUM[0x0000:0x1FFF] + CFGW & 0x3BFF0x1BFF0xE7CD 0x1F00 : 0x1FFF SUM[0x0000:0x1EFF] + CFGW & 0x3BFF +SUM_ID0x28EE0xDAA30x1000 : 0x1FFF SUM[0x0000:0x0FFF] + CFGW & 0x3BFF + SUM_ID0x27DE0xD993 ALL CFGW & 0x3BFF + SUM_ID0x27CE0xF39C Legend:CFGW=Configuration WordSUM[a:b]=[Sum of locations a to b inclusive]SUM_ID=ID locations masked by 0xF then made into a 16-bit value with ID0 as the most significant nibble.For example, ID0 = 0x1, ID1 = 0x2, ID3 = 0x3, ID4 = 0x4, then SUM_ID = 0x1234 *Checksum=[Sum of all the individual expressions] MODULO [0xFFFF]+=Addition&=Bitwise AND6.0PROGRAM/VERIFY MODE ELECTRICAL CHARACTERISTICS TABLE 6-1:TIMING REQUIREMENTS FOR PROGRAM/VERIFY MODEAC/DC CHARACTERISTICS Standard Operating Conditions (unless otherwise stated) Operating Temperature:0°C ≤ T A≤ +70°C Operating Voltage: 2.2V ≤ V DD≤ 5.5VCharacteristics Sym Min Typ Max Units Conditions/Comments GeneralV DD level for Algorithm 1V DD 2.2 5.5V Limited command set(See Table2-2)V DD level for Algorithm 2V DD 4.5 5.5V All commands available High voltage on MCLR forhigh voltage programming entry V IHH V DD + 3.513.5VVoltage on MCLR forlow voltage ICSP programming entryV IH 2.2 5.5VMCLR rise time (V SS to V HH) for Testmode entryt VHHR 1.0µs(RB6, RB7) input high level V IH10.8V DD V Schmitt Trigger input (RB6, RB7) input low level V IL10.2V DD V Schmitt Trigger inputRB<7:6> setup time before MCLR ↑ tset0100nsRB<7:6> hold time after MCLR ↑ thld05µsRB3 setup time before MCLR ↑tset2100nsSerial Program/VerifyData in setup time before clock ↓tset1100nsData in hold time after clock ↓thld1100nsData input not driven to next clock input(delay required between command/data orcommand/command)tdly1 1.0µsDelay between clock ↓ to clock ↑ of nextcommand or datatdly2 1.0µsClock ↑ to data out valid (during read data)tdly380nsErase cycle time tera24msProgramming cycle time tprog24ms2002 Microchip Technology Inc.DS39025F - page 21Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications.No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip ’s products as critical com-ponents in life support systems is not authorized except with express written approval by Microchip. No licenses are con-veyed, implicitly or otherwise, under any intellectual property rights.TrademarksThe Microchip name and logo, the Microchip logo, FilterLab,K EE L OQ , microID, MPLAB, PIC, PICmicro, PICMASTER,PICSTART , PRO MATE, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip T echnology Incorporated in the U.S.A. and other countries.dsPIC, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB,In-Circuit Serial Programming, ICSP , ICEPIC, microPort,Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM,MXDEV, PICC, PICDEM, , rfPIC, Select Mode and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A.Serialized Quick Term Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.All other trademarks mentioned herein are property of their respective companies.© 2002, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.Printed on recycled paper.Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities inChandler and Tempe, Arizona in July 1999. The Company’s quality system processes and procedures are QS-9000 compliant for itsPICmicro ® 8-bit MCUs, K EE L OQ ® code hopping devices, Serial EEPROMs and microperipheral products. In addition, Microchip ’s quality system for the design and manufacture of development systems is ISO 9001 certified.Note the following details of the code protection feature on PICmicro ® MCUs.•The PICmicro family meets the specifications contained in the Microchip Data Sheet.•Microchip believes that its family of PICmicro microcontrollers is one of the most secure products of its kind on the market today, when used in the intended manner and under normal conditions.•There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowl-edge, require using the PICmicro microcontroller in a manner outside the operating specifications contained in the data sheet. The person doing so may be engaged in theft of intellectual property.•Microchip is willing to work with the customer who is concerned about the integrity of their code.•Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as “unbreakable ”.•Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our product.If you have any further questions about this matter, please contact the local sales office nearest to you.。

S-80831中文资料

Hysteresis characteristics

5% typ.

Detection voltage

0.8 to 6.0 V (0.1 V step)

Nch open-drain active low and CMOS active low output SC-82AB Super-small plastic package TO-92 Plastic package SOT-89-3 Miniaturized power mold plastic package SOT-23-5 Very-small plastic package

Battery checker Power failure detector Power monitor for pagers, calculators,

organizers,

Constant voltage power monitor for cameras,

video equipment, communication devices

OUT VDD NC VSS

1 2 3

OUT VDD VSS

1 Bottom view

2

3

1

2

3

Figure 1

Seiko InstrALL PACKAGE HIGH-PRECISION VOLTAGE DETECTOR S-808 Series

2

Seiko Instruments Inc.

易网

SUPER-SMALL PACKAGE HIGH-PRECISION VOLTAGE DETECTOR S-808 Series

Table 1

Detection voltage range (V) 0.8V±2.0% 0.9V±2.0% 1.0V±2.0% 1.1V±2.0% 1.2V±2.0% 1.3V±2.0% 1.4V±2.0% 1.5V±2.0% 1.6V±2.0% 1.7V±2.0% 1.8V±2.0% 1.9V±2.0% 2.0V±2.0% 2.1V±2.0% 2.2V±2.0% 2.3V±2.0% 2.4V±2.0% 2.5V±2.0% 2.6V±2.0% 2.7V±2.0% 2.8V±2.0% 2.9V±2.0% 3.0V±2.0% 3.1V±2.0% 3.2V±2.0% 3.3V±2.0% 3.4V±2.0% 3.5V±2.0% 3.6V±2.0% 3.7V±2.0% 3.8V±2.0% 3.9V±2.0% 4.0V±2.0% 4.1V±2.0% 4.2V±2.0% 4.3V±2.0% 4.4V±2.0% 4.5V±2.0% 4.6V±2.0% 4.7V±2.0% 4.8V±2.0% 4.9V±2.0% 5.0V±2.0% 5.1V±2.0% 5.2V±2.0% 5.3V±2.0% 5.4V±2.0% 5.5V±2.0% 5.6V±2.0% 5.7V±2.0% 5.8V±2.0% 5.9V±2.0% 6.0V±2.0% Hysteresis width VHYS typ.(V) 0.034 0.044 0.054 0.064 0.073 0.083 0.093 0.075 0.080 0.085 0.090 0.095 0.100 0.105 0.110 0.115 0.120 0.125 0.130 0.135 0.140 0.145 0.150 0.155 0.160 0.165 0.170 0.175 0.180 0.185 0.190 0.195 0.200 0.205 0.210 0.215 0.220 0.225 0.230 0.235 0.240 0.245 0.250 0.255 0.260 0.265 0.270 0.275 0.280 0.285 0.290 0.295 0.300 Nch Open Drain(Low) SC-82AB S-80808ANNP-E7Y-T2 S-80809ANNP-E7Z-T2 S-80810ANNP-E70-T2 S-80811ANNP-E71-T2 S-80812ANNP-E72-T2 S-80813ANNP-EDA-T2 S-80814ANNP-EDB-T2 S-80815ANNP-EDC-T2 S-80816ANNP-EDD-T2 S-80817ANNP-EDE-T2 S-80818ANNP-EDF-T2 S-80819ANNP-EDG-T2 S-80820ANNP-EDH-T2 S-80821ANNP-EDJ-T2 S-80822ANNP-EDK-T2 S-80823ANNP-EDL-T2 S-80824ANNP-EDM-T2 S-80825ANNP-EDN-T2 S-80826ANNP-EDP-T2 S-80827ANNP-EDQ-T2 S-80828ANNP-EDR-T2 S-80829ANNP-EDS-T2 S-80830ANNP-EDT-T2 S-80831ANNP-EDV-T2 S-80832ANNP-EDW -T2 S-80833ANNP-EDX-T2 S-80834ANNP-EDY-T2 S-80835ANNP-EDZ-T2 S-80836ANNP-ED0-T2 S-80837ANNP-ED1-T2 S-80838ANNP-ED2-T2 S-80839ANNP-ED3-T2 S-80840ANNP-ED4-T2 S-80841ANNP-ED5-T2 S-80842ANNP-ED6-T2 S-80843ANNP-ED7-T2 S-80844ANNP-ED8-T2 S-80845ANNP-ED9-T2 S-80846ANNP-EJA-T2 S-80847ANNP-EJB-T2 S-80848ANNP-EJC-T2 S-80849ANNP-EJD-T2 S-80850ANNP-EJE-T2 S-80851ANNP-EJF-T2 S-80852ANNP-EJG-T2 S-80853ANNP-EJH-T2 S-80854ANNP-EJJ-T2 S-80855ANNP-EJK-T2 S-80856ANNP-EJL-T2 S-80857ANNP-EJM-T2 S-80858ANNP-EJN-T2 S-80859ANNP-EJP-T2 S-80860ANNP-EJQ-T2 TO-92 — — — — — — — S-80815ANY S-80816ANY S-80817ANY S-80818ANY S-80819ANY S-80820ANY S-80821ANY S-80822ANY S-80823ANY S-80824ANY S-80825ANY S-80826ANY S-80827ANY S-80828ANY S-80829ANY S-80830ANY S-80831ANY S-80832ANY S-80833ANY S-80834ANY S-80835ANY S-80836ANY S-80837ANY S-80838ANY S-80839ANY S-80840ANY S-80841ANY S-80842ANY S-80843ANY S-80844ANY S-80845ANY S-80846ANY S-80847ANY S-80848ANY S-80849ANY S-80850ANY S-80851ANY — S-80853ANY — — — — — — — SOT-89-3 — — — — — — — S-80815ANUP-EDC-T2 S-80816ANUP-EDD-T2 S-80818ANUP-EDF-T2 SOT-23-5 — — — — — — — — — S-80818ANMP-EDF-T2

LMK03806BEVALNOPB;中文规格书,Datasheet资料

March 2012

LMK03806BEVAL Users GuideLMK03806B Ultra Low Jitter Clock Generator

March 2012

SNAU075

/

CONTENTS 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 12. 13. 14. 15. 16. 17. 18. 19. INTRODUCTION ......................................................................................................... 4 QUICK START ............................................................................................................ 5 DEFAULT CODELOADER MODES FOR EVALUATION BOARDS ......................... 6 EXAMPLE: USING CODELOADER TO PROGRAM THE LMK03806B ................... 7 PROGRAM/LOAD DEVICE ........................................................................................ 8 RESTORING A DEFAULT MODE .............................................................................. 8 VISUAL CONFIRMATION OF FREQUENCY LOCK .................................................. 9 ENABLE CLOCK OUTPUTS ...................................................................................... 9 PLL LOOP FILTERS AND LOOP PARAMETERS .................................................. 10 EVALUATION BOARD INPUTS AND OUTPUTS .................................................. 11 CODELOADER USAGE.......................................................................................... 15 TYPICAL PHASE NOISE PERFORMANCE PLOTS ............................................. 22 SCHEMATICS ......................................................................................................... 26 BILL OF MATERIALS ............................................................................................. 31 PCB LAYERS STACKUP ....................................................................................... 34 PCB LAYOUT .......................................................................................................... 35 PROPERLY CONFIGURING THE LPT PORT ....................................................... 40 TROUBLESHOOTING INFORMATION .................................................................. 41

LM4863中文资料