bypass_capacitors_decoupling_KCP

MB90F546GSPF中文资料

2

MB90540/540G/545/545G Series

(Continued) • UART 1 With full-duplex double buffer (8-bit length) Clock asynchronized or clock synchronized serial (extended I/O serial) can be used. • External interrupt circuit (8 channels) A module for starting an extended intelligent I/O service (EI2OS) and generating an external interrupt which is triggered by an external input. • Delayed interrupt generation module Generates an interrupt request for switching tasks. • 8/10-bit A/D converter (8 channels) 8/10-bit resolution can be selectively used. Starting by an external trigger input. Conversion time : 26.3 µs • FULL-CAN interfaces MB90540 series : 2 channel MB90545 series : 1 channel Conforming to Version 2.0 Part A and Part B Flexible message buffering (mailbox and FIFO buffering can be mixed) • External bus interface : Maximum address space 16 Mbytes • Package: QFP-100, LQFP-100

STM32固件库使用手册的中文翻译版

因为该固件库是通用的,并且包括了所有外设的功能,所以应用程序代码的大小和执行速度可能不是最优 的。对大多数应用程序来说,用户可以直接使用之,对于那些在代码大小和执行速度方面有严格要求的应 用程序,该固件库驱动程序可以作为如何设置外设的一份参考资料,根据实际需求对其进行调整。

1.3.1 变量 ................................................................................................................................................ 28 1.3.2 布尔型 ............................................................................................................................................ 28 1.3.3 标志位状态类型 ........................................................................................................................... 29 1.3.4 功能状态类型 .............................................................................................................

Raspberry Pi RP2040微控制器数据手册说明书

ColophonCopyright © 2020 Raspberry Pi (Trading) Ltd.The documentation of the RP2040 microcontroller is licensed under a Creative Commons Attribution-NoDerivatives 4.0 International (CC BY-ND).Portions Copyright © 2019 Synopsys, Inc.All rights reserved. Used with permission. Synopsys & DesignWare are registered trademarks of Synopsys, Inc.Portions Copyright © 2000-2001, 2005, 2007, 2009, 2011-2012, 2016 ARM Limited.All rights reserved. Used with permission.build-date: 2021-01-04build-version: githash: 1f2b413-dirty (pico-sdk: 04605c3-clean pico-examples: cc4c1c7-clean)IP ContributorsIntellectual property from the following companies was used in RP2040:•ARM Limited (M0+, UART, SPI)•Synopsys, Inc. (I2C, SSI)•Taiwan Semiconductor Manufacturing Company Limited (TSMC) (standard cells, memories)•Dolphin Design SAS (Voltage Regulator, Power-on Reset/Brown-out Detector)•Aragio Solutions (GPIO and Crystal Pad library)•Silicon Creations (PLL)•GF Micro (ADC, TS, USB PHY)Legal Disclaimer NoticeTECHNICAL AND RELIABILITY DATA FOR RASPBERRY PI PRODUCTS (INCLUDING DATASHEETS) AS MODIFIED FROM TIME TO TIME (“RESOURCES”) ARE PROVIDED BY RASPBERRY PI (TRADING) LTD (“RPTL) "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW IN NO EVENT SHALL RPTL BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THE RESOURCES, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.RPTL reserves the right to make any enhancements, improvements, corrections or any other modifications to the RESOURCES or any products described in them at any time and without further notice.The RESOURCES are intended for skilled users with suitable levels of design knowledge. Users are solely responsible for their selection and use of the RESOURCES and any application of the products described in them. User agrees to indemnify and hold RPTL harmless against all liabilities, costs, damages or other losses arising out of their use of the RESOURCES.RPTL grants users permission to use the RESOURCES solely in conjunction with the Raspberry Pi products. All other useHIGH RISK ACTIVITIES. Raspberry Pi products are not designed, manufactured or intended for use in hazardous environments requiring fail safe performance, such as in the operation of nuclear facilities, aircraft navigation or communication systems, air traffic control, weapons systems or safety-critical applications (including life support systems and other medical devices), in which the failure of the products could lead directly to death, personal injury or severe physical or environmental damage (“High Risk Activities”). RPTL specifically disclaims any express or implied warranty of fitness for High Risk Activities and accepts no liability for use or inclusions of Raspberry Pi products in High Risk Activities.Raspberry Pi products are provided subject to RPTL’s Standard Terms. RPTL’s provision of the RESOURCES does not expand or otherwise modify RPTL’s Standard Terms including but not limited to the disclaimers and warranties expressed in them.Table of ContentsColophon. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 IP Contributors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Legal Disclaimer Notice. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 1. Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151.1. Why is the chip called RP2040?. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151.2. Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151.3. The Chip. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161.4. Pinout Reference. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161.4.1. Pin Locations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171.4.2. Pin Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171.4.3. GPIO Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 182. System Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 212.1. Bus Fabric. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 212.1.1. AHB-Lite Crossbar. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 222.1.1.1. Bus Priority. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 222.1.1.2. Bus Performance Counters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 232.1.2. Atomic Register Access. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 242.1.3. APB Bridge. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 242.1.4. Narrow IO Register Writes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 242.1.5. List of Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 252.2. Address Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 282.2.1. Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 282.2.2. Detail. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 292.3. Processor subsystem. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 312.3.1. SIO. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 312.3.1.1. CPUID. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 322.3.1.2. GPIO Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 322.3.1.3. Hardware Spinlocks. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 342.3.1.4. Inter-processor FIFOs (Mailboxes). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 342.3.1.5. Integer Divider. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 352.3.1.6. Interpolator. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 362.3.1.6.1. Lane Operations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 372.3.1.6.2. Blend Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 402.3.1.6.3. Clamp Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 422.3.1.6.4. Sample Use Case: Linear Interpolation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 432.3.1.6.5. Sample Use Case: Simple Affine Texture Mapping. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 442.3.1.7. List of Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 462.3.2. Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 752.3.3. Event Signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 752.3.4. Debug. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 762.3.4.1. Software control of SWD pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 762.3.4.2. Rescue DP. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 762.4. Cortex-M0+. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 772.4.1. Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 772.4.1.1. Interfaces. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 772.4.1.2. Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 782.4.1.3. ARM architecture. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 782.4.2. Functional Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 782.4.2.1. Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 782.4.2.2. Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 792.4.2.3. NVIC features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 792.4.2.4. Debug features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 792.4.2.4.1. Debug Access Port. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 802.4.2.5. MPU features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 802.4.2.8. Power Management Unit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 802.4.2.8.1. Power Management. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 812.4.2.8.2. Wait For Event and Send Event. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 812.4.2.8.3. Wait For Interrupt. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 822.4.2.8.4. Wakeup Interrupt Controller. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 822.4.2.9. Reset Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 822.4.3. Programmer’s model. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 832.4.3.1. About the programmer’s model. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 832.4.3.2. Modes of operation and execution. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 832.4.3.3. Instruction set summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 832.4.3.4. Memory model. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 862.4.3.5. Processor core registers summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 872.4.3.6. Exceptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 872.4.3.6.1. Exception handling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 872.4.4. System control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 882.4.4.1. System control register summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 882.4.4.1.1. CPUID Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 882.4.5. NVIC. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 892.4.5.1. About the NVIC. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 892.4.5.1.1. SysTick timer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 892.4.5.1.2. Low power modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 892.4.5.2. NVIC register summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 892.4.6. MPU. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 902.4.6.1. About the MPU. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 902.4.6.2. MPU register summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 902.4.7. Debug. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 902.4.8. List of Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91 2.5. Memory. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1042.5.1. ROM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1052.5.2. SRAM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1052.5.2.1. Other On-chip Memory. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1062.5.3. Flash. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1062.5.3.1. XIP Cache. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1072.5.3.2. Cache Flushing and Maintenance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1082.5.3.3. SSI. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1082.5.3.4. Flash Streaming and Auxiliary Bus Slave. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1092.5.3.5. Performance Counters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1092.5.3.6. List of XIP Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110 2.6. Boot Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113 2.7. Bootrom. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1132.7.1. Bootrom Source. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1142.7.2. Processor Controlled Boot Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1142.7.2.1. Watchdog Boot. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1152.7.2.2. Flash Boot Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1152.7.2.3. Flash Second Stage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1162.7.2.3.1. Checksum. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1162.7.3. Bootrom Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1162.7.3.1. Bootrom Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1172.7.3.1.1. Fast Bit Counting / Manipulation Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1172.7.3.1.2. Fast Bulk Memory Fill / Copy Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1182.7.3.1.3. Flash Access Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1182.7.3.1.4. Debugging Support Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1192.7.3.1.5. Miscellaneous Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1202.7.3.2. Fast Floating Point Library. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1202.7.3.2.1. Implementation Details. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1202.7.3.2.2. Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1212.7.3.3. Bootrom Data. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1272.7.4. USB Mass Storage Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1272.7.5. USB PICOBOOT Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1292.7.5.1. Identifying The Device. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1292.7.5.2. Identifying The Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1292.7.5.3. Identifying The Endpoints. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1302.7.5.4. PICOBOOT Commands. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1302.7.5.4.1. EXCLUSIVE_ACCESS (0x01). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1302.7.5.4.2. REBOOT (0x02). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1312.7.5.4.3. FLASH_ERASE (0x03). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1312.7.5.4.4. READ (0x84). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1322.7.5.4.5. WRITE (0x05). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1322.7.5.4.6. EXIT_XIP (0x06). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1322.7.5.4.7. ENTER_XIP (0x07). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1322.7.5.4.8. EXEC (0x08). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1332.7.5.4.9. VECTORIZE_FLASH (0x09). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1332.7.5.5. Control Requests. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1342.7.5.5.1. INTERFACE_RESET (0x41). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1342.7.5.5.2. GET_COMMAND_STATUS (0x42). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134 2.8. Power Supplies. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1352.8.1. Digital IO Supply (IOVDD). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1352.8.2. Digital Core Supply (DVDD). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1362.8.3. On-Chip Voltage Regulator Input Supply (VREG_IOVDD). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1362.8.4. USB PHY Supply (USB_IOVDD). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1362.8.5. ADC Supply (ADC_IOVDD). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1362.8.6. Power Supply Sequencing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1372.8.7. Power Supply Schemes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1372.8.7.1. Single3.3V Supply. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1372.8.7.2. External Core Supply. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1382.8.7.3. 1.8V Digital IO with Functional USB and ADC. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1382.8.7.4. Single 1.8V Supply. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139 2.9. On-Chip Voltage Regulator. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1392.9.1. Application Circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1402.9.2. Operating Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1402.9.2.1. Normal Operation Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1402.9.2.2. High Impedance Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1412.9.2.3. Shutdown Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1412.9.3. Output Voltage Select. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1412.9.4. Status. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1412.9.5. Current Limit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1412.9.6. List of Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1412.9.7. Detailed Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144 2.10. Power Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1442.10.1. Top-level Clock Gates. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1442.10.2. SLEEP State. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1452.10.3. DORMANT State. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1452.10.4. Memory Power Down. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1452.10.5. Programmer’s Model. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1462.10.5.1. Sleep. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1462.10.5.2. Dormant. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147 2.11. Chip-Level Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1472.11.1. Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1472.11.2. Power-on Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1482.11.2.1. Detailed Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1482.11.3. Brown-out Detection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1492.11.3.1. Detection Enable. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1492.11.3.2. Adjusting the Detection Threshold. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1502.11.3.3. Detailed Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1502.11.4. Supply Monitor. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1512.11.4.1. Detailed Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151。

Decoupling Capacitors

Decoupling Capacitors电子制作2007-10-15 20:10:45 阅读143 评论0 字号:大中小在数字电路中,我们常常见到在数字芯片的电源管脚附近放置了电容,它们也可能集中出现在原理图的某一页中,但在Layout的过程中,这些电容还会最终被分配给数字芯片的电源管脚。

通常大家称其为去藕或者滤波电容,其作用自然也无非就是去藕或者滤波了。

然而对于这些电容的叫法和作用存在一定的争议和误解。

Decoupling和Filtering分别是去藕和滤波的英文翻译,相信大家对滤波的意义都很清楚,电子学上的Filtering无非就是通过某种手段,从频率上加以区分,去除掉不想要的或者保留希望得到的信号的过程。

再谈去藕,我们都知道耦合的意思,通常会见到,直流耦合,交流耦合,电阻耦合和电容耦合等等说法,无非是将一个信号或者一部分能量通过某种方法,施加到另外一个信号或者部分能量上面。

而Decoupling的意思是,必然和Coupling是相对应的,就是通过某种方法阻止信号或者能量在某一点的传递。

滤波是实现去藕多种方式中的一种。

这里关于电容的讨论里面,去藕和滤波这两个概念是等同的。

旁路(Bypass)电容是另外一种叫法,其意思无非是给某一个频率的信号或者能量提供了一个通道,等同于上述的滤波。

在真正理解了这些电容在数字电路中的作用以后,称谓也就变得不重要了。

那么究竟是什么原因致使需要这些的电容的存在哪?数字芯片的电源有两个作用,一是为里面的逻辑电路工作提供能量;二是提供一个参考电平,为输入信号提供一个判决的参考-------差分输入的电路除外,差分电路的两个输入彼此参考。

针对第一个功能,要提供稳定充足的电流和电压,作为参考电平,自然对电压有一定的要求。

造成电源不理想的因素大致有如下几个:电源自身纹波,噪声以及数字电路工作在开关状态时引起的电流电压的波动。

由于电源自身的工作原理决定了,电源自身纹波不可避免,尤其是开关电源,所以通常可以看到电源的输出端会放置几颗电容,来滤除纹波-----道理自然很简单,纹波是施加在直流上面的交流成份,利用电容通交隔直作用,避免纹波被施加到后面电路。

知从青龙BOOTLOADER产品手册说明书

知从青龙BOOTLOADER产品手册知从®青龙BootLoader1功能概述知从青龙BootLoader是由知从科技自主研发的程序刷新软件(BootLoader)。

使用知从青龙BootLoader的控制器,可以通过CAN、LIN、SPI等通信方式实现应用程序的更新功能。

目前,知从青龙BootLoader已支持NXP、Infineon、Renesas、ST等多家芯片,并且支持多家整车厂程序刷新规范,可提供定制开发服务。

通常每家整车厂都有各自的程序刷新规范,目前知从青龙BootLoader支持的整车厂程序刷新规范包括:广汽、长安、上汽、一汽、东风商用车、东风、上海通用、吉利、奇瑞、上汽通用五菱、萨博、长城、北汽新能源等(以上排名不分先后)。

2应用领域知从青龙BootLoader可应用于整车各个域中的控制器程序刷新功能。

支持的控制器包括:车身系统车身控制器、空调控制器、车门控制器、网关等动力系统发动机控制器、电池管理系统、电机控制器、整车控制器等底盘系统电动助力转向系统、制动防抱死系统、电气稳定系统等ADAS系统雷达、摄像头系统等3芯片支持4开发背景目前,汽车上的电子电气架构越来越复杂,并伴随着汽车的电动化、智能化、网联化、共享化,软件的研发在汽车上占比越来越大。

软件更新的频率越来越高。

而且,在汽车的整个生命周期中,包括研发阶段、生产阶段、售后阶段,各个阶段都需要实现软件的更新功能。

因此,客户对软件程序更新的需求越来越迫切。

对于整车厂或供应商,BootLoader是控制器开发必备的功能。

并且,不同的整车厂有不同的程序更新规范,同时BootLoader驱动又依赖于不同的芯片。

因此,为了满足不同的整车厂程序更新规范,又适配不同的芯片,知从科技提供了完整的BootLoader解决方案—知从青龙BootLoader。

知从青龙BootLoader既适用于不同的整车厂程序更新规范,又适用于不同芯片厂商的芯片,让客户更专注与自己的控制器产品研发。

kb9012qf工作原理

KB9012QF是由仁宝(Compal)生产的主板EC(Embedded Controller),这款芯片在2012年进行了升级。

其工作原理是将BIOS程序内置于芯片内部,不同于传统的将BIOS存储于外部的128KB闪存中。

除了BIOS管理之外,KB9012QF还负责各种硬件初始化和电源管理功能。

当你打开或关闭计算机时,EC会执行一系列自检程序,以确保所有硬件都在正常工作状态。

如果发现任何问题,EC会生成相应的错误代码并显示在屏幕上。

KB9012QF还具有高级电源管理(APM)功能,这是早期用于管理笔记本电脑电池寿命的一种技术。

通过这种技术,EC可以自动调整系统性能和功耗,以延长电池寿命。

HCPL788J中文资料

VDD2 10

8 GND1

GND2 9

µC 0.1 µF

4.7 kΩ TO OTHER PHASE OUTPUTS A/D VREF

GND

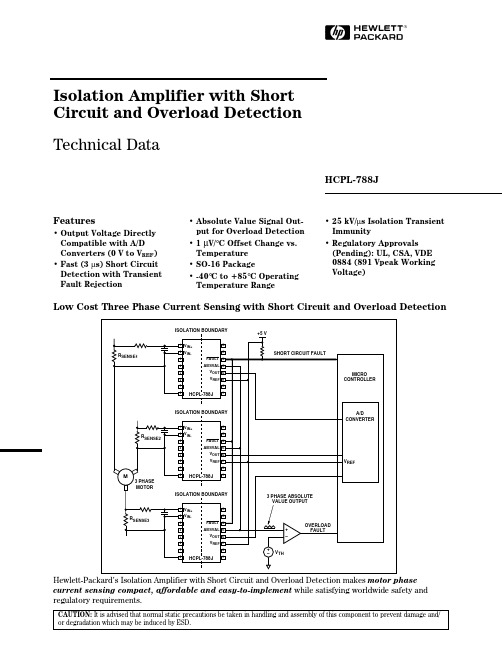

Figure 1. Current Sensing Circuit.

Pin Descriptions

Symbol

Description

VIN+ Positive input voltage (± 200 mV recommended).

12345678

0.406 ± 0.10 (10.312 ± 0.254) 9°

0.345 ± 0.010 (8.986 ± 0.254)

ALL LEADS TO BE COPLANAR ± 0.002

Package Characteristics

Parameter

Symbol

Input-Output Momentary

INPUT

+

CURRENT RSHUNT

0.02 Ω

39 Ω .01 µF

0.1 µF

ISOLATED +5 V

0.1 µF

1 VIN+

HCPL-788J

GND2 16

2 VIN-

VDD2 15

3 CH

FAULT 14

4 CL

ABSVAL 13

5 VDD1

VOUT 12

6 VLED+

VREF 11

7 VDD1

CAUTION: It is advised that normal static precautions be taken in handling and assembly of this component to prevent damage and/ or degradation which may be induced by ESD.

FS2115B夸克微芯片规格书

F e a t u r e sFixed 5V ± 4% OutputVIN Range: 2.5V to 5VOutput Current: Up to 250mAConstant Frequency Operation at All Loads Low Noise Constant Frequency (400kHz) OperationAutomatic Soft-Start Reduces Inrush CurrentShutdown Current <1µAShort-Circuit ProtectionNo InductorsAvailable in Low Profile 6-Lead SOT23 PackageA p p l i c a t i o nWhite LED BacklightingLi-Ion Battery Backup SuppliesLocal 3V to 5V ConversionSmart Card ReadersPCMCIA Local 5V Supplies D e s c r i p t i o nThe FS2115B is a low noise, constant frequency (400kHz) switched capacitor voltage doubler. It produce a regulated output voltage from a 2.5V to 4.5V input with up to 250mA of output current. Low external parts count (one flying capacitor and two small bypass capacitors at VIN and VOUT) make the FS2115B ideally suited for small, battery-powered applications.A new charge-pump architecture maintains constant switching frequency to zero load and reduces both output and input ripple. The FS2115B have thermal shutdown capability and can survive a continuous short circuit from VOUT to GND. Built-in soft-start circuitry prevents excessive inrush current during start-up.High switching frequency enables the use of small ceramic capacitors. A low current shutdown feature disconnects the load from VIN and reduces quiescent current to <1uA.The FS2115B is available in the industry standard SOT-23-6 power packages.T y p i c a l A p p l i c a t i o n sFigure 1: Regulated 5V Output Figure 2: USB Port to Regulated 5V Power SupplyFigure 3: Lithium-Ion Battery to 5V White or Blue LED DriversP i n D e s c r i p t i o nPIN NUMBER SOT-23-6PIN NAME 1 VOUT 2 GND 3 EN 4 C- 5 VIN 6C+FS2115B夸克微原厂技术支持A b s o l u t e M a x i m u m R a t i n g s (Note 1)V IN ……………………………….…………………………….…….….…..….………- 0.3V to 6V V OUT ………………………………………………………………………………….….- 0.3V to 5.5V VOUT Short-circuit Duration.…………………………………………..….………………indefinite V EN ……………………………………………………...…………………….…...……- 0.3V to 6V IOUT (Note 2) …………………….................................………………………...................... 300mA Operating Temperature Range (Note 3)……………………………………………...……- 30℃ to 85℃ Lead Temperature (Soldering 10 sec.) ……………………………………..………………300℃ Storage Temperature Range ………………………………………………..…..- 65℃ to 125℃Note 1: Absolute Maximum Ratings are those values beyond which the life of a device may be impaired. Note 2: Based on long term current density limitations.Note 3: The FS2115B are guaranteed to meet performance speci fications from 0°C to 70°C. Specifications over the –40°C to 85°C operating temperature range are assured by design, characterization and correlation with statistical process controls.E l e c t r i c a l C h a r a c t e r i s t i c sThe specifications are at TA = 25 ℃. EN= V IN , C IN =C OUT =2.2uF unless otherwise noted. * EFFI = [(Output Voltage × Output Current) / (Input Voltage × Input Current)] × 100%PARAMETERC O ND I T I O N S MIN TYP MAX UNITS Input Voltage Range (V IN )2.55.5 V Output Voltage Range (V OUT ) 2.7V <V IN < 5.5V, I OUT < 65mA 4.7 5 5.2 VI SHDN Shutdown Current EN=0V,V OUT = 0V 0.3 µA No load input current I OUT = 0mA, V IN = 2.7V 0.65 mA Output current limit250 mA Output Ripple (VR) V IN = 2.7V , I OUT = 100mA 150 mVP-P EfficiencyV IN = 2.7V, I OUT =100mA 81 %Open-Loop Output Resistance R OL =(2V IN -V OUT )/I OUTV IN = 2.7V, I OUT = 100mA 4 Ω Switching Frequency ( f osc )400kHzFS2115B夸克微原厂技术支持FS2115B T y p i c a l P e r f o r m a n c e C h a r a c t e r i s t i c sVOUT Soft-Start Ramp (VIN=3V)P i n F u n c t i o n sVOUT (Pin 1): Regulated Output Voltage. VOUT should be bypassed with a low ESR ceramic capacitor providing at least 2µF of capacitance as close to the pin as possible for best performance.GND (Pin 2): Ground. These pins should be tied to a ground plane for best performance. The exposed pad must be soldered to PCB ground to provide electrical contact and optimum thermal performance. EN (Pin 3): Active Low Shutdown Input. This pin must not be allowed to float. C- (Pin 4): Flying Capacitor Negative Terminal.VIN (Pin 5): Input Supply Voltage. VIN should be bypassed with a 1µF to 4.7µF low impedance ceramic capacitor.C+ (Pin 6): Flying Capacitor Positive Terminal.FS2115BFS2115B A p p l i c a t i o n I n f o r m a t i o nOperationThe FS2115B use a switched capacitor charge pump to boost VIN to a regulated output voltage. Regulation is achieved by sensing the output voltage through an internal resistor divider and modulating the charge pump output current based on the error signal. A 2-phase nonoverlapping clock activates the charge pump switches. The flying capacitor is charged from VIN on the first phase of the clock. On the second phase of the clock it is stacked in series with VIN and connected to VOUT. This sequence of charging and discharging the flying capacitor continues at a free running frequency of 0.4MHz (typ).In shutdown mode all circuitry is turned off and the FS2115B draw only leakage current from the VIN supply. Furthermore, VOUT is disconnected from VIN. The EN pin is a CMOS input with a threshold voltage of approximately 0.8V. The FS2115B is in shutd own when a logic low is applied to the EN pin. Since the EN pin is a high impedance CMOS input it should never be allowed to float. To ensure that its state is defined it must always be driven with a valid logic level.Short-Circuit ProtectionThe FS2115B have built-in short-circuit current limitin g. During short-circuit conditions, they will automatically limit their output current to approximately 200mA.Soft-StartThe FS2115B have built-in soft-start circuitry to prevent excessive current flow at VIN during start-up. The soft-start time is preprogrammed to approximately 1ms, so the start-up current will be primarily dependent upon the output capacitor.VIN, VOUT Capacitor SelectionThe style and value of capacitors used with the FS2115B d etermine several important parameters suchas regulator control loop stability, output ripple, charge pump strength and minimum start-up time.To reduce noise and ripple, it is recommended that low ESR (< 0.1Ω) ceramic capacitors be used for both CIN and COUT. These capacitors should be 0.47uF or greater. Tantalum and aluminum capacitors are not recommended because of their high ESR.The value of COUT directly controls the amount of output ripple for a given load current. Increasing the size of COUT will reduce the output ripple at the expense of higher minimum turn on time and higher start-up current. The peak-to-peak output ripple is approximately given by the expression:Where f OSC is the FS2115B oscillator frequency (typically 0.4MHz) a nd COUT is the output charge storage capacitor.FS2115B Both the style and value of the output capacitor can significantly affect the stability of the FS2115B. The FS2115B use a linear control loop to adjust the stren gth of the charge pump to match the current required at the output. The error signal of this loop is stored directly on the output charge storage capacitor. The charge storage capacitor also serves to form the dominant pole for the control loop. To prevent ringing or instability on the FS2115B it is important for the output capacitor to maintain at least 0.47uF of capacitance over all conditions.Likewise excessive ESR on the output capacitor will tend to degrade the loop stability of theFS2115B Ceramic capacitors typically have exceptional ESR performance and combined with a tight board layout should yield very good stability and load transient performance.As the value of COUT controls the amount of output ripple, the value of CIN controls the amount of ripple present at the input pin (VIN). The input current to the FS2115B will be relatively constant while t he charge pump is on either the input charging phase or the output charging phase but will drop to zero during the clock nonoverlap times. Since the nonoverlap time is small (~25ns), these missing “notches” will result in only a small perturbation on the input power supply line. Note that a higher ESR capacitor such as tantalum will have higher input noise due to the input current change times the ESR. Therefore ceramic capacitors are again recommended for their exceptional ESR performance.Flying Capacitor SelectionWarning: A polarized capacitor such as tantalum or aluminum should never be used for the flying capacitor since its voltage can reverse upon start-up of the FS2115B. Low ESR ceramic capacitors should always be used for the flying capacitor.The flying capacitor controls the strength of the charge pump. In order to achieve the rated output current it is necessary to have at least 0.68uF of capacitance for the flying capacitor.For very light load applications the flying capacitor may be reduced to save space or cost. The theoretical minimum output resistance of a voltage doubling charge pump is given by:Where f OSC is the switching frequency (0.4Hz typ) and CFLY is the value of the flying capacitor. The charge pump will typically be weaker than the theoretical limit due to additional switch resistance, however for very light load applications the above expression can be used as a guideline in determininga starting capacitor value.Power EfficiencyThe power efficiency of the FS2115B is similar to that of a linear regulator with an effective input voltageof twice the actual input voltage. This occurs because the input current for a voltage doubling charge pump is approximately twice the output current. In an ideal regulating voltage doubler the power efficiency would be given by:FS2115BAt moderate to high output power the switching losses and quiescent current of the FS2115B are negligible and the expression above is valid. For example with VIN = 3V, IOUT = 50mA and VOUT =5V the measured efficiency is 80% which is in close agreement with the theoretical 83.3% calculation.Layout ConsiderationsDue to its high switching frequency and the high transient currents produced by the FS2115B, careful board layout is necessary. A true ground plane and short connections to all capacitors will improve performance and ensure proper regulation under all conditions. Figure 4 shows an example layout for the FS2115B.Figure 4: Recommended LayoutP a c k a g i n g I n f o r m a t i o nSOT-23-6 Package Outline DimensionDimensions In Millimeters Dimensions In Inches SymbolMin Max Min MaxA 1.050 1.250 0.041 0.049A1 0.000 0.100 0.000 0.004 A2 1.050 1.150 0.041 0.045b 0.300 0.500 0.012 0.020c 0.100 0.200 0.004 0.008D 2.820 3.020 0.111 0.119E 1.500 1.700 0.059 0.067E1 2.650 2.950 0.104 0.116e 0.950(BSC) 0.037(BSC)e1 1.800 2.000 0.071 0.079 L 0.300 0.600 0.012 0.024 θ0°8°0°8°FS2115B。

ADuC8XX系列常见问题解答

ADuC8XX系列常见问题解答问题:ADUC8XX系列的开发方法和开发工具是怎样的?答案:ADuC8xx的开发方法是非常简便的。

ADUC8XX系列提供了评估板套件,以帮助用户熟悉ADuC8xx的开发方法和开发环境。

以ADUC831为例,EVAL- ADUC831QSZ套件包括评估板一块,下载线,9V电源和相应的软件光盘。

评估版套件中的光盘中包含了开发中用到的所有的软件,数据手册,应用笔记,评估板原理图、例子代码等信息。

如果没有购买评估板的用户想要得到此光盘, 可以联系800-810-1742或者发email至china.support@索取。

下面根据光盘中提供的各种开发软件对开发方法做一介绍。

1.Aspire它是一个集成开发环境。

可以编辑、编译、仿真及在线调试基于汇编语言和C语言的程序。

如果要使用在线调试功能,需要使用ACCUTRON公司的ACE仿真器。

这个ACE仿真器与PC的接口是USB,与芯片的接口只需一个管脚,所以称为单管脚调试。

2.Keil它是一个集成开发环境。

它支持编辑、编译、软件仿真。

目前最新版本的Keil C51支持UART口直接硬件在线调试,而不需仿真器(ACE)。

用户可在Keil的网站下载最新版本的软件。

3.WSD它是下载程序的工具。

当用Aspire或Keil编译生成*.hex文件后,可以用此软件把程序从PC上下载到芯片中。

PC与芯片之间的连接是通过串口实现的。

在两种评估板套件中,都包含了串口下载线。

如果没有购买评估板套件,您也可以自己在市场上买一根串口线。

但是需要在您的电路板上加入一颗RS232电平转换芯片。

如果您已经有ACE 仿真器,也可以不用WSD,而用ACE直接下载。

4.DEBUGV2它是在线调试汇编语言的工具。

也是通过串口来实现的。

不需要任何仿真器。

5.WASP它是用来评估ADuC8xx产品内部ADC性能的软件。

它也是通过串口与芯片通信。

不需要任何仿真器。

如需更加详细的软件使用方法,请参看光盘中的文档8XXGetStartedvx.x.pdf。

LNK625DG;LNK623DG;LNK623PG;LNK625PG;LNK626PG;中文规格书,Datasheet资料

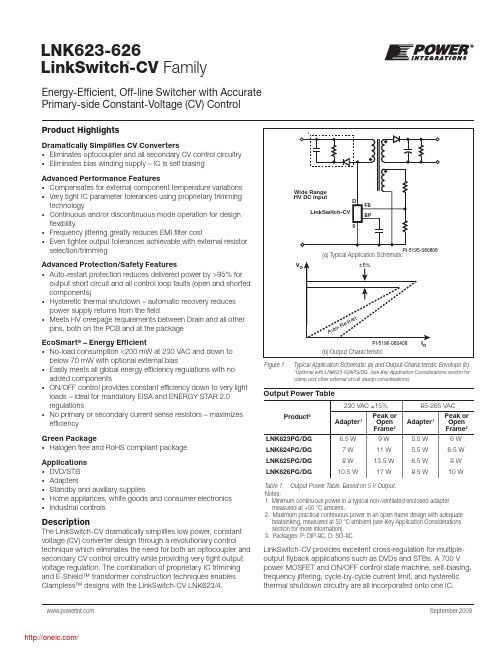

LNK623-626LinkSwitch-CV Family September 2009Energy-Effi cient, Off-line Switcher with Accurate Primary-side Constant-Voltage (CV) Control®Output Power TableProduct 3230 VAC ±15%85-265 VAC Adapter 1Peak or Open Frame 2Adapter 1Peak or Open Frame 2LNK623PG/DG 6.5 W 9 W 5.0 W 6 W LNK624PG/DG 7 W 11 W 5.5 W 6.5 W LNK625PG/DG 8 W 13.5 W 6.5 W 8 W LNK626PG/DG10.5 W17 W8.5 W10 WTable 1. Output Power Table. Based on 5 V Output. Notes:1. Minimum continuous power in a typical non-ventilated enclosed adapter measured at +50 °C ambient.2. Maximum practical continuous power in an open frame design with adequate heatsinking, measured at 50 °C ambient (see Key Application Considerations section for more information).3. Packages: P: DIP-8C, D: SO-8C.Product HighlightsDramatically Simplifi es CV Converters• Eliminates optocoupler and all secondary CV control circuitry • Eliminates bias winding supply – IC is self biasingAdvanced Performance Features• Compensates for external component temperature variations • Very tight IC parameter tolerances using proprietary trimming technology• Continuous and/or discontinuous mode operation for design fl exibility• Frequency jittering greatly reduces EMI fi lter cost• Even tighter output tolerances achievable with external resistor selection/trimming Advanced Protection/Safety Features• Auto-restart protection reduces delivered power by >95% for output short circuit and all control loop faults (open and shorted components)• Hysteretic thermal shutdown – automatic recovery reduces power supply returns from the fi eld• Meets HV creepage requirements between Drain and all other pins, both on the PCB and at the package EcoSmart ® – Energy Effi cient• No-load consumption <200 mW at 230 VAC and down to below 70 mW with optional external bias • Easily meets all global energy effi ciency regulations with no added components• ON/OFF control provides constant effi ciency down to very light loads – ideal for mandatory EISA and ENERGY STAR 2.0 regulations• No primary or secondary current sense resistors – maximizes effi ciency Green Package• Halogen free and RoHS compliant packageApplications • DVD/STB • Adapters• Standby and auxiliary supplies• Home appliances, white goods and consumer electronics • Industrial controlsDescriptionThe LinkSwitch-CV dramatically simplifies low power, constant voltage (CV) converter design through a revolutionary control technique which eliminates the need for both an optocoupler and secondary CV control circuitry while providing very tight output voltage regulation. The combination of proprietary IC trimming and E-Shield™ transformer construction techniques enables Clampless™ designs with the LinkSwitch-CV LNK623/4.Figure 1. Typical Application Schematic (a) and Output Characteristic Envelope (b).*Optional with LNK623-624PG/DG. (see Key Application Considerations section forclamp and other external circuit design considerations).LinkSwitch-CV provides excellent cross-regulation for multiple-output flyback applications such as DVDs and STBs. A 700 V power MOSFET and ON/OFF control state machine, self-biasing, frequency jittering, cycle-by-cycle current limit, and hysteretic thermal shutdown circuitry are all incorporated onto one IC.Rev. E 09/09Pin Functional DescriptionDRAIN (D) Pin:This pin is the power MOSFET drain connection. It provides internal operating current for both start-up and steady-state operation.BYPASS (BP) Pin:This pin is the connection point for an external bypass capacitor for the internally generated 6 V supply.FEEDBACK (FB) Pin:During normal operation, switching of the power MOSFET is controlled by this pin. This pin senses the AC voltage on the bias winding. This control input regulates the output voltage based on the fl yback voltage of the bias winding.SOURCE (S) Pin:This pin is internally connected to the output MOSFET source for high voltage power and control circuit common returns.Figure 2 Functional Block Diagram.Figure 3. Pin Confi guration.Rev. E 09/09LinkSwitch-CV Functional DescriptionThe LinkSwitch-CV combines a high voltage power MOSFET switch with a power supply controller in one device. Similar to the LinkSwitch-LP and TinySwitch-III it uses ON/OFF control to regulate the output voltage. The LinkSwitch-CV controllerconsists of an oscillator, feedback (sense and logic) circuit, 6 V regulator, over-temperature protection, frequency jittering, current limit circuit, leading-edge blanking, and ON/OFF state machine for CV control.Constant Voltage (CV) OperationThe controller regulates the feedback pin voltage to remain at V FBth using an ON/OFF state-machine. The feedback pinvoltage is sampled 2.5 μs after the turn-off of the high voltage switch. At light loads the current limit is also reduced to decrease the transformer fl ux density. Auto-Restart and Open-Loop ProtectionIn the event of a fault condition such as an output short or an open loop condition the LinkSwitch-CV enters into an appropriate protection mode as described below.In the event the feedback pin voltage during the Flyback period falls below V FBth -0.3 V before the feedback pin sampling delay (~2.5 μs) for a duration in excess of 200 ms (auto-restart on-time (t AR-ON ) the converter enters into Auto-restart, wherein the power MOSFET is disabled for 2.5 seconds (~8% Auto-Restart duty cycle). The auto-restart alternately enables and disables the switching of the power MOSFET until the fault condition is removed.In addition to the conditions for auto-restart described above, if the sensed feedback pin current during the Forward period of the conduction cycle (switch “on” time) falls below 120 μA, theconverter annunciates this as an open-loop condition (topresistor in potential divider is open or missing) and reduces the Auto-restart time from 200 ms to approximately 6 clock cycles (90 μs), whilst keeping the disable period of 2.5 seconds. This effectively reduces the Auto-Restart duty cycle to less than 0.01%.Over-Temperature ProtectionThe thermal shutdown circuitry senses the die temperature. The threshold is set at 142 °C typical with a 60 °C hysteresis. When the die temperature rises above this threshold (142 °C) the power MOSFET is disabled and remains disabled until the die temperature falls by 60 °C, at which point the MOSFET is re-enabled.Current LimitThe current limit circuit senses the current in the power MOSFET. When this current exceeds the internal threshold(I LIMIT ), the power MOSFET is turned off for the remainder of that cycle. The leading edge blanking circuit inhibits the current limit comparator for a short time (t LEB ) after the power MOSFET is turned on. This leading edge blanking time has been set so that current spikes caused by capacitance and rectifi er reverse recovery time will not cause premature termination of the MOSFET conduction.6.0 V RegulatorThe 6 V regulator charges the bypass capacitor connected to the BYPASS pin to 6 V by drawing a current from the voltage on the DRAIN, whenever the MOSFET is off. The BYPASS pin is the internal supply voltage node. When the MOSFET is on, the device runs off of the energy stored in the bypass capacitor. Extremely low power consumption of the internal circuitry allows the LinkSwitch-CV to operate continuously from the current drawn from the DRAIN pin. A bypass capacitor value of 1 μF is suffi cient for both high frequency decoupling and energy storage.Rev. E 09/09Applications ExampleCircuit DescriptionThis circuit is confi gured as a three output, primary-side regulated fl yback power supply utilizing the LNK626PG. It can deliver 7 W continuously and 10 W peak (thermally limited) from an universal input voltage range (85 – 265 VAC). Effi ciency is >67% at 115 VAC/230 VAC and no-load input power is <140 mW at 230 VAC.Input FilterAC input power is rectifi ed by diodes D1 through D4. The rectifi ed DC is fi ltered by the bulk storage capacitors C1 and C2. Inductor L1, L2, C1 and C2 form a pi (π) fi lter, which attenuates conducted differential-mode EMI noise. This confi guration along with Power Integrations transformerE-shield ™ technology allow this design to meet EMI standard EN55022 class B with good margin without requiring aY capacitor. Fuse F1 provides protection against catastrophic failure. Negative temperature coeffi cient thermistor RT1 limits the inrush current when AC is fi rst applied to below themaximum rating of diodes D1 through D4. Metal oxide varistor RV1 clamps the AC input during differential line transients, protecting the input components and maintaining the peakdrain voltage of U1 below its 700 V BV DSS rating. For differential surge levels at or below 2 kV this component may be omitted.LNK626 PrimaryThe LNK626PG device (U1) incorporates the power switching device, oscillator, CV control engine, startup, and protectionfunctions. The integrated 700 V MOSFET provides a large drain voltage margin in universal input AC applications, increasing reliability and also reducing the output diode voltage stress by allowing a greater transformer turns ratio. The device can be completely self-powered from the BYPASS pin and decoupling capacitor C4. In this design a bias circuit (D6, C6 and R4) was added to reduce no load input power below 140 mW.The rectifi ed and fi ltered input voltage is applied to one side of the primary winding of T1. The other side of the transformer’s primary winding is driven by the integrated MOSFET in U1. The leakage inductance drain voltage spike is limited by the clamp circuit D5, R1, R2, C3 and VR1. The zener bleed clamparrangement was selected for lowest no-load input power but in applications where higher no-load input power is acceptable VR1 may be omitted and the value of R1 increased to form a standard RCD clamp.Output Rectifi cationThe secondaries of the transformer are rectifi ed by D7, D8 and D9. A Schottky barrier type was used for the main 5 V output for higher effi ciency. The +12 V and -22 V outputs use an ultrafast rectifi er diode. The main output is post fi ltered by L3 and C10 to remove switching frequency ripple. Resistors R7, R8 and R9 provide a preload to maintain the output voltages within their respective limits when unloaded. To reduce high frequency ringing and associated radiated EMI an RC snubber formed by R10 and C13 was added across D7.Figure 4. 7 W (10 W peak) Multiple Output Flyback Converter for DVD Applications with Primary Sensed Feedback.Rev. E 09/09Output RegulationThe LNK626 regulates the output using ON/OFF control, enabling or disabling switching cycles based on the sampled voltage on the FEEDBACK pin. The output voltage is sensed using a primary referenced winding on transformer T1 eliminating the need for an optocoupler and a secondary sense circuit. The resistor divider formed by R3 and R6 feeds the winding voltage into U1. Standard 1% resistor values were used to center the nominal output voltages. Resistor R5 and C5 reduce pulse grouping by creating an offset voltage that is proportional to the number of consecutive enabled switching cycles. Key Application ConsiderationsOutput Power TableThe data sheet maximum output power table (Table 1)represents the maximum practical continuous output power level that can be obtained in a Flyback converter under the following assumed conditions:1. The minimum DC input voltage is 100 V or higher at 90 VACinput. The value of the input capacitance should be large enough to meet these criteria for AC input designs.2. Secondary output of 5 V with a Schottky rectifi er diode.3. Assumed effi ciency of 80%.4. Continuous conduction mode operation (K P = 0.4).5. Refl ected Output Voltage (V OR ) of 110 V .6. The part is board mounted with SOURCE pins soldered to asuffi cient area of copper to keep the SOURCE pin tempera-ture at or below 110 °C for P package and 100 °C for D packaged devices.7. Ambient temperature of 50 °C for open frame designs andan internal enclosure temperature of 60 °C for adapter designs.Note: Higher output power are achievable if the effi ciency is higher than 80%, typically for high output voltage designs.Bypass Pin CapacitorA 1 μF Bypass pin capacitor (C4) is recommended. The capacitor voltage rating should be equal to or greater than 6.8 V. The capacitor’s dielectric material is not important. The capacitor must be physically located close to the LinkSwitch-CV BYPASS pin.Circuit board layoutLinkSwitch-CV is a highly integrated power supply solution that integrates on a single die, both the controller and the highvoltage MOSFET. The presence of high switching currents and voltages together with analog signals makes it especiallyimportant to follow good PCB design practice to ensure stable and trouble free operation of the power supply.When designing a board for the LinkSwitch-CV based power supply, it is important to follow the following guidelines:Single Point GroundingUse a single point (Kelvin) connection at the negative terminal of the input fi lter capacitor for the LinkSwitch-CV SOURCE pin and bias winding return. This improves surge capabilities by returning surge currents from the bias winding directly to the input fi lter capacitor. Bypass CapacitorThe BYPASS pin capacitor should be located as close as possible to the SOURCE and BYPASS pins.Feedback ResistorsPlace the feedback resistors directly at the FEEDBACK pin of the LinkSwitch-CV device. This minimizes noise coupling.Thermal ConsiderationsThe copper area connected to the source pins provide the LinkSwitch-CV heat sink. A rule of thumb estimate is that the LinkSwitch-CV will dissipate 10% of the output power. Provide enough copper area to keep the source pin temperature below 110° C to provide margin for part to part R DS(ON) variation.Secondary Loop AreaTo minimize leakage inductance and EMI, the area of the loop connecting the secondary winding, the output diode and the output fi lter capacitor should be minimized. In addition, suffi cient copper area should be provided at the anode and cathode terminal of the diode for heatsinking. A larger area is preferred at the quiet cathode terminal. A large anode area can increase high frequency radiated EMI.Electrostatic Discharge Spark GapIn chargers and adapters ESD discharges may be applied to the output of the supply. In these applications the addition of a spark gap is recommended. A trace is placed along theisolation barrier to form one electrode of a spark gap. The other electrode, on the secondary side, is formed by the output return node. The arrangement directs ESD energy from the secondary to the primary side AC input. A 10 mil gap is placed near the AC input. The gap decouples any noise picked up on the spark gap trace to the AC input. The trace from the AC input to the spark gap electrode should be spaced away from other traces to prevent unwanted arcing occurring and possible circuit damage.Rev. E 09/096Figure 5. PCB Layout Example.Figure 6. Schematic Representation of Recommended Layout Without External Bias.Figure 7. Schematic Representation of Recommended Layout WithExternal Bias.+-AC INPI-5269-122408Y1-Capacitor(optional)Isolation Barrier TransformerT1Output RectifiersPrimary SideSecondary SideR1JP1J1C1R3R4C12R10D9C11C13D7C9R9R8D816R7C8L3C10C2R2C3D1D3D5VR1D6C6R6R5C5C4D4RV1F1D2RT1L2L1J2Input Filter Capacitor Drain trace area miniminzed ClampComponentsCopper area maximized for heatsinkingDC OutputsESD spark gapBypass Capacitor close to device Feedback Resistors close to device10 mil gapU1SFB BP D S S S Output Filter CapacitorRev. E 09/09Figure 8. Schematic Representation of Electrical Impact of Improper Layout.Rev. E 09/09Drain ClampRecommended Clamp CircuitsComponents R1, R2, C3, VR1 and D5 in fi gure 4 comprise the clamp. This circuit is preferred when the primary leakage inductance is greater than 125 μH to reduce drain voltageovershoot or ringing present on the feedback winding. For best output regulation, the feedback voltage must settle to within 1% at 2.1 μs from the turn off of the primary MOSFET. This requires careful selection of the clamp circuit components. The voltage of VR1 is selected to be ~20% above the refl ected output voltage (V OR ). This is to clip any turn off spike on the drain but avoid conduction during the fl yback voltage interval when the output diode is conducting. The value of R1 should be the largest value that results in acceptable settling of the feedback pin voltage and peak drain voltage. Making R1 too large will increase the discharge time of C3 and degrade regulation. Resistor R2dampens the leakage inductance ring. The value must be large enough to dampen the ring in the required time but must not be too large to cause the drain voltage to exceed 680 V.If the primary leakage inductance is less than 125 μH, VR1 can be eliminated and the value of R1 increased. A value of 470 k Ω with an 820 pF capacitor is a recommended starting point. Verify that the peak drain voltage is less than 680 V under all line and load conditions. Verify the feedback winding settles to an acceptable limit for good line and load regulation.Effect of Fast (500 ns) versus Slow (2 μs) RecoveryDiodes in Clamp Circuit on Pulse Grouping and Output Ripple.A slow reverse recovery diode reduces the feedback voltage ringing. The amplitude of ringing with a fast diode represents 8% error in Figure 10.Figure 9. RCD Clamp, Low Power or Low Leakage Inductance Designs. RCD Clamp With Zener Bleed. High Power or High Leakage Inductance Designs.Figure 10. Effect of Clamp Diode on Feedback Pin Settling. Clamp Circuit (top). Feedback Pin Voltage (bottom).Black Trace: D C1 is a FR107 (fast type, trr = 500 ns)Gray Trace: D C1 is a 1N4007G (standard recovery, trr = 2 us)Rev. E 09/09Figure 11. Not Pulse Grouping (<5 Consecutive Switching Cycles).Pulse Grouping (>5 Consecutive Switching Cycles).Top Trace: Drain Waveform (200 V/div)Bottom Trace: Output Ripple Voltage (50 mV/div)Split Screen with Bottom Screen Zoom Top Trace: Drain Waveform (200 V/div)Bottom Trace: Output Ripple Voltage (50 mV/div)Clampless DesignsClampless designs rely solely on the drain node capacitance to limit the leakage inductance induced peak drain-to-sourcevoltage. Therefore the maximum AC input line voltage, the value of V OR , the leakage inductance energy, (a function of leakage inductance and peak primary current), and the primary winding capacitance determine the peak drain voltage. With no signifi -cant dissipative element present, as is the case with an external clamp, the longer duration of the leakage inductance ringing can increase EMI.The following requirements are recommended for a universal input or 230 VAC only Clampless design:1. Clampless designs should only be used for P O ≤5 W using aV OR of ≤90 V2. For designs with P O ≤5 W, a two-layer primary must be usedto ensure adequate primary intra-winding capacitance in the range of 25 pF to 50 pF . A bias winding must be added to the transformer using a standard recovery rectifi er diode(1N4003– 1N4007) to act as a clamp. This bias winding may also be used to externally power the device by connecting a resistor from the bias winding capacitor to the BYPASS pin. This inhibits the internal high-voltage current source, reducing device dissipation and no-load consumption.3. For designs with P O >5 W, Clampless designs are not practicaland an external RCD or Zener clamp should be used.4. Ensure that worst-case, high line, peak drain voltage is belowthe BV DSS specifi cation of the internal MOSFET and ideally ≤650 V to allow margin for design variation.V OR (Refl ected Output Voltage), is the secondary output plus output diode forward voltage drop that is refl ected to the primary via the turns ratio of the transformer during the diode conduction time. The V OR adds to the DC bus voltage and the leakage spike to determine the peak drain voltage.Pulse GroupingPulse grouping is defi ned as 6 or more consecutive pulses followed by two or more timing state changes. The effect of pulse grouping is increased output voltage ripple. This isshown on the right of Figure 11 where pulse grouping has caused an increase in the output ripple.To eliminate group pulsing verify that the feedback signal settles within 2.1 μs from the turn off of the internal MOSFET. A Zener diode in the clamp circuit may be needed to achieve the desired settling time. If the settling time is satisfactory, then a RC network across R LOWER (R6) of the feedback resistors is necessary.The value of R (R5 in the Figure 12) should be an order of magnitude greater than R LOWER and selected such that R×C = 32 μs where C is C5 in Figure 12.Quick Design ChecklistAs with any power supply design, all LinkSwitch-CV designs should be verifi ed on the bench to make sure that component specifi cations are not exceeded under worst-case conditions.Figure 12. RC Network Across R BOTTOM (R6) to Reduce Pulse Grouping.Rev. E 09/09The following minimum set of tests is strongly recommended:1. Maximum drain voltage – Verify that peak V DS does not exceed680 V at highest input voltage and maximum output power. 2. Maximum drain current – At maximum ambient temperature,maximum input voltage and maximum output load, verify drain current waveforms at start-up for any signs of trans-former saturation and excessive leading edge current spikes. LinkSwitch-CV has a leading edge blanking time of 215 ns to prevent premature termination of the ON-cycle. Verify that the leading edge current spike is below the allowed current limit envelope for the drain current waveform at the end of the 215 ns blanking period.3. Thermal check – At maximum output power, both minimumand maximum input voltage and maximum ambient tempera-ture; verify that temperature specifi cations are not exceeded for LinkSwitch-CV , transformer, output diodes and output capacitors. Enough thermal margin should be allowed for the part-to-part variation of the R DS(ON) of LinkSwitch-CV , as specifi ed in the data sheet. It is recommended that the maximum source pin temperature does not exceed 110 °C.Design ToolsUp-to-date information on design tools can be found at the Power Integrations web site: 分销商库存信息:POWER-INTEGRATIONSLNK625DG LNK623DG LNK623PG LNK625PG LNK626PG LNK624DG LNK623DG-TL LNK624DG-TL LNK624PG LNK625DG-TL LNK626DG-TL LNK626DG RDK-201。

XN297L_Datasheet_V4p3

XN297L Datasheet Single Chip 2.4GHz TransceiverFEATURES●Low Power16mA TX at 0dBm output power15mA RX at 2Mbps air data rate2uA in power down●Low Cost BOMFew external componentsFour Capacitors, One crystaloscillator●High PerformanceExcellent Receiver sensitivity-85dBm@2Mbps-88dBm@1Mbps-93dBm@250KbpsProgrammable Output Power Up to 13dBm APPLICATIONS●TV and STB remote controls ●Wireless M ouse and keyboard ●Toys and wireless audio●Wireless gamepads●Active RFID●Smart home automationGENERAL DESCRIPTIONThe XN297L is a single chip 2.4GHz transceiver , designed for operation in the world wide ISM frequency band at 2.400~2.483GHz. The XN297L integrates radio frequency (RF) transmitter and receiver, frequency synthesizer, crystal oscillator, baseband GFSK modem, and so on. The XN297L supports one to multiple network and communication with ACK. TX power, frequency channel, and data rate can be1 Electrical characteristics Table1 XN297L Electrical characteristicsreceiver sensitivity degrades about 2dB; and modulation quality of the emission signal (EVM) falls by 10%.* Note: In 250KBps mode, it should not be more than 16 bytes of payload length, because of frequency drift in open-loop transmition.2 Absolute maximum ratingsTable 2 XN297L absolute maximum ratings* Note: Exceeding one or more of the limiting values may cause permanent damage to XN297L.* Caution: Electrostatic sensitive device, comply with protection rules when operating.3 Block diagramMISO MOSI CSN SCKIRQ CEANTX C 1X C 2V S S V D DFigure 1 XN297L block diagram4 Pin definitionCE CSNSCK MOSI MISO I R QV D DV S SX IX ONCNC ANT NCVDD S SN CN C N C N CFigure2 XN297L pin definitionTable 3 Pin function5 Operational ModesThis chapter describes XN297L all kinds of working mode, and is used to control the chip into the working mode of method. XN297L own state machine is controlled by chip internal registers configuration values and external signal pin. 5.1 State diagramSix kinds of working mode in table 4 gives the corresponding mode of control register and FIFO registers.Table 4 Control BIT and function description5.2 State diagramFigure 3 is XN297L working state diagram, said six working mode between jump XN297L in VDD is greater than 2.2 V to begin to work properly into sleep mode, the MCU can be sent via SPI configuration commands and CE pin into the other five state.STB2->STB3: 10usFigure3 state diagram5.3 IRQ PINIn the status register TX_DS RX_DR or MAX_RT is 1, report and the corresponding interrupt enable bit is 0, IRQ pins interrupt trigger. The MCU writes 1 to the corresponding interrupt source, clear the interrupt. IRQ pins interrupt trigger can be blocked or enabled, report by setting the interrupt enable bit is 1, ban IRQ pins interrupt triggered.6 DATA FIFOFigure 4 FIFO block diagramThe XN297L contains TX FIFO, RX FIFO. It is sent via SPI read/write command. It writes TX FIFO in TX mode by W_TX_PAYLOAD and W_TX_NO_ACK instructions. If MAX_RT interruption, data will be cleared in the TX FIFO. It reads PAYLOAD in RX FIFO in receiving mode by R_RX_PAYLOAD, and it reads the length of the PAYLOAD by R_RX_PL_WID instruction. FIFO_STATUS register indicates FIFO states.7 SPI CONTROLThe XN297L is controlled by SPI port for read and write register, and command. The XN297L is a slave terminal, SPI transfer rate depends on the MCU interface speed, and the maximum data transfer rate is 8 MBps.SPI interface is a standard SPI interface are shown in table 5, you can use the general I/O for MCU simulation SPI interface. CSN pin to 0, SPI interface instructions to be performed. From 1 to 0 a CSN pin changes execute one instruction. After the change from 1 to 0 CSN pin can be read by MISO status register contents.Table 5 SPI port7.1 SPI CommandsTable 6 SPI command format<Command word: MSBit to LSBit (one byte)><Data bytes: LSByte to MSByte, MSBit in each byte first>The R_REGISTER and W_REGISTER commands can operate on single or multi-byte registers. When accessing multi-byte registers, first read or write theMSBit of LSByte. Terminate the writing before all bytes in a multi-byte register are written, then it leaves the unwritten MSByte(s) unchanged. For example, the LSByte of RX_ADDR_P0 can be modified by writing only one byte to the RX_ADDR_P0 register.7.2 SPI TimingCSNSCK MOSIMISOFigure 5 SPI read operationCSNSCKMOSIMISOFigure 6 SPI write operationCSNSCKMOSIMISOFigure 7 SPI NOP timing diagram8 Packet format description8.1 Packet format for normal BurstTable 7 Packet format for normal burstconfiguration bits.8.2 Packet format for Enhanced Burst Table 8 Packet format for enhanced burstaccording to scrambler configuration bits.8.3 Packet format for Enhanced Burst ACK Table 9 Packet format for enhanced burst ackscrambler configuration bits.9 Application exampleFigure 8 XN297L application *Note 1: NC pin can be floating.*Note 2: the external components10 Package sizeFigure 9 QFN20L 0303 package size。

MORNSUN B05_XT-2WR3 Series DC DC Converter Datashe