Farsight070714Cadence

cadence教程

cadence教程Cadence 是一款流行的电路设计和仿真工具。

它广泛应用于电子工程领域,可以帮助工程师进行电路设计、布局、仿真和验证。

以下是一个简单的 Cadence 教程,帮助你快速入门使用该软件。

第一步: 下载和安装 Cadence首先,你需要从 Cadence 官方网站下载适用于你操作系统的Cadence 软件安装包。

在下载完成后,双击安装包文件并按照安装向导的指示进行安装。

第二步: 创建新项目打开 Cadence 软件后,你将看到一个初始界面。

点击“File”菜单,然后选择“New”来创建一个新的项目。

第三步: 添加电路元件在新项目中,你可以开始添加电路元件。

点击菜单栏上的“Library”按钮,然后选择“Add Library”来添加一个元件库。

接下来,使用菜单栏上的“Place”按钮来添加所需的电路元件。

第四步: 连接电路元件一旦添加了电路元件,你需要使用连线工具来连接它们。

点击菜单栏上的“Place Wire”按钮,然后将鼠标指针移到一个元件的引脚上。

点击引脚,然后按照电路的设计布局开始连接其他元件。

第五步: 设置仿真参数在完成电路布局后,你需要设置仿真参数。

点击菜单栏上的“Simulate”按钮,然后选择“Configure”来设置仿真器类型、仿真时间等参数。

第六步: 运行仿真设置完成后,你可以点击菜单栏上的“Simulate”按钮,然后选择“Run”来运行仿真。

仿真过程会模拟电路的运行情况,并生成相应的结果。

总结通过这个简单的 Cadence 教程,你了解了如何下载安装Cadence 软件、创建新项目、添加电路元件、连接元件、设置仿真参数和运行仿真。

掌握了这些基本操作后,你可以进一步学习和探索 Cadence 的更多功能和高级技巧。

祝你在使用Cadence 中取得成功!。

cadence简介和使用基础

CMOS电路原理图设计

或者CIW窗口→File→Open(打开已有的 Cellview)。

CMOS电路原理图设计

也可以在Library Manager中直接打开。

Cadence的使用基础

双击Schematics,出现原理图编辑器

Cadence的使用基础

之后出现Symbol Generation Options窗口。

Cadence的使用基础

出现界面:

Cadence的使用基础

可将上图修改为惯用图形,以CMOS反相器为例。

CMOS电路原理图设计

电路仿真 仿真环境简介

Schematic图形窗口→Tools→Analog Environment。

Cadence的使用基础

Cadence的使用基础

基本工作环境

局域网资源

Cadence的使用基础

用户登陆 微机登陆后,点击桌面X-manager 图标,

Cadence的使用基础

打开X-manager图标后,点击xstart 图标,出现对话 框,进行如下设置:

Cadence的使用基础

登录时出现Linux-CDE (Common Desktop Environment) 界面

一、 cadence简介和使用

集成电路设计软件技术介绍

EDA技术的概念

EDA技术是在电子CAD技术基础上发展起来 的计算机软件系统,是指以计算机为工作平台, 融合了应用电子技术、计算机技术、信息处理 及智能化技术的最新成果,进行电子产品的自 动设计

EDA工具的功能

利用EDA工具,电子设计师可以从概念、算法、 协议等开始设计电子系统,大量工作可以通过 计算机完成,并可以将电子产品从电路设计、

cadence仿真工具介绍1

( TB ( TO ( GT ( W1 ( A1 ( W2 ( A2 ( W3 ( A3

"nwell" ) "diff" ) "poly" ) "cut" ) "metal" ) "cut" ) "metal" ) "cut" ) "metal" )

COPYRIGHT FOR ZHOUQN

COPYRIGHT FOR ZHOUQN

原理图编辑窗口结构分类编辑命令菜单常用快捷命令菜单1instance调用库单元cellview浏览器librarycellviewnameoption阵列行数列数旋转x镜像y镜像variable如果有2addpin调用端口pinpinnames总线命名方式总线名放置方式pin的旋转和镜像3addwire连线narroworwide4wirename连线命名连线规则连线粗细连线名称连线名称的相关属性10属性参数修改9undo11chechandsave12save5放大缩小8删除6stretch拉动保持连接7copy从分类菜单中可以看到命令的快捷键和许多其它命令仿真环境设置版图设计基本过程和要求在一定工艺下根据电路的要求依据版图设计规则设计每个器件的图形并完成排版布线形成一套完整的电路光刻掩膜版图形

COPYRIGHT FOR ZHOUQN

版图主要编辑命令 (2)修改类命令 ) Undo, Redo , Move, Copy, 拉动,改变形状, 拉动,改变形状, 删除,查找, 删除,查找, 合并图形, 合并图形, 制作单元, 制作单元, 打散单元, 打散单元, 劈切图形, 劈切图形, 胀缩图形, 胀缩图形, 旋转图形等等。 旋转图形等等。

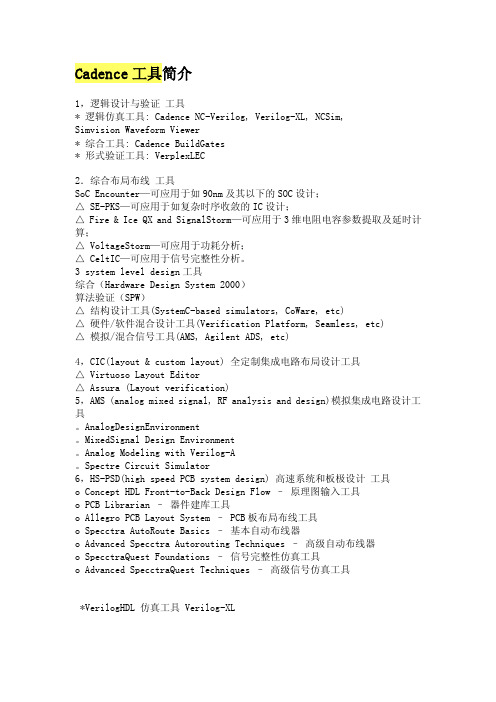

Cadence工具简介

Cadence工具简介1,逻辑设计与验证工具* 逻辑仿真工具: Cadence NC-Verilog, Verilog-XL, NCSim,Simvision Waveform Viewer* 综合工具: Cadence BuildGates* 形式验证工具: VerplexLEC2.综合布局布线工具SoC Encounter—可应用于如90nm及其以下的SOC设计;△ SE-PKS—可应用于如复杂时序收敛的IC设计;△ Fire & Ice QX and SignalStorm—可应用于3维电阻电容参数提取及延时计算;△ VoltageStorm—可应用于功耗分析;△ CeltIC—可应用于信号完整性分析。

3 system level design工具综合(Hardware Design System 2000)算法验证(SPW)△ 结构设计工具(SystemC-based simulators, CoWare, etc)△ 硬件/软件混合设计工具(Verification Platform, Seamless, etc)△ 模拟/混合信号工具(AMS, Agilent ADS, etc)4,CIC(layout & custom layout) 全定制集成电路布局设计工具△ Virtuoso Layout Editor△ Assura (Layout verification)5,AMS (analog mixed signal, RF analysis and design)模拟集成电路设计工具。

AnalogDesignEnvironment。

MixedSignal Design Environment。

Analog Modeling with Verilog-A。

Spectre Circuit Simulator6,HS-PSD(high speed PCB system design) 高速系统和板极设计工具o Concept HDL Front-to-Back Design Flow –原理图输入工具o PCB Librarian –器件建库工具o Allegro PCB Layout System – PCB板布局布线工具o Specctra AutoRoute Basics –基本自动布线器o Advanced Specctra Autorouting Techniques –高级自动布线器o SpecctraQuest Foundations –信号完整性仿真工具o Advanced SpecctraQuest Techniques –高级信号仿真工具*VerilogHDL 仿真工具 Verilog-XL*电路设计工具 Composer电路模拟工具 Analog Artist*版图设计工具 Virtuoso Layout Editor版图验证工具 Dracula 和 Diva*自动布局布线工具 Preview 和 Silicon Ensembleform:Mr Bond coms-chip expert设计任务 EDA工具功能仿真和测试 a. Cadence, NC_simb. Mentor ModelSim (调试性能比较突出)c. Synopsys VCS/VSSd. Novas Debussy (仅用于调试)逻辑综合 a. Synopsys, DCb. Cadence, BuildGatesc. Mentor, LeonardoDFT a. Mentor, DFTAdvisorb. Mentor, Fastscanc. Mentor, TestKompressd. Mentor, DFTInsighte. Mentor, MBISTArchitectf. Mentor, LBISTArchitectg. Mentor, BSDArchitecth. Mentor, Flextesti. Synopsys, DFT Complierj. Synopsys, Tetra MAXk. Synopsys, BSD Complier布局,时钟树综合和自动布线a. Cadence, Design Plannerb. Cadence, CT-Genc. Cadence, PKSd. Cadence, Silicon Ensemblee. Synopsys, Chip Architectf. Synopsys, Floorplan Managerg. Synopsys, Physical Complier & Apolloh. Synopsys, FlexRoute网表提取及RC参数提取物理验证a. Mentor, xCalibreb. Cadence, Assure RCXc. Synopsys, Star-RCXTd. Mentor, Calibree. Synopsys, Herculef. Cadence, Assure延时计算与静态时序分析a. Synopsys, Prime Timeb. Cadence, Pearlc. Mentor, SST Velocity形式验证 a. Mentor, FormalProb. Synopsys, Formalityc. Cadence, FormalCheck功能优化与分析 a. Synopsys, Power Compilerb. Synopsys, PowerMill-ACEHDLQA a. TransEDA, Verification Navigatorb. Synopsys, LEDAFPGA开发 a. Mentor, FPGAdvantageb. XILINX, ISEc. Altera, QuartusIISoC开发 a. Mentor, Seamless CVEb. Cadence, SPWc. Synopsys, Co-Centric版图设计工具 a. Cadence, Virtuosob. Mentor, IC-Stationc. 思源科技, Laker电路级仿真 a. Mentor, ELDOb. Mentor, ADMSc. Cadence, Spectre, Spectre RFd. Cadence, AMSe. Synopsys, Star-Hspice以下只是个人和本公司的评价,不一定十分全面,仅供参考。

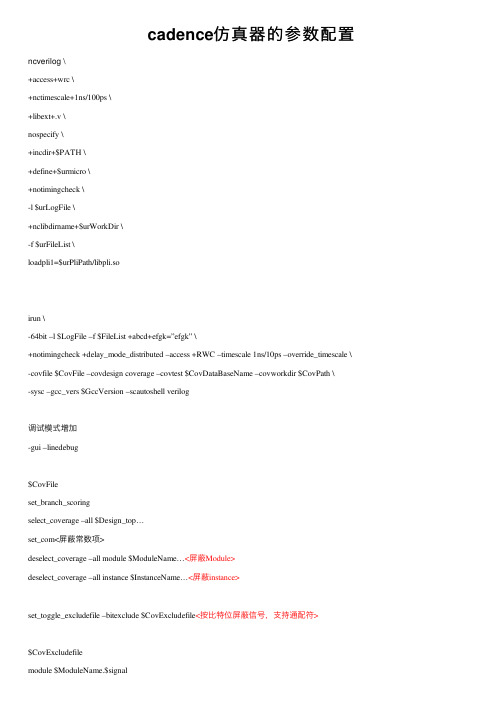

cadence仿真器的参数配置

cadence仿真器的参数配置ncverilog \+access+wrc \+nctimescale+1ns/100ps \+libext+.v \nospecify \+incdir+$PATH \+define+$urmicro \+notimingcheck \-l $urLogFile \+nclibdirname+$urWorkDir \-f $urFileList \loadpli1=$urPliPath/libpli.soirun \-64bit –l $LogFile –f $FileList +abcd+efgk=”efgk” \+notimingcheck +delay_mode_distributed –access +RWC –timescale 1ns/10ps –override_timescale \ -covfile $CovFile –covdesign coverage –covtest $CovDataBaseName –covworkdir $CovPath \-sysc –gcc_vers $GccVersion –scautoshell verilog调试模式增加-gui –linedebug$CovFileset_branch_scoringselect_coverage –all $Design_top…set_com<屏蔽常数项>deselect_coverage –all module $ModuleName…<屏蔽Module>deselect_coverage –all instance $InstanceName…<屏蔽instance>set_toggle_excludefile –bitexclude $CovExcludefile<按⽐特位屏蔽信号,⽀持通配符>$CovExcludefilemodule $ModuleName.$signalinstance $InstanceName.$signal我们知道,由于NC-Verilog使⽤了Native Compile Code的技术来加强电路模拟的效率,因此在进⾏模拟时必须经过compile(ncvlog命令)以及elaborate(ncelab命令)的步骤。

cadence使用方法

cadence使用方法Cadence 是一种流行的电子设计自动化(EDA)工具,用于VLSI(Very Large Scale Integration)设计和仿真。

它由美国卡内基梅隆大学的Circuit Design Group开发,是IC设计工程师广泛使用的一种工具。

Cadence 提供了一整套的工具,包括电路设计、物理布局、封装设计以及信号完整性仿真等。

1.工程设置:在开始之前,你需要设置你的工程。

这包括指定设计库和工作目录。

你可以在Cadence的命令行界面输入"set"命令,设置Cadence工程的相关参数。

2.电路设计:在Cadence中,你可以使用Virtuoso Schematic Editor或者Silicon Ensemble Schematic Editor进行电路设计。

你可以从菜单中选择相应的元件,然后将它们拖放到画布上,并连接它们。

你还可以设置元件的参数和属性。

3.电路仿真:完成电路设计后,你可以使用Spectre或者HSPICE等仿真工具来验证你的设计。

你需要定义相应的仿真参数,如仿真器类型、仿真时间等。

Cadence还提供了仿真结果的分析和波形显示,以便你评估电路的性能和稳定性。

4.物理布局:5.物理验证:完成物理布局后,你需要进行物理验证,以确保设计的可制造性和可靠性。

Cadence提供了Innovus和Tempus等工具,用于进行电压引脚冲突检查、信号完整性分析和时序分析等。

这些工具可以帮助你发现潜在的物理问题,并提供相应的解决方案。

6.封装设计:在完成物理验证后,你需要设计封装。

Cadence提供了封装设计工具,如Allegro Package Designer。

你可以定义芯片的引脚布局和间距规则,并生成封装文件。

7.电路板设计:当你完成芯片设计后,你可能需要进行电路板设计。

Cadence提供了Allegro PCB Designer等工具,用于进行电路板布局和连线。

Cadence解决方案助力创意电子20nm SoC测试芯片成功流片

8 0 2 . 1 1 b迅 速饱 和 ,但 启 动 Q o S机 制 后 。 G P F和 8 0 2 . 1 1 e的 时 延上 升缓慢 , 某个 中间阶段 时延甚 至出现 下降 ; 在 业 务 强 度

小于 2 5时 , G P F时 延 维 持 在 1 S内 , 而 8 0 2 . 1 1 e则 偏 大 : 业 务

[ 3 】I E E E S t a n d a r d 8 0 2 1 1 e / A me n d m e n t 8 ,Me d i u m A c c e s s

C o n t r o l( M A C)Q u a l i t y o f S e r v i c e( Q o s )e n h a n c e me n t s [ S ] .

【 2 】B a n c h s A, V o l l e r o L .A d e l a y m o d e l f o r I E E E 8 0 2 . 1 1 e E D C 椰 I E E E C o mm u n i c a t i o n s L e t t e r s , 2 0 0 5 , 9 ( 6 ) : 5 0 8 - 5 1 0 .

V o l P i n I E E E 8 0 2 1 l e w i r e l e s s L A N s[ J ] .I E E E Wi r e l e s s

Co mmu n i c a t i o n s , 2 0 0 8, 1 5( 1 ) : 5 6 - 6 2 .

参考文献 :

【 l 】 L I F H, X I A O Y A N G, Z H AN G J I N G - Y U A N . V a r i a b l e b i t r a t e

cadence教程-IC设计工具原理共页课件 (二)

cadence教程-IC设计工具原理共页课件 (二) - Cadence教程-IC设计工具原理共页课件

1. 什么是Cadence?

Cadence是一家专门从事电子设计自动化软件的公司。

其产品涵盖了芯片设计、系统设计、封装设计和PCB设计等领域。

Cadence的软件被广泛应用于半导体、通信、计算机、消费电子等行业。

2. Cadence的主要产品

Cadence的主要产品包括Virtuoso、Allegro、OrCAD、Sigrity等。

其中,Virtuoso是一款用于模拟、布局和验证芯片的工具;Allegro是

一款用于PCB设计的工具;OrCAD是一款用于电路设计的工具;

Sigrity则是一款用于信号完整性分析的工具。

3. Cadence的应用领域

Cadence的软件被广泛应用于各种电子产品的设计和制造中,如手机、平板电脑、笔记本电脑、服务器、网络设备、汽车电子、医疗设备等。

在半导体行业中,Cadence的软件被用于设计各种芯片,如处理器、存储器、模拟集成电路、射频集成电路等。

4. Cadence的优势

Cadence的软件具有高度的可靠性、灵活性和易用性。

其产品支持多种操作系统,如Windows、Linux、Solaris等。

此外,Cadence还提供了丰富的教程和技术支持,帮助用户更好地使用其软件。

5. Cadence的未来发展

随着电子行业的不断发展,Cadence的软件也在不断升级和改进。

未来,Cadence将继续加强与各大芯片厂商和设备厂商的合作,开发出更加先进和适用的软件,为电子行业的发展做出更大的贡献。

cadence相关软件介绍.

公司概述Cadence是全球电子设计自动化(EDA领先企业,从事软件与硬件设计工具、芯片知识产权与设计服务,目前正致力于EDA产业的转型。

Cadence把此次转型构想命名为EDA360,因为它将包含设计过程中的所有方面,并关注最终产品的可盈利性。

这种应用驱动型方法,能在创建、集成与优化电子设计方面帮助我们的客户以更低的成本和更高的质量完成硅芯片、片上系统设备、以及完整的系统实现。

Cadence Design System, Inc.公司成立于1988年,总部位于美国加州圣荷塞,其设计中心、研发中心和销售部门分布于世界各地。

CADENCE中国1992年Cadence 公司进入中国大陆市场,迄今已拥有大量的集成电路 (IC 及系统设计客户群体。

在过去的二十年里,Cadence公司在中国不断发展壮大,建立了北京、上海、深圳分公司以及北京研发中心、上海研发中心,并于2008年将亚太总部设立在上海,Cadence中国现拥有员工400余人。

北京研发中心和上海研发中心主要承担美国公司总部EDA软件研发任务,力争提供给用户更加完美的设计工具和全流程服务。

Cadence在中国拥有强大的技术支持团队,提供从系统软硬件仿真验证、数字前端和后端及低功耗设计、数模混合RF 前端仿真与DFM以及后端物理验证、SiP封装以及PCB设计等技术支持。

我们的销售方案中还包括提供专业设计服务,VCAD团队为用户提供高质量、有效的设计和外包服务。

把世界顶尖的产品技术和服务融入中国,成为中国电子行业最亲密合作伙伴,和中国电子高科技产业共同腾飞是Cadence 在中国的坚定信念。

市场与趋势Cadence服务于产值达2万亿美元的全球电子市场,其中包括产值超过3000亿美元的半导体市场。

我们的主要垂直市场领域包括:有线与无线通讯;工业、医疗与汽车电子;计算机与消费电子,比如多媒体和个人娱乐设备。

这些领域占全球电子设备营收和半导体营收的90%以上。

cadence 教程

cadence 教程Cadence 是一种电子设计自动化工具,常用于模拟、验证和布局设计。

它可以帮助工程师在各种电子系统中设计和验证电路,从而提高电路设计的效率和可靠性。

下面将介绍一些 Cadence 的基本使用方法和技巧。

1. 创建新项目要使用 Cadence,首先需要创建一个新项目。

可以通过菜单栏上的"File" -> "New"来创建新项目。

然后输入项目名称、路径等信息,并选择适当的项目类型。

2. 添加电路在 Cadence 中,可以通过绘制电路原理图来添加电路。

可以使用"Create Schematic"工具来创建新的电路原理图。

在绘制电路原理图时,注意使用正确的元件符号和连线方式。

3. 设置仿真参数在进行电路仿真之前,需要设置仿真参数。

可以通过菜单栏上的"Simulator" -> "Edit Simulation"来打开仿真设置窗口。

在仿真设置窗口中,可以设置仿真类型(如DC、AC、Transient 等)、仿真时间范围、仿真步长等参数。

4. 运行仿真设置好仿真参数后,可以通过菜单栏上的"Simulator" -> "Run Simulation"来运行仿真。

运行仿真后,可以查看仿真结果,如电压波形、电流波形等。

5. 进行验证在验证电路设计时,可以使用 Cadence 提供的调试工具和验证功能。

可以通过菜单栏上的"Debug" -> "Start Debugging"来启动调试。

在调试过程中,可以查看电路元件的属性、信号的波形等信息,以发现和解决问题。

6. 进行布局设计在电路设计完成后,可以进行布局设计。

可以使用 Cadence 提供的布局工具来布局电路版图。

布局时,要注意合理安排电路元件的位置和走线方式,以满足电路设计的要求。

cadence入门教程_修改版

Introduction to Cadence Customer IC Design Environment熊三星徐太龙编写安徽大学电子信息工程学院微电子学系目录1. Linux 常用命令 (3)2. 软件的启动 (5)3. 建立工程 (7)4. 画原理图 (9)5. 原理图仿真 (17)6. 生成symbol (25)7. 版图 (30)8. DRC检查 (50)9. LVS检查 (54)10. PEX参数提取 (58)11. 后仿真 (61)1.Linux 常用命令目前,电子设计自动化(Electronic Design Automation, EDA)工具多数都基于Linux操作系统,因此在学习使用EDA之前,有必要掌握一些Linux操作系统的基本命令。

1.mkdirmkdir命令让用户在有写权限的文件夹(目录)下建立一个或多个文件夹(目录)。

其基本格式如下:mkdir dirname1 dirname2 ... (dirname 为文件夹或者目录的名字)2.cdcd命令让用户进入一个有权限的文件夹(目录)。

其基本格式如下:cd Filename (Filename为文件夹或者目录的名字)cd .. (.. 表示上一层文件夹或者目录)3.lsls命令用以显示一个文件夹(目录)中包含的文件夹(目录)或者文件。

其基本格式如下:ls Filename (Filename为文件夹或者目录的名字)如果ls命令后没有跟文件夹(目录)名字,显示当前文件夹(目录)的内容。

ls 命令可以带一些参数,给予用户更多相关的信息:-a : 在UNIX/Linux中若一个文件夹(目录)或文件名字的第一个字元为"." ,该文件为隐藏文件,使用ls 将不会显示出这个文件夹(目录)或文件的名字。

如cshell 的初始化文件.cshrc,如果我们要察看这类文件,则必须加上参数-a。

格式如下:ls –a Filename-l : 这个参数代表使用ls 的长(long)格式,可以显示更多的信息,如文件存取权,文件拥有者(owner),文件大小,文件更新日期,或者文件链接到的文件、文件夹。

cadence使用教程

cadence使用教程Cadence是一种电路设计和仿真软件,非常适合电子工程师用于电路设计和分析。

在本教程中,我们将介绍如何使用Cadence进行基本的电路设计和仿真。

首先,打开Cadence软件,并新建一个新项目。

请确保你已经安装了Cadence软件,并且拥有一个有效的许可证。

在新项目中,你需要定义电路的基本参数,如电源电压、电阻值等。

可以通过绘制原理图的方式来完成这些参数的定义。

在绘图界面中,你可以选择不同的元件,包括电源、电阻、电容、电感等。

你可以使用菜单栏中的工具来放置和连接这些元件。

一旦电路图绘制完成,你可以对电路进行仿真。

首先,需要选择合适的仿真器。

Cadence提供了多种仿真器,如Spectre和HSPICE。

选择一个适合你电路的仿真器,并设置仿真参数,如仿真时间、仿真步长等。

在仿真之前,你首先需要对电路进行布局。

布局涉及将电路中的元件放置在芯片上,并根据布线规则进行连接。

Cadence提供了强大的布局工具,可以帮助你完成这个过程。

完成布局后,你可以进行后仿真。

后仿真涉及将布局好的电路导入到仿真器中,并进行仿真分析。

你可以查看电路的性能指标,如电压、电流和功耗等。

除了基本的电路设计和仿真,Cadence还提供了其他功能,如噪声分析、温度分析和优化设计等。

你可以根据需要选择适合的功能。

总的来说,Cadence是一个功能强大的电路设计和仿真软件。

通过本教程,你可以学会如何使用Cadence进行基本的电路设计和仿真。

希望这对你的电子工程项目有所帮助。

Cadence软件介绍【范本模板】

Cadence软件介绍Cadence 是一个大型的EDA 软件,它几乎可以完成电子设计的方方面面,包括ASIC 设计、FPGA 设计和PCB 板设计。

Cadence 在仿真、电路图设计、自动布局布线、版图设计及验证等方面有着绝对的优势。

Cadence 包含的工具较多几乎包括了EDA 设计的方方面面.下面主要介绍其产品线的范围.1、板级电路设计系统包括原理图输入、生成、模拟数字/混合电路仿真,fpga设计,pcb编辑和自动布局布线mcm电路设计、高速pcb版图的设计仿真等等。

包括:A、Concept HDL原理图设计输入工具, 有for NT和for Unix的产品。

B、Check Plus HDL原理图设计规则检查工具.(NT & Unix)D、Allegro Expert专家级PCB版图编辑工具(NT & Unix)E、SPECTRA Expert AutoRouter 专家级pcb自动布线工具F、SigNoise信噪分析工具G、EMControl 电磁兼容性检查工具H、Synplify FPGA / CPLD综合工具I、HDL Analyst HDL分析器J、Advanced Package Designer先进的MCM封装设计工具2、Alta系统级无线设计这部分包括:A、SPW (Cierto Signal Processing Work System)信号处理系统.可以说,spw包括了matlab的很多功能,连demo都有点象.它是面向电子系统的模块化设计、仿真和实现的环境.它的通常的应用领域包括无线和有线载波通信、多媒体和网络设备.在进行算法设计、滤波器设计、c Code生成、软/硬件结构联合设计和硬件综合的理想环境.它里面非常有意思的就是信号计算器。

B、HDS (Hardware Design System)硬件系统设计系统它现在是SPW的集成组件之一.包括仿真、库和分析扩展部分。

可以进行spw的定点分析行为级和rtl级的代码生成.C、Mutimedia多媒体(Multimedia Design Kit)它可以进行多媒体应用的设计,包括电视会议系统、数字电视等等以及任何种类的图象处理系统的设计。

Cadence 公司产品介绍

Cadence 公司旗下有两个产品链,一个是IC产品,一个是PCB产品。

PCB产品又分成PO系列和PS 系列,PO就是Orcad系列,PS是高端系列,有的人称其为Allegro系列,其实并不准确。

Cadence公司在收购Orcad之前,它的原理图工具叫Concept HDL,PCB工具就是Allegro,也就是Allegro的PCB Editor,另外还有SI工具(做信号完整性分析的)。

Orcad旗下有三个工具,原理图工具Caputre CIS,原理图仿真工具Pspice AD和PSpice AA,还有一款PCB布局布线工具Orcad 的Layout(PLUs)。

Cadence收购了Orcad之后,就完全将Orcad的Capture CIS和Pspice与自身的产品做了无缝整合而摒弃了Orcad以前的Layout(Plus)。

目前Cadence的Allegro已经完全作为PCB布线工具整合到Orcad系列中。

(到这里,你可以明白,为什么PS系列不能简单的叫做Allegro了吧)。

那么,Orcad系列和PS(SPB)系列到底区别在哪里呢?1、核心产品是一样的。

Orcad的原理图是Capture CIS,PS里面的原理图有两个,一个就是Cadence以前的concept HDL,还有,就是Capture CIS,不过在PS里面,名称改为Design Entry CIS;Orcad的PCB布局布线器是PCB Edior,PS系列里面的也是两者核心是完全一样的;Orcad的原理图仿真工具是PSpice AD和Pspice AA,PS系列也是,不过在PS系列里,把Pspice AD和PspiceAA整合成一个产品包,并改名为AMS simulator.2、PS系列里面分成三个等级,L,XL和GXL,就像衣服的大小号一样,号越大,功能越强,当然价格肯定也越贵了。

L也好,XL也好,Gxl也好,原理图工具Capture CIS是没有任何区别的,而Pspice 功能不分等级,都是一样的。

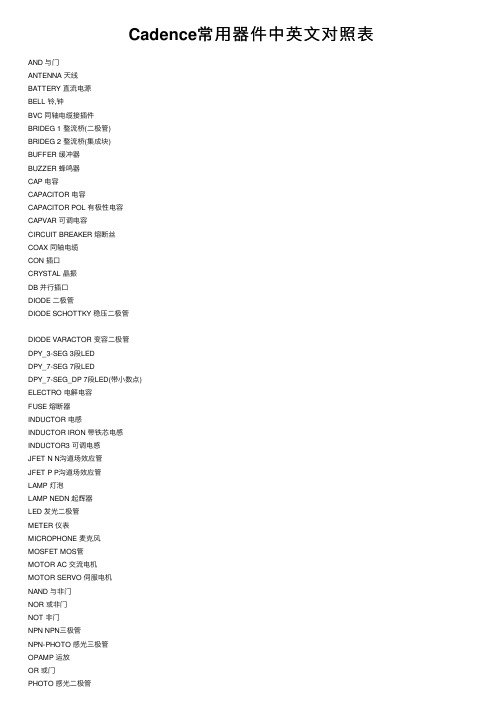

Cadence常用器件中英文对照表

Cadence常⽤器件中英⽂对照表AND 与门ANTENNA 天线BATTERY 直流电源BELL 铃,钟BVC 同轴电缆接插件BRIDEG 1 整流桥(⼆极管)BRIDEG 2 整流桥(集成块)BUFFER 缓冲器BUZZER 蜂鸣器CAP 电容CAPACITOR 电容CAPACITOR POL 有极性电容CAPVAR 可调电容CIRCUIT BREAKER 熔断丝COAX 同轴电缆CON 插⼝CRYSTAL 晶振DB 并⾏插⼝DIODE ⼆极管DIODE SCHOTTKY 稳压⼆极管DIODE VARACTOR 变容⼆极管DPY_3-SEG 3段LEDDPY_7-SEG 7段LEDDPY_7-SEG_DP 7段LED(带⼩数点)ELECTRO 电解电容FUSE 熔断器INDUCTOR 电感INDUCTOR IRON 带铁芯电感INDUCTOR3 可调电感JFET N N沟道场效应管JFET P P沟道场效应管LAMP 灯泡LAMP NEDN 起辉器LED 发光⼆极管METER 仪表MICROPHONE 麦克风MOSFET MOS管MOTOR AC 交流电机MOTOR SERVO 伺服电机NAND 与⾮门NOR 或⾮门NOT ⾮门NPN NPN三极管NPN-PHOTO 感光三极管OPAMP 运放OR 或门PHOTO 感光⼆极管PNP 三极管NPN DAR NPN三极管PNP DAR PNP三极管POT 滑线变阻器PELAY-DPDT 双⼑双掷继电器RES1.2 电阻RES3.4 可变电阻RESISTOR BRIDGE ? 桥式电阻RESPACK ? 电阻SCR 晶闸管PLUG ? 插头PLUG AC FEMALE 三相交流插头SOCKET ? 插座SOURCE CURRENT 电流源SOURCE VOLTAGE 电压源SPEAKER 扬声器SW ? 开关SW-DPDY ? 双⼑双掷开关SW-SPST ? 单⼑单掷开关SW-PB 按钮THERMISTOR 电热调节器。

cadence简介

实际上,机房中我们已将各配置文件写好,只要在终端中执行

cds.setup

Cadence的相关配置文件就已经自动设置完毕。如果用户在启动Cadence后,发现无法使用快捷键,则需要把.cdsinit从Cadence的安装目录中拷贝到自己的工作目录下,在终端中输入:

此外还有一个What’new窗口,介绍Cadence新版本特性,不必理会,双击左上角将其关闭。

2.5

Cadence是以库来组织文件的。为了使我们的工作和系统自带库区别,我们需要建立自己的工作库。有两种方法来建立新库,一是通过菜单栏Tools->Library Maneger打开库管理器,另一种是通过File->New->Library来建立新库。这里我们用第一种方法建立新库。单击菜单栏Tools->Library Maneger,会打开LM(Library Maneger)窗口,如图2.3所示。

②点击工具栏的zoomin和zoomout按钮可以放大缩小电路图。键入快捷键f可以使电路图自动缩放到合适大小。

③编辑电路图过程中注意要及时保存,保存方法是菜单栏->Design->Save,也可以键入快捷键大写的S(Shift+s)来保存。

3

现在,我们要开始画一个标准的CMOS反相器。一个反相器包括PMOS,NMOS,VDD,GND。

同样的方法继续设置NMOS参数,只是模型名为n18,栅长为固定值0.18u,栅宽设为pPar(“wn”)。设置好参数后的电路图如图3.9所示。

注意:①设置参数时不要自己输入单位,系统会自动加上。比如0.18uM是错误的写法。如果非要自己写单位,也要和数值之间留一个空格,否则系统会把M识别为变量。

Cadence使用初步简介

Cadence使用初步简介在早期的ASIC 设计中电路图起着更为重要的作用作为流行的CAD软件Cadence 提供了一个优秀的电路图编辑工具Composer。

Composer不但界面友好操作方便而且功能非常强大电路图设计好后其功能是否正确性能是否优越必须通过电路模拟才能进行验证Cadence 同样提供了一个优秀的电路模拟软件Analog Artist由于Analog Artist 通过Cadence 与Hspice 的接口调用Hspice 对电路进行模拟。

但是我们的虚拟机中并没有安装Hspice软件,所以我们使用Cadence自带的仿真软件进行仿真。

本章将介绍电路图设计工具Composer 和电路模拟软件Analog Artist 的设置启动界面及使用方法简单的示例以及相关的辅助文件以便大家能对这两种工具有一个初步的理解。

一、Cadence平台的启动:①右击桌面,在弹出菜单中单击open Terminal②在弹出的终端中输入icfb&然后按回车启动Cadence③Cadence启动过程④Cadence启动完成后,关闭提示信息二、设计项目的建立①点击Tools—Library Manager…启动设计库管理软件②启动设计库管理软件③点击File—New--Library新建设计库文件④在弹出的菜单项中输入你的设计的库的名称,比如MyDesign,点击OK⑤选择关联的工艺库文件,我们选择关联已有的工艺库文件,点击OK⑥在弹出菜单中的Technology Library下拉菜单中选择我们需要的TSMC35mm 工艺库,然后点击OK。

⑦设计的项目库文件建立完成,然后我们在这个项目库的基础上建立其子项目。

点击选择mydesign,然后点击File-New-Cell View…⑧输入子项目的名称及子项目的类型,多种类型,目前课程设计中用到的主要是电路图编辑和版图编辑。

在设计版图之前我们假定先设计原理图:所以我们选择,然后点击OK。

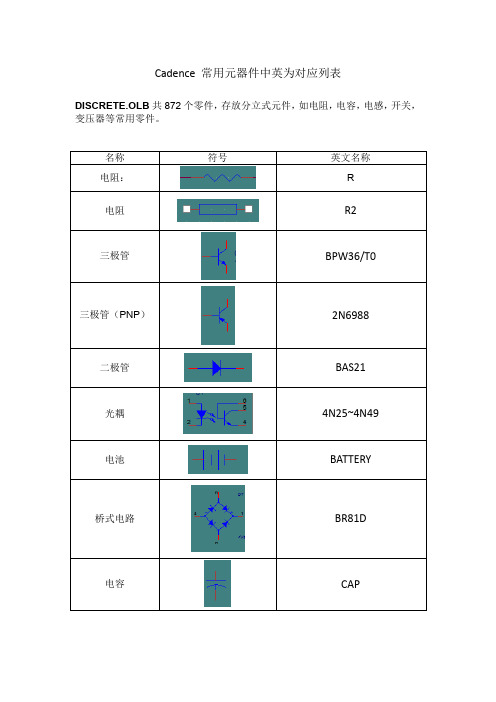

Cadence常用元器件对应表

CONNECTOR.OLB 共 816 个零件,存放连接器,如 4 HEADER,CON AT62,RCA JACK 等。

COUNTER.OLB 共 182 个零件,存放计数器 IC,如 74LS90,CD4040B。

DISCRETE.OLB 共 872 个零件,存放分立式元件,如电阻,电容,电感,开关,变压器等常用零 件。

MISCLINEAR.OLB 共 365 个零件,存放线性杂项图件(未分类),如 14573,4127,VFC32 等。

MISCMEMORY.OLB 共 278 个零件,存放记忆体杂项图件(未分类),如 28F020,X76F041 等。

MISCPOWER.OLB 共 222 个零件,存放高功率杂项图件(未分类),如 REF-01,PWR505,TPS67341 等。

DRAM.OLB 共 623 个零件,存放动态存储器,如 TMS44C256,MN41100-10 等。

ELECTRO MECHANICAL.OLB 共 6 个零件,存放马达,断路器等电机类元件。

FIFO.OLB 共 177 个零件,存放先进先出资料暂存器,如 40105,SN74LS232。

FILTRE.OLB 共 80 个零件,存放滤波器类元件,如 MAX270,LTC1065 等。

桥式电路

BR81D

电容

CAP

无极性电容

电感 振荡器

稳压器 电位器 开关 开关 变压器

CAPACITOR

CHOKE CRYSTAL

P1602AB POT

SPLIFIER.OLB 共 182 个零件,存放模拟放大器 IC,如 CA3280,TL027C,EL4093 等。

Cadence数字、签核与定制-模拟工具助力实现三星7LPP和8LPP工艺技术

Cadence数字、签核与定制/模拟工具助力实现三星7LPP和8LPP工艺技术楷登电子(美国Cadence公司)今日宣布其数字、签核与定制/模拟工具成功在三星电子公司7LPP和8LPP工艺技术上实现。

较前代高阶工艺节点FinFET技术,7LPP和8LPP工艺技术不仅进一步优化了功耗、性能和面积特性,扩展能力也更为出色。

目前,客户已经可以应用下一代技术开始早期设计。

Cadence定制/模拟、数字和签核工具全面满足三星工艺需求,支持实现7LPP和8LPP工艺技术;三星客户可开发各类复杂的高阶节点设计,充分满足移动市场和其他垂直市场的应用需求。

如需了解Cadence®数字与签核解决方案的详细内容,请访问cadence/go/samsung7nm8nmdands。

欲详细了解Cadence 定制/模拟解决方案,请访问cadence/go/samsung7nm8nmcanda。

目前,三星7LPP工艺采用的数字与签核工具包括Innovus™设计实现系统和针对DRC的物理验证系统;采用的定制/模拟工具为Virtuoso®先进工艺节点平台,包括Spectre®APS仿真器、Spectre®XPS仿真器、VirtuosoADE产品套件、Virtuoso版三星8LPP工艺采用的数字与签核工具包括Innovus™设计实现系统、QuantusQRC提取解决方案和物理验证系统;采用的定制/模拟工具为Virtuoso®先进工艺节点平台,包括Spectre®APS仿真器、Spectre®XPS仿真器、VirtuosoADE产品套件、Virtuoso版“我们与Cadence开展紧密合作,确保其定制/模拟、数字和签核工具帮助客户迅速、轻松地发挥高阶节点技术的优势,”三星电子代工厂设计团队高级副总裁JaehongPark表示。

“能够尽早有Cadence上述工具的支持对我们的客户非常重要,唯有如此才能在紧迫的上市时间内将设计交付大规模量产客户。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

嵌入式培训专家SPECCTRAQuest Foundations华清远见The SPECCTRAQuest Design FlowThe SPECCTRAQuest Design Flow consists of the following six steps:Pre-Placement Solution Space Analysis Constraint-Driven Floorplanning Constraint-Driven Routing Post-Route DRC Post-Route Analysis华清远见Design Flow: Pre-PlacementStandard form factors, mechanical restrictions, and standard practices often predefine locations of critical components. Electrical design must start with these requirements, or present a strong case why things should be changed. Pre-placed design is usually created by the CAD group as a starting point for design. Chip set placementpredetermined华清远见Database Setup AdvisorØ The first screen of the Database Seup Advisor. Ø Explains the use of Database Setup Advisor. Ø Describes the steps you must take to set up the database correctly. Ø “Set up Right, Set up Once”.华清远见Defining the Layout Cross-SectionDesignates the currently selected layer as a shield layer. The shield layer prevents the electrical signals from the two adjacent layers from interacting with each other.Activate Differential Mode Layout Cross-Section Editor华清远见DC VoltagesSPECCTRAQuest SI Expert needs source voltages for terminators and capacitors to build an electrically correct circuit.Terminated buses to 1.5 Volts华清远见Signal Model Assignment FormSignal Model U1 IBIS IOCell Model RLC RLC RLC IBIS Device Model Package Model华清远见Translating and Adding LibrariesAn Index file (.ndx) is a group of library files that have been merged and indexed together. You can use the models for simulation, but cannot modify the index file in any way.You can translate these types of signal models to SPECCTRAQuest format.Ibis2signoise quad2signoise华清远见Pre-Route Template ExtractionThe Xnet includes the drivers, receivers and interconnects of an extended net.华清远见SQ Signal Explorer Expert Parameters TabToggle to display the units on the TLine to Length or Time.华清远见SQ Signal Explorer Expert Results Tab华清远见SigWave Current WaveformsMenu Bar Tool BarWaveform library windowWaveform windowStatus Bar华清远见Solution Space Analysis Step 1Ø Extract / create topology to be analyzed. ü Pin ordering ü Discrete devices ü Rat-T positions (if any) Ø Identify / enter nominal values for all parameters. ü Board impedance ü Trace velocity ü Terminator value ü Segment lengths Point-to-point device connectionTerminators at the end of the net on short stubs.华清远见Solution Space Analysis Step 2Ø Identify manufacturing variances that are to be included in the analysis. ü Trace impedance (for example +/- 10%) ü Trace velocity ü Fast / slow components ü Device values (ex. terminators) ü Power supplies (if applicable) Ø Identify initial ranges for “design rule” parameters. ü Min / max segment lengths Trace impedance is1.5 volt supply is +/- 5%Devices = Fast and Slow65 ohms +/- 5 ohms.Terminators are +/-1ohmTrace length varies for each TLine: TL1: 4000 mils to 8000 mils, TL2 and TL3: 0 mils to 2000 mils.华清远见Solution Space Analysis Step 3Ø Create a “master list” of all variables for analyses and their ranges. Ø Identify “dependencies” between variables, based on how the design will be implemented.ü Traces on the same layer have identical characteristics. ü Resistors in the same RPAK match closely.Ø Develop a simulation strategy based on combinations to be analyzed.Devices = Fast and SlowTerminators are +/-1ohm华清远见Solution Space Analysis Step 4Ø Run simulations and gather results.ü SigXp “tabbed” report format is designed to import easily into Microsoft Excel and Access.Ø Evaluate results and identify “cases” (combinations of variables) that cause topology to fail (not meet design goals). Ø Simulate individual cases, analyze, correct design if needed, and iterate.华清远见Solution Space Analysis Step 5Ø The solution found thus far is a single-line solution. Ø Crosstalk timing shifts must be within crosstalk budget. Ø Single-line topology is modified to model coupling where appropriate. Ø Different line width / spacing rules are evaluated for timing impact. Ø Result is line width / spacing rules for layout.Devices = Fast and SlowTerminators are +/-1ohm华清远见Solution Space Analysis Step 6Ø Create final topology template from analysis results: ü Segment min / max lengths ü Parallelism rules Ø Some variances should not be included in the final topology template: ü Trace min / max impedances are often not included in the router’s rulesDevices = Fast and SlowTerminators are +/-1ohm华清远见Parametric SweepsSweep parameters are chosen by setting a start and stop value. The count value determines the number of sweep count points.华清远见Count value determines the number of sweep count points.Setting Sweep ParametersExpression listed and other parameters used in the expression determine the number of sweep count points.Discrete values determines the number of sweep count points.华清远见Assigning Prop Delay ConstraintsList the Pin or Pin-Tee pairs that have delay constraints assigned in the current topology. Identify the desired points between which Prop Delay constraint is to be applied. Delay Length % Manhattan Components are listed with their pinuse values. Identify the desired min and max delay acceptable for this pair.华清远见Template Applications and Constraint-Driven PlacementViolations in CM correspond to DRC errors Actual manhattan routing distance Worst case bubbles to the topConstraint values华清远见Constraint-Driven RoutingBubble: Hug Preferred Dynamic timing meter highlights high-speed timing constraint violation. Bubble: Off Bubble: Shove PreferredThe etch that is routed hugs the object to avoid DRC violation. The spacing rule violation flagged off by DRC markersThe etch that is routed pushes the existing etch to resolve DRC violation.华清远见U1 RLC RLCPost-Route DRC and AnalysisVCC RLCVCC RLCU2 RLC RLCStimu lusRLCTL ineRLCRLC Package Model RLCVCC RLC U3 RLC RLC RLC Package ModelRLC GNDRLCTLine Victim NetT L in ePackage Model GND RLCVCC RLC U4 RLCGNDRLCRLC GNDRLC Package Model华清远见U1 RLC RLC RLC Package Model GND RLC RLC VCCCrosstalk SimulationVCC RLC U2 RLC RLC GND RLC RLC Package ModelStimulusU3 RLC RLC RLC Package Model GND RLC RLC VCCNeighbor NetTLineU4 VCC RLC RLC RLC GND RLC RLC Package ModelLow level Victim Net TLineStimulus TLineU5 RLC RLC RLC Package Model GND RLC RLC VCCNeighbor NetU6 VCC RLC RLC RLC GND RLC RLC Package Model华清远见Simultaneous Switching Noise Report Results from a SSN simulation:华清远见System-Level AnalysisTwo layouts identified for this DesignLinkConnection, length and RLGC cable model identifiedNumber of wires in this connectionConnections on the first boardConnections on the second board华清远见Differential Pair Design ExplorationExtracted Ideal TlineCoupled model华清远见Custom Stimulus to Analyze Differential Pair TopologyMaximum of 1024 bits华清远见Differential Pair Topology Analysis华清远见Gap and Line WidthFrom the SPECCTRAQuest SI Expert menu, select Route—Connect command.Coupled ToleranceMin Line SpacingPrimary GapNeck GapLine WidthNeck Width华清远见华清远见CADENCE相关课程v v v v v v v v v v v v v初级班(三天) 1. Concept HDL 原理图设计 2. Allegro PCB设计 3. Librarian Expert 库管理 高级班(三天) Day 1: Basic theories in high-speed PCB design Pre-Placement Extracting and Simulating Topologies Day 2: Determining and Adding Constraints Template Applications and Constraint-Driven Placement Day 3: Constraint-Driven Routing Post-Route DRC and Analysis Differential Pair Design Exploration华清远见让我们一起讨论!The success's road谢谢!。