基于FPGA多通道数据采集系统设计

一种基于DSP和FPGA的多通道数据采集系统的设计

计 中还 采用 ADC 8 9模 数 转换 器。该 系统 采集信 号 频率 范围 宽、 数据 传送 量 大、数据 00 传 输速度 高 , 并具 有较 强 的扩 展 能 力,并且 具有 电路 结构 简单 、功耗低 、数据 传输 方便 等优 点 , 用于 电压 、 电流 、温度 、压 力等参量 的采集 系统 中。 可

变 为高 电平 ,指 示 A / D转 换结 束 ,结 果 数据 已 存 入锁 存器 ,这个 信号 可用作 中断 申请 。 当 OE输

入 高 电平 时 ,输 出三 态 门打开 ,转换 结 果 的数字 量 输 出到数 据总 线上 ,采用 串行接 口方 式 。F GA P

门阵列 ( P A E 1 6 20 8 F G ) P C Q 4 C 作为系统的控制部 系 统 选 择 Cy ln co e系 列 的 E 1 6 2 0 8芯 片 , PC Q 4C P采 用 T 公 司 生 产 T 3 0 5 1 芯 片 I MS 2 VC 4 6 ’ 分 , 过FG 通 P A逻辑 控制 AD 采集 电路 进行模 拟通 DS /

现代仪器 ( w. d r isr.r .n ww mo enn t ogc ) s

一

种基于 D P和 F G S P A的多通道数据采集系统的设计

吴永鹏 王章瑞 。 赵煜 滢 向前 勇

(. 1西南石油大学 电子信息工程学院 成都分公 司川西 北气矿 甲醇厂 江 油 6 10 ) 2 9 7

率 高 ,内部 时 延小 ,全 部 控 制逻 辑 由硬件 完 成 , 速 度 快 、效率 高 ,适 于大 数据 量 的高 速传 输控 制 , 可

业生 产和 科学 技术研究 的各 行业 中 , 常常 需要对 各

种数 据进行 采集 , 如液位 、温度 、压力 、频 率等信

基于FPGA的多通道数据采集系统设计与实现

基于FPGA的多通道数据采集系统设计与实现摘要:近年来,随着国内航空事业的高速发展,现代空情变得日益复杂,航管雷达目标数据和地空话音通信数据作为航空空情数据保存以及事故分析的主要手段,在空管自动化系统中发挥越来越重要的作用。

其记录系统运行的稳定性、数据记录和回放的真实性是重要空情重演、异常事故分析准确可靠的关键因素。

在航管系统应用中,记录重演系统往往具有数据量大、记录通道多,数据的可靠性、实时性以及设备模块化要求高,并且要求长时间持续不断地进行记录和处理。

为此,文章对基于FPGA的多通道数据采集系统设计与实现方面展开详细研究,希望能够给相关人士提供重要的参考价值。

关键词:数据采集;信号处理;FPGA引言:为适应当前日益复杂的空情,提高航管数据采集的精确性和可靠性,设计了一种多通道雷达话音数据采集系统。

给出了系统硬件设计架构,利用FPGA作为数据采集和逻辑控制核心,实现了16路话音数据编解码以及8路雷达数据采集和转换。

应用层软件采用多线程开发技术和原子访问内存共享设计方案,提高了业务运行的效率以及系统的可靠性。

硬件电路及应用软件实现均采用模块化设计,具有良好的可移植性。

最后,对设计的系统进行了多通道话音和大时段大数据量雷达数据采集回放测试,并对话音和雷达数据采集误差精度进行了分析,验证了系统的可靠性和精确性。

1、系统硬件架构设计数据采集系统硬件系统由以下几个模块组成:MCU控制模块、FPGA算法模块、RS232雷达数据接收串口、FXO/FXS语音、时钟模块、电源模块、连接器等;其中MCU系统是本板的控制单元,完成对板上芯片初始化、性能检测以及通过串口实现本板与其他单板的通信;FPGA模块主要对采集的雷达数据和语音信号进行监控和记录,实现机场空管部门指挥调度的语音通话和雷达探测数据的同步记录和同步回放功能;RS232雷达数据采集串口模块实现简化的三线异步RS232接口的电平转换;FXO/FXS语音模块完成FXO/FXS语音信号的数字化,支持软件切换FXS或者FXO工作模式;时钟模块负责时钟产生、时钟驱动,为各模块提供所需要的时钟;电源模块提供整板各模块所需要的工作电压。

基于FPGA+USB2.0多通道数据采集系统设计

计算 机 的广泛应用 使得 数据采 集系统 在多个 领 域有着 十分重 要 的应 用 。传 统 的数 据采 集 系 统 , 通 常采用单 片机或 D P作 为主控 制器 , 制 A D以及 S 控 / 存 储器 和其 他外 围 电路 的工 作 。用 D P作 为 主控 S 制器 , 现方式灵 活 , 是 由于其结 构限制 不能进行 实 但 并行运算 , 使得 对 多 通 道 A D采样 增 加 了难 度 , / 延 长 了开发 周期 , 处理速 度也大 大降低 了 , 本也相对 成 较高 ; 单片机 作 为主 控 制器 操 作 简单 , 本低 , 用 成 但

sg in,hg tbly,c n b iey ue o l—h n e aa a q i t n ih S it a i a ew d l sd frmut c a n ld t c us i . i io

Ke r s:F y wo d PGA ;USB;F R;Daa a q iiin I t c ust o

较前者有很大提高, E 19 I E 34还支持异步 、 E 等时传 输、 点对 点连 接 、 插拔 、 缆 提供 等 , 与 U B 比 热 线 但 S 较,S U B具有 支持热 插拔 、 带方便 、 携 标准 统一 、 以 可 连接 多个 设 备 等 优点 。笔 者 利用 F G 和 U B设 PA S

Absr c :I h r d t n ld t c u st n s se de in,p i r o to lri r o u d t n h t a t n t e ta ii a aa a q iii y tm sg o o rmay c nr l shad t p ae a d t e e ta s s in s e d o a s s in c i slw. T s p p r h sd sg e lic a e a c u st n r n miso p e ft n miso h p i o r hi e e a e in d a mu t— h nn ld t a q iio a i s se b s d o PGA n y t m a e n F a d USB 0.T e s se a he e c u rn 一r u e d t c u sto t e 2. h y t m c iv s a q iig 4 o t aa a q ii n wi t i hh ma i lfe u n y o 5 xma q e c f1 0 KHz a d t e p e ii n o 2 b t. e s se h s d s ie lic a ne I r n h r c so f 1 is T y tm a e gn d mu t— h n lF R h i t .T i p r a h c n a h e e r a—i t n lmia et e it re e c .Th y tm smo u a e fl r h sa p o c a c iv e ltme fl ra d ei n t h n e fr n e e i e e s se i d l rd —

基于FPGA+DSP的多通道数据采集系统设计

Q a u 8 0a dC S2po eta ted s no ess m i fai e ur s I . n C rv t h ei f yt s l. t I h g h t e se b

Ke r s: d t c u sto y tm ;F y wo d aa a q iiin s se PGA;DS P;FI FO

( .兰州交通大学 电子信息与工程学院 , 1 兰州 7 07 ;2 30 0 .兰州 交通大学 电工 电子实验中心 , 兰州 7 07 ) 3 0

摘

要 :介 绍 了一 种基 于 F G P A+D P的 多路数 据采 集 系统 的设 计方 案 ,描 述 了系统 的硬 件 设计 S

方 案和硬ห้องสมุดไป่ตู้件 电路 ,介 绍 了信 息采 集过程 以及 外 围通讯接 口及 软件 设计 。 过 Q at 8 02.C 2 通 ur s I.  ̄ S uI C

一

时钟域高 , 内部延时小 , 速度快 , 全部逻辑由硬件完 成 等优点 , 因此 在 高速 数 据 采集 方 面 F G P A相 对有

着 巨大优 势 , 但也 存在难 于实 现复杂 的算法 的缺点 , 而 D P适合 于高 速算法 的处 理 , S 因此 为 了 弥补 系统

的不足 , 系统 采 用 F G 本 P A+D P的方 案 。本 系统 S

方面 对多路 模拟开 关进行 选通 让选通 信号通过 信

号 调理 电路实 现 电平 调 整 并 进 行 A D转 换 的时 序 / 控 制 , 一方 面 把 转 换 好 的数 据 进 行 数 据 缓 存 , 另 当 FF IO满 时并 产生 D P能识 别 的外 部 中断信 号 及标 S 识信 号 , 知 D P取数 据 , 后 D P对 采 集 到 的数 通 S 最 S 据进 行滤波 处理 、 变换 、 分析 。 谱

基于FPGA的多通道信号采集电路设计

块单 元通 过 内部 的 三 通 连 接 器 进 行 互 联 。为 了便 于对 路 信 号 的采 样 控 制 , 设 计 中充分 利 用 了 F P G A 内部 的块 R A M资源 , 建 立 了采 样 信 号 的查 找 表 结

制 核心 。

多通 道数 据 采集 系 统 的外 部结 构 如 图 1 所示 ,

其采 用笼 屉 式 级 联 结 构 。整 个 系统 可 分 为 三 个 部 分: ① 电源 卡 , 外 部 电源 进 入 后 通 过 电源 卡 进 行 相 应 的隔离 和 转 化 成 采 集 系统 所 需 的 电源 提 供 给各

2 0 1 3年 3月 2 8日收 到

采 集 电路 采用 的并联模 式设计 , 如 图 2所示 。

该模式设计 是针对三种传统采集模式的缺点

优化 而来 。这 三种 传 统采 集 模式 为 : 一 种 是 总线 模

第一作者简介 : 储成君( 1 9 8 9 一) , 男,电路 与系统专业硕 士研究生 研 究方向: 嵌入式电路与系统 。E — ma i l : c c h e n  ̄ u n @s i n a . c n 。

构, 通 过对 各 通 道 进 行 编 码 , 从 而 实 现 大 量 的不 同

号, 如在现 代 航 天 测 试 中 , 为掌 握 飞行 器 飞 行 过 程

中系统的各种状态信息 , 需要同时对飞行过程 中的

目标 飞行 器所 受 到 的 冲 击 、 过载 、 振 动 等 参 数 进 行

实 时测量 ¨ J 。在 医疗诊 断 时 , 需要 同时 对 病 患 的血

存储 , 实现 了大量 的不 同类型 的模 拟信 号的实时采样 。

基于FPGA的高速数据采集系统设计

基于FPGA的高速数据采集系统设计随着科学技术的不断进步,数据采集系统在许多领域都发挥着重要作用。

为了满足高速数据采集的需求,基于现场可编程门阵列(FPGA)的高速数据采集系统设计应运而生。

本文将介绍这一系统的设计原理和关键技术。

首先,我们需要了解FPGA的基本原理。

FPGA是一种可编程的硬件设备,可以根据需要重新配置其内部逻辑电路。

这使得FPGA在数据采集系统中具有极大的灵活性和可扩展性。

与传统的数据采集系统相比,基于FPGA的系统可以实现更高的采样率和更低的延迟。

基于FPGA的高速数据采集系统设计主要包括以下几个关键技术。

首先是模数转换(ADC)技术。

ADC是将连续的模拟信号转换为数字信号的关键环节。

在高速数据采集系统中,需要使用高速、高精度的ADC来保证数据的准确性和完整性。

其次是FPGA内部逻辑电路的设计。

为了实现高速数据采集,需要设计高效的数据处理逻辑电路。

这些电路可以实现数据的实时处理、存储和传输等功能。

同时,还需要考虑电路的时序约束和资源分配等问题,以确保系统的稳定性和可靠性。

另外,时钟同步技术也是高速数据采集系统设计的重要内容。

在高速数据采集过程中,各个模块需要保持同步,以确保数据的准确性。

因此,需要设计合理的时钟同步方案,保证各个模块在同一个时钟周期内完成数据的采样和处理。

最后,还需要考虑系统的接口和通信问题。

基于FPGA的高速数据采集系统通常需要与其他设备进行数据交互,如计算机、存储设备等。

因此,需要设计合适的接口和通信协议,实现数据的传输和存储。

综上所述,基于FPGA的高速数据采集系统设计涉及多个关键技术,包括ADC技术、FPGA内部逻辑电路设计、时钟同步技术以及接口和通信问题。

通过合理的设计和优化,可以实现高速、高精度的数据采集,满足现代科学研究和工程应用的需求。

这将为各个领域的数据采集工作带来巨大的便利和发展空间。

基于FPGA的数据采集系统设计与实现

了异步传输 中跨时钟域造成的亚稳态问题 [ 5 1 。在本 数据采集系统的设计中采用异步 FF IO的方式来解

图 2 数 据 采 集 系统 数 据 流 程

决跨时钟域 的数据传输 问题 。因为本数据采集系统 是针对 A C芯片的测试所用的, D 因此数据采集接 口 的数据率不是 固定 的 10 H x4i 而 D R 控制 5M z5b , D 2 t 器的用户接 口和 G E控制器接 口数据率是 固定的 , 分别为 10 H x 1b 和 15 z 2i 5 M zl2i t 2MH x b ,所 以选用 3 t 异步 FF IO可以使 系统更加灵活。

基于 F GA的数据采集系统设计与实现 P

张 泽 军 , 平 分 林

( 北京工业 大学 嵌入式 系统重点 实验 室, 北京, 1 4 102 ) 0

摘要 : 设计 并 实现 了一种基 于 FG P A的 高速 数据 采 集 系统 , 端 系统 用于采 集 目标 A C芯 片 的数 字输 出, 后 D 将 采集后 的数据传 输 至 P C机再 进行 分析 。数据 采 集 系统 采用 DR D A 储 、 兆 以太 网 ( ia i D 2SRM存 千 G gb t

数据传输及控制。同时 , 模块还负责 G I F E控制器、

图 1数 据 采 集 系统 框 图

D R D 2控制 器 的用户 总线及 外 部数 据采 集 接 口之间

h¨ n . h n nA 、 ,m a , , n / s A i, ;、 1 、

L一设 — 计

巾国集成电路

Chi na nt I eg r ed icu i at C r t

块 ,其 功 能 相 当 于 一 个 D MA ( i c M m r Dr t e oy e

基于FPGA的多通道高速数据采集系统

De i n o u t— sg fM liCha ne ih- pe d Da a A c u sto S se s d o FPGA n lH g S e t q iiin y t m Ba e n

J — i., h -a HU u C a — o , IDawe - XU S u y n , J n , AO Xio t MU n t a Xi

( . h n c u ntueo t sFn eh nc n h s , 1 C a gh nIs tt f i ,ie ca i a dP yi i Op c M s s c

Ch n s a e ce c s Ch n c u 3 0 3, i a; i e e Ac d my o S in e , a g h n 1 0 3 Ch n f

10 3 ) 00 9

欣

10 3 ; 3 03

(. 1 中国科学院长春光学精 密机械 与物理 研究所 , 吉林长春

2 中 国科 学 院研 究 生 院 , 京 . 北

摘要 : 了实时监测 多轴 运动控制单元 , 测其性能及可靠性 , 为 检 设计 了一种 集 F G P A与 P I C 总线 于一 体的 多通道 高速 数据采集 系统 。该 系统并行采集 1 6通道控 制信 号 , 用 F G 应 P A对采集 的信 号进行分析 并提 取检测信 息和反馈 信息 ; 测 检 信 息通过 P I C 总线传输给计算机 , 闭环控 制反馈 信息通过 R 4 2串行通讯发 送控制 单元。信号采 集实验表 明 : 系统 S一 2 该

1 数 据 采 集 系 统 工 作 原 理 及 组 成 1 1 系统 工 作 原 理 .

将 FG P A的处 理 结果 由外部 FF IO缓 存。数 据 通 信模 块 通 过

基于FPGA的多路数据采集系统的设计

文章编号 :0 9— 5 2 2 1 ) 6— 14— 4 10 2 5 【02 0 0 2 0 中图分类号 :P 7 . T 24 2 文献标识码 : A

基 于 F G 的 多路 数 据 采 集 系统 的 设 计 PA

郭建 强,张秋云 ,王 黎 , 晓蓉 , 高 王泽勇

轮对踏 面擦 伤 的根 本原 因是列 车在 制动过 程 中

的制 动力大 于粘 着力 , 得 车 轮 在钢 轨 上 滑行 前 进 使 而并 非正 常的运 行 。众 所 周 知 , 滑行 时产 生 的摩 擦

力远 远大 于滚动 时产生 的摩擦 力 , 长期这 样 , 就会在 车轮 踏 面上形 成不 同程度 的擦伤 。 踏 面擦伤 具有 相 当严 重 的危 害 , 体表 现 为 以 具

实价值 。

1 F G 硬 件 设 计 PA

1 1 数字 系统设 计 介绍 .

通过 5个加 速 度传 感 器 采集 5路 模 拟信 号 , 经 过 电荷放 大器 , 将传 感 器 输 出 的 电荷 信 号转 化 为 电 压 信号输 出 , 后再 通过前 端 信号调 节 电路 , 模拟 然 将 信 号进行 缓 冲 、 大 、 波 和定 标 , 成 电压 差分 模 放 滤 形 拟 信号 , 目的是 减 少 直流 漂 移 , 除共 模 干 扰 , 其 去 为 后 级 的模/ 数转 换 器 ( D ) 准 备 , 统 的硬 件 框 A C做 系 图如 图 1 示 。经 过 A S34模 数 转换 器 件 后 , 所 D86 将 输入 的模拟 差分 信号 变换 为适用 于控 制过 程 、 存储 、 处理 、 执行 计算并 显示 读 出等其 他 目的 的数 字信 号 。

Ke r s: FP y wo d GA ;a r so t s ;Ve io DL ;M o esm b a in e t rl g H d li

基于FPGA的多路数据采集模块硬件设计

I s u n T c n q e a d S n o n t me t r eh iu n e sr

2 0 01

第 3期

No 3 .

基 于 F GA 的 多路 数 据 采 集 模 块 硬 件 设 计 P

李 鹏 , 游春 。李锦 明 马 , ,

摘 要 : 了实现 对 5 路 模 拟 信 号 进 行 不 同频 率 的 采 集 , 计 了一 种 以 现 场 可 编 程 门 阵 列 ( P A) 为 8 设 F G 为核 心 的 多路 模 拟 信号采集模块。该模块采用 F G 芯片 X 23 PA C S0作 为 系统 的核 心 控 制 器件 来 实 现 对 A D 转 换 器 的 控 制 、 / 多路 模 拟 开 关 的

w s d sg e o i lme t h a a a q ii o f i e e t e u n y t h 8 c a n la Mo i n l.T e F GA c i 2 3 f a e in d t mp e n e d t c ust n o f r n  ̄ q e e ot e5 一 h n e n g sg a s h P h p XC S 0 o t i df XI I op r t n w s u e s t e c nr ld vc o a h e e t e fl wig f n t n ,t e A D o v r rc n r l n lg mu t L NX C r o ai a s d a h o t e ie t c iv h ol n u ci s h / c n et o t ,a ao l — o o o o e o i p e e sc nr l aa c d n ,t e c n e so ft e p r l ld t o s ra d t n O o . T e p o rm t cu e o h e in i lx r o to ,d t o i g h o v r in o a a l a a t e il aa a d S n h e h r g a sr t r ft e d sg s u f xb e a y t o to ,v r e ib e n t fn t n h s b e a ia e h o g e t l i l ,e s o c n r l ey rl l ,a d i u ci a e n v l t d t r u h ts. e a s o d Ke r s f l r g a y wo d : ed p o r mma l ae a r y aa a q ii o i b e g t ra ;d t c u st n;d t o i g i aa c d n

基于FPGA的多通道高速数据采集系统设计共3篇

基于FPGA的多通道高速数据采集系统设计共3篇基于FPGA的多通道高速数据采集系统设计1随着现代科技的高速发展,各种高速数据的采集变得越来越重要。

而基于FPGA的多通道高速数据采集系统因具有高速、高精度和高可靠性等优点,逐渐受到了越来越多人的关注和青睐。

本篇文章将围绕这一课题,对基于FPGA的多通道高速数据采集系统进行设计和探讨。

1、FPGA的基础知识介绍FPGA(Field-Programmable Gate Array)是可重构的数字电路,可在不使用芯片的新版本的情况下重新编程。

FPGA具有各种不同规模的可用逻辑单元数,可以根据需要进行定制化配置。

FPGA可以根据需要配置每个逻辑单元,并使用活动配置存储器从而实现功能的完整性、高速度和多样化的应用领域。

2、多通道高速数据采集系统的设计在高速数据采集领域中,多通道采集是非常常见的需求。

多通道采集系统通常由高速采集模块、ADC芯片、DSP芯片等核心部件组成。

在本文中,我们将会采用 Analog Devices(ADI)公司的AD7699高速ADC和Xilinx(赛灵思)公司的Kintex-7 FPGA,来设计多通道高速数据采集系统。

2.1系统架构设计系统架构是设计一个多通道高速数据采集系统的第一步。

本系统的架构由两个主要芯片组成,分别为高速的ADC模块和FPGA模块。

其中ADC模块负责将模拟信号转换为数字信号,而FPGA模块则负责将数据处理为人类可以处理的数据。

2.2模块设计由于本系统是多通道高速数据采集系统,所以我们需要设计多个模块来完成数据采集任务。

在本系统中,每个模块包含一个ADC芯片和一个FPGA芯片,用于处理和存储采集的数据。

ADC 芯片可以通过串行接口将数据传递给FPGA芯片,FPGA芯片则可以将数据存储在DDR3内存中。

2.3信号采集与处理对于多通道高速数据采集系统,信号的采集与处理是至关重要的。

因此我们需要谨慎设计。

在本系统中,每个通道的采样速率可以达到1MSPS,采样精度为16位。

基于FPGA多通道数据采集系统设计

关 键 词 : 数 据 采 集 ; F P G A; C S5101A; 标 定 ; 延 时 寄 存 器

中 图 分 类 号 : T N79

文献标识码:B

Abstr act:This paper describes a multi - channel data acquisition system using EP1K100 serials FPGA and CS5101A A/D converter.

您的论文得到两院院士关注 文章编号:1008- 0570(2007)02- 2- 0199- 03

P LD CP LD FP GA 应 用

基于 FPGA 多通道数据采集系统设计

De s ig n o f Da ta Acq u is itio n S ys te m Ba s e d o n FPGA

技 系统的精度主要取决于信号的输入路径, 即必须考虑到板卡上

的元器件工作情况和线路上信号传输对实际转换精度的影响,

术 因此实现采集通道的标定对于整个采集系统有重要的意义。每

一组模拟输入信号均要经多路开关, 到一个前置放大电路, 再

创 进入 ADC 中。该信号路径即为待标定的通道。当多路开关通道

之间的匹配较好时, 一路通道一次即可标定该组多路开关的所

《 P LC 技术应用 200 例》

邮局订阅号: 82-946 360 元 / 年 - 199 -

P LD CP LD FP GA 应 用

中 文 核 心 期 刊《 微 计 算 机 信 息 》( 嵌 入 式 与 S OC )2007 年 第 23 卷 第 2-2 期

入端 。该 采集 系 统 使用 3 片 CS5101A, 分 别对 应 3 个 采 集 子 单 元, 至 多 可 满足 48 路 输 入通 道 的 要求 。在 一 个采 样 周 期内 , 选 择 哪 路 差 分 模 拟 信 号 进 行 A/D 转 换 由 采 集 控 制 FPGA 通 过 控 制 每 片 ADG407 的 地 址 选 择 端 和 每 片 CS5101A 的 通 道 选 择 端 实现。电路及 FPGA 结构框图见图 2 所示。

基于FPGA的多通道数据隔离采集电路设计

化

工

自 动 化

及 仪

表

第3 8卷

P 位 于输 出端 , 采 集 电路 共 地 。 H N 2 1的 D 与 C R0 主要 工作 参数 如下 :

非线 性误 差 0 0 % .1

2所示 。当 L D通过驱 动 电流 时 , 出红外 光 , E 发 该 光分 别 照射 在 光 敏 二 极 管 P 和 P : 。P D D 上 D、 电容 c 与运放 A。 成 反 馈 回 路 , 构 调整 流 经 L D E

关键词 FG P A 线性光耦 数 据 采 集 隔 离

中图 分 类 号

T24 P 7

文 献 标 识 码 A

文 章 编 号 10 .9 2 2 1 )010 .3 003 3 (0 1 1 —2 90

数 据 采 集 技术 是 信 息 科 学 的一 个 重 要 分 支 ,

它在 自控 、 达 、 感及 通 信等 领域 有着 广泛 的应 雷 遥 用 … 。在通 常 的采 集 条 件 下 , 输 入 量 之 间 是 共 各 地 的 , 以采用 常规方 法对 输入 量进 行采 集 , 必 可 不 考 虑 地线 之 间的 隔离 问题 。但 在某 些特 殊 的测 试 条 件 下 ( 同时监 测不 同设 备 的电 源 电压 ) 各 输 如 , 入 量 之 间是不 共 地 的 , 能 因测 试 设 备 的 接 人 而 不 导 致输 入 量 共 地 , 变 了设 备 原 有 的工 作 状 态 。 改

序 号

9 l 0 1 1 1 2 l 3 1 4 1 5 1 6 28 0 0 3o o o 35 0 0 380 0 4o o o 450 0 480 0 5oo o 28 3 7 30 8 7 35 91 38 9 9 4l4 0 4 61 7 4 92 5 5l0 3

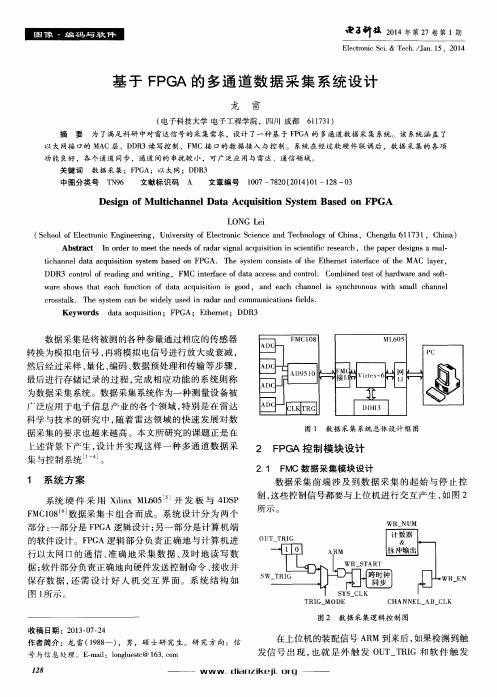

基于FPGA的多通道数据采集系统设计

wa r e s h o ws t h a t e a c h f u n c t i o n o f d a t a a c q u i s i t i o n i s g o o d, a n d e a c h c h a n n e l i s s y n c h r o n o u s wi t h s ma l l c h a n n e l c r o s s t a l k . T h e s y s t e m c a n b e wi d e l y u s e d i n r a d a r a n d c o mmu n i c a t i o n s ie f l d s .

L0NG L e i

( S c h o o l o f E l e c t r o n i c E n g i n e e r i n g ,U n i v e r s i t y o f E l e c t r o n i c S c i e n c e a n d T e c h n o l o g y o f C h i n a ,C h e n g d u 6 1 1 7 3 1 ,C h i n a )

关键词 数 据 采 集 ;F P G A; 以 太 网 ;D D R 3

中图分类号

T N 9 6

文献 标 识 码

A

文章 编 号

1 0 0 7— 7 8 2 0 ( 2 0 1 4 ) 0 1 —1 2 8— 0 3

基于fpga多通道实现对信号的采集技术案例

基于FPGA多通道实现对信号的采集技术案例1. 引言在现代科技发展中,信号采集技术是一项至关重要的内容。

而基于FPGA的多通道信号采集技术能够有效地完成对不同信号的采集和处理。

本文将从简单到复杂,由浅入深地介绍基于FPGA多通道实现对信号的采集技术,并给出相关案例和个人观点。

2. 什么是FPGA(Field Programmable Gate Array)?FPGA是一种集成电路,它提供了一种灵活可编程的硬件评台,可以根据需要进行重新配置和编程,实现不同功能。

3. 信号采集技术概述信号采集技术是指将各种源自不同环境和介质的信号转换成数字信号的技术。

它在电子、通信、仪器仪表等领域有着广泛的应用。

4. FPGA多通道实现对信号的采集技术基于FPGA的多通道信号采集技术通过多个通道同时采集信号,并实现多通道的同步和并行处理。

这种技术在某些特定应用场景下具有显著的优势。

4.1 FPGA多通道信号采集技术的优势•高性能:FPGA具有并行处理能力,能够实现快速、高效的信号采集和处理。

•灵活性:FPGA硬件可编程的特性使得其能够根据具体需求进行灵活配置和定制,适用于不同的信号采集场景。

•可扩展性:FPGA可以根据需要增加或减少通道,实现对不同数量通道的信号采集。

4.2 FPGA多通道信号采集技术的应用案例以某高端仪器仪表为例,该仪器需要同时采集多路信号,并对这些信号进行实时处理和分析。

基于FPGA的多通道信号采集技术使得该仪器能够满足高速、高精度的数据采集要求,并实现了多通道数据的同步处理,为用户提供了更加全面的数据分析和展示功能。

4.3 个人观点和理解我认为基于FPGA的多通道信号采集技术不仅具有高性能和灵活性,而且在一些特定的领域有着得天独厚的优势。

随着科技的进步和应用场景的扩大,这项技术将会有着更广阔的发展前景。

5. 总结本文从FPGA的定义开始,介绍了信号采集技术的概念,然后重点介绍了基于FPGA 的多通道信号采集技术,并结合实际案例进行了说明。

基于FPGA的多通道高速数据采集系统设计

四、数据存储与传输

在高速数据采集系统中,数据的存储和传输是非常重要的环节。我们可以使用 DDR3 SDRAM作为主要的数据存储设备,其高带宽和低延迟特性能够满足高速 数据采集的需求。对于数据的传输,我们可以使用PCIe或者以太网等高速接口, 确保数据传输的实时性和稳定性。

五、系统优化与测试

在系统设计完成后,我们需要进行系统测试和优化。我们可以通过实际的信号 输入来验证系统的采样率、分辨率和噪声性能。同时,我们还需要对系统的功 耗进行测试和优化,以确保系统的长时间稳定运行。

3、硬件实现:FPGA内部的各种硬件资源,如查找表(LUT)、触发器(Flipflop)和数字信号处理器(DSP)等,被充分利用来实现数据采集和处理。

参考内容

关键词:FPGA,高速数据采集, 实时处理,高精度测量

引言

随着科技的不断发展,高速数据采集技术在许多领域的应用越来越广泛。例如, 在工业生产中需要实时监控生产过程的数据,而在科学研究领域中则需要获取 大量实验数据进行分析。为了满足这些需求,基于FPGA(现场可编程门阵列) 的高速数据采集系统应运而生。本次演示将详细介绍基于FPGA的高速数据采集 系统的设计方法、技术特点、应用场景及未来展望。

2、FPGA核心:进行数据的高速处理和传输。 3、存储和传输模块:用于数据的存储和传输。

4、电源和时钟模块:提供稳定的电源和时钟信号。

三、FPGA逻辑设计

FPGA逻辑设计是整个系统的核心部分,主要负责数据的接收、处理和传输。在 设计中,我们需要利用FPGA的并行处理能力,优化算法,提高数据处理速度。 同时,我们还需要考虑到系统的可扩展性,以便在未来能够方便地进行功能升 级。

六、结论

基于FPGA的高速数据采集系统因其灵活性和高性能而具有广泛的应用前景。通 过合理的设计和优化,我们可以实现高采样率、高分辨率、低噪声、低功耗的 高速数据采集。随着科技的不断发展,我们期待看到更多的创新和突破在高速 数据采集领域取得。

多路数据采集系统的FPGA方案实现

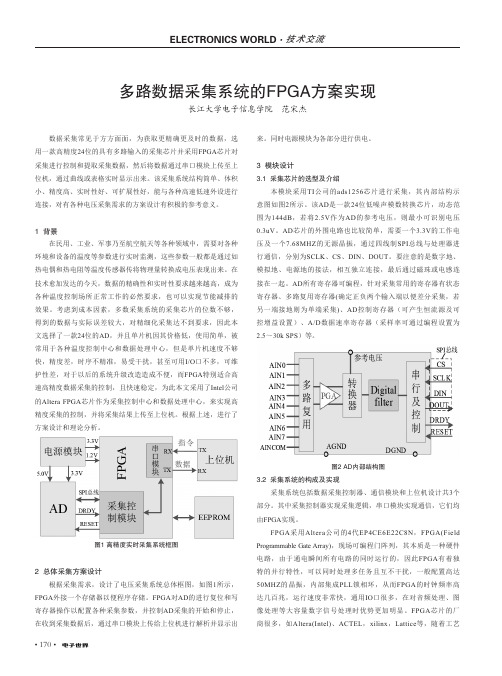

• 170•数据采集常见于方方面面,为获取更精确更及时的数据,选用一款高精度24位的具有多路输入的采集芯片并采用FPGA 芯片对采集进行控制和提取采集数据,然后将数据通过串口模块上传至上位机,通过曲线或表格实时显示出来。

该采集系统结构简单、体积小、精度高、实时性好、可扩展性好,能与各种高速低速外设进行连接,对有各种电压采集需求的方案设计有积极的参考意义。

1 背景在民用、工业、军事乃至航空航天等各种领域中,需要对各种环境和设备的温度等参数进行实时监测,这些参数一般都是通过如热电偶和热电阻等温度传感器传将物理量转换成电压表现出来。

在技术愈加发达的今天,数据的精确性和实时性要求越来越高,成为各种温度控制场所正常工作的必然要求,也可以实现节能减排的效果。

考虑到成本因素,多数采集系统的采集芯片的位数不够,得到的数据与实际误差较大,对精细化采集达不到要求,因此本文选择了一款24位的AD ,并且单片机因其价格低,使用简单,被常用于各种温度控制中心和数据处理中心,但是单片机速度不够快,精度差,时序不精准,易受干扰,甚至可用I/O 口不多,可维护性差,对于以后的系统升级改造造成不便,而FPGA 特别适合高速高精度数据采集的控制,且快速稳定,为此本文采用了Intel 公司的Altera FPGA 芯片作为采集控制中心和数据处理中心,来实现高精度采集的控制,并将采集结果上传至上位机。

根据上述,进行了方案设计和理论分析。

图1 高精度实时采集系统框图2 总体采集方案设计根据采集需求,设计了电压采集系统总体框图,如图1所示,FPGA 外接一个存储器以便程序存储。

FPGA 对AD 的进行复位和写寄存器操作以配置各种采集参数,并控制AD 采集的开始和停止,在收到采集数据后,通过串口模块上传给上位机进行解析并显示出来。

同时电源模块为各部分进行供电。

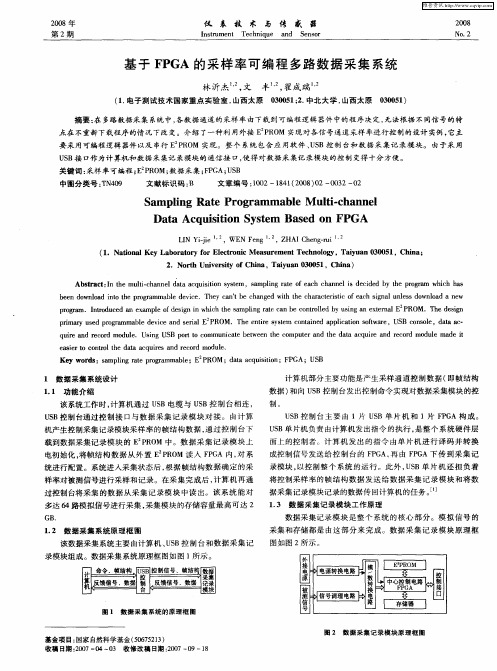

3 模块设计3.1 采集芯片的选型及介绍本模块采用TI 公司的ads1256芯片进行采集,其内部结构示意图如图2所示。

基于FPGA的采样率可编程多路数据采集系统

2 ot nv ri f hn , ay a 3 0 1 C ia .N rhU ies yo ia T iu n00 5 , hn ) t C

Ab t a t I h l — h n ld t c u st n s se ,s mp i g r t fe c h n li e i e y t e p o rm h c a sr c :n t e mu t c a e aa a q i i y tm i n io a l ae o a h c a e s d cd d b h r g a w ih h s n n b e o n o d i t te p o rmma l e ie e n d w la n o h r ga be d v c ,T e a ’ b h n e i h h r ce it fe c in l ne sd w la e h y C t e c a g d w t t e c a a tr i o a h sg a ls o n o d a n w n h sc u p o rm .I t d c d a x mp eo e in i h c es mp i gr t a e c nr l d b sn n e tr a ROM.T ed s n rga nr u e n e a l f sg n w ih t a l ae c n b o t l y u ig a xe n l P o d h n oe E h ei g

维普资讯

2 08 拄 0

仪

表 技 术 与 传 感 器

2 08 o No .2

第 2期

I sr me Te h q a Se s r n tu nt c niue nd no

基 于 F GA 的采样 率 可 编程 多路数 据 采集 系统 P

基于FPGA的多通道同步数据采集系统设计的开题报告

基于FPGA的多通道同步数据采集系统设计的开题报告一、研究背景及意义现今科学技术的发展离不开数据采集系统的支持,特别是对于多通道同步数据采集需求的应用场景,如地震观测、医学信号测量、声学分析等方面,需要高效、准确地采集各通道信号,并进行后续处理。

传统的基于单片机或DSP的数据采集系统受限于计算速度和存储容量,很难满足多通道大规模数据采集的实时要求,因此需要一种高性能、可扩展性强的解决方案。

FPGA(Field Programmable Gate Array)作为一种可编程逻辑芯片,能够在硬件层面完成指定的计算任务,具有并发处理能力、低功耗、高速度等优点,因此被广泛应用于科学研究和工业应用领域。

基于FPGA的数据采集系统不仅能够实现多通道同步数据采集,而且具有高速率和实时性,可以满足各种应用场景的需求。

本课题旨在设计一种基于FPGA的多通道同步数据采集系统,能够高效采集并存储多通道信号,具有高带宽和实时性,为相关领域研究提供支持和帮助。

二、研究内容及关键技术1. 多通道信号采集:设计多通道ADC(Analog-to-Digital Converter)接口电路,通过FPGA进行并行采集多路模拟信号,并将其转换为数字信号。

2. 同步采集控制:设计同步模块实现各通道信号的同步采集控制,保证数据的同步性和可靠性。

采用外部触发方式,通过引入时钟信号对多通道ADC进行同步采集。

3. 数据存储和处理:将采集到的数据通过高速接口(如DDR2/DDR3)传输到FPGA内部或外部存储器进行存储,实现高速率、大容量的数据存储和后续处理。

4. 系统性能优化:优化系统性能,如降低功耗、提高采样速度和精度等,以适应不同应用场景的需求。

三、研究对象与方法1. 硬件实现:选用FPGA芯片作为核心器件,通过Verilog HDL等硬件描述语言编写设计代码进行FPGA开发与实现。

2. 软件开发:对于设计的数据采集系统,需要进行软件平台的开发工作,包括FPGA设计工具、数据处理和存储相关软件等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

该 数 据 采 集 系 统 涉 及 到 的 关 键 芯 片 主 要 为 FPGA、ADC 转

个 传 感 器 , 系 统 要 求 在 不 多 于 180us 的 时 间 内 需 实 现 全 部 40 换芯片。

路通 道数 据 的 现场 高 精 度采 集 、预 处理 、实 时 存储 及 远 程传 输 。

FPGA选用 Altera 公 司的 EP1K100 系 列 。该系 列 芯 片 采 用

《 P LC 技术应用 200 例》

邮局订阅号: 82-946 360 元 / 年 - 199 -

P LD CP LD FP GA 应 用

中 文 核 心 期 刊《 微 计 算 机 信 息 》( 嵌 入 式 与 S OC )2007 年 第 23 卷 第 2-2 期

入端 。该 采集 系 统 使用 3 片 CS5101A, 分 别对 应 3 个 采 集 子 单 元, 至 多 可 满足 48 路 输 入通 道 的 要求 。在 一 个采 样 周 期内 , 选 择 哪 路 差 分 模 拟 信 号 进 行 A/D 转 换 由 采 集 控 制 FPGA 通 过 控 制 每 片 ADG407 的 地 址 选 择 端 和 每 片 CS5101A 的 通 道 选 择 端 实现。电路及 FPGA 结构框图见图 2 所示。

3.2 FPGA 设计 采集 控 制 FPGA 的 全 局 时 钟 频 率 为 20MHz, 其 主 要 的 I/O 引 脚 包 括 3 组 CS5101A 的 控 制 信 号 和 ADG407 的 通 道 选 择 信 号, 以及与光纤接口通讯用的 32 位数据总线、8 位地址 总 线 、读 写控制线和采集开始/结束信号。信号具体描述如下。 SCLK:ADC 串 行 转 换 结 果 在 此 输 入 信 号 的 下 降 沿 变 化 , 在 上升沿有效。 SDATA:在 SCLK 的 下 降 沿 输 出 数 据 位 , 可 在 SCLK 的 上 升 沿对数据进行有效锁存。 /HOLD:该 引 脚 的 下 降 沿 将 CS5101A 设 定 为 保 持 状 态 并 触 发一个转换。 /STBY:在 ADC 复位后指示校准状态。在校准期间保持低电 平, 校准完毕返回高电平。 /RST: 低电平复位。回复高电平时触发 一 完 整的 校 准 序列 波。校准系统结构框图 该系 统 实现 数 据 的采 集 、预 处理 和 存 储功 能 。当 采 集 控 制 FPGA 经光纤接口接收到来自远程 伺服 控 制 板卡 的 开 始采 集 指 令, 来自各个传感器的差分模拟信号即经系统内的多路开关被 选通地输入模数转换器, 转换 结 果 进而 被 引 入采 集 控 制 FPGA

创 新

理、存储 和 传 输, 即 用 软 件实 现 数 据的 采 集 , 这在 一 定 程度 上 局 限了 数 据 采集 的 速 度、效 率 及 时序 的 精 确控 制 。本 文研 究 的 数

2 关键芯片介绍

据 采 集 系统 应 用 于某 高 速 高精 IC 设 备 , 待 采 集 信 号 来 源 于 多

关 键 词 : 数 据 采 集 ; F P G A; C S5101A; 标 定 ; 延 时 寄 存 器

中 图 分 类 号 : T N79

文献标识码:B

Abstr act:This paper describes a multi - channel data acquisition system using EP1K100 serials FPGA and CS5101A A/D converter.

FPGA 为本采集系统的核心, 如图 1 所示。

其工作时无需外部跟随和保持运放器。CS5101A 的线性度误差

为±0.001%FS, 满刻度误差为±1LSB, 转换频率为 100KHz, 具有自

校准、抗温漂特性, 长时间空载可维持精度不变。选用该高性能

ADC芯 片 对 实 现 采 集 系 统 的 精 度 校 准 和 诊 断 作 用 有 重 要 意 义 。

您的论文得到两院院士关注 文章编号:1008- 0570(2007)02- 2- 0199- 03

P LD CP LD FP GA 应 用

基于 FPGA 多通道数据采集系统设计

De s ig n o f Da ta Acq u is itio n S ys te m Ba s e d o n FPGA

1 系统结构

数据采集系统。 Crystal 公司的 CS5101A 是一款 16 位 高精 度 CMOS 模 数串

本文设计的 数 据 采集 系 统 划分 为 A/D 转 换电 路 、采 集控 制 行 转 换芯 片 , 内 含双 通 道 输入 多 路 开 关 、ADC、转 换 和 校 准 微 控

FPGA 和光纤传输接口等若干部分, 以 A/D 转换电路 、采集 控 制 制 器 、时 钟发 生 器 、比较 器 和 串行 通 讯 口, 其 固 有 的采 样 结 构 使

为核 心 控 制 ADC 和 数 据 传输 , 这 样 可达 到 预 期 要 求 , 并 简 化 外 持 3.3V/5V 混 合 电 压 信 号 , 无 需 额 外 电 平 转 换 芯 片 进 行 电 平 匹

围电路, 降低设计风险, 缩短开发周期。

配 。其 特点 正 适 合应 用 于 具有 复 杂 逻辑 及 有 存储 、缓 冲 能 力 的

路 最 大 采 样 频 率 100KHz、精 度 为 12 位 有 效 数 位 的 差 分 模 拟 信 号 采 集 , 具 有 采 集 通 道 输 入 路 径 的 自 标 定 功 能 。介 绍 了 该 控 制

FPGA 由 顶 至 下 模 块 化 设 计 的 具 体 实 现 方 案 , 并 给 出 其 核 心 模 块 的 状 态 跃 迁 图 及 时 序 仿 真 波 形 。

新 有通道。在此选择每片 ADG407 的最后一路输入通道作为其标

定通道, 以采集系统板卡提供的零位电压( 模拟地) 和差分参考 电压为其输入信号, 从而进行 ADC 整体精度的校准和诊断。

在上 述 设计 下 , 将 CS5101A 的 BP/UPN 引 脚 拉 高 使 其 工 作 在双端状态。并通过设置其 SCKMOD 引脚和 OUTMOD 引脚电 平 使 CS5101A 工 作 在 PDT( 管 道 数 据 传 输 ) 的 串 行 数 据 输 出 模 式下, 以利 FPGA 的时序控制。在此模式下, 采集控制 FPGA 为 CS5101A 提供 串 行数 据 输 出时 钟 信 号 SCLK, 在 转 换 时 刻 寄 存 当前数据, 进而在下一个转换周期输出上一次转换结果。 CS5101A 的/HOLD 信 号 必 须 在 上 次 转 换 的 数 据 出 现 在 SDATA 引脚之前保持为低电平, 以激发下一次转换。系统采用 8.192MHz 的石英晶振器为 CS5101A 提供时钟信号。

The system achieves acquiring 40 - route differential analog signals with the maximal frequency of 100KHz and the precision of 12

bits,and also provides self- calibration function.A top- down methodology is used in the design of FPGA. The state diagrams and sim- ulation waveforms of main modules are presented. Key wor ds:FPGA,data acquisition,CS5101A,calibr ation,delay r egister

技 系统的精度主要取决于信号的输入路径, 即必须考虑到板卡上

的元器件工作情况和线路上信号传输对实际转换精度的影响,

术 因此实现采集通道的标定对于整个采集系统有重要的意义。每

一组模拟输入信号均要经多路开关, 到一个前置放大电路, 再

创 进入 ADC 中。该信号路径即为待标定的通道。当多路开关通道

之间的匹配较好时, 一路通道一次即可标定该组多路开关的所

技 术

引言

数据采集系统是计算机测控系统中不可或缺的组成部分, 是 影 响 测 控 系 统 的 精 度 等 性 能 指 标 的 关 键 因 素 之 一 。常 用 数 据 采集 方 案是 以 微 处理 器 为 核心 控 制 多个 通 道 的信 号 采 集、预 处

中 , 在 进 行 适 当 的 预 处 理 后 , 数 据 被 存 储 在 FPGA 内 嵌 的 DPRAM 中 等 待 读取 。同 时 根 据 对 FPGA 内 建 的 寄 存 器 操 作 实 现采 集 系 统的 其 他 功能 , 如 复 位、标 定 等 。全系 统 12 位 有 效 数 位 的 转 换 精 度 由 高 精 度 A/D 芯 片 以 及 对 模 拟 差 分 信 号 输 入 路 径的标定来保证。

万耀:硕士研究生 湖北省自然科学基金项目资助( 编号: 2006ABA065)

3 方案实现

3.1 电路设计 系统 以 8 通道 差 分 多路 开 关 ADG407、差分 运 放 器 INA105 和 CS5101A 构 成 采 集 控 制 FPGA 的 信 号 输 入 通 道 , 如 图 2 所 示。该采集系统需要有 40 路差分模拟电压信号 输入 , 故 使 用 6 片 ADG407 以 实 现最 大 48 路 模拟 输 入 通 道 的 多 路 复 用 。 每 片 ADG407 的 输 出 连 接 到 一 个 0.5 倍 差 分 运 放 器 INA105 实 现 差 分至单端转换, 经过运放网络后连接到 CS5101A 的 一 个模 拟 输

考 虑到 FPGA 器 件 的高 集 成 度、高 时 钟 频 率 、时 序 控 制 精 确 、编 查 找表 ( LUT) 和 EAB( 嵌 入 式 阵 列 块 ) 相 结 合 的 结 构 , 内 核 采 用