MBD101中文资料

开关量输入采集器使用说明书讲解

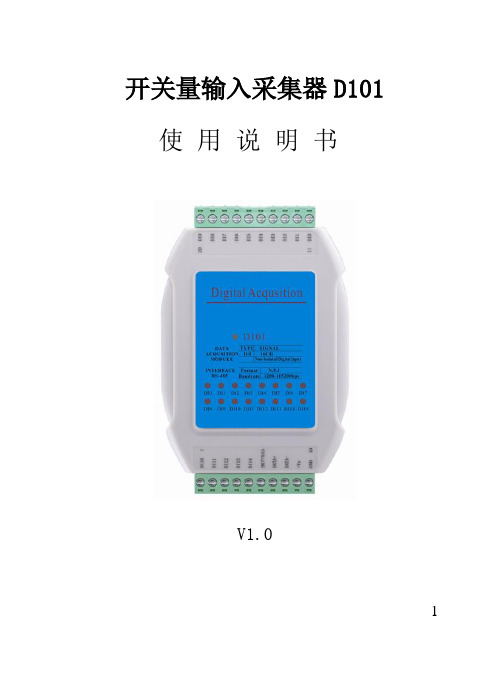

1开关量输入采集器D101 使用说明书V1.0尊敬的用户:衷心感谢您选用深圳市聚贤达科技有限公司的产品。

本手册主要介绍开关量输入采集器D101的工作原理、技术指标、主要功能、安装调试及使用与维护等内容。

为了使您更好地使用我们的产品,请您仔细阅读本手册,在应用中如果您有任何问题和要求,或需要相关技术支持,可以与我们的销售单位联系,我们将及时给予回应。

2目录1.前言 (5)2.内容 (5)3.要求 (5)4.警示 (5)5.概述 (6)6.技术参数 (6)7.产品外观 (7)7.1装置运行指示灯 (8)7.2各通道指示灯 (8)7.3产品接线端子定义 (8)8.产品原理和功能 (10)9.安装操作 (11)9.1外形尺寸 (11)9.2机柜安装 (12)310.常见问题及解决 (14)11.售后服务 (14)12.技术培训 (14)13.其他声明 (14)14.设备清单 (15)41.前言请在使用本产品前仔细阅读各章节。

2.内容本手册主要介绍开关量输入采集器D101的工作原理、技术指标、主要功能、安装调试及使用与维护等内容,由资深的专业技术人员编写,是设备使用维护的必备资料。

3.要求在任何情况下,都不应该由不具备专业资历或未经培训的人员来操作。

使用者必须是具有电气设备安装和操作经验的专业技术人员。

由不具备资历的人员对设备进行设置和操作,或不按照本书中有关规定进行包装、储运、安装和连接电源,都将可能导致设备损坏。

4.警示运输或存储不当会对设备造成损害;5供电电压错误会对设备造成损坏或引起火灾;如发现无法解决的问题,请及时与我公司联系或将设备送回我公司处理,请勿自行拆装维修。

5.概述开关量输入采集器D101是用于计算机机房、重要设备间、配线间、网络机柜、服务器机柜、配电柜、粮库、重要仓库以及其他室内场合的开关量数据采集装置。

采集开关量,装置能通过RS-485接口将信号传送给中央监控设备。

6.技术参数供电电源:DC10V~30V;通道: 16;LED显示:与16通道一一对应;开关量输入电平:干接点:逻辑电平0:接地;67 逻辑电平1: 断开;干接点有效距离: 最大500m ; D/I 用于计数器通道: 16;输入频率: 100Hz ;16位 : 0~65535;电源 :功耗: 0.9W ;尺寸规格:124mm×80mm×33mm;7.产品外观指示灯和按键功能说明7.1装置运行指示灯正常:正常工作时指示灯按1Hz的频率闪亮;故障:常亮、常灭、快闪为故障。

MPDRX103S;中文规格书,Datasheet资料

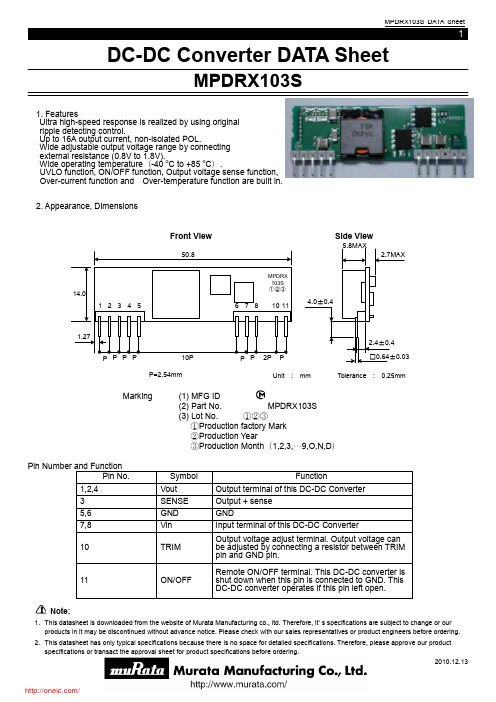

Note:1. This datasheet is downloaded from the website of Murata Manufacturing co., ltd. Therefore, it ’ s specifications are subject to change or our products in it may be discontinued without advance notice. Please check with our sales representatives or product engineers before ordering.DC-DC Converter DATA SheetMPDRX103S1. FeaturesUltra high-speed response is realized by using original ripple detecting control.Up to 16A output current, non-isolated POL.Wide adjustable output voltage range by connecting external resistance (0.8V to 1.8V). Wide operating temperature (-40 o C to +85 oC ).UVLO function, ON/OFF function, Output voltage sense function, Over-current function and Over-temperature function are built in. 2. Appearance, DimensionsFront ViewSide ViewP=2.54mm(1) MFG ID (2) Part No. MPDRX103S (3) Lot No. ①②③ ①Production factory Mark ②Production Year③Production Month (1,2,3,…9,O,N,D )MarkingNote:1. This datasheet is downloaded from the website of Murata Manufacturing co., ltd. Therefore, it ’ s specifications are subject to change or our products in it may be discontinued without advance notice. Please check with our sales representatives or product engineers before ordering. 3. Block Diagram4. Environmental Conditions4 .1 Operating Temperature Range -40 to +85 °C (Temperature gradient ≦10°C /H ) 4 .2 Storage Temperature Range -40 to +85 °C (Temperature gradient ≦25°C /H ) 4 .3 Operating Humidity Range 20% ~ 85%(No water condenses in any cases.)4 .4 Storage Humidity Range 10% ~ 90% (Unpacked condition. No water condenses in any cases.) 4 .5 Maximum Wet Bulb39°C5. Absolute Maximum Rating 5 .1 Input Voltage Range10.8V – 13.2V 5 .2 ON/OFF Pin InputVoltage Range-0.3V to Vin+0.3V7,81,2,410115,63Note:1. This datasheet is downloaded from the website of Murata Manufacturing co., ltd. Therefore, it ’ s specifications are subject to change or our products in it may be discontinued without advance notice. Please check with our sales representatives or product engineers before ordering. 6. Characteristicso※CautionThe above electrical characteristics are guaranteed with the condition that the impedance of the input voltage source is sufficiently low as shown in section 9. Connecting an input inductance or using an input power supply with output inductance may cause an unstable operation of this device. Please check the proper operation of this device with the peripheral circuits on your system.Note:1. This datasheet is downloaded from the website of Murata Manufacturing co., ltd. Therefore, it ’ s specifications are subject to change or our products in it may be discontinued without advance notice. Please check with our sales representatives or product engineers before ordering.6. 2 Thermal DeratingThe above derating limits apply to this product soldered directly to 101.6*180mm*1.6mm PCB (double-sided, with 70um copper). Any adjacent parts of high temperature may cause overheating. For reliable operation, please ensure that the FET temperature of this product is maintained below 120°C and the inductor temperature is below 106°C.Note:1. This datasheet is downloaded from the website of Murata Manufacturing co., ltd. Therefore, it ’ s specifications are subject to change or ourproducts in it may be discontinued without advance notice. Please check with our sales representatives or product engineers before ordering.7. Operation in information7.1 Adjusting the Output VoltageThe output voltage can be adjusted ranging from 0.8V to 1.8V by connecting resistors between TRIM-pin (10Pin) to GND-pin (5Pin).The following equation gives the required external-resistance value to adjust the output voltage to the required Vout.Internal circuit7.2 ON/OFF ControlON/OFF functionBy using ON/OFF function, the operation of this product can be disabled without disconnection of input voltage. Sequence of a power supply system and power-saving control can be easily achieved usingthis function.ON/OFF control usageWhen ON/OFF-pins(11pin) are left open …… Output Voltage =ON When ON/OFF-pins(11pin) are connected to GND …… Output Voltage=OFFVout 0.8-5440Rtrim= -5100[ohm]RtrimNote: 1. This datasheet is downloaded from the website of Murata Manufacturing co., ltd. Therefore, it ’ s specifications are subject to change or our products in it may be discontinued without advance notice. Please check with our sales representatives or product engineers before ordering. 7.3 Output Voltage SensingBy connecting SENSE-pin to the load, output voltage drop in wiring shall be compensated.Please do NOT connect SENSE-pin to the output of LC filter that is set to the Vout line. When using this way, this product will not operate properly.7.4 Input External capacitorIt is recommended to connect a ceramic capacitor or a low-impedance electrolytic capacitor of 22μF or more at Vin terminal. Smaller input capacitor may leads to an unstable operation of this product caused by input voltagefluctuation. Please check the proper operation of it on your product when smaller input capacitor is used.7.5 Output External capacitorCeramic capacitors are recommended as output external capacitor.Using ceramic capacitors, small output variation and small ripple voltage are realized.Output capacitor should be within 47μF to 1000μF. Output capacitor shall be placed near th e output terminal. When using plural capacitors, please make sure to place a capacitor of at least 47μF near the output terminal, and place other capacitors near the load.When using LC output filter, please make sure to place a capacitor of at least 47μF near the output terminal.8. Reliability 8.1 HumidityAccording to JIS-C-0022.40 土2°C, 90 to 95%RH, 100 hours. Leave for 4 hours at room temperature.No damage in appearance and no deviation from electrical characteristics (section 6.1.).8.2 Temperature CyclesRepeat cycle 5 times. Leave 2 hours at room temp.No damage in appearance and no deviation from electrical characteristics (section 6.1.).8.3 Vibration10 to 55Hz, 1.5mm amplitude (1minute cycle), 1 hour for each of X, Y , Z directions.No damage in appearance and no deviation from electrical characteristics (section 6.1.).8.4 Mechanical Shock20G, 1 time for each X, Y , Z directions.No damage in appearance and no deviation from electrical characteristics (section 6.1.).LoadLoadNote: 1. This datasheet is downloaded from the website of Murata Manufacturing co., ltd. Therefore, it ’ s specifications are subject to change or our products in it may be discontinued without advance notice. Please check with our sales representatives or product engineers before ordering.9. Test CircuitIn the following test circuit, the initial values under item 6.1. should be met.9.1. General Measure CircuitCin : 100uF /16V (16ZL120MMRKTA6.3X11,Rubycon)(Low-impedance Electrolytic Capacitor )Cout : 100uF /6.3V (GRM32EB30J107ME16L, Murata)(Ceramic Capacitor )9.2. Ripple Voltage Measurement CircuitCoaxial cable :1.5D-2V, L=1.5mVinNote: 1. This datasheet is downloaded from the website of Murata Manufacturing co., ltd. Therefore, it ’ s specifications are subject to change or our products in it may be discontinued without advance notice. Please check with our sales representatives or product engineers before ordering. 10. Packaging Specification①Like the figure below, put the product on the conductive mat in a row. (5lines ×4columns)「 ②Pile and pack the 3 above –mentioned units at maximum.Fig1-1. Top View Product4 columnsFig1-2. S ide View1. This datasheet is downloaded from the website of Murata Manufacturing co., ltd. Therefore, it’ s specifications are subject to change or ourproducts in it may be discontinued without advance notice. Please check with our sales representatives or product engineers before ordering.Note:1. This datasheet is downloaded from the website of Murata Manufacturing co., ltd. Therefore, it ’ s specifications are subject to change or our products in it may be discontinued without advance notice. Please check with our sales representatives or product engineers before ordering.11. Production factoryKomatsu Murata Mfg.Co.,Ltd. Kanazu Murata Mfg.Co.,Ltd. Wakura Murata Mfg. Co., Ltd.分销商库存信息: MURATAMPDRX103S。

开关-温度传感器和开关选型 -中文

插入式显示表

MBD 1000 VVS no EAN no 5702423187898 订货号 060G2850

MAKING MODERN LIVING POSSIBLE

何处应用

针对温度控制和测量领域不同的应用,丹佛斯提供了丰富的温度开关和传感器产品。 选型手册上的产品为当今市场提供了最精确和可靠的选择,而它们仅是我们产品家族中 最常用的一部分。 这一系列产品覆盖了从轻工业到重工业的各种应用,其中包括:船舶、农业、供热 和卫生、空调、蒸汽动力厂以及液压等。 KP系列温度开关为干燥环境(防护等级IP33)的工业应用提供了一种紧凑和经济的 控制方案。 RT和KPS系列温度开关以高防护等级而知名,因此可以应用于潮湿的环境中。同时, KPS开关可以承受高强度振动和冲击的影响,因此它成为一些特殊环境如发动机监测领 域独一无二的选择。

0 - 40

3 - 10

30/33*

Room sensor

5702423148769

060L117166

* when mounted on wall

开关-RT系列

类型 RT 14 (capillary tube) RT 101 (capillary tube) 带毛细管的KP 61, 78, 79, 81 室内传感器KP 75 RT 101 (capillary tube) RT 101 (capillary tube) - max. reset RT 107 (capillary tube) - max. reset RT 107 (capillary tube) RT 120 (capillary tube) RT 123 (capillary tube) 设定温度 ˚C -5 - 30 25 - 90 25 - 90 25 - 90 70 - 150 70 - 150 120 - 215 150-250 可调回差 ˚C (最低-最高) 2 - 10 2.4 - 20 2.4 - 20 2.4 - 20 1.8 - 25 1.8 - 25 1.8 - 30 1.8 - 30 防护等级(IP) 66 66 66 54 54 66 66 66 毛细管长度 2m 2m 5m 2m 2m 2m 2m 2m EAN no 5702428004206 5702423119448 5702423119486 5702423119455 5702423119622 5702423119615 5702423120659 5702423120802 订货号 017-509966 017-500366 017-502266 017-500466 017-513666 017-513566 017-520866 017-522066

【微计算机信息】_可编程计算机控制器_期刊发文热词逐年推荐_20140724

科研热词 可编程控制器 plc 可编程序控制器 控制系统 造纸机械 自动控制 纺织机械 石油化工 电力传动 步进电机 印刷机械 包装机械 《plc技术应用200例》 触摸屏 现场总线 控制器 控制 可编程逻辑器件 cpld 组态软件 组态王 现场可编程门阵列 接口 可编程自动化 变频器 动态数据交换 profibus-dp can总线 高频发射机 高速计数器 高速脉冲 高温高压 驱动器 间隙调整 镗孔挖槽 金刚石 通讯 通用可编程接口 通用串行总线 远程监控 远程控制 运动控制系统 运动控制模块 运动控制 输入输出模块 软件设计 转换模块 读卡机 语法分析 试验环道 词法分析 设备控制

推荐指数 21 10 9 5 4 4 4 4 4 4 4 4 4 3 3 3 3 3 3 2 2 2 2 2 2 2 2 2 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

2009年 序号 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52

2008年 序号 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52

时序 无级调速 数据通信 数据传输 故障诊断 扩展模块 总线 彩灯控制器 开放性 开放式结构 开关磁阻电机 带式输送机 巡线机器人 定位控制 多泵制 处理系统 塞焊 图像传感器 回转窑 喷涂机器人 可编程运动控制器 可编程计算机控制器 可编程自动化控制器 可编程控制器模块 可编程多轴控制器 可编程器件 反模糊化 双向通讯 参数化编程 压缩机 医疗机器人 区域控制 动态调光 分布式系统 光电传感器 倍加福编码器 信号发生装置 位置控制 伺服电机控制 伺服电机 代码生成 人机界面 主从通讯 串行通讯 串行通信 串口扩展 中断功能 下位机 上位机 wtopcsvr.dll工具包 wincc visual c++ vhdl usb2.o

巴斯夫原油破乳剂Basorol L 101安全技术说明书

安全技术说明书页: 1/9 巴斯夫安全技术说明书按照GB/T 16483编制日期 / 本次修订: 18.12.2021版本: 4.2日期/上次修订: 07.10.2019上次版本: 4.1日期 / 首次编制: 19.11.2007产品: 原油破乳剂 Basorol L 101Product: Basorol® L 101(30434591/SDS_GEN_CN/ZH)印刷日期 01.08.20231. 化学品及企业标识原油破乳剂 Basorol L 101Basorol® L 101推荐用途和限制用途: 油田用特性化学品公司:巴斯夫(中国)有限公司中国上海浦东江心沙路300号邮政编码 200137电话: +86 21 20391000传真号: +86 21 20394800E-mail地址: **********************紧急联络信息:巴斯夫紧急热线中心(中国)+86 21 5861-1199巴斯夫紧急热线中心(国际):电话: +49 180 2273-112Company:BASF (China) Co., Ltd.300 Jiang Xin Sha RoadPu Dong Shanghai 200137, CHINA Telephone: +86 21 20391000Telefax number: +86 21 20394800E-mail address: ********************** Emergency information:Emergency Call Center (China):+86 21 5861-1199International emergency number: Telephone: +49 180 2273-1122. 危险性概述纯物质和混合物的分类:根据 GHS 标准,该产品不需要进行分类。

巴斯夫安全技术说明书日期 / 本次修订: 18.12.2021版本: 4.2产品: 原油破乳剂 Basorol L 101Product: Basorol® L 101(30434591/SDS_GEN_CN/ZH)印刷日期 01.08.2023标签要素和警示性说明:根据GHS标准,该产品不需要添加危险警示标签其它危害但是不至于归入分类:注意有关存储和操作的规定或注解,无已知特殊危害。

防腐阀门

-

-

-

1/8

163.87

7.2

1/8

196.65

8.9

1/8

229.4

10.6

1/4

1425.7 19.5

1/4

2284.1 34.9

1/4

3048

39.9

1/4

3244.7 51.9

3/8

6964.5 93.2

3/8

7439.7 105.3

3/8

14912 184.5

1/2

49161 407.4

-

目录

衬氟对夹式蝶阀-D371F4 衬氟对夹式蝶阀 衬氟截止阀-J41F46 衬氟截止阀 衬氟截止阀 衬氟手动蝶阀 衬氟放料球阀-FQ41F46 衬氟放料球阀 衬氟放料球阀-FQ41F 衬氟放料球阀 衬氟放料球阀 衬氟旋塞阀 衬氟止回阀-H41F46 衬氟止回阀 衬氟止回阀 衬氟法兰截止阀-J41F46 衬氟法兰截止阀 衬氟法兰球阀-Q41F46 衬氟法兰球阀 衬氟球阀 衬氟直流截止阀 衬氟直角截止阀-J44F46 衬氟直角截止阀 衬氟直角截止阀 衬氟立式止回阀-H42F46 衬氟立式止回阀 衬氟蓝式过滤器 衬氟蝶阀

三、材料:

阀体:铸铁、球墨铸铁、碳钢、不锈钢 阀盖:铸铁、球墨铸铁、碳钢、不锈钢 衬里:无衬里、橡胶 隔膜:橡胶 阀瓣:铸铁 气缸:铝合金、碳钢 气动薄膜:橡胶 阀杆:碳钢、不锈钢 手轮:铸铁

四、测试:

衬里层:电火花检测 试验与检验按 BS6755 标准 公称压力:PN(MPa) 阀体:PN×1.5 密封:PN×1.1

3/8

16715

212

注:1. 气动隔膜阀门尚可附装反馈信号、限位器或定位器,以适应自控、程控或调节流量的需要。 2. 气动阀门的反馈信号采用无触点传感技术。 3. 采用薄膜式气缸替代活塞式气缸,排除了活塞易损漏而导致无法启闭阀门的弊端。 4. 当气源发生故障时,可操作手轮使阀门开启。

ES1001-9PDDB1中文资料(Power-One)中文数据手册「EasyDatasheet - 矽搜」

Page

电磁兼容性(EMC).................................... 15 抗扰度环境条件.................................. 17 机械数据................................................ .................... 18 安全和安装说明........................................ 19 选项说明............................................... ............. 23 配件................................................. ........................... 32 EC-一致性声明............................................. ... 33

C S 2 5 40 -9 E R

系列................................................. ...............................小号

输出数量............................................... ......... 1,2

Eff. 输入电压

Eff. 选项

V算I一个- VI最大

[%] 20至100伏直流

[%]

77

FS1001-7R

83

FS1301-7R

77

-9

83 E , -9E

84

FS1501-7R

84

V

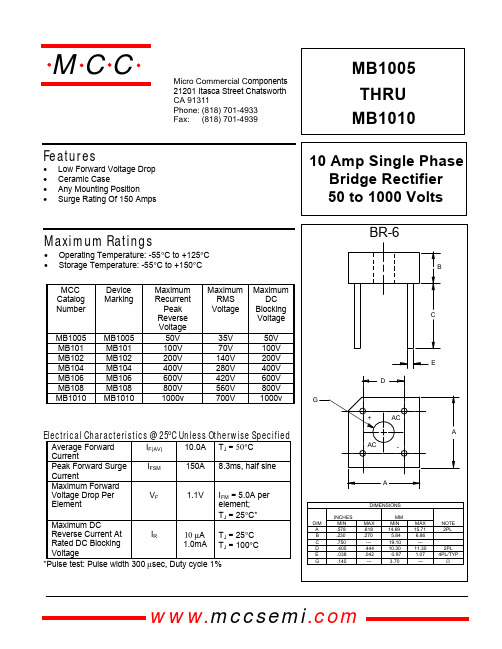

MB101资料

Electrical Characteristics @ 25°C Unless Otherwise Specified

Average Forward Current Peak Forward Surge Current Maximum Forward Voltage Drop Per Element IF(AV) IFSM 10.0A 150A TJ = 50°C 8.3ms, half sine

Volts Instantaneous Reverse Leakage Current - MicroAmperes versus Percent Of Rated Peak Reverse Voltage - Volts

Figure 4 Peak Forward Surge Current 200

元器件交易网

MCC

Features

• • • • Low Forward Voltage Drop Ceramic Case Any Mounting Position Surge Rating Of 150 Amps

omponents 21201 Itasca Street Chatsworth !"# $

10

150 100

86 Amps 4来自Amps50 25 0 1 4 6 8 10 20 40 60 80 100

2 Single Phase, Half Wave 60Hz Resistive or Inductive Load 0 0 25 50 75 100 150 175

2

Cycles Peak Forward Surge Current - Amperesversus Number Of Cycles At 60Hz - Cycles

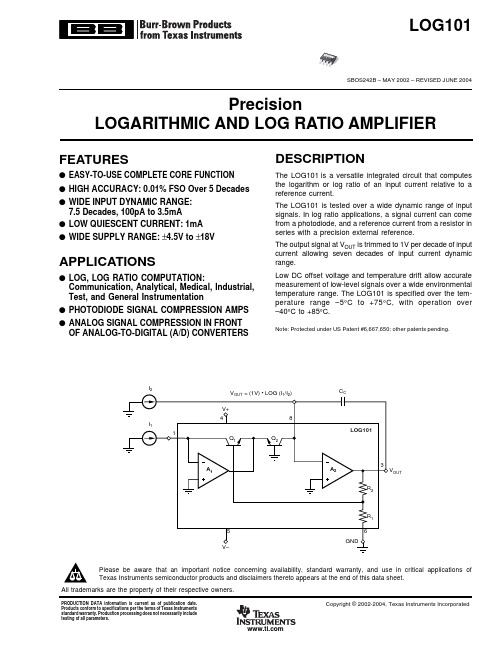

LOG101资料

I2 V+ 4 I1 1

VOUT = (1V) • LOG (I1/I2)

CC

8 LOG101 Q1 Q2

A1

A2 R2

3

VOUT

R1 5 GND V– 6

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

ELECTRICAL CHARACTERISTICS

At TA = +25°C, VS = ±5V, and ROUT = 10kΩ, unless otherwise noted.

Boldface limits apply over the specified temperature range, TA = –5°C to +75°C.

LOG101AID PARAMETER CORE LOG FUNCTION IIN / VOUT Equation LOG CONFORMITY ERROR(1) Initial over Temperature GAIN(3) Initial Value Gain Error vs Temperature INPUT, A1 and A2 Offset Voltage vs Temperature vs Power Supply (PSRR) Input Bias Current vs Temperature Voltage Noise Current Noise Common-Mode Voltage Range (Positive) (Negative) Common-Mode Rejection Ratio (CMRR) OUTPUT, A2 (VOUT) Output Offset, VOSO, Initial vs Temperature Full-Scale Output (FSO) Short-Circuit Current 1nA to 100µA (5 decades) 100pA to 3.5mA (7.5 decades) 1nA to 100µA (5 decades) 100pA to 3.5mA (7.5 decades)(2) 1nA to 100µA 1nA to 100µA TMIN to TMAX CONDITION MIN TYP VO = (1V) • log (I1/I2) 0.01 0.06 0.0001 0.0005 1 0.15 0.003 ±0.3 ±2 5 ±5 Doubles Every 10°C 3 30 4 (V+) – 2 (V+) – 1.5 (V–) + 2 (V–) + 1.2 105 ±3 ±2 (V–) + 1.2 ±18 0.2 MAX UNITS V % % %/ °C %/ °C V/decade % %/ °C mV µV/°C µV/V pA µVrms nV/√Hz fA/√Hz V V dB ±15 (V+) – 1.5 mV

LH28F008BVT-BTL10资料

LHF08VZ1q Handle this document carefully for it contains material protected by international copyright law. Any reproduction, full or in part, of this material is prohibited without the express written permission of the company.q When using the products covered herein, please observe the conditions written herein and the precautions outlined in the following paragraphs. In no event shall the company be liable for any damages resulting from failure to strictly adhere to these conditions and precautions.(1) The products covered herein are designed and manufactured for the following applicationareas. When using the products covered herein for the equipment listed in Paragraph (2), even for the following application areas, be sure to observe the precautions given in Paragraph (2). Never use the products for the equipment listed in Paragraph (3).•Office electronics•Instrumentation and measuring equipment•Machine tools•Audiovisual equipment•Home appliance•Communication equipment other than for trunk lines(2) Those contemplating using the products covered herein for the following equipment whichdemands high reliability, should first contact a sales representative of the company and then accept responsibility for incorporating into the design fail-safe operation, redundancy, and other appropriate measures for ensuring reliability and safety of the equipment and the overall system.•Control and safety devices for airplanes, trains, automobiles, and othertransportation equipment•Mainframe computers•Traffic control systems•Gas leak detectors and automatic cutoff devices•Rescue and security equipment•Other safety devices and safety equipment, etc.(3) Do not use the products covered herein for the following equipment which demandsextremely high performance in terms of functionality, reliability, or accuracy.•Aerospace equipment•Communications equipment for trunk lines•Control equipment for the nuclear power industry•Medical equipment related to life support, etc.(4) Please direct all queries and comments regarding the interpretation of the above threeParagraphs to a sales representative of the company.q Please direct all queries regarding the products covered herein to a sales representative of the company.Rev. 1.1CONTENTSPAGE1 INTRODUCTION (3)1.1 Features (3)1.2 Product Overview (3)2 PRINCIPLES OF OPERATION (6)2.1 Data Protection (7)3 BUS OPERATION (7)3.1 Read (7)3.2 Output Disable (7)3.3 Standby (7)3.4 Deep Power-Down (7)3.5 Read Identifier Codes Operation (8)3.6 Write (8)4 COMMAND DEFINITIONS (8)4.1 Read Array Command (10)4.2 Read Identifier Codes Command (10)4.3 Read Status Register Command (10)4.4 Clear Status Register Command (10)4.5 Block Erase Command (10)4.6 Byte Write Command (11)4.7 Block Erase Suspend Command (11)4.8 Byte Write Suspend Command (12)4.9 Considerations of Suspend (12)4.10 Block Locking (12)4.10.1 V PP=V IL for Complete Protection (12)4.10.2 WP#=V IL for Block Locking (12)4.10.3 WP#=V IH for Block Unlocking (12)PAGE5 DESIGN CONSIDERATIONS (18)5.1 Three-Line Output Control (18)5.2 Power Supply Decoupling (18)5.3 V PP Trace on Printed Circuit Boards (18)5.4 V CC, V PP, RP# Transitions (18)5.5 Power-Up/Down Protection (19)5.6 Power Dissipation (19)6 ELECTRICAL SPECIFICATIONS (20)6.1 Absolute Maximum Ratings (20)6.2 Operating Conditions (20)6.2.1 Capacitance (20)6.2.2 AC Input/Output Test Conditions (21)6.2.3 DC Characteristics (22)6.2.4 AC Characteristics - Read-Only Operations (24)6.2.5 AC Characteristics - Write Operations (26)6.2.6 Alternative CE#-Controlled Writes (28)6.2.7 Reset Operations (30)6.2.8 Block Erase and Byte Write Performance (31)Rev. 1.1LH28F008BVT-BTL10 8M-BIT (1Mbit × 8) Smart3 Flash MEMORYs Smart3 Technology2.7V-3.6V V CC2.7V-3.6V,4.5V-5.5V or 11.4V-12.6V V PPs High-Performance Access Time100ns(2.7V-3.6V)s Operating Temperature0°C to +70°Cs Optimized Array Blocking Architecture Two 8K-byte Boot BlocksSix 8K-byte Parameter BlocksFifteen 64K-byte Main BlocksBottom Boot Locations Extended Cycling Capability100,000 Block Erase Cycless Enhanced Data Protection FeaturesAbsolute Protection with V PP=GNDBlock Erase and Byte Write Lockoutduring Power TransitionsBoot Blocks Protection with WP#=V IL s Enhanced Automated Suspend OptionsByte Write Suspend to ReadBlock Erase Suspend to Byte WriteBlock Erase Suspend to Reads Automated Byte Write and Block EraseCommand User InterfaceStatus Registers Low Power ManagementDeep Power-Down ModeAutomatic Power Savings Mode DecreasesI CC in Static Modes SRAM-Compatible Write Interfaces Industry-Standard Packaging40-Lead TSOPs ETOX TM* Nonvolatile Flash Technologys CMOS Process (P-type silicon substrate)s Not designed or rated as radiation hardenedSHARP’s LH28F008BVT-BTL10 Flash memory with Smart3 technology is a high-density, low-cost, nonvolatile, read/write storage solution for a wide range of applications. LH28F008BVT-BTL10 can operate at V CC=2.7V-3.6V and V PP=2.7V-3.6V. Its low voltage operation capability realize battery life and suits for cellular phone application.Its Boot, Parameter and Main-blocked architecture, flexible voltage and extended cycling provide for highly flexible component suitable for portable terminals and personal computers. Its enhanced suspend capabilities provide for an ideal solution for code + data storage applications. For secure code storage applications, such as networking, where code is either directly executed out of flash or downloaded to DRAM, the LH28F008BVT-BTL10 offers two levels of protection: absolute protection with V PP at GND, selective hardware boot block locking. These alternatives give designers ultimate control of their code security needs.The LH28F008BVT-BTL10 is manufactured on SHARP’s 0.35µm ETOX TM* process technology. It come in industry-standard package: the 40-lead TSOP ideal for board constrained applications.*ETOX is a trademark of Intel Corporation.Rev. 1.11 INTRODUCTIONThis datasheet contains LH28F008BVT-BTL10 specifications. Section 1 provides a flash memory overview. Sections 2, 3, 4 and 5 describe the memory organization and functionality. Section 6 covers electrical specifications.1.1 FeaturesKey enhancements of LH28F008BVT-BTL10 Smart3 Flash memory are:•Smart3 Technology•Enhanced Suspend Capabilities•Boot Block ArchitecturePlease note following important differences:•V PPLK has been lowered to 1.5V to support 2.7V-3.6V and 4.5V-5.5V block erase and byte write operations.The V PP voltage transitions to GND is recommended for designs that switch V PP off during read operation.•To take advantage of Smart3 technology, allow V CC and V PP connection to 2.7V-3.6V.1.2 Product OverviewThe LH28F008BVT-BTL10 is a high-performance 8-Mbit Smart3 Flash memory organized as 1M-byte of 8 bits. The 1M-byte of data is arranged in two 8K-byte boot blocks, six 8K-byte parameter blocks and fifteen 64K-byte main blocks which are individually erasable in-system. The memory map is shown in Figure 3.Smart3 technology provides a choice of V CC and V PP combinations, as shown in Table 1, to meet system performance and power expectations. V PP at 2.7V-3.6V and 4.5V-5.5V eliminates the need for a separate 12V converter, while V PP=12V maximizes block erase and byte write performance. In addition to flexible erase and program voltages, the dedicated V PP pin gives complete data protection when V PP≤ V PPLK.Table 1. V CC and V PP Voltage Combinations Offered bySmart3 TechnologyV CC Voltage V PP Voltage2.7V-3.6V 2.7V-3.6V,4.5V-5.5V, 11.4V-12.6V Internal V CC and V PP detection Circuitry automatically configures the device for optimized read and write operations.A Command User Interface (CUI) serves as the interface between the system processor and internal operation of the device. A valid command sequence written to the CUI initiates device automation. An internal Write State Machine (WSM) automatically executes the algorithms and timings necessary for block erase and byte write operations.A block erase operation erases one of the device’s 64K-byte blocks typically within 0.51s (2.7V-3.6V V CC, 11.4V-12.6V V PP), 8K-byte blocks typically within 0.31s (2.7V-3.6V V CC, 11.4V-12.6V V PP) independent of other blocks. Each block can be independently erased 100,000 times. Block erase suspend mode allows system software to suspend block erase to read or write data from any other block.Writing memory data is performed in byte increments of the device’s 64K-byte blocks typically within 12.6µs (2.7V-3.6V V CC, 11.4V-12.6V V PP), 8K-byte blocks typically within 24.5µs (2.7V-3.6V V CC, 11.4V-12.6V V PP). Byte write suspend mode enables the system to read data or execute code from any other flash memory array location.The boot blocks can be locked for the WP# pin. Block erase or byte write for boot block must not be carried out by WP# to Low and RP# to V IH.The status register indicates when the WSM’s block erase or byte write operation is finished.The access time is 100ns (t AVQV) over the commercial temperature range (0°C to +70°C) and V CC supply voltage range of 2.7V-3.6V.The Automatic Power Savings (APS) feature substantially reduces active current when the device is in static mode (addresses not switching). In APS mode, the typical I CCR current is 3mA at 2.7V V CC.When CE# and RP# pins are at V CC, the I CC CMOS standby mode is enabled. When the RP# pin is at GND, deep power-down mode is enabled which minimizes power consumption and provides write protection during reset. A reset time (t PHQV) is required from RP# switching high until outputs are valid. Likewise, the device has a wake time (t PHEL) from RP#-high until writes to the CUI are recognized. With RP# at GND, the WSM is reset and the status register is cleared.The device is available in 40-lead TSOP (Thin Small Outline Package, 1.2 mm thick). Pinout is shown in Figure 2.Rev. 1.1Rev. 1.1Table 2. Pin Descriptions Symbol Type Name and FunctionA0-A19INPUT ADDRESS INPUTS: Inputs for addresses during read and write operations. Addresses are internally latched during a write cycle.A16-A19: Main Block Address. (Boot and Parameter block Addresses are A13-A19.)DQ0-DQ7INPUT/OUTPUTDATA INPUT/OUTPUTS: Inputs data and commands during CUI write cycles; outputs dataduring memory array, status register and identifier code read cycles. Data pins float to high-impedance when the chip is deselected or outputs are disabled. Data is internally latched during awrite cycle.CE#INPUT CHIP ENABLE: Activates the device’s control logic, input buffers, decoders and sense amplifiers. CE#-high deselects the device and reduces power consumption to standby levels.RP#INPUT RESET/DEEP POWER-DOWN: Puts the device in deep power-down mode and resets internal automation. RP#-high enables normal operation. When driven low, RP# inhibits write operations which provides data protection during power transitions. Exit from deep power-down sets the device to read array mode. With RP#=V HH, block erase or byte write can operate to all blocks without WP# state. Block erase or byte write with V IH<RP#<V HH produce spurious results and should not be attempted.OE#INPUT OUTPUT ENABLE: Gates the device’s outputs during a read cycle.WE#INPUT WRITE ENABLE: Controls writes to the CUI and array blocks. Addresses and data are latched on the rising edge of the WE# pulse.WP#INPUT WRITE PROTECT: Master control for boot blocks locking. When V IL, locked boot blocks cannot be erased and programmed.V PP SUPPLY BLOCK ERASE AND BYTE WRITE POWER SUPPLY: For erasing array blocks or writing bytes. With V PP≤V PPLK, memory contents cannot be altered. Block erase and byte write with an invalid V PP (see DC Characteristics) produce spurious results and should not be attempted.V CC SUPPLY DEVICE POWER SUPPLY: Do not float any power pins. With V CC≤V LKO, all write attempts to the flash memory are inhibited. Device operations at invalid V CC voltage (see DC Characteristics) produce spurious results and should not be attempted.GND SUPPLY GROUND: Do not float any ground pins.NC NO CONNECT: Lead is not internal connected; it may be driven or floated.Rev. 1.17FFFF 700006FFFF 600005FFFF 500004FFFF 400003FFFF 300002FFFF 200001FFFF 100000FFFF 000008K-byte Parameter Block 58K-byte Boot Block 001FFF 0E0000C0000DFFF 0A0000BFFF 0800009FFF 0600007FFF 0400005FFF 0200003FFF Bottom Boot8K-byte Parameter Block 48K-byte Parameter Block 38K-byte Parameter Block 28K-byte Parameter Block 18K-byte Parameter Block 08K-byte Boot Block 164K-byte Main Block 664K-byte Main Block 564K-byte Main Block 464K-byte Main Block 364K-byte Main Block 264K-byte Main Block 164K-byte Main Block 0FFFFF F0000EFFFF E0000DFFFF D0000CFFFF C0000BFFFF B0000AFFFF A00009FFFF 9000064K-byte Main Block 1464K-byte Main Block 1364K-byte Main Block 1264K-byte Main Block 1164K-byte Main Block 1064K-byte Main Block 964K-byte Main Block 88FFFF 8000064K-byte Main Block 7[A 19-A 0]Rev. 1.12 PRINCIPLES OF OPERATIONThe LH28F008BVT-BTL10 Smart3 Flash memory includes an on-chip WSM to manage block erase and byte write functions. It allows for: 100% TTL-level control inputs, fixed power supplies during block erasure and byte write, and minimal processor overhead with RAM-like interface timings.After initial device power-up or return from deep power-down mode (see Bus Operations), the device defaults to read array mode. Manipulation of external memory control pins allow array read, standby and output disable operations.Status register and identifier codes can be accessed through the CUI independent of the V PP voltage. High voltage on V PP enables successful block erasure and byte writing. All functions associated with altering memory contents−block erase, byte write, status and identifier codes−are accessed via the CUI and verified through the status register.Commands are written using standard microprocessor write timings. The CUI contents serve as input to the WSM, which controls the block erase and byte write. The internal algorithms are regulated by the WSM, including pulse repetition, internal verification and margining of data. Addresses and data are internally latch during write cycles. Writing the appropriate command outputs array data, accesses the identifier codes or outputs status register data.Interface software that initiates and polls progress of block erase and byte write can be stored in any block. This code is copied to and executed from system RAM during flash memory updates. After successful completion, reads are again possible via the Read Array command. Block erase suspend allows system software to suspend a block erase to read/write data from/to blocks other than that which is suspend. Byte write suspend allows system software to suspend a byte write to read data from any other flash memory array location.Figure 3. Memory Map2.1 Data ProtectionDepending on the application, the system designer may choose to make the V PP power supply switchable (available only when memory block erases or byte writes are required) or hardwired to V PPH1/2/3. The device accommodates either design practice and encourages optimization of the processor-memory interface.When V PP≤V PPLK, memory contents cannot be altered. The CUI, with two-step block erase or byte write command sequences, provides protection from unwanted operations even when high voltage is applied to V PP. All write functions are disabled when V CC is below the write lockout voltage V LKO or when RP# is at V IL. The device’s boot blocks locking capability for WP# provides additional protection from inadvertent code or data alteration by block erase and byte write operations. Refer to Table 6 for write protection alternatives.3 BUS OPERATIONThe local CPU reads and writes flash memory in-system. All bus cycles to or from the flash memory conform to standard microprocessor bus cycles.3.1 ReadInformation can be read from any block, identifier codes or status register independent of the V PP voltage. RP# can be at either V IH or V HH.The first task is to write the appropriate read mode command (Read Array, Read Identifier Codes or Read Status Register) to the CUI. Upon initial device power-up or after exit from deep power-down mode, the device automatically resets to read array mode. Five control pins dictate the data flow in and out of the component: CE#, OE#, WE#, RP# and WP#. CE# and OE# must be driven active to obtain data at the outputs. CE# is the device selection control, and when active enables the selected memory device. OE# is the data output (DQ0-DQ7) control and when active drives the selected memory data onto the I/O bus. WE# must be at V IH and RP# must be at V IH or V HH. Figure 11 illustrates read cycle.3.2 Output DisableWith OE# at a logic-high level (V IH), the device outputs are disabled. Output pins (DQ0-DQ7) are placed in a high-impedance state.3.3 StandbyCE# at a logic-high level (V IH) places the device in standby mode which substantially reduces device power consumption. DQ0-DQ7 outputs are placed in a high-impedance state independent of OE#. If deselected during block erase or byte write, the device continues functioning, and consuming active power until the operation completes.3.4 Deep Power-DownRP# at V IL initiates the deep power-down mode.In read modes, RP#-low deselects the memory, places output drivers in a high-impedance state and turns off all internal circuits. RP# must be held low for a minimum of 100ns. Time t PHQV is required after return from power-down until initial memory access outputs are valid. After this wake-up interval, normal operation is restored. The CUI is reset to read array mode and status register is set to 80H.During block erase or byte write modes, RP#-low will abort the operation. Memory contents being altered are no longer valid; the data may be partially erased or written. Time t PHWL is required after RP# goes to logic-high (V IH) before another command can be written.As with any automated device, it is important to assert RP# during system reset. When the system comes out of reset, it expects to read from the flash memory. Automated flash memories provide status information when accessed during block erase or byte write modes. If a CPU reset occurs with no flash memory reset, proper CPU initialization may not occur because the flash memory may be providing status information instead of array data. SHARP’s flash memories allow proper CPU initialization following a system reset through the use of the RP# input. In this application, RP# is controlled by the same RESET# signal that resets the system CPU.Rev. 1.1Rev. 1.1Table 3. Bus Operations(1,2)Mode Notes RP#CE#OE#WE#Address V PP DQ0-7 Read7V IH or V HH V IL V IL V IH X X D OUT Output Disable V IH or V HH V IL V IH V IH X X High Z Standby8V IH or V HH V IH X X X X High Z Deep Power-Down3,8V IL X X X X X High ZRead Identifier Codes7V IH or V HH V IL V IL V IHSeeFigure 4X Note 4Write5,6,7V IH or V HH V IL V IH V IL X X D IN NOTES:1.Refer to DC Characteristics. When V PP≤V PPLK, memory contents can be read, but not altered.2.X can be V IL or V IH for control pins and addresses, and V PPLK or V PPH1/2/3 for V PP. See DC Characteristics for V PPLKand V PPH1/2/3 voltages.3.RP# at GND±0.2V ensures the lowest deep power-down current.4.See Section 4.2 for read identifier code data.mand writes involving block erase or byte write are reliably executed when V PP=V PPH1/2/3 and V CC=2.7V-3.6V.Block erase or byte write with V IH<RP#<V HH produce spurious results and should not be attempted.6.Refer to Table 4 for valid D IN during a write operation.7.Never hold OE# low and WE# low at the same timing.8.WP# set to V IL or V IH.Table 4. Command Definitions(7)Bus Cycles First Bus Cycle Second Bus Cycle Command Req’d.Notes Oper(1)Addr(2)Data(3)Oper(1)Addr(2)Data(3) Read Array/Reset1Write X FFHRead Identifier Codes≥24Write X90H Read IA ID Read Status Register2Write X70H Read X SRD Clear Status Register1Write X50HBlock Erase25Write BA20H Write BA D0HByte Write25,6Write WA 40H or10HWrite WA WDBlock Erase and Byte WriteSuspend15Write X B0HBlock Erase and Byte WriteResume15Write X D0HNOTES:1.BUS operations are defined in Table 3.2.X=Any valid address within the device.IA=Identifier Code Address: see Figure 4.BA=Address within the block being erased. The each block can select by the address pin A19 through A13 combination.WA=Address of memory location to be written.3.SRD=Data read from status register. See Table 7 for a description of the status register bits.WD=Data to be written at location WA. Data is latched on the rising edge of WE# or CE# (whichever goes high first).ID=Data read from identifier codes.4.Following the Read Identifier Codes command, read operations access manufacturer and device codes. See Section 4.2 forread identifier code data.5.If the block is boot block, WP# must be at V IH or RP# must be at V HH to enable block erase or byte write operations.Attempts to issue a block erase or byte write to a boot block while WP# is V IH or RP# is V IH.6.Either 40H or 10H are recognized by the WSM as the byte write setup.mands other than those shown above are reserved by SHARP for future device implementations and should not beused.4.1 Read Array CommandUpon initial device power-up and after exit from deep power-down mode, the device defaults to read array mode. This operation is also initiated by writing the Read Array command. The device remains enabled for reads until another command is written. Once the internal WSM has started a block erase or byte write, the device will not recognize the Read Array command until the WSM completes its operation unless the WSM is suspended via an Erase Suspend or Byte Write Suspend command. The Read Array command functions independently of the V PP voltage and RP# can be V IH or V HH.4.2 Read Identifier Codes CommandThe identifier code operation is initiated by writing the Read Identifier Codes command. Following the command write, read cycles from addresses shown in Figure 4 retrieve the manufacturer and device codes (see Table 5 for identifier code values). To terminate the operation, write another valid command. Like the Read Array command, the Read Identifier Codes command functions independently of the V PP voltage and RP# can be V IH or V HH. Following the Read Identifier Codes command, the following information can be read:Table 5. Identifier CodesCode Address[A19-A0]Data[DQ7-DQ0]Manufacture Code00000H B0H Device Code00001H4BH4.3 Read Status Register CommandThe status register may be read to determine when a block erase or byte write is complete and whether the operation completed successfully. It may be read at any time by writing the Read Status Register command. After writing this command, all subsequent read operations output data from the status register until another valid command is written. The status register contents are latched on the falling edge of OE# or CE#, whichever occurs. OE# or CE# must toggle to V IH before further reads to update the status register latch. The Read Status Register command functions independently of the V PP voltage. RP# can be V IH or V HH.4.4 Clear Status Register CommandStatus register bits SR.5, SR.4, SR.3 or SR.1 are set to "1"s by the WSM and can only be reset by the Clear Status Register command. These bits indicate various failure conditions (see Table 7). By allowing system software to reset these bits, several operations (such as cumulatively erasing multiple blocks or writing several bytes in sequence) may be performed. The status register may be polled to determine if an error occurred during the sequence.To clear the status register, the Clear Status Register command (50H) is written. It functions independently of the applied V PP Voltage. RP# can be V IH or V HH. This command is not functional during block erase or byte write suspend modes.4.5 Block Erase CommandErase is executed one block at a time and initiated by a two-cycle command. A block erase setup is first written, followed by an block erase confirm. This command sequence requires appropriate sequencing and an address within the block to be erased (erase changes all block data to FFH). Block preconditioning, erase, and verify are handled internally by the WSM (invisible to the system). After the two-cycle block erase sequence is written, the device automatically outputs status register data when read (see Figure 5). The CPU can detect block erase completion by analyzing the output data of the status register bit SR.7. When the block erase is complete, status register bit SR.5 should be checked. If a block erase error is detected, the status register should be cleared before system software attempts corrective actions. The CUI remains in read status register mode until a new command is issued.This two-step command sequence of set-up followed by execution ensures that block contents are not accidentally erased. An invalid Block Erase command sequence will result in both status register bits SR.4 and SR.5 being set to "1". Also, reliable block erasure can only occur when V CC=2.7V-3.6V and V PP=V PPH1/2/3. In the absence of this high voltage, block contents are protected against erasure. If block erase is attempted while V PP≤V PPLK, SR.3 and SR.5 will be set to "1". Successful block erase for boot blocks requires that the corresponding if set, that WP#=V IH or RP#=V HH. If block erase is attempted to boot block when the corresponding WP#=V IL or RP#=V IH, SR.1 and SR.5 will be set to "1". Block erase operations with V IH<RP#<V HH produce spurious results and should not be attempted.4.6 Byte Write CommandByte write is executed by a two-cycle command sequence. Byte write setup (standard 40H or alternate 10H) is written, followed by a second write that specifies the address and data (latched on the rising edge of WE#). The WSM then takes over, controlling the byte write and write verify algorithms internally. After the byte write sequence is written, the device automatically outputs status register data when read (see Figure 6). The CPU can detect the completion of the byte write event by analyzing the status register bit SR.7.When byte write is complete, status register bit SR.4 should be checked. If byte write error is detected, the status register should be cleared. The internal WSM verify only detects errors for "1"s that do not successfully write to "0"s. The CUI remains in read status register mode until it receives another command.Reliable byte writes can only occur when V CC=2.7V-3.6V and V PP=V PPH1/2/3. In the absence of this high voltage, memory contents are protected against byte writes. If byte write is attempted while V PP≤V PPLK, status register bits SR.3 and SR.4 will be set to "1". Successful byte write for boot blocks requires that the corresponding if set, that WP#=V IH or RP#=V HH. If byte write is attempted to boot block when the corresponding WP#=V IL or RP#=V IH, SR.1 and SR.4 will be set to "1". Byte write operations with V IH<RP#<V HH produce spurious results and should not be attempted.4.7 Block Erase Suspend CommandThe Block Erase Suspend command allows block-erase interruption to read or byte write data in another block of memory. Once the block-erase process starts, writing the Block Erase Suspend command requests that the WSM suspend the block erase sequence at a predetermined point in the algorithm. The device outputs status register data when read after the Block Erase Suspend command is written. Polling status register bits SR.7 and SR.6 can determine when the block erase operation has been suspended (both will be set to "1"). Specification section 6.2.8 defines the block erase suspend latency.At this point, a Read Array command can be written to read data from blocks other than that which is suspended.A Byte Write command sequence can also be issued during erase suspend to program data in other blocks. Using the Byte Write Suspend command (see Section 4.8), a byte write operation can also be suspended. During a byte write operation with block erase suspended, status register bit SR.7 will return to "0". However, SR.6 will remain "1" to indicate block erase suspend status.The only other valid commands while block erase is suspended are Read Status Register and Block Erase Resume. After a Block Erase Resume command is written to the flash memory, the WSM will continue the block erase process. Status register bits SR.6 and SR.7 will automatically clear. After the Erase Resume command is written, the device automatically outputs status register data when read (see Figure 7). V PP must remain at V PPH1/2/3 (the same V PP level used for block erase) while block erase is suspended. RP# must also remain at V IH or V HH (the same RP# level used for block erase). WP# must also remain at V IL or V IH (the same WP# level used for block erase). Block erase cannot resume until byte write operations initiated during block erase suspend have completed.。

丹佛斯变频器 FC101_样本_中文_V1

X

无显示面板

主 电源3×2 0 0 - 2 4 0 V A C

型号 FC101PK25 FC101PK37 FC101PK75 FC101P1K5 FC101P2K2 FC101P3K7 FC101P5K5 FC101P7K5 FC101P11K

HVAC Drive

现今,生产交流变频器的厂商枚不胜 举--然而VLT®品牌却只此一家!

1968年 , 丹佛 斯 首先 将 变频 调 速器 投 入批量生产,即时创立了VLT®品牌。

自 此 , VLT®便 成 为变 频 器质 量 精 益 求 精的代名词。

·我们是世界上公认的提供高质 量,优质服务以及高性价比产品 的变频器生产商。

AC-1:250VAC,3A;AC-15:250VAC, 0.2ADC-1:30VDC,2A;DC-13:24VDC,0.1A

最大端子负载(01-0 3)

AC-1:250VAC,3A;AC-15:250VAC, 0.2ADC-1:30VDC,2A;

控制卡,RS485串行通讯 端子号 端子号

68(P,T X+,RX+),69(N,TX-,RX-) 61,端子68、69的公 用端

控 制 卡,2 4V直 流 输出 端子号 最大负载

12 80mA

现场总线通信 FLN ApogeeModbusRTU

标准内置:FC协议 N2 Metasys BACnet mstp

环境 防护等级 振动测试 最高相对湿度 环境温度

IP20/IP21/IP54 1.0g 5-95%(IEC 60721-3-3;工作环境中为3K3类(无冷凝) 45℃

电机电流

电机电压

自动负荷调节

标配的自动能量优化功能可在所有转速及负荷条件下优化电机的磁化特性,从而在调速控制基础上进一步实现节能 4

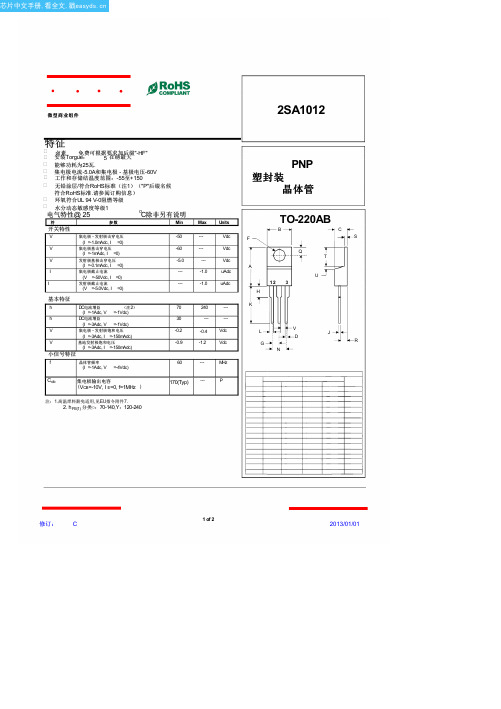

2SA1012-BP中文资料(Micro Commercial)中文数据手册「EasyDatasheet - 矽搜」

I

集电极截止电流

---

(V =-50Vdc, I =0)

I

发射极截止电流

---

(V =-5.0Vdc, I =0)

基本特征

h

DC电流增益

(注2)

70

(I =-1Adc, V =-1Vdc)

h

DC电流增益

30

(I =-3Adc, V =-1Vdc)

V

集电极 - 发射极饱和电压

-0.2

(I =-3Adc, I =-150mAdc)

V

基地发射极饱和电压

-0.9

(I =-3Adc, I =-150mAdc)

小信号特征

f

晶体管频率

60

(I =-1Adc, V =-4Vdc)

Cob

集电极输出电容

(VCB=-10V, I E=0, f=1MHz )

170(Typ)

Max -------1.0 -1.0

240 ---

-0.4 -1.2

---

***生命防护障 ***

未经明确书面MCC产品不得用于生命支持设备或系统关键组件 审批微型商业组件公司.

***客户意识 ***

半导体零部件假冒是在行业内日益严重问题.微型商业组件(MCC)正在

强有力措施防护护我们自己和我们客户从假冒伪劣配件泛滥.中冶大力鼓励

客户可以直接从MCC或谁是对上市由国家授权MCC分销商购买MCC件

1 of 2

2013/01/01

芯片中文手册,看全文,戳

微型商业组件

订购信息 :

器

型号- BP

Note : Adding "-HF" suffix for halogen free, eg. Part Number-BP-HF

XKD10120资料

Cautions : * Semiconductor relays don't provide any galvanic insulation between the load and the mains. * On inductive load put a free-wheeling diode (or clamp). * In case of many SSRs side by side, take a derating current in to account.

celduc

r e l a i s

Rue Ampère B.P. 4 42290 SORBIERS - FRANCE E-Mail : celduc-relais@ Fax +33 (0) 4 77 53 85 51 Service Commercial France Tél. : +33 (0) 4 77 53 90 20 Sales Dept.For Europe Tel. : +33 (0) 4 77 53 90 21 Sales Dept. Asia : Tél. +33 (0) 4 77 53 90 19

2500 8 30 12,2

2500 8 30 12,2

2500 8 30 12,2

2500 8 30 17,2

Proud to serve you

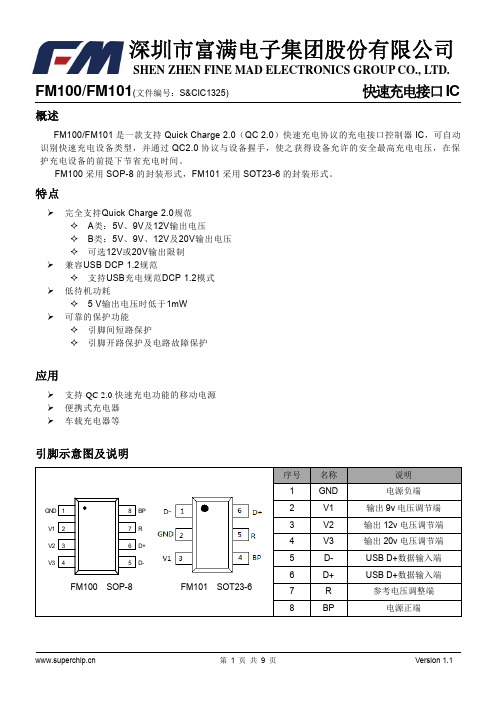

富满电子集团FM100 FM101快速充电接口IC说明书

FM100/FM101(文件编号:S&CIC1325)快速充电接口IC概述FM100/FM101是一款支持Quick Charge2.0(QC2.0)快速充电协议的充电接口控制器IC,可自动识别快速充电设备类型,并通过QC2.0协议与设备握手,使之获得设备允许的安全最高充电电压,在保护充电设备的前提下节省充电时间。

FM100采用SOP-8的封装形式,FM101采用SOT23-6的封装形式。

特点完全支持Quick Charge2.0规范✧A类:5V、9V及12V输出电压✧B类:5V、9V、12V及20V输出电压✧可选12V或20V输出限制兼容USB DCP1.2规范✧支持USB充电规范DCP1.2模式低待机功耗✧5V输出电压时低于1mW可靠的保护功能✧引脚间短路保护FM100/FM101(文件编号:S&CIC1325)快速充电接口IC 绝对最大额定值旁路引脚电压........................................................................................................................................-0.3to9V 参考引脚电压........................................................................................................................................-0.3to9V V1/V2/V3引脚电压................................................................................................................................-0.3to9V D+/D-引脚电压......................................................................................................................................-0.3to5V 旁路引脚电流..............................................................................................................................................25mA V1/V2/V3引脚电流....................................................................................................................................0.5mA D+/D引脚电流................................................................................................................................................1mA 工作结温.........................................................................................................................................-40°C to+150工作环境温度..............................................................................................................................-10°C to105°C 存储温度.....................................................................................................................................-65°C to150°C 焊接温度......................................................................................................................................………..260°C电气参数FM100/FM101(文件编号:S&CIC1325)快速充电接口IC 功能描述FM100/FM101是一种低成本的HVDCP专用充电端口控制芯片,支持QC2.0规范,支持PI如TOPSwitch和TinySwitch系列电源管理芯片。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

NOTE: MMBD101LT1 is also available in bulk packaging. Use MMBD101L as the device title to order this device in bulk.

Preferred devices are Motorola recommended choices for future use and best overall value.

Figure 1. Reverse Leakage

Figure 2. Forward Voltage

1.0

11 10 NF, NOISE FIGURE (dB) LOCAL OSCILLATOR FREQUENCY = 1.0 GHz (TEST CIRCUIT IN FIGURE 5)

C, CAPACITANCE (pF)

UHF NOISE SOURCE H.P. 349A

DIODE IN TUNED MOUNT

NOISE FIGURE METER H.P. 342A

IF AMPLIFIER NF = 1.5 dB f = 30 MHz

Figure 5. Noise Figure Test Circuit

2

Motorola Small–Signal Transistors, FETs and Diodes Device Data

SOLDERING PRECAUTIONS

The melting temperature of solder is higher than the rated temperature of the device. When the entire device is heated to a high temperature, failure to complete soldering within a short time could result in device failure. Therefore, the following items should always be observed in order to minimize the thermal stress to which the devices are subjected. • Always preheat the device. • The delta temperature between the preheat and soldering should be 100°C or less.* • When preheating and soldering, the temperature of the leads and the case must not exceed the maximum temperature ratings as shown on the data sheet. When using infrared heating with the reflow soldering method, the difference shall be a maximum of 10°C. • The soldering temperature and time shall not exceed 260°C for more than 10 seconds. • When shifting from preheating to soldering, the maximum temperature gradient shall be 5°C or less. • After soldering has been completed, the device should be allowed to cool naturally for at least three minutes. Gradual cooling should be used as the use of forced cooling will increase the temperature gradient and result in latent failure due to mechanical stress. • Mechanical stress or shock should not be applied during cooling. * Soldering a device without preheating can cause excessive thermal shock and stress which can result in damage to the device.

元器件交易网

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

Order this document by MBD101/D

Schottky Barrier Diodes

• Low Noise Figure — 6.0 dB Typ @ 1.0 GHz

0.037 0.95

0.037 0.95

0.079 2.0 0.035 0.9 0.031 0.8

inches mm

SOT–23 SOT–23 POWER DISSIPATION

The power dissipation of the SOT–23 is a function of the drain pad size. This can vary from the minimum pad size for soldering to a pad size given for maximum power dissipation. Power dissipation for a surface mount device is determined by TJ(max), the maximum rated junction temperature of the die, RθJA, the thermal resistance from the device junction to ambient, and the operating temperature, TA . Using the values provided on the data sheet for the SOT–23 package, PD can be calculated as follows: PD = TJ(max) – TA RθJA

MBD101 Rating Reverse Voltage Forward Power Dissipation @ TA = 25°C Derate above 25°C Junction Temperature Storage Temperature Range Symbol VR PF 280 2.2 TJ Tstg +150 – 55 to +150 225 1.8 mW mW/°C °C °C MMBD101LT1 Value 7.0 Unit Volts CASE 318 – 08, STYLE 8 SOT– 23 (TO – 236AB)

Thermal Clad is a registered trademark of the Berquist Company.

Motorola Small–Signal Transistors, FETs and Diodes Device Data © Motorola, Inc. 1997

1

元器件交易网 MBD101 MMBD101LT1

Figure 4. Noise Figure

LOCAL OSCILLATOR

NOTES ON TESTING AND SPECIFICATIONS Note 1 — CC and CT are measured using a capacitance bridge (Boonton Electronics Model 75A or equivalent). Note 2 — Noise figure measured with diode under test in tuned diode mount using UHF noise source and local oscillator (LO) frequency of 1.0 GHz. The LO power is adjusted for 1.0 mW. IF amplifier NF = 1.5 dB, f = 30 MHz, see Figure 5. Note 3 — LS is measured on a package having a short instead of a die, using an impedance bridge (Boonton Radio Model 250A RX Meter).

Surface mount board layout is a critical portion of the total design. The footprint for the semiconductor packages must be the correct size to insure proper solder connection interface between the board and the package. With the correct pad geometry, the packages will self align when subjected to a solder reflow process.

元器件交易网

MBD101 MMBD101LT1

INFORMATION FOR USING THE SOT–23 SURFACE MOUNT PACKAGE

MINIMUM RECOMMENDED FOOTPRINT FOR SURFACE MOUNTED APPLICATIONS

TYPICAL CHARACTERISTICS