CY7C1412AV18中文资料

EP1C12F144C7中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

EP1C6

5,980 20

92,160 2

185

EP1C12

12,060 52

239,616 2

249

EP1C20 20,060

64 294,912

2 301

1

芯片中文手册,看全文,戳

气旋 FPGA系列数据手册

初稿信息

Cyclone器件在四方扁平封装(QFP),并提供节省空间

FineLine BGA 包(见

Cyclone器件提供一个全局时钟网络和多达两个PLL.全局时钟网络由八 个全局时钟线驱动整个器件.全局时钟网络可以为设备内所有资源 ,如IOEs,LE和存储器块提供时钟.

全局时钟线也可用于控制信号.旋风PLL提供通用与时钟倍频和移相,以 及外部输出高速差分I / O支持时钟.

图1

示出旋风EP1C12装置图.

M4K RAM块与4K位内存加上平价(4,608位)真正双端口存储器 块.这些块宽高达200 MHz提供专用真正双端口,简单双端口或单端 口内存最高可达36位.这些块加在器件分成列在一定LAB之间. Cyclone器件提供嵌入式RAM 60至288千位之间.

每个Cyclone器件I / O引脚由I / O单元(IOE)位于输送 围绕装置外周端部LAB行和列. I / O 引脚支持各种单端和差分I / O标准,如 66 MHz32位PCI标准,并在到LVDS I / O标准 311 Mbps.每个IOE包含一个双向I / O缓冲区和三个寄存器 用于登记输入,输出和输出使能信号.两用 DQS,DQ和DM引脚以及延时链(用于相位对齐DDR 信号)提供与外部存储器设备,诸如接口支持 DDR SDRAM和高达133兆赫(266 Mbps)FCRAM器件.

配置设备配置Cyclone器件.

C系列斜齿轮减速机

C系列斜齿轮减速机

产品简介

斜齿轮减速机,具有体积小,传递扭矩大、效率高、工作平稳、寿命长,所配电机功率范围广,传动比分级精细等特点,该样本中只列出了4极Y系列电机直联的参数和外形安装尺寸,若需要低于该样本中所列的输出转速,我们会给您提供配6极、8极电机的直联产品,或级成两级斜齿轮减速机,达到更大的速比。

请与生产厂家咨询。

C系列斜齿轮减速机安装型式

产品代号

C

C系列斜齿轮减速机选型表(0.25kW)

C系列斜齿轮减速机选型表(0.37kW)

C系列斜齿轮减速机选型表(0.55kW)

C系列斜齿轮减速机选型表(0.75kW)

C系列斜齿轮减速机选型表(1.1kW)

C系列斜齿轮减速机选型表(1.5kW)

C系列斜齿轮减速机选型表(2.2kW)

C系列斜齿轮减速机选型表(3kW)

C系列斜齿轮减速机选型表(4kW)

C系列斜齿轮减速机选型表(5.5kW)

C系列斜齿轮减速机选型表(7.5kW)

C系列斜齿轮减速机选型表(11kW)

C系列斜齿轮减速机选型表(15kW)

C系列斜齿轮减速机选型表(18.5kW)

Y系列4极电机尺寸表

C底脚安装斜齿轮减速机安装尺寸

CF法兰安装斜齿轮减速机安装尺寸。

CY7C68013A中文资料

EZ-USB FX2LP™ USB MicrocontrollerCY7C68013A/CY7C68014A CY7C68015A/CY7C68016A1.0Features (CY7C68013A/14A/15A/16A)•USB 2.0–USB-IF high speed certified (TID # 40440111)•Single-chip integrated USB 2.0 transceiver, smart SIE, and enhanced 8051 microprocessor•Fit, form and function compatible with the FX2—Pin-compatible—Object-code-compatible—Functionally-compatible (FX2LP is a superset)•Ultra Low power: I CC no more than 85 mA in any mode —Ideal for bus and battery powered applications •Software: 8051 code runs from:—Internal RAM, which is downloaded via USB —Internal RAM, which is loaded from EEPROM —External memory device (128 pin package)•16 KBytes of on-chip Code/Data RAM•Four programmable BULK/INTERRUPT/ISOCHRO-NOUS endpoints—Buffering options: double, triple, and quad•Additional programmable (BULK/INTERRUPT) 64-byte endpoint•8- or 16-bit external data interface •Smart Media Standard ECC generation •GPIF (General Programmable Interface)—Allows direct connection to most parallel interface—Programmable waveform descriptors and configu-ration registers to define waveforms—Supports multiple Ready (RDY) inputs and Control (CTL) outputs•Integrated, industry-standard enhanced 8051—48-MHz, 24-MHz, or 12-MHz CPU operation —Four clocks per instruction cycle —Two USARTS—Three counter/timers—Expanded interrupt system —Two data pointers•3.3V operation with 5V tolerant inputs•Vectored USB interrupts and GPIF/FIFO interrupts •Separate data buffers for the Set-up and Data portions of a CONTROL transfer•Integrated I 2C controller, runs at 100 or 400 kHz •Four integrated FIFOs—Integrated glue logic and FIFOs lower system cost —Automatic conversion to and from 16-bit buses —Master or slave operation—Uses external clock or asynchronous strobes —Easy interface to ASIC and DSP ICs•Available in Commercial and Industrial temperature grade (all packages except VFBGA)A d d r e s s (16)x20PLL/0.5/1.0/2.08051 Core 12/24/48 MHz,four clocks/cycleI 2CVCC1.5kD+D–A d d r e s s (16) / D a t aB u s (8)FX2LPGPIFCY Smart USB 1.1/2.0EngineUSB 2.0XCVR16 KB RAM4 kB FIFOIntegrated full- and high-speedXCVRAdditional I/Os (24)ADDR (9)CTL (6)RDY (6)8/16D a t a (8)24 MHz Ext. XTALEnhanced USB core Simplifies 8051 code “Soft Configuration”Easy firmware changes FIFO and endpoint memory (master or slave operation)Up to 96 MBytes/s burst rateGeneralprogrammable I/F to ASIC/DSP or bus standards such as ATAPI, EPP , etc.Abundant I/Oincluding two USARTS High-performance micro using standard toolswith lower-power optionsMasterFigure 1-1. Block Diagramconnected for full speedECC1.1Features (CY7C68013A/14A only)•CY7C68014A: Ideal for battery powered applications —Suspend current: 100 µA (typ)•CY7C68013A: Ideal for non-battery powered applica-tions—Suspend current: 300 µA (typ)•Available in five lead-free packages with up to 40 GPIOs —128-pin TQFP (40 GPIOs), 100-pin TQFP (40 GPIOs),56-pin QFN (24 GPIOs), 56-pin SSOP (24 GPIOs), and 56-pin VFBGA (24 GPIOs)1.2Features (CY7C68015A/16A only)•CY7C68016A: Ideal for battery powered applications—Suspend current: 100 µA (typ)•CY7C68015A: Ideal for non-battery powered applica-tions—Suspend current: 300 µA (typ)•Available in lead-free 56-pin QFN package (26 GPIOs)—2 more GPIOs than CY7C68013A/14A enabling addi-tional features in same footprintCypress Semiconductor Corporation’s (Cypress’s) EZ-USB FX2LP™ (CY7C68013A/14A) is a low-power version of the EZ-USB FX2™ (CY7C68013), which is a highly integrated, low-power USB 2.0 microcontroller. By integrating the USB 2.0 transceiver, serial interface engine (SIE), enhanced 8051 microcontroller, and a programmable peripheral interface in a single chip, Cypress has created a very cost-effective solution that provides superior time-to-market advantages with low power to enable bus powered applications.The ingenious architecture of FX2LP results in data transfer rates of over 53 Mbytes per second, the maximum-allowable USB 2.0 bandwidth, while still using a low-cost 8051 microcon-troller in a package as small as a 56 VFBGA (5mm x 5mm). Because it incorporates the USB 2.0 transceiver, the FX2LP is more economical, providing a smaller footprint solution than USB 2.0 SIE or external transceiver implementations. With EZ-USB FX2LP, the Cypress Smart SIE handles most of the USB 1.1 and 2.0 protocol in hardware, freeing the embedded microcontroller for application-specific functions and decreasing development time to ensure USB compatibility. The General Programmable Interface (GPIF) and Master/Slave Endpoint FIFO (8- or 16-bit data bus) provides an easy and glueless interface to popular interfaces such as ATA, UTOPIA, EPP, PCMCIA, and most DSP/processors. The FX2LP draws considerably less current than the FX2 (CY7C68013), has double the on-chip code/data RAM and is fit, form and function compatible with the 56-, 100-, and 128-pin FX2.Five packages are defined for the family: 56VFBGA, 56 SSOP, 56 QFN, 100 TQFP, and 128 TQFP.2.0 Applications•Portable video recorder•MPEG/TV conversion•DSL modems•ATA interface•Memory card readers•Legacy conversion devices•Cameras•Scanners•Home PNA•Wireless LAN•MP3 players•NetworkingThe “Reference Designs” section of the Cypress web site provides additional tools for typical USB 2.0 applications. Each reference design comes complete with firmware source and object code, schematics, and documentation. Please visit for more information.3.0Functional Overview3.1USB Signaling SpeedFX2LP operates at two of the three rates defined in the USB Specification Revision 2.0, dated April 27, 2000:•Full speed, with a signaling bit rate of 12 Mbps •High speed, with a signaling bit rate of 480 Mbps.FX2LP does not support the low-speed signaling mode of 1.5Mbps.3.28051 MicroprocessorThe 8051 microprocessor embedded in the FX2LP family has 256 bytes of register RAM, an expanded interrupt system,three timer/counters, and two USARTs.3.2.18051 Clock FrequencyFX2LP has an on-chip oscillator circuit that uses an external 24-MHz (±100-ppm) crystal with the following characteristics:•Parallel resonant •Fundamental mode •500-µW drive level•12-pF (5% tolerance) load capacitors.An on-chip PLL multiplies the 24-MHz oscillator up to 480MHz, as required by the transceiver/PHY , and internal counters divide it down for use as the 8051 clock. The default 8051 clock frequency is 12 MHz. The clock frequency of the 8051 can be changed by the 8051 through the CPUCS register, dynamically.The CLKOUT pin, which can be three-stated and inverted using internal control bits, outputs the 50% duty cycle 8051clock, at the selected 8051 clock frequency—48, 24, or 12MHz.3.2.2USARTSFX2LP contains two standard 8051 USARTs, addressed via Special Function Register (SFR) bits. The USART interface pins are available on separate I/O pins, and are not multi-plexed with port pins.UART0 and UART1 can operate using an internal clock at 230KBaud with no more than 1% baud rate error. 230-KBaud operation is achieved by an internally derived clock source that generates overflow pulses at the appropriate time. The internal clock adjusts for the 8051 clock rate (48, 24, 12 MHz)such that it always presents the correct frequency for 230-KBaud operation.[1]3.2.3Special Function RegistersCertain 8051 SFR addresses are populated to provide fast access to critical FX2LP functions. These SFR additions are shown in Table 3-1. Bold type indicates non-standard,enhanced 8051 registers. The two SFR rows that end with “0”and “8” contain bit-addressable registers. The four I/O ports A–D use the SFR addresses used in the standard 8051 for ports 0–3, which are not implemented in FX2LP . Because of the faster and more efficient SFR addressing, the FX2LP I/O ports are not addressable in external RAM space (using the MOVX instruction).3.3I 2C BusFX2LP supports the I 2C bus as a master only at 100-/400-KHz.SCL and SDA pins have open-drain outputs and hysteresis inputs. These signals must be pulled up to 3.3V, even if no I 2C device is connected.3.4BusesAll packages: 8- or 16-bit “FIFO” bidirectional data bus, multi-plexed on I/O ports B and D. 128-pin package: adds 16-bit output-only 8051 address bus, 8-bit bidirectional data bus.Figure 3-1. Crystal Configuration12 pf12 pf24 MHz20 × PLLC1C212-pF capacitor values assumes a trace capacitanceof 3 pF per side on a four-layer FR4 PCANote:1.115-KBaud operation is also possible by programming the 8051 SMOD0 or SMOD1 bits to a “1” for UART0 and/or UART1, respectively.3.5USB Boot MethodsDuring the power-up sequence, internal logic checks the I2C port for the connection of an EEPROM whose first byte is either 0xC0 or 0xC2. If found, it uses the VID/PID/DID values in the EEPROM in place of the internally stored values (0xC0), or it boot-loads the EEPROM contents into internal RAM (0xC2). If no EEPROM is detected, FX2LP enumerates using internally stored descriptors. The default ID values for FX2LP are VID/PID/DID (0x04B4, 0x8613, 0xAxxx where xxx = Chip revision).[2]3.6ReNumeration™Because the FX2LP’s configuration is soft, one chip can take on the identities of multiple distinct USB devices.When first plugged into USB, the FX2LP enumerates automat-ically and downloads firmware and USB descriptor tables over the USB cable. Next, the FX2LP enumerates again, this time as a device defined by the downloaded information. This patented two-step process, called ReNumeration™, happens instantly when the device is plugged in, with no hint that the initial download step has occurred.Two control bits in the USBCS (USB Control and Status) register control the ReNumeration process: DISCON and RENUM. To simulate a USB disconnect, the firmware sets DISCON to 1. To reconnect, the firmware clears DISCON to 0. Before reconnecting, the firmware sets or clears the RENUM bit to indicate whether the firmware or the Default USB Device will handle device requests over endpoint zero: if RENUM = 0, the Default USB Device will handle device requests; if RENUM = 1, the firmware will.3.7Bus-powered ApplicationsThe FX2LP fully supports bus-powered designs by enumer-ating with less than 100 mA as required by the USB 2.0 speci-fication.3.8Interrupt System3.8.1INT2 Interrupt Request and Enable RegistersFX2LP implements an autovector feature for INT2 and INT4. There are 27 INT2 (USB) vectors, and 14 INT4 (FIFO/GPIF) vectors. See EZ-USB Technical Reference Manual (TRM) for more details.3.8.2USB-Interrupt AutovectorsThe main USB interrupt is shared by 27 interrupt sources. To save the code and processing time that normally would be required to identify the individual USB interrupt source, the FX2LP provides a second level of interrupt vectoring, called Autovectoring. When a USB interrupt is asserted, the FX2LP pushes the program counter onto its stack then jumps to address 0x0043, where it expects to find a “jump” instruction to the USB Interrupt service routine.Table 3-1. Special Function Registersx8x9x Ax Bx Cx Dx Ex Fx 0IOA IOB IOC IOD SCON1PSW ACC B 1SP EXIF INT2CLR IOE SBUF12DPL0MPAGE INT4CLR OEA3DPH0OEB4DPL1OEC5DPH1OED6DPS OEE7PCON8TCON SCON0IE IP T2CON EICON EIE EIP 9TMOD SBUF0A TL0AUTOPTRH1EP2468STAT EP01STAT RCAP2LB TL1AUTOPTRL1EP24FIFOFLGS GPIFTRIG RCAP2HC TH0reserved EP68FIFOFLGS TL2D TH1AUTOPTRH2GPIFSGLDATH TH2E CKCON AUTOPTRL2GPIFSGLDATLXF reserved AUTOPTRSET-UP GPIFSGLDATLNOXTable 3-2. Default ID Values for FX2LPDefault VID/PID/DIDVendor ID0x04B4Cypress SemiconductorProduct ID0x8613EZ-USB FX2LPDevice release0xAnnn Depends on chip revision(nnn = chip revision where firstsilicon = 001)Note:2.The I2C bus SCL and SDA pins must be pulled up, even if an EEPROM is not connected. Otherwise this detection method does not work properly.The FX2LP jump instruction is encoded as follows.If Autovectoring is enabled (AV2EN = 1 in the INTSET-UP register), the FX2LP substitutes its INT2VEC byte. Therefore, if the high byte (“page”) of a jump-table address is preloaded at location 0x0044, the automatically-inserted INT2VEC byte at 0x0045 will direct the jump to the correct address out of the 27 addresses within the page.3.8.3FIFO/GPIF Interrupt (INT4)Just as the USB Interrupt is shared among 27 individual USB-interrupt sources, the FIFO/GPIF interrupt is shared among 14 individual FIFO/GPIF sources. The FIFO/GPIF Interrupt, like the USB Interrupt, can employ autovectoring. Table3-4 shows the priority and INT4VEC values for the 14 FIFO/GPIF interrupt sources.Table 3-3. INT2 USB InterruptsUSB INTERRUPT TABLE FOR INT2 Priority INT2VEC Value Source Notes1 00SUDAV Set-up Data Available2 04 SOF Start of Frame (or microframe)3 08SUTOK Set-up Token Received4 0C SUSPEND USB Suspend request5 10USB RESET Bus reset6 14HISPEED Enteredhigh speed operation7 18 EP0ACK FX2LP ACK’d the CONTROL Handshake8 1C reserved9 20 EP0-IN EP0-IN ready to be loaded with data10 24 EP0-OUT EP0-OUT has USB data11 28 EP1-IN EP1-IN ready to be loaded with data12 2C EP1-OUT EP1-OUT has USB data13 30 EP2 IN: buffer available. OUT: buffer has data14 34 EP4 IN: buffer available. OUT: buffer has data15 38 EP6 IN: buffer available. OUT: buffer has data16 3C EP8 IN: buffer available. OUT: buffer has data17 40 IBN IN-Bulk-NAK (any IN endpoint)18 44reserved19 48 EP0PING EP0 OUT was Pinged and it NAK’d20 4C EP1PING EP1 OUT was Pinged and it NAK’d21 50 EP2PING EP2 OUT was Pinged and it NAK’d22 54 EP4PING EP4 OUT was Pinged and it NAK’d23 58 EP6PING EP6 OUT was Pinged and it NAK’d24 5C EP8PING EP8 OUT was Pinged and it NAK’d25 60 ERRLIMIT Bus errors exceeded the programmed limit26 6427 68 reserved28 6C reserved29 70 EP2ISOERR ISO EP2 OUT PID sequence error30 74 EP4ISOERR ISO EP4 OUT PID sequence error31 78 EP6ISOERR ISO EP6 OUT PID sequence error32 7C EP8ISOERR ISO EP8 OUT PID sequence errorIf Autovectoring is enabled (AV4EN = 1 in the INTSET-UP register), the FX 2LP substitutes its INT4VEC byte. Therefore, if the high byte (“page”) of a jump-table address is preloaded at location 0x0054, the automatically-inserted INT4VEC byte at 0x0055 will direct the jump to the correct address out of the 14 addresses within the page. When the ISR occurs, the FX2LP pushes the program counter onto its stack then jumps to address 0x0053, where it expects to find a “jump” instruction to the ISR Interrupt service routine.3.9Reset and Wakeup3.9.1Reset PinThe input pin, RESET#, will reset the FX2LP when asserted. This pin has hysteresis and is active LOW. When a crystal is used with the CY7C680xxA the reset period must allow for the stabilization of the crystal and the PLL. This reset period should be approximately 5 ms after VCC has reached 3.0V. If the crystal input pin is driven by a clock signal the internal PLL stabilizes in 200 µs after VCC has reached 3.0V[3]. Figure3-2 shows a power-on reset condition and a reset applied during operation. A power-on reset is defined as the time reset is asserted while power is being applied to the circuit. A powered reset is defined to be when the FX2LP has previously been powered on and operating and the RESET# pin is asserted. Cypress provides an application note which describes and recommends power on reset implementation and can be found on the Cypress web site. For more information on reset imple-mentation for the FX2 family of products visit the .Table 3-4. Individual FIFO/GPIF Interrupt SourcesPriority INT4VEC Value Source Notes 180EP2PF Endpoint 2 Programmable Flag2 84 EP4PF Endpoint 4 Programmable Flag388EP6PF Endpoint 6 Programmable Flag48C EP8PF Endpoint 8 Programmable Flag590EP2EF Endpoint 2 Empty Flag694EP4EF Endpoint 4 Empty Flag798EP6EF Endpoint 6 Empty Flag89C EP8EF Endpoint 8 Empty Flag9A0 EP2FF Endpoint 2 Full Flag10A4EP4FF Endpoint 4 Full Flag11 A8EP6FF Endpoint 6 Full Flag12AC EP8FF Endpoint 8 Full Flag13 B0GPIFDONE GPIF Operation Complete14 B4GPIFWF GPIF WaveformNote:3.If the external clock is powered at the same time as the CY7C680xxA and has a stabilization wait period, it must be added to the 200 µs.3.9.2Wakeup PinsThe 8051 puts itself and the rest of the chip into a power-down mode by setting PCON.0 = 1. This stops the oscillator and PLL. When WAKEUP is asserted by external logic, the oscil-lator restarts, after the PLL stabilizes, and then the 8051receives a wakeup interrupt. This applies whether or not FX2LP is connected to the USB.The FX2LP exits the power-down (USB suspend) state using one of the following methods:•USB bus activity (if D+/D– lines are left floating, noise on these lines may indicate activity to the FX2LP and initiate a wakeup).•External logic asserts the WAKEUP pin •External logic asserts the PA3/WU2 pin.The second wakeup pin, WU2, can also be configured as a general purpose I/O pin. This allows a simple external R-C network to be used as a periodic wakeup source. Note that WAKEUP is by default active LOW.3.10Program/Data RAM3.10.1SizeThe FX2LP has 16 KBytes of internal program/data RAM,where PSEN#/RD# signals are internally ORed to allow the 8051 to access it as both program and data memory. No USB control registers appear in this space.Two memory maps are shown in the following diagrams:Figure 3-3 Internal Code Memory, EA = 0Figure 3-4 External Code Memory, EA = 1.3.10.2Internal Code Memory, EA = 0This mode implements the internal 16-KByte block of RAM (starting at 0) as combined code and data memory. When external RAM or ROM is added, the external read and write strobes are suppressed for memory spaces that exist inside the chip. This allows the user to connect a 64-KByte memory without requiring address decodes to keep clear of internal memory spaces.Only the internal 16 KBytes and scratch pad 0.5 KBytes RAM spaces have the following access:•USB download •USB upload •Set-up data pointer •I 2C interface boot load.3.10.3External Code Memory, EA = 1The bottom 16 KBytes of program memory is external, and therefore the bottom 16 KBytes of internal RAM is accessible only as data memory.Figure 3-2. Reset Timing PlotsV IL 0V3.3V 3.0VT RESETVCCRESET#Power on ResetT RESETVCCRESET#V IL Powered Reset3.3V0VTable 3-5. Reset Timing ValuesConditionT RESET Power-on Reset with crystal 5 msPower-on Reset with external clock200 µs + Clock stability timePowered Reset 200 µsFigure 3-3. Internal Code Memory, EA = 0Inside FX2LPOutside FX2LP7.5 KBytes USB regs and 4K FIFO buffers (RD#,WR#)0.5 KBytes RAM Data (RD#,WR#)*(OK to populate data memory here—RD#/WR#strobes are not active)40 KBytes External Data Memory (RD#,WR#)(Ok to populate data memory here—RD#/WR#strobes are not active)16 KBytes RAM Code and Data(PSEN#,RD#,WR#)*48 KBytes External Code Memory (PSEN#)(OK to populate programmemory here—PSEN# strobe is not active)*SUDPTR, USB upload/download, I 2C interface boot accessFFFFE200E1FF E0003FFF0000DataCodeFigure 3-4. External Code Memory, EA = 1Inside FX2LPOutside FX2LP7.5 KBytes USB regs and 4K FIFO buffers (RD#,WR#)0.5 KBytes RAM Data (RD#,WR#)*(OK to populatedata memory here—RD#/WR#strobes are not active)40 KBytes External Data Memory (RD#,WR#)(Ok to populate data memory here—RD#/WR#strobes are not active)16 KBytes RAM Data(RD#,WR#)*64 KBytes External Code Memory (PSEN#)*SUDPTR, USB upload/download, I 2C interface boot accessFFFFE200E1FFE0003FFF0000DataCode3.11Register Addresses3.12Endpoint RAM3.12.1Size•3× 64 bytes (Endpoints 0 and 1)•8 × 512 bytes (Endpoints 2, 4, 6, 8)3.12.2Organization•EP0•Bidirectional endpoint zero, 64-byte buffer •EP1IN, EP1OUT•64-byte buffers, bulk or interrupt •EP2,4,6,8•Eight 512-byte buffers, bulk, interrupt, or isochronous. EP4 and EP8 can be double buffered, while EP2 and 6 can be either double, triple, or quad buffered. For high-speed end-point configuration options, see Figure 3-5.3.12.3Set-up Data BufferA separate 8-byte buffer at 0xE6B8-0xE6BF holds the Set-up data from a CONTROL transfer.3.12.4Endpoint Configurations (High-speed Mode)Endpoints 0 and 1 are the same for every configuration.Endpoint 0 is the only CONTROL endpoint, and endpoint 1 can be either BULK or INTERRUPT. The endpoint buffers can be configured in any 1 of the 12 configurations shown in the vertical columns. When operating in full-speed BULK mode only the first 64 bytes of each buffer are used. For example in high-speed, the max packet size is 512 bytes but in full-speed it is 64 bytes. Even though a buffer is configured to be a 512byte buffer, in full-speed only the first 64 bytes are used. The unused endpoint buffer space is not available for other opera-tions. An example endpoint configuration would be:FFFFE800E7BF E740E73F E700E6FF E500E4FF E480E47F E400E200E1FFE000E3FF EFFF2 KBytes RESERVED64 Bytes EP0 IN/OUT 64 Bytes RESERVED 8051 Addressable RegistersReserved (128)128 bytes GPIF Waveforms512 bytes 8051 xdata RAMF000(512)Reserved (512)E78064 Bytes EP1OUT E77F 64 Bytes EP1IN E7FF E7C0 4 KBytes EP2-EP8buffers(8 x 512)EP2–1024 double buffered; EP6–512 quad buffered (column 8).3.12.5Default Full-Speed Alternate Settings3.12.6Default High-Speed Alternate Settings6464645125121024102410241024102410241024512512512512512512512512512512EP0 IN&OUTEP1 IN EP1 OUTFigure 3-5. Endpoint Configuration1024102410245125125125125125125125125125125125125125125125125125125125125125125125125125125125125125121024102410241024102410245125121024102451251251251251251251251210241024512512512512512512646464646464646464646464646464646464646464646464646464646464646464123456789101112Table 3-6. Default Full-Speed Alternate Settings [4, 5]Alternate Setting 0123ep064646464ep1out 064 bulk 64 int 64 int ep1in 064 bulk 64 int 64 int ep2064 bulk out (2×)64 int out (2×)64 iso out (2×)ep4064 bulk out (2×)64 bulk out (2×)64 bulk out (2×)ep6064 bulk in (2×)64 int in (2×)64 iso in (2×)ep8064 bulk in (2×)64 bulk in (2×)64 bulk in (2×)Notes:4.“0” means “not implemented.”5.“2×” means “double buffered.”6.Even though these buffers are 64 bytes, they are reported as 512 for USB 2.0 compliance. The user must never transfer packets larger than 64 bytes to EP1.Table 3-7. Default High-Speed Alternate Settings [4, 5]Alternate Setting 0123ep064646464ep1out 0512 bulk [6]64 int 64 int ep1in 0512 bulk [6]64 int64 intep20512 bulk out (2×)512 int out (2×)512 iso out (2×)ep40512 bulk out (2×)512 bulk out (2×)512 bulk out (2×)ep60512 bulk in (2×)512 int in (2×)512 iso in (2×)ep80512 bulk in (2×)512 bulk in (2×)512 bulk in (2×)3.13External FIFO Interface3.13.1ArchitectureThe FX2LP slave FIFO architecture has eight 512-byte blocks in the endpoint RAM that directly serve as FIFO memories, and are controlled by FIFO control signals (such as IFCLK, SLCS#, SLRD, SLWR, SLOE, PKTEND, and flags).In operation, some of the eight RAM blocks fill or empty from the SIE, while the others are connected to the I/O transfer logic. The transfer logic takes two forms, the GPIF for internally generated control signals, or the slave FIFO interface for externally controlled transfers.3.13.2Master/Slave Control SignalsThe FX2LP endpoint FIFOS are implemented as eight physi-cally distinct 256x16 RAM blocks. The 8051/SIE can switch any of the RAM blocks between two domains, the USB (SIE) domain and the 8051-I/O Unit domain. This switching is done virtually instantaneously, giving essentially zero transfer time between “USB FIFOS” and “Slave FIFOS.” Since they are physically the same memory, no bytes are actually transferred between buffers.At any given time, some RAM blocks are filling/emptying with USB data under SIE control, while other RAM blocks are available to the 8051 and/or the I/O control unit. The RAM blocks operate as single-port in the USB domain, and dual-port in the 8051-I/O domain. The blocks can be configured as single, double, triple, or quad buffered as previ-ously shown.The I/O control unit implements either an internal-master (M for master) or external-master (S for Slave) interface.In Master (M) mode, the GPIF internally controls FIFOADR[1..0] to select a FIFO. The RDY pins (two in the 56-pin package, six in the 100-pin and 128-pin packages) can be used as flag inputs from an external FIFO or other logic if desired. The GPIF can be run from either an internally derived clock or externally supplied clock (IFCLK), at a rate that transfers data up to 96 Megabytes/s (48-MHz IFCLK with 16-bit interface).In Slave (S) mode, the FX2LP accepts either an internally derived clock or externally supplied clock (IFCLK, max. frequency 48 MHz) and SLCS#, SLRD, SLWR, SLOE, PKTEND signals from external logic. When using an external IFCLK, the external clock must be present before switching to the external clock with the IFCLKSRC bit. Each endpoint can individually be selected for byte or word operation by an internal configuration bit, and a Slave FIFO Output Enable signal SLOE enables data of the selected width. External logic must insure that the output enable signal is inactive when writing data to a slave FIFO. The slave interface can also operate asynchronously, where the SLRD and SLWR signals act directly as strobes, rather than a clock qualifier as in synchronous mode. The signals SLRD, SLWR, SLOE and PKTEND are gated by the signal SLCS#.3.13.3GPIF and FIFO Clock RatesAn 8051 register bit selects one of two frequencies for the internally supplied interface clock: 30 MHz and 48 MHz. Alter-natively, an externally supplied clock of 5 MHz–48 MHz feeding the IFCLK pin can be used as the interface clock. IFCLK can be configured to function as an output clock when the GPIF and FIFOs are internally clocked. An output enable bit in the IFCONFIG register turns this clock output off, if desired. Another bit within the IFCONFIG register will invert the IFCLK signal whether internally or externally sourced. 3.14GPIFThe GPIF is a flexible 8- or 16-bit parallel interface driven by a user-programmable finite state machine. It allows the CY7C68013A/15A to perform local bus mastering, and can implement a wide variety of protocols such as ATA interface, printer parallel port, and Utopia.The GPIF has six programmable control outputs (CTL), nine address outputs (GPIFADRx), and six general-purpose ready inputs (RDY). The data bus width can be 8 or 16 bits. Each GPIF vector defines the state of the control outputs, and deter-mines what state a ready input (or multiple inputs) must be before proceeding. The GPIF vector can be programmed to advance a FIFO to the next data value, advance an address, etc. A sequence of the GPIF vectors make up a single waveform that will be executed to perform the desired data move between the FX2LP and the external device.3.14.1Six Control OUT SignalsThe 100- and 128-pin packages bring out all six Control Output pins (CTL0-CTL5). The 8051 programs the GPIF unit to define the CTL waveforms. The 56-pin package brings out three of these signals, CTL0–CTL2. CTLx waveform edges can be programmed to make transitions as fast as once per clock (20.8 ns using a 48-MHz clock).3.14.2Six Ready IN SignalsThe 100- and 128-pin packages bring out all six Ready inputs (RDY0–RDY5). The 8051 programs the GPIF unit to test the RDY pins for GPIF branching. The 56-pin package brings out two of these signals, RDY0–1.3.14.3Nine GPIF Address OUT SignalsNine GPIF address lines are available in the 100- and 128-pin packages, GPIFADR[8..0]. The GPIF address lines allow indexing through up to a 512-byte block of RAM. If more address lines are needed, I/O port pins can be used.3.14.4Long Transfer ModeIn master mode, the 8051 appropriately sets GPIF transaction count registers (GPIFTCB3, GPIFTCB2, GPIFTCB1, or GPIFTCB0) for unattended transfers of up to 232 transactions. The GPIF automatically throttles data flow to prevent under or overflow until the full number of requested transactions complete. The GPIF decrements the value in these registers to represent the current status of the transaction.。

USB控制芯片cy7c68013中文手册

■ 3.3V 工作电压,容限输入为 5V

■ 向量化 USB 中断和 GPIF/FIFO 中断

■ 16 K 字节片上代码/数据 RAM

■ 四个可编程的 BULK/INTERRUPT/ISOCHRONOUS 端点 ❐ 缓冲区大小选项:两倍,三倍,四倍

■ 附加的可编程 (BULK/INTERRUPT) 64 位端点

■ 8 位或 16 位外部数据接口

■ 可生成智能介质标准错误校正码 ECC

■ 通用可编程接口 (General Programmable Interface, GPIF) ❐ 可与大多数并行接口直接连接 ❐ 由可编程波形描述符和配置寄存器定义波形 ❐ 支持多个 Ready (RDY) 输入和 Control (CTL) 输出

4 KB8/16源自FIFO丰富的 I/O 接口包含 两个 USART

通用可编程 I/F 符合 ASIC/DSP 或 总线标准,例如 ATAPI、 EPP 等

高达 96 MB/s 突发速率

增强型 USB 核 简化 8051 代码

“软配置”容易 进行固件更换

FIFO 和端点存储器 (主控端或从属端操作)

1.1 特色 (仅限 CY7C68013A/14A)

片上 PLL 可根据收发器 /PHY 的需要将 24 MHz 振荡器倍频到 480 MHz,而内部计数器可将其分频以用作 8051 时钟。默认的 8051 时钟频率是 12 MHz。 8051 的时钟频率可以由 8051 通过 CPUCS 寄存器动态更改。

CY7C1470V33中文资料

WRITE DRIVERS

O

U

T

S E N

P U T

S

MEMORY

E

ARRAY A

M

P

S

R E G I S T E

R

S

E

O

U

T

D

P

A

U

T

T

A

B

S

U

T

F

E

F

E

E

R

R

I

S

N

G

E

INPUT REGISTER 1 E

INPUT REGISTER 0 E

DQs DQPa DQPb

OE CE1 CE2 CE3

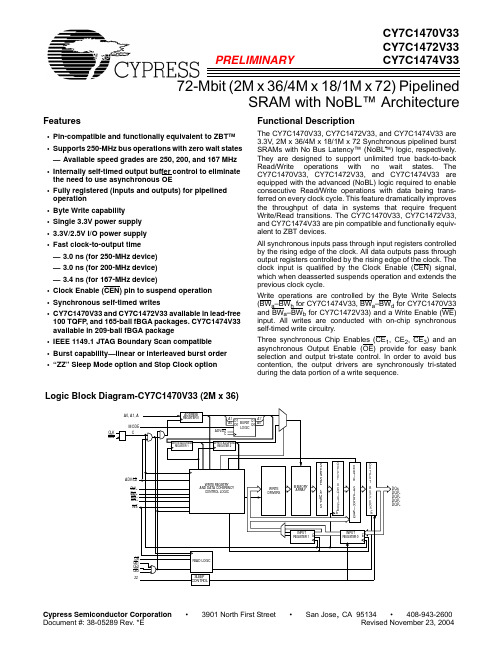

Functional Description

The CY7C1470V33, CY7C1472V33, and CY7C1474V33 are 3.3V, 2M x 36/4M x 18/1M x 72 Synchronous pipelined burst SRAMs with No Bus Latency™ (NoBL™) logic, respectively. They are designed to support unlimited true back-to-back Read/Write operations with no wait states. The CY7C1470V33, CY7C1472V33, and CY7C1474V33 are equipped with the advanced (NoBL) logic required to enable consecutive Read/Write operations with data being transferred on every clock cycle. This feature dramatically improves the throughput of data in systems that require frequent Write/Read transitions. The CY7C1470V33, CY7C1472V33, and CY7C1474V33 are pin compatible and functionally equivalent to ZBT devices.

CY7C1041CV33-10ZXI中文资料

Industrial

100

95

Automotive-A

100

Automotive-E

Commercial/

10

10

Industrial

Automotive-A

10

Automotive-E

48-ball FBGA

(Top View)

12

3

4

5

6

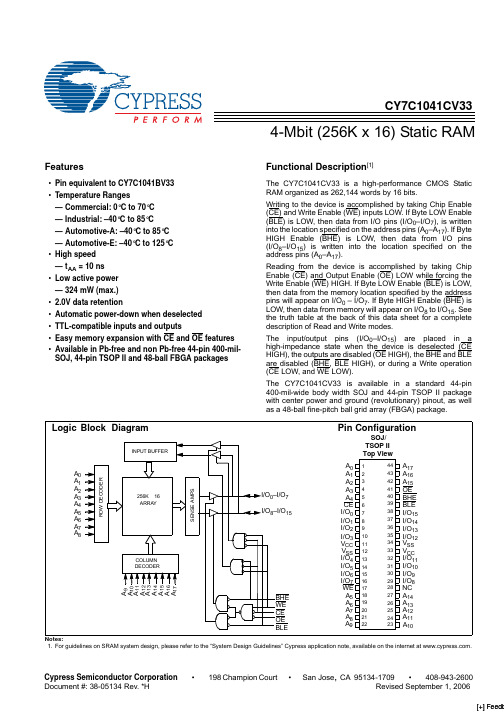

CY7C1041CV33

-15

-20

Unit

15

20

ns

80

28

A6, E3, G2, H1, No Connect No Connects. This pin is not connected to the die

H6

17

G5

Input/Control Write Enable Input, active LOW. When selected LOW, a

A5 18 A6 19 A7 20 A8 21 A9 22

44 A17 43 A16 42 A15 41 OE

40 BHE 39 BLE

38 I/O15 37 I/O14 36 I/O13 35 I/O12 34 VSS 33 VCC 32 I/O11 31 I/O10 30 I/O9 29 I/O8 28 NC

WRITE is conducted. When selected HIGH, a READ is

conducted.

6

ห้องสมุดไป่ตู้B5

Input/Control Chip Enable Input, active LOW. When LOW, selects the chip.

When HIGH, deselects the chip.

CY7C1387D-167BZXI中文资料

Q0

DQD,DQPD BYTE WRITE DRIVER DQc,DQPC BYTE WRITE DRIVER DQB,DQPB BYTE WRITE DRIVER DQA,DQPA BYTE WRITE DRIVER

MEMORY ARRAY SENSE AMPS

BWC

OUTPUT REGISTERS

Shaded areas contain advance information. Please contact your local Cypress sales representative for availability of these parts. Notes: 1. For best-practices recommendations, please refer to the Cypress application note System Design Guidelines on . 2. CE3 and CE2 are for TQFP and 165 fBGA package only. 119 BGA is offered only in Single Chip Enable.

CY7C1386D CY7C1387D

100 99 98 97 96 95 94 93 92 91 90 89 88 87 86 85 84 83 82 81

DQPC DQC DQC VDDQ VSSQ DQC DQC DQC DQC VSSQ VDDQ DQC DQC NC VDD NC VSS DQD DQD VDDQ VSSQ DQD DQD DQD DQD VSSQ VDDQ DQD DQD DQPD

Cypress Semiconductor Corporation Document #: 38-05545 Rev. *A

CY7C1411AV18资料

Errata Revision: *CMay 02, 2007RAM9 QDR-I/DDR-I/QDR-II/DDR- II ErrataCY7C129*DV18/CY7C130*DV25CY7C130*BV18/CY7C130*BV25/CY7C132*BV25CY7C131*BV18 / CY7C132*BV18/CY7C139*BV18CY7C191*BV18/CY7C141*AV18 / CY7C142*AV18/CY7C151*V18 /CY7C152*V18This document describes the DOFF issue for QDRII/DDRII and the Output Buffer and JTAG issues for QDRI/DDRI/QDRII/DDRII. Details include trigger conditions, possible workarounds and silicon revision applicability.This document should be used to compare to the respective datasheet for the devices to fully describe the device functionality.Please contact your local Cypress Sales Representative for availability of the fixed devices and any other questions.Devices AffectedTable 1. List of Affected devicesProduct StatusAll of the above densities and revisions are available in sample as well as production quantities.QDR/DDR DOFF Pin, Output Buffer and JTAG Issues Errata SummaryThe following table defines the issues and the fix status for the different devices which are affected.Density & Revision Part Numbers Architecture 9Mb - Ram9(90 nm)CY7C130*DV25QDRI/DDRI 9Mb - Ram9(90 nm)CY7C129*DV18QDRII 18Mb - Ram9(90nm)CY7C130*BV18CY7C130*BV25CY7C132*BV25QDRI/DDRI18Mb - Ram9(90nm)CY7C131*BV18CY7C132*BV18CY7C139*BV18CY7C191*BV18QDRII/DDRII36Mb - Ram9(90nm)CY7C141*AV18CY7C142*AV18QDRII/DDRII 72Mb -Ram9(90nm)CY7C151*V18CY7C152*V18QDRII/DDRIIItemIssueDeviceFix Status1.DOFF pin is used for enabling/dis-abling the DLL circuitry within the SRAM. To enable the DLL circuitry, DOFF pin must be externally tied HIGH. The QDR-II/DDR-II devices have an internal pull down resistor of ~5K . The value of the external pull-up resistor should be 500 or less in order to ensure DLL is enabled.9Mb - “D” Rev - Ram918Mb - “B” Rev - Ram936Mb - “A” Rev - Ram972Mb - Ram9QDR-II/DDR-II DevicesThe fix involved removing the in-ternal pull-down resistor on the DOFF pin. The fix has been im-plemented on the new revision and is now available.ΩΩTable 2.Issue Definition and fix status for different devices1. DOFF Pin Issue•ISSUE DEFINITIONThis issue involves the DLL not turning ON properly if a large resistor is used (eg:-10K ) as an external pullup resistor to enable the DLL. If a 10K or higher pullup resistor is used externally, the voltage on DOFF is not high enough to enable the DLL.•PARAMETERS AFFECTEDThe functionality of the device will be affected because of the DLL is not turning ON properly. When the DLL is enabled, all AC and DC parameters on the datasheet are met. •TRIGGER CONDITION(S)Having a 10K or higher external pullup resistor for disabling the DOFF pin.•SCOPE OF IMPACTThis issue will alter the normal functionality of the QDRII/DDRII devices when the DLL is disabled.•EXPLANATION OF ISSUEFigure 1 shows the DOFF pin circuit with an internal 5K internal resistor. The fix planned is to disable the internal 5K leaker.•WORKAROUND2.O/P Buffer enters a locked up unde-fined state after controls or clocks are left floating. No proper read/write access can be done on the device until a dummy read is performed.9Mb - “D” Rev - Ram918Mb - “B” Rev - Ram936Mb - “A” Rev - Ram972Mb - Ram9QDR-I/DDR-I/QDR-II/DDR-II Devices The fix has been implemented onthe new revision and is now avail-able.3.The EXTEST function in the JTAG test fails when input K clock is floating in the JTAG mode.9Mb - “D” Rev - Ram918Mb - “B” Rev - Ram936Mb - “A” Rev - Ram972Mb - Ram9QDR-I/DDR-I/QDR-II/DDR-II DevicesThe fix involved bypassing the ZQ circuitry in JTAG mode. This was done by overriding the ZQ circuit-ry by the JTAG signal. The fix has been implemented on the new re-vision and is now available.Figure 1.DOFF pin with the 5K internal resistorItemIssueDeviceFix StatusΩΩΩΩΩΩThe workaround is to have a low value of external pullup resistor for the DOFF pin (recommended value is <500). When DOFF pins from multiple QDR devices are connected through the same pull-up resistors on the board, it is recommended that this DOFF pin be directly connected to Vdd due to the lower effective resistance since the "leakers" are in parallel.Figure 2 shows the proposed workaround and the fix planned.•FIXSTATUSFix involved removing the internal pull-down resistor on the DOFF pin. The fix has been implemented on the new revision and is now available. The new revision is an increment of the existing revision. The following table lists the devices affected, current revision and the new revision after the fix.Table 3.List of Affected Devices and the new revison2.Output Buffer IssueFigure 2.Proposed workaround with the 500 external pullupCurrent Revision New Revision after the FixCY7C129*DV18CY7C129*EV18CY7C131*BV18CY7C131*CV18CY7C132*BV18CY7C132*CV18CY7C139*BV18CY7C139*CV18CY7C191*BV18CY7C191*CV18CY7C141*AV18CY7C141*BV18CY7C142*AV18CY7C142*BV18CY7C151*V18CY7C151*AV18CY7C152*V18CY7C152*AV18ΩΩ•ISSUE DEFINITIONThis issue involves the output buffer entering an unidentified state when the input signals (only Control signals or Clocks) are floating during reset or initialization of the memory controller after power up. •PARAMETERS AFFECTEDNo timing parameters are affected. The device may drive the outputs even though the read operation is not enabled. A dummy read is performed to clear this condition.•TRIGGER CONDITION(S)Input signals(namely RPS# for QDR-I/QDRII , WE# and LD# for DDR-I/DDRII) or Clocks (K/K# and/or C/C#) are floating during reset or initialization of the memory controller after power up.•SCOPE OF IMPACTThis issue will jeopardize any number of writes or reads which take place after the controls or clock are left floating. This can occur anywhere in the SRAM access ( all the way from power up of the memory device to transitions taking place for read/write accesses to the memory device) if the above trigger conditions are met.•EXPLANATION OF ISSUEFigure 3 shows the output register Reset circuit with an SR Latch circled. This latch has two inputs with one of them coming from some logic affected by the clock and RPS#(QDR) or WE# and LD#(DDR).The issue happens when clocks are glitching/toggling with controls floating. This will cause the SR latch to be taken into an unidentified state. The SR Latch will need to be reset by a dummy read operation if this happens. Array•WORKAROUNDThis is viable only if the customer has the trigger conditions met during reset or initialization of the memory controller after power up. In order for the workaround to perform properly, Cypress recommends the insertion of a minimum of 16 “dummy” READ operations to every SRAM device on the board prior to writing any meaningful data into the SRAM. After this one “dummy” READ operation, the device will perform properly.“Dummy” READ is defined as a read operation to the device that is not meant to retrieve required data. The “dummy” READ can be to any address location in the SRAM. Refer to Figure 4 for the dummy read implemen-tation.In systems where multiple SRAMs with multiple RPS# lines are used, a dummy read operation will have to be performed on every SRAM on the board. Below is an example sequence of events that can be performed before valid access can be performed on the SRAM.1) Initialize the Memory Controller2) Assert RPS# Low for each of the memory devicesNote:For all devices with x9 bus configuration, the following sequence needs to be performed:1) For the 72M / 36M / 18M x9 devices drive address pin A2 / A10 / A3 low respectively and perform dummyread.2) For the 72M / 36M / 18M x9 devices drive address pin A2 / A10 / A3 high respectively and perform dummyread.If the customer has the trigger conditions met during normal access to the memory then there is no workaround at this point.•FIX STATUSThe fix has been implemented on the new revision and is now available. The new revision is an increment of the existing revision. Please refer to Table 4 for the list of devices affected, current revision and the new revision after the fix.3. JTAG Mode Issue•ISSUE DEFINITIONIf the input clock (K Clock) is left floating when the device is in JTAG mode, spurious high frequency noise on this input can be interpreted by the device as valid clocks. This could cause the impedance matching circuitry (ZQ) on the QDR/DDR devices to periodically load itself with incorrect values. These incorrect values in the ZQ register could force the outputs into a High-Impedance state. The ZQ circuitry requires at least 1000 valid K clock cycles to drive the outputs from high impedance to low impedance levels.•PARAMETERS AFFECTEDThis issue only affects the EXTEST command when the device is in the JTAG mode. The normal functionality of the device will not be affected.•TRIGGER CONDITION(S)EXTEST command executed immediately after power-up without providing any K clock cycles.•SCOPE OF IMPACTThis issue only impacts the EXTEST command when device is tested in the JTAG mode. Normal functionality of the device is not affected. •EXPLANATION OF ISSUEImpedance matching circuitry (ZQ) is present on the QDR/DDR devices to set the desired impedance on the outputs. This ZQ circuitry is updated every 1000 clock cycles of K clock to ensure that the impedance of the O/P is set to valid state. However, when the device is operated in the JTAG mode immediately after power-up, high frequency noise on the input K clock can be treated by the ZQ circuitry as valid clocks thereby setting the outputs in to a high-impedance mode. If a minimum of 1000 valid K clocks are applied before performing the JTAG test, this should clear the ZQ circuitry and ensure that the outputs are driven to valid impedance levels.•WORKAROUNDElimination of the issue: After power-up, before any valid operations are performed on the device, insert a minimum of 1000 valid clocks on K input.•FIX STATUSThe fix involved bypassing the ZQ circuitry in JTAG mode. This was done by overriding the ZQ circuitry by the JTAG signal. The fix has been implemented on the new revision and is now available. The new revision is an increment of the existing revision. Please refer to Table 4 for the list of devices affected, current revision and the new revision after the fix..Table 4.List of Affected devices and the new revisionCurrent Revision New Revision after the FixCY7C129*DV18CY7C129*EV18CY7C130*DV25CY7C130*EV25CY7C130*BV18CY7C130*CV18CY7C130*BV25CY7C130*CV25CY7C132*BV25CY7C132*CV25CY7C131*BV18CY7C131*CV18CY7C132*BV18CY7C132*CV18CY7C139*BV18CY7C139*CV18CY7C191*BV18CY7C191*CV18CY7C141*AV18CY7C141*BV18CY7C142*AV18CY7C142*BV18CY7C151*V18CY7C151*AV18CY7C152*V18CY7C152*AV18ReferencesAll 90nm QDRI/DDRI/QDRII/DDRII datasheets:-Table 5.List of Datasheet spec# for the Affected devicesSpec#Part#DensityArchitecture38-05628CY7C1304DV259-MBIT QDR(TM) SRAM 4-WORD BURST 38-05632CY7C1308DV259-MBIT DDR-I SRAM 4-WORD BURST 001-00350CY7C1292DV18/1294DV189-MBIT QDR- II(TM) SRAM 2-WORD BURST 38-05621CY7C1316BV18/1916BV18/1318BV18/1320BV1818-MBIT DDR-II SRAM 2-WORD BURST 38-05622CY7C1317BV18/1917BV18/1319BV18/1321BV1818-MBIT DDR-II SRAM 4-WORD BURST 38-05623CY7C1392BV18/1393BV18/1394BV1818-MBIT DDR-II SIO SRAM 2-WORD BURST 38-05631CY7C1323BV2518-MBIT DDR-I SRAM 4-WORD BURST 38-05630CY7C1305BV25/1307BV2518-MBIT QDR(TM) SRAM 4-WORD BURST 38-05627CY7C1303BV25/1306BV2518-MBIT QDR(TM) SRAM 2-WORD BURST 38-05629CY7C1305BV18/1307BV1818-MBIT QDR(TM) SRAM 4-WORD BURST 38-05626CY7C1303BV18/1306BV1818-MBIT QDR(TM) SRAM 2-WORD BURST 38-05619CY7C1310BV18/1910BV18/1312BV18/1314BV1818-MBIT QDR - II (TM) SRAM 2-WORD BURST 38-05620CY7C1311BV18/1911BV18/1313BV18/1315BV1818-MBIT QDR - II SRAM 4-WORD BURST 38-05615CY7C1410AV18/1425AV18/1412AV18/1414AV1836-MBIT QDR-II(TM) SRAM 2-WORD BURST 38-05614CY7C1411AV18/1426AV18/1413AV18/1415AV1836-MBIT QDR(TM)-II SRAM 4-WORD BURST 38-05616CY7C1416AV18/1427AV18/1418AV18/1420AV1836-MBIT DDR-II SRAM 2-WORD BURST 38-05618CY7C1417AV18/1428AV18/1419AV18/1421AV1836-MBIT DDR-II SRAM 4-WORD BURST 38-05617CY7C1422AV18/1429AV18/1423AV18/1424AV1836-MBIT DDR-II SIO SRAM 2-WORD BURST 38-05489CY7C1510V18/1525V18/1512V18/1514V1872-MBIT QDR-II SRAM 2-WORD BURST 38-05363CY7C1511V18/1526V18/1513V18/1515V1872-MBIT QDR(TM)-II SRAM 4-WORD BURST 38-05563CY7C1516V18/1527V18/1518V18/1520V1872-MBIT DDR-II SRAM 2-WORD BURST 38-05565CY7C1517V18/1528V18/1519V18/1521V1872-MBIT DDR-II SRAM 4-WORD BURST 38-05564CY7C1522V18/1529V18/1523V18/1524V1872-MBITDDR-II SIO SRAM 2-WORD BURSTDocument History PageDocument Title: RAM9 QDR-I/DDR-I/QDR-II/DDR- II Errata Document #: 001-06217 Rev. *CREV.ECN NO.IssueDateOrig. ofChange Description of Change**419849See ECN REF New errata for Ram9 QDR2/DDR2 SRAMs.*A493936See ECN QKS Added Output buffer and JTAG mode issues, Item#2 and #3Added 9Mb QDR-II Burst of 2 and QDR-1/DDR-I part numbers.*B733176See ECN NJY Added missing part numbers in the title for Spec#’s 38-05615,38-05614,38-05363,38-05563 on Table 5 on page 7.*C1030020 See ECN TBE Updated the fix status of the three issues, and modified the description forthe Output Buffer workaround for x9 devices on page 5.。

CCS-18T14C资料

TTL

SP6T

H = 2.15 STD Model H = 2.65 TTL Model

SP5T

SP4T

SP3T

Part Numbering System for CCS-18 (Normally Open) CCS-18 N 1 5 O - T

Series Connectors Actuator Voltage Connector S: SMA Female N: N type Female T: TNC Female* Actuator Voltage 1: 28Vdc Normally Open 2: 15Vdc Normally Open 3: 12Vdc Normally Open Number of Positions 3: SP3T 4: SP4T 5: SP5T 6: SP6T Options Actuator Type Number of Switch Positions Actuator Type O: No Indicator Contacts C: Indicator Contacts Options T: TTL Drivers with Diodes R: Positive + Common TD: TTL Driver with Decoder

3000

Typical Performance

Hig

800 400

Sta nda r

nne

dN

cto

Power CW (Watts)

Typ e

rs

200

Co nne cto

rs

15

80

40

25

Return Loss

hP ow er

Co

珍贵资料-cy7c68013中文手册

CY7C68013A, CY7C68014ACY7C68015A, CY7C68016A EZ-USB FX2LP (TM) USB 微控制器高速 USB 外设控制器1. 特色 (CY7C68013A/14A/15A/16A)■USB 2.0 USB IF 高速性能且经过认证 (TID # 40460272)■单芯片集成 USB 2.0 收发器、智能串行接口引擎 (SIE) 和增强型 8051 微处理器■适用性、外观和功能均与FX2兼容❐引脚兼容❐目标代码兼容❐功能兼容(FX2LP 是超集)■超低功耗:I CC在任何模式下都不超过 85 mA❐适合总线和电池供电的应用■软件:8051 代码运行介质:❐内部 RAM,通过 USB 下载❐内部 RAM,从 EEPROM 加载❐外部存储设备(128 引脚封装)■16 K 字节片上代码/数据 RAM■四个可编程的 BULK/INTERRUPT/ISOCHRONOUS 端点❐缓冲区大小选项:两倍,三倍,四倍■附加的可编程(BULK/INTERRUPT) 64 位端点■8 位或 16 位外部数据接口■可生成智能介质标准错误校正码 ECC ■通用可编程接口 (General Programmable Interface,GPIF)❐可与大多数并行接口直接连接❐由可编程波形描述符和配置寄存器定义波形❐支持多个 Ready (RDY) 输入和 Control (CTL) 输出■符合行业标准的集成增强型 8051❐48 MHz、24 MHz 或 12 MHz CPU 操作❐每个指令周期四个时钟❐两个 USART❐三个计数器/定时器❐扩展的中断系统❐两个数据指针■3.3V 工作电压,容限输入为 5V■向量化 USB 中断和 GPIF/FIFO 中断■分离的 CONTROL 传输设置部分和数据部分数据缓冲■集成 I2C 控制器,在 100 或 400 kHz 下运行■集成的四个先进先出 (FIFO) 缓冲❐集成胶合逻辑和 FIFO 有助于降低系统成本❐与 16 位总线之间的自动转换❐可主-从操作❐使用外部时钟或异步选通脉冲❐易于与 ASIC 和 DSP IC 相连的接口■有商业和工业温度等级供选择(除 VFBGA 外的所有封装)1.1 特色(仅限 CY7C68013A/14A )■CY7C68014A :适合电池供电应用❐挂起电流:100 μA (typ)■CY7C68013A :适合非电池供电应用❐挂起电流:300 μA (typ)■有五种无铅封装供选择,可包含多达 40 个 GPIO ❐128 引脚 TQFP (40 个 GPIO )、100 引脚 TQFP (40 个 GPIO )、56 引脚 QFN (24 个 GPIO )、56 引脚 SSOP (24 个 GPIO )和 56 引脚 VFBGA (24 个 GPIO )1.2 特色(仅限 CY7C68015A/16A )■CY7C68016A :适合电池供电应用❐挂起电流:100 μA (typ)■CY7C68015A :适合非电池供电应用❐挂起电流:300 μA (typ)■采用无铅 56 引脚 QFN 封装(26 个 GPIO )❐比 CY7C68013A/14A 多 2 个 GPIO ,可在同样的空间内实现额外的功能赛普拉斯半导体公司(赛普拉斯)的 EZ-USB FX2LP ™ (CY7C68013A/14A) 是高集成、低功耗 USB 2.0 微控制器EZ-USB FX2™ (CY7C68013) 的一个低功耗版本。

CY7C1069AV33-10BAI中文资料

–8

Parameter

Description

Test Conditions

Min. Max.

VOH

Output HIGH Voltage VCC = Min.,

IOH = –4.0 mA

VOL

tDOE

OE LOW to Data Valid

tLZOE

OE LOW to Low-Z[6]

1

tHZOE

OE HIGH to High-Z[6]

tLZCE

CE1 LOW/CE2 HIGH to Low-Z[6]

2.0

–0.3 –1 –1

VCC + 0.3 0.8

+1 +1

260 260 70

50

Unit V

V

V

V µA µA mA mA mA

mA

Capacitance[2]

Parameter

Package

Description

Test Conditions

CIN

Z54

Input Capacitance

TA = 25°C, f = 1 MHz, VCC = 3.3V

Disabled

2.4

0.4

2.0 VCC + 0.3

–0.3 0.8 –1 +1 –1 +1

ICC

VCC Operating

VCC = Max., f = fMAX Commercial

300

Supply Current

= 1/tRC

Industrial

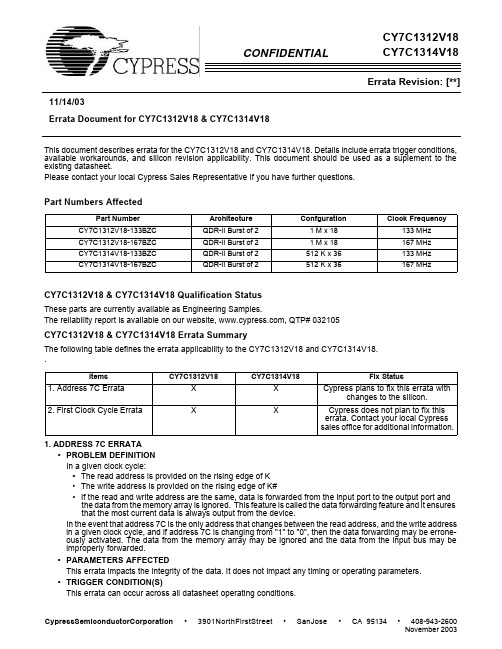

CY7C1314V18-167BZC资料

Errata Revision: [**]CY7C1312V18CY7C1314V18CONFIDENTIAL11/14/03Errata Document for CY7C1312V18 & CY7C1314V18This document describes errata for the CY7C1312V18 and CY7C1314V18. Details include errata trigger conditions,available workarounds, and silicon revision applicability. This document should be used as a suplement to the existing datasheet.Please contact your local Cypress Sales Representative if you have further questions.Part Numbers AffectedCY7C1312V18 & CY7C1314V18 Qualification StatusThese parts are currently available as Engineering Samples.The reliability report is available on our website, , QTP# 032105CY7C1312V18 & CY7C1314V18 Errata SummaryThe following table defines the errata applicability to the CY7C1312V18 and CY7C1314V18. .1. ADDRESS 7C ERRATA•PROBLEM DEFINITION In a given clock cycle:•The read address is provided on the rising edge of K •The write address is provided on the rising edge of K#•If the read and write address are the same, data is forwarded from the input port to the output port and the data from the memory array is ignored. This feature is called the data forwarding feature and it ensures that the most current data is always output from the device.In the event that address 7C is the only address that changes between the read address, and the write address in a given clock cycle, and if address 7C is changing from "1" to "0", then the data forwarding may be errone-ously activated. The data from the memory array may be ignored and the data from the input bus may be improperly forwarded.•PARAMETERS AFFECTEDThis errata impacts the integrity of the data. It does not impact any timing or operating parameters.•TRIGGER CONDITION(S)This errata can occur across all datasheet operating conditions.Part Number Architecture Confguration Clock FrequencyCY7C1312V18-133BZC QDR-II Burst of 2 1 M x 18133 MHz CY7C1312V18-167BZC QDR-II Burst of 2 1 M x 18167 MHz CY7C1314V18-133BZC QDR-II Burst of 2512 K x 36133 MHz CY7C1314V18-167BZCQDR-II Burst of 2512 K x 36167 MHzItemsCY7C1312V18CY7C1314V18Fix Status1. Address 7C Errata X X Cypress plans to fix this errata withchanges to the silicon.2. First Clock Cycle ErrataXXCypress does not plan to fix this errata. Contact your local Cypress sales office for additional information.元器件交易网CY7C1312V18CY7C1314V18CONFIDENTIALErrata Document•SCOPE OF IMPACTThis issue only applies to the burst of 2 arhcitecture only. QDR-II. Burst of 4 devices are NOT affected by this issue. This errata affects the output of the data from the device. It does not affect the data integrity in the memory array.The impact this has in an application has two components. First, it is dependent on how often the failing condition occurs. Second, it is dependent on the system’s ability to recover from the occurance of incorrect data.In applications with truly random access of the memory, it will occur at a rate of 2 PPM for the CY7C1312V18and 4 PPM for the CY7C1314V18. However, it will occur more frequently in applications where the failing conditions occur more frequently.•WORKAROUNDProhibit the failing conditions in the SRAM controller’s software.•FIX STATUSCypress has identified a change to the silicon that will eliminate this errata.2. FIRST CLOCK CYCLE ERRATA•PROBLEM DEFINITIONIn the first clock cylce seen by the device, it is possible for data to be written into the memory array incorrectly. Specificlly, the first word may be written to the second burst address and the second word may be written to the first burst address. This can only occur in the first clock cycle seen by the device and will not occur in subsequent clock cycles.To date, Cypress is unaware of any applications that have experienced this issue.•PARAMETERS AFFECTEDThis errata impacts the integrity of the data. It does not impact any timing or operating parameters.•TRIGGER CONDITION(S)This errata will only occur during the first clock cycle seen by the device. It will not occur after the second rising edges of the K and K# clocks. Therefore, if the device sees any clock cycles during power up, this errata will not occur.This errata occurs under the following conditions:(1) V DD reaches 1.7 V at t 0,(2) K# rises from low to high after t 0 + 25 ns,(3) K# rises from low to high before the first rising edge of K.A timing diagram for these trigger conditions is shown below:Timing Diagram For First Clock Cycle Errata Trigger ConditionsCONFIDENTIALErrata DocumentCY7C1312V18CY7C1314V18•SCOPE OF IMPACTThis errata only impacts the data integrity of data written during the first clock cycle seen by the device. All subsequent writes will be written correctly.To date, none of our customers have reported seeing this failure mechanism in an application.A timing diagram describing device operation after the first clock cycle errata is triggered is shown below.•WORKAROUNDThere are numerous available workarounds to this errata. These include the following:1. Wait until after the first clock cycle to write to the device.2. Ensure that K rises high before K# (Shown Below)Timing Diagram For Ensuring K Rises Before K#CY7C1312V18CY7C1314V18Errata DocumentCONFIDENTIAL© Cypress Semiconductor Corporation, 2003. The information contained herein is subject to change without notice. Cypress Semicon ductor Corporation assumes no responsibility for the use3. Bring K# input high prior to t0 + 25 ns.•FIX STATUSCypress does not have a plan to correct this errata. If your application cannot accommodate the suggestedworkarounds, please contact your Cypress FAE.References[1] Document # 38-05180,CY7C1310V18/CY7C1312V18/CY7C1314V18: 18-Mb QDR(TM)-II SRAM Two-wordBurst Architecture (Preliminary)Timing Diagram For Bringing K# High Prior to t0 + 25 ns元器件交易网CY7C1312V18CY7C1314V18CONFIDENTIALErrata DocumentDocument History PageDocument Title: CY7C1312V18 & CY7C1314V18 Errata Document Number: 38-17005REV.ECN NO.Issue Date Orig. ofChange Description of Change**13128411/14/03RCS1.New Document元器件交易网。

CY7C131中文资料

1K x 8 Dual-Port Static RAMCY7C130/CY7C131CY7C140/CY7C141Features•True Dual-Ported memory cells which allow simulta-neous reads of the same memory location •1K x 8 organization•0.65-micron CMOS for optimum speed/power •High-speed access: 15 ns•Low operating power: I CC = 110 mA (max.)•Fully asynchronous operation •Automatic power-down•Master CY7C130/CY7C131 easily expands data bus width to 16 or more bits using slave CY7C140/CY7C141•BUSY output flag on CY7C130/CY7C131; BUSY input on CY7C140/CY7C141•INT flag for port-to-port communication•Available in 48-pin DIP (CY7C130/140), 52-pin PLCC, 52-Pin TQFP .•Pb-Free packages availableFunctional DescriptionThe CY7C130/CY7C131/CY7C140 and CY7C141 are high-speed CMOS 1K by 8 dual-port static RAMs. Two ports are provided permitting independent access to any location in memory. The CY7C130/ CY7C131 can be utilized as either a standalone 8-bit dual-port static RAM or as a master dual-port RAM in conjunction with the CY7C140/CY7C141 slave dual-port device in systems requiring 16-bit or greater word widths. It is the solution to applications requiring shared or buffered data, such as cache memory for DSP , bit-slice, or multiprocessor designs.Each port has independent control pins; chip enable (CE), write enable (R/W), and output enable (OE). Two flags are provided on each port, BUSY and INT. BUSY signals that the port is trying to access the same location currently being accessed by the other port. INT is an interrupt flag indicating that data has been placed in a unique location (3FF for the left port and 3FE for the right port). An automatic power-down feature is controlled independently on each port by the chip enable (CE) pins.The CY7C130 and CY7C140 are available in 48-pin DIP . The CY7C131 and CY7C141 are available in 52-pin PLCC, 52-pin Pb-free PLCC, 52-pin PQFP and 52-pin Pb-free PQFP .Note:1.CY7C130/CY7C131 (Master): BUSY is open drain output and requires pull-up resistor2.Open drain outputs: pull-up resistor required.Logic Block DiagramPin Configurations131415161718192021222326272832313029333635342425GND123456789101138394044434241454847461237R/W L CE L BUSY L INT L OE L A 0L A 1L A 2L A 3L A 4L A 5L A 6L A 7L A 8L A 9L I/O 0L I/O 1L I/O 2L I/O 3L I/O 4L I/O 5L I/O 6L I/O 7L CE R R/W R BUSY R INT R OE R A 0R A 1R A 2R A 3R A 4R A 5R A 6R A 7R A 8R A 9R I/O 7R I/O 6R I/O 5R I/O 4R I/O 3R I/O 2R I/O 1R I/O 0RV CCDIP Top View7C1307C140R/W L BUSY LCE L OE LA 9L A 0LA 0RA 9R R/W R CE R OE RCE R OE R CE L OE L R/W LR/W RI/O 7L I/O 0L I/O 7R I/O 0R BUSY RINT LINT RARBITRATIONLOGIC(7C130/7C131ONLY)ANDINTERRUPT LOGICCONTROL I/O CONTROLI/O MEMORY ARRAYADDRESS DECODERADDRESS DECODER[1][2][2]Pin Configuration (continued )1V C CTop ViewPLCC OE R A 0R 8910111213141516171819204645444342414039383736353421222324252627282930313233765432525150494847A 1R A 2R A 3R A 4R A 5R A 6R A 7R A 8R A 9R NC I/O 7RA 1LA 2L A 3L A 4L A 5L A 6L A 7L A 8L A 9L I/O 0L I/O 1L I/O 2L I/O 3LI /O I /O I /O I /O I /O I /O I /O I /O I /O I /O I /O 4L 5L6L 7L0R 1R2R 3R 4R5R 6RN C G N DO E B U S Y I N T A N C R /W C E R /W B U S Y I N T N C0LL L LL L C E R R R R7C1317C14146123456789101112133938373635343332313029282714151617181920212223242526525150494847454443424140Top ViewPQFPV C CO E B U S Y I N T A N C R /W C E R /W B U S Y I N T N C0LL L LL L C E R R R ROE R A 0R A 1R A 2R A 3R A 4R A 5R A 6R A 7R A 8R A 9R NC I/O 7RA 1L A 2L A 3L A 4L A 5L A 6L A 7L A 8L A 9L I/O 0L I/O 1L I/O 2L I/O 3LI /O I /O I /O I /O I /O I /O I /O I /O I /O I /O I /O 4L 5L6L 7L0R 1R2R 3R 4R5R 6RN C G N D 7C1317C141Pin DefinitionsLeft PortRight PortDescriptionCE L CE R Chip Enable R/W L R/W R Read/Write Enable OE LOE ROutput Enable A 0L –A 11/12L A 0R –A 11/12R AddressI/O 0L –I/O 15/17L I/O 0R –I/O 15/17R Data Bus Input/Output INT L INT R Interrupt Flag BUSY L BUSY RBusy Flag V CC Power GNDGroundSelection Guide7C131-15[3]7C141-157C131-25[3]7C141-257C130-307C131-307C140-307C141-307C130-357C131-357C140-357C141-357C130-457C131-457C140-457C141-457C130-557C131-557C140-557C141-55Unit Maximum Access Time 152530354555ns Maximum Operating CurrentCom’l/Ind 190170170120120110mAMilitary 170170120Maximum Standby CurrentCom’l/Ind 756565454535mAMilitary656545Shaded areas contain preliminary information.Note:3.15 and 25-ns version available only in PLCC/PQFP packages.Maximum Ratings[4](Above which the useful life may be impaired. For user guide-lines, not tested.)Storage Temperature .................................–65°C to +150°C Ambient Temperature withPower Applied.............................................–55°C to +125°C Supply Voltage to Ground Potential(Pin 48 to Pin 24)...........................................–0.5V to +7.0V DC Voltage Applied to Outputsin High Z State...............................................–0.5V to +7.0V DC Input Voltage............................................–3.5V to +7.0V Output Current into Outputs (LOW).............................20 mA Static Discharge Voltage........................................... >2001V (per MIL-STD-883, Method 3015)Latch-Up Current.................................................... >200 mA Operating RangeRangeAmbientTemperature V CC Commercial0°C to +70°C 5V ± 10% Industrial–40°C to +85°C 5V ± 10% Military[5]–55°C to +125°C 5V ± 10%Electrical Characteristics Over the Operating Range[6]Parameter Description Test Conditions 7C131-15[3]7C141-157C130-30[3]7C131-25,307C140-307C141-25,307C130-35,457C131-35,457C140-35,457C141-35,457C130-557C131-557C140-557C141-55Unit Min.Max.Min.Max.Min.Max.Min.Max.V OH Output HIGHVoltageV CC = Min., I OH = –4.0 mA 2.4 2.4 2.4 2.4VV OL Output LOWVoltage I OL = 4.0 mA0.40.40.40.4V I OL = 16.0 mA[7]0.50.50.50.5V IH Input HIGH Voltage 2.2 2.2 2.2 2.2V V IL Input LOW Voltage0.80.80.80.8V I IX Input LeakageCurrentGND < V I < V CC–5+5–5+5–5+5–5+5µAI OZ Output LeakageCurrent GND < V O < V CC,Output Disabled–5+5–5+5–5+5–5+5µAI OS Output ShortCircuit Current[8, 9]V CC = Max.,V OUT = GND–350–350–350–350mAI CC V CC OperatingSupply Current CE = V IL,Outputs Open,f = f MAX[10]Com’l190170120110mAMil170120I SB1Standby CurrentBoth Ports,TTL Inputs CE L and CE R >V IH, f = f MAX[10]Com’l75654535mAMil6545I SB2Standby CurrentOne Port,TTL Inputs CE L or CE R > V IH,Active Port OutputsOpen,f = f MAX[10]Com’l1351159075mAMil11590I SB3Standby CurrentBoth Ports,CMOS Inputs Both Ports CE L andCE R >V CC – 0.2V,V IN > V CC – 0.2Vor V IN < 0.2V, f = 0Com’l15151515mAMil1515Shaded areas contain preliminary information.Note:4.The Voltage on any input or I/O pin cannot exceed the power pin during power-up.5.T A is the “instant on” case temperature6.See the last page of this specification for Group A subgroup testing information.7.BUSY and INT pins only.8.Duration of the short circuit should not exceed 30 seconds.9.This parameter is guaranteed but not tested.10.At f = f MAX, address and data inputs are cycling at the maximum frequency of read cycle of 1/t RC and using AC Test Waveforms input levels of GND to 3V.I SB4Standby Current One Port, CMOS InputsOne Port CE L or CE R > V CC – 0.2V,V IN > V CC – 0.2V or V IN < 0.2V, Active Port Outputs Open, f = f MAX [10]Com’l 1251058570mAMil10585Capacitance [9]Parameter DescriptionTest ConditionsMax.Unit C IN Input Capacitance T A = 25°C, f = 1 MHz, V CC = 5.0V15pF C OUTOutput Capacitance10pFElectrical Characteristics Over the Operating Range [6] (continued)Parameter Description Test Conditions 7C131-15[3]7C141-157C130-30[3]7C131-25,307C140-307C141-25,307C130-35,457C131-35,457C140-35,457C141-35,457C130-557C131-557C140-557C141-55Unit Min.Max.Min.Max.Min.Max.Min.Max.AC Test Loads and Waveforms3.0V 5V OUTPUTR1 893ΩR2347Ω30pF INCLUDING JIGAND SCOPEGND90%90%10%≤ 5ns≤5ns5V OUTPUTR1 893ΩR2347Ω5pFINCLUDING JIGAND SCOPE(a)(b)OUTPUT1.40VEquivalent to:THÉVENIN EQUIVALENT5V 281Ω30pFBUSY OR INT(CY7C130/CY7C131ONLY)10%ALL INPUT PULSES 250ΩSwitching Characteristics Over the Operating Range[6, 11]Parameter Description7C131-15[3]7C141-157C130-25[3]7C131-257C140-257C141-257C130-307C131-307C140-307C141-30Unit Min.Max.Min.Max.Min.Max.READ CYCLEt RC Read Cycle Time152530ns t AA Address to Data Valid[12]152530ns t OHA Data Hold from Address Change000ns t ACE CE LOW to Data Valid[12]152530ns t DOE OE LOW to Data Valid[12]101520ns t LZOE OE LOW to Low Z[9, 13, 14]333ns t HZOE OE HIGH to High Z[9, 13, 14]101515ns t LZCE CE LOW to Low Z[9, 13, 14]355ns t HZCE CE HIGH to High Z[9, 13, 14]101515ns t PU CE LOW to Power-Up[9]000ns t PD CE HIGH to Power-Down[9]152525ns WRITE CYCLE[15]t WC Write Cycle Time152530ns t SCE CE LOW to Write End122025ns t AW Address Set-Up to Write End122025ns t HA Address Hold from Write End222ns t SA Address Set-Up to Write Start000ns t PWE R/W Pulse Width121525ns t SD Data Set-Up to Write End101515ns t HD Data Hold from Write End000ns t HZWE R/W LOW to High Z[14]101515ns t LZWE R/W HIGH to Low Z[14]000ns Shaded areas contain preliminary information.Note:11.Test conditions assume signal transition times of 5 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V and output loading of the specifiedI OL/I OH, and 30-pF load capacitance.12.AC Test Conditions use V OH = 1.6V and V OL = 1.4V.13.At any given temperature and voltage condition for any given device, t HZCE is less than t LZCE and t HZOE is less than t LZOE.14.t LZCE, t LZWE, t HZOE, t LZOE, t HZCE and t HZWE are tested with C L = 5pF as in part (b) of AC Test Loads. Transition is measured ±500 mV from steady state voltage.15.The internal write time of the memory is defined by the overlap of CS LOW and R/W LOW. Both signals must be low to initiate a write and either signal canterminate a write by going high. The data input set-up and hold timing should be referenced to the rising edge of the signal that terminates the write.BUSY/INTERRUPT TIMING t BLA BUSY LOW from Address Match 152020ns t BHA BUSY HIGH from Address Mismatch [16]152020ns t BLC BUSY LOW from CE LOW 152020ns t BHC BUSY HIGH from CE HIGH [16]152020ns t PS Port Set Up for Priority 555ns t WB [17]R/W LOW after BUSY LOW 000ns t WH R/W HIGH after BUSY HIGH 132030ns t BDD BUSY HIGH to Valid Data152530ns t DDD Write Data Valid to Read Data Valid Note 18Note 18Note 18ns t WDD Write Pulse to Data Delay Note 18Note 18Note 18ns INTERRUPT TIMINGt WINS R/W to INTERRUPT Set Time 152525ns t EINS CE to INTERRUPT Set Time 152525ns t INS Address to INTERRUPT Set Time 152525ns t OINR OE to INTERRUPT Reset Time [16]152525ns t EINR CE to INTERRUPT Reset Time [16]152525ns t INRAddress to INTERRUPT Reset Time [16]152525nsShaded areas contain preliminary information.Note:16.These parameters are measured from the input signal changing, until the output pin goes to a high-impedance state.17.CY7C140/CY7C141 only.18.A write operation on Port A, where Port A has priority, leaves the data on Port B’s outputs undisturbed until one access time after one of the following:BUSY on Port B goes HIGH. Port B’s address is toggled. CE for Port B is toggled.R/W for Port B is toggled during valid read.Switching Characteristics Over the Operating Range [6, 11] (continued)ParameterDescription7C131-15[3]7C141-157C130-25[3]7C131-257C140-257C141-257C130-307C131-307C140-307C141-30UnitMin.Max.Min.Max.Min.Max.Switching Characteristics Over the Operating Range [6,11]Parameter Description7C130-357C131-357C140-357C141-357C130-457C131-457C140-457C141-457C130-557C131-557C140-557C141-55UnitMin.Max.Min.Max.Min.Max.READ CYCLE t RC Read Cycle Time 354555ns t AA Address to Data Valid [12]354555ns t OHA Data Hold from Address Change 0ns t ACE CE LOW to Data Valid [12]354555ns t DOE OE LOW to Data Valid [12]202525ns t LZOE OE LOW to Low Z [9, 13, 14]333ns t HZOE OE HIGH to High Z [9, 13, 14]202025ns t LZCECE LOW to Low Z [9, 13, 14]555nst HZCE CE HIGH to High Z [9, 13, 14]202025ns t PU CE LOW to Power-Up [9]0ns t PD CE HIGH to Power-Down [9]353535ns WRITE CYCLE [15]t WC Write Cycle Time 354555ns t SCE CE LOW to Write End 303540ns t AW Address Set-Up to Write End 303540ns t HA Address Hold from Write End 222ns t SA Address Set-Up to Write Start 000ns t PWE R/W Pulse Width253030ns t SD Data Set-Up to Write End 152020ns t HD Data Hold from Write End 0ns t HZWE R/W LOW to High Z [14]202025ns t LZWE R/W HIGH to Low Z [14]ns BUSY/INTERRUPT TIMINGt BLA BUSY LOW from Address Match 202530ns t BHA BUSY HIGH from Address Mismatch [16]202530ns t BLC BUSY LOW from CE LOW 202530ns t BHC BUSY HIGH from CE HIGH [16]202530ns t PS Port Set Up for Priority 555ns t WB [17]R/W LOW after BUSY LOW 000ns t WH R/W HIGH after BUSY HIGH 303535ns t BDD BUSY HIGH to Valid Data354545ns t DDD Write Data Valid to Read Data Valid Note 18Note 18Note 18ns t WDDWrite Pulse to Data DelayNote 18Note 18Note 18nsINTERRUPT TIMING t WINS R/W to INTERRUPT Set Time 253545ns t EINS CE to INTERRUPT Set Time 253545ns t INS Address to INTERRUPT Set Time 253545ns t OINR OE to INTERRUPT Reset Time [16]253545ns t EINR CE to INTERRUPT Reset Time [16]253545ns t INRAddress to INTERRUPT Reset Time [16]253545nsSwitching Characteristics Over the Operating Range [6,11] (continued)Parameter Description7C130-357C131-357C140-357C141-357C130-457C131-457C140-457C141-457C130-557C131-557C140-557C141-55Unit Min.Max.Min.Max.Min.Max.Switching WaveformsRead Cycle No. 1[19, 20]Read Cycle No. 2[19, 21]Read Cycle No. 3[20]Notes:19.R/W is HIGH for read cycle.20.Device is continuously selected, CE = V IL and OE = V IL .21.Address valid prior to or coincident with CE transition LOW.t RCt AAt OHADATA VALIDPREVIOUS DATA VALIDDATA OUTADDRESSEither Port Address Accesst ACEt LZOEt DOEt HZOEt HZCEDATA VALIDDATA OUTCE OEt LZCEt PUI CC I SBt PDEither Port CE/OE Accesst BHAt BDDVALIDt DDDt WDDADDRESS MATCHADDRESS MATCHR/W R ADDRESS RD INRADDRESS LBUSY LDOUT Lt PSt BLARead with BUSY , Master: CY7C130 and CY7C131t RCt PWEVALIDt HDWrite Cycle No. 1 (OE Three-States Data I/Os—Either Port [15, 22]Write Cycle No. 2 (R/W Three-States Data I/Os—Either Port)[16, 23]Notes:22.PWE or t HZWE + t SD to allow the data I/O pins to enter high impedanceand for data to be placed on the bus for the required t SD .23.If the CE LOW transition occurs simultaneously with or after the R/W LOW transition, the outputs remain in the high-impedance state.Switching Waveforms (continued)t AWt WCDATA VALIDHIGH IMPEDANCEt SCEt SAt PWEt HDt SDt HACER/WADDRESSt HZOEOED OUTDATA INEither Portt AWt WCt SCEt SAt PWEt HDt SDt HZWEt HAHIGH IMPEDANCEDATA VALIDt LZWEADDRESSCER/WDATA OUTDATA INBusy Timing Diagram No. 1 (CE Arbitration)Busy Timing Diagram No. 2 (Address Arbitration)Switching Waveforms (continued)ADDRESS MATCHt PSCE L Valid First:t BLCt BHCADDRESS MATCHt PSt BLCt BHCADDRESS L,RBUSY RCE LCE RBUSY LCE RCE LADDRESS L,RCE R Valid First:Left Address Valid First:ADDRESS MATCHt PSADDRESS LBUSY RADDRESS MISMATCHt RC or t WC t BLA t BHAADDRESS RADDRESS MATCHADDRESS MISMATCHt PSADDRESS LBUSY Lt RC or t WC t BLA t BHAADDRESS RRight Address Valid First:Switching Waveforms (continued)Busy Timing Diagram No. 3Write with BUSY (Slave:CY7C140/CY7C141)CEt PWER/Wt WB t WH BUSYInterrupt Timing Diagrams Switching Waveforms (continued)WRITE 3FFt INSt WCt EINSRight Side Clears INT Rt HAt SAt WINSREAD 3FF t RCt EINRt HAt INTt OINRWRITE 3FEt INSt WCt EINSt HAt SAt WINSRight Side Sets INT LLeft Side Sets INT RLeft Side Clears INT LREAD 3FE t EINRt HAt INRt OINRt RC ADDR RCE LR/W L INT LOE LADDR RR/W R CE RINT LADDR RCE RR/W R INT ROE RADDR LR/W LCE LINT RTypical DC and AC Characteristics1.41.00.44.04.55.05.56.0–55251251.21.01201008060402001.02.03.04.0O U T P U T S O U R C E C U R R E N T (m A )SUPPLY VOLTAGE (V)NORMALIZED SUPPLY CURRENTvs. SUPPLY VOLTAGENORMALIZED SUPPLY CURRENT vs. AMBIENT TEMPERATURE AMBIENT TEMPERATURE (°C)OUTPUT VOLTAGE (V)OUTPUT SOURCE CURRENT vs. OUTPUT VOLTAGE 0.00.80.80.60.6N O R M A L I Z E D I C C , I S BV CC = 5.0V V IN = 5.0V V CC = 5.0V T A = 25°C0I CC1.61.41.21.00.8–55125N O R M A L I Z E D t A ANORMALIZED ACCESS TIME vs. AMBIENT TEMPERATURE AMBIENT TEMPERATURE (°C)1.41.31.21.00.94.04.55.05.56.0N O R M A L I Z E D t A ASUPPLY VOLTAGE (V)NORMALIZED ACCESS TIME vs. SUPPLY VOLTAGE 120140*********0.01.02.03.04.0O U T P U T S I N K C U R R E N T (m A )080OUTPUT VOLTAGE (V)OUTPUT SINK CURRENT vs. OUTPUT VOLTAGE0.60.8 1.251.00.751040N O R M A L I Z E D I C C0.50NORMALIZED I CC vs. CYCLE TIME CYCLE FREQUENCY (MHz)3.02.52.01.50.501.02.03.05.0N O R M A L I Z E D t P C25.030.020.010.05.00200400600800D E L T A t A A (n s )015.00.0SUPPLY VOLTAGE (V)TYPICAL POWER-ON CURRENT vs. SUPPLY VOLTAGE CAPACITANCE (pF)TYPICAL ACCESS TIME CHANGE vs. OUTPUT LOADING4.010001.020300.20.61.2I SB30.20.4251.1V V IN = 0.5VN O R M A L I Z E D I C C , I S BI CCI SB3T A = 25°CV CC = 5.0VV CC = 5.0V T A = 25°CT A = 25°CCC = 4.5V V CC = 4.5V T A = 25°COrdering InformationSpeed(ns)Ordering Code PackageName Package TypeOperatingRange30CY7C130-30PC P2548-Lead (600-Mil) Molded DIP Commercial CY7C130-30PI P2548-Lead (600-Mil) Molded DIP Industrial 35CY7C130-35PC P2548-Lead (600-Mil) Molded DIP Commercial CY7C130-35PI P2548-Lead (600-Mil) Molded DIP Industrial CY7C130-35DMB D2648-Lead (600-Mil) Sidebraze DIP Military45CY7C130-45PC P2548-Lead (600-Mil) Molded DIP Commercial CY7C130-45PI P2548-Lead (600-Mil) Molded DIP Industrial CY7C130-45DMB D2648-Lead (600-Mil) Sidebraze DIP Military55CY7C130-55PC P2548-Lead (600-Mil) Molded DIP Commercial CY7C130-55PI P2548-Lead (600-Mil) Molded DIP Industrial CY7C130-55DMB D2648-Lead (600-Mil) Sidebraze DIP Military15CY7C131-15JC J6952-Lead Plastic Leaded Chip Carrier Commercial CY7C131-15JXC J6952-Lead Pb-Free Plastic Leaded Chip CarrierCY7C131-15NC N5252-Pin Plastic Quad FlatpackCY7C131-15JI J6952-Lead Plastic Leaded Chip Carrier Industrial CY7C131-15JXI J6952-Lead Pb-Free Plastic Leaded Chip Carrier25CY7C131-25JC J6952-Lead Plastic Leaded Chip Carrier Commercial CY7C131-25JXC J6952-Lead Pb-Free Plastic Leaded Chip CarrierCY7C131-25NC N5252-Pin Plastic Quad FlatpackCY7C131-25NXC N5252-Pin Pb-Free Plastic Quad FlatpackCY7C131-25JI J6952-Lead Plastic Leaded Chip Carrier Industrial CY7C131-25NI N5252-Pin Plastic Quad Flatpack30CY7C131-30JC J6952-Lead Plastic Leaded Chip Carrier Commercial CY7C131-30NC N5252-Pin Plastic Quad FlatpackCY7C131-30JI J6952-Lead Plastic Leaded Chip Carrier Industrial 35CY7C131-35JC J6952-Lead Plastic Leaded Chip Carrier Commercial CY7C131-35NC N5252-Pin Plastic Quad FlatpackCY7C131-35JI J6952-Lead Plastic Leaded Chip Carrier Industrial CY7C131-35NI N5252-Pin Plastic Quad Flatpack45CY7C131-45JC J6952-Lead Plastic Leaded Chip Carrier Commercial CY7C131-45NC N5252-Pin Plastic Quad FlatpackCY7C131-45JI J6952-Lead Plastic Leaded Chip Carrier Industrial CY7C131-45NI N5252-Pin Plastic Quad Flatpack55CY7C131-55JC J6952-Lead Plastic Leaded Chip Carrier Commercial CY7C131-55JXC J6952-Lead Pb-Free Plastic Leaded Chip CarrierCY7C131-55NC N5252-Pin Plastic Quad FlatpackCY7C131-55NXC N5252-Pin Pb-Free Plastic Quad FlatpackCY7C131-55JI J6952-Lead Plastic Leaded Chip Carrier Industrial CY7C131-55JXI J6952-Lead Pb-Free Plastic Leaded Chip CarrierCY7C131-55NI N5252-Pin Plastic Quad Flatpack30CY7C140-30PC P2548-Lead (600-Mil) Molded DIP Commercial CY7C140-30PI P2548-Lead (600-Mil) Molded DIP Industrial 35CY7C140-35PC P2548-Lead (600-Mil) Molded DIP Commercial CY7C140-35PI P2548-Lead (600-Mil) Molded DIP Industrial CY7C140-35DMBD2648-Lead (600-Mil) Sidebraze DIP Military 45CY7C140-45PC P2548-Lead (600-Mil) Molded DIP Commercial CY7C140-45PI P2548-Lead (600-Mil) Molded DIP Industrial CY7C140-45DMBD2648-Lead (600-Mil) Sidebraze DIP Military 55CY7C140-55PC P2548-Lead (600-Mil) Molded DIP Commercial CY7C140-55PI P2548-Lead (600-Mil) Molded DIP Industrial CY7C140-55DMBD2648-Lead (600-Mil) Sidebraze DIP Military 15CY7C141-15JC J6952-Lead Plastic Leaded Chip Carrier CommercialCY7C141-15NC N5252-Pin Plastic Quad Flatpack 25CY7C141-25JC J6952-Lead Plastic Leaded Chip Carrier Commercial CY7C141-25JXC J6952-Lead Pb-Free Plastic Leaded Chip Carrier CY7C141-25NC N5252-Pin Plastic Quad Flatpack CY7C141-25JI J6952-Lead Plastic Leaded Chip Carrier Industrial CY7C141-25NIN5252-Pin Plastic Quad Flatpack 30CY7C141-30JC J6952-Lead Plastic Leaded Chip Carrier Commercial CY7C141-30NC N5252-Pin Plastic Quad Flatpack CY7C141-30JIJ6952-Lead Plastic Leaded Chip Carrier Industrial 35CY7C141-35JC J6952-Lead Plastic Leaded Chip Carrier Commercial CY7C141-35NC N5252-Pin Plastic Quad Flatpack CY7C141-35JI J6952-Lead Plastic Leaded Chip Carrier Industrial CY7C141-35NIN5252-Pin Plastic Quad Flatpack 45CY7C141-45JC J6952-Lead Plastic Leaded Chip Carrier Commercial CY7C141-45NC N5252-Pin Plastic Quad Flatpack CY7C141-45JI J6952-Lead Plastic Leaded Chip Carrier Industrial CY7C141-45NIN5252-Pin Plastic Quad Flatpack 55CY7C141-55JC J6952-Lead Plastic Leaded Chip Carrier Commercial CY7C141-55NC N5252-Pin Plastic Quad Flatpack CY7C141-55JI J6952-Lead Plastic Leaded Chip Carrier Industrial CY7C141-55NIN5252-Pin Plastic Quad FlatpackOrdering Information (continued)Speed (ns)Ordering Code Package Name Package TypeOperating RangeMILITARY SPECIFICATIONS Group A Subgroup Testing Note:24.CY7C140/CY7C141 only.DC CharacteristicsParameterSubgroups V OH 1, 2, 3V OL 1, 2, 3V IH 1, 2, 3V IL Max.1, 2, 3I IX 1, 2, 3I OZ 1, 2, 3I CC 1, 2, 3I SB11, 2, 3I SB21, 2, 3I SB31, 2, 3I SB41, 2, 3Switching CharacteristicsParameterSubgroups READ CYCLEt RC 7, 8, 9, 10, 11t AA 7, 8, 9, 10, 11t ACE 7, 8, 9, 10, 11t DOE7, 8, 9, 10, 11WRITE CYCLEt WC 7, 8, 9, 10, 11t SCE 7, 8, 9, 10, 11t AW 7, 8, 9, 10, 11t HA 7, 8, 9, 10, 11t SA 7, 8, 9, 10, 11t PWE 7, 8, 9, 10, 11t SD 7, 8, 9, 10, 11t HD7, 8, 9, 10, 11BUSY/INTERRUPT TIMINGt BLA 7, 8, 9, 10, 11t BHA 7, 8, 9, 10, 11t BLC 7, 8, 9, 10, 11t BHC 7, 8, 9, 10, 11t PS 7, 8, 9, 10, 11t WINS 7, 8, 9, 10, 11t EINS 7, 8, 9, 10, 11t INS 7, 8, 9, 10, 11t OINR 7, 8, 9, 10, 11t EINR 7, 8, 9, 10, 11t INR7, 8, 9, 10, 11BUSY TIMINGt WB [24]7, 8, 9, 10, 11t WH 7, 8, 9, 10, 11t BDD7, 8, 9, 10, 11Package Diagrams48-Lead (600-Mil) Sidebraze DIP D26MIL-STD-1835 D-14 Config. C51-80044 **Document #: 38-06002 Rev. *DPage 18 of 19All products and company names mentioned in this document may be the trademarks of their respective holders.Package Diagrams (continued)51-85020-*A48-Lead (600-Mil) Molded DIP P2551-85042-**52-Lead Pb-Free Plastic Quad Flatpack N5252-Lead Plastic Quad Flatpack N52Document History PageDocument Title: CY7C130/CY7C131/CY7C140/CY7C141 1K x 8 Dual-Port Static RAM Document Number: 38-06002REV.ECN NO.IssueDateOrig. ofChange Description of Change**11016909/29/01SZV Change from Spec number: 38-00027 to 38-06002*A12225512/26/02RBI Power up requirements added to Maximum Ratings Information*B236751See ECN YDT Removed cross information from features section*C325936See ECN RUY Added pin definitions table, 52-pin PQFP package diagram and Pb-freeinformation*D393153See ECN YIM Added CY7C131-15JI to ordering informationAdded Pb-Free parts to ordering information:CY7C131-15JXI。

BZX84C18-V中文资料