AT90SC25672R中文资料

AT90SC6464C中文资料

Note:This is a summary document.A complete document is available under NDA.For more information,please contactyour local Atmel sales office.Features•Accurate Real-time Emulation of AT91SC,AT90SC and AT05SC Secure Microcontroller Products•Non-intrusive Emulation•Breakpoint Capability on any Hardware Instruction or Address •Emulation Allows Multiple Resets •Real-time Variables •Code Coverage•128-bit by 64K Deep Bus Trace •Watch Points and Breakpoints •Complex Triggering Capability •External Triggering Ability•Fast System Context Save and Retrieval •Integrated User Help•Hardware I/O Capability (USB,ISO,SPI &Contactless All Supported)•Advanced Scripting SupportNote:Not all features are available on the first release of the system.System Requirements•A PC Running Windows ®95/98/2000or Windows NT®•C-Spy ®Debugger from IAR Systems Installed (May be Obtained Directly from IARSystems)OverviewThe ATV1(Voyager),designed and manufactured by Atmel,provides a flexible emula-tion platform to support current and future Smart Card products.This platform has the intrinsic ability to support ARM ®(AT91SC),AVR ®(AT90SC)and HC05(AT05SC)based smart card products,and has been designed to be both flexible and easy to use.For maximum flexibility,the system has been designed to be upgraded easily.It has been engineered to support future device architectures.Switching to support other devices within a given core family is done simply by running a software utility that guides the user through the device update process –there is no need to change PCBs or jumper settings.For maximum usability,the system provides support for the IAR Systems C-Spy front-end.It also uses a proprietary configuration control application,which allows the developer not only to configure the hardware setup,but also to perform a variety of functions such as bus state analysis and code coverage.©Atmel Corporation 2002.Atmel Corporation makes no warranty for the use of its products,other than those expressly contained in the Com-pany’s standard warranty which is detailed in Atmel’s Terms and Conditions located on the Company’s web site.The Company assumes no responsibility for any errors which may appear in this document,reserves the right to change devices or specifications detailed herein at any time without notice,and does not make any commitment to update the information contained herein.No licenses to patents or other intellectual property of Atmel are granted by the Com-pany in connection with the sale of Atmel products,expressly or by implication.Atmel’s products are not authorized for use as critical compo-nents in life support devices or systems.Corporate Headquarters,2325Orchard Parkway,San Jose,CA 95131,TEL (408)441-0311,FAX (408)487-2600Atmel Colorado Springs,1150E.Cheyenne Mtn.Blvd.,Colorado Springs,CO 80906,TEL (719)576-3300,FAX (719)540-1759Atmel Grenoble,Avenue de Rochepleine,BP 123,38521Saint-Egreve Cedex,France,TEL (33)4-7658-3000,FAX (33)4-7658-3480Atmel Heilbronn,Theresienstrasse 2,POB 3535,D-74025Heilbronn,Germany,TEL (49)7131672594,FAX (49)7131672423Atmel Nantes,La Chantrerie,BP 70602,44306Nantes Cedex 3,France,TEL (33)024*******,FAX (33)024*******Atmel Rousset,Zone Industrielle,13106Rousset Cedex,France,TEL (33)4-4253-6000,FAX (33)4-4253-6001Atmel Smart Card ICs,Scottish Enterprise Technology Park,East Kilbride,Scotland G750QR,TEL (44)1355-803-000,FAX (44)1355-242-743on recycled paper.Figure 1.The ATV1Development SystemOrdering InformationOrder the ATV1using the following Atmel product name and part number.Contact DetailsContact your local Atmel sales office to order the Voyager Emulation Platform.Contact IAR’s Regional offices and distributors at or email info@ to order C-Spy Debugger.Power Switch SCADPT5and SPI Port (ISO7816Compatible)USB PortReset SwitchStatus Indicators1553BS–SMIC–03/02ATMEL ®and AVR ®are the registered trademarks of Atmel.ARM ®is the registered trademark of ARM Ltd.;Windows ®95/98/2000and Windows NT ®are the registered trademarks of Microsoft Corporation;C-Spy ®is the registered trademark of IAR Systems AB.Other terms and product names may be the trademarks of others.This datasheet has been download from: Datasheets for electronics components.。

AT91SAM7X256中文版

– 64K 字节 (AT91SAM7X256) – 32K 字节 (AT91SAM7X128)

• 内存控制器 (MC)

– 嵌入式 Flash 控制器, 中止状态和未对齐检测

• 复位控制器 (RSTC)

– 基于上电复位单元和经过工厂标定的低功耗掉电检测 – 提供外部信号整形和复位源状态

2. AT91SAM7X256 和 AT91SAM7X128 的配置比较

AT91SAM7X256 和 AT91SAM7X128 仅在存储器大小上有所差别。Table 2-1 是这两个设备的主 要配置差别。

Table 2-1. 配置差别

设备 AT91SAM7X256 AT91SAM7X128

Flash 256K 字节 128K 字节

欢迎访问本公司网站 /

免责声明

本资料英文版本来源于互联网,将其译成中文版本以便于中国广大ARM爱好者交 流、学习,请勿用于任何商业目的。

本文件为英文原本之非正式翻译,不保证翻译的真实性和准确性,同时声明文件以英 文版本为准。

由于嵌入式领域我国并无统一名称规范,大部分术语均直译,另有部分术语参考了 ATMEL 公司的 AT91SAM7S64 中文资料,由于译者对嵌入式领域理解的深度有限,难 免有疏漏和错误之处,也希望大家指出。

– 8 个完全可编程消息对象邮箱, 16 位时间标志计数器

• 一个同步串行控制器 (SSC)

– 每个接受器和发送器都有独立的时钟和帧同步信号 – 支持I²S 模拟接口, 支持分时复用 – 支持 32 位数据传输的高速连续数据流功能

• 两个通用同步/异步收发器 (USART)

– 独立的波特率发生器, 可以 IrDA 红外调制/解调 – 支持 ISO7816 T0/T1 智能卡, 硬件握手信号以及 RS485 – USART1 口支持全 Modem 线

L7820C中文资料

1/34November 2004s OUTPUT CURRENT TO 1.5AsOUTPUT VOLTAGES OF 5; 5.2; 6; 8; 8.5; 9; 10; 12; 15; 18; 24Vs THERMAL OVERLOAD PROTECTION s SHORT CIRCUIT PROTECTIONsOUTPUT TRANSITION SOA PROTECTIONDESCRIPTIONThe L7800 series of three-terminal positive regulators is available in TO-220, TO-220FP,TO-220FM, TO-3 and D 2PAK packages and several fixed output voltages, making it useful in a wide range of applications. These regulators can provide local on-card regulation, eliminating the distribution problems associated with single point regulation. Each type employs internal current limiting, thermal shut-down and safe area protection, making it essentially indestructible. If adequate heat sinking is provided, they can deliver over 1A output current. Although designed primarily as fixed voltage regulators, these devices can be used with external components to obtain adjustable voltage and currents.L7800SERIESPOSITIVE VOLTAGE REGULATORSL7800 SERIESTable 1: Absolute Maximum RatingsAbsolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these condition is not implied.Table 2: Thermal DataFigure 2: Schematic DiagramSymbol ParameterValue Unit V I DC Input Voltage for V O = 5 to 18V 35Vfor V O = 20, 24V40I O Output Current Internally Limited P tot Power DissipationInternally LimitedT stg Storage Temperature Range-65 to 150°C T opOperating Junction Temperature Range for L7800-55 to 150°C for L7800C0 to 150SymbolParameterD 2PAK TO-220TO-220FP TO-220FMTO-3Unit R thj-case Thermal Resistance Junction-case Max 35554°C/W R thj-ambThermal Resistance Junction-ambient Max62.550606035°C/WL7800 SERIES3/34Figure 3: Connection Diagram (top view)Table 3: Order Codes(*) Available in Tape & Reel with the suffix "-TR".TYPE TO-220(A Type)TO-220(C Type)TO-220(E Type)D 2PAK (A Type) (*)D 2PAK (C Type)(T & R)TO-220FPTO-220FMTO-3L7805L7805T L7805C L7805CV L7805C-V L7805CV1L7805CD2T L7805C-D2TRL7805CP L7805CF L7805CT L7852C L7852CV L7852CD2T L7852CP L7852CF L7852CT L7806L7806T L7806C L7806CV L7806C-V L7806CD2T L7806CP L7806CF L7806CT L7808L7808T L7808C L7808CV L7808C-V L7808CD2T L7808CP L7808CF L7808CT L7885C L7885CV L7885CD2T L7885CP L7885CF L7885CT L7809C L7809CV L7809C-VL7809CD2T L7809CP L7809CFL7809CT L7810C L7810CV L7810CD2T L7810CP L7812L7812T L7812C L7812CV L7812C-V L7812CD2T L7812CP L7812CF L7812CT L7815L7815T L7815C L7815CV L7815C-VL7815CD2T L7815CP L7815CF L7815CT L7818L7818T L7818C L7818CV L7818CD2T L7818CP L7818CF L7818CT L7820L7820T L7820C L7820CV L7820CD2T L7820CP L7820CF L7820CT L7824L7824T L7824CL7824CVL7824CD2TL7824CPL7824CFL7824CTL7800 SERIESFigure 4: Application CircuitsTEST CIRCUITSFigure 5: DC ParameterFigure 6: Load Regulation4/34L7800 SERIES5/34Figure 7: Ripple RejectionTable 4: Electrical Characteristics Of L7805 (refer to the test circuits, T J = -55 to 150°C, V I = 10V,I O = 500 mA, C I = 0.33 µF, C O = 0.1 µF unless otherwise specified).(*) Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must be taken into account separately. Pulse testing with low duty cycle is used.Symbol ParameterTest ConditionsMin.Typ.Max.Unit V O Output Voltage T J = 25°C 4.85 5.2V V O Output Voltage I O = 5 mA to 1 A P O ≤ 15WV I = 8 to 20 V 4.655 5.35V ∆V O (*)Line Regulation V I = 7 to 25 V T J = 25°C 350mVV I = 8 to 12 V T J = 25°C 125∆V O (*)Load Regulation I O = 5 mA to 1.5 A T J = 25°C 100mV I O = 250 to 750 mA T J = 25°C25I d Quiescent Current T J = 25°C 6mA ∆I dQuiescent Current ChangeI O = 5 mA to 1 A 0.5mA V I = 8 to 25 V0.8∆V O /∆T Output Voltage Drift I O = 5 mA0.6mV/°C eN Output Noise Voltage B =10Hz to 100KHz T J = 25°C40µV/V O SVR Supply Voltage Rejection V I = 8 to 18 V f = 120Hz68dB V d Dropout Voltage I O = 1 A T J = 25°C2 2.5V R O Output Resistance f = 1 KHz 17m ΩI sc Short Circuit Current V I = 35 V T J = 25°C0.75 1.2A I scpShort Circuit Peak CurrentT J = 25°C1.32.23.3AL7800 SERIES6/34Table 5: Electrical Characteristics Of L7806 (refer to the test circuits, T J = -55 to 150°C, V I = 11V,I O = 500 mA, C I = 0.33 µF, C O = 0.1 µF unless otherwise specified).(*) Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must be taken into account separately. Pulse testing with low duty cycle is used.Table 6: Electrical Characteristics Of L7808 (refer to the test circuits, T J = -55 to 150°C, V I = 14V,I O = 500 mA, C I = 0.33 µF, C O = 0.1 µF unless otherwise specified).(*) Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must be taken into account separately. Pulse testing with low duty cycle is used.Symbol ParameterTest ConditionsMin.Typ.Max.Unit V O Output Voltage T J = 25°C 5.756 6.25V V O Output Voltage I O = 5 mA to 1 A P O ≤ 15WV I = 9 to 21 V 5.6566.35V ∆V O (*)Line Regulation V I = 8 to 25 V T J = 25°C 60mVV I = 9 to 13 V T J = 25°C 30∆V O (*)Load Regulation I O = 5 mA to 1.5 A T J = 25°C 100mV I O = 250 to 750 mA T J = 25°C30I d Quiescent Current T J = 25°C 6mA ∆I dQuiescent Current ChangeI O = 5 mA to 1 A 0.5mA V I = 9 to 25 V0.8∆V O /∆T Output Voltage Drift I O = 5 mA0.7mV/°C eN Output Noise Voltage B =10Hz to 100KHz T J = 25°C40µV/V O SVR Supply Voltage Rejection V I = 9 to 19 V f = 120Hz65dB V d Dropout Voltage I O = 1 A T J = 25°C2 2.5V R O Output Resistance f = 1 KHz 19m ΩI sc Short Circuit Current V I = 35 V T J = 25°C0.75 1.2A I scpShort Circuit Peak CurrentT J = 25°C1.32.23.3A Symbol ParameterTest ConditionsMin.Typ.Max.Unit V O Output Voltage T J = 25°C 7.788.3V V O Output Voltage I O = 5 mA to 1 A P O ≤ 15WV I = 11.5 to 23 V 7.688.4V ∆V O (*)Line Regulation V I = 10.5 to 25 V T J = 25°C 80mVV I = 11 to 17 V T J = 25°C 40∆V O (*)Load Regulation I O = 5 mA to 1.5 A T J = 25°C 100mV I O = 250 to 750 mA T J = 25°C40I d Quiescent Current T J = 25°C 6mA ∆I dQuiescent Current ChangeI O = 5 mA to 1 A 0.5mA V I = 11.5 to 25 V0.8∆V O /∆T Output Voltage Drift I O = 5 mA1mV/°C eN Output Noise Voltage B =10Hz to 100KHz T J = 25°C 40µV/V O SVR Supply Voltage Rejection V I = 11.5 to 21.5 V f = 120Hz62dB V d Dropout Voltage I O = 1 A T J = 25°C2 2.5V R O Output Resistance f = 1 KHz 16m ΩI sc Short Circuit Current V I = 35 V T J = 25°C0.75 1.2A I scpShort Circuit Peak CurrentT J = 25°C1.32.23.3AL7800 SERIES7/34Table 7: Electrical Characteristics Of L7812 (refer to the test circuits, T J = -55 to 150°C, V I = 19V,I O = 500 mA, C I = 0.33 µF, C O = 0.1 µF unless otherwise specified).(*) Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must be taken into account separately. Pulse testing with low duty cycle is used.Table 8: Electrical Characteristics Of L7815 (refer to the test circuits, T J = -55 to 150°C, V I = 23V,I O = 500 mA, C I = 0.33 µF, C O = 0.1 µF unless otherwise specified).(*) Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must be taken into account separately. Pulse testing with low duty cycle is used.Symbol ParameterTest ConditionsMin.Typ.Max.Unit V O Output Voltage T J = 25°C 11.51212.5V V O Output Voltage I O = 5 mA to 1 A P O ≤ 15WV I = 15.5 to 27 V 11.41212.6V ∆V O (*)Line Regulation V I = 14.5 to 30 V T J = 25°C 120mVV I = 16 to 22 V T J = 25°C 60∆V O (*)Load Regulation I O = 5 mA to 1.5 A T J = 25°C 100mV I O = 250 to 750 mA T J = 25°C60I d Quiescent Current T J = 25°C 6mA ∆I dQuiescent Current ChangeI O = 5 mA to 1 A 0.5mA V I = 15 to 30 V0.8∆V O /∆T Output Voltage Drift I O = 5 mA1.5mV/°C eN Output Noise Voltage B =10Hz to 100KHz T J = 25°C 40µV/V O SVR Supply Voltage Rejection V I = 15 to 25 V f = 120Hz61dB V d Dropout Voltage I O = 1 A T J = 25°C2 2.5V R O Output Resistance f = 1 KHz 18m ΩI sc Short Circuit Current V I = 35 V T J = 25°C0.75 1.2A I scpShort Circuit Peak CurrentT J = 25°C1.32.23.3A Symbol ParameterTest ConditionsMin.Typ.Max.Unit V O Output Voltage T J = 25°C 14.41515.6V V O Output Voltage I O = 5 mA to 1 A P O ≤ 15WV I = 18.5 to 30 V 14.251515.75V ∆V O (*)Line Regulation V I = 17.5 to 30 V T J = 25°C 150mVV I = 20 to 26 V T J = 25°C 75∆V O (*)Load Regulation I O = 5 mA to 1.5 A T J = 25°C 150mV I O = 250 to 750 mA T J = 25°C75I d Quiescent Current T J = 25°C 6mA ∆I dQuiescent Current ChangeI O = 5 mA to 1 A 0.5mA V I = 18.5 to 30 V0.8∆V O /∆T Output Voltage Drift I O = 5 mA1.8mV/°C eN Output Noise Voltage B =10Hz to 100KHz T J = 25°C 40µV/V O SVR Supply Voltage Rejection V I = 18.5 to 28.5 V f = 120Hz60dB V d Dropout Voltage I O = 1 A T J = 25°C2 2.5V R O Output Resistance f = 1 KHz 19m ΩI sc Short Circuit Current V I = 35 V T J = 25°C0.75 1.2A I scpShort Circuit Peak CurrentT J = 25°C1.32.23.3AL7800 SERIES8/34Table 9: Electrical Characteristics Of L7818 (refer to the test circuits, T J = -55 to 150°C, V I = 26V,I O = 500 mA, C I = 0.33 µF, C O = 0.1 µF unless otherwise specified).(*) Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must be taken into account separately. Pulse testing with low duty cycle is used.Table 10: Electrical Characteristics Of L7820 (refer to the test circuits, T J = -55 to 150°C, V I = 28V,I O = 500 mA, C I = 0.33 µF, C O = 0.1 µF unless otherwise specified).(*) Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must be taken into account separately. Pulse testing with low duty cycle is used.Symbol ParameterTest ConditionsMin.Typ.Max.Unit V O Output Voltage T J = 25°C 17.31818.7V V O Output Voltage I O = 5 mA to 1 A P O ≤ 15WV I = 22 to 33 V 17.11818.9V ∆V O (*)Line Regulation V I = 21 to 33 V T J = 25°C 180mVV I = 24 to 30 V T J = 25°C 90∆V O (*)Load Regulation I O = 5 mA to 1.5 A T J = 25°C 180mV I O = 250 to 750 mA T J = 25°C90I d Quiescent Current T J = 25°C 6mA ∆I dQuiescent Current ChangeI O = 5 mA to 1 A 0.5mA V I = 22 to 33 V0.8∆V O /∆T Output Voltage Drift I O = 5 mA2.3mV/°C eN Output Noise Voltage B =10Hz to 100KHz T J = 25°C 40µV/V O SVR Supply Voltage Rejection V I = 22 to 32 V f = 120Hz59dB V d Dropout Voltage I O = 1 A T J = 25°C2 2.5V R O Output Resistance f = 1 KHz 22m ΩI sc Short Circuit Current V I = 35 V T J = 25°C0.75 1.2A I scpShort Circuit Peak CurrentT J = 25°C1.32.23.3A Symbol ParameterTest ConditionsMin.Typ.Max.Unit V O Output Voltage T J = 25°C 19.22020.8V V O Output Voltage I O = 5 mA to 1 A P O ≤ 15WV I = 24 to 35 V 192021V ∆V O (*)Line Regulation V I = 22.5 to 35 V T J = 25°C 200mVV I = 26 to 32 V T J = 25°C 100∆V O (*)Load Regulation I O = 5 mA to 1.5 A T J = 25°C 200mV I O = 250 to 750 mA T J = 25°C100I d Quiescent Current T J = 25°C 6mA ∆I dQuiescent Current ChangeI O = 5 mA to 1 A 0.5mA V I = 24 to 35 V0.8∆V O /∆T Output Voltage Drift I O = 5 mA2.5mV/°C eN Output Noise Voltage B =10Hz to 100KHz T J = 25°C 40µV/V O SVR Supply Voltage Rejection V I = 24 to 35 V f = 120Hz58dB V d Dropout Voltage I O = 1 A T J = 25°C2 2.5V R O Output Resistance f = 1 KHz 24m ΩI sc Short Circuit Current V I = 35 V T J = 25°C0.75 1.2A I scpShort Circuit Peak CurrentT J = 25°C1.32.23.3AL7800 SERIES9/34Table 11: Electrical Characteristics Of L7824 (refer to the test circuits, T J = -55 to 150°C, V I = 33V,I O = 500 mA, C I = 0.33 µF, C O = 0.1 µF unless otherwise specified).(*) Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must be taken into account separately. Pulse testing with low duty cycle is used.Table 12: Electrical Characteristics Of L7805C (refer to the test circuits, T J = 0 to 125°C, V I = 10V,I O = 500 mA, C I = 0.33 µF, C O = 0.1 µF unless otherwise specified).(*) Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must be taken into account separately. Pulse testing with low duty cycle is used.Symbol ParameterTest ConditionsMin.Typ.Max.Unit V O Output Voltage T J =25°C 232425V V O Output Voltage I O = 5 mA to 1 A P O ≤ 15WV I = 28 to 38 V 22.82425.2V ∆V O (*)Line Regulation V I = 27 to 38 V T J = 25°C 240mVV I = 30 to 36 V T J = 25°C 120∆V O (*)Load Regulation I O = 5 mA to 1.5 A T J = 25°C 240mV I O = 250 to 750 mA T J = 25°C120I d Quiescent Current T J = 25°C 6mA ∆I dQuiescent Current ChangeI O = 5 mA to 1 A 0.5mA V I = 28 to 38 V0.8∆V O /∆T Output Voltage Drift I O = 5 mA3mV/°C eN Output Noise Voltage B =10Hz to 100KHz T J = 25°C 40µV/V O SVR Supply Voltage Rejection V I = 28 to 38 V f = 120Hz56dB V d Dropout Voltage I O = 1 A T J = 25°C2 2.5V R O Output Resistance f = 1 KHz 28m ΩI sc Short Circuit Current V I = 35 V T J = 25°C0.75 1.2A I scpShort Circuit Peak CurrentT J = 25°C1.32.23.3A Symbol ParameterTest ConditionsMin.Typ.Max.Unit V O Output Voltage T J = 25°C 4.85 5.2V V O Output Voltage I O = 5 mA to 1 A P O ≤ 15WV I = 7 to 20 V 4.755 5.25V ∆V O (*)Line Regulation V I = 7 to 25 V T J = 25°C 3100mVV I = 8 to 12 VT J = 25°C 150∆V O (*)Load Regulation I O = 5 mA to 1.5 A T J = 25°C 100mV I O = 250 to 750 mA T J = 25°C50I d Quiescent Current T J = 25°C 8mA ∆I dQuiescent Current ChangeI O = 5 mA to 1 A 0.5mA V I = 7 to 25 V0.8∆V O /∆T Output Voltage Drift I O = 5 mA-1.1mV/°C eN Output Noise Voltage B =10Hz to 100KHz T J = 25°C40µV/V O SVR Supply Voltage Rejection V I = 8 to 18 V f = 120Hz62dB V d Dropout Voltage I O = 1 A T J = 25°C2V R O Output Resistance f = 1 KHz 17m ΩI sc Short Circuit Current V I = 35 V T J = 25°C 0.75A I scpShort Circuit Peak CurrentT J = 25°C2.2AL7800 SERIES10/34Table 13: Electrical Characteristics Of L7852C (refer to the test circuits, T J = 0 to 125°C, V I = 10V,I O = 500 mA, C I = 0.33 µF, C O = 0.1 µF unless otherwise specified).(*) Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must be taken into account separately. Pulse testing with low duty cycle is used.Table 14: Electrical Characteristics Of L7806C (refer to the test circuits, T J = 0 to 125°C, V I = 11V,I O = 500 mA, C I = 0.33 µF, C O = 0.1 µF unless otherwise specified).(*) Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must be taken into account separately. Pulse testing with low duty cycle is used.Symbol ParameterTest ConditionsMin.Typ.Max.Unit V O Output Voltage T J = 25°C 5.0 5.2 5.4V V O Output Voltage I O = 5 mA to 1 A P O ≤ 15WV I = 8 to 20 V 4.955.2 5.45V ∆V O (*)Line Regulation V I = 7 to 25 V T J = 25°C 3105mVV I = 8 to 12 V T J = 25°C 152∆V O (*)Load Regulation I O = 5 mA to 1.5 A T J = 25°C 105mV I O = 250 to 750 mA T J = 25°C52I d Quiescent Current T J = 25°C 8mA ∆I dQuiescent Current ChangeI O = 5 mA to 1 A 0.5mA V I = 7 to 25 V1.3∆V O /∆T Output Voltage Drift I O = 5 mA-1mV/°C eN Output Noise Voltage B =10Hz to 100KHz T J = 25°C42µV/V O SVR Supply Voltage Rejection V I = 8 to 18 V f = 120Hz61dB V d Dropout Voltage I O = 1 A T J = 25°C2V R O Output Resistance f = 1 KHz 17m ΩI sc Short Circuit Current V I = 35 V T J = 25°C 0.75A I scpShort Circuit Peak CurrentT J = 25°C2.2A Symbol ParameterTest ConditionsMin.Typ.Max.Unit V O Output Voltage T J = 25°C 5.756 6.25V V O Output Voltage I O = 5 mA to 1 A P O ≤ 15WV I = 8 to 21 V 5.766.3V ∆V O (*)Line Regulation V I = 8 to 25 V T J = 25°C 120mVV I = 9 to 13 V T J = 25°C 60∆V O (*)Load Regulation I O = 5 mA to 1.5 A T J = 25°C 120mV I O = 250 to 750 mA T J = 25°C60I d Quiescent Current T J = 25°C 8mA ∆I dQuiescent Current ChangeI O = 5 mA to 1 A 0.5mA V I = 8 to 25 V1.3∆V O /∆T Output Voltage Drift I O = 5 mA-0.8mV/°C eN Output Noise Voltage B =10Hz to 100KHz T J = 25°C45µV/V O SVR Supply Voltage Rejection V I = 9 to 19 V f = 120Hz59dB V d Dropout Voltage I O = 1 A T J = 25°C2V R O Output Resistance f = 1 KHz 19m ΩI sc Short Circuit Current V I = 35 V T J = 25°C 0.55A I scpShort Circuit Peak CurrentT J = 25°C2.2A(*) Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must be taken into account separately. Pulse testing with low duty cycle is used.Table 16: Electrical Characteristics Of L7885C (refer to the test circuits, T J = 0 to 125°C, V I = 14.5V,I O = 500 mA, C I = 0.33 µF, C O = 0.1 µF unless otherwise specified).(*) Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must be taken into account separately. Pulse testing with low duty cycle is used.Symbol ParameterTest ConditionsMin.Typ.Max.Unit V O Output Voltage T J = 25°C 7.788.3V V O Output Voltage I O = 5 mA to 1 A P O ≤ 15WV I = 10.5 to 25 V 7.688.4V ∆V O (*)Line Regulation V I = 10.5 to 25 V T J = 25°C 160mVV I = 11 to 17 V T J = 25°C 80∆V O (*)Load Regulation I O = 5 mA to 1.5 A T J = 25°C 160mV I O = 250 to 750 mA T J = 25°C80I d Quiescent Current T J = 25°C 8mA ∆I dQuiescent Current ChangeI O = 5 mA to 1 A 0.5mA V I = 10.5 to 25 V1∆V O /∆T Output Voltage Drift I O = 5 mA-0.8mV/°C eN Output Noise Voltage B =10Hz to 100KHz T J = 25°C 52µV/V O SVR Supply Voltage Rejection V I = 11.5 to 21.5 V f = 120Hz56dB V d Dropout Voltage I O = 1 A T J = 25°C2V R O Output Resistance f = 1 KHz 16m ΩI sc Short Circuit Current V I = 35 V T J = 25°C 0.45A I scpShort Circuit Peak CurrentT J = 25°C2.2A Symbol ParameterTest ConditionsMin.Typ.Max.Unit V O Output Voltage T J = 25°C 8.28.58.8V V O Output Voltage I O = 5 mA to 1 A P O ≤ 15WV I = 11 to 26 V 8.18.58.9V ∆V O (*)Line Regulation V I = 11 to 27 V T J = 25°C 160mVV I = 11.5 to 17.5 V T J = 25°C 80∆V O (*)Load Regulation I O = 5 mA to 1.5 A T J = 25°C 160mV I O = 250 to 750 mA T J = 25°C80I d Quiescent Current T J = 25°C 8mA ∆I dQuiescent Current ChangeI O = 5 mA to 1 A 0.5mA V I = 11 to 27 V1∆V O /∆T Output Voltage Drift I O = 5 mA-0.8mV/°C eN Output Noise Voltage B =10Hz to 100KHz T J = 25°C 55µV/V O SVR Supply Voltage Rejection V I = 12 to 22 V f = 120Hz56dB V d Dropout Voltage I O = 1 A T J = 25°C2V R O Output Resistance f = 1 KHz 16m ΩI sc Short Circuit Current V I = 35 V T J = 25°C 0.45A I scpShort Circuit Peak CurrentT J = 25°C2.2A(*) Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must be taken into account separately. Pulse testing with low duty cycle is used.Table 18: Electrical Characteristics Of L7810C (refer to the test circuits, T J = 0 to 125°C, V I = 16V,I O = 500 mA, C I = 0.33 µF, C O = 0.1 µF unless otherwise specified).(*) Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must be taken into account separately. Pulse testing with low duty cycle is used.Symbol ParameterTest ConditionsMin.Typ.Max.Unit V O Output Voltage T J = 25°C 8.6499.36V V O Output Voltage I O = 5 mA to 1 A P O ≤ 15WV I = 11.5 to 26 V 8.5599.45V ∆V O (*)Line Regulation V I = 11.5 to 26 V T J = 25°C 180mVV I = 12 to 18 V T J = 25°C 90∆V O (*)Load Regulation I O = 5 mA to 1.5 A T J = 25°C 180mV I O = 250 to 750 mA T J = 25°C90I d Quiescent Current T J = 25°C 8mA ∆I dQuiescent Current ChangeI O = 5 mA to 1 A 0.5mA V I = 11.5 to 26 V1∆V O /∆T Output Voltage Drift I O = 5 mA-1mV/°C eN Output Noise Voltage B =10Hz to 100KHz T J = 25°C 70µV/V O SVR Supply Voltage Rejection V I = 12 to 23 V f = 120Hz55dB V d Dropout Voltage I O = 1 A T J = 25°C2V R O Output Resistance f = 1 KHz 17m ΩI sc Short Circuit Current V I = 35 V T J = 25°C 0.40A I scpShort Circuit Peak CurrentT J = 25°C2.2A Symbol ParameterTest ConditionsMin.Typ.Max.Unit V O Output Voltage T J = 25°C 9.61010.4V V O Output Voltage I O = 5 mA to 1 A P O ≤ 15WV I = 12.5 to 26 V 9.51010.5V ∆V O (*)Line Regulation V I = 12.5 to 26 V T J = 25°C 200mVV I = 13.5 to 19 V T J = 25°C 100∆V O (*)Load Regulation I O = 5 mA to 1.5 A T J = 25°C 200mV I O = 250 to 750 mA T J = 25°C100I d Quiescent Current T J = 25°C 8mA ∆I dQuiescent Current ChangeI O = 5 mA to 1 A 0.5mA V I = 12.5 to 26 V1∆V O /∆T Output Voltage Drift I O = 5 mA-1mV/°C eN Output Noise Voltage B =10Hz to 100KHz T J = 25°C 70µV/V O SVR Supply Voltage Rejection V I = 13 to 23 V f = 120Hz55dB V d Dropout Voltage I O = 1 A T J = 25°C2V R O Output Resistance f = 1 KHz 17m ΩI sc Short Circuit Current V I = 35 V T J = 25°C 0.40A I scpShort Circuit Peak CurrentT J = 25°C2.2A(*) Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must be taken into account separately. Pulse testing with low duty cycle is used.Table 20: Electrical Characteristics Of L7815C (refer to the test circuits, T J = 0 to 125°C, V I = 23V,I O = 500 mA, C I = 0.33 µF, C O = 0.1 µF unless otherwise specified).(*) Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must be taken into account separately. Pulse testing with low duty cycle is used.Symbol ParameterTest ConditionsMin.Typ.Max.Unit V O Output Voltage T J = 25°C 11.51212.5V V O Output Voltage I O = 5 mA to 1 A P O ≤ 15WV I = 14.5 to 27 V 11.41212.6V ∆V O (*)Line Regulation V I = 14.5 to 30 V T J = 25°C 240mVV I = 16 to 22 V T J = 25°C 120∆V O (*)Load Regulation I O = 5 mA to 1.5 A T J = 25°C 240mV I O = 250 to 750 mA T J = 25°C120I d Quiescent Current T J = 25°C 8mA ∆I dQuiescent Current ChangeI O = 5 mA to 1 A 0.5mA V I = 14.5 to 30 V1∆V O /∆T Output Voltage Drift I O = 5 mA-1mV/°C eN Output Noise Voltage B =10Hz to 100KHz T J = 25°C 75µV/V O SVR Supply Voltage Rejection V I = 15 to 25 V f = 120Hz55dB V d Dropout Voltage I O = 1 A T J = 25°C2V R O Output Resistance f = 1 KHz 18m ΩI sc Short Circuit Current V I = 35 V T J = 25°C 0.35A I scpShort Circuit Peak CurrentT J = 25°C2.2A Symbol ParameterTest ConditionsMin.Typ.Max.Unit V O Output Voltage T J = 25°C 14.51515.6V V O Output Voltage I O = 5 mA to 1 A P O ≤ 15WV I = 17.5 to 30 V 14.251515.75V ∆V O (*)Line Regulation V I = 17.5 to 30 V T J = 25°C 300mVV I = 20 to 26 V T J = 25°C 150∆V O (*)Load Regulation I O = 5 mA to 1.5 A T J = 25°C 300mV I O = 250 to 750 mA T J = 25°C150I d Quiescent Current T J = 25°C 8mA ∆I dQuiescent Current ChangeI O = 5 mA to 1 A 0.5mA V I = 17.5 to 30 V1∆V O /∆T Output Voltage Drift I O = 5 mA-1mV/°C eN Output Noise Voltage B =10Hz to 100KHz T J = 25°C 90µV/V O SVR Supply Voltage Rejection V I = 18.5 to 28.5 V f = 120Hz54dB V d Dropout Voltage I O = 1 A T J = 25°C2V R O Output Resistance f = 1 KHz 19m ΩI sc Short Circuit Current V I = 35 V T J = 25°C 0.23A I scpShort Circuit Peak CurrentT J = 25°C2.2A(*) Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must be taken into account separately. Pulse testing with low duty cycle is used.Table 22: Electrical Characteristics Of L7820C (refer to the test circuits, T J = 0 to 125°C, V I = 28V,I O = 500 mA, C I = 0.33 µF, C O = 0.1 µF unless otherwise specified).(*) Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must be taken into account separately. Pulse testing with low duty cycle is used.Symbol ParameterTest ConditionsMin.Typ.Max.Unit V O Output Voltage T J = 25°C 17.31818.7V V O Output Voltage I O = 5 mA to 1 A P O ≤ 15WV I = 21 to 33 V 17.11818.9V ∆V O (*)Line Regulation V I = 21 to 33 V T J = 25°C 360mVV I = 24 to 30 V T J = 25°C 180∆V O (*)Load Regulation I O = 5 mA to 1.5 A T J = 25°C 360mV I O = 250 to 750 mA T J = 25°C180I d Quiescent Current T J = 25°C 8mA ∆I dQuiescent Current ChangeI O = 5 mA to 1 A 0.5mA V I = 21 to 33 V1∆V O /∆T Output Voltage Drift I O = 5 mA-1mV/°C eN Output Noise Voltage B =10Hz to 100KHz T J = 25°C 110µV/V O SVR Supply Voltage Rejection V I = 22 to 32 V f = 120Hz53dB V d Dropout Voltage I O = 1 A T J = 25°C2V R O Output Resistance f = 1 KHz 22m ΩI sc Short Circuit Current V I = 35 V T J = 25°C 0.20A I scpShort Circuit Peak CurrentT J = 25°C2.1A Symbol ParameterTest ConditionsMin.Typ.Max.Unit V O Output Voltage T J = 25°C 19.22020.8V V O Output Voltage I O = 5 mA to 1 A P O ≤ 15WV I = 23 to 35 V 192021V ∆V O (*)Line Regulation V I = 22.5 to 35 V T J = 25°C 400mVV I = 26 to 32 V T J = 25°C 200∆V O (*)Load Regulation I O = 5 mA to 1.5 A T J = 25°C 400mV I O = 250 to 750 mA T J = 25°C200I d Quiescent Current T J = 25°C 8mA ∆I dQuiescent Current ChangeI O = 5 mA to 1 A 0.5mA V I = 23 to 35 V1∆V O /∆T Output Voltage Drift I O = 5 mA-1mV/°C eN Output Noise Voltage B =10Hz to 100KHz T J = 25°C 150µV/V O SVR Supply Voltage Rejection V I = 24 to 35 V f = 120Hz52dB V d Dropout Voltage I O = 1 A T J = 25°C2V R O Output Resistance f = 1 KHz 24m ΩI sc Short Circuit Current V I = 35 V T J = 25°C 0.18A I scpShort Circuit Peak CurrentT J = 25°C2.1A。

AT90SC资料

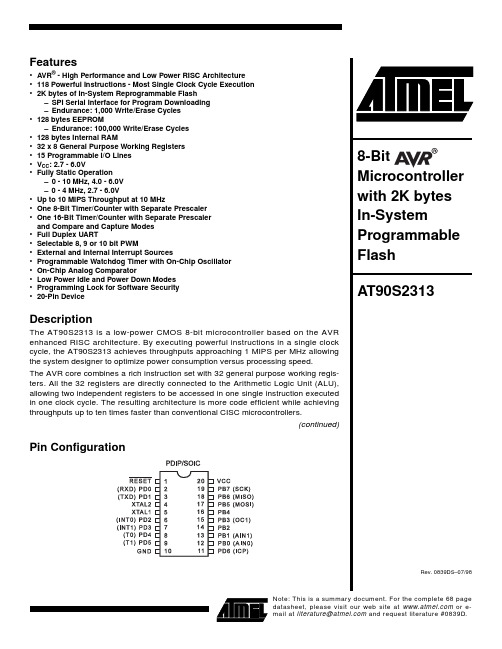

1Features•High-performance, Low-power 8-bit AVR ® RISC Architecture –120 Powerful Instructions–Most Single Clock Cycle Execution •Up to 64K Bytes Flash Program Memory –Endurance: 10K Write/Erase Cycles •Up to 64K Bytes EEPROM User Memory –Endurance: 250K Write/Erase Cycles •Up to 2.5K Bytes RAM •Cryptoprocessor–Pre-programmed Functions for Cryptography and Authentication •Supervisor Mode (Memory Management)•One or Two ISO 7816 I/O Ports •Random Number Generator •One or Two 16-bit Timers•2-level, 6-vector Interrupt Controller •Security Features–Power-down Protection–Low-frequency and High-frequency Protection –Logical Scrambling on Program Code •Low-power Idle and Power-down Modes •Bond Pad Locations Conform to ISO 7816•V CC : 3.0V ± 10%, 5.0V ± 10%DescriptionThe AT90SC series is a low-power, high-performance, 8-bit microcontroller with Flash program memory and EEPROM data memory, based on the AVR RISC architecture.By executing powerful instructions in a single clock cycle, the AT90SC achieves throughputs close to 1 MIPS per MHz. Its Harvard architecture includes 32 general-purpose working registers directly connected to the ALU, allowing two independent registers to be accessed in one single instruction executed in one clock cycle.Some products in the AT90SC family feature a cryptoprocessor: a 16-bit crypto engine dedicated to performing fast encryption or authentication functions (see table below). Additional security features include power and frequency protection logic, log-ical scrambling on program data and addresses, and memory accesses controlled by a supervisor mode.The AT90SC family provides up to 128K bytes of Atmel ’s high-density, nonvolatile memory technology. The on-chip downloadable Flash allows the program memory to be reprogrammed in-system. This technology combined with the versatile 8-bit CPU on a monolithic chip provides a highly flexible and cost-effective solution to many smart card applications. Table 1. The AT90SC FamilyDevice Program Memory Flash BytesUser Memory EEPROM BytesRAM BytesCrypto-processorI/O Ports A T90SC1616C 16K 16K 1K Y es 2A T90SC323232K 32K 1.5K No 1A T90SC3232C 32K 32K 1K Y es 1A T90SC6464C64K64K2.5KY es2AT90SC2Block DiagramNote: 1.Only available on products featuring a cryptoprocessor.2.Only available on products not featuring a cryptoprocessor.3.Currently available only on A T90SC1616C and A T90SC6464C.Pin DescriptionVCCSupply voltage.GND Ground.RSTReset input. A low level on this pin for two clock cycles while the AT90SC is running resets the device.This pin includes an internal pull-up resistor.CLKClock input to internal clock operating circuit.This pin includes an internal pull-up resistor.IN/OUTOn products with a single IN/OUT pin, IN/OUT is a single bit open drain bi-directional I/O port. This bi-directional pin includes a pull-up resistor.Products with a second I/O port can be configured as open drain with pull-up or as a true CMOS I/O port.AT90SC38-bit AVR RISC Microcontroller CPUThe AVR uses a Harvard architecture concept with sepa-rate memories and buses for program and data. The program memory is accessed with a two stage pipeline.While one instruction is being executed, the next instruction is prefetched from the program memory. This concept enables instructions to be executed in every clock cycle.The fast-access register file concept contains 32 x 8 gen-eral purpose working registers with a single clock cycle access time. This means that during one single clock cycle,one ALU operation is executed. Two operands are output from the register file, the operation is executed, and the result is stored back in the register file in one clock cycle.The timer and other I/O functions are located in the I/O memory space. The 64 addresses of the I/O memory space can be accessed directly as I/O registers or as memory space.Memory OrganizationThe AT90SC microcontrollers have the following memory organization as shown in Figures 1 and 2.Program memory:•16-bit addressable EEPROM user memory •16-bit addressable Flash program memory Data memory:•8-bit addressable EEPROM user memory •8-bit addressable SRAM shared between AVR and crypto engine •8-bit registers addressable as data memoryThe EEPROM is shared between program memory and data memory depending on the mode. The portion of EEPROM dedicated to each function is flexible and varies according to the application.Program memory is read-only in normal operation mode.Both Flash and EEPROM memory locations are directly addressable. The EEPROM memory locations follow the Flash memory in the program address space.Program MemoryThe AT90SC microcontroller has separate address spaces for program memory and data memory. Up to 64K bytes of Flash program memory are available. Figure 1 shows the program memory.Data MemoryThe AT90SC can directly address up to 64K bytes of data memory. The LOAD and STORE instructions access the whole data memory.The AT90SC family also features 96 bytes of register and I/O space and up to 2.5K bytes of SRAM.The I/O space of the RAM can be accessed by direct addressing.The 128-byte last page of the EEPROM user memory is an OTP memory (64 bytes) and bit addressable memory (64bytes).Figure 1. The AT90SC Program MemoryFigure 2. The AT90SC Data Memory元器件交易网AT90SC4Flash Program Memory•Page size of 128 bytes•Minimum endurance of 10K write/erase cycles •Data retention for a minimum of 40 yearsThe AT90SC contains up to 64K bytes of downloadable Flash memory for program storage. Since all instructions are 16-bit words, the Flash is organized as 32K x 16. The Flash memory is read-only except during the program download mode. This mode is selected by setting a bit in the memory control I/O register.Once the Flash memory is loaded, a security feature dis-ables the download function, making the writing of the Flash impossible.EEPROM User Memory•Erasure and Writing:- Byte-by-byte - Bit mode- Page mode (128 bytes per page)•Minimum endurance of 250K write/erase cycles •Data retention for a minimum of 40 yearsThe user memory is organized as up to 32K x 16. A write mode bit in the memory control register selects byte by byte or page mode. During the write cycle, a bit is set in the memory control register, disabling pending write opera-tions. When the write cycle is finished, this bit is cleared and an interrupt request is generated.In addition, the AT90SC features a pseudo bit mode which allows individual bits to be overwritten (one to zero).Bit Addressable MemoryThe 64 bytes of bit addressable memory are found in the last 128-byte page of the EEPROM address space and represent the first 64 bytes of this page.OTP MemoryThe 64 bytes of OTP (One-Time Programmable) Memory are found in the last 128-byte page of the EEPROM address space and represent the last 64 bytes of this page.CryptoprocessorThe cryptoprocessor is a 16-bit crypto engine dedicated to performing fast encryption or authentication functions. It isbased on a parallel RISC architecture allowing most instructions to be performed in a single clock cycle. The crypto engine can run in parallel with the microcontroller.An internal 16 x 16 multiplier provides 32-bit results within one cycle.The cryptoprocessor runs on its own internal clock.The cryptoprocessor ROM stores the program code which contains the following catalog of functions: •Reset and self test•Random Number Generation•Exponentiation with CRT (241 to 1024)•Exponentiation without CRT (241 to 1024)•DSARAM Memory SharingThe cryptoprocessor and the AVR share the RAM memory as follows: when the cryptoprocessor is inactive, the entire RAM can be accessed by the CPU. When the cryptopro-cessor is active, the shared RAM is not accessible by the CPU.Operational ModesThe AT90SC features two operational modes:• A supervisor mode with a privileged access to data, active when code is executed from the supervisor memory • A user mode with data access restrictions, active when code is executed from EEPROM user memory The supervisor and user locations are programmed in I/O registers.In user mode, direct read and write access to I/O registers and EEPROM is not allowed. Furthermore, a programma-ble zone in the RAM can be reserved for supervisor mode.Any attempt to access the I/O, EEPROM or reserved RAM area generates a maskable interrupt.Also, any jump to the supervisor zone in user mode gener-ates a non-maskable security interrupt. The AT90SC provides a supervisor call instruction to branch at a defined vector address of the supervisor zone.This powerful hardware solution is specially designed to ensure full separation between applications. It provides secure protection against program dumping and secure data access control.元器件交易网AT90SC5Security FeaturesFor security reasons the following list is not exhaustive.•Shipping and Initialization are protected by a Transport Code •Power-down/up protection•Low-frequency protection against static analysis •High-frequency protection against intrusion •Unique serial number •Supervisor mode •Secured test structure •Logical scrambling •Secure layoutISO 7816 I/O PortsThe ISO 7816 I/O pins are controlled by the CPU. They can be configured to generate an interrupt on:- Low level - Positive edge - Negative edge- Positive or negative edgeInterrupt ControllerThe AT90SC has a total of six interrupt vectors: security,I/O pins 0 and 1, timer, EEPROM end of write cycle and a cryptoprocessor interrupt.Each of these interrupt sources can be individually enabled or disabled by setting or clearing a bit in the Interrupt Mask Register located in the I/O memory space. This register also contains a global disable bit which disables all inter-rupts at once.One priority level can be programmed in the Interrupt Prior-ity register. A second priority level is given by the vector number.The interrupt controller is able to memorize interrupts. It sends them to the microcontroller in the correct order according to their priority level.Reduced Power ModeTo exploit the power savings for smart cards available in CMOS circuitry, Atmel ’s microcontrollers have two soft-ware-invoked reduced power modes.Idle ModeDuring Idle Mode, the CPU is disabled while all on-chip peripherals (RAM, I/O registers, timer and serial port)remain active. This mode is invoked by a SLEEP instruc-tion and by an enabled bit in an I/O register. Idle Mode can be terminated by any enabled interrupt or by a hardware reset.If a reset occurs during sleep mode, the CPU awakes and executes from the reset vector.If an interrupt occurs, the CPU awakes and executes the interrupt routine, and resumes execution from the instruc-tion following SLEEP.Power-down ModeDuring Power-down Mode, the clock is frozen. The on-chip RAM and I/O registers retain their values during Power-down Mode. The SLEEP instruction forces this mode. Exit from Power-down can be initiated either by a hardware reset or by the enabled external interrupt. Reset redefines the I/O registers but does not change the on-chip RAM.The I/O registers keep their value if the exit from Power-down is generated by an external interrupt.Download ModeThe AT90SC microcontroller has a special mode which allows the Flash to be written for new software download.The new software is loaded through the ISO port and writ-ten into the Flash memory. This download mode is software controlled, so if the software in use does not con-tain the download facility, no new program can be loaded. If the product contains only Flash for the code, during pro-gram download (OS or application) the code is fetched from the EEPROM.TimersThe AT90SC provides one or two 16-bit general timers with prescalers. The timers can run on a 16-bit counter or on an 8-bit counter with auto-reload mode.元器件交易网AT90SC6The Instruction SetAll members of the AT90SC series execute the same instruction set. The 16-bit instruction set provides a variety of fast addressing modes to facilitate byte and word opera-tions on small data structures. The instruction set supports 32 general-purpose registers for efficient implementation of software.Addressing ModeThe AT90SC AVR RISC microcontroller supports powerful and efficient addressing modes for access to program and data memory:•Direct I/O addressing•Direct Register addressing with one or two registers •Data direct : Operand address is specified by a 16-bit code •Indirect address data: Operand address is a 16-bit register •Indirect data with displacement : Operand address is a 16-bit register with a 6-bit offset •Indirect data with pre-decrement and post-increment: Operand address is a 16-bit register •Access to program memory : Operand address is a 16-bit register for access in byte LPM instruction •Indirect program addressing : Operand address is a 16-bit register for IJMP and ICALL •Relative program addressing : Operand address is a 16-bit PC with an offset of -2048 to +2047•Direct program addressingInstruction type •Data Transfers- From/to internal I/O, RAM, Registers - From/to internal EEPROM - From Flash •Arithmetic and logical Instruction - Manipulation, one or two registers - Manipulation, constant and register •Boolean Instruction- Manipulation and test on bit •Branch instruction - Relative branch - Indirect branch - Conditional skip- Unconditional branch - Conditional branch- Subroutine call and return - Interrupt returnMaster Clock GenerationThe master clock of the CPU is generated by the external ISO 7816 clock.Development ToolsA complete set of AT90SC development tools and a hard-ware emulator are available.© Atmel Corporation 1999.Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company ’s standard war-ranty which is detailed in Atmel ’s Terms and Conditions located on the Company ’s web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual prop-erty of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel ’s products are not authorized for use as critical components in life support devices or systems.Atmel HeadquartersAtmel OperationsCorporate Headquarters2325 Orchard Parkway San Jose, CA 95131TEL (408) 441-0311FAX (408) 487-2600EuropeAtmel U.K., Ltd.Coliseum Business Centre Riverside WayCamberley, Surrey GU15 3YL EnglandTEL (44) 1276-686-677FAX (44) 1276-686-697AsiaAtmel Asia, Ltd.Room 1219Chinachem Golden Plaza 77 Mody Road Tsimhatsui East Kowloon Hong KongTEL (852) 2721-9778FAX (852) 2722-1369JapanAtmel Japan K.K.9F, Tonetsu Shinkawa Bldg.1-24-8 ShinkawaChuo-ku, Tokyo 104-0033JapanTEL (81) 3-3523-3551FAX (81) 3-3523-7581Atmel Colorado Springs1150 E. Cheyenne Mtn. Blvd.Colorado Springs, CO 80906TEL (719) 576-3300FAX (719) 540-1759Atmel RoussetZone Industrielle13106 Rousset Cedex FranceTEL (33) 4-4253-6000FAX (33) 4-4253-6001Fax-on-DemandNorth America:1-(800) 292-8635International:1-(408) 441-0732e-mailliterature@Web Site BBS1-(408) 436-43091065CS –10/99/5MMarks bearing ® and/or ™ are registered trademarks and trademarks of Atmel Corporation.Terms and product names in this document may be trademarks of others.。

AT91SAM7S256-AU-001中文资料

Features Array•Incorporates the ARM7TDMI® ARM® Thumb® Processor–High-performance 32-bit RISC Architecture–High-density 16-bit Instruction Set–Leader in MIPS/Watt–Embedded ICE In-circuit Emulation, Debug Communication Channel Support •256 Kbytes of Internal High-speed Flash, Organized in 1024 Pages of 256 Bytes –Single Cycle Access at Up to 30 MHz in Worst Case Conditions–Prefetch Buffer Optimizing Thumb Instruction Execution at Maximum Speed–Page Programming Time: 4 ms, Including Page Auto-erase, Full Erase Time: 10 ms –10,000 Write Cycles, 10-year Data Retention Capability, Sector Lock Capabilities, Flash Security Bit–Fast Flash Programming Interface for High Volume Production•64 Kbytes of Internal High-speed SRAM, Single-cycle Access at Maximum Speed •Memory Controller (MC)–Embedded Flash Controller, Abort Status and Misalignment Detection•Reset Controller (RSTC)–Based on Power-on Reset and Low-power Factory-calibrated Brown-out Detector –Provides External Reset Signal Shaping and Reset Source Status•Clock Generator (CKGR)–Low-power RC Oscillator, 3 to 20 MHz On-chip Oscillator and one PLL•Power Management Controller (PMC)–Software Power Optimization Capabilities, Including Slow Clock Mode (Down to 500 Hz) and Idle Mode–Three Programmable External Clock Signals•Advanced Interrupt Controller (AIC)–Individually Maskable, Eight-level Priority, Vectored Interrupt Sources–Two External Interrupt Sources and One Fast Interrupt Source, Spurious Interrupt Protected•Debug Unit (DBGU)–2-wire UART and Support for Debug Communication Channel interrupt,Programmable ICE Access Prevention•Periodic Interval Timer (PIT)–20-bit Programmable Counter plus 12-bit Interval Counter•Windowed Watchdog (WDT)–12-bit key-protected Programmable Counter–Provides Reset or Interrupt Signals to the System–Counter May Be Stopped While the Processor is in Debug State or in Idle Mode •Real-time Timer (RTT)–32-bit Free-running Counter with Alarm–Runs Off the Internal RC Oscillator•One Parallel Input/Output Controller (PIOA)–Thirty-two Programmable I/O Lines Multiplexed with up to Two Peripheral I/Os –Input Change Interrupt Capability on Each I/O Line–Individually Programmable Open-drain, Pull-up resistor and Synchronous Output •Eleven Peripheral DMA Controller (PDC) Channels•One USB 2.0 Full Speed (12 Mbits per second) Device Port–On-chip Transceiver, 328-byte Configurable Integrated FIFOs26117BS–ATARM–07-Apr-05AT91SAM7S256•One Synchronous Serial Controller (SSC)–Independent Clock and Frame Sync Signals for Each Receiver and Transmitter –I²S Analog Interface Support, Time Division Multiplex Support–High-speed Continuous Data Stream Capabilities with 32-bit Data Transfer •Two Universal Synchronous/Asynchronous Receiver Transmitters (USART)–Individual Baud Rate Generator, IrDA Infrared Modulation/Demodulation–Support for ISO7816 T0/T1 Smart Card, Hardware Handshaking, RS485 Support –Manchester Encoder/Decoder–Full Modem Line Support on USART1•One Master/Slave Serial Peripheral Interface (SPI)–8- to 16-bit Programmable Data Length, Four External Peripheral Chip Selects •One Three-channel 16-bit Timer/Counter (TC)–Three External Clock Inputs, Two Multi-purpose I/O Pins per Channel –Double PWM Generation, Capture/Waveform Mode, Up/Down Capability •One Four-channel 16-bit PWM Controller (PWMC)•One Two-wire Interface (TWI)–Master Mode Support Only, All Two-wire Atmel EEPROMs Supported•One 8-channel 10-bit Analog-to-Digital Converter, Four Channels Multiplexed with Digital I/Os •IEEE 1149.1 JTAG Boundary Scan on All Digital Pins•5V-tolerant I/Os, including Four High-current Drive I/O lines, Up to 16 mA Each •Power Supplies–Embedded 1.8V Regulator, Drawing up to 100 mA for the Core and External Components –3.3V VDDIO I/O Lines Power Supply, Independent 3.3V VDDFLASH Flash Power Supply –1.8V VDDCORE Core Power Supply with Brown-out Detector•Fully Static Operation: Up to 55 MHz at 1.65V and 85°C Worst Case Conditions •Available in a 64-lead LQFP Green Package1.DescriptionAtmel’s AT91SAM7S256 is a member of a series of low pincount Flash microcontrollers based on the 32-bit ARM RISC processor. It features a 256 Kbyte high-speed Flash and a 64 Kbyte SRAM, a large set of peripherals, including a USB 2.0 device, and a complete set of system functions minimizing the number of external components. The device is an ideal migration path for 8-bit microcontroller users looking for additional performance and extended memory.The embedded Flash memory can be programmed in-system via the JTAG-ICE interface or via a parallel interface on a production programmer prior to mounting. Built-in lock bits and a security bit protect the firmware from accidental overwrite and preserves its confidentiality.The AT91SAM7S256 system controller includes a reset controller capable of managing the power-on sequence of the microcontroller and the complete system. Correct device operation can be monitored by a built-in brownout detector and a watchdog running off an integrated RC oscillator.The AT91SAM7S256 is a general-purpose microcontroller. Its integrated USB Device port makes it an ideal device for peripheral applications requiring connectivity to a PC or cellular phone. Its aggressive price point and high level of integration pushes its scope of use far into the cost-sensitive, high-volume consumer market.36117BS–ATARM–07-Apr-05AT91SAM7S2562.Block DiagramFigure 2-1.AT91SAM7S256 Block Diagram46117BS–ATARM–07-Apr-05AT91SAM7S2563.Signal DescriptionTable 3-1.Signal Description ListSignal NameFunctionTypeActive LevelCommentsPowerVDDIN Voltage and ADC Regulator Power Supply Input Power 3.0 to 3.6V VDDOUT Voltage Regulator Output Power 1.85V nominal VDDFLASH Flash Power Supply Power 3.0V to 3.6V VDDIO I/O Lines Power Supply Power 3.0V to 3.6V VDDCORE Core Power Supply Power 1.65V to 1.95V VDDPLL PLL Power 1.65V to 1.95VGNDGroundGroundClocks, Oscillators and PLLsXIN Main Oscillator Input Input XOUT Main Oscillator Output Output PLLRC PLL FilterInput PCK0 - PCK2Programmable Clock OutputOutputICE and JTAGTCK Test Clock Input No pull-up resistor TDI Test Data In Input No pull-up resistorTDO Test Data Out Output TMS Test Mode Select Input No pull-up resistor JTAGSELJTAG SelectionInputPull-down resistor Flash MemoryERASEFlash and NVM Configuration Bits Erase CommandInputHighPull-down resistorReset/TestNRST Microcontroller Reset I/O Low Pull-Up resistor TSTTest Mode SelectInputHighPull-down resistorDebug UnitDRXD Debug Receive Data Input DTXDDebug Transmit DataOutput AICIRQ0 - IRQ1External Interrupt Inputs Input FIQFast Interrupt InputInput56117BS–ATARM–07-Apr-05AT91SAM7S256PIOP A0 - P A31Parallel IO Controller A I/OPulled-up input at resetUSB Device PortDDM USB Device Port Data - Analog DDPUSB Device Port Data +AnalogUSARTSCK0 - SCK1Serial Clock I/O TXD0 - TXD1Transmit Data I/O RXD0 - RXD1 Receive Data Input RTS0 - RTS1Request T o Send Output CTS0 - CTS1Clear T o Send Input DCD1Data Carrier Detect Input DTR1Data Terminal Ready Output DSR1Data Set Ready Input RI1Ring IndicatorInputSynchronous Serial ControllerTD Transmit Data Output RD Receive Data Input TK Transmit Clock I/O RK Receive Clock I/O TF Transmit Frame Sync I/O RFReceive Frame SyncI/OTimer/CounterTCLK0 - TCLK2External Clock Inputs Input TIOA0 - TIOA2I/O Line A I/O TIOB0 - TIOB2I/O Line BI/OPWM ControllerPWM0 - PWM3PWM ChannelsOutputSPIMISO Master In Slave Out I/O MOSI Master Out Slave In I/O SPCK SPI Serial ClockI/O NPCS0SPI Peripheral Chip Select 0I/O Low NPCS1-NPCS3SPI Peripheral Chip Select 1 to 3OutputLowTable 3-1.Signal Description List (Continued)Signal NameFunctionTypeActive LevelComments66117BS–ATARM–07-Apr-05AT91SAM7S256Two-Wire InterfaceTWD Two-wire Serial Data I/O TWCKTwo-wire Serial ClockI/OAnalog-to-Digital ConverterAD0-AD3Analog Inputs Analog Digital pulled-up inputs at reset AD4-AD7Analog Inputs Analog Analog InputsADTRG ADC Trigger Input ADVREFADC ReferenceAnalogFast Flash Programming InterfacePGMEN0-PGMEN2Programming Enabling Input PGMM0-PGMM3Programming Mode Input PGMD0-PGMD15Programming Data I/O PGMRDY Programming Ready Output High PGMNVALID Data Direction Output Low PGMNOE Programming Read Input LowPGMCK Programming Clock Input PGMNCMDProgramming CommandInputLow Table 3-1.Signal Description List (Continued)Signal NameFunctionTypeActive LevelComments76117BS–ATARM–07-Apr-05AT91SAM7S2564.Package and PinoutThe AT91SAM7S256 is available in a 64-lead LQFP package.4.164-lead LQFP Mechanical OverviewFigure 4-1 shows the orientation of the 64-lead LQFP package. A detailed mechanical description is given in the section Mechanical Characteristics of the full datasheet.Figure 4-1.64-lead LQFP Package Pinout (Top View)4.2PinoutTable 4-1.AT91SAM7S256 Pinout in 64-lead LQFP Package1ADVREF 17GND 33TDI 49TDO 2GND 18VDDIO 34P A6/PGMNOE 50JTAGSEL 3AD419P A16/PGMD435P A5/PGMRDY 51TMS 4AD520P A15/PGMD336P A4/PGMNCMD 52P A315AD621P A14/PGMD237P A27/PGMD1553TCK 6AD722P A13/PGMD138P A2854VDDCORE 7VDDIN 23P A24/PGMD1239NRST 55ERASE 8VDDOUT 24VDDCORE 40TST 56DDM 9P A17/PGMD5/AD025P A25/PGMD1341P A2957DDP 10P A18/PGMD6/AD126P A26/PGMD1442P A3058VDDIO 11P A21/PGMD927P A12/PGMD043P A359VDDFLASH12VDDCORE 28P A11/PGMM344P A2/PGMEN260GND 13P A19/PGMD7/AD229P A10/PGMM245VDDIO 61XOUT 14P A22/PGMD1030P A9/PGMM146GND 62XIN/PGMCK 15P A23/PGMD1131P A8/PGMM047P A1/PGMEN163PLLRC 16P A20/PGMD8/AD332P A7/PGMNVALID48P A0/PGMEN064VDDPLL86117BS–ATARM–07-Apr-05AT91SAM7S2565.Power Considerations5.1Power SuppliesThe AT91SAM7S256 has six types of power supply pins and integrates a voltage regulator, allowing the device to be supplied with only one voltage. The six power supply pin types are:•VDDIN pin. It powers the voltage regulator and the ADC; voltage ranges from 3.0V to 3.6V , 3.3V nominal. If the voltage regulator is not used, VDDIN should be connected to GND.•VDDOUT pin. It is the output of the 1.8V voltage regulator.•VDDIO pin. It powers the I/O lines and the USB transceivers; dual voltage range issupported. Ranges from 3.0V to 3.6V , 3.3V nominal. Note that supplying less than 3.0V to VDDIO prevents any use of the USB transceivers.•VDDFLASH pin. It powers a part of the Flash and is required for the Flash to operate correctly; voltage ranges from 3.0V to 3.6V, 3.3V nominal.•VDDCORE pins. They power the logic of the device; voltage ranges from 1.65V to 1.95V, 1.8V typical. It can be connected to the VDDOUT pin with decoupling capacitor.VDDCORE is required for the device, including its embedded Flash, to operate correctly.•VDDPLL pin. It powers the oscillator and the PLL. It can be connected directly to the VDDOUT pin.No separate ground pins are provided for the different power supplies. Only GND pins are pro-vided and should be connected as shortly as possible to the system ground plane.5.2Power ConsumptionThe AT91SAM7S256 has a static current of less than 60 µA on VDDCORE at 25°C, including the RC oscillator, the voltage regulator and the power-on reset when the brown-out detector is deactivated. Activating the brown-out detector adds 20 µA static current.The dynamic power consumption on VDDCORE is less than 50 mA at full speed when running out of the Flash. Under the same conditions, the power consumption on VDDFLASH does not exceed 10 mA.5.3Voltage RegulatorThe AT91SAM7S256 embeds a voltage regulator that is managed by the System Controller.In Normal Mode, the voltage regulator consumes less than 100 µA static current and draws 100 mA of output current.The voltage regulator also has a Low-power Mode. In this mode, it consumes less than 25 µA static current and draws 1 mA of output current.Adequate output supply decoupling is mandatory for VDDOUT to reduce ripple and avoid oscillations. The best way to achieve this is to use two capacitors in parallel: one external 470 pF (or 1 nF) NPO capacitor must be connected between VDDOUT and GND as close to the chip as possible. One external 2.2 µF (or 3.3 µF) X7R capacitor must be connected between VDDOUT and GND.Adequate input supply decoupling is mandatory for VDDIN in order to improve startup stability and reduce source voltage drop. The input decoupling capacitor should be placed close to the chip. For example, two capacitors can be used in parallel: 100 nF NPO and 4.7 µF X7R.96117BS–ATARM–07-Apr-05AT91SAM7S2565.4Typical Powering SchematicsThe AT91SAM7S256 supports a 3.3V single supply mode. The internal regulator is connected to the 3.3V source and its output feeds VDDCORE and the VDDPLL. Figure 5-1 shows the power schematics to be used for USB bus-powered systems.Figure 5-1.3.3V System Single Power Supply Schematic106117BS–ATARM–07-Apr-05AT91SAM7S2566.I/O Lines Considerations6.1JTAG Port PinsTMS, TDI and TCK are schmitt trigger inputs. TMS and TCK are 5-V tolerant, TDI is not. TMS, TDI and TCK do not integrate a pull-up resistor.TDO is an output, driven at up to VDDIO, and has no pull-up resistor.The pin JTAGSEL is used to select the JTAG boundary scan when asserted at a high level. The pin JTAGSEL integrates a permanent pull-down resistor of about 15 k Ω to GND, so that it can be left unconnected for normal operations.6.2Test PinThe pin TST is used for manufacturing test or fast programming mode of the AT91SAM7S256 when asserted high. The pin TST integrates a permanent pull-down resistor of about 15 k Ω to GND, so that it can be left unconnected for normal operations.To enter fast programming mode, the pin TST and the pins PA0 and PA1 should be tied hig-hand PA2 tied to low.Driving the pin TST at a high level while PA0 or PA1 is driven at 0 leads to unpredictable results.6.3Reset PinThe pin NRST is bidirectional. It is handled by the on-chip reset controller and can be driven low to provide a reset signal to the external components or asserted low externally to reset the microcontroller. There is no constraint on the length of the reset pulse, and the reset controller can guarantee a minimum pulse length. This allows connection of a simple push-button on the pin NRST as system user reset, and the use of the signal NRST to reset all the components of the system.The pin NRST integrates a permanent pull-up resistor to VDDIO.6.4ERASE PinThe pin ERASE is used to re-initialize the Flash content and some of its NVM bits. It integrates a permanent pull-down resistor of about 15 k Ω to GND, so that it can be left unconnected for normal operations.6.5PIO Controller A LinesAll the I/O lines PA0 to PA31 are 5V-tolerant and all integrate a programmable pull-up resistor. Programming of this pull-up resistor is performed independently for each I/O line through the PIO controllers.5V-tolerant means that the I/O lines can drive voltage level according to VDDIO, but can be driven with a voltage of up to 5.5V. However, driving an I/O line with a voltage over VDDIO while the programmable pull-up resistor is enabled can lead to unpredictable results. Care should be taken, in particular at reset, as all the I/O lines default to input with pull-up resistor enabled at reset.116117BS–ATARM–07-Apr-05 AT91SAM7S2566.6I/O Line Drive LevelsThe PIO lines PA0 to PA3 are high-drive current capable. Each of these I/O lines can drive up to 16 mA permanently.The remaining I/O lines can draw only 8 mA.However, the total current drawn by all the I/O lines cannot exceed 150 mA.126117BS–ATARM–07-Apr-05AT91SAM7S2567.Processor and Architecture7.1ARM7TDMI Processor•RISC processor based on ARMv4T Von Neumann architecture–Runs at up to 55 MHz, providing 0.9 MIPS/MHz•Two instruction sets–ARM ® high-performance 32-bit instruction set–Thumb ® high code density 16-bit instruction set•Three-stage pipeline architecture–Instruction Fetch (F)–Instruction Decode (D)–Execute (E)7.2Debug and Test Features •Integrated embedded in-circuit emulator–Two watchpoint units–Test access port accessible through a JTAG protocol–Debug communication channel•Debug Unit–Two-pinUART–Debug communication channel interrupt handling–Chip ID Register•IEEE1149.1 JT AG Boundary-scan on all digital pins7.3Memory Controller•Bus Arbiter–Handles requests from the ARM7TDMI and the Peripheral DMA Controller•Address decoder provides selection signals for–Three internal 1 Mbyte memory areas–One 256 Mbyte embedded peripheral area•Abort Status Registers–Source, Type and all parameters of the access leading to an abort are saved–Facilitates debug by detection of bad pointers•Misalignment Detector–Alignment checking of all data accesses–Abort generation in case of misalignment•Remap Command–Remaps the SRAM in place of the embedded non-volatile memory–Allows handling of dynamic exception vectors•Embedded Flash Controller–Embedded Flash interface, up to three programmable wait states136117BS–ATARM–07-Apr-05 AT91SAM7S256–Prefetch buffer, bufferizing and anticipating the 16-bit requests, reducing therequired wait states–Key-protected program, erase and lock/unlock sequencer–Single command for erasing, programming and locking operations–Interrupt generation in case of forbidden operation7.4Peripheral DMA Controller•Handles data transfer between peripherals and memories•Eleven channels–Two for each USART–Two for the Debug Unit–Two for the Serial Synchronous Controller–Two for the Serial Peripheral Interface–One for the Analog-to-digital Converter•Low bus arbitration overhead–One Master Clock cycle needed for a transfer from memory to peripheral–Two Master Clock cycles needed for a transfer from peripheral to memory•Next Pointer management for reducing interrupt latency requirements146117BS–ATARM–07-Apr-05AT91SAM7S2568.Memory•256 Kbytes of Flash Memory–1024 pages of 256 bytes–Fast access time, 30 MHz single-cycle access in worst case conditions–Page programming time: 4 ms, including page auto-erase–Page programming without auto-erase: 2 ms–Full chip erase time: 10 ms–10,000 write cycles, 10-year data retention capability–16 lock bits, each protecting 16 sectors of 64 pages–Protection Mode to secure contents of the Flash•64 Kbytes of Fast SRAM–Single-cycle access at full speed8.1Memory Mapping 8.1.1Internal SRAMThe AT91SAM7S256 embeds a high-speed 64-Kbyte SRAM bank. After reset and until the Remap Command is performed, the SRAM is only accessible at address 0x0020 0000. After Remap, the SRAM also becomes available at address 0x0.8.1.2Internal FlashThe AT91SAM77S256 features one bank of 256 Kbytes of Flash. At any time, the Flash is mapped to address 0x0010 0000. It is also accessible at address 0x0 after the reset and before the Remap Command.Figure 8-1.Internal Memory Mapping156117BS–ATARM–07-Apr-05 AT91SAM7S2568.2Embedded Flash 8.2.1Flash OverviewThe Flash of the AT91SAM7S256 is organized in 1024 pages of 256 bytes. The 262,144 bytes are organized in 32-bit words.The Flash contains a 256-byte write buffer, accessible through a 32-bit interface.The Flash benefits from the integration of a power reset cell and from the brownout detector. This prevents code corruption during power supply changes, even in the worst conditions.When Flash is not used (read or write access), it is automatically placed into standby mode.8.2.2Embedded Flash ControllerThe Embedded Flash Controller (EFC) manages accesses performed by the masters of the system. It enables reading the Flash and writing the write buffer. It also contains a User Inter-face, mapped within the Memory Controller on the APB. The User Interface allows:•programming of the access parameters of the Flash (number of wait states, timings, etc.)•starting commands such as full erase, page erase, page program, NVM bit set, NVM bit clear, etc.•getting the end status of the last command•getting error status•programming interrupts on the end of the last commands or on errorsThe Embedded Flash Controller also provides a dual 32-bit Prefetch Buffer that optimizes 16-bit access to the Flash. This is particularly efficient when the processor is running in Thumb mode.8.2.3Lock RegionsThe Embedded Flash Controller manages 16 lock bits to protect 16 regions of the flash against inadvertent flash erasing or programming commands. The AT91SAM7S256 contains 16 lock regions and each lock region contains 64 pages of 256 bytes. Each lock region has a size of 16 Kbytes.If a locked-regions erase or program command occurs, the command is aborted and the EFC trigs an interrupt.The 16 NVM bits are software programmable through the EFC User Interface. The command "Set Lock Bit" enables the protection. The command "Clear Lock Bit" unlocks the lock region.Asserting the ERASE pin clears the lock bits, thus unlocking the entire Flash.8.2.4Security Bit FeatureThe AT91SAM7S256 features a security bit, based on a specific NVM-Bit. When the security is enabled, any access to the Flash, either through the ICE interface or through the Fast Flash Programming Interface, is forbidden. This ensures the confidentiality of the code programmed in the Flash.This security bit can only be enabled, through the Command "Set Security Bit" of the EFC User Interface. Disabling the security bit can only be achieved by asserting the ERASE pin at 1, and after a full flash erase is performed. When the security bit is deactivated, all accesses to the flash are permitted.It is important to note that the assertion of the ERASE pin should always be longer than 50 ms.166117BS–ATARM–07-Apr-05AT91SAM7S256As the ERASE pin integrates a permanent pull-down, it can be left unconnected during normal operation. However, it is safer to connect it directly to GND for the final application.8.2.5Non-volatile Brownout Detector ControlTwo general purpose NVM (GPNVM) bits are used for controlling the brownout detector (BOD), so that even after a power loss, the brownout detector operations remain in their state. These two GPNVM bits can be cleared or set respectively through the commands "Clear Gen-eral-purpose NVM Bit" and "Set General-purpose NVM Bit" of the EFC User Interface.•GPNVM Bit 0 is used as a brownout detector enable bit. Setting the GPNVM Bit 0 enables the BOD, clearing it disables the BOD. Asserting ERASE clears the GPNVM Bit 0 and thus disables the brownout detector by default.•The GPNVM Bit 1 is used as a brownout reset enable signal for the reset controller. Setting the GPNVM Bit 1 enables the brownout reset when a brownout is detected, Clearing the GPNVM Bit 1 disables the brownout reset. Asserting ERASE disables the brownout reset by default.8.2.6Calibration BitsEight NVM bits are used to calibrate the brownout detector and the voltage regulator. These bits are factory configured and cannot be changed by the user. The ERASE pin has no effect on the calibration bits.8.3Fast Flash Programming InterfaceThe Fast Flash Programming Interface allows programming the device through either a serial JTAG interface or through a multiplexed fully-handshaked parallel port. It allows gang-pro-gramming with market-standard industrial programmers.The FFPI supports read, page program, page erase, full erase, lock, unlock and protect commands.The Fast Flash Programming Interface is enabled and the Fast Programming Mode is entered when the TST pin and the PA0 and PA1 pins are all tied high and PA2 is tied low.176117BS–ATARM–07-Apr-05 AT91SAM7S2569.System ControllerThe System Controller manages all vital blocks of the microcontroller: interrupts, clocks, power, time, debug and reset.Figure 9-1.System Controller Block Diagram186117BS–ATARM–07-Apr-05AT91SAM7S2569.1System Controller MappingThe System Controller peripherals are all mapped to the highest 4 Kbytes of address space, between addresses 0xFFFF F000 and 0xFFFF FFFF.Figure 9-2 shows the mapping of the System Controller. Note that the Memory Controller con-figuration user interface is also mapped within this address space.Figure 9-2.System Controller Mapping196117BS–ATARM–07-Apr-05 AT91SAM7S2569.2Reset ControllerThe Reset Controller is based on a power-on reset cell and one brownout detector. It gives the status of the last reset, indicating whether it is a power-up reset, a software reset, a user reset, a watchdog reset or a brownout reset. In addition, it controls the internal resets and the NRST pin output. It allows to shape a signal on the NRST line, guaranteeing that the length of the pulse meets any requirement.Note that if NRST is used as a reset output signal for external devices during power-off, the brownout detector must be activated.9.2.1Brownout Detector and Power-on ResetThe AT91SAM7S256 embeds a brownout detection circuit and a power-on reset cell. Both are supplied with and monitor VDDCORE. Both signals are provided to the Flash to prevent any code corruption during power-up or power-down sequences or if brownouts occur on the VDDCORE power supply.The power-on reset cell has a limited-accuracy threshold at around 1.5V. Its output remains low during power-up until VDDCORE goes over this voltage level. This signal goes to the reset controller and allows a full re-initialization of the device.The brownout detector monitors the VDDCORE level during operation by comparing it to a fixed trigger level. It secures system operations in the most difficult environments and prevents code corruption in case of brownout on the VDDCORE.Only VDDCORE is monitored, as a voltage drop on VDDFLASH or any other power supply of the device cannot affect the Flash.When the brownout detector is enabled and VDDCORE decreases to a value below the trigger level (Vbot-, defined as Vbot - hyst/2), the brownout output is immediately activated.When VDDCORE increases above the trigger level (Vbot+, defined as Vbot + hyst/2), the reset is released. The brownout detector only detects a drop if the voltage on VDDCORE stays below the threshold voltage for longer than about 1µs.The threshold voltage has a hysteresis of about 50 mV, to ensure spike free brownout detec-tion. The typical value of the brownout detector threshold is 1.68V with an accuracy of ± 2% and is factory calibrated.The brownout detector is low-power, as it consumes less than 20 µA static current. However, it can be deactivated to save its static current. In this case, it consumes less than 1µA. The deactivation is configured through the GPNVM bit 0 of the Flash.206117BS–ATARM–07-Apr-05AT91SAM7S2569.3Clock GeneratorThe Clock Generator embeds one low-power RC Oscillator, one Main Oscillator and one PLL with the following characteristics:•RC Oscillator ranges between 22 KHz and 42 KHz•Main Oscillator frequency ranges between 3 and 20 MHz•Main Oscillator can be bypassed•PLL output ranges between 80 and 220 MHzIt provides SLCK, MAINCK and PLLCK.Figure 9-3.Clock Generator Block Diagram。

96SC Crystal 502 2的物质安全数据表说明书