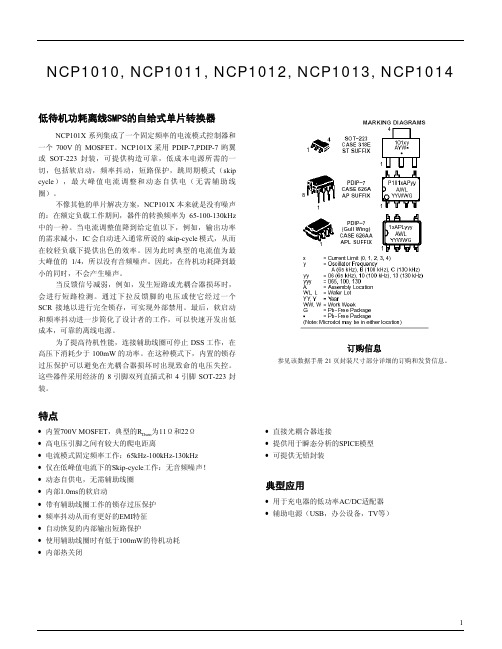

NCP5181PG中文资料

CS42L51中文资料

Advance Product InformationThis document contains information for a new product.Cirrus Logic reserves the right to modify this product without notice.Low Power, Stereo CODEC with Headphone AmpDIGITAL to ANALOG FEATURES!98 dB Dynamic Range (A-wtd) !-86 dB THD+N!Headphone Amplifier - GND Centered–On-Chip Charge Pump Provides -VA_HP –No DC-Blocking Capacitor Required –46mW Power Into Stereo 16Ω @ 1.8V –88mW Power Into Stereo 16Ω @ 2.5V –-75 dB THD+N!Digital Signal Processing Engine–Bass & Treble Tone Control, De-Emphasis –PCM + ADC Mix w/Independent Vol Control –Master Digital Volume Control–Soft Ramp & Zero Cross Transitions ! Beep Generator–Tone Selections Across Two Octaves –Separate Volume Control–Programmable On & Off Time Intervals –Continuous, Periodic or One-Shot Beep Selections!Programmable Peak-Detect and Limiter !Pop and Click SuppressionANALOG to DIGITAL FEATURES!98 dB Dynamic Range (A-wtd)! -88 dB THD+N !Analog Gain Controls–+32 dB or +16 dB MIC Pre-Amplifiers –Analog Programmable Gain Amplifier (PGA)!+20 dB Digital Boost!Programmable Automatic Level Control (ALC)–Noise Gate for Noise Suppression –Programmable Threshold and Attack/Release Rates!Independent Channel Control !Digital Volume Control!High-Pass Filter Disable for DC Measurements !Stereo 3:1 Analog Input MUX !Dual MIC Inputs–Programmable, Low Noise MIC Bias Levels –Differential MIC Mix for Common Mode Noise Rejection!Very Low 64 Fs Oversampling Clock ReducesPower ConsumptionCS42L51SYSTEM FEATURES!24-bit Converters! 4 kHz to 96kHz Sample Rate!Multi-bit Delta Sigma Architecture!Low Power Operation–Stereo Playback: 12.93 mW @ 1.8 V–Stereo Record and Playback: 20.18 mW @1.8 V!Variable Power Supplies– 1.8 V to 2.5 V Digital & Analog– 1.8 V to 3.3V Interface Logic!Power Down Management–ADC, DAC, CODEC, MIC Pre-Amplifier, PGA!Software Mode (I²C & SPI™ Control)!Hardware Mode (Stand-Alone Control)!Digital Routing/Mixes:–Analog Out=ADC+Digital In–Digital Out=ADC+Digital In–Internal Digital Loopback–Mono Mixes!Flexible Clocking Options–Master or Slave Operation–High-Impedance Digital Output Option (for easy MUXing between CODEC and OtherData Sources)–Quarter-Speed Mode - (i.e. Allows 8 kHz Fs while maintaining a flat noise floor up to16kHz)APPLICATIONS!HDD & Flash-Based Portable Audio Players !MD Players/Recorders!PDAs!Personal Media Players!Portable Game Consoles!Digital Voice Recorders!Digital Camcorders!Digital Cameras!Smart Phones GENERAL DESCRIPTIONThe CS42L51 is a highly integrated, 24-bit, 96kHz, low power stereo CODEC. Based on multi-bit, delta-sigma modulation, it allows infinite sample rate adjustment be-tween 4 kHz and 96 kHz. Both the ADC and DAC offer many features suitable for low power, portable system applications.The ADC input path allows independent channel control of a number of features. An input multiplexer selects be-tween line-level or microphone level inputs for each channel. The microphone input path includes a select-able programmable-gain pre-amplifier stage and a low noise MIC bias voltage supply. A PGA is available for line or microphone inputs and provides analog gain with soft ramp and zero cross transitions. The ADC also fea-tures a digital volume attenuator with soft ramp transitions. A programmable ALC and Noise Gate mon-itor the input signals and adjust the volume levels appropriately.The DAC output path includes a digital signal process-ing engine. Tone Control provides bass and treble adjustment of four selectable corner frequencies. The Mixer allows independent volume control for both the ADC mix and the PCM mix, as well as a master digital volume control for the analog output. All volume level changes may be configured to occur on soft ramp and zero cross transitions. The DAC also includes de-em-phasis, limiting functions and a beep generator delivering tones selectable across a range of two full octaves.The stereo headphone amplifier is powered from a sep-arate positive supply and the integrated charge pump provides a negative supply. This allows a ground-cen-tered analog output with a wide signal swing and eliminates external DC-blocking capacitors.In addition to its many features, the CS42L51 operates from a low-voltage analog and digital core, making this CODEC ideal for portable systems that require ex-tremely low power consumption in a minimal amount of space.The CS42L51 is available in a 32-pin QFN package in both Commercial (-10 to +70° C) and Automotive grades (-40 to +85° C). The CDB42L51 Customer Dem-onstration board is also available for device evaluation and implementation suggestions. Please see “Ordering Information” on page81 for complete details.TABLE OF CONTENTS1. PIN DESCRIPTIONS - SOFTWARE (HARDWARE) MODE (7)1.1 Digital I/O Pin Characteristics (9)2. TYPICAL CONNECTION DIAGRAMS (10)3. CHARACTERISTIC AND SPECIFICATION TABLES (12)SPECIFIED OPERATING CONDITIONS (12)ABSOLUTE MAXIMUM RATINGS (12)ANALOG INPUT CHARACTERISTICS (COMMERCIAL - CNZ) (13)ANALOG INPUT CHARACTERISTICS (AUTOMOTIVE - DNZ) (14)ADC DIGITAL FILTER CHARACTERISTICS (15)ANALOG OUTPUT CHARACTERISTICS (COMMERCIAL - CNZ) (16)ANALOG OUTPUT CHARACTERISTICS (AUTOMOTIVE - DNZ) (17)LINE OUTPUT VOLTAGE CHARACTERISTICS (18)HEADPHONE OUTPUT POWER CHARACTERISTICS (19)COMBINED DAC INTERPOLATION & ON-CHIP ANALOG FILTER RESPONSE (20)SWITCHING SPECIFICATIONS - SERIAL PORT (20)SWITCHING SPECIFICATIONS - I²C CONTROL PORT (22)SWITCHING CHARACTERISTICS - SPI CONTROL PORT (23)DC ELECTRICAL CHARACTERISTICS (24)DIGITAL INTERFACE SPECIFICATIONS & CHARACTERISTICS (24)POWER CONSUMPTION (25)4. APPLICATIONS (26)4.1 Overview (26)4.1.1 Architecture (26)4.1.2 Line & MIC Inputs (26)4.1.3 Line & Headphone Outputs (26)4.1.4 Signal Processing Engine (26)4.1.5 Beep Generator (26)4.1.6 Device Control (Hardware or Software Mode) (26)4.1.7 Power Management (26)4.2 Hardware Mode (27)4.3 Analog Inputs (28)4.3.1 Digital Code, Offset & DC Measurement (28)4.3.2 High-Pass Filter and DC Offset Calibration (29)4.3.3 Digital Routing (29)4.3.4 Differential Inputs (29)4.3.4.1 External Passive Components (29)4.3.5 Analog Input Multiplexer (30)4.3.6 MIC & PGA Gain (31)4.3.7 Automatic Level Control (ALC) (31)4.3.8 Noise Gate (32)4.4 Analog Outputs (33)4.4.1 De-Emphasis Filter (33)4.4.2 Volume Controls (34)4.4.3 Mono Channel Mixer (34)4.4.4 Beep Generator (34)4.4.5 Tone Control (35)4.4.6 Limiter (35)4.4.7 Line-Level Outputs and Filtering (36)4.4.8 On-Chip Charge Pump (36)4.5 Serial Port Clocking (37)4.5.1 Slave (37)4.5.2 Master (38)4.5.3 High-Impedance Digital Output (38)4.5.4 Quarter- and Half-Speed Mode (39)4.6 Digital Interface Formats (39)4.7 Initialization (40)4.8 Recommended Power-Up Sequence (40)4.9 Recommended Power-Down Sequence (41)4.10 Software Mode (42)4.10.1 SPI Control (42)4.10.2 I²C Control (42)4.10.3 Memory Address Pointer (MAP) (44)4.10.3.1 Map Increment (INCR) (44)5. REGISTER QUICK REFERENCE (45)6. REGISTER DESCRIPTION (47)6.1 Chip I.D. and Revision Register (Address 01h) (Read Only) (47)6.2 Power Control 1 (Address 02h) (47)6.3 MIC Power Control & Speed Control (Address 03h) (48)6.4 Interface Control (Address 04h) (49)6.5 MIC Control (Address 05h) (51)6.6 ADC Control (Address 06h) (52)6.7 ADCx Input Select, Invert & Mute (Address 07h) (53)6.8 DAC Output Control (Address 08h) (54)6.9 DAC Control (Address 09h) (55)6.10 ALCX & PGAX Control:ALCA, PGAA (Address 0Ah) & ALCB, PGAB (Address 0Bh) (56)6.11 ADCx Attenuator:ADCA (Address 0Ch) & ADCB (Address 0Dh) (57)6.12 ADCx Mixer Volume Control:ADCA (Address 0Eh) & ADCB (Address 0Fh) (58)6.13 PCMX Mixer Volume Control:PCMA (Address 10h) & PCMB (Address 11h) (59)6.14 Beep Frequency & Timing Configuration (Address 12h) (60)6.15 Beep Off Time & Volume (Address 13h) (61)6.16 Beep Configuration & Tone Configuration (Address 14h) (62)6.17 Tone Control (Address 15h) (63)6.18 AOUTx Volume Control:AOUTA (Address 16h) & AOUTB (Address 17h) (64)6.20 Limiter Threshold SZC Disable (Address 19h) (65)6.21 Limiter Release Rate Register (Address 1Ah) (66)6.22 Limiter Attack Rate Register (Address 1Bh) (67)6.23 ALC Enable & Attack Rate (Address 1Ch) (67)6.24 ALC Release Rate (Address 1Dh) (68)6.25 ALC Threshold (Address 1Eh) (69)6.26 Noise Gate Configuration & Misc. (Address 1Fh) (70)6.27 Status (Address 20h) (Read Only) (71)6.28 Charge Pump Frequency (Address 21h) (71)7. ANALOG PERFORMANCE PLOTS (72)7.1 Headphone THD+N versus Output Power Plots (72)7.2 ADC_FILT+ Capacitor Effects on THD+N (74)8. EXAMPLE SYSTEM CLOCK FREQUENCIES (75)8.1 Auto Detect Enabled (75)8.2 Auto Detect Disabled (76)9. PCB LAYOUT CONSIDERATIONS (77)9.1 Power Supply, Grounding (77)9.2 QFN Thermal Pad (77)10. ADC & DAC DIGITAL FILTERS (78)11. PARAMETER DEFINITIONS (79)12. PACKAGE DIMENSIONS (80)THERMAL CHARACTERISTICS (80)13. ORDERING INFORMATION (81)14. REFERENCES (81)15. REVISION HISTORY (82)LIST OF FIGURESFigure 1. Typical Connection Diagram (Software Mode) (10)Figure 2. Typical Connection Diagram (Hardware Mode) (11)Figure 3. Headphone Output Test Load (19)Figure 4. Serial Audio Interface Slave Mode Timing (21)Figure 5. TDM Serial Audio Interface Timing (21)Figure 6. Serial Audio Interface Master Mode Timing (21)Figure 7. Control Port Timing - I²C (22)Figure 8. Control Port Timing - SPI Format (23)Figure 9. Analog Input Architecture (28)Figure 10. MIC Input Mix w/Common Mode Rejection (30)Figure 11. Differential Input (30)Figure 12. ALC (31)Figure 13. Noise Gate Attenuation (32)Figure 14. Output Architecture (33)Figure 15. De-Emphasis Curve (33)Figure 16. Beep Configuration Options (34)Figure 17. Peak Detect & Limiter (35)Figure 18. Master Mode Timing (38)Figure 19. Tri-State Serial Port (38)Figure 20. I²S Format (39)Figure 21. Left-Justified Format (39)Figure 22. Right-Justified Format (DAC only) (39)Figure 23. Initialization Flow Chart (41)Figure 24. Control Port Timing in SPI Mode (42)Figure 25. Control Port Timing, I²C Write (43)Figure 26. Control Port Timing, I²C Read (43)Figure 27. AIN & PGA Selection (53)Figure 28. THD+N vs. Ouput Power per Channel at 1.8V (16 Ω load) (72)Figure 29. THD+N vs. Ouput Power per Channel at 2.5V (16 Ω load) (72)Figure 30. THD+N vs. Ouput Power per Channel at 1.8V (32 Ω load) (73)Figure 31. THD+N vs. Ouput Power per Channel at 2.5V (32 Ω load) (73)Figure 32. ADC THD+N vs. Frequency w/Capacitor Effects (74)Figure 33. ADC Passband Ripple (78)Figure 34. ADC Stopband Rejection (78)Figure 35. DAC Passband Ripple (78)Figure 36. DAC Stopband (78)Figure 35. DAC Transition Band (78)Figure 36. DAC Transition Band (Detail) (78)Figure 35. ADC Transition Band (78)Figure 36. ADC Transition Band (Detail) (78)1.PIN DESCRIPTIONS - SOFTWARE (HARDWARE) MODEPin Name#Pin DescriptionLRCK 1Left Right Clock (Input/Output ) - Determines which channel, Left or Right, is currently active on the serial audio data line.SDA/CDIN 2Serial Control Data (Input /Output ) - SDA is a data I/O in I²C mode. CDIN is the input data line for the control port interface in SPI mode.(MCLKDIV2)MCLK Divide by 2 (Input ) - Hardware Mode: Divides the MCLK by 2 prior to all internal circuitry.SCL/CCLK 3Serial Control Port Clock (Input ) - Serial clock for the serial control port.(I²S/LJ)Interface Format Selection (Input ) - Hardware Mode: Selects between I²S & Left-Justified interface for-mats for the ADC & DAC.AD0/CS 4Address Bit 0 (I²C) / Control Port Chip Select (SPI) (Input) - AD0 is a chip address pin in I²C mode; CS is the chip select signal for SPI format.(DEM)De-Emphasis (Input) - Hardware Mode: Enables/disables the de-emphasis filter.VA_HP 5Analog Power For Headphone (Input) - Positive power for the internal analog headphone section.FLYP 6Charge Pump Cap Positive Node (Input) - Positive node for the external charge pump capacitor.GNDHP 7Analog Ground (Input ) - Ground reference for the internal headphone/charge pump section.FLYN 8Charge Pump Cap Negative Node (Input) - Negative node for the external charge pump capacitor.VSS_HP 9Negative Voltage From Charge Pump (Output) - Negative voltage rail for the internal analog head-phone section.AOUTB AOUTA 1011Analog Audio Output (Output ) - The full-scale output level is specified in the DAC Analog Characteris-tics specification table.VA 12Analog Power (Input) - Positive power for the internal analog section.AGND13Analog Ground (Input) - Ground reference for the internal analog section.M /S )V S S _H A O U T BA O U T V A G N D A C _F I L T A D C _F I L T VDAC_FILT+ ADC_FILT+1416Positive Voltage Reference (Output) - Positive reference voltage for the internal sampling circuits.VQ15Quiescent Voltage (Output) - Filter connection for internal quiescent voltage.MICIN1/ AIN3A 17Microphone Input 1 (Input) - The full-scale level is specified in the ADC Analog Characteristics specifi-cation table.MICIN2/ BIAS/AIN3B 18Microphone Input 2 (Input/Output) - The full-scale level is specified in the ADC Analog Characteristics specification table. This pin can also be configured as an output to provide a low noise bias supply for an external microphone. Electrical characteristics are specified in the DC Electrical Characteristics table.AIN2A19Analog Input (Input) - The full-scale level is specified in the ADC Analog Characteristics specification table.AIN2B/BIAS20Analog Input (Input/Output) - The full-scale level is specified in the ADC Analog Characteristics specifi-cation table. This pin can also be configured as an output to provide a low noise bias supply for an exter-nal microphone. Electrical characteristics are specified in the DC Electrical Characteristics table.AFILTA AFILTB 2122Filter Connection (Output) - Filter connection for the ADC inputs.AIN1A AIN1B 2324Analog Input (Input) - The full-scale level is specified in the ADC Analog Characteristics specification table.RESET25Reset (Input) - The device enters a low power mode when this pin is driven low.VL26Digital Interface Power (Input) - Determines the required signal level for the serial audio interface and host control port. Refer to the Recommended Operating Conditions for appropriate voltages.VD27Digital Power (Input) - Positive power for the internal digital section.DGND28Digital Ground (Input) - Ground reference for the internal digital section.SDOUT29Serial Audio Data Output (Output) - Output for two’s complement serial audio data.(M/S)Serial Port Master/Slave (Input/Output) - Hardware Mode Startup Option: Selects between master and slave mode for the serial port.MCLK30Master Clock (Input) -Clock source for the delta-sigma modulators.SCLK31Serial Clock (Input/Output) - Serial clock for the serial audio interface.SDIN32Serial Audio Data Input (Input) - Input for two’s complement serial audio data.Thermal Pad-Thermal relief pad for optimized heat dissipation. See “QFN Thermal Pad” on page77.1.1Digital I/O Pin CharacteristicsThe logic level for each input should adhere to the corresponding power rail and should not exceed the maximum ratings.Power Rail Pin NameSW/(HW)I/O Driver ReceiverVL RESET Input- 1.8 V - 3.3 V SCL/CCLK(I²S/LJ)Input- 1.8 V - 3.3 V, with HysteresisSDA/CDIN(MCLKDIV2)Input/Output 1.8 V - 3.3 V, CMOS/Open Drain 1.8 V - 3.3 V, with HysteresisAD0/CS(DEM)Input- 1.8 V - 3.3 V MCLK Input- 1.8 V - 3.3 VLRCK Input/Output 1.8 V - 3.3 V, CMOS 1.8 V - 3.3 VSCLK Input/Output 1.8 V - 3.3 V, CMOS 1.8 V - 3.3 VSDOUT(M/S)Input/Output 1.8 V - 3.3 V, CMOS 1.8 V - 3.3 V SDIN Input- 1.8 V - 3.3 VTable 1. I/O Power Rails2.TYPICAL CONNECTION DIAGRAMSFigure 1. Typical Connection Diagram (Software Mode)Figure 2. Typical Connection Diagram (Hardware Mode)3.CHARACTERISTIC AND SPECIFICATION TABLES(All Min/Max characteristics and specifications are guaranteed over the Specified Operating Conditions. Typical performance characteristics and specifications are derived from measurements taken at nominal supply voltages and T A = 25° C.)SPECIFIED OPERATING CONDITIONS(AGND=DGND=0 V, all voltages with respect to ground.)ABSOLUTE MAXIMUM RATINGS(AGND = DGND = 0 V; all voltages with respect to ground.)WARNING:Operation at or beyond these limits may result in permanent damage to the device. Normal operationis not guaranteed at these extremes.Notes:1.The device will operate properly over the full range of the analog, headphone amplifier, digital core andserial/control port interface supplies.2.Any pin except supplies. Transient currents of up to ±100 mA on the analog input pins will not causeSCR latch-up.3.The maximum over/under voltage is limited by the input current.ParametersSymbol Min NomMaxUnitsDC Power Supply (Note 1)Analog Core VA 1.712.37 1.82.5 1.892.63V V Headphone Amplifier VA_HP 1.712.37 1.82.5 1.892.63V V Digital CoreVD 1.712.37 1.82.5 1.892.63V V Serial/Control Port InterfaceVL1.712.373.14 1.82.53.3 1.892.633.47V V V Ambient TemperatureCommercial - CNZ Automotive - DNZT A-10-40--+70+85°C °CParametersSymbol MinMaxUnitsDC Power SupplyAnalog Digital Serial/Control Port Interface VA, VA_HP VDVL-0.3-0.3-0.3 3.03.04.0V V V Input Current(Note 2)I in -±10mAAnalog Input Voltage(Note 3)V INAGND-0.7VA+0.7VDigital Input Voltage (Note 3))V IND-0.3VL+ 0.4V Ambient Operating Temperature Commercial - CNZ(power applied)Automotive - DNZT A -20-50+85+95°C °C Storage TemperatureT stg-65+150°C(Test Conditions (unless otherwise specified): All supplies = VA = 2.5 V and 1.8 V; Input sine wave (relative to dig-ital full-scale): 1kHz through passive input filter; Measurement Bandwidth is 10Hz to 20kHz unless otherwise specified. Sample Frequency = 48kHz)VA = 2.5V VA = 1.8VParameter (Note 4)Min Typ Max Min Typ Max Unit Analog In to ADC (PGA bypassed)Dynamic Range A-weightedunweighted 93909996--90879693--dBdBTotal Harmonic Distortion + Noise -1dBFS-20dBFS-60dBFS ----86-76-36-80------84-73-33-78--dBdBdBAnalog In to PGA to ADC Dynamic RangePGA Setting: 0 dB A-weightedunweighted 92899895--89869592--dBdBPGA Setting: +12 dB A-weightedunweighted 85829188--82798885--dBdBTotal Harmonic Distortion + NoisePGA Setting: 0 dB -1dBFS -60dBFS ---88-35-82----86-32-80-dBdBPGA Setting: +12 dB -1dBFS--85-79--83-77dB Analog In to MIC Pre-Amp(+16 dB) to PGA to ADCDynamic RangePGA Setting: 0 dB A-weightedunweighted --8683----8380--dBdBTotal Harmonic Distortion + NoisePGA Setting: 0 dB -1dBFS--76---74-dB Analog In to MIC Pre-Amp(+32 dB) to PGA to ADCDynamic RangePGA Setting: 0 dB A-weightedunweighted --7874----7571--dBdBTotal Harmonic Distortion + NoisePGA Setting: 0 dB -1dBFS--74---71-dB Other CharacteristicsDC AccuracyInterchannel Gain Mismatch-0.1--0.1-dB Gain Drift-±100--±100-ppm/°C InputInterchannel Isolation-90--90-dB DAC Isolation (Note 5)-70--70-dB Full-scale Input Voltage (x•VA) (Note 7)0.70•VA0.72•VA0.75•VA0.70•VA0.72•VA0.75•VA VppInput Impedance (Note 6)ADCPGAMIC 184050------184050------kΩkΩkΩ(Test Conditions (unless otherwise specified): All supplies = VA = 2.5 V and 1.8 V; Input sine wave (relative to full-scale): 1 kHz through passive input filter; Measurement Bandwidth is 10Hz to 20kHz unless otherwise specified. Sample Frequency = 48kHz)Notes:4.Referred to the typical full-scale voltage.5.Measured with DAC delivering full-scale output power into 16 Ω.VA = 2.5V VA = 1.8V Parameter (Note 4)MinTypMaxMinTypMaxUnitAnalog In to ADCDynamic RangeA-weighted unweighted91789996--88859693--dB dB Total Harmonic Distortion + Noise -1dB -20dB-60dB ----86-76-36-78------84-73-33-76--dB dB dBAnalog In to PGA to ADC Dynamic RangePGA Setting: 0 dB A-weighted unweighted 90879895--87849592--dB dB PGA Setting: +12 dBA-weighted unweighted83809188--80778885--dB dB Total Harmonic Distortion + Noise PGA Setting: 0 dB -1dB -60dB ---88-35-80----86-32-78-dB dB PGA Setting: +12 dB -1dB--85-77--83-75dBAnalog In to MIC Pre-Amp (+16 dB) to PGA to ADC Dynamic RangePGA Setting: 0 dBA-weighted unweighted--8683----8380--dB dB Total Harmonic Distortion + Noise PGA Setting: 0 dB-1dB--76---74-dBAnalog In to MIC Pre-Amp (+32 dB) to PGA to ADC Dynamic RangePGA Setting: 0 dBA-weighted unweighted--7874----7571--dB dB Total Harmonic Distortion + Noise PGA Setting: 0 dB-1dB--74---71-dBOther CharacteristicsDC AccuracyInterchannel Gain Mismatch -0.1--0.1-dB Gain Drift-±100--±100-ppm/°C InputInterchannel Isolation -90--90-dB DAC Isolation (Note 5)-70--70-dB Full-scale Input Voltage (Note 7) 0.70•VA 0.72•VA0.75•VA0.70•VA 0.72•VA0.75•VAVpp Input Impedance (Note 6)ADC PGA MIC 184050------184050------k Ωk Ωk ΩNotes:6.Measured between AINxx and AGND.7.Full-scale input voltage characteristics for the PGA and Microphone inputs are scaled based on the gainsetting for each.ADC DIGITAL FILTER CHARACTERISTICSNotes:8.Response is clock dependent and will scale with Fs. Note that the response plots (Figures 33to 36 onpage 78) have been normalized to Fs and can be de-normalized by multiplying the X-axis scale by Fs.Parameter (Note 8)MinTypMaxUnitPassband (Frequency Response) to -0.1 dB corner0-0.4948Fs Passband Ripple -0.09-0dB Stopband0.6677--Fs Stopband Attenuation 48.4--dB Total Group Delay-2.7/Fs -s High-Pass Filter CharacteristicsFrequency Response -3.0 dB -0.13 dB -- 3.724.2--Hz Hz Phase Deviation @ 20Hz-10-Deg Passband Ripple --0.17dB Filter Settling Time-105/Fss(Test conditions (unless otherwise specified): Input test signal is a full-scale 997 Hz sine wave; measurement bandwidth is 10 Hz to 20 kHz; Sample Frequency = 48 kHz; test load R L = 10 kΩ, C L = 10 pF for the line output (see Figure3), and test load R L = 16 Ω, C L = 10 pF (see Figure3) for the headphone output. HP_GAIN[2:0] = 011.)Parameter(Note 9)VA = 2.5VMin Typ MaxVA = 1.8VMin Typ Max UnitR L = 10 kΩDynamic Range18 to 24-Bit A-weighted unweighted 16-Bit A-weightedunweighted 9289--98959693----8986--95929390----dBdBdBdBTotal Harmonic Distortion + Noise18 to 24-Bit0 dB-20 dB-60 dB 16-Bit0 dB-20 dB-60 dB -------86-75-35-86-73-33-80------------88-72-32-88-70-30-82-----dBdBdBdBdBdBR L = 16 ΩDynamic Range18 to 24-Bit A-weightedunweighted 16-Bit A-weightedunweighted 9289--98959693----8986--95929390----dBdBdBdBTotal Harmonic Distortion + Noise18 to 24-Bit0 dB-20 dB-60 dB 16-Bit0 dB-20 dB-60 dB -------75-75-35-75-73-33-69------------75-72-32-75-70-30-69-----dBdBdBdBdBdBOther Characteristics for R L = 16 Ω or 10 kΩOutput Parameters Modulation Index (MI) (Note 10)Analog Gain Multiplier (G)-0.67870.6047--0.67870.6047-Full-scale Output Voltage (2•G•MI•VA) (Note 10)Refer to Table“Line Output Voltage Characteristics” onpage18VppFull-scale Output Power (Note 10)Refer to Table“Headphone Output Power Characteristics” onpage19Interchannel Isolation (1 kHz)16 Ω10 kΩ--8095----8093--dBdBInterchannel Gain Mismatch-0.10.25-0.10.25dB Gain Drift-±100--±100-ppm/°C AC-Load Resistance (R L)(Note 11)16--16--ΩLoad Capacitance (C L)(Note 11)--150--150pF(Test conditions (unless otherwise specified): Input test signal is a full-scale 997 Hz sine wave; measurement bandwidth is 10 Hz to 20 kHz; Sample Frequency = 48 kHz and 96 kHz; test load R L = 10 kΩ, C L = 10 pF for the line output (see Figure3), and test load R L = 16 Ω, C L = 10 pF (see Figure3) for the headphone output.HP_GAIN[2:0] = 011.)Parameter(Note 9)VA = 2.5VMin Typ MaxVA = 1.8VMin Typ Max UnitR L = 10 kΩDynamic Range18 to 24-Bit A-weighted unweighted 16-Bit A-weightedunweighted 9087--98959693----8784--95929390----dBdBdBdBTotal Harmonic Distortion + Noise18 to 24-Bit0 dB-20 dB-60 dB 16-Bit0 dB-20 dB-60 dB -------86-75-35-86-73-33-78------------88-72-32-88-70-30-80-----dBdBdBdBdBdBR L = 16 ΩDynamic Range18 to 24-Bit A-weightedunweighted 16-Bit A-weightedunweighted 9087--98959693----8784--95929390----dBdBdBdBTotal Harmonic Distortion + Noise18 to 24-Bit0 dB-20 dB-60 dB 16-Bit0 dB-20 dB-60 dB -------75-75-35-75-73-33-67------------75-72-32-75-70-30-67-----dBdBdBdBdBdBOther Characteristics for R L = 16 Ω or 10 kΩOutput Parameters Modulation Index (MI) (Note 10)Analog Gain Multiplier (G)-0.67870.6047--0.67870.6047-Full-scale Output Voltage (2•G•MI•VA) (Note 10)Refer to Table “Line Output Voltage Characteristics” onpage18VppFull-scale Output Power (Note 10)Refer to Table “Headphone Output Power Characteristics” onpage19Interchannel Isolation (1 kHz)16 Ω10 kΩ--8095----8093--dBdBInterchannel Gain Mismatch-0.10.25-0.10.25dB Gain Drift-±100--±100-ppm/°C AC-Load Resistance (R L)(Note 11)16--16--ΩLoad Capacitance (C L)(Note 11)--150--150pF。

领世达K518PRO全功能防盗匹配一体机用户手册说明书

K518KPO全功能防盗匹配一体机用户手册★使用前请仔细阅读完本使用说明书版权所有领世达对其发行的或与合作公司共同发行的包括但不限产品或服务的全部内容及领世达所属相关网站上的材料、软件等拥有版权等知识产权,受法律保护。

未经本公司书面许可,任何单位及个人不得以任何方式或理由对上述产品、服务、信息、材料的任何部分进行拷贝、修改、抄录、传播或与其他产品捆绑使用、销售等。

凡侵犯本公司版权等知识产权的,我司必依法追究其法律责任!产品领世达K518PRO全功能防盗匹配一体机及其相关资料仅用于汽车正常维修、诊断及检测,切勿用于违法违规行为。

若因使用我司产品触犯法律法规,本公司不承担任何法律责任。

本产品有一定的可靠性,但不排除可能产生的损失和破坏,对此产生的风险由用户自行承担,本公司不承担任何风险及责任。

声明单位:领世达法律事务部安全须知使用此产品前,请阅读本节信息,并了解这些信息。

有关更详细的信息,请参阅附录的“安全须知事项”。

1、请勿撞击、扔掷、针刺本产品,并避免跌落、挤压、弯曲。

2、请勿在浴室等潮湿的环境中使用本产品,并避免本产品被液体浸湿或冲洗。

在禁止使用本产品的场所,或者使用本产品会引起干扰或危险时,请关闭本产品。

3、请勿在驾驶汽车时使用本产品,以免妨碍安全驾驶。

4、在医疗场所,请遵守有关规定或条例。

在靠近医疗设备的区域,请关闭本产品。

5、在使用高精度的电子设备附近,请关闭本产品,否则可能导致电子设备故障。

6、请勿擅自拆卸本产品及附件,只有授权机构才可维修。

7、请勿将本产品及附件放置于具有强大电磁场的器具中。

8、请将本产品远离磁性设备,磁性设备的辐射会抹掉本产品上存储的信息。

9、请勿在高温处、有易燃气体的地方(如加油站附近)使用本产品。

10、使用本产品时,请遵守相关法律法规,并尊重他人隐私及合法权利。

目录版权声明 (1)安全须知 (2)目录 (3)第一章.注册引导 (4)第二章.产品概述 (5)2.1产品介绍 (5)2.2软硬件优势 (5)2.3产品参数 (6)2.4整机介绍 (6)2.5产品清单 (6)2.5整机介绍 (7)2.5.1K518PRO主机 (7)2.5.2OBDII转接头+转接线 (8)2.5.3采集模拟天线+采集L-JCD线 (10)2.5.4KPROG适配器 (11)2.6功能展示 (12)2.6.1主界面功能 (12)2.6.2特殊功能界面 (13)2.6.3系统设置界面 (14)2.6.4功能操作界面 (15)第三章.售后服务 (16)保修服务卡 (18)第一章:注册引导注:开机后,请连接好WIFI,进入注册流程。

NCP5181中文资料

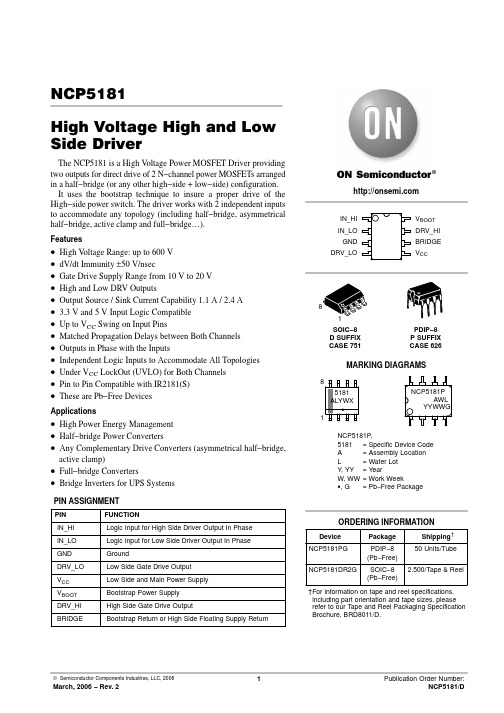

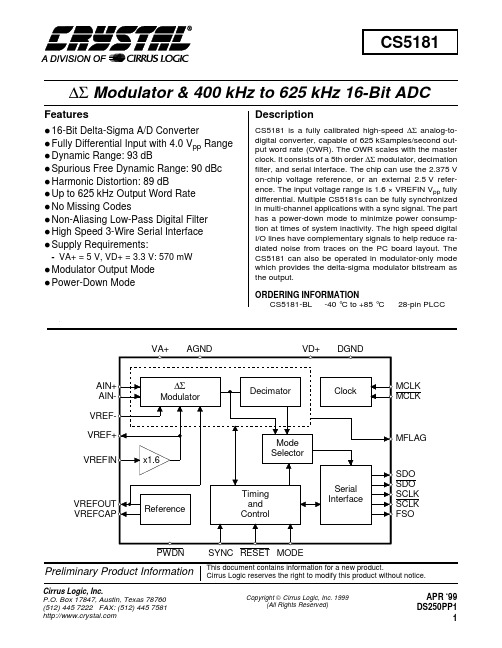

NCP5181High Voltage High and Low Side DriverThe NCP5181 is a High V oltage Power MOSFET Driver providing two outputs for direct drive of 2 N−channel power MOSFETs arranged in a half−bridge (or any other high−side + low−side) configuration. It uses the bootstrap technique to insure a proper drive of the High−side power switch. The driver works with 2 independent inputs to accommodate any topology (including half−bridge, asymmetrical half−bridge, active clamp and full−bridge…).Features•High V oltage Range: up to 600 V•dV/dt Immunity ±50 V/nsec•Gate Drive Supply Range from 10 V to 20 V•High and Low DRV Outputs•Output Source / Sink Current Capability 1.1 A / 2.4 A•3.3 V and 5 V Input Logic Compatible•Up to V CC Swing on Input Pins•Matched Propagation Delays between Both Channels •Outputs in Phase with the Inputs•Independent Logic Inputs to Accommodate All Topologies •Under V CC LockOut (UVLO) for Both Channels•Pin to Pin Compatible with IR2181(S)•These are Pb−Free DevicesApplications•High Power Energy Management•Half−bridge Power Converters•Any Complementary Drive Converters (asymmetrical half−bridge, active clamp)•Full−bridge Converters•Bridge Inverters for UPS SystemsPIN ASSIGNMENTPINFUNCTIONIN_HI Logic Input for High Side Driver Output In Phase IN_LO Logic Input for Low Side Driver Output In Phase GND GroundDRV_LO Low Side Gate Drive OutputV CC Low Side and Main Power SupplyVBOOT Bootstrap Power SupplyDRV_HI High Side Gate Drive OutputBRIDGE Bootstrap Return or High Side Floating Supply ReturnMARKING DIAGRAMSPDIP−8P SUFFIXCASE 626Device Package Shipping†ORDERING INFORMATIONNCP5181P,5181= Specific Device CodeA= Assembly LocationL= Wafer LotY, YY= YearW, WW= Work WeekG, G= Pb−Free PackageNCP5181PAWLYYWWGSOIC−8D SUFFIXCASE 751NCP5181PG PDIP−8(Pb−Free)50 Units/TubeNCP5181DR2G SOIC−8(Pb−Free)2.500/Tape & Reel†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.IN_HIIN_LOGNDDRV_LOV BOOTDRV_HIBRIDGEV CCFigure 1. Typical ApplicationFigure 2. Detailed Block DiagramMAXIMUM RATINGSRating Symbol Value Unit Main power supply voltage V CC−0.3 to 20V VHV: High Voltage BRIDGE pin V BRIDGE−1 to 600V VHV: Floating supply voltage V BOOT − V BRIDGE0 to 20V VHV: High side output voltage V DRV_HI V BRIDGE−0.3 to V BOOT+0.3V Low side output voltage V DRV_LO−0.3 to V CC+0.3V Allowable output slew rate dV BRIDGE/d t50V/ns Inputs IN_HI, IN_LO V IN_XX−1.0 to V CC+0.3V ESD Capability:HBM model (all pins except pins 6−7−8) Machine model (all pins except pins 6−7−8)2.0200kVVLatch up capability per Jedec JESD78 Power dissipation and thermal characteristicsPDIP8: Thermal resistance, Junction−to−Air SO−8: Thermal resistance, Junction−to−Air R q JAR q JA100178°C/WOperating junction temperature T J_minT J_max−55+150°CMaximum ratings are those values beyond which device damage can occur. Maximum ratings applied to the device are individual stress limit values (not normal operating conditions) and are not valid simultaneously. If these limits are exceeded, device functional operation is not implied, damage may occur and reliability may be affected.ELECTRICAL CHARACTERISTICS (V CC = V boot = 15 V, V gnd = V bridge, −40°C < T A< 125°C, Outputs loaded with 1 nF)Rating Symbol T A −40°C to 125°C Units OUTPUT SECTIONMin Typ MaxI DRVhigh− 1.4−A Output high short circuit pulsed currentV DRV= 0 V, PW ≤ 10 m s, (Note 1)I DRVlow− 2.2−A Output low short circuit pulsed currentV DRV= V CC, PW ≤ 10 m s, (Note 1)R OH−512W Output resistor (Typical value @ 25°C only)SourceOutput resistor (Typical value @ 25°C only)R OL−28W SinkDYNAMIC OUTPUT SECTIONRating Symbol Min Typ Max Units Turn−on propagation delay (V bridge = 0 V)t ON−100170ns Turn−off propagation delay (V bridge = 0 V or 50 V) (Note 2)t OFF−100170nst r−4060ns Output voltage rise time(from 10% to 90% @ V CC = 15 V) with 1 nF loadt f−2040ns Output voltage falling edge(from 90% to 10% @ V CC = 15 V) with 1 nF loadD t−2035ns Propagation delay matching between the High side and the Low side@ 25°C (Note 3)Minimum input pulse width that changes the output t PW−−100ns INPUT SECTIONLow level input voltage threshold V IN−−0.8V Input pull−down resistor (V IN < 0.5 V)R IN−200−k W High level input voltage threshold V IN 2.3−−V SUPPLY SECTIONV CC UV Start−up voltage threshold V CC_stup7.98.99.8V V CC UV Shut−down voltage threshold V CC_shtdwn7.38.29.0V Hysteresis on V CC V CC_hyst0.30.7−V V boot Start−up voltage threshold reference to bridge pinV boot_stup7.98.99.8V (V boot_stup = V boot − V bridge)V boot UV Shut−down voltage threshold V boot_shtdwn7.38.29.0V Hysteresis on V boot V boot_shtdwn0.30.7−VI HV_LEAK−0.540m A Leakage current on high voltage pins to GND(V BOOT= V BRIDGE= DRV_HI = 600 V)I CC1− 4.5 6.5mA Consumption in active mode(V CC= V boot, f sw= 100 kHz and 1 nF load on both driver outputs)Consumption in inhibition mode (V CC= V boot)I CC2−250400m A V CC current consumption in inhibition mode I CC3−215−m A V boot current consumption in inhibition mode I CC4−35−m A *Note: see also characterization curves1.Guaranteed by design.2.Turn−off propagation delay @ V bridge = 600 V is guaranteed by design3.See characterization curve for D t parameters variation on the full range temperature.4.Timing diagram definition see Figures 4, 5 and 6.IN_HI IN_LODRV_HI DRV_LOIN_HI 50%90%90%10%10%IN_LODRV_HI DRV_LO50%Figure 3. Input/Output Timing DiagramFigure 4. Switching Time Waveform Definitions50%90%10%50%90%10%DRV_HIDRV_LOIN_LO IN_HIDelta_t Delta_tFigure 5. Delay Matching Waveforms Definition50%90%10%50%90%10%DRV_HIDRV_LOIN_LO IN_HIDelta_tDelta_t&Figure 6. Other Delay Matching Waveforms Definitiont ont rt offt ft ont off t ont off t on_HIt on_LOt on_LOt off_HITYPICAL CHARACTERISTICS020406080100120160020406080100160180Figure 11. High Side Turn−on PropagationDelay vs. V BRIDGE Voltage Figure 12. High Side Turn−off PropagationDelay vs. V BRIDGE VoltageBRIDGE PIN VOLTAGE (V)BRIDGE PIN VOLTAGE (V)507090*********T o n P R O P A G A T I O N D E L A Y (n s )120140T o f f P R O P A G A T I O N D E L A Y (n s )T o n P R O P A G A T I O N D E L A Y (n s )TYPICAL CHARACTERISTICS05.0101520253040Figure 15. Turn−off Fall Time vs. TemperatureFigure 16. Turn−off Fall Time vs. V CC Voltage(V CC = V boot )TEMPERATURE (°C)SUPPLY VOLTAGE; V CC = V boot (V)05.010********Figure 17. Propagation Delay Matching Between High Side and Low Side Driver35T U R N −O N R I S E T I M E (n s )T U R N −O F F F A L L T I M E (n s )TEMPERATURE (°C)10080604020−20−400510152025304012035P R O P A G A T I O N D E L A Y M A T C H I N G (n s )TYPICAL CHARACTERISTICSFigure 18. Low Level Input Voltage Thresholdvs. TemperatureFigure 19. Low Level Input Voltage Thresholdvs. V CC VoltageTEMPERATURE (°C)SUPPLY VOLTAGE; V CC = V boot (V)00.20.61.01.420181614121000.20.41.01.4L O W L E V E L I N P U T V O L T A G E T H R E S H O L D (V )L O W L E V E L I N P U T V O L T A G E T H R E S H O L D (V )10080604020−20−401200.40.81.20.60.81.2Figure 20. High Level Input Voltage Thresholdvs. TemperatureFigure 21. High Level Input Voltage Thresholdvs. V CC VoltageTEMPERATURE (°C)SUPPLY VOLTAGE; V CC = V boot (V)100806040200−20−4000.51.01.52.520181********0.51.01.52.02.5Figure 22. Leakage Current on High Voltage Pins (600 V) to Ground vs. TemperatureFigure 23. Leakage Current on High VoltagePins to Ground vs. V bridge Voltage(V bridge = V boot = V DRV_HI )TEMPERATURE (°C)BRIDGE PIN VOLTAGE (V)100806040200−20−4000.51.01.52.53.04.060040030020010000.050.100.150.200.250.401202.0120L E A K A G E C U R R E N T T O G N D (m A )H I G H S I D E L E A K A G E C U R R E N T T O G N D (m A )0.300.35H I G H L E V E L I N P U T V O L T A G E T H R E S H O L D (V )H I G H L E V E L I N P U T V O L T A G E T H R E S H O L D (V )2.03.5500TYPICAL CHARACTERISTICSFigure 24. High Side Supply Current vs.TemperatureFigure 25. High Side Supply Current vs.Bootstrap Supply VoltageTEMPERATURE (°C)BOOTSTRAP SUPPLY VOLTAGE (V)040100201816141210020100B O O T S T R A P S U P P L YC U R R E N T (m A )B O O T S T R A P S U P P L YC U R R E N T (m A )100806040200−20−40120206080406080Figure 26. V CC Supply Current vs.TemperatureFigure 27. V CC Supply Current vs. V CC SupplyVoltageTEMPERATURE (°C)V CC , SUPPLY VOLTAGE (V)100806040200−20−401002003004005002018161412100100200300400500Figure 28. UVLO Start Up Voltage vs.Temperature Figure 29. UVLO Shut Down Voltage vs.Bootstrap Supply VoltageTEMPERATURE (°C)TEMPERATURE (°C)10120V C C S U P P L Y C U R R E N T (m A )V C C S U P P L Y C U R R E N T (m A )U V L O S T A R T U P V O L T A G E t h (V )U V L O S H U T D O W N V O L T A G E t h (V )TYPICAL CHARACTERISTICSFigure 30. ICC1 Consumption vs. Switching Frequency with 15 nC Load on Each DriverFigure 31. ICC1 Consumption vs. Switching Frequency with 33 nC Load on Each DriverSWITCHING FREQUENCY (kHz)SWITCHING FREQUENCY (kHz)05.0152535010204060I C C + I b o o t C U R R E N T S U P P L Y (m A )I C C + I b o o t C U R R E N T S U P P L Y (m A )1020303050Figure 32. ICC1 Consumption vs. Switching Frequency with 50 nC Load on Each Driver Figure 33. ICC1 Consumption vs. Switching Frequency with 100 nC Load on Each DriverSWITCHING FREQUENCY (kHz)SWITCHING FREQUENCY (kHz)01020304050608070I C C + I b o o t C U R R E N T S U P P L Y (m A )11PACKAGE DIMENSIONSSOIC−8 NB CASE 751−07NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.4.MAXIMUM MOLD PROTRUSION 0.15 (0.006)PER SIDE.5.DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBARPROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.6.751−01 THRU 751−06 ARE OBSOLETE. NEWSTANDARD IS 751−07.DIM A MIN MAX MIN MAX INCHES4.805.000.1890.197MILLIMETERS B 3.80 4.000.1500.157C 1.35 1.750.0530.069D 0.330.510.0130.020G 1.27 BSC 0.050 BSC H 0.100.250.0040.010J 0.190.250.0070.010K 0.40 1.270.0160.050M 0 8 0 8 N 0.250.500.0100.020S5.806.200.2280.244YM0.25 (0.010)Z SXS____ǒmm inchesǓSCALE 6:1*For additional information on our Pb−Free strategy and solderingdetails, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT*PACKAGE DIMENSIONS8 LEAD PDIP CASE 626−05NOTES:1.DIMENSION L TO CENTER OF LEAD WHEN FORMED PARALLEL.2.PACKAGE CONTOUR OPTIONAL (ROUND OR SQUARE CORNERS).3.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.DIM MIN MAX MIN MAX INCHESMILLIMETERS A 9.4010.160.3700.400B 6.10 6.600.2400.260C 3.94 4.450.1550.175D 0.380.510.0150.020F 1.02 1.780.0400.070G 2.54 BSC 0.100 BSC H 0.76 1.270.0300.050J 0.200.300.0080.012K 2.92 3.430.1150.135L 7.62 BSC 0.300 BSC M −−−10 −−−10 N0.76 1.010.0300.040__ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATIONThe product described herein (NCP5181), is covered by U.S. patent: 6,362, 067. There may be some other patent pending.。

MAX5181BEEG+中文资料

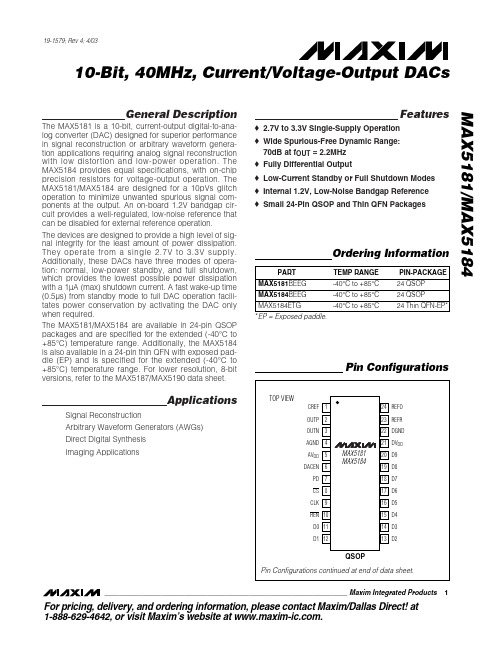

Ordering Information

PART

TEMP RANGE

MAX5181BEEG

-40°C to +85°C

MAX5184BEEG

-40°C to +85°C

MAX5184ETG

-40°C to +85°C

*EP = Exposed paddle.

PIN-PACKAGE 24 QSOP 24 QSOP 24 Thin QFN-EP*

Storage Temperature Range .............................-65°C to +150°C Lead Temperature (soldering, 10s) .................................+300°C

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

NCP5181 36 W镇流器评估板用户手册说明书

NCP5181BAL36WEVB NCP5181 36 W Ballast Evaluation Board User's ManualDescriptionThis document describes how the NCP5181 driver can be implemented in a ballast application. The scope of this evaluation board user’s manual is to highlight the NCP5181driver and not to explain or detail how to build an electronic ballast.The NCP5181 is a high voltage power MOSFET driver providing two outputs for direct drive of two N-channel power MOSFETs arranged in a half-bridge (or any other high-side + low-side topology) configuration.It uses the bootstrap technique to ensure a proper drive of the high-side power switch. The driver works with two independent inputs to accommodate with any topology (including half-bridge, asymmetrical half-bridge, active clamp and full-bridge).Evaluation Board Specification•Input Range: 85−145Vac OR 184−265Vac •Ballast Output Power: 36W (type PL −L 36W)•Pre-heating Current: 295mA •Pre-heating Time: 1second •Nominal Current: 414mADetailed OperationThe lamp ballast is powered via a half bridge configuration. The two power MOSFETs are driven with the NCP5181 driver. The driver is supplied by the V CC rail, and the high side driver is supplied by the bootstrap diode: when the low side power MOSFET (Q2) is switched ON, the BRIDGE pin is pulled down to the ground, thus the capacitor connected between the BRIDGE pin and VBOOT pin is refuelled via the diode D3 and the resistor R5 connected to V CC . When Q2 is switched OFF, the bootstrap capacitor C6supplies the high side driver with a voltage equal to V CC level minus D3 forward voltage diode. Given the NCP5181architecture, it is up to the designer to generate the right input signal polarity. This includes a dead time to avoid a short circuit between the high and low side power MOSFET.The 555 timer generates only one signal for the driver, the second one, in opposite phase is built by inserting an NPN transistor (Q4) for inverting the signal. Afterwards, the dead time is built with R2, D2 and C13 (typically 260ns, see Figure 2).Figure 1. NCP5181 Evaluation BoardWARNING:BEFORE PLUGGING IN THE EVALUATION BOARD, MAKE SURE THE JUMPER IS IN THE CORRECT POSITION: IF J2IS USED, THEN Vin MUST BE LOWER THAN 145Vac.EVAL BOARD USER’S MANUALNCP5181BAL36WEVBDRV_HI (5 V/div)DRV_LO (5 V/div)Time(400 ns/div)Dead time260nsFigure 2. Dead Time Between the High and Low Side DriverIN_HI (10 V/div)DRV_HI (10 V/div)IN_LO(10 V/div)DRV_LO (10 V/div)Time (4 μs/div)Figure 3. Input Output Timing DiagramTube V oltage (100 V /div)Tube current (0.5 V /div)Tube Power (50W/div)TubeAverage power = 32WFigure 4. Tube SignalsNCP5181BAL36WEVBFigure 5. Evaluation Board Schematic720n F 00V820n F 00VFigure 6. PCB Printout: Top and Bottom ViewTEST PROCEDUREFigure 7. Test Setup ConnectionR Load 200 WTable 1. REQUIRED EQUIPMENTAC Power Source can be able to deliver 230V rms or 110V rmsTwo Volt-metersTwo Ampere-meters1 Resistive Load: 200W /50WOne NCP5181 Evaluation Board−Test Procedure1.First of all check if you need jumper #2 (J2 on the board close the diode bridge). This jumper must be removed for use with European mains (230Vac input voltage), and must be in place when using US mains (110Vac). This jumper is used to build a voltage doubler just after the bridge diode in case one is using US mains input voltage range.2.Connect the test setup as shown in Figure 7:•AC Source•V oltmeter and Ampmeter on the Load •Load on the Output3.Apply 230Vac for European mains or 110Vac for US mains on the input connector.4.Check I Load and V Load with the appropriate value in the table below.5.If you get the correct output and input voltage, you can then connect a 36W fluorescent tube on the output (see Figure 8).Table 2. TEST RESULTSInput Mains J2V in (V rms )I in (A rms)V Load (V rms )ILoad (A rms )European Removed230V 278mA 303V 370mA US Yes → Max Input Voltage: 132 V rms110V514mA263V340mAFigure 8. Ballast ConnectionInput ConnectionOutput Connection36W TubeTable 3. BILL OF MATERIAL FOR THE NCP5181 EVALUATION BOARDDesignator Qty.Description Value Tolerance Footprint Manufacturer ManufacturerPart NumberSubstitutionAllowedLeadFreeU21NCP5181NA NA DIP8ON Semiconductor NCP5181PG No Yes U11CMOS IC Analog/Timer NA DIP8Texas Instruments TLC555CP Yes No C1, C22Electrolytic Capacitor47m F, 400V20%Radial Panasonic ECA2GM470Yes No C31Electrolytic Capacitor220m F, 16V20%Radial Panasonic ECA1CM221Yes No C41Electrolytic Capacitor 4.7m F, 63V20%Radial Panasonic EEUEB1J4R7Yes No C5, C62Capacitor100nF, 50V10%Radial Murata RPER71H104K2M1A05U Yes No C7, C82Capacitor220nF, 400V10%Radial Vishay MKT1822422405Yes No C9, C102Capacitor220nF, 100V5%Radial Murata RPE5C2A221J2M1Z05A Yes No C111Capacitor10nF, 100V10%Radial Murata RPER72A103K2M1B05A Yes No C12, C132Capacitor18pF, 100V2%Radial Vishay2252 586 20154Yes Yes C141Capacitor220pF, 400V10%Radial Panasonic ECKATS221KB Yes No C151Capacitor 6.8nF, 1600V5%Radial Vishay2222 375 30682Yes No C161Capacitor NC−Radial−−−−C171Electrolytic Capacitor100m F, 16V20%Radial Panasonic ECA1CM101Yes No D11Zener Diode15V, 1.3W5%Axial Vishay BZX85C15Yes No D21High-speed Diode0.2A, 75V NA Axial PhilipsSemiconductor1N4148Yes No D3, D5, D63Rectifier Diode1A, 400V NA Axial ON Semiconductor1N4936G Yes Yes D41Zener Diode 5.1V, 1.3W5%Axial Vishay BZX85C5V1Yes No F11Fuse500mA, 250V NA Radial Schurter0034.6612Yes No L11Inductor 1.4mH NA NA Vogt53−044No No PT11Diode Bridge600V, 1A NA DFM Vishay DF06M Yes No R11Resistor12k W, 0.33W5%Axial Vishay CFA020712K Yes No R21Resistor82k W, 0.33W5%Axial Vishay CFA020782K Yes No R3, R42Resistor82k W, 3W5%Axial Vishay CPF382K000JN Yes No R5, R6, R73Resistor10W, 0.33W5%Axial Vishay CFA020710R Yes No R8, R92Resistor10k W, 0.33W5%Axial Yageo CFA020710K Yes No R101Resistor33k W, 0.33W5%Axial Vishay CFA020733K Yes No R111Resistor47k W, 0.33W5%Axial Vishay CFA020747K Yes No R121Resistor27k W, 0.33W5%Axial Vishay CFA020727K Yes No R131Resistor15k W, 0.33W5%Axial Vishay CFA020715K Yes No R141Resistor390k W, 0.33W5%Axial Vishay CFA0207390K Yes No R151Resistor22k W, 0.33W5%Axial Vishay CFA020722K Yes No R161Resistor68 k W, 0.33 W5%Axial Vishay CFA020768K Yes NoQ1, Q22Power MOSFETN-channel 8A, 500V NA TO220InternationalRectifierIRF840LC Yes NoQ3, Q42NPN Transistor100mA, 45V NA TO−92ON Semiconductor BC547BG Yes Yes B1, J12Connector2/″NA 5.08mm Weidmuller PM5.08/2/90(1760510000)Yes No J21Jumper Resistor0W, 0.25W NA Axial Yageo ZOR−25−B−52Yes NoADDITIONAL INFORMATIONTECHNICAL PUBLICATIONS :Technical Library: /design/resources/technical−documentation onsemi Website: ONLINE SUPPORT : /supportFor additional information, please contact your local Sales Representative at /support/sales。

TEA1753TN1,518;中文规格书,Datasheet资料

2.4 Flyback green features

Valley switching for minimum switching losses (NXP patented) Frequency reduction with adjustable minimum peak current at low-power operation to maintain high efficiency at low output power levels

3 ofductors

TEA1753T

HV start-up flyback controller with integrated PFC controller

5. Block diagram

3)&'5,9(5 3)& GULYHU

TEA1753T

HV start-up DCM/QR flyback controller with integrated DCM/QR PFC controller

Rev. 3 — 24 August 2012 Product data sheet

1. General description

The TEA1753T is the third generation of green Switched Mode Power Supply (SMPS) controller ICs. The TEA1753T combines a controller for Power Factor Correction (PFC) and a flyback controller. Its high level of integration allows the design of a cost-effective power supply with a very low number of external components. The special built-in green functions provide high efficiency at all power levels. This efficiency applies to quasi-resonant operation at high-power levels, quasi-resonant operation with valley skipping, as well as reduced frequency operation at lower power levels. At low-power levels, the PFC switches off to maintain high efficiency. During low-power conditions, the flyback controller switches to frequency reduction mode and limits the peak current to an adjustable minimum value. This mode ensures high efficiency at low-power and good standby power performance while minimizing audible noise from the transformer. The controller is switched to the power-down mode for no-load operation. In this mode, the controller is shut down for very low standby power applications. The TEA1753T is a Multi-Chip Module, (MCM), containing two chips. The proprietary high-voltage BCD800 process which makes direct start-up possible from the rectified universal mains voltage in an effective and green way. The second low voltage Silicon On Insulator (SOI) is used for accurate, high-speed protection functions and control. The TEA1753T enables the design of highly efficient and reliable supplies with power requirements of up to 250 W using the minimum number of external components. Remark: All values provided throughout this data sheet are typical values unless otherwise stated.

ControlLogix 類比 I O 模組 1756-IF16、1756-IF6CIS、1756-

AI-518 518P 型人工智能温度控制器 说明书 v7.1

(一)显示状态....................................................................................................................17 (二)基本使用操作.............................................................................................................19 (三)AI 人工智能调节及自整定(AT)操作 ............................................................................20 (四)程序操作(仅适用 AI-518P 型)................................................................................22

NCP1582资料

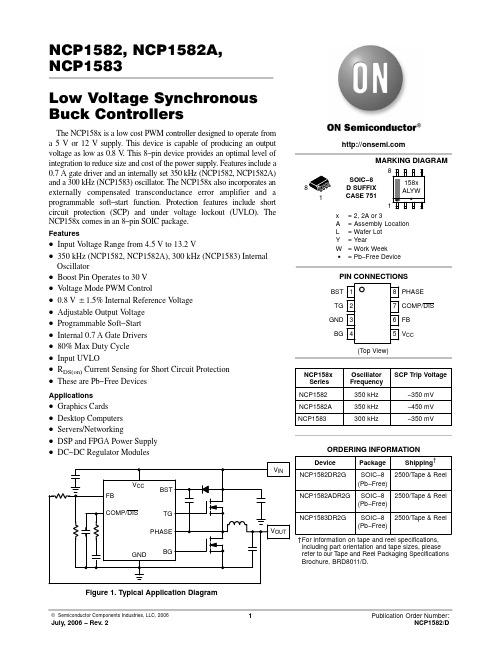

NCP1582, NCP1582A,NCP1583Low Voltage Synchronous Buck ControllersThe NCP158x is a low cost PWM controller designed to operate from a 5 V or 12 V supply. This device is capable of producing an output voltage as low as 0.8 V. This 8−pin device provides an optimal level of integration to reduce size and cost of the power supply. Features include a0.7 A gate driver and an internally set 350 kHz (NCP1582, NCP1582A) and a 300 kHz (NCP1583) oscillator. The NCP158x also incorporates an externally compensated transconductance error amplifier and a programmable soft−start function. Protection features include short circuit protection (SCP) and under voltage lockout (UVLO). The NCP158x comes in an 8−pin SOIC package.Features•Input V oltage Range from 4.5 V to 13.2 V•350 kHz (NCP1582, NCP1582A), 300 kHz (NCP1583) Internal Oscillator•Boost Pin Operates to 30 V•V oltage Mode PWM Control•0.8 V $1.5% Internal Reference V oltage•Adjustable Output V oltage•Programmable Soft−Start•Internal 0.7 A Gate Drivers•80% Max Duty Cycle•Input UVLO•R DS(on) Current Sensing for Short Circuit Protection •These are Pb−Free DevicesApplications•Graphics Cards•Desktop Computers•Servers/Networking•DSP and FPGA Power Supply•DC−DC Regulator ModulesFigure 1. Typical Application DiagramSOIC−8D SUFFIXCASE 7511MARKING DIAGRAMPIN CONNECTIONSx= 2, 2A or 3A= Assembly LocationL= Wafer LotY= YearW= Work WeekG= Pb−Free DeviceBST PHASETGGNDBGCOMP/DISFBV CC(Top View)Device Package Shipping†ORDERING INFORMATIONNCP1582DR2G SOIC−8(Pb−Free)2500/Tape & Reel†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our T ape and Reel Packaging Specifications Brochure, BRD8011/D.NCP1582ADR2G SOIC−8(Pb−Free)2500/Tape & ReelNCP1583DR2G SOIC−8(Pb−Free)2500/Tape & Reel NCP158xSeriesOscillatorFrequencySCP Trip Voltage NCP1582350 kHz−350 mV NCP1582A350 kHz−450 mV NCP1583300 kHz−350 mVFigure 2. Typical VGA Card Application DiagramFigure 3. Detailed Block DiagramV CCTG BST PHASEBG GNDPIN FUNCTION DESCRIPTIONPin No.Symbol Description1BST Supply rail for the floating top gate driver. To form a boost circuit, use an external diode to bring thedesired input voltage to this pin (cathode connected to BST pin). Connect a capacitor (C BST) between this pinand the PHASE pin. Typical values for C BST range from 0.1 m F to 1 m F. Ensure that C BST is placed near the IC.2TG Top gate MOSFET driver pin. Connect this pin to the gate of the top N−Channel MOSFET.3GND IC ground reference. All control circuits are referenced to this pin.4BG Bottom gate MOSFET driver pin. Connect this pin to the gate of the bottom N−Channel MOSFET.5V CC Supply rail for the internal circuitry. Operating supply range is 4.5 V to 15 V. Decouple with a 1 m Fcapacitor to GND. Ensure that this decoupling capacitor is placed near the IC.6FB This pin is the inverting input to the error amplifier. Use this pin in conjunction with the COMP pin tocompensate the voltage−control feedback loop. Connect this pin to the output resistor divider (if used) ordirectly to Vout.7COMP/DIS Compensation Pin. This is the output of the error amplifier (EA) and the non−inverting input of the PWM comparator. Use this pin in conjunction with the FB pin to compensate the voltage−control feedback loop. Thecompensation capacitor also acts as a soft−start capacitor. Pull this pin low with an open drain transistor fordisable.8PHASE Switch node pin. This is the reference for the floating top gate driver. Connect this pin to the source of the top MOSFET.ABSOLUTE MAXIMUM RATINGSPin Name Symbol V MAX V MINMain Supply Voltage Input V CC15 V−0.3 VBootstrap Supply Voltage Input BST30 V wrt/GND15 V wrt/PHASE−0.3 VSwitching Node (Bootstrap Supply Return)PHASE24 V−0.7 V−5 V for < 50 nsHigh−Side Driver Output (Top Gate)TG30 V wrt/GND15 V wrt/PHASE−0.3 V wrt/PHASELow−Side Driver Output (Bottom Gate)BG15 V−0.3 V−2 V for < 200 ns Feedback FB 5.5 V−0.3 V COMP/DISABLE COMP/DIS 5.5 V−0.3 VMAXIMUM RATINGSRating Symbol Value Unit Thermal Resistance, Junction−to−Ambient R q JA165°C/W Thermal Resistance, Junction−to−Case R q JC45°C/W Operating Junction Temperature Range T J−40 to 150°C Operating Ambient Temperature Range T A−40 to 85°C Storage Temperature Range T stg−55 to +150°CLead Temperature Soldering (10 sec): Reflow (SMD styles only) Pb−Free(Note 1)260 peak°C Moisture Sensitivity Level MSL1−Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.1.60−180 seconds minimum above 237°C.ELECTRICAL CHARACTERISTICS (0_C < T A < 70_C, −40_C < T J < 125_C (Note 2), 4.5 V < V CC < 13.2 V, 4.5 V < BST < 26.5 V, C TG= C BG= 1.0 nF(REF:NTD30N02), for min/max values unless otherwise noted.)Characteristic Conditions Min Typ Max Unit Input Voltage Range⎯ 4.513.2V Boost Voltage Range⎯ 4.526.5V Supply CurrentQuiescent Supply Current V FB = 1.0 V, No SwitchingV CC= 13.2 V− 1.0 1.75mA Boost Quiescent Current V FB = 1.0 V, No Switching−140−m A Under Voltage LockoutUVLO Threshold V CC Rising Edge 3.85 4.2V UVLO Hysteresis⎯−0.5V Switching RegulatorVFB Feedback Voltage, Control Loop in Regulation T A = 0 to 70°C−40 to 125°C0.7880.80.80.812VOscillator Frequency (NCP1582, NCP1582A)T A = 0 to 70°C−40 to 125°C300350350400kHzOscillator Frequency (NCP1583)T A = 0 to 70°C−40 to 125°C 275300300325kHzRamp−Amplitude Voltage− 1.1−V Minimum Duty Cycle−0−% Maximum Duty Cycle707580% Minimum Pulse Width Static Operating100150ns Blanking Time50ns BG Minimum On Time~500ns Error Amplifier (GM)Transconductance 5.0mmho Open Loop DC Gain5570−DBOutput Source Current Output Sink Current V FB = 0.8 VV FB > 0.8 V8080120120m Am AInput Offset Voltage−2.00 2.0mV Input Bias Current0.1 1.0m A Unity Gain Bandwidth 4.0Mhz Soft−StartSS Source Current V FB < 0.8 V 5.01015m A Switch Over Threshold100% of Vref Current LimitTrip Voltage (NCP1582, NCP1583)Vphase to ground−350mV Trip Voltage (NCP1582A)Vphase to ground−450mV Gate DriversUpper Gate Source Vgs = 6.0 V−0.7A Upper Gate Sink Vugate wrt Phase = 1.0 V 2.4W Lower Gate Source Vgs = 6.0 V−0.7A Lower Gate Sink Vlgate wrt GND = 1.0 V 2.2W PHASE Falling to BG Rising Delay V CC = 12 V, PHASE < 2.0 V, BG > 2.0 V−3090ns BG Falling to TG Rising Delay V CC = 12 V, BG < 2.0 V, TG > 2.0 V−3060ns Enable Threshold0.4V 2.Specifications to −40°C are guaranteed via correlation using standard quality control (SQC), not tested in production.TYPICAL OPERATING CHARACTERISTICSF S W , F R E Q U E N C Y (k H z )V r e f , R E F E R E N C E V O L T A G E (m V )−50−250255075100125T J , JUNCTION TEMPERATURE (°C)S O F T S T A R T S O U R C I N G C U R R E N T (m A )Figure 8. Soft Start Sourcing Current vs.TemperatureFigure 9. I−Limit vs. TemperatureT J , JUNCTION TEMPERATURE (°C)−50−250255075100125DETAILED OPERATING DESCRIPTION GeneralThe NCP158x is an 8−pin PWM controller intended forDC−DC conversion from 5.0 V & 12 V buses. The NCP158xhas a 0.7 A internal gate driver circuit designed to driveN−channel MOSFETs in a synchronous−rectifier bucktopology. The output voltage of the converter can beprecisely regulated down to 800 mV 1.5% when the V FB pinis tied to V OUT. The switching frequency is internally set. Ahigh gain operational transconductance error amplifier(OTA) is used.Duty Cycle and Maximum Pulse Width LimitsIn steady state DC operation, the duty cycle will stabilizeat an operating point defined by the ratio of the input to theoutput voltage. The NCP158x can achieve an 80% dutycycle. There is a built in off−time which ensures that thebootstrap supply is charged every cycle. The NCP158x,which is capable of a 100 nsec pulse width (min.), can allow a 12 V to 0.8 V conversion at 350 kHz.Input Voltage Range (V CC and BST)The input voltage range for both V CC and BST is 4.5 V to 13.2 V with respect to GND and PHASE, respectively. Although BST is rated at 13.2 V with respect to PHASE, it can also tolerate 26.5 V with respect to GND.External Enable/DisableWhen the Comp pin voltage falls or is pulled externally below the 400 mv threshold, it disables the PWM Logic and the gate drive outputs. In this disabled mode, the operational transconductance error amplifier’s (EOTA) output source current is reduced and limited to the Soft Start current of 10m A. Normal Shutdown BehaviorNormal shutdown occurs when the IC stops switching because the input supply reaches UVLO threshold. In this case, switching stops, the internal SS is discharged, and all GATE pins go low. The switch node enters a high impedance state and the output capacitors discharge through the load with no ringing on the output voltage.External Soft StartThe NCP158x features an external soft start function, which reduces inrush current and overshoot of the output voltage. Soft start is achieved by using the internal current source of 10 m A. (typ), which charges the external integrator capacitor of the transconductance amplifier. Figure 10 is a typical soft start sequence. This sequence begins once V CC surpasses its UVLO threshold. During Soft Start, as the Comp Pin rises through 400 mV, the PWM Logic and gate drives are enabled. When the feedback voltage crosses 800mV, the EOTA will be given control to switch to its higher regulation mode output current of 120m A. In the event of an overcurrent during soft start, the overcurrent logic will override the soft start sequence and will shut down the PWM logic and both the high side and low side gates.Figure 10. Soft Start ImplementationVEnableVIsource/SinkTiming Diagram NCP1582: Enable SequenceUVLOUnder V oltage Lockout (UVLO) is provided to ensure that unexpected behavior does not occur when V CC is too low to support the internal rails and power the converter. For the NCP158x, the UVLO is set to ensure that the IC will start up when V CC reaches 4.2 V and shutdown when V CC drops below 3.7 V. This permits operation when converting from a 5.0 input voltage.Current Limit ProtectionIn case of a short circuit or overload, the low−side (LS) FET will conduct large currents. The controller will shut down the regulator in this situation for protection against overcurrent. The low−side R DSon sense is implemented by comparing the voltage at the Phase node when BG starts going low to an internally generated fixed voltage. If the phase voltage is lower than SCP trip voltage, an overcurrent condition occurs and a counter is initiated. When the counter completes, the PWM logic and both HS−FET and LS−FET are turned off. The controller will retry to see if the short circuit or overload condition is removed through the soft start cycle. The minimum turn−on time of the LS−FET is set to be 500 ns. The trip thresholds have a −95 mV, +45 mV process and temperature variation.DriversThe NCP158x includes 0.7 A gate drivers to switch external N−channel MOSFETs. This allows the NCP158x to address high−power as well as low−power conversion requirements. The gate drivers also include adaptive non−overlap circuitry. The non−overlap circuitry increase efficiency, which minimizes power dissipation, by minimizing the body diode conduction time.A detailed block diagram of the non−overlap and gate drive circuitry used in the chip is shown in Figure 11.Figure 11. Block Diagram of Gate Driverand Non−Overlap CircuitryPHASETG BSTV CC BGGNDCareful selection and layout of external components is required, to realize the full benefit of the onboard drivers.The capacitors between V CC and GND and between BST and SWN must be placed as close as possible to the IC. The current paths for the TG and BG connections must be optimized. A ground plane should be placed on the closest layer for return currents to GND in order to reduce loop area and inductance in the gate drive circuit.APPLICATION SECTIONInput Capacitor SelectionThe input capacitor has to sustain the ripple current produced during the on time of the upper MOSFET, so it must have a low ESR to minimize the losses. The RMS value of this ripple is:Iin RMS +I OUT D (1*D)Ǹ,where D is the duty cycle, Iin RMS is the input RMS current,& I OUT is the load current. The equation reaches its maximum value with D = 0.5. Losses in the input capacitors can be calculated with the following equation:P CIN +ESR CIN Iin RMS 2,where P CIN is the power loose in the input capacitors &ESR CIN is the effective series resistance of the input capacitance. Due to large d I /d t through the input capacitors,electrolytic or ceramics should be used. If a tantalum must be used, it must be surge protected. Otherwise, capacitor failure could occur.Calculating Input Start−up CurrentTo calculate the input start up current, the following equation can be used.I inrush +C OUT V OUTt SS,where I inrush is the input current during start−up, C OUT is the total output capacitance, V OUT is the desired output voltage,and t SS is the soft start interval.If the inrush current is higher than the steady state input current during max load, then the input fuse should be rated accordingly, if one is used.Calculating Soft Start TimeTo calculate the soft start time, the following equation can be used.t SS +(C P )C C)*D VI SSWhere C C is the compensation as well as the soft start capacitor,C P is the additional capacitor that forms the second pole.I SS is the soft start currentD V is the comp voltage from zero to until it reachesregulation.V compV outThe above calculation includes the delay from comp rising to when output voltage becomes valid.To calculate the time of output voltage rising to when it reaches regulation; D V is the difference between the comp voltage reaching regulation and 1.1 V .Output Capacitor SelectionThe output capacitor is a basic component for the fast response of the power supply. In fact, during load transient,for the first few microseconds it supplies the current to the load. The controller immediately recognizes the load transient and sets the duty cycle to maximum, but the current slope is limited by the inductor value.During a load step transient the output voltage initial drops due to the current variation inside the capacitor and the ESR. (neglecting the effect of the effective series inductance (ESL)):D V OUT−ESR +D I OUT ESR COUT ,where V OUT−ESR is the voltage deviation of V OUT due to the effects of ESR and the ESR COUT is the total effective series resistance of the output capacitors.A minimum capacitor value is required to sustain the current during the load transient without discharging it. The voltage drop due to output capacitor discharge is given by the following equation:D V OUT−DISCHARGE +D I OUT 2 L OUT2 C OUT (V IN D *V OUT ),where V OUT−DISCHARGE is the voltage deviation of V OUT due to the effects of discharge, L OUT is the output inductor value & V IN is the input voltage.It should be noted that ΔV OUT−DISCHARGE and V OUT−ESR are out of phase with each other, and the larger of these two voltages will determine the maximum deviation of the output voltage (neglecting the effect of the ESL).Inductor SelectionBoth mechanical and electrical considerations influence the selection of an output inductor. From a mechanical perspective, smaller inductor values generally correspond to smaller physical size. Since the inductor is often one of the largest components in the regulation system, a minimum inductor value is particularly important in space−constrained applications. From an electrical perspective, the maximum current slew rate through the output inductor for a buck regulator is given by:SlewRate LOUT +V IN *VOUT L OUT.This equation implies that larger inductor values limit the regulator’s ability to slew current through the output inductor in response to output load transients. Consequently,output capacitors must supply the load current until the inductor current reaches the output load current level. Thisresults in larger values of output capacitance to maintain tight output voltage regulation. In contrast, smaller values of inductance increase the regulator’s maximum achievable slew rate and decrease the necessary capacitance, at the expense of higher ripple current. The peak−to−peak ripple current is given by the following equation:Ipk *pk LOUT +V OUT (1*D)L OUT 350kHz,where Ipk−pk LOUT is the peak to peak current of the output.From this equation it is clear that the ripple current increases as L OUT decreases, emphasizing the trade−off between dynamic response and ripple current.Feedback and CompensationThe NCP158x allows the output of the DC−DC converter to be adjusted from 0.8 V to 5.0 V via an external resistor divider network. The controller will try to maintain 0.8 V at the feedback pin. Thus, if a resistor divider circuit was placed across the feedback pin to V OUT , the controller will regulate the output voltage proportional to the resistordivider network in order to maintain 0.8 V at the FB pin.FBThe relationship between the resistor divider network above and the output voltage is shown in the following equation:R 2+R 1 ǒV REFV OUT *V REFǓ.Resistor R1 is selected based on a design tradeoff between efficiency and output voltage accuracy. For high values of R1 there is less current consumption in the feedback network, However the trade off is output voltage accuracy due to the bias current in the error amplifier. The output voltage error of this bias current can be estimated using the following equation (neglecting resistor tolerance):Error%+0.1m A R 1V REF100%.Once R1 has been determined, R2 can be calculated.Figure 12. Type II Transconductance ErrorAmplifierR C Figure 12 shows a typical Type II transconductance error amplifier (EOTA). The compensation network consists of the internal error amplifier and the impedance networks ZIN (R 1, R 2) and external Z FB (R c , C c and C p ). The compensation network has to provide a closed loop transfer function with the highest 0 dB crossing frequency to have fast response (but always lower than F SW /8) and the highest gain in DC conditions to minimize the load regulation. A stable control loop has a gain crossing with −20dB/decade slope and a phase margin greater than 45°. Include worst−case component variations when determining phase margin. Loop stability is defined by the compensation network around the EOTA, the output capacitor, output inductor and the output divider. Figure 13. shows the open loop and closed loop gain plots.Compensation Network Frequency:The inductor and capacitor form a double pole at the frequencyF LC +12p @L O @C OǸThe ESR of the output capacitor creates a “zero” at the frequency,F ESR +12p @ESR @C O The zero of the compensation network is formed as,F Z +12p @R C C CThe pole of the compensation network is calculated as,F P +12p @R C @C PFigure 13. Gain Plot of the Error AmplifierG A I N (d B )FREQUENCY (Hz)100100010 k100 k1000 kThermal ConsiderationsThe power dissipation of the NCP158x varies with the MOSFETs used, V CC , and the boost voltage (V BST ). The average MOSFET gate current typically dominates the control IC power dissipation. The IC power dissipation is determined by the formula:P IC +(I CC @V CC ))P TG )P BG .Where:P IC = control IC power dissipation,I CC = IC measured supply current,V CC = IC supply voltage,P TG = top gate driver losses,P BG = bottom gate driver losses.The upper (switching) MOSFET gate driver losses are:P TG +Q TG @f SW @V BST .Where:Q TG = total upper MOSFET gate charge at V BST ,f SW = the switching frequency,V BST = the BST pin voltage.The lower (synchronous) MOSFET gate driver losses are:P BG.Where:Q BG = total lower MOSFET gate charge at V CC .The junction temperature of the control IC can then be calculated as:T J +T A )P IC @q JA .Where:T J = the junction temperature of the IC,T A = the ambient temperature,θJA = the junction−to−ambient thermal resistance of the IC package.The package thermal resistance can be obtained from the specifications section of this data sheet and a calculation can be made to determine the IC junction temperature. However,it should be noted that the physical layout of the board, the proximity of other heat sources such as MOSFETs and inductors, and the amount of metal connected to the IC,impact the temperature of the device. Use these calculations as a guide, but measurements should be taken in the actual application.Layout ConsiderationsAs in any high frequency switching converter, layout is very important. Switching current from one power device to another can generate voltage transients across the impedances of the interconnecting bond wires and circuit traces. These interconnecting impedances should be minimized by using wide, short printed circuit traces. The critical components should be located as close together as possible using ground plane construction or single point grounding. The figure below shows the critical power components of the converter. To minimize the voltage overshoot the interconnecting wires indicated by heavy lines should be part of ground or power plane in a printed circuit board. The components shown in the figure below should be located as close together as possible. Please note that the capacitors C IN and C OUT each represent numerous physical capacitors. It is desirable to locate the NCP158x within 1inch of the MOSFETs, Q1 and Q2. The circuit traces for the MOSFETs’ gate and source connections from the NCP158x must be sized to handle up to 2 A peak current.Figure 14. Components to be Considered forLayout SpecificationsRETURNNCP1582, NCP1582A, NCP1583 Design ExampleSwitching Frequency F SW = 350 KHZOutput Capacitance C ESR = 45 m W/EachOutput Capacitance C out = 6630 m FOutput Inductance L out = 0.75 m HInput V oltage V in = 12 VOutput V oltage V out = 3.3 VChoose the loop gain crossover frequency;F CO+110*F SW+35kHzThe corner frequency of the output filter is calculatedbelow;F LC+12*p*0.75m H*6630m FǸ+2.3kHzLet R C = 1500Check that the ESR zero frequency is not too high;F ESR+12*p@CESR@C O t F SW5This condition is mandatory for loop stability.Zero of the compensation network is calculated as follows;F Z+F LCC C+1Z C+12*p*2.3kHz*1500+46nFThe compensation capacitor also acts as the soft start capacitor. By adjusting the value of this compensation capacitor, the soft start time can be adjusted.Pole of the compensation network is calculated as follows;F P+5*F CO+175kHzC P+12*p*F P*R C+12*p*175kHz*1500+700pFThe recommended compensation values are;R C = 1500, C C = 46 nF, C P = 700 pFThe NCP158x bode plot as measured from the network analyzer is shown below.Figure 15. Typical Bode plot of the Open−loop Frequency Response of the NCP158x Top plot: Phase−Frequency (Phase Margin = 62.519°) Bottom plot: Gain−Frequency (UGBW= 5 MHz)NCP1582, NCP1582A, NCP1583 Demo Board PCB LayoutBill of MaterialsItem Number Part Reference Value Quantity MFG 1C1 C2 C3 C41500 m F4PANASONIC 2C5 C6 C722 m F3TDK3C8 1.0 m F1TAIYO YUDEN 4C9100 pF1AVX5C100.022 m F1KEMET6C110.1 m F1AVX7C12 C13 C14 C151800 m F4PANASONIC 8C16 C17 C18 C1910 m F4KEMET9C20OPEN1−10C21OPEN1−11CR1BAS116LT11ON SEMICONDUCTOR 12L10.75 m H1TOKO13Q1 Q240N032ON SEMICONDUCTOR 14R14021DALE15R2OPEN1−16R3 1.02 K1DALE17R4OPEN1−18R6 R702DALE19R8OPEN1−20U1NCP158x1ON SEMICONDUCTORTYPICAL PERFORMANCE CHARACTERISTICSFigure 16. Start UpFigure 17. Gate Waveforms15 A Load SustainingFigure 18. Transient Response (0−10 A Step Load)8083868992123456789101112131415LOAD CURRENT (A)E F F I C I E N C Y (%)Figure 19. Transient ResponseFigure 20. Over Current Protection (22 A DC Trip)Figure 21. Efficiency vs. Load CurrentPACKAGE DIMENSIONSSOIC−8D SUFFIXCASE 751−07ISSUE AHNOTES:1.DIMENSIONING AND TOLERANCING PERANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSION A AND B DO NOT INCLUDEMOLD PROTRUSION.4.MAXIMUM MOLD PROTRUSION 0.15 (0.006)PER SIDE.5.DIMENSION D DOES NOT INCLUDE DAMBARPROTRUSION. ALLOWABLE DAMBARPROTRUSION SHALL BE 0.127 (0.005) TOTALIN EXCESS OF THE D DIMENSION ATMAXIMUM MATERIAL CONDITION.6.751−01 THRU 751−06 ARE OBSOLETE. NEWSTANDARD IS 751−07.DIMAMIN MAX MIN MAXINCHES4.805.000.1890.197MILLIMETERSB 3.80 4.000.1500.157C 1.35 1.750.0530.069D0.330.510.0130.020G 1.27 BSC0.050 BSCH0.100.250.0040.010J0.190.250.0070.010K0.40 1.270.0160.050M0 8 0 8N0.250.500.0100.020S 5.80 6.200.2280.244 YM0.25 (0.010)Z S X S____ǒmminchesǓSCALE 6:1*For additional information on our Pb−Free strategy and solderingdetails, please download the ON Semiconductor Soldering andMounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT*ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

CS5181资料