3D-IC TSV堆叠技术之发展趋势

芯片行业在未来的技术发展趋势和变革方向

随着科技的飞速发展,芯片行业正经历着前所未有的变革。

未来几年,芯片行业的技术发展趋势和变革方向将深刻影响整个科技领域的发展。

本文将探讨芯片行业在未来的技术发展趋势和变革方向。

一、技术发展趋势1.先进制程工艺:随着摩尔定律的延续,芯片制造的制程工艺不断突破物理极限。

未来,更先进的制程工艺将进一步提高芯片的性能、降低功耗,同时带来更小的尺寸和更低的成本。

2.异构集成:异构集成技术将不同工艺、不同材料的芯片集成在一个封装内,实现性能优化和功耗降低。

这种技术将为各种应用场景提供灵活、高效的解决方案。

3.3D集成:3D集成技术通过将多个芯片堆叠在一起,实现更快的传输速度和更低的功耗。

这种技术将为高性能计算、人工智能等领域提供强大的支持。

4.柔性电子:柔性电子技术使得芯片可以弯曲、折叠,适应各种不规则表面。

这种技术将广泛应用于可穿戴设备、智能家居等领域,为人们的生活带来更多便利。

5.人工智能芯片:人工智能技术的快速发展对芯片提出了更高的要求。

未来,更高效、更智能的AI芯片将成为行业发展的热点。

二、变革方向1.封装革命:随着制程工艺的进步,芯片封装的重要性日益凸显。

未来,封装技术将发生深刻变革,从传统的芯片级封装向系统级封装、晶圆级封装发展。

这种变革将进一步提高芯片的性能、降低成本,并适应各种新兴应用的需求。

2.智能制造:智能制造是未来芯片制造的重要方向。

通过引入自动化、智能化技术,提高生产效率、降低能耗和减少人力成本。

智能制造将为芯片行业带来巨大的变革,推动整个产业链的升级。

3.开放创新:未来,芯片行业将更加注重开放创新,打破传统封闭式创新的局限。

通过与学术界、产业界的合作,共享技术资源、加速技术研发和应用。

这种开放创新的模式将促进整个行业的创新力和竞争力提升。

4.可持续发展:随着全球对环保问题的日益重视,可持续发展成为芯片行业的必然趋势。

厂商将更加注重环保材料的使用、能效比的优化以及废弃物的回收利用,推动整个行业的绿色发展。

三维集成电路封装技术的发展与应用

三维集成电路封装技术的发展与应用随着科技的不断进步,电子设备的功能越来越强大,体积却越来越小。

这一切都离不开集成电路的发展,而三维集成电路封装技术的应用则是推动整个行业向前发展的重要一环。

本文将探讨三维集成电路封装技术的发展与应用。

一、三维集成电路封装技术的发展历程三维集成电路封装技术是指将多个芯片堆叠在一起,通过垂直连接技术实现芯片之间的互联。

这种封装技术的出现,为电子设备的体积和性能提供了新的解决方案。

三维集成电路封装技术的发展经历了几个重要的阶段。

最早的阶段是通过晶圆间互联技术实现的二维封装,这种封装方式虽然能够实现多个芯片的互联,但由于晶圆间的连接距离较远,导致信号传输速度较慢。

为了解决这个问题,人们开始研究垂直封装技术,即将芯片堆叠在一起,通过垂直连接实现芯片之间的互联。

这种封装方式大大提高了信号传输速度,但也带来了新的问题,如热管理和可靠性等。

随着技术的不断进步,三维集成电路封装技术逐渐成熟。

目前,已经有了多种不同的三维封装技术,如TSV(Through-Silicon Via)封装、硅互联封装和芯片层间互联封装等。

这些封装技术在不同的应用场景下,具有各自的优势和适用性。

二、三维集成电路封装技术的应用领域三维集成电路封装技术的应用领域非常广泛。

首先,它在移动设备领域发挥了重要作用。

如今的智能手机和平板电脑越来越薄,但功能却越来越强大。

这得益于三维封装技术的应用,使得更多的芯片能够被集成在一个更小的空间内,从而实现了更高的性能和更低的功耗。

其次,三维集成电路封装技术在大数据处理和云计算领域也有广泛的应用。

随着数据量的不断增加,传统的二维封装已经无法满足高速数据传输的需求。

而三维封装技术的应用,则可以提供更高的带宽和更低的延迟,从而提升数据处理的效率。

此外,三维集成电路封装技术还在人工智能和物联网等领域发挥着重要作用。

在人工智能领域,深度学习算法的广泛应用导致了更高的计算需求,而三维封装技术则可以提供更大的计算能力。

三维集成技术的现状和发展趋势

三维集成技术的现状和发展趋势作者:吴际谢冬青来源:《现代电子技术》2014年第06期摘要:给出了三维技术的定义,并给众多的三维技术一个明确的分类,包括三维封装(3D⁃P)、三维晶圆级封装(3D⁃WLP)、三维片上系统(3D⁃SoC)、三维堆叠芯片(3D⁃SIC)、三维芯片(3D⁃IC)。

分析了比较有应用前景的两种技术,即三维片上系统和三维堆叠芯片和它们的TSV技术蓝图。

给出了三维集成电路存在的一些问题,包括技术问题、测试问题、散热问题、互连线问题和CAD工具问题,并指出了未来的研究方向。

关键词:三维集成电路;三维晶圆级封装;三维堆叠技术;三维片上系统中图分类号: TN431.2⁃34 文献标识码: A 文章编号: 1004⁃373X(2014)06⁃0104⁃04依靠减小特征尺寸来不断提高集成度的方式因为特征尺寸越来越小而逐渐接近极限,而三维芯片则是继续延续摩尔定律的最佳选择[1]。

理想的三维芯片是在硅片上交替的制造器件层和布线层,由于难度较大,现阶段基本无法实现。

目前的三维芯片,本质上是封装技术的一种延伸,是将多个裸晶片(die)堆叠起来,这种技术允许基本电路元件在垂直方向堆叠,而不是仅仅在平面互连。

三维芯片的主流技术有两种:SOI技术[2]和纯硅技术[3],TSV最小间距可达6 mm,最小直径可达2 mm,即将走向量产阶段,成为主流技术[4]。

三维芯片优势很多,除了明显的提高集成度之外,更小的垂直互连,还可提高互连速度和减小最长全局连线。

同时,连线的缩短会减少长连线上中继器的数量,从而减少功耗[5]。

因为堆叠的晶片可以是不同工艺的,三维芯片非常符合片上系统(System⁃on⁃Chip,SoC)的需求,生产异构的复杂系统。

三维芯片符合未来的高性能计算和多核/众核处理器的需求。

目前IBM和Intel都纷纷在众核处理器中试用三维堆叠技术,如IBM的Cyclops系统[6]和Intel的万亿次计算系统[7]。

半导体技术的最新进展和未来发展趋势

半导体技术的最新进展和未来发展趋势近年来,随着科技的不断进步和人类对高效能电子产品的需求增加,半导体技术作为电子行业的核心技术受到了广泛的关注和研究。

本文将介绍半导体技术的最新进展以及未来的发展趋势。

1. 3D芯片技术的突破3D芯片技术是近年来取得突破性进展的一个重要方向。

传统的芯片平面结构容纳的元器件数量和功能有限,而采用3D芯片技术可以在垂直方向上增加层次,大幅度提升芯片的处理能力和存储能力。

目前,3D芯片技术已被广泛应用于智能手机、云计算、人工智能等领域。

2. 新一代制程技术的发展制程技术是半导体技术进步的重要推动力之一。

过去几十年间,半导体技术的制程技术取得了长足的发展,从20纳米到7纳米,再到5纳米的工艺,每一次突破都带来了半导体器件尺寸的缩小和性能的提升。

未来,随着更高精度的制程技术的研究和应用,半导体器件将进一步实现微纳级尺寸,从而推动芯片处理性能的提升。

3. 宽禁带半导体材料的研究宽禁带半导体材料具有较大的能带间隙,对高温、高功率等极端环境具有较好的适应性。

近年来,宽禁带半导体材料的研究逐渐成为半导体技术发展的热点。

例如,氮化镓材料具有宽禁带特性,可以应用于高效能电子器件、激光器等领域。

随着对宽禁带半导体材料研究的深入,未来将会有更多新材料被开发和应用于半导体技术中。

4. 半导体器件的多样化和集成化随着电子产品功能的不断增强和多样化需求的出现,半导体器件也在朝着多样化和集成化方向发展。

例如,传感器、RFID芯片、功率器件等不同类型的半导体器件得到了广泛应用。

未来,这些半导体器件的集成度将会更高,通过多功能芯片的设计和制造,实现各种功能的集成,提高整个系统的性能和效率。

5. 生态系统合作与互联互通半导体技术的发展不仅仅依赖于单个研究机构或企业,更需要各方共同合作和互相支持。

未来,半导体技术的发展趋势将更加强调生态系统的合作与互联互通。

不同研究机构、企业、产业链的紧密合作,将促进技术的共享和创新,提高整个行业的竞争力。

国家集成电路产业发展趋势

国家集成电路产业发展趋势国家集成电路产业发展趋势导语:随着信息技术的飞速发展,集成电路作为核心零部件和基础设施,对于现代社会的发展起到了至关重要的作用。

国家集成电路产业的发展不仅涉及到经济发展和技术进步,还与国家安全和军事实力密切相关。

本文将着重讨论国家集成电路产业的发展趋势,从技术、政策、市场等多个角度进行剖析。

一、技术发展趋势1.超大规模集成电路(ULSI)的发展随着技术的进步,集成电路芯片上的晶体管数量将越来越多,集成度将越来越高。

目前,单个芯片上晶体管的数量已经超过了20亿个,不久的将来,这个数字将进一步增加。

超大规模集成电路将具备更高性能、更低功耗和更大容量,将成为国家集成电路产业发展的一个重要方向。

2.先进制程技术的突破制程技术是集成电路产业发展的核心。

随着电子器件的缩小以及半导体材料和工艺的不断改进,先进制程技术的突破将推动集成电路产业的进一步发展。

当前,14纳米和10纳米制程已经成为主流,未来,7纳米、5纳米乃至更小的制程技术将逐渐成熟,实现规模化生产。

3.三维堆叠(3D)集成技术的应用三维堆叠集成技术是集成电路行业的新兴技术,通过垂直堆叠多层芯片,大幅提高了集成电路的集成度和性能。

相比传统的二维结构,三维堆叠技术具有更小的面积占用、更高的信号传输速度和更低的功耗。

未来,三维堆叠技术将广泛应用于移动智能终端、人工智能、云计算等领域。

4.新型材料的应用新型材料对于集成电路产业的发展具有重要意义。

比如,碳纳米管、石墨烯等材料具有卓越的电学和导热性能,能够提高芯片的性能和可靠性。

此外,新型材料还可以应用于光通信、量子计算等领域,拓宽集成电路的应用范围。

二、政策环境趋势1.支持政策的制定和实施国家集成电路产业是一个战略性新兴产业,对经济增长、国家安全和军事实力具有重要影响。

因此,政府将加大对集成电路产业的支持力度,制定相关政策,鼓励技术研发、创新创业和产业升级。

政府还将加大对集成电路产业的投资,提供资金支持、税收优惠等多种政策措施,推动产业的健康发展。

半导体行业的未来技术趋势洞察下一代半导体技术的发展方向

半导体行业的未来技术趋势洞察下一代半导体技术的发展方向随着科技的不断进步,半导体行业作为信息技术的核心推动力量,正迅速发展并引领着全球经济的新一轮浪潮。

为了满足不断增长的技术和市场需求,半导体技术也在不断演进和创新。

本文将探讨半导体行业的未来技术趋势,揭示下一代半导体技术的发展方向。

一、3D堆叠集成电路技术在传统的二维集成电路中,电路元件是在同一平面上布置的。

然而,随着集成度的不断提高,传统的二维布局将无法满足需求。

为了提高集成度和性能,3D堆叠集成电路技术应运而生。

这种技术通过将电路元件垂直堆叠在一起,大大提高了电路的集成度,减少了电路之间的互连长度,从而提高了性能和能效。

未来,3D堆叠集成电路技术将成为下一代半导体技术的重要发展方向。

二、新型材料的应用半导体材料是制造集成电路的基础,因此材料的研究和应用将直接影响半导体技术的发展。

目前,新型材料如石墨烯、硅基石墨烯、氮化硅、碳化硅等正逐渐应用于半导体行业。

这些材料具有优异的电学特性、导热性和机械性能,能够实现更高的工作频率、更低的功耗和更小的体积,推动半导体技术的进步。

未来,随着对新型材料的深入研究和应用,半导体行业将迎来更为高效和环保的新一代材料。

三、人工智能与半导体融合人工智能的兴起正在对各行各业产生深远的影响,半导体行业也不例外。

人工智能需要大量的计算资源和高效的处理能力,而半导体技术正是实现这一目标的核心。

人工智能芯片的快速发展,不仅为半导体行业带来了新的需求,同时也推动着半导体技术的创新。

未来,随着人工智能技术的不断成熟,半导体与人工智能的融合将成为半导体行业的重要方向,推动行业向更智能、更高效的方向发展。

四、量子计算的崛起量子计算作为未来计算技术的重要方向,正受到全球科研机构和企业的高度关注。

量子计算利用量子力学的性质进行运算,具有比传统计算机更高的计算能力和速度。

而实现量子计算的关键就在于量子比特的制备和操控,而这就需要依赖于半导体技术。

3D IC 的TSV集成–现有工艺及未来展望

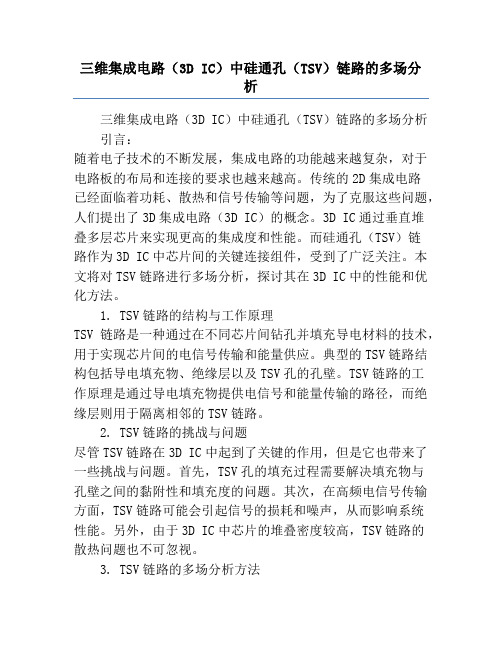

13DIC Integration with TSV –Current Progress and Future OutlookShan Gao, Dim-Lee KwongInstitute of Microelectronics,A*STAR (Agency for Science,Technology and Research)Singapore9 September, 2010OverviewIntroduction3DIC integration and main applicationProducts to be commercializedTechnologies and key challenges for 3DIC with TSV Current progress in 3D TSV developmentOutlookWhy 3DIC? -Pre-positioning Strategyfor More than MooreENABLERDiscrete 2-D IntegrationHigh Density MemoryLow Power LogicHigh PerformanceLogicHigh Speed Memory RadioPhotonicsPower RegulatorSensorsPhotonicsSensorsI/O High DensitymemoryHigh SpeedMemory High Perf.Logic Low Power Logic PowerReg.Radio 3-D Integration3D TSV Application Status3D TSV Market Drivers3D TSV Packaging Market Forecast•Logic + memory application to drive >30% of the 3D TSV packagingmarket by 2015•CIS, MEMS, SENSOR to drive 30% of market share•Memory + Memory stacking combined DRAM & NAND drive 20%Substrate•Mechanical simulation for low stress•Thermal simulation for low chip temperature •Electrical simulation for Signal Integrity (SI), Power Integrity (PI)•Electrical test, Reliability test and FMEAModeling & CharacterizationMicro-bumpingWafer Level RDLWafer ThinningTSV FabricationC2W/C2C BondingCu-Cu Wafer Bonding •Temporary bonding/debonding adhesive •Plating chemicals for high AR (>10) TSV filling •CMP slurries for high removal rate (5µm/min) •Low curing temperature dielectric (< 180ºC)•Small gap wafer level underfills (<10µm)•Low stress/warpage wafer level encapsulantsDevelopment of Materials3D IC Structure3D IC Technology Development in IME(TSV Interposer)Via ‐First (TSV Interposer)(Logic, Memory)Via ‐Middle(Logic, Memory)(CIS, Memory)Via ‐Last (B2T)(CIS, Memory)TSV ETCH TSV Photo FEOLTSV CLEAN TSV CVD TSV PVD TSV ECP TSV CMPTSV ETCH TSV Photo TSV CLEAN TSV CVD TSV PVD TSV ECP TSV CMPTSV ETCH BOND & THIN TSV LTCVD CONTACT ETCH TSV PHOTO TSV PVD TSV ECP DEBONDBEOLSiRDL & BUMP TSV CLEAN BOND & THIN BS VIA REVEAL BS RDL/BUMPCHIP STACK ASSY & TESTFEOL BEOLSi FEOL BEOLSi 3D TSV Integration Process FlowKey challenges:•Conformal dielectric step coverage and Barrier / Cu seed step coverage •Void free electroplating, Cu ProtrusionOn ‐going Research:•Via size 2um/AR10, < 10um pitchDescription Established in IME Dielectric coverage~10% for AR10Barrier metal and seed step coverage ~5% for AR10Electro ‐plated via Ø5um/AR10, 15um pitch Wafer / TSV thickness50umVia etching Barrier/Seed/Cu Filling Cu CMPDielectric Layer TSV Fabrication ProcessTSV Fabrication Process Challenges•Cu protrusion (hundreds to thousands Å) may attack M1 and ILD layer •Double CMP and Heat Treatment method have been reported for via ‐middle process –but these are typically high temperature processes •Low temperature ILD process for Cu BEOL can minimize Cu protrusion for interposer application –process development neededProcess Challengess –Cu Protrusion•Need carrier wafer for chip bonding•Lower density integration •No need carrier wafer•High density integration •Work only between 1st and 2nd wafer bonding only, the 3rd wafer stack back to “Face to back”Interconnection –Cu-Cu Wafer Bonding On‐going Research:•Cu‐Cu W2W bonding: Temperature 300o C, Pitch 15umKey challenges :•Low bonding temperature, Fine pitch and High reliabilityCu pillar + Thin solder layerMicro ‐bump IMC based interconnectionDescription Specification Bonding Temperature Micro ‐bump180°C Cu pillar with lead free solder260°C Bump material AuInSn, InSn Bump Pitch25umSi ChipSi chipOn ‐going Research:•Composite joint for C2C, C2W bonding, Bump Pitch: 15umInterconnection -Fine Pitch Micro-Bump3M –Laser released adhesiveBSI –Thermal plastic adhesiveTMAT –Mechanically released adhesiveTOK ‐Chemical released adhesiveThin Wafer Handling -TemporallyBonding/DebondingKey challenges :•Multiple chip stacking with low stand ‐off interconnection •Low warpage wafer level encapsulationOn ‐going Research: •C2W bonding : 10 chips•Interconnection: RDLless and Bumpless Micro ‐jointC2C & C2W BondingWafer Level Underfilling Wafer Level MoldingChuckBase Wafer Base WaferDescriptionSpecificationBonding method (C2W, C2C)Thermo ‐compression Stand ‐offLow Temperature Solder (180°C)5um Cu pillar with leadfree solder (260°C)15umChip Stacking ProcessSubstrateReliability ChallengesStress concentration, Cracks around TSVsIMC, fatigue failure of microbumpsMoisture induceddelamination, corrosionHot Spot in Chip & Thermal ManagementElectromigration in Microbumps & TSVs[]110x []001'y []101y []010'x R 1R 4R 3R 2Stress sensor for processdevelopmentComb & Triple Tracks Sensor for moisture ingress & corrosionn-wellp substrateN++P + implant n-wellN++P + implantThermal chip design Crack sensor chip designSensor Chip Design For ReliabilityIntegrated single or two phase liquid cooling for high power chips in 3DIC‐Chip carrier with fluidic and electrical paths by C2C bonding‐3D electrical and fluidic interconnection using silicon interposerHeat ExchangerMini Pump PCBSilicon carrierFluidic adaptor TSVElectrical I/OFluidic Inlet Micro Channels Seal ring0.010.020.030.040.050.060.070.080.090.0100.0110.00102030405060708090100Chip Heat Dissipation (W/cm2)A v g . C h i p T e m p e r a t u r e (°C )Chip with 400 Bumps ( Measured Data)Chip with 2500 Bumps ( Simulation Data)Avg Cooling Liquid TempIntegrated Cooling SolutionOn ‐going Research:•Two Phase Boiling CoolingIdentify & establishment –300mm line through consortium efforts1st YearProcess & Characterization studies on 300mm wafer2nd Year 3rd YearPhase ‐1 (18 months)Phase ‐2 (18 months)Process & Reliability studiesApplication: Mobile Devices•One Logic Chip & Six Memory Chips Consortium Deliverables:•Phase ‐1: Design Guidelines & Process Development •Phase ‐2: Full Functional Device DemonstrationDesign & Modeling StudiesSingapore 3D TSV Consortium201020112012201320143D Stacking (C2C, C2W, W2W)Design, Simulation & CharacterizationWafer Level RDL & Micro-bumpingTSV FabricationWafer Handling & ThinningHigh freq. (up to 80GHz) TSV Electrical Characterization (Φ<2um, D<20um)Thermo-Mechanical simulationDynamic two-phase flow simulationVia Last Φ5um, D50umSub-micron Via Φ1um, D10umVia Middle Φ2um, D20umC2C/C2W bonding with solder (10 chips)W2W Cu-Cu Bonding(Pad size: 5um, pitch: 10um, Bonding temp.: <200◦C)12”50um thickness12”20um thickness12”10um thickness8”50um thicknessCuInSn solder: 180◦C, Size: 8um, Pitch: 15umLine/Space: 10um/10umLine/Space: 15um/15umSensor + Mixed SignalPMIC + Memory + RFICSensor + Memory + FPGAIME 3DIC Development Roadmap3DIC Product Development Challenges Infrastructure availability and supply chainI/O standardization between interfacesThermal management and interconnect reliabilityShift in the Design/Test method paradigm and systemco‐designThank you for your attention!。

3D IC路漫漫 TSV方兴未艾

3D IC路漫漫TSV方兴未艾作者:曹明霞,SEMI特约编辑随着半导体制造工艺的发展,CMOS图像传感器、Memory、Logic、RF及MEMS等器件模块的发展方向将朝着3D架构积极迈进。

未来的技术将更多以3D IC的方式,而不是在一块IC上整合多个设计功能模块的形式。

但可以肯定的是通往3D IC的道路将是漫长的。

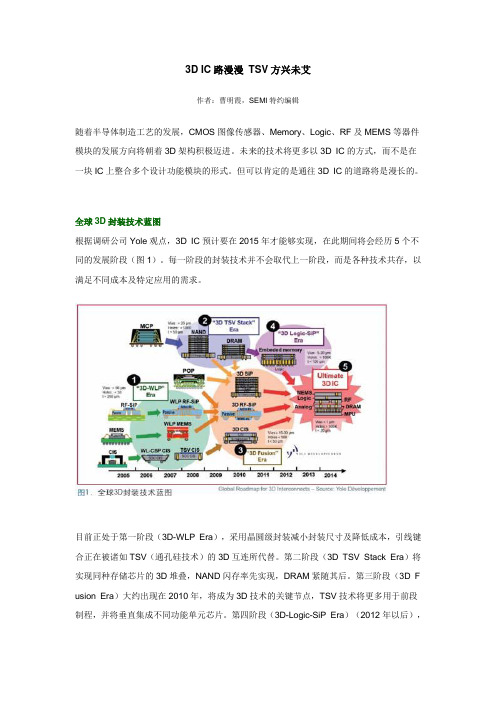

全球3D封装技术蓝图根据调研公司Yole观点,3D IC预计要在2015年才能够实现,在此期间将会经历5个不同的发展阶段(图1)。

每一阶段的封装技术并不会取代上一阶段,而是各种技术共存,以满足不同成本及特定应用的需求。

目前正处于第一阶段(3D-WLP Era),采用晶圆级封装减小封装尺寸及降低成本,引线键合正在被诸如TSV(通孔硅技术)的3D互连所代替。

第二阶段(3D TSV Stack Era)将实现同种存储芯片的3D堆叠,NAND闪存率先实现,DRAM紧随其后。

第三阶段(3D F usion Era)大约出现在2010年,将成为3D技术的关键节点,TSV技术将更多用于前段制程,并将垂直集成不同功能单元芯片。

第四阶段(3D-Logic-SiP Era)(2012年以后),存储芯片与逻辑芯片将能够直接堆叠,通孔更小(小于5um)互连密度更高。

第五阶段(U ltimate 3D IC),最终实现3D集成芯片。

Nokia与Intel关于TSV规划TSV作为新一代封装技术,是通过在芯片和芯片之间,晶圆和晶圆之间制造垂直导通,实现芯片之间互连的最新技术,能够在三维方向使得堆叠密度最大,而外形尺寸最小,大大改善了芯片速度和低功耗性能。

手机是加速开发3D封装的重要动力,手机已从低端(通话和收发短消息)向高端(可拍照、电视、广播、MP3、彩屏、和弦振声、蓝牙和游戏等功能集成)发展,并要求手机体积小,重量轻且功能多。

高端手机芯片需要拥有强大的内存容量。

诺基亚公司技术平台高级工程经理Kauppi Kujala称,存储器通孔硅(TSV)封装技术将很快应用到手机中,然而,采用T SV技术将不同芯片垂直互连,真正实现3D IC,估计需要10年时间(图2)。

芯片制造技术的发展趋势与国际竞争力分析

芯片制造技术的发展趋势与国际竞争力分析随着信息技术和数字化产业的快速发展,芯片制造技术作为信息产业的基石,也在不断发展。

芯片技术的进步不仅影响着数字化产业的发展,而且还关系到国家经济的整体实力。

从芯片制造技术的发展趋势和国际竞争力分析,我们可以了解到芯片制造技术的最新进展及其对中国和世界影响。

一、芯片制造技术的发展趋势1、极紫外光刻技术(EUV)的应用随着工艺尺寸越来越小,射线刻画和电子束刻画等现有的制造技术也越来越难以应对这种趋势。

极紫外光刻技术(EUV)作为下一代芯片制造技术,具有高精度、高速度、低成本等优点。

EUV技术的成熟应用将使芯片的制造技术迈向新台阶。

目前,EUV技术已经在英特尔、三星、台积电等公司得到应用。

2、3D封装和堆叠技术目前的芯片技术已经相当先进,但节能、降低成本、提高性能仍然是现代芯片制造技术的重要任务。

3D封装和堆叠技术也是指望达成这一目标的途径之一。

3D 封装技术是指将芯片和多个器件封装到3D结构中,以避免芯片和器件之间的热传递、电磁辐射等关键问题。

通过3D堆叠技术来合并芯片,形成一个更为紧密和可靠的体系。

这些技术的应用还有待进一步的探索和推进。

二、国际竞争力分析1、美国美国芯片产业是全球最大的,也是最完整的。

它在创新和产品开发上具有相当优势,同时美国政府也呼吁加大对芯片产业的支持。

美国迄今已经投入了大量的资金和研发资源,努力把其芯片产业打造成全球一流的产业。

2、中国中国芯片产业的发展在近年来迅速,但与先进国家还有一段距离。

尽管中国政府投入大量资源以支持芯片产业,但其发展步伐相对缓慢。

顶尖芯片制造商如三星、英特尔和台积电等仍然占据着芯片市场的主导地位。

可以说,中国芯片产业的发展还有很长的路要走。

需要加大投入,提高技术防范不良竞争,才能实现行业的快速发展。

总之,芯片技术的发展与国家的整体实力密不可分。

随着信息产业的快速发展,芯片制造技术的进步也将越来越受到关注。

芯片制造技术的未来发展方向,将更多地体现出创新、智能、高效的特点。

三维集成电路(3D IC)中硅通孔(TSV)链路的多场分析

三维集成电路(3D IC)中硅通孔(TSV)链路的多场分析三维集成电路(3D IC)中硅通孔(TSV)链路的多场分析引言:随着电子技术的不断发展,集成电路的功能越来越复杂,对于电路板的布局和连接的要求也越来越高。

传统的2D集成电路已经面临着功耗、散热和信号传输等问题,为了克服这些问题,人们提出了3D集成电路(3D IC)的概念。

3D IC通过垂直堆叠多层芯片来实现更高的集成度和性能。

而硅通孔(TSV)链路作为3D IC中芯片间的关键连接组件,受到了广泛关注。

本文将对TSV链路进行多场分析,探讨其在3D IC中的性能和优化方法。

1. TSV链路的结构与工作原理TSV链路是一种通过在不同芯片间钻孔并填充导电材料的技术,用于实现芯片间的电信号传输和能量供应。

典型的TSV链路结构包括导电填充物、绝缘层以及TSV孔的孔壁。

TSV链路的工作原理是通过导电填充物提供电信号和能量传输的路径,而绝缘层则用于隔离相邻的TSV链路。

2. TSV链路的挑战与问题尽管TSV链路在3D IC中起到了关键的作用,但是它也带来了一些挑战与问题。

首先,TSV孔的填充过程需要解决填充物与孔壁之间的黏附性和填充度的问题。

其次,在高频电信号传输方面,TSV链路可能会引起信号的损耗和噪声,从而影响系统性能。

另外,由于3D IC中芯片的堆叠密度较高,TSV链路的散热问题也不可忽视。

3. TSV链路的多场分析方法为了解决上述问题,人们利用电磁场理论、热传导理论和机械力学理论等多场分析方法对TSV链路进行研究。

在电磁场方面,可以通过研究TSV链路的等效电路模型和传输线理论来分析电信号的传输损失和噪声问题。

在热传导方面,可以通过模拟TSV链路的热传导路径和热源来分析散热性能。

在机械力学方面,可以分析TSV链路在机械应力下的稳定性和可靠性。

4. TSV链路的优化方法为了提高TSV链路的性能,人们提出了一系列的优化方法。

例如,在TSV孔填充过程中可以选择合适的填充材料和填充工艺,以提高填充度和黏附性。

三维封装技术提升芯片集成度研究

三维封装技术提升芯片集成度研究三维封装技术,作为半导体产业中的一项革命性创新,正逐步重塑集成电路的设计、制造与应用模式。

随着摩尔定律逐渐逼近物理极限,传统的二维平面集成技术在提高芯片性能和降低成本方面的效能日益减弱。

三维封装技术,通过垂直堆叠芯片或在芯片间建立密集互连,打破了平面扩展的限制,实现了更高的集成密度、更短的信号传输路径及更强的计算能力,为持续提升芯片性能开辟了新的途径。

以下从六个方面深入探讨三维封装技术如何促进芯片集成度的飞跃。

一、三维封装技术的基本原理与类型三维封装技术基于多种不同的实现方式,主要包括硅通孔(Through-Silicon Vias, TSV)、微凸点互联(Micro Bumps)、芯片堆叠(Chip Stacking)及中介层(Interposer)技术等。

其中,TSV技术通过在硅片中直接钻孔并填充导电材料形成垂直通道,实现芯片间的直接电气连接,极大缩短了信号传输距离,降低了延迟和功耗。

微凸点互联则为芯片间提供了灵活的机械和电气连接点,而芯片堆叠允许不同功能的芯片直接堆叠,形成高度集成的系统级封装(System-in-Package, SiP)。

中介层技术则作为高性能芯片之间的桥梁,扩展了互连面积,提升了集成复杂度。

二、提升集成密度与计算能力三维封装技术最直观的优势在于显著提升芯片的集成密度。

通过垂直整合多个裸片,可以在更小的空间内封装更多的晶体管,进而增加单个封装体的计算能力和存储容量。

这对于大数据处理、、高性能计算等领域尤为重要,能够有效应对数据爆炸式增长带来的处理需求,同时减少系统尺寸,提升能效。

三、缩短信号传输路径与降低功耗传统的二维芯片设计中,信号需跨越长距离的印刷电路板(PCB)进行互连,这不仅增加了信号延迟,也导致了能量损失。

三维封装技术通过直接在芯片之间建立垂直连接,显著缩短了信号传输路径,降低了信号传输延迟,减少了能耗。

特别是在高速数据交换的应用中,这一优势尤为明显,可提高系统整体的响应速度和能源效率。

存储器产业最新技术趋势

存储器产业最新技术趋势存储器产业是信息技术领域中的关键产业之一,随着信息技术的迅猛发展,存储器技术也在不断创新和进步。

在本文中,将介绍存储器产业最新的技术趋势,包括新型存储器技术、存储器的集成化与模块化设计、存储器的高速化与低功耗化以及存储器的可靠性与安全性。

一、新型存储器技术传统的存储器技术,如动态随机存取存储器(DRAM)和闪存,已经在各种设备中得到了广泛应用。

然而,随着信息技术的快速发展,传统存储器技术已经难以满足日益增长的存储需求。

因此,研究人员正在开发新型存储器技术,以提高存储器的容量、速度和稳定性。

1. 三维堆叠存储器技术三维堆叠存储器技术是一种将多层存储体积整合到一个芯片中的技术。

通过堆叠多个存储层,可以实现更高的存储密度和更小的芯片面积。

此外,三维堆叠存储器技术还可以提高存储器的速度和能效。

目前,三维堆叠存储器技术已经在一些高端服务器和高性能计算领域得到了广泛应用,并且有望在未来的个人电脑和移动设备中得到普及。

2. 相变存储器技术相变存储器是一种基于相变材料的非易失性存储器技术。

相变材料可以在不同的温度下改变其电阻状态,从而实现数据的存储和读取。

相较于传统的存储器技术,相变存储器具有更高的速度、更高的密度和更低的功耗。

目前,相变存储器技术已经商业化,并且有望在未来替代闪存技术成为主流存储器技术。

3. 非易失性存储器技术非易失性存储器是一种可以长期保持数据的存储器技术。

与传统的易失性存储器不同,非易失性存储器可以在断电后保持数据完整。

目前,非易失性存储器技术已经广泛应用于闪存和相变存储器等领域。

未来,研究人员正在开发新型的非易失性存储器技术,以提高数据的持久性和可靠性。

二、存储器的集成化与模块化设计随着云计算、大数据和人工智能等技术的快速发展,存储器的需求量不断增加。

为了满足这一需求,存储器产业正在朝着集成化和模块化设计的方向发展。

1. 存储器的集成化设计存储器的集成化设计是指将多个存储设备集成到一个芯片或一个模块中的设计方法。

半导体产业未来的趋势

半导体产业未来的趋势半导体产业未来的趋势引言:半导体是一种关键的电子材料,用于制造各种电子设备和芯片。

在过去几十年中,半导体产业经历了巨大的发展和变革,为现代科技带来了巨大的影响。

随着科技的不断进步和需求的不断增长,半导体产业面临着新的机遇和挑战。

本文将探讨半导体产业未来的趋势,包括技术发展、市场需求和全球竞争等方面。

一、技术发展趋势1. 纳米技术的应用:纳米技术是半导体产业的重要发展方向之一。

通过使用纳米级材料和工艺,可以提高芯片的制造精度和性能。

纳米技术还可以用于开发新型的材料和器件,如纳米电子器件、纳米激光器等,进一步推动半导体产业的发展。

2. 三维堆叠技术:三维堆叠技术是一种将多个芯片或器件垂直堆叠在一起的制造技术。

通过这种技术,可以提高芯片的集成度和功能性。

三维堆叠技术有助于减小芯片的尺寸,提高能源利用率,并实现更高的性能和可扩展性。

3. 光子学技术的应用:光子学技术是一种利用光的传输和控制信息的技术。

在半导体产业领域,光子学技术可以用于制造更快速、高密度和低功耗的光通信器件和芯片。

光子学技术还可以用于开发新型的光电子器件和光存储器件,进一步推动半导体产业的发展。

4. 人工智能和机器学习的应用:人工智能和机器学习是当前热门的技术领域,也对半导体产业产生了重大影响。

在半导体领域,人工智能和机器学习可以用于设计、制造和测试芯片,提高效率和质量。

人工智能和机器学习还可以用于优化芯片的功耗和性能,推动半导体产业向更加智能化的方向发展。

二、市场需求趋势1. 云计算的快速发展:云计算是一种将计算资源和服务通过互联网提供给用户的模式。

随着云计算在各行各业的应用不断增加,半导体产业将面临巨大的市场机遇。

云计算需要大量的服务器、存储器和网络设备,这就对半导体产业提出了更高的要求,如更高的集成度、更低的功耗和更高的性能。

2. 物联网的快速发展:物联网是指通过互联网将各种智能设备和传感器连接起来,实现设备之间的通信和数据交换。

芯片 堆叠技术

芯片堆叠技术芯片堆叠技术是一种将多个芯片垂直堆叠在一起的先进封装技术。

这种技术的出现,极大地提高了芯片的集成度和性能,为各种电子设备的发展带来了巨大的推动力。

本文将从芯片堆叠技术的原理、应用和发展趋势三个方面进行探讨。

一、芯片堆叠技术的原理芯片堆叠技术的原理是将多个芯片通过微细的连接线进行堆叠,形成一个整体的芯片系统。

这样做的好处是可以在有限的空间内集成更多的功能模块,并且可以提高芯片之间的通信速度和数据传输效率。

芯片堆叠技术通常使用垂直连接和水平连接两种方式。

垂直连接是通过通过硅通孔或微针等方式将芯片堆叠在一起,形成一个垂直的结构;水平连接则是将芯片通过微细的金属线进行连接,形成一个水平的结构。

二、芯片堆叠技术的应用芯片堆叠技术在各个领域都有广泛的应用。

在移动设备领域,芯片堆叠技术可以使手机、平板电脑等设备更加轻薄,同时提供更强大的性能和更长的电池续航时间。

在数据中心领域,芯片堆叠技术可以提高服务器的计算能力和存储容量,满足日益增长的数据处理需求。

在人工智能领域,芯片堆叠技术可以提供更高的计算速度和更大的存储空间,加速深度学习算法的训练和推理过程。

此外,芯片堆叠技术还可以应用于物联网、汽车电子、医疗设备等领域,为各种应用场景提供更高效的解决方案。

三、芯片堆叠技术的发展趋势随着科技的不断进步,芯片堆叠技术也在不断发展。

未来,芯片堆叠技术将呈现以下几个发展趋势:1. 三维堆叠:目前的芯片堆叠技术主要是二维堆叠,即将多个芯片在水平方向上进行堆叠。

未来,随着材料和工艺的进一步突破,三维堆叠将成为可能。

三维堆叠可以进一步提高芯片的集成度和性能,实现更复杂的功能。

2. 高密度互连:芯片堆叠技术的关键是芯片之间的连接。

未来,随着互连技术的不断创新,高密度互连将成为可能。

高密度互连可以提高芯片之间的通信速度和数据传输效率,进一步提升整个芯片系统的性能。

3. 异构堆叠:目前的芯片堆叠技术主要是同质堆叠,即将多个相同的芯片堆叠在一起。

半导体行业的未来颠覆者揭示半导体行业中的新兴技术和颠覆性创新

半导体行业的未来颠覆者揭示半导体行业中的新兴技术和颠覆性创新半导体行业的未来颠覆者:揭示半导体行业中的新兴技术和颠覆性创新随着科技的迅猛发展,半导体行业成为推动现代社会进步的重要支柱。

然而,随着时间的推移,传统的半导体技术面临着瓶颈和挑战。

为了突破这一局面,许多新兴技术和颠覆性创新在半导体行业中崭露头角。

本文将揭示这些未来的颠覆者,展示他们带来的新技术和创新,以及对半导体行业的影响。

一、三维堆叠技术半导体行业中的三维堆叠技术正迅速崭露头角。

传统的二维集成电路在面临功耗、散热等问题时,难以突破局限。

而三维堆叠技术通过垂直堆叠芯片,使得芯片间的通信更加高效,大大提升了性能和整体能效。

此外,三维堆叠技术还能解决封装和连接密度的问题,进一步提高了集成度。

可以预见,在未来的发展中,三维堆叠技术将成为半导体行业的重要利器。

二、量子计算量子计算被视为半导体行业的下一次颠覆性创新。

传统的计算机以比特为基本单位进行计算,而量子计算则使用量子位(qubit)来实现超强的计算能力。

量子计算的优势在于其并行计算的能力,可以在极短的时间内解决传统计算机无法处理的问题。

虽然目前的量子计算技术还处于起步阶段,但已经吸引了全球各大科技巨头的关注,并且在一些特定领域取得了突破性的进展。

可以预见,在不久的将来,量子计算将引领半导体行业的发展方向。

三、柔性电子技术随着人们对于移动性和便携性的需求越来越高,传统的刚性半导体器件已经无法满足市场需求。

柔性电子技术的出现为解决这一问题提供了新的途径。

相比传统的硅基材料,柔性电子技术使用了可弯曲的材料,如塑料,使得电子设备能够更加轻薄、便携。

此外,柔性电子技术还能适应各种异形表面,为无处不在的智能化提供了可能。

可以预见,在未来的发展中,柔性电子技术将改变人们对于电子设备的认知。

四、生物芯片技术生物芯片技术是半导体行业中的另一项颠覆性创新。

传统的半导体技术主要应用于信息处理和存储方面,而生物芯片技术则将半导体技术应用于生物领域。

3D-IC TSV堆叠技术之发展趋势

3D-IC TSV堆叠技术之发展趋势时间:2021-10-06 12:35:17 来源:今日半导体编辑:许明哲1 詹印丰1 李景贤2 一、引言半导体技术必须持续发展,以增加IC性能与功能,同时减小芯片尺寸,降低耗电量与成本。

目前我们已发展出具创新性、小尺寸、成本效益之三维导线互连技术,可满足以上需求。

其中,硅导孔(Through Silicon Via; TSV) 技术由于采取三维互连方法,可加速晶片堆叠技术上之应用,尤其在异质元件整合上,具有重要地位。

针对多晶片整合需求,3D 堆叠技术是一项非常有用的解决方案,然而目前仍有许多技术挑战尚待克服。

本文将整合最新发表之文献[1~12],探讨现今半导体晶片3D 堆叠技术之发展趋势。

二、封装技术之演进International SEMATECH (ISMT)于公元2021年开始,将三维硅导孔(3 Dimensional Through Silicon Via; 3D TSV)之金属导线互连技术,列入首要挑战性技术之重要排名榜上。

由于电子产品之日新月异,强调多功能、体积小、及重量轻等诉求,促使半导体晶片之功能不断增加,相对应地I/O点数目也快速增加,同时晶片尺寸不断在缩小,以进而提供更佳之性能表现。

尤其要将不同性能之组件,如被动元件(Passive)、微电子机械系统(MEMS)进行异类组合,此外,因操作频率(Operation Frequency)增加,导线互连长度(Interconnection Distance)缩短,以及增加新的数位类比(New Digital / Analog)功能(例如:RF),所以封装技术必须持续发展创新以降低成本,满足未来量产需求。

而消耗性电子市场不断扩张,则是驱动半导体技术持续进步之主要动力。

最新封装技术,包括:(1).晶圆级封装(Wafer Level package; WLP):在晶圆上整合各种功能,作晶圆对晶圆之接合或晶片对晶圆之接合; (2).系统级封装(System in Package; SiP)和系统级晶圆(System on Wafer; SOW); (3).三维集成电路(3D ICs):在IC前段作晶片堆叠。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3D-IC TSV堆叠技术之发展趋势时间:2009-10-06 12:35:17 来源:今日半导体编辑:许明哲1 詹印丰1 李景贤2一、引言半导体技术必须持续发展,以增加IC性能与功能,同时减小芯片尺寸,降低耗电量与成本。

目前我们已发展出具创新性、小尺寸、成本效益之三维导线互连技术,可满足以上需求。

其中,硅导孔(Through Silicon Via; TSV) 技术由于采取三维互连方法,可加速晶片堆叠技术上之应用,尤其在异质元件整合上,具有重要地位。

针对多晶片整合需求,3D 堆叠技术是一项非常有用的解决方案,然而目前仍有许多技术挑战尚待克服。

本文将整合最新发表之文献[1~12],探讨现今半导体晶片3D 堆叠技术之发展趋势。

二、封装技术之演进International SEMATECH (ISMT)于公元2005年开始,将三维硅导孔(3 Dimensional Through Silicon Via; 3D TSV)之金属导线互连技术,列入首要挑战性技术之重要排名榜上。

由于电子产品之日新月异,强调多功能、体积小、及重量轻等诉求,促使半导体晶片之功能不断增加,相对应地I/O点数目也快速增加,同时晶片尺寸不断在缩小,以进而提供更佳之性能表现。

尤其要将不同性能之组件,如被动元件(Passive)、微电子机械系统(MEMS)进行异类组合,此外,因操作频率(Operation Frequency)增加,导线互连长度(Interconnection Distance)缩短,以及增加新的数位类比(New Digital / Analog)功能(例如:RF),所以封装技术必须持续发展创新以降低成本,满足未来量产需求。

而消耗性电子市场不断扩张,则是驱动半导体技术持续进步之主要动力。

最新封装技术,包括:(1).晶圆级封装(Wafer Level package; WLP):在晶圆上整合各种功能,作晶圆对晶圆之接合或晶片对晶圆之接合; (2).系统级封装(System in Package; SiP)和系统级晶圆(System on Wafer; SOW); (3).三维集成电路(3D ICs):在IC前段作晶片堆叠。

然而,在此必须强调一件事,晶圆级封装(WLP)与三维技术(3D Technology)是两种截然不同之技术,绝不可相混淆。

有许多三维工艺技术被应用于晶圆级封装,但不可归类于晶圆级封装。

真正的电子封装趋势,是由二维结构(2D Configuration)进展到三维工艺技术(3D Process Technology),然后发展到三维集成电路,以减少封装尺寸及增加硅的效率(即所有硅的面积与基材面积之比值),并且以更短的导线作电性连接。

三、系统级封装(System in Package; SiP)之定义系统级封装可以整合不同功能之晶片(Heterogeneous Chips),晶片与晶片之间,可作上下堆叠或并列结合。

ITRS-TWG对SiP所作的定义为:针对超过一种以上之不同功能的主动电子组件,可以选择性地与被动组件,或者其它组件(例如:微电子机械系统或光学组件)作整合,以构成单一的标准封装体,与系统或次系统相结合,进而提供多重功能(Multiple Functions)。

SiP一般包括:类比和数字电路,以及非电子组件。

SiP具有许多解决方案,它可以使用各种不同的基板,以及不同的导线连接技术,可使用整合或分离式的被动组件,在尺寸及性能上可作各种非限定之变异。

SiP可以整合被动组件及其它不同的组件技术,可将数字及类比、CMOS 与Bipolar或基频(Base Band)与RF等不同的IC组件整合于一个封装体上。

其长远目标是将无线(Wireless)、光学(Optical),流体(Fluid)和生物元素(Bio Element)等作整合,并且具有界面电磁波隔绝保护和热的管理等功能。

SiP最新整合技术,可以将感测组件(Sensor Device)、讯号及数据处理器(Signal & Data Processors)、无线及光学沟通技术(Wireless & Optical Communication Technologies)、功率转换及储存组件(Power Conversion & Storage Devices)等整合在单一封装体上。

目前SiP有许多种分类,其中3D堆叠是属于SiP中之一项技术。

四、发展三维整合技术(3D Integration Technology)之驱动力促使三维整合技术发展的首要驱动力,主要是尺寸的缩小,也就是使封装体尽量缩小到最小体积。

然而,使用并列封装(Side by Side)、封装体与封装体之间的堆叠(Stacked Packages)和晶片堆叠(Stacked Die)等方案,其导线连接长度仍然太长。

因导线连接长度太长,则会导致讯号传输速度变慢,以及增加电力消耗。

所以三维整合技术是解决上述问题之最佳方案。

现今市场上之手持式电子产品,例如:手机、数字摄像机、Notebook、PDA及卫星导航等电子产品,皆为三维整合技术发展的最大诱因。

目前有许多种基于堆叠方法的三维封装技术,包括:在晶片上进行3-D整合,即在一个晶片上淀积各种功能性薄膜层;晶片到晶片或封装体到封装体之3-D 堆叠技术(package-on-package [POP] 或package-in-package [PIP]); 以及IC三维整合,其中使用硅导孔(Through Silicon Via; TSV)作晶片到晶片之互连技术,在所有三维封装(3-D Packaging)技术中,TSV技术可以提供最短和最直接的垂直连接。

五、发展硅导孔(Through Silicon Via; TSV)之3D IC方案的四大因素:图一. 发展TSV 3D IC方案的四大因素● 形状因素(Form Factor):可减少封装体尺寸和重量,增加封装密度,使单位体积内容纳最多组件。

在消费性电子走向轻薄短小的趋势下,各种电子组件,在单位面积与体积下,不断增加IC功能与内存容量,在水平方向的封装已经无法再扩张时,垂直方向的封装密度增加,将为未来发展趋势。

● 提高电性(Increased Electrical Performance):使用垂直互连技术,可以取代二维互连技术,以缩短组件之线路连接距离,进而降低寄生电容(Parasitic Capacitance)和耗电量(Power Consumption)。

●异质组件之整合(Heterogeneous Devices Integration):将不同性质之组件技术(RF、Memory、Logic、Sensors、Imagers)整合在一个封装体上;因此TSV之3D IC方案在性能、功能和尺寸上,可提供极大之优势。

●成本(Cost Driven):根据ITRS /Moore Law所公布,在技术与设备成熟条件下,未来采用3D整合技术会比2D设计准则,将更具成本效益。

比起Wire bonding在组件周围绕线,TSV的方法在同样的性能表现下,最多能节省30%的硅基板用量。

六、TSV技术被公认具有的三大潜在优势:● 连接长度可缩短至与薄晶圆厚度相同,可将逻辑区块(Logic Blocks)作垂直堆叠,以取代水平分布式之导线互连方式,所以可大大降低逻辑区块间导线互连(Block-to-Block Interconnects)之平均导线长度。

● 可达高密度、高深宽比之封装连接,能够整合复杂、多晶片系统在硅晶圆上,可作多次物理性封装,其封装密度比目前先进多晶片模块更佳。

● 可避免共平面式长导线互连所产生之RC延迟,采用立体方式来缩短逻辑区块间电性互连之长度。

截至目前为止以及不久的将来,集成电路封装的发展趋势,首先会将2-D结构提升至3-D 堆叠结构(引线、焊球和微导孔);进而应用TSV技术作三维集成电路之导线接合。

打线接合(Wire Bond)受到封装密度和性能的限制,而覆晶技术(Flip Chip)无法广泛应用于晶片堆叠。

因此为实现封装的小型化和提升性能,将无可避免地会应用到TSV技术。

3D- IC的主要目标市场,则包括:快闪记忆体(Flash Memory)、影像传感器(Image Sensor)、RF,以及内存与逻辑组件的异质整合。

尤其快闪记忆体和影像传感器,将会是最快使用TSV技术之产品。

七、TSV制作3D晶片堆叠的关键技术:图二. TSV的典型制作流程TSV的典型制作流程如图二所示,图三为TSV的关键技术示意图。

(1).导孔的蚀刻(Via Etch):可以使用雷射钻孔(Laser Drill)或深反应性离子蚀刻(Deep Reactive Ion Etching; DRIE):工艺上强调导孔轮廓尺寸之一致性,以及导孔不能有残渣存在,而且导孔的形成必须能达到相当的高速度需求。

导孔(Via)的规格则根据应用领域的不同而定,其直径范围为5~100μm,深度范围为10~100μm,导孔密度为102到105 Vias / Chip。

其中,TSV导孔的蚀刻,一般采用的Bosch蚀刻工艺,会快速转换SF6电浆蚀刻与沉积聚合物气体(例如:C4F8)两道交换步骤。

因为在聚合物沉积与低RF Bias电压条件,其蚀刻对于光阻之选择比较高,在一些情况下选择比可高达100:1[3]。

(2.)导孔的填充(Via Fill):绝缘层(Insulation Layer)、阻挡层(Barrier Layer)和晶种层(Seed Layer)的淀积,铜的电镀填充(Copper Electroplating)、CMP去除多于电镀铜和重新分布引线(Redistribution Layer)电镀,金属层蚀刻与凸块制作。

其中,填充材料可分为多晶硅、铜、钨和高分子导体等材料;而填充技术可使用电镀、化学气相沉积、高分子涂布等方法[5]。

图四为TSV微导孔的结构图。

(3.) 导孔的工艺顺序(Via Process Flow Sequence):导孔的工艺顺序可分为,先导孔(Via First)或后导孔(Via Last)两种技术。

先导孔(Via First):在晶圆制造CMOS或BEOL步骤之前完成硅导孔通常被称作Via-first。

此时,TSV的制作可以在Fab厂前端金属互连之前进行,实现core-to-core的连接。

该方案目前在微处理器等高性能器件领域研究较多,主要作为SoC的替代方案。

Via First也可以在CMOS完成之后再进行TSV的制作,然后完成组件制造和后端的封装。

Via First 之直径范围1-10μm,深度范围10-60μm。

后导孔(Via Last):指的是将TSV放在封装生产阶段进行,该方案的明显优势是可以不改变现有集成电路之流程和设计。