IS24C01-PA中文资料

CAT24C0A1GWA-1.8TE13资料

© 2005 by Catalyst Semiconductor, Inc. Characteristics subject to change without notice 1Doc. No. 1081, Rev. EVDis co n ti n ue dPa rt CAT24C01B2Doc. No. 1081, Rev. E© 2005 by Catalyst Semiconductor, Inc.Characteristics subject to change without noticeABSOLUTE MAXIMUM RATINGS*Temperature Under Bias .................–55°C to +125°C Storage Temperature.......................–65°C to +150°C Voltage on Any Pin withRespect to Ground (1)...........–2.0V to +V CC + 2.0V V CC with Respect to Ground ...............–2.0V to +7.0V Package Power DissipationCapability (Ta = 25°C)..................................1.0W Lead Soldering Temperature (10 secs)............300°C Output Short Circuit Current (2)........................100mA *COMMENTStresses above those listed under “Absolute Maximum Ratings ” may cause permanent damage to the device.These are stress ratings only, and functional operation of the device at these or any other conditions outside of those listed in the operational sections of this specification is not implied. Exposure to any absolute maximum rating for extended periods may affect device performance and reliability.RELIABILITY CHARACTERISTICS Symbol Parameter Min MaxUnits Reference Test MethodN END (3)Endurance 1,000,000Cycles/Byte MIL-STD-883, Test Method 1033T DR (3)Data Retention 100Years MIL-STD-883, Test Method 1008V ZAP (3)ESD Susceptibility 2000Volts MIL-STD-883, Test Method 3015I LTH (3)(4)Latch-up100mAJEDEC Standard 17D.C. OPERATING CHARACTERISTICSV CC = +1.8V to +6.0V, unless otherwise specified.Limits Symbol ParameterMin TypMax Units Test Conditions I CC Power Supply Current 3mA f SCL = 100 KHz I SB (5)Standby Current (V CC = 5.0V)1µA V IN = GND or V CC I LI Input Leakage Current 10µA V IN = GND to V CC I LO Output Leakage Current 10µA V OUT = GND to V CCV IL Input Low Voltage –1V CC x 0.3V V IH Input High VoltageV CC x 0.7V CC + 0.5V V OL1Output Low Voltage (V CC = 3.0V)0.4V I OL = 3 mA V OL2Output Low Voltage (V CC = 1.8V)0.5VI OL = 1.5 mANote:(1)The minimum DC input voltage is –0.5V. During transitions, inputs may undershoot to –2.0V for periods of less than 20 ns. Maximum DCvoltage on output pins is V CC +0.5V, which may overshoot to V CC + 2.0V for periods of less than 20ns.(2)Output shorted for no more than one second. No more than one output shorted at a time.(3)These parameter are tested initially and after a design or process change that affects the parameter according to appropriate AEC-Q100and JEDEC test methods.(4)Latch-up protection is provided for stresses up to 100 mA on address and data pins from –1V to V CC +1V.(5)Maximum standby current (I SB ) = 10µA for the Automotive and Extended Automotive temperature range.CAPACITANCE T A = 25°C, f = 1.0 MHz, V CC = 5V Symbol TestMax Units Conditions C I/O (3)Input/Output Capacitance (SDA)8pF V I/O = 0V C IN (3)Input Capacitance (A0, A1, A2, SCL, WP)6pFV IN = 0VCAT24C01B3Doc. No. 1081, Rev. E© 2005 by Catalyst Semiconductor, Inc.Characteristics subject to change without noticeA.C. CHARACTERISTICSV CC = +1.8V to +6.0V, C L =1TTL Gate and 100pF (unless otherwise specified).Read & Write Cycle Limits Note:(1)This parameter is tested initially and after a design or process change that affects the parameter.(2)t PUR and t PUW are the delays required from the time V CC is stable until the specified operation can be initiated.The write cycle time is the time from a valid stop condition of a write sequence to the end of the internal program/erase cycle. During the write cycle, the businterface circuits are disabled, SDA is allowed to remainhigh, and the device does not respond to its input.dPa rt CAT24C01B4Doc. No. 1081, Rev. E© 2005 by Catalyst Semiconductor, Inc.Characteristics subject to change without noticeFUNCTIONAL DESCRIPTIONThe CAT24C01B uses a 2-wire data transmission pro-tocol. The protocol defines any device that sends data to the bus to be a transmitter and any device receiving data to be a receiver. Data transfer is controlled by the Master device which generates the serial clock and all START and STOP conditions for bus access. The CAT24C01B operates as a Slave device. Both the Master and Slave devices can operate as either transmitter or receiver, but the Master device controls which mode is activated.PIN DESCRIPTIONSSCL: Serial ClockThe CAT24C01B serial clock input pin is used to clock all data transfers into or out of the device. This is an input pin.SDA: Serial Data/AddressThe CAT24C01B bidirectional serial data/address pin is used to transfer data into and out of the device. The SDA pin is an open drain output and can be wired with other open drain or open collector outputs.2-WIRE BUS PROTOCOLThe following defines the features of the 2-wire bus protocol:(1)Data transfer may be initiated only when the bus isnot busy.(2)During a data transfer, the data line must remainstable whenever the clock line is high. Any changes in the data line while the clock line is high will be interpreted as a START or STOP condition.Figure 3. Start/Stop Timing5020 FHD F055020 FHD F03SCLSDA INSDA OUTSTART BITSDA STOP BITSCLDis co n ti n ue dPa rt CAT24C01B5Doc. No. 1081, Rev. E© 2005 by Catalyst Semiconductor, Inc.Characteristics subject to change without noticeSTART ConditionThe START Condition precedes all commands to the device, and is defined as a HIGH to LOW transition of SDA when SCL is HIGH. The CAT24C01B monitors the SDA and SCL lines and will not respond until this condition is met.STOP ConditionA LOW to HIGH transition of SDA when SCL is HIGH determines the STOP condition. All operations must end with a STOP condition.AcknowledgeAfter a successful data transfer, each receiving device is required to generate an acknowledge. The Acknowledg-ing device pulls down the SDA line during the ninth clock cycle, signaling that it received the 8 bits of data.The CAT24C01B responds with an acknowledge after receiving a START condition and its slave address. If the device has been selected along with a write operation,it responds with an acknowledge after receiving each 8-bit byte.When the CAT24C01B is in a READ mode it transmits 8 bits of data, releases the SDA line, and monitors the line for an acknowledge. Once it receives this acknowl-edge, the CAT24C01B will continue to transmit data. If no acknowledge is sent by the Master, the device terminates data transmission and waits for a STOP condition.WRITE OPERATIONSByte WriteIn the Byte Write mode, the Master device sends the START condition and the slave address information (with the R/W bit set to zero) to the Slave device. After the Slave generates an acknowledge, the Master sends the byte address that is to be written into the address pointer of the CAT24C01B. After receiving another acknowl-edge from the Slave, the Master device transmits the data byte to be written into the addressed memory location. The CAT24C01B acknowledge once more and the Master generates the STOP condition, at which time the device begins its internal programming cycle to nonvolatile memory. While this internal cycle is in progress, the device will not respond to any request from the Master device.Page WriteThe CAT24C01B writes up to 4 bytes of data in a single write cycle, using the Page Write operation. The Page Write operation is initiated in the same manner as the Byte Write operation, however instead of terminating after the initial word is transmitted, the Master is allowed to send up to 3 additional bytes. After each byte has been transmitted the CAT24C01B will respond with an ac-knowledge, and internally increment the low order ad-dress bits by one. The high order bits remain un-changed.If the Master transmits more than 4 bytes prior to sending the STOP condition, the address counter ‘wraps around,’and previously transmitted data will be overwritten.Once all 4 bytes are received and the STOP condition has been sent by the Master, the internal programming cycle begins. At this point all received data is written to the CAT24C01B in a single write cycle.Note: Catalyst Semiconductor does program all "1" datainto the entire memory array prior to shipping our EEPROM products.Figure 4. Acknowledge Timing5020 FHD F06ACKNOWLEDGESTARTSCL FROM MASTERDATA OUTPUTFROM TRANSMITTERDATA OUTPUT FROM RECEIVERDis co n ti n ue dPa rt CAT24C01B6Doc. No. 1081, Rev. E© 2005 by Catalyst Semiconductor, Inc.Characteristics subject to change without noticeFigure 6. Page Write TimingFigure5. Byte Write Timinging with an acknowledge and by issuing a stop condition.Refer to Figure 7 for the start word address, read bit,acknowledge and data transfer sequence.Sequential ReadThe Sequential READ operation can be initiated after the 24C01B sends the initial 8-bit byte requested, the Master will respond with an acknowledge which tells the device it requires more data. The CAT24C01B will continue to output an 8-bit byte for each acknowledge sent by the Master. The operation is terminated when the Master fails to respond with an acknowledge, thus sending the STOP condition.The data being transmitted from the CAT24C01B is output sequentially with data from address N followed by data from address N+1. The READ operation address counter increments all of the CAT24C01B address bits so that the entire memory array can be read during one operation. If more than bytes are read out, the counter will “wrap around ” and continue to clock out data bytes.Acknowledge PollingThe disabling of the inputs can be used to take advan-tage of the typical write cycle time. Once the stop condition is issued to indicate the end of the host ’s write operation, the CAT24C01B initiates the internal write cycle. ACK polling can be initiated immediately. This involves issuing the start condition followed by the byte address for a write operation. If the CAT24C01B is still busy with the write operation, no ACK will be returned.If the CAT24C01B has completed the write operation, an ACK will be returned and the host can then proceed with the next read or write operation.READ OPERATIONSThe READ operation for the CAT24C01B is initiated in the same manner as the write operation with the one exception that the R/W bit is set to a one. Two different READ operations are possible: Byte READ and Se-quential READ.It should be noted that the ninth clock cycle of the read operation is not a "don't care." To terminate a read operation, the master must either issure a stop condition during the ninth cycle or hold SDA HIGH during the ninth clock cycle and then issue a stop condition.Byte ReadTo initiate a read operation, the master sends a start condition followed by a seven bit word address and a read bit. The CAT24C01B responds with an acknowl-edge and then transmits the eight bits of data. The read operation is terminated by the master; by not respond-BUS ACTIVITY:SDA LINEC KC KDATA n S T O C K C KS T A R WORD S BS B /W BUS ACTIVITY:BUS ACTIVITY:SDA LINEA C KA C KDATA nST O P SST A R TPWORD ADDRESS(n)MS BL S B R /W BUS ACTIVITY:ue drt CAT24C01B7Doc. No. 1081, Rev. E© 2005 by Catalyst Semiconductor, Inc.Characteristics subject to change without noticeFigure 7. Byte Read TimingBUS ACTIVITYMASTER SDA LINE KA C ST O AC A C /W BUS ACTIVITY CAT24C01BFigure 8. Sequential Read TimingORDERING INFORMATIONNotes:(1)The device used in the above example is a 24C01BJI-1.8TE13 (SOIC, Industrial Temperature, 1.8 Volt to 6 Volt OperatingVoltage, Tape & Reel)(2)Product die revision letter is marked on top of the package as a suffix to the production date code (e.g. AYWWA). For additionalinformation, please contact your Catalyst sales office.BUS ACTIVITYMASTERSDA LINE A C KA C KDATA nS T O P S S T A R T PWORD ADDRESS(n)M S BL S B R /W BUS ACTIVITY CAT24C01B(2)Dis co n ti n ue dPa rt Catalyst Semiconductor, Inc.Corporate Headquarters 1250 Borregas Avenue Sunnyvale, CA 94089Phone: 408.542.1000Fax: 408.542.1200Copyrights, Trademarks and PatentsTrademarks and registered trademarks of Catalyst Semiconductor include each of the following:DPP ™AE 2 ™MiniPot™Catalyst Semiconductor has been issued U.S. and foreign patents and has patent applications pending that protect its products. For a complete list of patents issued to Catalyst Semiconductor contact the Company’s corporate office at 408.542.1000.CATALYST SEMICONDUCTOR MAKES NO WARRANTY, REPRESENTATION OR GUARANTEE, EXPRESS OR IMPLIED, REGARDING THE SUITABILITY OF ITS PRODUCTS FOR ANY PARTICULAR PURPOSE, NOR THAT THE USE OF ITS PRODUCTS WILL NOT INFRINGE ITS INTELLECTUAL PROPERTY RIGHTS OR THE RIGHTS OF THIRD PARTIES WITH RESPECT TO ANY PARTICULAR USE OR APPLICATION AND SPECIFICALLY DISCLAIMS ANY AND ALL LIABILITY ARISING OUT OF ANY SUCH USE OR APPLICATION, INCLUDING BUT NOT LIMITED TO, CONSEQUENTIAL OR INCIDENTAL DAMAGES.Catalyst Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Catalyst Semiconductor product could create a situation where personal injury or death may occur.Catalyst Semiconductor reserves the right to make changes to or discontinue any product or service described herein without notice. Products with data sheets labeled "Advance Information" or "Preliminary" and other products described herein may not be in production or offered for sale.Catalyst Semiconductor advises customers to obtain the current version of the relevant product information before placing orders. Circuit diagrams illustrate typical semiconductor applications and may not be complete.Publication #:1081Revison:EIssue date:08/03/05REVISION HISTORYe t a D n o i s i v e R st n e m m o C 4002/71/40Bn o i t a m r o f n I g n i r e d r O e t a d p U re b m u N .v e R e t a d p U 4002/7/7C n o i t a m r of n Ig n i r e d r O o t n o i s i v e r e i d d e d d A 50/30/80Eno i t a m r o f n I g n i r e d r O e t a d p U。

24C01中文资料

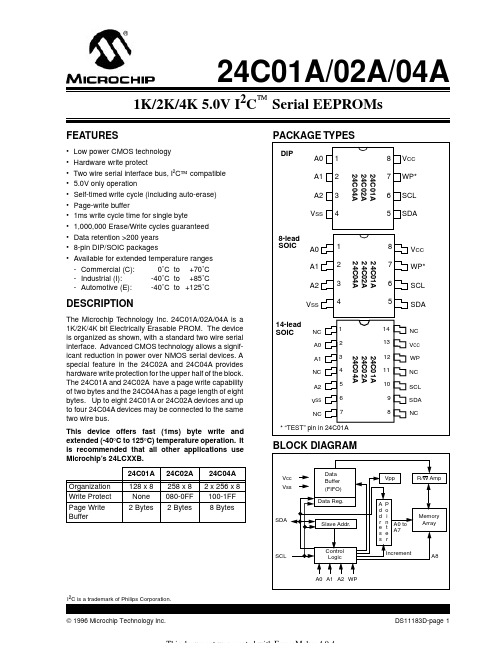

©1996 Microchip Technology Inc.DS11183D-page 124C01A/02A/04AFEATURES•Low power CMOS technology •Hardware write protect•Two wire serial interface bus, I 2 C ™ compatible • 5.0V only operation•Self-timed write cycle (including auto-erase)•Page-write buffer•1ms write cycle time for single byte•1,000,000 Erase/Write cycles guaranteed •Data retention >200 years •8-pin DIP/SOIC packages•Available for extended temperature ranges DESCRIPTIONThe Microchip Technology Inc. 24C01A/02A/04A is a 1K/2K/4K bit Electrically Erasable PROM. The device is organized as shown, with a standard two wire serial interface. Advanced CMOS technology allows a signif-icant reduction in power over NMOS serial devices. A special feature in the 24C02A and 24C04A provides hardware write protection for the upper half of the block.The 24C01A and 24C02A have a page write capability of two bytes and the 24C04A has a page length of eight bytes. Up to eight 24C01A or 24C02A devices and up to four 24C04A devices may be connected to the same two wire bus.This device offers fast (1ms) byte write and extended (-40 ° C to 125 ° C) temperature operation. It is recommended that all other applications use Microchip’s 24LCXXB.-Commercial (C):0˚C to +70˚C -Industrial (I):-40˚C to +85˚C -Automotive (E):-40˚C to +125˚C24C01A24C02A 24C04A Organization 128 x 8258 x 8 2 x 256 x 8Write Protect None 080-0FF 100-1FF Page Write Buffer2 Bytes2 Bytes8 BytesPACKAGE TYPESBLOCK DIAGRAMNC SS CC A0A1NC A2NCV 1234567141312NC SCL SDA NC981110WP V NC * “TEST” pin in 24C01A24C01A 24C02A 24C04A24C01A 24C02A 24C04A24C01A 24C02A 24C04AA0A1A2V SS12348765V CC WP*SCL SDAA0A1A2V SS12348765V CC WP*SCL SDADIP8-leadSOIC14-lead SOICVcc VssSDASCLData Buffer (FIFO)Data Reg.VppR/W AmpMemory ArrayA d d r e s s P o in te rA0 to A7IncrementA8Slave Addr.Control LogicA0A1A2WP1K/2K/4K 5.0V I 2 C ™Serial EEPROMsI 2 C is a trademark of Philips Corporation.This document was created with FrameMaker 404元器件交易网24C01A/02A/04ADS11183D-page 2 © 1996 Microchip Technology Inc.1.0ELECTRICAL CHARACTERISTICS1.1Maximum Ratings*V CC ...................................................................................7.0V All inputs and outputs w.r.t. V SS ...............-0.6V to V CC +1.0V Storage temperature.....................................-65˚C to +150˚C Ambient temp. with power applied................-65˚C to +125˚C Soldering temperature of leads (10 seconds).............+300˚C ESD protection on all pins................................................4 kV*Notice: Stresses above those listed under “Maximum ratings”may cause permanent damage to the device. This is a stress rat-ing only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.TABLE 1-1:PIN FUNCTION TABLEName FunctionA0No Function for 24C04A only, Must be connected to V CC or V SS A0, A1, A2Chip Address Inputs V SS GroundSDA Serial Address/Data I/O SCL Serial ClockTEST (24C01A only) V CC or V SS WP Write Protect Input VCC+5V Power SupplyTABLE 1-2:DC CHARACTERISTICSFIGURE 1-1:BUS TIMING START/STOPVCC = +5V ( ± 10%)Commercial (C):Tamb =0 ° C to +70 ° C Industrial (I):Tamb =-40 ° C to +85 ° C Automotive (E):Tamb =-40 ° C to +125 ° CParameterSymbolMin.Max.Units ConditionsV CC detector threshold V TH 2.8 4.5V SCL and SDA pins:High level input voltage Low level input voltage Low level output voltage V IH V IL V OL V CC x 0.7-0.3V CC + 1V CC x 0.30.4V V V I OL = 3.2 mA (SDA only)A1 & A2 pins:High level input voltage Low level input voltage V IH V IL V CC - 0.5-0.3V CC + 0.50.5V V Input leakage current ILI—10 µ A V IN = 0V to V CC Output leakage current ILO —10 µ A V OUT = 0V to V CCPin capacitance (all inputs/outputs)C IN , C OUT —7.0pF V IN /V OUT = 0V (Note) Tamb = +25˚C, f = 1 MHzOperating current I CC Write — 3.5mA F CLK = 100 kHz, program cycle time = 1 ms, Vcc = 5V, Tamb = 0˚C to +70˚CI CC Write—4.25mAF CLK = 100 kHz, program cycle time = 1 ms, Vcc = 5V, Tamb = (I) and (E)ICC Read—750 µ AV CC = 5V, Tamb= (C), (I) and (E)Standby current ICCS—100 µ A SDA=SCL=VCC=5V (no PROGRAM active)Note:This parameter is periodically sampled and not 100% testedT SU :STAT HD :STAV HYST SU :STOSTART STOPSCLSDA元器件交易网©1996 Microchip Technology Inc.DS11183D-page 324C01A/02A/04ATABLE 1-3:AC CHARACTERISTICSFIGURE 1-2:BUS TIMING DATAParameterSymbol Min.Typ Max.Units RemarksClock frequency F CLK ——100kHz Clock high time T HIGH 4000——ns Clock low timeT LOW 4700——ns SDA and SCL rise time T R ——1000ns SDA and SCL fall time T F ——300ns START condition hold time T HD :S TA 4000——ns After this period the first clock pulse is generated START condition setup time T SU :S TA 4700——ns Only relevant for repeated START conditionData input hold time T HD :D AT 0——ns Data input setup time T SU :D AT 250——nsData output delay time T AA 300—3500(Note 1)STOP condition setup time T SU :S TO 4700——ns Bus free timeT BUF4700——nsTime the bus must be free before a new transmission can startInput filter time constant (SDA and SCL pins)T I ——100ns Program cycle timeTWC—.41ms Byte mode.4N N ms Page mode, N=# of bytesEndurance —1M ——cycles25 °C, Vcc = 5.0V, BlockMode (Note 2)Note 1:As transmitter the device must provide this internal minimum delay time to bridge the undefined region (min-imum 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.2:This parameter is not tested but guaranteed by characterization. For endurance estimates in a specific appli-cation, please consult the Total Endurance Model which can be obtained on our BBS or website.T SU :STAT FT LOWT HIGHT RT HD :DATT SU :DAT T SU :STOT HD :STAT BUFT AAT AAT SPT HD :STASCLSDA INSDA OUT元器件交易网24C01A/02A/04ADS11183D-page 4© 1996 Microchip Technology Inc.2.0FUNCTIONAL DESCRIPTIONThe 24C01A/02A/04A supports a bidirectional two wire bus and data transmission protocol. A device that sends data onto the bus is defined as transmitter, and a device receiving data as receiver. The bus has to be controlled by a master device which generates the serial clock (SCL), controls the bus access, and gener-ates the START and STOP conditions, while the 24C01A/02A/04A works as slave. Both master and slave can operate as transmitter or receiver but the master device determines which mode is activated.Up to eight 24C01/24c02s can be connected to the bus,selected by the A0, A1 and A2 chip address inputs. Up to four 24C04As can be connected to the bus, selected by A1 and A2 chip address inputs. A0 must be tied to V CC or V SS for the 24C04A. Other devices can be con-nected to the bus but require different device codes than the 24C01A/02A/04A (refer to section Slave Address).3.0BUS CHARACTERISTICSThe following bus protocol has been defined:•Data transfer may be initiated only when the bus is not busy.•During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is HIGH will be interpreted as a START or STOP condition.Accordingly, the following bus conditions have been defined (Figure 3-1).3.1Bus not Busy (A)Both data and clock lines remain HIGH.3.2Start Data Transfer (B)A HIGH to LOW transition of the SDA line while the clock (SCL) is HIGH determines a START condition. All commands must be preceded by a START condition.3.3Stop Data Transfer (C)A LOW to HIGH transition of the SDA line while the clock (SCL) is HIGH determines a STOP condition. All operations must be ended with a STOP condition.3.4Data Valid (D)The state of the data line represents valid data when,after a START condition, the data line is stable for the duration of the HIGH period of the clock signal.The data on the line must be changed during the LOW period of the clock signal. There is one clock pulse per bit of data.Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of the data bytes transferred between the START and STOP conditions is determined by the master device and is theoretically unlimited.3.5AcknowledgeEach receiving device, when addressed, is obliged to generate an acknowledge after the reception of each byte. The master device must generate an extra clock pulse which is associated with this acknowledge bit.The device that acknowledges has to pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse. Of course, setup and hold times must be taken into account. A master must signal an end of data to the slave by not generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case, the slave must leave the data line HIGH to enable the master to generate the STOP condition.Note:The 24C01A/02A/04A does not generate any acknowledge bits if an internal pro-gramming cycle is in progress.FIGURE 3-1:DATA TRANSFER SEQUENCE ON THE SERIAL BUS(A)(B)(D)(D)(A)(C)START CONDITIONADDRESS OR ACKNOWLEDGEVALID DATA ALLOWED TO CHANGESTOP CONDITIONSCLSDA元器件交易网© 1996 Microchip Technology Inc.DS11183D-page 524C01A/02A/04A4.0SLAVE ADDRESSThe chip address inputs A0, A1 and A2 of each 24C01A/02A/04A must be externally connected to either V CC or ground (V SS ), assigning to each 24C01A/02A/04A a unique address. A0 is not used on the 24C04A and must be connected to either V CC or V SS . Up to eight 24C01A or 24C02A devices and up to four 24C04A devices may be connected to the bus. Chip selection is then accomplished through software by setting the bits A0, A1 and A2 of the slave address to the corresponding hard-wired logic levels of the selected 24C01A/02A/04A.After generating a START condition, the bus master transmits the slave address consisting of a 4-bit device code (1010) for the 24C01A/02A/04A, followed by the chip address bits A0, A1 and A2. In the 24C04A, the seventh bit of that byte (A0) is used to select the upper block (addresses 100—1FF) or the lower block (addresses 000—0FF) of the array.The eighth bit of slave address determines if the master device wants to read or write to the 24C01A/02A/04A (Figure 4-1).The 24C01A/02A/04A monitors the bus for its corre-sponding slave address all the time. It generates an acknowledge bit if the slave address was true and it is not in a programming mode.FIGURE 4-1:SLAVE ADDRESS ALLOCATION5.0BYTE PROGRAM MODEIn this mode, the master sends addresses and one data byte to the 24C01A/02A/04A.Following the START signal from the master, the device code (4-bits), the slave address (3-bits), and the R/W bit, which is logic LOW, are placed onto the bus by the master. This indicates to the addressed 24C01A/02A/04A that a byte with a word address will follow after it has generated an acknowledge bit. Therefore the next byte transmitted by the master is the word address and will be written into the address pointer of the 24C01A/02A/04A. After receiving the acknowledge of the 24C01A/02A/04A, the master device transmits the data word to be written into the addressed memory location.The 24C01A/02A/04A acknowledges again and the master generates a STOP condition. This initiates the internal programming cycle of the 24C01A/02A/04A (Figure 6-1).SLAVE ADDRESS1010A2A1A0R/W ASTARTREAD/WRITE6.0PAGE PROGRAM MODETo program the 24C01A/02A/04A, the master sends addresses and data to the 24C01A/02A/04A which is the slave (Figure 6-1 and Figure 6-2). This is done by supplying a START condition followed by the 4-bit device code, the 3-bit slave address, and the R/W bit which is defined as a logic LOW for a write. This indi-cates to the addressed slave that a word address will follow so the slave outputs the acknowledge pulse to the master during the ninth clock pulse. When the word address is received by the 24C01A/02A/04A, it places it in the lower 8 bits of the address pointer defining which memory location is to be written. (The A0 bit transmitted with the slave address is the ninth bit of the address pointer for the 24C04A). The 24C01A/02A/04A will generate an acknowledge after every 8-bits received and store them consecutively in a RAM buffer until a STOP condition is detected. This STOP condi-tion initiates the internal programming cycle. The RAM buffer is 2 bytes for the 24C01A/02A and 8 bytes for the 24C04A. If more than 2 bytes are transmitted by the master to the 24C01A/02A, the device will not acknowl-edge the data transfer and the sequence will be aborted. If more than 8 bytes are transmitted by the master to the 24C04A, it will roll over and overwrite the data beginning with the first received byte. This does not affect erase/write cycles of the EEPROM array and is accomplished as a result of only allowing the address registers bottom 3 bits to increment while the upper 5bits remain unchanged.If the master generates a STOP condition after trans-mitting the first data word (Point ‘P’ on Figure 6-1), byte programming mode is entered.The internal, completely self-timed PROGRAM cycle starts after the STOP condition has been generated by the master and all received data bytes in the page buffer will be written in a serial manner.The PROGRAM cycle takes N milliseconds, whereby N is the number of received data bytes (N max = 8 for 24C04A, 2 for 24C01A/02A).元器件交易网24C01A/02A/04ADS11183D-page 6© 1996 Microchip Technology Inc.FIGURE 6-1:BYTE WRITEFIGURE 6-2:PAGE WRITESPBUS ACTIVITY MASTER SDA LINE BUS ACTIVITYS T A R TS T O PCONTROL BYTE WORD ADDRESSDATAA C KA C KA C KSPBUS ACTIVITY MASTERSDA LINE BUS ACTIVITYS T A R TCONTROL BYTE WORD ADDRESS (n)DATA n DATA n + 7S T O PA C KA C KA C KA C KA C KDATA n + 17.0ACKNOWLEDGE POLLINGSince the device will not acknowledge during a write cycle, this can be used to determine when the cycle is complete (this feature can be used to maximize bus throughput). Once the stop condition for a write com-mand has been issued from the master, the device ini-tiates the internally timed write cycle. ACK polling can be initiated immediately. This involves the master send-ing a start condition followed by the control byte for a write command (R/W = 0). If the device is still busy with the write cycle, then no ACK will be returned. If the cycle is complete, then the device will return the ACK and the master can then proceed with the next read or write command. See Figure 7-1 for flow diagram.FIGURE 7-1:ACKNOWLEDGE POLLING FLOWSendWrite CommandSend Stop Condition to Initiate Write CycleSend StartSend Control Byte with R/W = 0Did Device Acknowledge (ACK = 0)?Next OperationNOYES元器件交易网© 1996 Microchip Technology Inc.DS11183D-page 724C01A/02A/04A8.0WRITE PROTECTIONProgramming of the upper half of the memory will not take place if the WP pin of the 24C02A or 24C04A is connected to V CC (+5.0V). The device will accept slave and word addresses but if the memory accessed is write protected by the WP pin, the 24C02A/04A will not generate an acknowledge after the first byte of data has been received, and thus the program cycle will not be started when the STOP condition is asserted. Polarity of the WP pin has no effect on the 24C01A.9.0READ MODEThis mode illustrates master device reading data from the 24C01A/02A/04A.As can be seen from Figure 9-2 and Figure 9-3, the master first sets up the slave and word addresses by doing a write. (Note: Although this is a read mode, the address pointer must be written to). During this period the 24C01A/02A/04A generates the necessary acknowledge bits as defined in the appropriate section.The master now generates another START condition and transmits the slave address again, except this time the read/write bit is set into the read mode. After the slave generates the acknowledge bit, it then outputs the data from the addressed location on to the SDA pin,increments the address pointer and, if it receives an acknowledge from the master, will transmit the next consecutive byte. This auto-increment sequence is only aborted when the master sends a STOP condition instead of an acknowledge.Note 1:If the master knows where the addresspointer is, it can begin the read sequence at the current address (Figure 9-1) and save time transmitting the slave and word addresses.Note 2:In all modes, the address pointer will notincrement through a block (256 byte)boundary, but will rotate back to the first location in that block.FIGURE 9-1:CURRENT ADDRESS READFIGURE 9-2:RANDOM READSPBUS ACTIVITY MASTERSDA LINE BUS ACTIVITYS T A R TS T O PCONTROL BYTEDATA nA C KN O A C KSPSBUS ACTIVITY MASTERSDA LINEBUS ACTIVITYS T A R TS T O PCONTROL BYTE A C KWORD ADDRESS (n)CONTROL BYTES T A R TDATA (n)A C KA C KN O A C K元器件交易网24C01A/02A/04ADS11183D-page 8© 1996 Microchip Technology Inc.FIGURE 9-3:SEQUENTIAL READPBUS ACTIVITY MASTER SDA LINE BUS ACTIVITYS T O PCONTROL BYTEA C KN O A C KDATA n DATA n + 1DATA n + 2DATA n + XA C KA C KA C K10.0PIN DESCRIPTION10.1A0, A1, A2 Chip Address InputsThe levels on these inputs are compared with the cor-responding bits in the slave address. The chip is selected if the compare is true. For 24C04 A0 is no function.Up to eight 24C01A/02A's or up to four 24C04A's can be connected to the bus.These inputs must be connected to either V SS or V CC .10.2SDA Serial Address/Data Input/OutputThis is a bidirectional pin used to transfer addresses and data into and data out of the device. It is an open drain terminal, therefore the SDA bus requires a pull-up resistor to V CC (typical 10K Ω).For normal data transfer, SDA is allowed to change only during SCL LOW. Changes during SCL HIGH are reserved for indicating the START and STOP condi-tions.10.3SCL Serial ClockThis input is used to synchronize the data transfer from and to the device.10.4WP Write ProtectionThis pin must be connected to either V CC or V SS for 24C02A or 24C04A. It has no effect on 24C01A.If tied to V CC , PROGRAM operations onto the upper memory block will not be executed. Read operations are possible.If tied to V SS , normal memory operation is enabled (read/write the entire memory).This feature allows the user to assign the upper half of the memory as ROM which can be protected against accidental programming. When write is disabled, slave address and word address will be acknowledged but data will not be acknowledged.Note 1: A “page” is defined as the maximum num-ber of bytes that can be programmed in a single write cycle. The 24C04A page is 8bytes long; the 24C01A/02A page is 2bytes long.Note 2: A “block” is defined as a continuous areaof memory with distinct boundaries. The address pointer can not cross the bound-ary from one block to another. It will how-ever, wrap around from the end of a block to the first location in the same block. The 24C04A has two blocks, 256 bytes each.The 24C01A and 24C02A each have only one block.元器件交易网元器件交易网24C01A/02A/04A NOTES:© 1996 Microchip Technology Inc.DS11183D-page 924C01A/02A/04ADS11183D-page 10© 1996 Microchip Technology Inc.NOTES:元器件交易网24C01A/02A/04A© 1996 Microchip Technology Inc.DS11183D-page 1124C01A/02A/04A Product Identification SystemTo order or to obtain information, e.g., on pricing or delivery, please use the listed part numbers, and refer to the factory or the listed sales offices.Package:P =Plastic DIPSN =Plastic SOIC (150 mil Body), 8-lead SM =Plastic SOIC (207 mil Body), 8-leadSL =Plastic SOIC (150 mil Body), 14-lead, 24C04A onlyTemperature Blank =0°C to +70°CRange:I =-40°C to +85°C E =-40°C to +125°C Device:24C01A 1K I 2C Serial EEPROM24C01AT 1K I 2C Serial EEPROM (Tape and Reel)24C02A 2K I 2C Serial EEPROM24C02AT 2K I 2C Serial EEPROM (Tape and Reel)24C04A 4K I 2C Serial EEPROM24C04AT4K I 2C Serial EEPROM (Tape and Reel)24C01A/02A/04A-/P元器件交易网DS11183D-page 12© 1996 Microchip Technology Inc.Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. No repre-sentation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip’s products as critical components in life support systems is not autho-rized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights. The Microchip logo and name are registered trademarks of Microchip Technology Inc. All rights reserved. All other trademarks mentioned herein are the property of their respective companies.W ORLDWIDE S ALES & S ERVICEASIA/PACIFICChinaMicrochip TechnologyUnit 406 of Shanghai Golden Bridge Bldg.2077 Yan’an Road West, Hongiao District Shanghai, Peoples Republic of China Tel: 86 21 6275 5700Fax: 011 86 21 6275 5060 Hong KongMicrochip Technology RM 3801B, Tower Two Metroplaza223 Hing Fong RoadKwai Fong, N.T. Hong KongTel: 852 2 401 1200 Fax: 852 2 401 3431IndiaMicrochip TechnologyNo. 6, Legacy, Convent Road Bangalore 560 025 IndiaTel: 91 80 526 3148 Fax: 91 80 559 9840KoreaMicrochip Technology168-1, Youngbo Bldg. 3 Floor Samsung-Dong, Kangnam-Ku,Seoul, KoreaTel: 82 2 554 7200 Fax: 82 2 558 5934SingaporeMicrochip Technology 200 Middle Road #10-03 Prime Centre Singapore 188980Tel: 65 334 8870 Fax: 65 334 8850Taiwan, R.O.CMicrochip Technology 10F-1C 207Tung Hua North Road Taipei, Taiwan, ROCTel: 886 2 717 7175 Fax: 886 2 545 0139EUROPEUnited KingdomArizona Microchip Technology Ltd.Unit 6, The CourtyardMeadow Bank, Furlong RoadBourne End, Buckinghamshire SL8 5AJ Tel: 44 1628 850303 Fax: 44 1628 850178FranceArizona Microchip Technology SARL Zone Industrielle de la Bonde 2 Rue du Buisson aux Fraises 91300 Massy - FranceTel: 33 1 69 53 63 20 Fax: 33 1 69 30 90 79GermanyArizona Microchip Technology GmbH Gustav-Heinemann-Ring 125D-81739 Muenchen, GermanyTel: 49 89 627 144 0 Fax: 49 89 627 144 44ItalyArizona Microchip Technology SRLCentro Direzionale Colleone Pas Taurus 1Viale Colleoni 120041 Agrate Brianza Milan ItalyTel: 39 39 6899939 Fax: 39 39 689 9883JAPANMicrochip Technology Intl. Inc.Benex S-1 6F3-18-20, Shin Yokohama Kohoku-Ku, Yokohama Kanagawa 222 JapanTel: 81 45 471 6166 Fax: 81 45 471 61229/3/96AMERICASCorporate OfficeMicrochip Technology Inc.2355 West Chandler Blvd.Chandler, AZ 85224-6199Tel: 602 786-7200 Fax: 602 786-7277Technical Support: 602 786-7627Web: AtlantaMicrochip Technology Inc.500 Sugar Mill Road, Suite 200B Atlanta, GA 30350Tel: 770 640-0034 Fax: 770 640-0307BostonMicrochip Technology Inc.5 Mount Royal Avenue Marlborough, MA 01752Tel: 508 480-9990 Fax: 508 480-8575ChicagoMicrochip Technology Inc.333 Pierce Road, Suite 180Itasca, IL 60143Tel: 708 285-0071 Fax: 708 285-0075DallasMicrochip Technology Inc.14651 Dallas Parkway, Suite 816Dallas, TX 75240-8809Tel: 972 991-7177 Fax: 972 991-8588DaytonMicrochip Technology Inc.Suite 150Two Prestige Place Miamisburg, OH 45342Tel: 513 291-1654 Fax: 513 291-9175Los AngelesMicrochip Technology Inc.18201 Von Karman, Suite 1090Irvine, CA 92612Tel: 714 263-1888 Fax: 714 263-1338New YorkMicrochip Technmgy Inc.150 Motor Parkway, Suite 416Hauppauge, NY 11788Tel: 516 273-5305 Fax: 516 273-5335San JoseMicrochip Technology Inc.2107 North First Street, Suite 590San Jose, CA 95131Tel: 408 436-7950 Fax: 408 436-7955TorontoMicrochip Technology Inc.5925 Airport Road, Suite 200Mississauga, Ontario L4V 1W1, Canada Tel: 905 405-6279Fax: 905 405-6253All rights reserved. © 1996, Microchip Technology Incorporated, USA. 9/96Printed on recycled paper.元器件交易网。

IS24C08中文资料

IS24C08中⽂资料IS24C01IS24C02IS24C04IS24C08IS24C16ISSICopyright ? 2002 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.1K-bit/2K-bit/4K-bit/8K-bit/16K-bit 2-WIRE SERIAL CMOS EEPROMAPRIL 2002DESCRIPTIONThe IS24CXX (refers to IS24C01, IS24C02, IS24C04,IS24C08, IS24C16) family is a low-cost and low voltage 2-wire Serial EEPROM. It is fabricated using ISSI’s advanced CMOS EEPROM technology and provides a low power and low voltage operation. The IS24CXX family features a write protection feature, and is available in 8-pin DIP and 8-pin SOIC packages.The IS24C01 is a 1K-bit EEPROM; IS24C02 is a 2K-bit EEPROM; IS24C04 is a 4K-bit EEPROM; IS24C08 is a 8K-bit EEPROM; IS24C16 is a 16K-bit EEPROM.The IS24C01 and IS24C02 are available in 8-pin MSOP package. The IS24C01, IS24C02, IS24C04, and IS24C08are available in 8-Pin TSSOP package.Automotive data is preliminary.FEATURESLow Power CMOS Technology–Standby Current less than 8 µA (5.5V)–Read Current (typical) less than 1 mA (5.5V)–Write Current (typical) less than 3 mA (5.5V)?Flexible Voltage Operation–Vcc = 1.8V to 5.5V for –2 version –Vcc = 2.5V to 5.5V for –3 version ?400 KHz (I 2C Protocol) Compatibility ?Hardware Data Protection–Write Protect Pin ?Sequential Read FeatureFiltered Inputs for Noise Suppression 8-pin PDIP and 8-pin SOIC packages 8-pin TSSOP (1K,2K, 4K & 8K only)8-pin MSOP (1K,2K only)Self time write cycle with auto clear 5 ms @ 2.5V Organization:–IS24C01128x8(one block of 128 bytes)–IS24C02256x8(one block of 256 bytes)–IS24C04512x8(two blocks of 256 bytes)–IS24C081024x8(four blocks of 256 bytes)–IS24C162048x8(eight blocks of 256 bytes)?Page Write BufferTwo-Wire Serial Interface–Bi-directional data transfer protocol ?High Reliability–Endurance: 1,000,000 Cycles –Data Retention: 100 YearsCommercial, Industrial and Automotive tempera-ture ranges元器件交易⽹/doc/af5937a6dd3383c4bb4cd241.html元器件交易⽹/doc/af5937a6dd3383c4bb4cd241.htmlIS24C01IS24C02IS24C04IS24C08 IS24C16ISSI?FUNCTIONAL BLOCK DIAGRAM2Integrated Silicon Solution, Inc. — /doc/af5937a6dd3383c4bb4cd241.html — 1-800-379-4774 Rev.DIS24C01IS24C02IS24C04IS24C08 IS24C16ISSIPIN DESCRIPTIONSA0-A2Address InputsSDA Serial Address/Data I/O SCL Serial Clock Input WP Write Protect Input Vcc Power Supply GNDGroundSCLThis input clock pin is used to synchronize the data transfer to and from the device.SDAThe SDA is a Bi-directional pin used to transfer addresses and data into and out of the device. The SDA pin is an open drain output and can be wire-Ored with other open drain or open collector outputs.The SDA bus requires a pullup resistor to Vcc. A0, A1, A2The A0, A1 and A2 are the device address inputs. The IS24C01 and IS24C02 use the A0, A1, and A2 for hardware addressing and a total of 8 devices may be used on a single bus system.PIN CONFIGURATION8-Pin DIP and SOIC8 Pin TSSOP (1K, 2K, 4K and 8K)8-Pin MSOP (1K, 2K)12348765A0A1A2GNDVCC WP SCL SDAThe IS24C04 uses A1 and A2 pins for hardwire addressing and a total of four devices may be addressed on a single bus system.The A0 pin is not used by IS24C04. This pin can be left floating or tied to GND or Vcc.The IS24C08 only use A2 input for hardwire addressing and a total of two devices may be addressed on a single bus system.The A0 and A1 pins are not used by IS24C08. They may be left floating or tied to either GND or Vcc.These pins are not used by IS24C16. A0 and A1 may be left floating or tied to either GND or Vcc. A2 should be tied to either GND or Vcc.WPWP is the Write Protect pin. On the 24C01, 24C02, IS24C04and 24C08, if the WP pin is tied to V CC the entire array becomes Write Protected (Read only). On the 24C16, if the WP pin is tied to Vcc the upper half array becomes Write Protected (Read only). When WP is tied to GND or left floating normal read/write operations are allowed to the device.元器件交易⽹/doc/af5937a6dd3383c4bb4cd241.htmlIS24C01IS24C02IS24C04IS24C08 IS24C16ISSI?DEVICE OPERATIONThe IS24CXX family features a serial communication and supports a bi-directional 2-wire bus transmission protocol. 2-WIRE BUSThe two-wire bus is defined as a Serial Data line(SDA), and a Serial Clock Line (SCL). The protocol defines any device that sends data onto the SDA bus as a transmitter, and the receiving devices as a receiver. The bus is controlled by MASTER device which generates the SCL, controls the bus access and generates the STOP and START conditions. The IS24CXX is the SLAVE device on the bus.THE BUS PROTOCOL:--Data transfer may be initiated only when the bus is not busy--During a data transfer, the data line must remain stable whenever the clock line is high. Any changes in the data line while the clock line is high will be interpreted as a START or STOP condition.The state of the data line represents valid data when after a START condition, the data line is stable for the duration of the HIGH period of the clock signal. The data on the line must be changed during the LOW period of the clock signal. There is one clock pulse per bit of data. Each data transfer is initiated with a START condition and terminated with a STOP condition.START CONDITIONThe START condition precedes all commands to the devices and is defined as a HIGH to LOW transition of SDA when SCL is HIGH. The IS24CXX monitors the SDA and SCL lines and will not respond until the START condition is met.STOP CONDITIONThe STOP condition is defined as a LOW to HIGH transition of SDA when SCL is HIGH. All operations must end with a STOP condition.ACKNOWLEDGEAfter a successful data transfer, each receiving device is required to generate an acknowledge. The Acknowledging device pulls down the SDA line.DEVICE ADDRESSINGThe MASTER begins a transmission by sending a START condition. The MASTER then sends the address of the particular slave devices it is requesting. The SLAVE address is 8 bytes.The four most significant bytes of the address are fixed as 1010 for the IS24CXX.For the IS24C16, the bytes(B2, B1 and B0) are used for memory page addressing (the IS24C16 is organized as eight blocks of 256 bytes).For the IS24C04 out of the next three bytes, B0 is for Memory Page Addressing (the IS24C04 is organized as two blocks of 256 bytes) and A2 and A1 bytes are used as device address bytes and must compare to its hard-wire inputs pins (A2 and A1). Up to four IS24C04's may be individually addressed by the system. The page addressing bytes forIS24Cxx should be considered the most significant bytes of the data word address which follows.For the IS24C08 out of the next three bytes, B1 and B0 are for memory page addressing (the IS24C08 is organized as four blocks of 256 bytes) and the A2 bit is used as device address bit and must compare to its hard-wired input pin (A2). Up to two IS24C08 may be individually addressed by the system. The page addressing bytes for IS24CXX should be considered the most significant bytes of the data word address which follows.For the IS24C01 and IS24C02, the A0, A1, and A2 are used as device address bytes and must compare to its hard-wired input pins (A0, A1, and A2) Up to Eight IS24C01 and/ or IS24C02's may be individually addressed by the system. The last bit of the slave address specifies whether a Read or Write operation is to be performed. When this bit is set to 1, a Read operation is selected, and when set to 0, a Write operation is selected.After the MASTER sends a START condition and the SLAVE address byte, the IS24CXX monitors the bus and responds with an Acknowledge (on the SDA line) when its address matches the transmitted slave address. The IS24CXX pulls down the SDA line during the ninth clock cycle, signaling that it received the eight bytes of data. The IS24CXX then performs a Read or Write operation depending on the state of the R/W bit.WRITE OPERATIONBYTE WRITEIn the Byte Write mode, the Master device sends the START condition and the slave address information(with the R/W set to Zero) to the Slave device. After the Slave generates an acknowledge, the Master sends the byte address that is to be written into the address pointer of the IS24CXX. After receiving another acknowledge from the Slave, the Master device transmits the data byte to be written into the address memory location. The IS24CXX acknowledges once more and the Master generatesthe STOP condition, at which time the device begins its internal programming cycle. While this internal cycle is in progress, the device will not respond to any request from the Master device.元器件交易⽹/doc/af5937a6dd3383c4bb4cd241.html4Integrated Silicon Solution, Inc. — /doc/af5937a6dd3383c4bb4cd241.html — 1-800-379-4774Rev.DIS24C01IS24C02IS24C04IS24C08 IS24C16ISSIcondition and the IS24CXX discontinues transmission. If 'n' is the last byte of the memory, then the data from location '0' will be transmitted. (Refer to Current Address Read Diagram.)RANDOM ADDRESS READSelective READ operations allow the Master device to select at random any memory location for a READ operation.The Master device first performs a 'dummy' write operation by sending the START condition, slave address and word address of the location it wishes to read. After the IS24CXX acknowledge the word address, the Master device resends the START condition and the slave address, this time with the R/W bit set to one. The IS24CXX then responds with its acknowledge and sends the data requested. The master device does not send an acknowledge but will generate a STOP condition. (Refer to Random Address Read Diagram.)SEQUENTIAL READSequential Reads can be initiated as either a Current Address Read or Random Address Read. After the IS24CXX sends initial byte sequence, the master device now responds with an ACKnowledge indicating it requires additional data from the IS24CXX. The IS24CXX continues to output data for each ACKnowledge received. The master device terminates the sequential READ operation by pulling SDA HIGH (no ACKnowledge) indicating the last data word to be read, followed by a STOP condition.The data output is sequential, with the data from address n followed by the data from address n+1, ... etc.The address counter increments by one automatically,allowing the entire memory contents to be serially read during sequential read operation. When the memory address boundary (127 for IS24C01; 255 for IS24C02; 511 for IS24C04; 1023 for IS24C08; 2047 forIS24C16) is reached,the address counter “rolls over” to address 0, and the IS24CXX continues to output data for each ACKnowledge received. (Refer to Sequential Read Operation Starting with a Random Address READ Diagram.)PAGE WRITEThe IS24CXX is capable of page-WRITE (8-byte for 24C01/02 and 16-byte for 24C04/08/16) operation. A page-WRITE is initiated in the same manner as a byte write, but instead of terminating the internal write cycle after the first data word is transferred, the master device can transmit up to N more bytes (N=7 for 24C01/02 and N=15 for 24C04/08/16). After the receipt of each data word, the IS24CXX responds immediately with an ACKnowledge on SDA line, and the three lower (24C01/24C02) or four lower (24C04/24C08/24C16) order data word address bits are internally incremented by one, while the higher order bits of the data word address remain constant. If the master device should transmit more than N+1 (N=7 for 24C01/02 and N=15 for 24C04/08/16) words, prior to issuing the STOP condition,the address counter will “roll over,” and the previously written data will be overwritten. Once all N+1 (N=7 for 24C01/02 and N=15 for 24C04/08/16) bytes are received and the STOP condition has been sent by the Master, the internal programming cycle begins. At this point, all received data is written to the IS24CXX in a single write cycle. All inputs are disabled until completion of the internal WRITE cycle. ACKNOWLEDGE POLLINGThe disabling of the inputs can be used to take advantage of the typical write cycle time. Once the stop condition is issued to indicate the end of the host's write operation, the IS24CXX initiates the internal write cycle. ACK polling can be initiated immediately. This involves issuing the start condition followed by the slave address for a write operation.If the IS24CXX is still busy with the write operation, no ACK will be returned. If the IS24CXX has completed the write operation, an ACK will be returned and the host can then proceed with the next read or write operation.READ OPERATIONREAD operations are initiated in the same manner as WRITE operations, except that the read/write bit of the slave address is set to “1”. There are three READ operation options: current address read, random address read and sequential read. CURRENT ADDRESS READThe IS24CXX contains an internal address counter which maintains the address of the last byte accessed, incremented by one. For example, if the previous operation is either a read or write operation addressed to the address location n,the internal address counter would increment to address location n+1. When the IS24CXX receives the Device Addressing Byte with a READ operation (read/write bit set to “1”), it will respond an ACKnowledge and transmit the 8-bit data word stored at address location n+1. The master will not acknowledge the transfer but does generate a STOP元器件交易⽹/doc/af5937a6dd3383c4bb4cd241.html元器件交易⽹/doc/af5937a6dd3383c4bb4cd241.htmlIS24C01IS24C02IS24C04IS24C08 IS24C16ISSI?TYPICAL SYSTEM BUS CONFIGURATIONSTART AND STOP CONDITIONS6Integrated Silicon Solution, Inc. — /doc/af5937a6dd3383c4bb4cd241.html — 1-800-379-4774 Rev.D元器件交易⽹/doc/af5937a6dd3383c4bb4cd241.htmlIS24C01IS24C02IS24C04IS24C08 IS24C16ISSI?DATA VALIDITY PROTOCOL元器件交易⽹/doc/af5937a6dd3383c4bb4cd241.htmlIS24C01IS24C02IS24C04IS24C08 IS24C16ISSI?PAGE WRITE8Integrated Silicon Solution, Inc. — /doc/af5937a6dd3383c4bb4cd241.html — 1-800-379-4774 Rev.D元器件交易⽹/doc/af5937a6dd3383c4bb4cd241.htmlIS24C01IS24C02IS24C04IS24C08 IS24C16ISSI?SEQUENTIAL READ元器件交易⽹/doc/af5937a6dd3383c4bb4cd241.htmlIS24C01IS24C02IS24C04IS24C08 IS24C16ISSI?ABSOLUTE MAXIMUM RATINGS(1)Symbol Parameter Value UnitV S Supply Voltage0.5 to +6.25VV P Voltage on Any Pin–0.5 to Vcc + 0.5VT BIAS Temperature Under Bias–40 to +85°CT STG Storage Temperature–65 to +150°CI OUT Output Current5mANotes:1.Stress greater than those listed under ABSOLUTE MAXIMUM RATINGS may causepermanent damage to the device. This is a stress rating only and functional operation of thedevice at these or any other conditions above those indicated in the operational sections ofthis specification is not implied. Exposure to absolute maximum rating conditions forextended periods may affect reliability.OPERATING RANGE(IS24C01-2, IS24C02-2, IS24C04-2 IS24C08-2, & IS24C16-2)Range Ambient Temperature V CCCommercial0°C to +70°C 1.8V to 5.5VIndustrial–40°C to +85°C 1.8V to 5.5VOPERATING RANGE(IS24C01-3, IS24C02-3, IS24C04-3, IS24C08-3, & IS24C16-3)Range Ambient Temperature V CCCommercial0°C to +70°C 2.5V to 5.5VIndustrial–40°C to +85°C 2.5V to 5.5VAutomotive–40°C to +125°C 2.7V to 5.5VNote: Automotive data is preliminary.OPERATING RANGE(IS24C01-5, IS24C02-5, IS24C04-5 IS24C08-5, & IS24C16-5)Range Ambient Temperature V CCAuromotive–40°C to +125°C 4.5V to 5.5VNote: Automotive data is preliminary.10Integrated Silicon Solution, Inc. — /doc/af5937a6dd3383c4bb4cd241.html — 1-800-379-4774 Rev.D元器件交易⽹/doc/af5937a6dd3383c4bb4cd241.htmlIS24C01IS24C02IS24C04IS24C08 IS24C16ISSI?DC ELECTRICAL CHARACTERISTICSSymbol Parameter Test Conditions Min.Max.UnitV OL1Output LOW Voltage V CC = 1.8V, I OL = 0.15 mA—0.2VV OL2Output LOW Voltage V CC = 2.5V, I OL = 1.0 mA—0.4VV IH Input HIGH Voltage V CC X 0.7V CC + 0.5VV IL Input LOW Voltage–1.0V CC X 0.3VI LI Input Leakage Current V IN = V CC max.—3µAI LO Output Leakage Current—3µANotes: V IL min and V IH max are reference only and are not tested.POWER SUPPLY CHARACTERISTICSSymbol Parameter Test Conditions Min.Max.UnitI CC1Vcc Operating Current READ at 100 KHz (Vcc = 5V)— 1.0mAI CC2Vcc Operating Current WRITE at 100 KHz (Vcc = 5V)— 3.0mAI SB1Standby Current Vcc = 1.8V— 4.0µAI SB2Standby Current Vcc = 5.5V—8.0µACAPACITANCE(1,2)Symbol Parameter Conditions Max.UnitC IN Input Capacitance V IN = 0V6pFC OUT Output Capacitance V OUT = 0V8pFNotes:1.Tested initially and after any design or process changes that may affect these parameters.2.Test conditions: T A = 25°C, f = 1 MHz, Vcc = 5.0V.12Integrated Silicon Solution, Inc. — /doc/af5937a6dd3383c4bb4cd241.html — 1-800-379-4774 Rev.D IS24C01IS24C02IS24C04IS24C08 IS24C16ISSIAC ELECTRICAL CHARACTERISTICS (Over Operating Range)Automotive (T A = –40°C to +125°C) 2.7V-5.5V 4.5V-5.5V Symbol Parameter Test ConditionsMin.Max.Min.Max.Unit f SCL SCL Clock Frequency 01000400KHz T Noise Suppression Time (1)—100—50ns t LOW Clock LOW Period 4.7— 1.2—µs t HIGH Clock HIGH Period4—0.6—µs t BUF Bus Free Time Before New Transmission 4.7— 1.2—µs t SU:STA Start Condition Setup Time 4.7—0.6—µs t SU:STO Stop Condition Setup Time 4.7—0.6—µs t HD:STA Start Condition Hold Time 4—0.6—µs t HD:STO Stop Condition Hold Time 4—0.6—µs t SU:DAT Data In Setup Time 200—100—ns t HD:DAT Data In Hold Time 0—0—ns t DH Data Out Hold Time SCL LOW to SDA Data Out Change 100—50—ns t AA Clock to Output SCL LOW to SDA Data Out Valid0.1 4.50.10.9µs t R SCL and SDA Rise Time(1)—1000—300ns t F SCL and SDA Fall Time (1)—300—300ns t WRWrite Cycle Time—10—10msNote:1. This parameter is characterized but not 100% tested.2. Automotive data is preliminary.AC ELECTRICAL CHARACTERISTICS (Over Operating Rnage)Commercial (T A = 0°C to +70°C) Industrial (T A = –40°C to +85°C) 1.8V-5.5V 2.5V-5.5V Symbol Parameter Test ConditionsMin.Max.Min.Max.Unit f SCL SCL Clock Frequency 01000400KHz T Noise Suppression Time (1)—100—50ns t LOW Clock LOW Period 4.7— 1.2—µs t HIGH Clock HIGH Period4—0.6—µs t BUF Bus Free Time Before New Transmission (1) 4.7— 1.2—µs t SU:STA Start Condition Setup Time 4.7—0.6—µs t SU:STO Stop Condition Setup Time 4.7—0.6—µs t HD:STA Start Condition Hold Time 4—0.6—µs t HD:STO StopCondition Hold Time 4—0.6—µs t SU:DAT Data In Setup Time 200—100—ns t HD:DAT Data In Hold Time 0—0—ns t DH Data Out Hold Time SCL LOW to SDA Data Out Change 100—50—ns t AA Clock to Output SCL LOW to SDA Data Out Valid 0.1 4.50.10.9µs t R SCL and SDA Rise Time (1)—1000—300ns t F SCL and SDA Fall Time (1)—300—300ns t WRWrite Cycle Time—10—5msNote:1. This parameter is characterized but not 100% tested.元器件交易⽹/doc/af5937a6dd3383c4bb4cd241.html元器件交易⽹/doc/af5937a6dd3383c4bb4cd241.htmlIS24C01IS24C02IS24C04IS24C08 IS24C16ISSI?AC WAVEFORMSBUS TIMINGWRITE CYCLE TIMING元器件交易⽹/doc/af5937a6dd3383c4bb4cd241.htmlIS24C01IS24C02IS24C04IS24C08 IS24C16ISSI?ORDERING INFORMATIONCommercial Range: 0°C to +70°CVol tageFrequency Range Part Number Package100 KHz 1.8V IS24C01-2P300-mil Plastic DIPto 5.5V IS24C01-2G Small Outline (JEDEC STD)IS24C01-2S MSOPIS24C01-2Z TSSOP100 KHz 1.8V IS24C02-2P300-mil Plastic DIPto 5.5V IS24C02-2G Small Outline (JEDEC STD)IS24C02-2S MSOPIS24C02-2Z TSSOP100 KHz 1.8V IS24C04-2P300-mil Plastic DIPto 5.5V IS24C04-2G Small Outline (JEDEC STD)IS24C04-2Z TSSOP100 KHz 1.8V IS24C08-2P300-mil Plastic DIPto 5.5V IS24C08-2G Small Outline (JEDEC STD)IS24C08-2Z TSSOP100 KHz 1.8V IS24C16-2P300-mil Plastic DIPto 5.5V IS24C16-2G Small Outline (JEDEC STD)400 KHz 2.5V IS24C01-3P300-mil Plastic DIPto 5.5V IS24C01-3G Small Outline (JEDEC STD)IS24C01-3S MSOPIS24C01-3Z TSSOP400 KHz 2.5V IS24C02-3P300-mil Plastic DIPto 5.5V IS24C02-3G Small Outline (JEDEC STD)IS24C02-3S MSOPIS24C02-3Z TSSOP400 KHz 2.5V IS24C04-3P300-mil Plastic DIPto 5.5V IS24C04-3G Small Outline (JEDEC STD)IS24C04-3Z TSSOP400 KHz 2.5V IS24C08-3P300-mil Plastic DIPto 5.5V IS24C08-3G Small Outline (JEDEC STD)IS24C08-3Z TSSOP400 KHz 2.5V IS24C16-3P300-mil Plastic DIPto 5.5V IS24C16-3G Small Outline (JEDEC STD)14Integrated Silicon Solution, Inc. — /doc/af5937a6dd3383c4bb4cd241.html — 1-800-379-4774 Rev.D元器件交易⽹/doc/af5937a6dd3383c4bb4cd241.htmlIS24C01IS24C02IS24C04IS24C08 IS24C16ISSI?ORDERING INFORMATIONIndustrial Range: –40°C to +85°CVoltageFrequency Range Part Number Package100 KHz 1.8V IS24C01-2PI300-mil Plastic DIPto 5.5V IS24C01-2GI Small Outline (JEDEC STD)IS24C01-2SI MSOPIS24C01-2ZI TSSOP100 KHz 1.8V IS24C02-2PI300-mil Plastic DIPto 5.5V IS24C02-2GI Small Outline (JEDEC STD)IS24C02-2SI MSOPIS24C02-2ZI TSSOP100 KHz 1.8V IS24C04-2PI300-mil Plastic DIPto 5.5V IS24C04-2GI Small Outline (JEDEC STD)IS24C04-2ZI TSSOP100 KHz 1.8V IS24C08-2PI300-mil Plastic DIPto 5.5V IS24C08-2GI Small Outline (JEDEC STD)IS24C08-2ZI TSSOP100 KHz 1.8V IS24C16-2PI300-mil Plastic DIPto 5.5V IS24C16-2GI Small Outline (JEDEC STD)400 KHz 2.5V IS24C01-3PI300-mil Plastic DIPto 5.5V IS24C01-3GI Small Outline (JEDEC STD)IS24C01-3SI MSOPIS24C01-3ZI TSSOP400 KHz 2.5V IS24C02-3PI300-mil Plastic DIPto 5.5V IS24C02-3GI Small Outline (JEDEC STD)IS24C02-3SI MSOPIS24C02-3ZI TSSOP400 KHz 2.5V IS24C04-3PI300-mil Plastic DIPto 5.5V IS24C04-3GI Small Outline (JEDEC STD)IS24C04-3ZI TSSOP400 KHz 2.5V IS24C08-3PI300-mil Plastic DIPto 5.5V IS24C08-3GI Small Outline (JEDEC STD)IS24C08-3ZI TSSOP400 KHz 2.5V IS24C16-3PI300-mil Plastic DIPto 5.5V IS24C16-3GI Small Outline (JEDEC STD)元器件交易⽹/doc/af5937a6dd3383c4bb4cd241.html IS24C01IS24C02IS24C04IS24C08 IS24C16ISSI?ORDERING INFORMATIONAutomotive Range: –40°C to +125°CVoltageFrequency Range Part Number Package100 KHz 2.7V IS24C01-3PA300-mil Plastic DIPto 5.5V IS24C01-3GA Small Outline (JEDEC STD)IS24C01-3SA MSOPIS24C01-3ZA TSSOP100 KHz 2.7V IS24C02-3PA300-mil Plastic DIPto 5.5V IS24C02-3GA Small Outline (JEDEC STD)IS24C02-3SA MSOPIS24C02-3ZA TSSOP100 KHz 2.7V IS24C04-3PA300-mil Plastic DIPto 5.5V IS24C04-3GA Small Outline (JEDEC STD)IS24C04-3ZA TSSOP100 KHz 2.7V IS24C08-3PA300-mil Plastic DIPto 5.5V IS24C08-3GA Small Outline (JEDEC STD)IS24C08-3ZA TSSOP100 KHz 2.7V IS24C16-3PA300-mil Plastic DIPto 5.5V IS24C16-3GA Small Outline (JEDEC STD)400 KHz 4.5V IS24C01-5PA300-mil Plastic DIPto 5.5V IS24C01-5GA Small Outline (JEDEC STD)IS24C01-5SA MSOPIS24C01-5ZA TSSOP400 KHz 4.5V IS24C02-5PA300-mil Plastic DIPto 5.5V IS24C02-5GA Small Outline (JEDEC STD)IS24C02-5SA MSOPIS24C02-5ZA TSSOP400 KHz 4.5V IS24C04-5PA300-mil Plastic DIPto 5.5V IS24C04-5GA Small Outline (JEDEC STD)IS24C04-5ZA TSSOP400 KHz 4.5V IS24C08-5PA300-mil Plastic DIPto 5.5V IS24C08-5GA Small Outline (JEDEC STD)IS24C08-5ZA TSSOP400 KHz 4.5V IS24C16-5PA300-mil Plastic DIPto 5.5V IS24C16-5GA Small Outline (JEDEC STD)Note: Automotive data is preliminary.16Integrated Silicon Solution, Inc. — /doc/af5937a6dd3383c4bb4cd241.html — 1-800-379-4774 Rev.D。

AT24C01资料的中文翻译

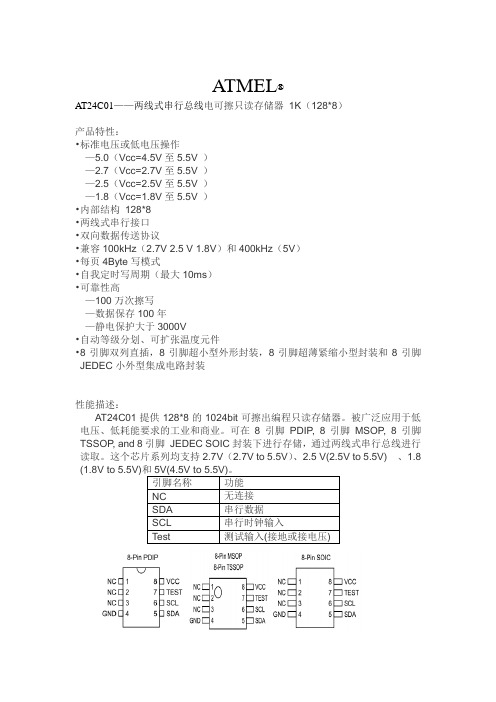

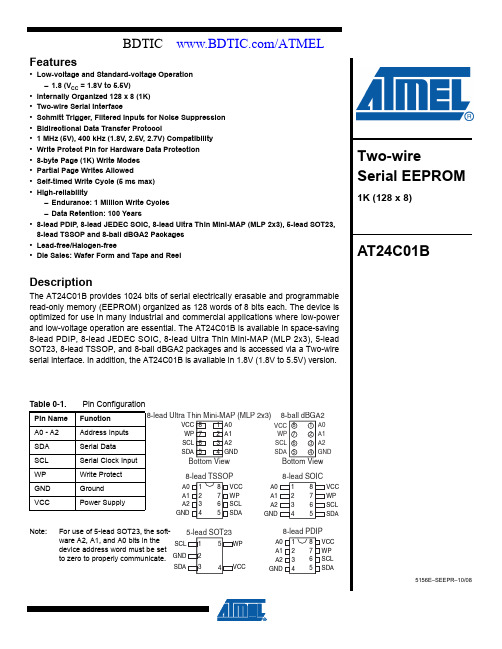

ATMEL®AT24C01——两线式串行总线电可擦只读存储器1K(128*8)产品特性:•标准电压或低电压操作—5.0(Vcc=4.5V至5.5V )—2.7(Vcc=2.7V至5.5V )—2.5(Vcc=2.5V至5.5V )—1.8(Vcc=1.8V至5.5V )•内部结构128*8•两线式串行接口•双向数据传送协议•兼容100kHz(2.7V 2.5 V 1.8V)和400kHz(5V)•每页4Byte写模式•自我定时写周期(最大10ms)•可靠性高—100万次擦写—数据保存100年—静电保护大于3000V•自动等级分划、可扩张温度元件•8引脚双列直插,8引脚超小型外形封装,8引脚超薄紧缩小型封装和8引脚JEDEC小外型集成电路封装性能描述:AT24C01提供128*8的1024bit可擦出编程只读存储器。

被广泛应用于低电压、低耗能要求的工业和商业。

可在8引脚PDIP, 8引脚MSOP, 8引脚TSSOP, and 8引脚JEDEC SOIC封装下进行存储,通过两线式串行总线进行读取。

这个芯片系列均支持2.7V(2.7V to 5.5V)、2.5 V(2.5V to 5.5V) 、1.8 (1.8V to 5.5V)和5V(4.5V to 5.5V)。

引脚名称功能NC 无连接SDA 串行数据SCL 串行时钟输入Test 测试输入(接地或接电压)绝对最大功率:运行温度…………-55°至+125°存储温度…………-65°至+150°引脚承受最高电压…………-1V至+7V运行最大电压…………6.25V直流最大电流…………5.0mA*注意:超过上述参数工作会损坏本元件,这是唯一的功能操作参数,超过此功率将不被支持。

按照额定功率工作将使元件更加可靠。

模块图引脚描述:SERIAL CLOCK (SCL):SCL引脚在电压上升沿时输入数据,下降沿时输出数据SERIAL DATA (SDA):SDA引脚用作双向传送数据,高电平驱动可能与其它任何引脚或元件进行线或运算。

芯片24C01C的说明文档

•Single supply with operation from 4.5 to 5.5V •Low power CMOS technology - 1 mA active current typical-10 µ A standby current typical at 5.5V•Organized as a single block of 128 bytes (128 x 8)•2-wire serial interface bus, I 2 C compatible •100kHz and 400 kHz compatibility •Page-write buffer for up to 16 bytes•Self-timed write cycle (including auto-erase)•Fast 1 mS write cycle time for byte or page mode •Address lines allow up to eight devices on bus •1,000,000 erase/write cycles guaranteed •ESD protection > 4,000V •Data retention > 200 years•8-pin PDIP , SOIC or TSSOP packages •Available for extended temperature ranges DESCRIPTIONThe Microchip T echnology Inc. 24C01C is a 1K bit Serial Electrically Erasable PROM with a voltage range of 4.5V to 5.5V . The device is organized as a single block of 128 x 8-bit memory with a 2-wire serial inter-face. Low current design permits operation with typical standby and active currents of only 10 µ A and 1 mA respectively. The device has a page-write capability for up to 16 bytes of data and has fast write cycle times of only 1 mS for both byte and page writes. Functional address lines allow the connection of up to eight 24C01C devices on the same bus for up to 8K bits of contiguous EEPROM memory. The device is available in the standard 8-pin PDIP , 8-pin SOIC (150 mil), and TSSOP packages.-Commercial (C):0 ° C to +70 ° C -Industrial (I): -40 ° C to +85 ° C -Automotive (E) -40 ° C to +125 °C224C01C1.0ELECTRICALCHARACTERISTICS1.1Maximum Ratings*V CC ........................................................................7.0V All inputs and outputs w.r.t. V SS ......-0.6V to V CC +1.0V Storage temperature...........................-65˚C to +150˚C Ambient temp. with power applied.......-65˚C to +125˚C Soldering temperature of leads (10 seconds)...+300˚C ESD protection on all pins ......................................≥ 4 kV*Notice:Stresses above those listed under “Maximum ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended peri-ods may affect device reliability.TABLE 1-1:PIN FUNCTION TABLEName Function V SS SDA SCL VCC A0, A1, A2T estGround Serial Data Serial Clock+4.5V to 5.5V Power Supply Chip SelectsT est Pin: may be tied high, low or left floatingTABLE 1-2:DC CHARACTERISTICSAll parameters apply across the speci-fied operating ranges unless otherwise noted.VCC = +4.5V to +5.5V Commercial (C):T amb = 0 ° C to +70 ° C Industrial (I):Tamb = -40 ° C to +85 ° C Automotive (E):T amb = -40 ° C to +125 ° C ParameterSymbol Min.Max.Units ConditionsSCL and SDA pins:High level input voltageV IH 0.7 V CCV Low level input voltageV IL .3 V CC V Hysteresis of Schmitt trigger inputs V HYS 0.05 V CC —V (Note)Low level output voltage V OL .40V I OL = 3.0 mA, V CC = 4.5V Input leakage current ILI -1010 µ A V IN = 0.1V to 5.5V , WP = Vss Output leakage currentILO -1010 µ A V OUT = 0.1V to 5.5V Pin capacitance (all inputs/outputs)C IN , C OUT —10pF VCC = 5.0V (Note)T amb = 25 ° C, f = 1 MHz Operating current I CC Read —1mA V CC = 5.5V , SCL = 400 kHz I CC Write —3mA V CC = 5.5VStandby currentICCS—50µ AV CC = 5.5V , SDA = SCL = VCCNote: This parameter is periodically sampled and not 100% tested.24C01CTABLE 1-3:AC CHARACTERISTICSAll parameters apply across the specified oper-ating ranges unless otherwise noted.Vcc = 4.5V to 5.5V Commercial (C):T amb = 0 ° C to +70 ° C Industrial (I):T amb = -40 ° C to +85 ° C Automotive (E):Tamb = -40 ° C to +125 ° C ParameterSymbol Tamb > +85 ° C -40 ° C ≤ Tamb ≤+85 ° CUnits RemarksMin.Max.Min.Max. Clock frequency F CLK —100—400kHz Clock high time T HIGH 4000—600—ns Clock low timeT LOW 4700—1300—ns SDA and SCL rise time T R —1000—300ns (Note 1)SDA and SCL fall time T F —300—300ns (Note 1)ST ART condition hold time T HD : STA 4000—600—ns After this period the first clock pulse is generated START condition setup time T SU : STA 4700—600—ns Only relevant for repeated ST ART condition Data input hold time T HD : DAT 0—0—ns (Note 2)Data input setup timeT SU : DAT 250—100—ns STOP condition setup time T SU : STO 4000—600—ns Output valid from clock T AA —3500—900ns (Note 2)Bus free timeT BUF4700—1300—nsTime the bus must be free before a new transmission can startOutput fall time from V IH minimum to V IL maximum T OF —25020 +0.1 C B250ns (Note 1), C B ≤ 100 pF Input filter spike suppression (SDA and SCL pins)T SP —50—50ns(Note 3)Write cycle time TWR— 1.5—1ms Byte or Page modeEndurance1M—1M—cycles 25 ° C, V CC = 5.0V , BlockMode (Note 4)Note 1: Not 100% tested. CB = total capacitance of one bus line in pF .2:As a transmitter, the device must provide an internal minimum delay time to bridge the undefined region (minimum 300 ns) of the falling edge of SCL to avoid unintended generation of ST ART or STOP conditions.3:The combined T SP and V HYS specifications are due to Schmitt trigger inputs which provide improved noise spike suppression. This eliminates the need for a TI specification for standard operation.4:This parameter is not tested but guaranteed by characterization. For endurance estimates in a specific appli-cation, please consult the T otal Endurance Model which can be obtained on our BBS or website.24C01C2.0PIN DESCRIPTIONS2.1SDA Serial DataThis is a bi-directional pin used to transfer addresses and data into and data out of the device. It is an open drain terminal, therefore the SDA bus requires a pull-up resistor to V CC (typical 10 k Ω for 100 kHz, 2 k Ω for 400 kHz).For normal data transfer SDA is allowed to change only during SCL low. Changes during SCL high are reserved for indicating the ST ART and STOP conditions.2.2SCL Serial ClockThis input is used to synchronize the data transfer from and to the device.2.3A0, A1, A2The levels on these inputs are compared with the cor-responding bits in the slave address. The chip is selected if the compare is true.Up to eight 24C01C devices may be connected to the same bus by using different chip select bit combina-tions. These inputs must be connected to either V CC or V SS .2.4TestThis pin is utilized for testing purposes only. It may be tied high, tied low or left floating.2.5Noise ProtectionThe 24C01C employs a V CC threshold detector circuit which disables the internal erase/write logic if the V CC is below 3.8 volts at nominal conditions.The SCL and SDA inputs have Schmitt trigger and filter circuits which suppress noise spikes to assure proper device operation even on a noisy bus.3.0FUNCTIONAL DESCRIPTIONThe 24C01C supports a bi-directional 2-wire bus and data transmission protocol. A device that sends data onto the bus is defined as transmitter, and a device receiving data as receiver. The bus has to be controlled by a master device which generates the serial clock (SCL), controls the bus access, and generates the ST ART and STOP conditions, while the 24C01C works as slave. Both master and slave can operate as trans-mitter or receiver but the master device determines which mode is activated.24C01C4.0BUS CHARACTERISTICSThe following bus protocol has been defined:•Data transfer may be initiated only when the bus is not busy.•During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is HIGH will be interpreted as a ST ART or STOP condition.Accordingly, the following bus conditions have been defined (Figure 4-1).4.1Bus not Busy (A)Both data and clock lines remain HIGH.4.2Start Data Transfer (B)A HIGH to LOW transition of the SDA line while the clock (SCL) is HIGH determines a START condition. All commands must be preceded by a ST ART condition.4.3Stop Data Transfer (C)A LOW to HIGH transition of the SDA line while the clock (SCL) is HIGH determines a STOP condition. All operations must be ended with a STOP condition.4.4Data Valid (D)The state of the data line represents valid data when,after a ST ART condition, the data line is stable for the duration of the HIGH period of the clock signal.The data on the line must be changed during the LOW period of the clock signal. There is one bit of data per clock pulse.Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of the data bytes transferred between the ST ART and STOP conditions is determined by the master device and is theoretically unlimited, although only the last six-teen will be stored when doing a write operation. When an overwrite does occur it will replace data in a first in first out fashion.4.5AcknowledgeEach receiving device, when addressed, is required to generate an acknowledge after the reception of each byte. The master device must generate an extra clock pulse which is associated with this acknowledge bit.The device that acknowledges has to pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse. Of course, setup and hold times must be taken into account. A master must signal an end of data to the slave by not generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case,the slave must leave the data line HIGH to enable the master to generate the STOP condition (Figure 4-2).24C01C5.0DEVICE ADDRESSINGA control byte is the first byte received following the start condition from the master device (Figure 5-1). The control byte consists of a four bit control code; for the 24C01C this is set as 1010 binary for read and write operations. The next three bits of the control byte are the chip select bits (A2, A1, A0). The chip select bits allow the use of up to eight 24C01C devices on the same bus and are used to select which device is accessed. The chip select bits in the control byte must correspond to the logic levels on the corresponding A2,A1, and A0 pins for the device to respond. These bits are in effect the three most significant bits of the word address.The last bit of the control byte defines the operation to be performed. When set to a one a read operation is selected, and when set to a zero a write operation is selected. Following the start condition, the 24C01C monitors the SDA bus checking the control byte being transmitted. Upon receiving a 1010 code and appropri-ate chip select bits, the slave device outputs an acknowledge signal on the SDA line. Depending on the state of the R/W bit, the 24C01C will select a read or write operation.5.1Contiguous Addressing Across Multiple DevicesThe chip select bits A2, A1, A0 can be used to expand the contiguous address space for up to 8K bits by add-ing up to eight 24C01C devices on the same bus. In this case, software can use A0 of the control byte as address bit A8, A1 as address bit A9, and A2 as address bit A10. It is not possible to write or read across device boundaries.24C01C6.0WRITE OPERATIONS6.1Byte WriteFollowing the start signal from the master, the device code(4 bits), the chip select bits (3 bits), and the R/W bit which is a logic low is placed onto the bus by the master transmitter. The device will acknowledge this control byte during the ninth clock pulse. The next byte transmitted by the master is the word address and will be written into the address pointer of the 24C01C. After receiving another acknowledge signal from the 24C01C the master device will transmit the data word to be written into the addressed memory location. The 24C01C acknowledges again and the master gener-ates a stop condition. This initiates the internal write cycle, and during this time the 24C01C will not generate acknowledge signals (Figure 6-1).6.2Page WriteThe write control byte, word address and the first data byte are transmitted to the 24C01C in the same way as in a byte write. But instead of generating a stop condi-tion, the master transmits up to 15 additional data bytes to the 24C01C which are temporarily stored in the on-chip page buffer and will be written into the memory after the master has transmitted a stop condition. After the receipt of each word, the four lower order address pointer bits are internally incremented by one. The higher order four bits of the word address remains con-stant. If the master should transmit more than 16 bytes prior to generating the stop condition, the address counter will roll over and the previously received data will be overwritten. As with the byte write operation,once the stop condition is received an internal write cycle will begin (Figure 6-2).24C01C7.0ACKNOWLEDGE POLLINGSince the device will not acknowledge during a write cycle, this can be used to determine when the cycle is complete (this feature can be used to maximize bus throughput). Once the stop condition for a write com-mand has been issued from the master, the device ini-tiates the internally timed write cycle. ACK polling can be initiated immediately. This involves the master send-ing a start condition followed by the control byte for a write command (R/W = 0). If the device is still busy with the write cycle, then no ACK will be returned. If no ACK is returned, then the start bit and control byte must be re-sent. If the cycle is complete, then the device will return the ACK and the master can then proceed with the next read or write command. See Figure 7-1 for flow diagram.FIGURE 7-1:ACKNOWLEDGE POLLING24C01C8.0READ OPERATIONSRead operations are initiated in the same way as write operations with the exception that the R/W bit of the slave address is set to one. There are three basic types of read operations: current address read, random read,and sequential read.8.1Current Address ReadThe 24C01C contains an address counter that main-tains the address of the last word accessed, internally incremented by one. Therefore, if the previous read access was to address n, the next current address read operation would access data from address n + 1. Upon receipt of the slave address with the R/W bit set to one,the 24C01C issues an acknowledge and transmits the eight bit data word. The master will not acknowledge the transfer but does generate a stop condition and the 24C01C discontinues transmission (Figure 8-1).8.2Random ReadRandom read operations allow the master to access any memory location in a random manner. To perform this type of read operation, first the word address must be set. This is done by sending the word address to the 24C01C as part of a write operation. After the wordaddress is sent, the master generates a start condition following the acknowledge. This terminates the write operation, but not before the internal address pointer is set. Then the master issues the control byte again but with the R/W bit set to a one. The 24C01C will then issue an acknowledge and transmits the eight bit data word. The master will not acknowledge the transfer but does generate a stop condition and the 24C01C dis-continues transmission (Figure 8-2). After this com-mand, the internal address counter will point to the address location following the one that was just read.8.3Sequential ReadSequential reads are initiated in the same way as a ran-dom read except that after the 24C01C transmits the first data byte, the master issues an acknowledge as opposed to a stop condition in a random read. This directs the 24C01C to transmit the next sequentially addressed 8-bit word (Figure 8-3).To provide sequential reads the 24C01C contains an internal address pointer which is incremented by one at the completion of each operation. This address pointer allows the entire memory contents to be serially read during one operation. The internal address pointer will automatically roll over from address 7F to address 00.24C01CNOTES:24C01C24C01C PRODUCT IDENTIFICATION SYSTEMT o order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.Sales and SupportData SheetsProducts supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recom-mended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:1.Y our local Microchip sales office.2.The Microchip Corporate Literature Center U.S. FAX: (602) 786-7277.3.The Microchip’s Bulletin Board, via your local CompuServe number (CompuServe membership NOT required).。

24C02B中文资料