EPM240开发板简介(送USB Blaster下载线)

ALTERA USB下载线接口说明

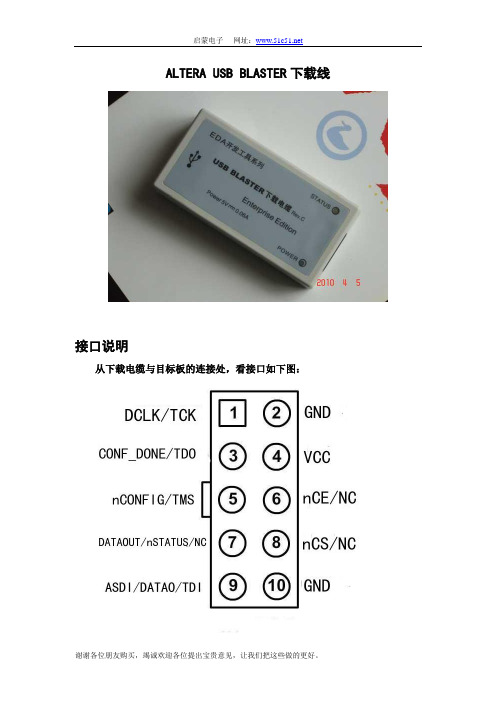

ALTERA USB BLASTER下载线接口说明从下载电缆与目标板的连接处,看接口如下图:或者从FC-10P接头处判断管脚的排序或者每个脚位的功能。

本图中,左上脚的那个FC-10P插件中,看到个三角符号,对应的就是1脚,按照1、3、5、7、9奇数和2、4、6、8、10偶数排列。

本图中也可以看到个三角符号,同样,对应的就是1脚,按照1、3、5、7、9奇数和2、4、6、8、10偶数排列。

ALTERA USB BLASTER下载线常见的接口顺序和形式如下:ALTERA USB BLASTER下载电缆管脚分配如下:产品简介:USB Blaster提供对Altera CPLD和FPGA器件下载支持。

USB Blaster提供对如下器件的数据下载支持:增强型配置器件(Advanced configuration device),包括EPC2,EPC4,EPC8,EPC16,EPC1441;串行配置器件(Serial configuration device),包括EPCS1,EPCS4,EPC16,EPCS64。

USB Blaster支持如下下载方式:JTAG方式:支持所有Altera器件,FLEX6000和EPCS系列器件除外。

PS方式(Passive Serial Programming):支持所有Altera器件,MAX3000,MAX7000,MAXII,EPC和EPCS系统列器件除外。

AS方式(Active Serial Programming):适用于EPCS1,EPCS4,EPC16,EPCS64,EPCS128等串行配置器件。

功能描述:USB Blaster提供对Altera CPLD和FPGA器件下载支持,USB Blaster提供对如下器件的数据下载支持:Ø增强型配置器件(Advanced configuration device),包括EPC2,EPC4,EPC8,EPC16,EPC1441;Ø串行配置器件(Serial configuration device),包括EPCS1,EPCS4,EPC16,EPCS64。

最小系统板 EPM240

EPM240T100\EPM570T100 最小系统板CPLD240\CPLD570核心板开发板

淘宝:美廉科技

EPM240T100C5N核心板、最小系统板

板子规格:

67mm*47mm

特点:

1、板载EPM240T100C5N(默认)

2、IO口全部引出

3、供电部分采用AMS1117-3.3V,输入输出均采用钽电容滤波,可用3种方式供电(其

中前两种可以用自锁按键控制):

1>电脑的USB供电(5V)

2>常见的DC座(内正外负)供电(5V)

3>用杜邦线将直流5V引入板上的双排针

4、标准10pin JTAG座,可用USB-BLASTER下载

5、可提供原理图(pdf格式)及排针位置图(PCB格式)

6、双有源晶振设计,方便用户开发(默认焊接一个)

7、轻触按键一个

8、板载四个贴片发光二极管,两个与BANK1引脚连接,两个与BANK2连接。

适用范围:电子设计比赛、毕业设计、产品验证、开发过程中的实验等。

USB-Blaster的制作资料

一、综述

USB-Blaster的制作资料早已经公开了,浏览了网上众多资料之后本人也制作了一款,非常小巧!如下图所示。

二、系统方案

主要芯片:缓冲SN74LVC244、CPLD器件EPM3064、USB芯片FT245RL

器件选择考虑:LVC244比HC244具有更大的优势,是可过压器件。

在TI的文档中可以看到相关介绍;EPM3064:资源正好够用,避免浪费,封装也小;FT245RL:减少了外围的配置芯片。

下面将按模块一一细述:

B模块

原理图如下:

本系统中采用了FT245RL。

关于Blaster的USB有两种方案,一种是FT245BM,是西面的封装,需要时钟和一个存储芯片,一般采用93C46;另一种就是FT245RL,他把时钟和EEPROM都集成到了内部,更加省空间。

该芯片的驱动程序已经被集成在了QuartusII软件中了,可以直接安装,非常方便。

另外这个芯片中也要烧录一定的数据,这个采用厂家提供的工具MProg3.0即可,数据包如下:

2.电源模块

本模块通过USB供电。

3.CPLD模块

本模块的CPLD选用了EPM3064,很多模块用的都是EPM240,但是资源有些浪费,而且封装也大。

软件的烧录数据如下附件:

4.电平转换模块

本模块的电平转换芯片采用了TI的SN74LVC244A,这款芯片是原装的Blaster使

用的片子,所以其他的也就不用细说了!具体的资料大家可以查看他的datasheet。

EPM240T100C5(C代表商业级I代表工业级 型号分为3号和5号)

艾米电子EPM240T100C5 CPLD开发板用户手册v1.0 6.7,2010淘宝:QQ(邮箱):amy-studio@序:艾米电子工作室成立于2009年。

经过1年多的运作,网站和论坛初具规模,得益于广大网友的支持与帮助,这里对支持艾米电子的热心网友表示感谢!艾米电子FPGA系列开发板自面市以来,一直得到广大网友的喜爱。

EP2C8Q208-FPGA/NIOS开发板09年热销1000多套,其中有几所高校定购了几十套作为实验室使用。

2010年艾米电子将延续09年的良好业绩,更好的发展,为客户提供更完善的开发板、开发模块以及资料。

2010年计划推出和完善如下产品:EPM240T100C5入门型CPLD开发板EP2C5T144-FPGA初级FPGA开发板EP2C8Q208-FPGA/NIOS高级FPGA开发板同时完善接口板以及外围接口模块,届时将会推出各种处理器的空板PCB。

敬请各位网友关注!艾米电子EPM240-CPLD开发板用户手册网站:目录序: (2)一、简介 (1)二、核心板照片及资源描述 (3)2.1EPM240T100C5芯片资源描述 (3)2.2照片及引脚分配 (4)2.3功能描述 (6)2.4硬件电路详解 (8)1.EPM240FPGA四个bank (8)3.板载led及I2C存储器接口 (8)6.时钟及复位部分电路 (9)7.电源部分电路 (9)四、注意事项 (15)4.1电源 (15)4.2JTAG拔插方法 (15)4.3软件说明 (15)4.4管脚复用 (16)五、测试开发板 (17)5.1JTAG测试 (17)5.2ASP测试 (17)一、简介EPM240-FPGA开发板(以下简称EPM240开发板)采用Altera公司推出的CYCLONE II系列芯片EPM240Q240C8芯片作为核心处理器进行设计,CYCLONE II系列芯片可以说是目前市场上性价比最高的芯片,比第一代的EP1C6或者EP1C12等芯片设计上、内部的艾米电子EPM240-CPLD开发板用户手册QQ(邮箱):amystudio@逻辑资源上都有很大的改进,同时价格也可以被广大客户接受;虽然Altera推出了CYCLONE III甚至于IV代的芯片,但是目前市场上价格走势偏高,尤其是针对广大初学者的定位,目前还不是适合采用。

EMP240开发板使用指南

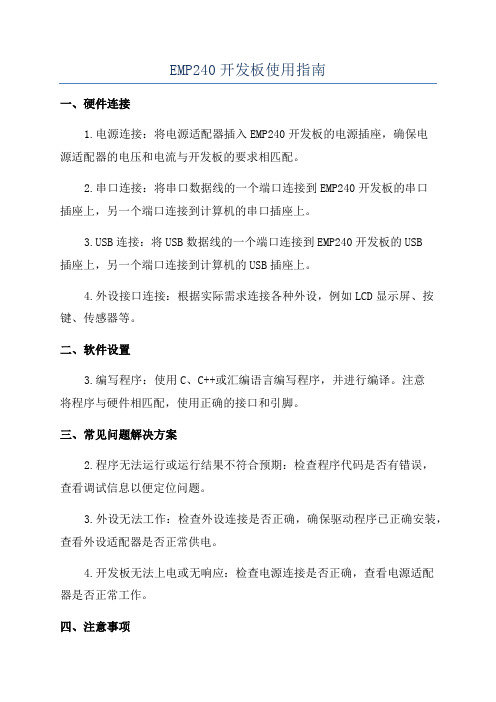

EMP240开发板使用指南一、硬件连接1.电源连接:将电源适配器插入EMP240开发板的电源插座,确保电源适配器的电压和电流与开发板的要求相匹配。

2.串口连接:将串口数据线的一个端口连接到EMP240开发板的串口插座上,另一个端口连接到计算机的串口插座上。

B连接:将USB数据线的一个端口连接到EMP240开发板的USB插座上,另一个端口连接到计算机的USB插座上。

4.外设接口连接:根据实际需求连接各种外设,例如LCD显示屏、按键、传感器等。

二、软件设置3.编写程序:使用C、C++或汇编语言编写程序,并进行编译。

注意将程序与硬件相匹配,使用正确的接口和引脚。

三、常见问题解决方案2.程序无法运行或运行结果不符合预期:检查程序代码是否有错误,查看调试信息以便定位问题。

3.外设无法工作:检查外设连接是否正确,确保驱动程序已正确安装,查看外设适配器是否正常供电。

4.开发板无法上电或无响应:检查电源连接是否正确,查看电源适配器是否正常工作。

四、注意事项1.在使用EMP240开发板时,遵循相应的安全操作规程,确保人身安全和设备安全。

2.仔细阅读开发板的技术文档和用户手册,了解开发板的硬件规格和软件功能。

3.在进行任何硬件连接或操作之前,先断开电源,以免发生电击或损坏设备。

总结:EMP240开发板是一种功能强大且易于使用的嵌入式开发板,通过正确的硬件连接和软件设置,可以实现各种嵌入式应用的开发和调试。

在使用开发板时,应注意安全操作和阅读相关文档,遇到问题时可参考常见问题解决方案进行排除。

祝您在使用EMP240开发板时取得成功!。

FPGA可编程逻辑器件芯片EPM240T100C5N中文规格书

Stratix II GX Architecture Drivers from internal logic GCLKDRV0v v GCLKDRV1v v GCLKDRV2v v GCLKDRV3v v RCLKDRV0v v RCLKDRV1v vRCLKDRV2v vRCLKDRV3vv RCLKDRV4vv RCLKDRV5vv RCLKDRV6vv RCLKDRV7vv PLL 1 outputs c0vv v v v v c1v vv v v v c2vv v v v v c3vv v v v v PLL 2 outputs c0vv v v v v c1v vv v v v c2vv v v v v c3vv v v v v PLL 7 outputs c0vv v v c1vv v v c2vv v v c3v v v v Table 2–27.Global and Regional Clock Connections from Left Side Clock Pins and Fast PLL Outputs (Part 2 of 3)Left Side Global and Regional Clock Network Connectivity C L K 0C L K 1C L K 2C L K 3R C L K 0R C L K 1R C L K 2R C L K 3R C L K 4R C L K 5R C L K 6R C L K 7TriMatrix MemoryTriMatrix memory provides three different memory sizes for efficientapplication support. The Quartus II software automatically partitions theuser-defined memory into the embedded memory blocks using the mostefficient size combinations. You can also manually assign the memory toa specific block size or a mixture of block sizes.M512 RAM BlockThe M512 RAM block is a simple dual-port memory block and is usefulfor implementing small FIFO buffers, DSP , and clock domain transferapplications. Each block contains 576 RAM bits (including parity bits).M512 RAM blocks can be configured in the following modes:■Simple dual-port RAM ■Single-port RAM ■FIFO ■ROM ■Shift registerWhen configured as RAM or ROM, you can use an initialization file topre-load the memory contents.Simple dual-port memorymixed width supportv v v T rue dual-port memorymixed width supportv v Power-up conditionsOutputs cleared Outputs cleared Outputs unknown Register clearsOutput registers Output registers Output registers Mixed-port read-during-writeUnknown output/old data Unknown output/old dataUnknown output Configurations 512 × 1256 × 2128 × 464 × 864 × 932 × 1632 × 184K × 12K × 21K × 4512 × 8512 × 9256 × 16256 × 18128 × 32128 × 3664K × 864K × 932K × 1632K × 1816K × 3216K × 368K × 648K × 724K × 1284K × 144Note to Table 2–19:(1)Violating the setup or hold time on the memory block address registers could corrupt memory contents. Thisapplies to both read and write operations.Table 2–19.TriMatrix Memory Features (Part 2 of 2)Memory FeatureM512 RAM Block (32×18 Bits)M4K RAM Block (128×36 Bits)M-RAM Block (4K ×144Bits)Digital Signal Processing (DSP) BlockFigure2–58.DSP Block Diagram for 18 × 18-Bit Configuration。

EPM240T100I5N中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

256-Pin FineLine

BGA

324-Pin FineLine

BGA

0.5

0.5

1

1

49

121

289

361

7×7

11 × 11 17 × 17 19 × 19

芯片中文手册,看全文,戳

MAX II器件具有内部线性稳压器,它支持3.3 V或2.5 V外接电源电压,调节 供给下降到1.8 V MAX IIG和MAX IIZ器件内部工作电压只接受1.8 V外部电源. MAX IIZ器件引脚兼容100针微型FineLine BGA和256引脚微型FineLine BGA封装 MAX IIG设备.除外部电源电压要求,MAX II和MAX II G设备具有相同引脚 输出和时序规范.

f

有关等效宏单元详细信息,请参阅

宏单元转换方法

白皮书.

MAX II逻辑元素

MAX II和MAX IIG器件有三种速度等级:-3,-4,-5,与

-3是最快.同样,MAX IIZ器件有三种速度等级可供选择:-6,

-7,和-8,以-6是最快.这些速度等级代表总体相对

性能,而不是任何特定时序参数.对于传播延迟定时

由MAX II系列支持.

表1-5 显示外部电源电压

表 1-5. MAX II外接电源电压

设备

多电压内核外部电源电压(V 多电压I / O接口电压电平(V 须知 表 1-5: (1)MAX IIG和MAX IIZ器件只接受1.8 V他们 (2)MAX II器件在1.8 V内部操作

) (2) )

EPM 240 EPM 570 EPM 1270 EPM 2210

3.3 V / 2.5 V或1.8 V ■ 多电压I / O接口,支持3.3 V,2.5 V,1.8 V和1.5 V逻辑电平 ■ 总线型架构,包括可编程摆率,驱动能力,

USB_Blaster安装和使用

6安装USB下载线驱动安装软件以后,我们还需要安装USB BLASTER(下载线)的驱动。

USB BLASTER 的驱动是有Quartus II软件提供的在安装过程中,大家要注意点,就是驱动的路径是:X:\altera\11.1\quartus\drivers\usb-blaster千万不要进入X32或x64文件路径下。

如果您是WIN7系统用户,如果出现不能安装的情况,请将防火墙,杀毒软件都关掉,然后重新安装。

在这里,我简单说明一下USB下载线的使用方法。

支持两种下载方式,一种是JTAG方式,一种是AS方式。

对应的在核心板上有两个10针的接口,上面有标识AS口和JTAG口。

USB下载线一端与电脑的USB口相连接,另一端与JTAG口或者AS口相连。

在同一时刻,我们只能使用其中一个接口。

其中JTAG方式负责FPGA在线仿真,程序通过USB下载线下载到FPGA内部SRAM 中。

由于FPGA是基于SRAM技术的,所以掉电以后,程序会丢失;AS方式是将程序下载到FPGA外部的配置芯片EPCSX中的,EPCSX实质是一种串行FLASH,因此,掉线以后,程序不会丢失。

每次上电,EPCSX中的程序都会自动加载到FPGA 中,然后再开始运行。

USB BLASTER本身就有仿真和下载两种功能,因此,FPGA开发过程中只需要USB BLASTER既可以实现在线仿真和程序固化两个功能。

其中JTAG方式主要用于在线仿真,而AS方式用于最终的程序固化到外部的配置芯片EPCSX中。

程序下载测试上述过程都完成以后,接下来,我们就要试试是否可以进行下载程序了,您也一定期待已久了吧,那现在我们就开始吧。

在光盘中,我们为大家准备了已经编译好的固件测试程序,在文件夹测试固件下。

下面我将为大家演示如何进行下载测试。

在这里要首先要说一下,拿到光盘以后,建议大家先将光盘内容拷贝到硬盘中,还有一点要注意的,就是不要放到含有中文和空格的路径下。

TD-DS-MAXII实验指导书(EPM240)

数字系统设计实验教程西安唐都科教仪器公司Copyright Reserved 2005- 数字系统设计实验教程西安唐都科教仪器公司版权声明本实验教程的版权归西安唐都科教仪器开发有限责任公司所有,保留一切权利。

未经本公司书面许可,任何单位和个人不得擅自摘抄、复制本实验教程的部分或全部内容,并以任何形式传播。

西安唐都科教仪器开发有限责任公司,2005(C),All right reserved.数字系统设计实验教程©版权所有非经许可严禁复制技术支持邮箱:service@唐都公司网址:- 数字系统设计实验教程西安唐都科教仪器公司目录第一章 TD-DS-MAXII系统简介 (1)1.1 TD-DS-MAXII系统构成 (1)1.2TD-DS-MAXII系统使用方法 (1)第二章 Quartus II开发软件简介 (3)2.1Quartus II软件的安装 (4)2.2 ByteBlasterII下载电缆驱动程序的安装 (10)2.2.1 Windows2000操作系统中安装驱动的步骤 (10)2.2.2 WindowsXP操作系统中安装驱动的步骤 (13)2.2.3 Quartus II软件中设置下载电缆 (16)第三章 数字系统设计实验 (18)3.1 基本门电路实验 (18)3.2 编码器实验 (26)3.3 译码器实验 (29)3.4 加法器实验 (31)3.5 乘法器实验 (35)3.6 寄存器实验 (38)3.7 计数器实验 (42)3.8 分频器实验 (45)3.9 流水灯实验 (52)3.10 扫描数码显示器实验 (56)3.11 数字钟实验 (63)第一章 TD-DS-MAXII系统简介随着大规模可编程器件的快速发展,基于EDA技术的CPLD/FPGA可编程器件的设计正在成为电子系统设计的主流。

纵观近年来各高校毕业设计及大学生电子设计竞赛,不难发现越来越多的题目需要采用EDA技术,借助可编程器件CPLD/FPGA来实现电子系统的设计。

EPM240G中文资料

MAX II and MAX IIG devices are available in three speed grades: –3, –4, and –5, with –3 being the fastest. Similarly, MAX IIZ devices are available in two speed grades: –6, –7, with –6 being faster. These speed grades represent the overall relative performance, not any specific timing parameter. For propagation delay timing numbers within each speed grade and density, refer to the DC and Switching Characteristics chapter in the MAX II Device Handbook.

© October 2008 Altera Corporation

MAX II Device Handbook

元器件交易网

I–2

Section I: MAX II Device Family Data Sheet Revision History

MAX II Device Handbook

Features

The MAX II CPLD has the following features: ■ Low-cost, low-power CPLD ■ Instant-on, non-volatile architecture ■ Standby current as low as 29 µA ■ Provides fast propagation delay and clock-to-output times ■ Provides four global clocks with two clocks available per logic array block (LAB) ■ UFM block up to 8 Kbits for non-volatile storage ■ MultiVolt core enabling external supply voltages to the device of either 3.3 V/2.5 V

BJ-EPM实验板介绍

BJ-EPM240CPLD开发板介绍BJ-EPM240学习板是特权同学和知名电子技术网站合作推出的一款FPGA/CPLD入门级学习板,该学习板在EDN助学活动期间以低廉的价格提供给所有注册会员,并且赠送免费的PCB板。

学习板以齐全的资料、良好的代码风格博得了广大网友的一致认可,很适合初学者入门学习。

该板子的一切相关问题都可以在EDN网站的CPLD/FPGA助学小组(网址:/1375/)里进行讨论。

该开发板配套北航出版社2010年6月出版的《深入浅出玩转FPGA》进行深入学习,并且特权同学录制了同名的《深入浅出玩转FPGA》视频教程配套。

1.BJ-EPM240学习板功能框图图1和图2是整板系统的功能框图,从图中可以清楚地看到EPM240T100学习板上丰富的外设资源及其位置分布情况。

图1 BJ-EPM学习板顶层资源分布及功能框图图2 BJ-EPM学习板底层资源分布及功能框图2.BJ-EPM240学习板基本配置●主芯片使用的是 Altera公司的MAX II系列EPM240T100C5,该芯片有240个逻辑单元,等效宏单元192个,资源比较丰富,内有8Kbit Flash的存储空间。

●50MHz有源晶振,作为系统主时钟。

●低电平复位按键,使用EPM240的全局复位管脚。

●8色VGA接口1个,让大家掌握电脑显示器的驱动原理。

●RS232串口1个,通过串口调试助手轻松实现UART通信协议。

●PS/2 接口1个,实现键盘解码,配合串口调试助手在PC机上显示键值。

●70ns快速读写的SRAM芯片IS62LV256-70U,具有32KB存储空间,让大家熟悉SRAM的读写操作。

●EEPROM 芯片AT24C02,让大家熟悉使用verilog进行I2C通信。

●4个独立按键,进行verilog脉冲采样和按键消抖控制。

●4个流水灯,配合4位按键进行Johnson计数器实验。

●蜂鸣器,实现简单的分频计数器。

●2位数码管,使用其进行计数实验。

如何使用USB_Blaster下载POF文件

USB_Blaster使用说明一、硬件连接1、将USB电缆取出,扁的一端接口插入电脑的USB插口,另外一端接入USB Blaster(金黄色方形盒子);2、彩虹色排线连接到电路板的Altera Config接口;3、硬件连接完毕,以上操作请在电路板断电的情况下进行。

二、Altera Programmer的下载和安装1、下载Altera Programmer打开网页https:///download/software/prog-software/11.0sp1,然后下载11.0sp1_programmer_windows.exe ,如下图所示:2、安装Altera Programmer双击11.0sp1_programmer_windows.exe开始安装,之后一路点击“next”直到软件安装完成。

注意:在以下界面时选择“I agree”前面的小方框。

三、下载POF文件1、打开刚刚安装好的programmer,并在打开的界面中寻找硬件,点击左上角的Hardware Setup,如下图:之后会出现以下界面:选中Hardware Settings选项卡,双击上图中的蓝色区域,即USB-Blaster,Current Selected Hardware会从“No Hardware”变成“USB-Blaster”,如下图:点击右下角的“Close”,回到Programmer界面。

2、选择需要下载的POF文件。

首先点击Programmer界面左侧的“Add File”,并选中要下载的POF文件,点后面的“OPEN”,如下图所示:此时的Programmer如下图所示:先选中Program/configure下面的小方框,并在“Mode”右侧选择“Active Serial Programming”然后点“Start”,Programmer开始下载POF文件。

3、确认成功。

下载成功后界面如下:下载成功后在断电条件下从电路板拔出下载线,此时就可以使用FPGA。

FPGA可编程逻辑器件芯片EPM240GF100I5N中文规格书

Stratix II GX ArchitectureM512 RAM blocks can have different clocks on its inputs and outputs.The wren, datain, and write address registers are all clocked togetherfrom one of the two clocks feeding the block. The read address, rden, andoutput registers can be clocked by either of the two clocks driving theblock, allowing the RAM block to operate in read and write or input andoutput clock modes. Only the output register can be bypassed. The sixlabclk signals or local interconnect can drive the inclock, outclock,wren, rden, and outclr signals. Because of the advanced interconnectbetween the LAB and M512 RAM blocks, ALMs can also control the wrenand rden signals and the RAM clock, clock enable, and asynchronousclear signals. Figure2–49 shows the M512 RAM block control signalgeneration logic.Figure2–49.M512 RAM Block Control SignalsStratix II GX Device Handbook, Volume 1TransceiversFigure2–4.Transmitter PLL Block Note(1)Note to Figure2–4:(1)The global clock line must be driven by an input pin.The transmitter PLLs support data rates up to 6.375 Gbps. The input clockfrequency is limited to 622.08 MHz. An optional pll_locked port isavailable to indicate whether the transmitter PLL is locked to thereference clock. Both transmitter PLLs have a programmable loopbandwidth parameter that can be set to low, medium, or high. The loopbandwidth parameter can be statically set in the Quartus II software.Table2–2 lists the adjustable parameters in the transmitter PLL.Table2–2.Transmitter PLL SpecificationsParameter SpecificationsInput reference frequency range50 MHz to 622.08 MHzData rate support600 Mbps to 6.375 GbpsMultiplication factor (W)1, 4, 5, 8, 10, 16, 20, 25Bandwidth Low, medium, or highStratix II GX Device Handbook, Volume 1I/O StructureFigure2–75.Stratix II GX Device Fast PLLNotes to Figure2–75:(1)The global or regional clock input can be driven by an output from another PLL, a pin-driven dedicated global orregional clock, or through a clock control block provided the clock control block is fed by an output from another PLL or a pin-driven dedicated global or regional clock. An internally generated global signal cannot drive the PLL.(2)In high-speed differential I/O support mode, this high-speed PLL clock feeds the serializer/deserializer (SERDES)circuitry. Stratix II GX devices only support one rate of data transfer per fast PLL in high-speed differential I/O support mode.(3)This signal is a differential I/O SERDES control signal.(4)Stratix II GX fast PLLs only support manual clock switchover.f Refer to the PLLs in Stratix II & Stratix II GX Devices chapter in volume 2of the Stratix II GX Device Handbook for more information on enhancedand fast PLLs. Refer to “High-Speed Differential I/O with DPA Support”on page2–136 for more information on high-speed differential I/Osupport.I/O Structure The Stratix II GX IOEs provide many features, including:■Dedicated differential and single-ended I/O buffers■ 3.3-V, 64-bit, 66-MHz PCI compliance■ 3.3-V, 64-bit, 133-MHz PCI-X 1.0 compliance■Joint Test Action Group (JTAG) boundary-scan test (BST) support■On-chip driver series termination■On-chip termination for differential standards■Programmable pull-up during configuration■Output drive strength control■Tri-state buffers■Bus-hold circuitry■Programmable pull-up resistors■Programmable input and output delaysStratix II GX Device Handbook, Volume 1。

usb blaster 使用手册

安装和使用手册/MIRROROKQQ4641452安装和使用手册 (1)1. USB B l ast er图片 (3)2. USB Blaster下载线特性 (4)3. 系统配置 (4)4. 产品清单 (4)5. 注意事项 (4)6. 接口定义 (5)7. USB-Blaster安装过程 (6)8.SignalTap II逻辑分析仪使用方法 (10)9. 用AS模式下载口对EPCSx配置器件编程 (17)10.用JTAG接口对FPGA编程 (20)11. 异常处理 (21)1、USB B l ast er图片淘宝链接:/USB-Blaster2、USB Blaster 下载线特性1、 真正完美支持 1.2V 到 5V 的 J TAG/ASP IO 电压(部分型号只支持 2V 到 5V);2、 支持 S ignalTap 嵌入式逻辑分析仪功能3、 支持 A LTERA 公司的全系列器件-- CP L D :MAX3000、MAX7000、MAX9000、和M AXII 等系列 -- FPGA :Stratix 、Stratix II 、StratixIII 、Stratix IV 、HardCopy I 、HardCopy II 、HardCopyIII 、 HardCopy IV 、Cyclone I 、Cyclone II 、Cyclone III 、Cyclone IV 、AC E X1K 、AC E X20K 和 A CEX10K 等-- 主动串行配置器件:EPCS1、EPCS4、EPCS16 等以及其它第三方配置器件 -- 增强型配置器件:EPC1、EPC4、EPC16 等。

4、 支持三种下在模式:EPCI 、EPCS4、EPCS16 等; 5、 支持与 N ios II 嵌入式软核处理器的通信和在系统调试; 6、 速度快:比常用的并口下载线 B yteBlasterII 快 6 倍; 7、 使用方便:USB 接口连接方便,2 个状态指示灯使调试更加得心应手; 8、 必须:目前笔记本电脑几乎已经淘汰了并口,所以常用的 B yteBlasterMV 和 B yteBlasterII下 载线都已选用 USB 下载线即A USB B la s te r ,使用方法和性能都和A LTERA 原厂下载线一致。

EMP240开发板使用指南

1.新建工程

2.编译

执行菜单processin g→start compilation

3.

新建文件→选择 other files→ vector waveform file→点击OK→保存(与文件同名)→在新建的波形文件中的左方NAME区域内单击右键选择Insert→ insert node or bus →点击 node finder →在filter中选择Pins:assigned (或all)→点击List

设定仿真终止时间

设定步长:

4.加激励信号(即输入时钟)

波形编译

5.将VHDL语言的程序例化成一个模块

6. 分配管脚

LED灯正极接在组选线上,负极接在红黄绿信号线上

看现象,则要修改一下程序:

下载:点击

二、点阵的应用

对于点阵来说,扫描和编码有两种方式,通过行扫就是对列编码,通过列扫就进行行编码,并且行高列低时灯亮!

可控计数器:

引脚分配:

L[7..0] 8*8点阵行选90~83 Sum[2..0] 8*8点阵列78、81、82 Rst 按键61

Cout 8*8点阵第4列77

En 拨码开关30

Up 拨码开关33。

epm240实验板说明书.

第1章 EPM240-CPLD实验板1.1 概述学习单片机、CPLD其实关键是实践,从51入门是个好选择,但不要停留在起点,学单片机方法得当是瞬间的事!但用好,就不好说了,一辈子都要努力随着产品控制技术的进步,CPLD与单片机的联系越来越密切,学会灵活应用CPLD已经作为我们工程技术人员的基本要求,抓紧时间学习吧,面对复杂的任务您就能应对自如,您的未来将更美好。

CPLD 开发板EMP240 是一套基于Altera MAX II240 芯片的学习开发平台,我们为用户提供了丰富的板载资源及例子程序(Verilog和VHDL),很容易实现产品的直接应用及再次开发。

本开发板供CPLD编程初学者学习使用,也可作为系统板嵌入到用户的产品供用户进行二次开发以便缩短产品开发周期,同时也可以作为毕业设计的开发平台,让您轻轻松松做好您的毕业设计,因为我们附带了众多功能实现的源代码,我们还将无偿提供板载资源的的资料,来提高您毕业的创新性,您的肯定就是我们最好的褒奖。

开发板提供丰富的接口资源和实例程序。

从易到难,一步步引导用户学习开发。

开发实例有VHDL和Verilog两个版本,同时还包括详细的使用手册和丰富的配套经典学习资料,非常适合CPLD,FPGA,VHDL,Verilog HDL开发学习者使用。

让用户理论和实际相结合,合理安排学习开发时间。

详细的说明文档,包括原理图讲解,实验操作及现象说明,QuartusII软件使用指导书,以及入门操作指导视频。

本开发板供CPLD编程初学者学习使用,也可作为系统板嵌入到用户的产品供用户进行二次开发以便缩短产品开发周期,同时也可以作为毕业设计的开发平台,让您轻轻松松做好您的毕业设计。

1.2 实验板的基本结构实验板是由美国ALTERA公司MAXII系列器件中的EPM240T100C5芯片以及可供设计者选择的丰富的外围接口器件组成。

EPM240T100C5芯片采用20MHz的石英晶体振荡器作为主时钟信号源。

EPM240开发板简介(送USB Blaster下载线)

CPLD 开发板EPM240 系列产品简介一. 产品简介CPLD 开发板EMP240 是一套基于Altera MAXⅡ240 芯片的学习开发平台,我们为用户提供了丰富的板载资源及例子程序(Verilog和VHDL),很容易实现产品的直接应用及再次开发。

本开发板供CPLD编程初学者学习使用,也可作为系统板嵌入到用户的产品供用户进行二次开发以便缩短产品开发周期,同时也可以作为毕业设计的开发平台,让您轻轻松松做好您的毕业设计,因为我们附带了众多功能实现的源代码,我们还将无偿提供板载资源的的资料,来提高您的创新性。

整体效果图二系统资源八位共阴数码管;8个LED灯;8 个独立按键;一个八位拔码开关;1个RS-232接口;1个PS/2接口;LCD1620字符液晶接口;1路步进电机接口;1路直流电机控制端口;USB接口和外接接口两种电源供电方式;采用50M有源晶振、ALTERA新一代MAX II CPLD EPM240一个红外接收头;1个DS18B20外置端口;1路独立继电器输;1路蜂鸣器;JTAG接口一个;I2C存储器24LC02扩展I/0,用户可以接其它用户设备,可以和自己的目标系统进行直接连接使用.。

三. CPLD 开发板实验代码(提供以下实验原代码,采用Verilog 编写,部分也采用VHDL 语言编写)实验一译码1、38译码2、与门实验二 LED显示1、LED 闪烁2、LED流水灯实验三数码管1、数码管静态显示2、数码管动态显示3、数字时钟实验四按键控制LED1、键值显示2、拔码开关译码3、按键控制继电器实验五音乐演奏1、七色音符演奏2、MUSIC播放实验六红外接收1、红外接收编码分析实验七电机控制1、PWM 脉宽调制控制直流电机转速2、步进电机调速控制实验八 LCD显示1、LCD1602显示控制实验九通讯1、串口发送2、串口接收实验十 PS/21、PS/2键盘键值显示2、PS/2鼠标功能仿真实验十一综合测试1、多功能综合测试四配套资料及软件1.完整的电路原理图(PDF格式);2.所有实验提供源代码;3.提供开发板上的所有芯片资料;4.赠送 QUARTUS 7.0完全开发视频教材(市面上买不到的视频教材);5. 提供 QUARTUS 7.0完全破解版软件及注册码;7. CPLD开发资料,用户手册等。

USB-Blaster 驱动安装方法

USB-Blaster 驱动安装方法提示:驱动程序只需要在第一次使用本产品时安装一次。

1. 将 USB 连接线一端(方形)连接到Sunshine-Blaster 的USB 接口,另一端(扁平)连接到插入计算机USB 接口。

在桌面的任务栏上将出现下图所示画面,指示检测到Altera USB-Blaster。

2.稍等片刻,出现“找到新的硬件向导”。

3.选择“是,仅这一次”,点下一步继续。

4.选择“从列表或指定位置安装”,点下一步继续。

5. 选中“在搜索中包括这个位置”,点浏览按钮找到驱动程序的位置。

驱动程序就位于QuartusII 安装目录的drivers/usb-blasater 子目录 下。

本图中QuartusII 安装在C:\altera\72\quartus 目录下。

6.点击“仍然继续”7. 点击“完成”结束驱动的安装。

如果您此时进入到设备管理器,您 将看到在通用串行总线控制器列表中,出现了ALTERA USB-Blaster。

8. 下载设计文件如果将设计文件下载到可编程逻辑器件EPM240T100C5芯片中,则要进行如下几个步骤:A.设备连接将下载电缆的一端与PC机usb口相连,另一端与实验板编程下载接口(JTAG)连接好,打开实验板电源。

B.打开编程下载窗口选择“Tools”菜单下的“Programmer”命令(或者直接在工具栏中单击按钮),打开如图所示编程下载窗口。

图编程下载窗口9.硬件设置对硬件的设置只需在第一次下载时进行,如果下载电路不变换,一次设置就可长期使用而不需要每次都重新设置。

进行硬件设置的方法如下:(1)单击“Hardware Setup…”按钮,弹出“Hardware Setup”对话框,选择“USB-Blaste[USB-0]”,单击“OK”按钮,即完成下载电缆的选择回到“Hardware Setup”对话框,如图所示。

图下载电缆选择完成(4)单击“Close”按钮,即完成了硬件的设置回到编程下载窗口。

usb blaster原理

usb blaster原理

USB blaster是一种硬件设备,用于将计算机与FPGA(现场可

编程门阵列)开发板连接起来,实现数据传输、编程和调试等功能。

其工作原理如下:

1. USB接口:USB blaster通过USB接口连接到计算机上,实

现与计算机的通信。

2. 驱动程序:计算机上运行的驱动程序能够识别并和USB blaster进行通信,驱动程序由FPGA芯片制造商提供。

3. FPGA接口:USB blaster通过一根电缆(通常是JTAG电缆)连接到FPGA开发板上的JTAG接口。

4. JTAG接口:JTAG(边界扫描测试)是一种用于FPGA调

试和编程的通用接口标准,它通过FPGA芯片内置的JTAG控制器与USB blaster进行通信。

5. 数据传输:USB blaster通过JTAG接口向FPGA芯片传输数据,包括配置文件(bitstream)和调试信息等。

6. 调试和编程:USB blaster能够在调试模式下读取和写入FPGA芯片的寄存器,以实现调试功能。

同时,它也可以用来

编程FPGA芯片,将配置文件加载到FPGA中实现特定功能。

综上所述,USB blaster通过USB接口与计算机连接,通过

JTAG接口与FPGA芯片通信,实现数据传输、调试和编程等

功能。

这使得工程师能够方便地进行FPGA开发和调试工作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

CPLD 开发板EPM240 系列产品简介

一. 产品简介

CPLD 开发板EMP240 是一套基于Altera MAXⅡ240 芯片的学习开发平台,我们为用户提供了丰富的板载资源及例子程序(Verilog和VHDL),很容易实现产品的直接应用及再次开发。

本开发板供CPLD编程初学者学习使用,也可作为系统板嵌入到用户的产品供用户进行二次开发以便缩短产品开发周期,同时也可以作为毕业设计的开发平台,让您轻轻松松做好您的毕业设计,因为我们附带了众多功能实现的源代码,我们还将无偿提供板载资源的的资料,来提高您的创新性。

整体效果图

二系统资源

八位共阴数码管;

8个LED灯;

8 个独立按键;

一个八位拔码开关;

1个RS-232接口;

1个PS/2接口;

LCD1620字符液晶接口;

1路步进电机接口;

1路直流电机控制端口;

USB接口和外接接口两种电源供电方式;

采用50M有源晶振、ALTERA新一代MAX II CPLD EPM240

一个红外接收头;

1个DS18B20外置端口;

1路独立继电器输;

1路蜂鸣器;

JTAG接口一个;

I2C存储器24LC02

扩展I/0,用户可以接其它用户设备,可以和自己的目标系统进行直接连接使用.。

三. CPLD 开发板实验代码

(提供以下实验原代码,采用Verilog 编写,部分也采用VHDL 语言编写)

实验一译码

1、38译码

2、与门

实验二 LED显示

1、LED 闪烁

2、LED流水灯

实验三数码管

1、数码管静态显示

2、数码管动态显示

3、数字时钟

实验四按键控制LED

1、键值显示

2、拔码开关译码

3、按键控制继电器

实验五音乐演奏

1、七色音符演奏

2、MUSIC播放

实验六红外接收

1、红外接收编码分析

实验七电机控制

1、PWM 脉宽调制控制直流电机转速

2、步进电机调速控制

实验八 LCD显示

1、LCD1602显示控制

实验九通讯

1、串口发送

2、串口接收

实验十 PS/2

1、PS/2键盘键值显示

2、PS/2鼠标功能仿真

实验十一综合测试

1、多功能综合测试

四配套资料及软件

1.完整的电路原理图(PDF格式);

2.所有实验提供源代码;

3.提供开发板上的所有芯片资料;

4.赠送 QUARTUS 7.0完全开发视频教材(市面上买不到的视频教材);

5. 提供 QUARTUS 7.0完全破解版软件及注册码;

7. CPLD开发资料,用户手册等。

以上赠送资料仅供学习用,请勿用于商业用途!

五.相关配件

A、发货配件

1、EPM240开发板 1块;

2、5V直流电机 1个;

3、串口线 1根;

4、USB连接线 1根;

5、AT89/BLASTER II通用下载线 1根;

6、跳线帽两个;

7、用户光盘;

B、选购配件

1、步进电机(选配件,售价:13元);

2、LCD1602液晶(选配件,售价:15元);

3、DS18B20芯片TO-92封装(选配件,售价:7元);。