AM27ID08

DiGiCo SD7数字调音台产品介绍中文

香港葵涌梨木道73-77号海晖中心五楼505室大中华区总代理華匯DiGiCo SD7,一步跨过两个时代。

DiGiCo D系列调音台邀您步入一个全新的数字调音世界。

使用全新的SD7数字调音台,我们将带您穿越两个时代。

结合了Stealth Digital Processing 技术与壮观的用户界面,再一次为世界各地的调音师解除了许多使用障碍。

目录2 一步跨过两个时代2 目录3 介绍5 创建12年,领先12年8 受启发的工程学9 Stealth音频处理能力11 一些调音台使人想起模拟的根源…13 20/20视觉:从一开始就非常直观15 SD7的工作界面:让您一目了然18 谁是我们最优先考虑的人?您!19 F.0.H的首选21 监听调音师们的梦想23 世界级剧场缩混25 从现场到转播:提供稳固的工作状态27 真正灵活的操作伙伴30 高达192KHz的纯正音质:耳听为实31 12输入通道为一组,仅仅是符合操作逻辑吗?33 4段均衡,也同样的4段动态均衡器34 “多段压缩”,不正是您想要的吗?36 不仅是音频桌面设置,也是您个性的体现!37 IDM:动态交互电平表桥40 诱人的效果Tiger SHARC®41 MADI,光纤,备份,AES,D-Tube,一应俱全42 调音台I/043 双备份44 12年传承45 技术信息当专业音频领域第一次将目光投向DiGiCo D5 Live时,它提供了在数字音频环境可以提供的最好的模拟工作实用性与音频通用性,以及丰富的功能。

许多年过去了,D系列调音台一直是标准的制定者,并且其精美的用户界面从来没有被其他调音台击败过。

对于大多数调音师来说,D系列调音台也继续提供了模拟平滑度和数字清晰度的最佳结合。

但人们的期待一直在增加。

当今世界,无论对音响工程师还是调音台生厂商而言,竞争都非常激烈。

您希望得到可以依赖的最好的工具;您同时也希望调音台考虑到每个主要应用,并且为艺术和音响工程科学而设计。

IR公司_大功率MOS管选型

I DContinuous Drain Current(A)70°Micro3Surface Mount PackagesV (BR)DSSDrain-to-Source Breakdown Voltage (V)R DS(on)On-State Resistance ()ΩI D Continuous Drain Current 25°C(A)R ΘMax.Thermal Resistance (°C/W)1FaxonDemand Number Case Outline KeyPartNumberPD Max.PowerDissipation (W)N-ChannelLogic LevelIRLML2402*912570.54200.25 1.20.95230H1IRLML2803912580.54300.251.20.93230P-ChannelLogic LevelIRLML6302*912590.54-200.6-0.62-4.8230H1IRLML5103912600.54-300.6-0.61-4.8230* Indicates low VGS(th), which can operate at VGS = 2.7VMeasured at ambient for Micro3, Micro6, Micro8, SO-8, and SOT-223 package styles. All others measured at case.1Micro3SO-8D-PakD -PakSOT-227Micro6SOT-223Micro82 Illustrations not to scaleI DContinuous Drain Current(A)70°Micro6Surface Mount PackagesV (BR)DSSDrain-to-Source Breakdown Voltage (V)R DS(on)On-State Resistance ()ΩI D Continuous Drain Current 25°C(A)R ΘMax.Thermal Resistance (°C/W)1FaxonDemand Number Case Outline KeyPartNumberPD Max.PowerDissipation (W)N-ChannelLogic LevelIRLMS1902915401.7200.10 3.2 2.675H2IRLMS1503915081.7300.103.22.675P-ChannelLogic LevelIRLMS6702*914141.7-200.20-2.3-1.975H2IRLMS5703914131.7-300.20-2.3-1.975* Indicates low VGS(th), which can operate at VGS = 2.7VMeasured at ambient for Micro3, Micro6, Micro8, SO-8, and SOT-223 package styles. All others measured at case.1Micro3SO-8D-PakD -PakSOT-227Micro6SOT-223Micro82 Illustrations not to scaleI DContinuous Drain Current(A)70°Micro8Surface Mount PackagesV (BR)DSSDrain-to-Source Breakdown Voltage (V)R DS(on)On-State Resistance ()ΩI D Continuous Drain Current 25°C(A)R ΘMax.Thermal Resistance (°C/W)1FaxonDemand Number Case Outline KeyPart NumberP D Max.PowerDissipation (W)N-Channel Logic LevelIRF7601* 912611.820 0.035 5.7 4.6 70 H3IRF7603 912621.830 0.035 5.6 4.5 70Dual N-Channel Logic LevelIRF7501* 912651.220 0.135 2.4 1.9 100 H3IRF7503 912661.2530 0.135 2.4 1.9 100P-Channel Logic LevelIRF7604* 912631.8-20 0.09 -3.6 -2.9 70 H3IRF7606 912641.8-30 0.09 -3.6 -2.9 70Dual P-Channel Logic LevelIRF7504* 912671.25-20 0.27 -1.7 -1.4 100 H3IRF7506 912681.25-30 0.27 -1.7 -1.4 100Dual N- and P-Channel Logic LevelIRF7507* 912691.2520 0.1352.4 1.9 100 H3-20 0.27 -1.7 -1.4IRF7509 912701.2530 0.135 2.4 1.9 100-30 0.27 -1.7 -1.4* Indicates low VGS(th), which can operate at VGS = 2.7VMeasured at ambient for Micro3, Micro6, Micro8, SO-8, and SOT-223 package styles. All others measured at case.1Micro3SO-8D-Pak D -PakSOT-227Micro6SOT-223Micro8 2 Illustrations not to scaleI DContinuous Drain Current(A)70°SO-8Surface Mount PackagesV (BR)DSSDrain-to-Source Breakdown Voltage (V)R DS(on)On-State Resistance ()ΩI D Continuous Drain Current 25°C(A)R ΘMax.Thermal Resistance (°C/W)1FaxonDemand Number Case Outline KeyPart Number P D Max.PowerDissipation (W)N-ChannelIRF7413913302.5300.011139.250H4IRF7413A 916132.5300.0135128.450IRF9410915622.5300.0375.850Dual N-ChannelIRF7311914352.0200.029 6.6 5.362.5H4IRF7313914802.0300.029 6.5 5.262.5IRF7333917002.0300.10 3.5 2.862.5917002.0300.050 4.9 3.962.5IRF9956915592.0300.103.52.862.5Dual P-ChannelIRF7314914352.0-200.058-5.3-4.362.5H4IRF7316915052.0-300.058-4.9-3.962.5IRF9953915602.0-300.25-2.3-1.862.5* Indicates low VGS(th), which can operate at VGS = 2.7VMeasured at ambient for Micro3, Micro6, Micro8, SO-8, and SOT-223 package styles. All others measured at case.1Micro3SO-8D-PakD -PakSOT-227Micro6SOT-223Micro82 Illustrations not to scaleI DContinuous Drain Current(A)70°SO-8Surface Mount PackagesV (BR)DSSDrain-to-Source Breakdown Voltage (V)R DS(on)On-State Resistance ()ΩI D Continuous Drain Current 25°C(A)RΘMax.ThermalResistance(°C/W)1FaxonDemand Number Case Outline KeyPart NumberP D Max.PowerDissipation (W)Dual N- and P-ChannelIRF7317 915682.020 0.029 6.6 5.3 62.5 H42.0-20 0.058 -5.3 -4.3 62.5IRF9952 915622.030 0.103.5 2.8 62.5915622.0-30 0.25 -2.3 -1.8 62.5IRF7319 916062.030 0.029 6.5 5.2 62.52.0-30 0.058 -4.9 -3.9 62.5* Indicates low VGS(th), which can operate at VGS = 2.7VMeasured at ambient for Micro3, Micro6, Micro8, SO-8, and SOT-223 package styles. All others measured at case.1Micro3SO-8D-Pak D -PakSOT-227Micro6SOT-223Micro8 2 Illustrations not to scaleI DContinuous Drain Current(A)70°SO-8Surface Mount PackagesV (BR)DSSDrain-to-Source Breakdown Voltage (V)R DS(on)On-State Resistance ()ΩI D Continuous Drain Current 25°C(A)R ΘMax.Thermal Resistance (°C/W)1FaxonDemand Number Case Outline KeyPart Number P D Max.PowerDissipation (W)N-ChannelLogic LevelIRF7401912442.5200.0228.77.050H4IRF7201911002.5300.0307.0 5.650IRF7403912452.5300.0228.55.450Dual N-ChannelLogic LevelIRF7101908712.0200.10 3.5 2.362.5H4IRF7301912382.0200.050 5.2 4.162.5IRF7303912392.0300.050 4.9 3.962.5IRF7103910952.0500.1303.02.362.5P-ChannelLogic LevelIRF7204911032.5-200.060-5.3-4.250H4IRF7404912462.5-200.040-6.7-5.450IRF7205911042.5-300.070-4.6-3.750IRF7406912472.5-300.045-5.8-3.750IRF7416913562.5-300.02-10-7.150* Indicates low VGS(th), which can operate at VGS = 2.7VMeasured at ambient for Micro3, Micro6, Micro8, SO-8, and SOT-223 package styles. All others measured at case.1Micro3SO-8D-PakD -PakSOT-227Micro6SOT-223Micro82 Illustrations not to scaleI DContinuous Drain Current(A)70°SO-8Surface Mount PackagesV (BR)DSSDrain-to-Source Breakdown Voltage (V)R DS(on)On-State Resistance ()ΩI D Continuous Drain Current 25°C(A)R ΘMax.Thermal Resistance (°C/W)1FaxonDemand Number Case Outline KeyPart Number P D Max.PowerDissipation (W)Dual P-ChannelLogic LevelIRF7104910962.0-200.250-2.3-1.862.5H4IRF7304912402.0-200.090-4.3-3.462.5IRF7306912412.0-300.10-3.6-2.962.5Dual N- and P-Channe Logic LevelIRF7307912421.4200.050 4.3 3.490H4-200.090-3.6-2.9IRF7105910972.0250.1093.5 2.862.52-250.25-2.3-1.862IRF7309912432.0300.050 4.9 3.962.5-300.10-3.6-2.9* Indicates low VGS(th), which can operate at VGS = 2.7VMeasured at ambient for Micro3, Micro6, Micro8, SO-8, and SOT-223 package styles. All others measured at case.1Micro3SO-8D-PakD -PakSOT-227Micro6SOT-223Micro82 Illustrations not to scaleI DContinuous Drain Current(A)70°SOT-223Surface Mount PackagesV (BR)DSSDrain-to-Source Breakdown Voltage (V)R DS(on)On-State Resistance ()ΩI D Continuous Drain Current 25°C(A)R ΘMax.Thermal Resistance (°C/W)1FaxonDemand Number Case Outline KeyPart Number P D Max.PowerDissipation (W)N-ChannelIRFL4105913812.1550.045 3.7 3.060H6IRFL110908612.01000.54 1.50.9660IRFL4310913682.11000.20 1.6 1.360IRFL21090868 2.02001.50.960.660IRFL214908622.02502.00.790.560P-ChannelIRFL9110908642.0-1001.2-1.1-0.6960H6N-ChannelLogic LevelIRLL3303913792.1300.031 4.6 3.760H6IRLL014N 914992.1550.14 2.0 1.660IRLL2705913802.1550.043.83.060* Indicates low VGS(th), which can operate at VGS = 2.7VMeasured at ambient for Micro3, Micro6, Micro8, SO-8, and SOT-223 package styles. All others measured at case.1Micro3SO-8D-PakD -PakSOT-227Micro6SOT-223Micro82 Illustrations not to scaleI DContinuous Drain Current(A)100°D-PakSurface Mount PackagesV (BR)DSSDrain-to-Source Breakdown Voltage (V)R DS(on)On-State Resistance ()ΩI D Continuous Drain Current 25°C(A)R ΘMax.Thermal Resistance (°C/W)1FaxonDemand Number Case Outline KeyPart Number P D Max.PowerDissipation (W)N-ChannelIRFR33039164257300.0313321 2.2H7IRFR024N9133638550.0751610 3.3IRFR41059130248550.0452516 2.7IRFR12059131869550.0273723 1.8IRFR11090524251000.54 4.3 2.75IRFR120N 91365391000.219.1 5.8 3.2IRFR391091364521000.11159.5 2.4IRFR2109052625200 1.5 2.6 1.75IRFR22090525422000.8 4.833IRFR21490703252502 2.2 1.45IRFR2249060042250 1.1 3.8 2.43IRFR3109059725400 3.6 1.7 1.15IRFR3209059842400 1.8 3.123IRFR42090599425003 2.4 1.53IRFRC2090637426004.421.33* Indicates low VGS(th), which can operate at VGS = 2.7VMeasured at ambient for Micro3, Micro6, Micro8, SO-8, and SOT-223 package styles. All others measured at case.1Micro3SO-8D-PakD -PakSOT-227Micro6SOT-223Micro82 Illustrations not to scaleI DContinuous Drain Current(A)100°D-PakSurface Mount PackagesV (BR)DSSDrain-to-Source Breakdown Voltage (V)R DS(on)On-State Resistance ()ΩI D Continuous Drain Current 25°C(A)R ΘMax.Thermal Resistance (°C/W)1FaxonDemand Number Case Outline KeyPart Number P D Max.PowerDissipation (W)P-ChannelIRFR55059161057-550.11-18-11 2.2H7IRFR53059140289-550.065-28-18 1.4IRFR90149065425-600.5-5.1-3.25IRFR90249065542-600.28-8.8-5.63IRFR91109051925-100 1.2-3.1-25IRFR91209052042-1000.6-5.6-3.63IRFR9120N 9150739-1000.48-6.5-4.1 3.2IRFR92109052125-2003-1.9-1.25IRFR92209052242-200 1.5-3.6-2.33IRFR92149165850-250 3.0-2.7-1.7 2.5IRFR93109166350-4007.0-1.8-1.12.5* Indicates low VGS(th), which can operate at VGS = 2.7VMeasured at ambient for Micro3, Micro6, Micro8, SO-8, and SOT-223 package styles. All others measured at case.1Micro3SO-8D-PakD -PakSOT-227Micro6SOT-223Micro82 Illustrations not to scaleI DContinuous Drain Current(A)100°D-PakSurface Mount PackagesV (BR)DSSDrain-to-Source Breakdown Voltage (V)R DS(on)On-State Resistance ()ΩI D Continuous Drain Current 25°C(A)R ΘMax.Thermal Resistance (°C/W)1FaxonDemand Number Case Outline KeyPart Number P D Max.PowerDissipation (W)N-ChannelLogic LevelIRLR27039133538300.0452214 3.3H7IRLR33039131657300.0313321 2.2IRLR31039133369300.0194629 1.8IRLR024N 9136338550.0651711 3.3IRLR27059131746550.042415 2.7IRLR29059133469550.0273623 1.8IRLR120N 91541391000.18511 6.9 3.2IRLR341091607521000.10159.52.4* Indicates low VGS(th), which can operate at VGS = 2.7VMeasured at ambient for Micro3, Micro6, Micro8, SO-8, and SOT-223 package styles. All others measured at case.1Micro3SO-8D-PakD -PakSOT-227Micro6SOT-223Micro82 Illustrations not to scaleI DContinuous Drain Current(A)100°D 2PakSurface Mount PackagesV (BR)DSSDrain-to-Source Breakdown Voltage (V)R DS(on)On-State Resistance ()ΩI D Continuous Drain Current 25°C(A)R ΘMax.Thermal Resistance (°C/W)1FaxonDemand Number Case Outline KeyPart NumberP D Max.PowerDissipation (W)N-ChannelIRFZ24NS 913554555 0.07 17 12 3.3 H10IRFZ34NS 913116855 0.04 29 20 2.2IRFZ44NS 9131511055 0.022 49 35 1.4IRFZ46NS 9130512055 0.020 53 37 1.3IRFZ48NS 9140814055 0.016 64 45 1.1IRF1010NS 913723.855 0.011 84 60 40IRF3205S 9130420055 0.008 110 80 0.75IRFZ44ES 9171411060 0.023 48 34 1.4IRF1010ES 9172017060 0.012 83 59 0.90IRF2807S 9151815075 0.013 71 50 1.0IRF520NS 9134047100 0.2 9.5 6.7 3.2IRF530NS 9135263100 0.11 15 11 2.4IRF540NS 91342110100 0.052 27 19 1.6IRF1310NS 91514120100 0.036 36 25 1.3IRF3710S 91310150100 0.028 46 33 1.0IRF3315S 9161794150 0.082 21 15 1.6IRF3415S 91509150150 0.042 37 26 1.0IRFBC20S 9.101450600 4.4 2.2 1.4 2.5IRFBC30S 9101574600 2.2 3.6 2.3 1.7IRFBC40S 91016130600 1.2 6.2 3.9 1.0* Indicates low VGS(th), which can operate at VGS = 2.7VMeasured at ambient for Micro3, Micro6, Micro8, SO-8, and SOT-223 package styles. All others measured at case.1Micro3SO-8D-Pak D -PakSOT-227Micro6SOT-223Micro8 2 Illustrations not to scaleI DContinuous Drain Current(A)100°D 2PakSurface Mount PackagesV (BR)DSSDrain-to-Source Breakdown Voltage (V)R DS(on)On-State Resistance ()ΩI D Continuous Drain Current 25°C(A)R ΘMax.Thermal Resistance (°C/W)1FaxonDemandNumberCase Outline KeyPart NumberP D Max.PowerDissipation (W)IRFBF20S 9166554900 8.0 1.7 1.1 2.3 H10P-ChannelIRF5305S 91386110-55 0.06 -31 -22 1.4 H10IRF4905S 914783.8-55 0.02 -74 -52 40IRF9520NS 9152247-100 0.48 -6.7 -4.8 3.2IRF9530NS 9152375-100 0.20 -14 -9.9 2.0IRF9540NS 9148394-100 0.117 -19 -13 1.6IRF5210S 91405150-100 0.06 -35 -25 1.0* Indicates low VGS(th), which can operate at VGS = 2.7VMeasured at ambient for Micro3, Micro6, Micro8, SO-8, and SOT-223 package styles. All others measured at case.1Micro3SO-8D-Pak D -PakSOT-227Micro6SOT-223Micro8 2 Illustrations not to scaleI DContinuous Drain Current(A)100°D 2PakSurface Mount PackagesV (BR)DSSDrain-to-Source Breakdown Voltage (V)R DS(on)On-State Resistance ()ΩI D Continuous Drain Current 25°C(A)R ΘMax.Thermal Resistance (°C/W)1FaxonDemand Number Case Outline KeyPart NumberP D Max.PowerDissipation (W)N-Channel Logic LevelIRL3302S 916925720 0.020 39 25 2.2 H10IRL3202S916756920 0.016 48 30 1.8IRL3102S 916918920 0.013 61 39 1.4IRL3402S 9169311020 0.01 85 54 1.1IRL3502S 9167614020 0.007 110 67 0.89IRL2703S 913604530 0.04 24 17 3.3IRL3303S 913236830 0.026 38 27 2.2IRL3103S 9133811030 0.014 64 45 1.4IRL2203NS 9136717030 0.007 116 82 0.90IRL3803S 9131920030 0.006 140 98 0.75IRLZ24NS 913584555 0.06 18 13 3.3IRLZ34NS 913086855 0.035 30 21 2.2IRLZ44NS 9134711055 0.022 47 33 1.4IRL3705NS 9150217055 0.01 89 63 0.90IRL2505S 9132620055 0.008 104 74 0.75IRLZ44S 9090615060 0.028 50 36 1.0IRL530NS 9134963100 0.1 15 11 2.4IRL2910S 91376150100 0.026 48 34 1.0* Indicates low VGS(th), which can operate at VGS = 2.7VMeasured at ambient for Micro3, Micro6, Micro8, SO-8, and SOT-223 package styles. All others measured at case.1Micro3SO-8D-Pak D -PakSOT-227Micro6SOT-223Micro8 2 Illustrations not to scaleI DContinuous Drain Current(A)100°SOT-227Surface Mount PackagesV (BR)DSSDrain-to-Source Breakdown Voltage (V)R DS(on)On-State Resistance ()ΩI D Continuous DrainCurrent 25°C(A)RΘMax.Thermal Resistance (°C/W)1FaxonDemand Number Case Outline KeyPart Number P D Max.PowerDissipation (W)N-ChannelFully Isolated Low ChargeFA38SA50LC 916155005000.1338240.25H21FA57SA50LC916506255000.0857360.20* Indicates low VGS(th), which can operate at VGS = 2.7VMeasured at ambient for Micro3, Micro6, Micro8, SO-8, and SOT-223 package styles. All others measured at case.1Micro3SO-8D-PakD -PakSOT-227Micro6SOT-223Micro82 Illustrations not to scaleI DContinuous Drain Current(A)100°I-PakThrough-Hole PackagesV (BR)DSSDrain-to-Source Breakdown Voltage (V)R DS(on)On-State Resistance ()ΩI D Continuous Drain Current 25°C(A)R ΘMax.Thermal Resistance (°C/W)1FaxonDemand Number Case Outline KeyPart Number P D Max.PowerDissipation (W)N-ChannelIRFU33039164257300.0313321 2.2H8IRFU024N 9133638550.0751610 3.3IRFU41059130248550.0452519 2.7IRFU12059131869550.0273723 1.8IRFU11090524251000.54 4.3 2.7 5.0IRFU120N 91365391000.219.1 5.8 3.2IRFU391091364521000.11159.5 2.4IRFU2109052625200 1.5 2.6 1.7 5.0IRFU22090525422000.80 4.8 3.0 3.0IRFU2149070325250 2.0 2.2 1.4 5.0IRFU2249060042250 1.1 3.8 2.4 3.0IRFU3109059725400 3.6 1.7 1.1 5.0IRFU3209059842400 1.8 3.1 2.0 3.0IRFU4209059942500 3.0 2.4 1.5 3.0IRFUC2090637426004.42.01.33.0I-PakTO-220 FullPakTO-262TO-247HEXDIPTO-220AB Illustrations not to scale** Not ratedI DContinuous Drain Current(A)100°I-PakThrough-Hole PackagesV (BR)DSSDrain-to-Source Breakdown Voltage (V)R DS(on)On-State Resistance ()ΩI D Continuous Drain Current 25°C(A)R ΘMax.Thermal Resistance (°C/W)1FaxonDemand Number Case Outline KeyPart Number P D Max.PowerDissipation (W)P-ChannelIRFU55059161057-550.11-18-11 2.2H8IRFU53059140289-550.065-28-18 1.4IRFU90149065425-600.50-5.1-3.2 5.0IRFU90249065542-600.28-8.8-5.6 3.0IRFU91109051925-100 1.2-3.1-2.0 5.0IRFU91209052042-1000.60-5.6-3.6 3.0IRFU9120N 9150739-1000.48-6.5-4.1 3.2IRFU92109052125-200 3.0-1.9-1.2 5.0IRFU92209052242-200 1.5-3.6-2.3 3.0IRFU92149165850-2503.0-2.7-1.7 2.5IRFU93109166350-4007.0-1.8-1.12.5N-ChannelLogic LevelIRLU27039133538300.0452214 3.3H8IRLU33039131657300.0313321 2.2IRLU31039133369300.0194629 1.8IRLU024N 9136338550.0651711 3.3IRLU27059131746550.04241715IRLU29059133469550.0273623 1.8IRLU120N 91541391000.18511 6.9 3.2IRLU341091607521000.10159.52.4I-PakTO-220 FullPakTO-262TO-247HEXDIPTO-220AB Illustrations not to scale** Not ratedI DContinuous Drain Current(A)100°HEXDIPThrough-Hole PackagesV (BR)DSSDrain-to-Source Breakdown Voltage (V)R DS(on)On-State Resistance ()ΩI D Continuous Drain Current 25°C(A)R ΘMax.Thermal Resistance (°C/W)1FaxonDemand Number Case Outline KeyPart Number P D Max.PowerDissipation (W)N-ChannelIRFD014907001.3600.2 1.7 1.2120H9IRFD024906991.3600.1 2.5 1.8120IRFD110903281.31000.54 1.00.71120IRFD120903851.31000.27 1.30.94120IRFD210903861.3200 1.50.60.38120IRFD220904171.32000.80.80.50120IRFD214912711.3250 2.00.570.32120IRFD224912721.3250 1.10.760.43120IRFD310912251.3400 3.60.420.23120IRFD320912261.3400 1.80.600.33120IRFD420912271.3500 3.00.460.26120IRFDC20912281.36004.40.320.21120I-PakTO-220 FullPakTO-262TO-247HEXDIPTO-220AB Illustrations not to scale** Not ratedI D Continuous Drain Current (A)100°TO-220Qg TotalGate Charge(nC)Through-Hole PackagesV (BR)DSSDrain-to-Source Breakdown Voltage (V)R DS(on)On-State Resistance ()ΩI D Continuous Drain Current 25°C (A)R ΘMax.Thermal Resistance(°C/W)1Faxon Demand Number Case OutlineKeyPart Number P D Max.Power Dissipation (W)N-ChannelLow ChargeIRF737LC91314743000.75 6.1** 1.7 3.9H11IRF740LC 910681254000.5510** 1.039IRF840LC 910691255000.858.0** 1.039IRFBC40LC910701256001.26.2**1.039I-PakTO-220 FullPakTO-262TO-247HEXDIPTO-220AB Illustrations not to scale** Not ratedI DContinuous Drain Current(A)100°TO-220ABThrough-Hole PackagesV (BR)DSSDrain-to-Source Breakdown Voltage (V)R DS(on)On-State Resistance ()ΩI D Continuous Drain Current 25°C(A)R ΘMax.Thermal Resistance (°C/W)1FaxonDemand Number Case Outline KeyPart Number P D Max.PowerDissipation (W)N-ChannelIRFZ24N 9135445550.071712 3.3H12IRFZ34N9127656550.042618 2.7IRFZ44N 9130383550.0244129 1.8IRFZ46N 9127788550.024633 1.7IRFZ48N 9140694550.0165337 1.6IRF1010N 91278130550.0127251 1.2IRF320591279150550.0089869 1.0IRFZ34E 9167268600.0422820 2.2IRFZ44E 91671110600.0234834 1.4IRF1010E 91670170600.01281570.90IRF280791517150750.0137150 1.0IRF520N 91339471000.209.5 6.79.5IRF530N 91351601000.111511 2.4IRF540N 91341941000.0522719 1.6IRF1310N 916111201000.0363625 1.3IRF3710913091501000.0284633 1.0IRF331591623941500.0822115 1.6IRF3415914771501500.0423726 1.0IRFBC209062350600 4.4 2.2 1.4 2.5IRFBC309048274600 2.2 3.6 2.3 1.7IRFBC4090506125600 1.2 6.2 3.9 1.0IRFBE2090610548006.51.81.22.3I-PakTO-220 FullPakTO-262TO-247HEXDIPTO-220AB Illustrations not to scale** Not ratedI DContinuous Drain Current(A)100°TO-220ABThrough-Hole PackagesV (BR)DSSDrain-to-Source Breakdown Voltage (V)R DS(on)On-State Resistance ()ΩI D Continuous Drain Current 25°C(A)R ΘMax.Thermal Resistance (°C/W)1FaxonDemand Number Case Outline KeyPart Number P D Max.PowerDissipation (W)IRFBE3090613125800 3.0 4.1 2.6 2.0H12IRFBF3090616125900 3.7 3.6 2.3 1.0IRFBG209060454100011 1.40.86 2.3IRFBG309062012510005.03.12.01.0P-ChannelIRF9Z24N 9148445-550.175-12-8.53.3H12IRF9Z34N 9148556-550.10-17-12 2.7IRF530591385110-550.06-31-22 1.4IRF490591280150-550.02-64-45 1.0IRF9530N 9148275-1000.20-13-9.2 2.0IRF9540N 9143794-1000.117-19-13 1.6IRF521091434150-1000.06-35-25 1.0IRF62159147983-1500.29-11-7.81.8I-PakTO-220 FullPakTO-262TO-247HEXDIPTO-220AB Illustrations not to scale** Not ratedI DContinuous Drain Current(A)100°TO-220ABThrough-Hole PackagesV (BR)DSSDrain-to-Source Breakdown Voltage (V)R DS(on)On-State Resistance ()ΩI D Continuous Drain Current 25°C(A)R ΘMax.Thermal Resistance (°C/W)1FaxonDemand Number Case Outline KeyPart NumberP D Max.PowerDissipation (W)N-Channel Logic LevelIRL3302 916965720 0.020 39 25 2.2 H12IRL3202 916956920 0.016 48 30 1.8IRL3102 916948920 0.013 61 39 1.4IRL3402 9169711020 0.01 85 54 1.1IRL3502 9169814020 0.007 110 67 0.89IRL2703 913594530 0.04 24 17 3.3IRL3303 913225630 0.026 34 24 2.7IRL3103 913378330 0.014 56 40 1.8IRL2203N 9136613030 0.007 100 71 1.230 0.007 61 43 3.2IRL3803 9130115030 0.006 120 83 1.0IRLZ24N 913574555 0.06 18 13 3.3IRLZ34N 913075655 0.035 27 19 2.7IRLZ44N 913468355 0.022 41 29 1.8IRL3705N 9137013055 0.01 77 54 1.2IRL2505 9132520055 0.008 104 74 0.75IRL520N 9149447100 0.18 10 7.1 3.2IRL530N 9134863100 0.10 15 11 2.4IRL540N 9149594100 0.044 30 21 1.6IRL2910 91375150100 0.026 48 34 1.0I-PakTO-220 FullPakTO-262TO-247HEXDIPTO-220AB Illustrations not to scale** Not ratedI D Continuous Drain Current (A)100°TO-220 FullPak (Fully Isolated)Qg TotalGate Charge(nC)Through-Hole PackagesV (BR)DSSDrain-to-Source Breakdown Voltage (V)R DS(on)On-State Resistance ()ΩI D Continuous DrainCurrent 25°C(A)R ΘMax.Thermal Resistance (°C/W)1Fax on Demand Number Case OutlineKeyPart Number P D Max.Power Dissipation (W)N-ChannelLow ChargeIRFI740GLC91209404000.55 6.0** 3.139H13IRFI840GLC 91208405000.85 4.8** 3.139IRFIBC40GLC91211406001.24.0**3.139I-PakTO-220 FullPakTO-262TO-247HEXDIPTO-220AB Illustrations not to scale** Not ratedI DContinuous Drain Current(A)100°TO-220 FullPak (Fully Isolated)Through-Hole PackagesV (BR)DSSDrain-to-Source Breakdown Voltage (V)R DS(on)On-State Resistance ()ΩI D Continuous Drain Current 25°C(A)R ΘMax.Thermal Resistance (°C/W)1FaxonDemand Number Case Outline KeyPart Number P D Max.PowerDissipation (W)N-ChannelIRFIZ24N 9150126550.07139.2 5.8H14IRFIZ34N9148931550.041913 4.8IRFIZ44N 9140338550.02428200.024IRFIZ46N 9130640550.023122 3.8IRFIZ48N 9140742550.0163625 3.6IRFI1010N 9137347550.0124431 3.2IRFI32059137448550.0085640 3.1IRFIZ24E 9167329600.071149.6 5.2IRFIZ34E 9167437600.0422115 4.1IRFI510G 90829271000.54 4.5 3.2 5.5IRFI520N 91362271000.207.2 5.1 5.5IRFI530N 91353331000.11117.8 4.5IRFI540N 91361421000.0521813 3.6IRFI1310N 91611451000.0362216 3.3IRFI371091387481000.0252820 3.1IRFI620G 90832302000.8 4.1 2.6 4.1IRFI630G 90652322000.4 5.9 3.7 3.6IRFI640G 90649402000.189.8 6.2 3.1IRFI614G 9083123250 2.0 2.1 1.3 5.5IRFI624G 9083330250 1.1 3.4 2.2 4.1IRFI634G 90738322500.45 5.6 3.5 3.6IRFI644G 90739402500.287.953.1I-PakTO-220 FullPakTO-262TO-247HEXDIPTO-220AB Illustrations not to scale** Not ratedI DContinuous Drain Current(A)100°TO-220 FullPak (Fully Isolated)Through-Hole PackagesV (BR)DSSDrain-to-Source Breakdown Voltage (V)R DS(on)On-State Resistance ()ΩI D Continuous Drain Current 25°C(A)R ΘMax.Thermal Resistance (°C/W)1FaxonDemand Number Case Outline KeyPart Number P D Max.PowerDissipation (W)IRFI720G 9083430400 1.8 2.6 1.7 4.1H14IRFI730G 9065032400 1.0 3.7 2.3 3.6IRFI740G 90651404000.55 5.4 3.4 3.1IRFI734G 9100135450 1.2 3.4 2.1 3.6IRFI744G 91002404500.63 4.9 3.1 3.1IRFI820G 9064130500 3.0 2.1 1.3 4.1IRFI830G 9064632500 1.5 3.12 3.6IRFI840G 90642405000.85 4.6 2.9 3.1IRFIBC20G 90850306004.41.71.1 4.1IRFIBC30G 90851356002.2 2.5 1.63.6IRFIBC40G 9085240600 1.2 3.5 2.2 3.1IRFIBE20G 9085330800 6.5 1.4.86 4.1IRFIBE30G 9085435800 3.0 2.1 1.4 3.6IRFIBF20G 90855309008.0 1.2.79 4.1IRFIBF30G90856359003.71.91.23.6P-ChannelIRFI9Z24N 9152929-550.175-9.5-6.7 5.2H14IRFI9Z34N 9153037-550.10-14-10 4.1IRFI49059152663-550.02-41-29 2.4IRFI9540G 9083742-1000.117-13-9.2 3.6IRFI9540N 9148742-1000.117-13-9.2 3.6IRFI52109140448-1000.06-20-14 3.1IRFI9634G 9148835-2501.0-4.1-2.63.6I-PakTO-220 FullPakTO-262TO-247HEXDIPTO-220AB Illustrations not to scale** Not ratedI DContinuous Drain Current(A)100°TO-220 FullPak (Fully Isolated)Through-Hole PackagesV (BR)DSSDrain-to-Source Breakdown Voltage (V)R DS(on)On-State Resistance ()ΩI D Continuous Drain Current 25°C(A)R ΘMax.Thermal Resistance (°C/W)1FaxonDemand Number Case Outline KeyPart Number P D Max.PowerDissipation (W)N-ChannelLogic LevelIRLI2203N 9137847300.0076143 3.2H14IRLI38039132048300.0066747 3.1IRLIZ24N 9134426550.06149.9 5.8IRLIZ34N 9132931550.0352014 4.8IRLIZ44N 9149838550.0222820 4.0IRLI3705N 9136947550.014733 3.2IRLI25059132763550.00858412.4IRLI520N 91496271000.187.7 5.4 5.5IRLI530N 91350331000.10117.8 4.5IRLI540N 91497421000.04420143.6IRLI291091384481000.02627193.1P-ChannelLogic LevelIRFI9520G 9083537-1000.6-5.2-3.6 4.1H14IRFI9530G 9083638-1000.03-7.7-5.4 3.6IRFI9620G 9087430-200 1.5-3.0-1.9 4.1IRFI9630G 9083840-2000.8-4.3-2.7 3.6IRFI9640G9083940-2000.5-6.1-3.93.1I-PakTO-220 FullPakTO-262TO-247HEXDIPTO-220AB Illustrations not to scale** Not ratedI D Continuous Drain Current (A)100°TO-247Qg TotalGate Charge(nC)Through-Hole PackagesV (BR)DSSDrain-to-Source Breakdown Voltage (V)R DS(on)On-State Resistance ()ΩI D Continuous Drain Current 25°C (A)R ΘMax.Thermal Resistance (°C/W)1Fax on Demand Number Case OutlineKeyPart Number P D Max.Power Dissipation (W)1N-ChannelLow ChargeIRFP350LC912291904000.3018**0.6570H16IRFP360LC 912302804000.2023**0.4598IRFP450LC 912311905000.4016**0.6570IRFP460LC 912322805000.2720**0.4598IRFPC50LC 912331906000.6013**0.6570IRFPC60LC912342806000.4016**0.4598I-PakTO-220 FullPakTO-262TO-247HEXDIPTO-220AB Illustrations not to scale** Not rated。

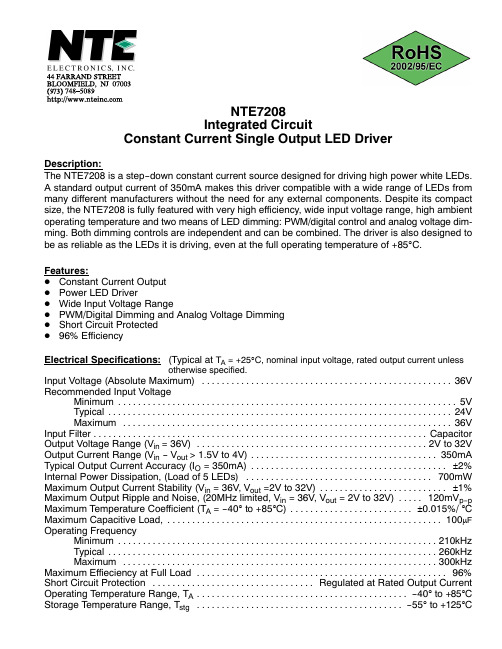

NTE7208 集成电路常电流单输出LED驱动器说明书

NTE7208Integrated CircuitConstant Current Single Output LED DriverDescription:The NTE7208 is a step-down constant current source designed for driving high power white LEDs.A standard output current of 350mA makes this driver compatible with a wide range of LEDs from many different manufacturers without the need for any external components. Despite its compact size, the NTE7208 is fully featured with very high efficiency, wide input voltage range, high ambient operating temperature and two means of LED dimming: PWM/digital control and analog voltage dim‐ming. Both dimming controls are independent and can be combined. The driver is also designed to be as reliable as the LEDs it is driving, even at the full operating temperature of +85°C.Features:D Constant Current OutputD Power LED DriverD Wide Input Voltage RangeD PWM/Digital Dimming and Analog Voltage DimmingD Short Circuit ProtectedD96% EfficiencyElectrical Specifications:(Typical at T A = +25°C, nominal input voltage, rated output current unlessotherwise specified.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Input Voltage (Absolute Maximum)36V Recommended Input Voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Minimum5V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Typical24V Maximum36V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Input Filter Capacitor. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Output Voltage Range (V in= 36V)2V to 32V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Output Current Range (V in - V out> 1.5V to 4V)350mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Typical Output Current Accuracy (I O = 350mA)±2%. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Internal Power Dissipation, (Load of 5 LEDs)700mW. . . . . . . . . . . . . . . . . . . . . . . . . . Maximum Output Current Stability (V in = 36V, V out =2V to 32V)±1%. . . . . Maximum Output Ripple and Noise, (20MHz limited, V in = 36V, V out = 2V to 32V)120mV p-p. . . . . . . . . . . . . . . . . . . . . . . . .Maximum Temperature Coefficient (T A = -40° to +85°C)±0.015%/ °C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Maximum Capacitive Load,100μF Operating Frequency. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Minimum210kHz . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Typical260kHz . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Maximum300kHz. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Maximum Effieciency at Full Load96%. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Short Circuit Protection Regulated at Rated Output Current. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Operating Temperature Range, T A-40° to +85°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Storage Temperature Range, T stg-55° to +125°CElectrical Specifications (Cont'd):(Typical at T A = +25°C, nominal input voltage, rated output currentunless otherwise specified.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Maximum Case Tempeature, T C+100°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Thermal Impedance (Nature Convection)+55°C/W . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Case Material Non Conductive Black Plastic Potting Material Epoxy (UL94-V0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Maximum Wave Soldering Profile (10 seconds)+235°C PWM Dimming and ON/OFF Control (Leave Open if Not Used):Remote ON/OFFDC/DC ON,Open or 0V < V r < 0.6V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .DC/DC OFF (Standby)0.6 < V r < 2.9V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .DC/DC OFF (Shutdown), 2.9 < V r < 6V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Maximum Remote Pin Drive Current (V r = 5V)1mA Maximum Quiescent Input Current in Shutdown Mode (V in = 36V, V r > 2.9V)200μA. . . . . . . . . . . .. . . . . . . Maximum PWM Frequency for Linear Operation (measured 10% to 90% Dimming)200Hz Analog Dimming Control (Leave Open if Not Used):. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Input Voltage Range0 to 15V Control Voltage Range Limits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Full On0.13V ± 50mV . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Full Off 4.5V ± 50mV. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Maximum Analog Pin Drive Current (V c = 5V)0.2mA Environmental:. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Relative Humidity (See Note)5% to 95% RH, non-condensing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Conducted Emissions EN55022, Class B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Radiated Emissions EN55022, Class B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .ESD EN61000-4-2, Class A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Radiated Immunity EN61000-4-3, Class A Fast Transient EN61000-4-4, Class A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Conducted Immunity EN61000-4-6, Class A MTBF (RCD-24-0.70, Nominal V in, Full Load)+25°C605 x 103 hours . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Using MIL-HDBK 217F, +71°C516 x 103 hoursNote: Requires an input filter to meet EN55022 Class B conducted emissions, see below.。

IC 规格书

TDA8927

• High efficiency (>94%) • Operating voltage from ±15 to ±30 V • Very low quiescent current • High output power • Short-circuit proof across the load, only in combination with controller TDA8929T • Diagnostic output • Usable as a stereo Single-Ended (SE) amplifier or as a mono amplifier in Bridge-Tied Load (BTL) • Electrostatic discharge protection (pin to pin) • Thermally protected, only in combination with controller TDA8929T. 2 APPLICATIONS

2001 Dec 11

2

Philips Semiconductors

Objective specification

Power stage 2 × 80 W class-D audio amplifier

1 FEATURES • Multimedia systems • All mains fed audio systems • Car audio (boosters). 3 GENERAL DESCRIPTION

MGW138

TDA8927J TDA8927ST

EN1 SW1 REL1 STAB DIAG POWERUP 4 1 2 9 3 15 CONTROL AND HANDSHAKE

派克液压密封件说明书

派克汉尼汾公司版权所有未经许可不能摘录,翻印。

保留修改权利2021年6月警告销售条件本样本中产品和/或系统或相关产品出现故障,选型不当或使用不当,均可能导致人身伤亡和财产损失。

本文档以及由派克·汉尼汾公司及其子公司和授权经销商提供的其他资料,为具有技术知识的用户提供进一步研究所需的产品和/或系统选项。

重要的是,用户必须对您的应用进行全面的分析,并对当前产品样本中与产品或系统相关的资料进行评估。

由于工作条件以及产品或系统的多样性,用户必须自行分析和测试,并独自承担一切后果,包括:产品和系统的最终选型以及确保满足应用的所有性能、安全和警告等方面的要求。

派克·汉尼汾及其子公司可能会随时对本样本中的产品,包括但不限于:产品的特性、产品的规格、产品的结构、产品的有效性以及产品的价格作出变更而不另行通知.本样本中的所有产品均由派克·汉尼汾公司及其子公司和援权经销商销售。

与派克签订的任何销售合同均按照派克标准条件和销售条件中规定的条款执行(提供复印件备索)。

本公司的密封件,只能在本公司的文件资料述及的应用参数范围与接触介质、压力、温度和存放时间相一致的情况下才能使用。

在规定的应用参数范围外使用以及错误选用不同的材料都可能导致密封件寿命的缩短以及设备的损坏,甚至更严重的后果(如生命安全,环境污染等)。

样本中所列出的工作压力、温度范围、运动速度是极限值,它们之间相互关联、相互影响;在极端的工况下,建议不要同时把各个参数都同时用到极限值。

对于特殊的要求(压力、温度、速度、介质等),请联系派克汉尼汾公司以咨询合适的密封结构、材料、配置、安装建议等。

由于诸多工作参数会影响到流体传动系统及密封元件,这些设备的制造商必须在实际工作条件下测试、验证并批准密封系统的功能与可靠性。

此外,对于不断出现的新的介质(液压油、润滑脂、清洗剂等),用户特别注意它们与目前所用的密封件弹性体材料的兼容性。

我们建议用户在大批量应用之前,在厂内或现场先做密封材料的兼容性能测试,作为密封产品与系统供应商,我们建议用户遵循我们的这些建议。

番茄SlNAM1_参与调节植物花青素累积

2023 ,43(3) : 001J.SHANXI AGRIC, UNIV . ( N atural Science Edition )学报(自然科学版)04189番茄SlNAM1参与调节植物花青素累积柳芳艳,张苹,郭慧敏,宋倩倩,孙亮亮*,徐进*(山西农业大学 园艺学院,山西 晋中 030801)摘要:[目的]探究番茄SlNAM1参与调节花青素累积的分子机理,深入理解植物花青素积累的调控机制。

[方法]通过酵母双杂交实验,检测番茄SlNAM1和SlMYB75、拟南芥NAC32与MYB75/PAP1蛋白相互作用;构建系统发育树,进行SlNAM1序列分析;通过烟草叶片瞬时表达分析,初步探明SlNAM1在调节植物花青素积累中的作用;在拟南芥pap1⁃D 突变体中过表达SlNAM1,研究SlNAM1在调节植物花青素积累中的作用;通过对拟南芥pap1⁃D NAC32OX (OX32)双突变体表型分析,进一步证明SlNAM1的拟南芥同源基因NAC32参与调控花青素积累。

[结果]酵母双杂交结果显示,SlNAM1与SlMYB75蛋白存在相互作用,其在拟南芥中的同源基因NAC32与MYB75/PAP1也存在相互作用;瞬时表达分析表明,SlNAM1通过与SlMYB75的相互作用,抑制了花青素积累;在拟南芥pap1⁃D 突变体中过表达SlNAM1可抑制花青素累积;拟南芥pap1⁃D OX32双突变体表型分析结果表明,NAC32过表达抑制了花青素积累。

[结论]综上所述,SlNAM1是花青素合成的负调节因子。

关键词:番茄; SlNAM1; SlMYB75; NAC32; 花青素中图分类号:S641.2 文献标识码:A 文章编号:1671-8151(2023)03-0001-08NAC 转录因子家族是植物体内特有的、最大的转录因子家族之一,它是以最早发现的基因成员矮牵牛无根分生组织(NAM )、拟南芥ATAF1、ATAF2及杯状子叶2(CUC2)的首字母来命名的[1]。

罗克韦尔自动化-2080-um002_-zh-e.pdf-Micro830、Micro850 和 M

Micro830、Micro850 和 Micro870可编程控制器Micro810 控制器产品目录号 2080-LC10-12AWA、2080-LC10-12QWB、2080-LC10-12DWD、2080-LC10-12QBBMicro820 控制器产品目录号 2080-LC20-20AWB、2080-LC20-20AWBR、2080-LC20-20QWB、2080-LC20-20QWBR、2080-LC20-20QBB、2080-LC20-20QBBRMicro830 控制器产品目录号 2080-LC30-10QWB、2080-LC30-10QVB、2080-LC30-16AWB、2080-LC30-16QWB、2080-LC30-16QVB、2080-LC30-24QWB、2080-LC30-24QVB、2080-LC30-24QBB、2080-LC30-48AWB、2080-LC30-48QWB、2080-LC30-48QVB、2080-LC30-48QBBMicro850 控制器产品目录号 2080-LC50-24AWB、2080-L50E-24AWB、2080-LC50-24QWB、2080-L50E-24QWB、2080-LC50-24QVB、2080-L50E-24QVB、2080-LC50-24QBB、2080-L50E-24QBB、2080-LC50-48AWB、2080-L50E-48AWB、2080-LC50-48QWB、2080-L50E-48QWB、2080-LC50-48QWBK、2080-L50E-48QWBK、2080-LC50-48QVB、2080-L50E-48QVB、2080-LC50-48QBB、2080-L50E-48QBBMicro870 控制器产品目录号 2080-LC70-24AWB、2080-L70E-24AWB、2080-LC70-24QWB、2080-L70E-24QWB、2080-LC70-24QWBK、2080-L70E-24QWBK、2080-L70E-24QWBN、2080-LC70-24QBB、2080-L70E-24QBB、2080-LC70-24QBBK、2080-L70E-24QBBK、2080-L70E-24QBBN2罗克⻙尔⾃动化出版物2080-UM002M-ZH-E - 2022 年4 月Micro830、Micro850 和 Micro870 可编程控制器⽤⼾⼿册重要⽤⼾须知在安装、配置、操作或维护本产品之前,请阅读本文档以及“其他资源”章节所列的文档,了解关于安装、配置和操作该设备的信息。

2008年Ford自动变速箱组件目录说明书

1622008 AUTOMATIC TRANSMISSION KIT & COMPONENTS CATALOG ©2008 PARKER HANNIFIN CORP. ALL RIGHTS RESERVED3790103008397797405R55N / 5R55S / 5R55WRWD 5 SpeedA544510034070670Input ShaftO.Dr. Ring GearO.Dr. CenterShaft783Center SupportInterm. BandDirect DrumForward ClutchForward PlanetReverse BandReverse DrumLow Sprag310037179520036178530311914363912911913910896904896437490996V.B.Parts741E414494765-6370Case313321320Valve Body917747765746322420002OHK Kit004Master L/Steels Kit 006Master 030External Seal Kit1632008 AUTOMATIC TRANSMISSION KIT & COMPONENTS CATALOG ©2008 PARKER HANNIFIN CORP . ALL RIGHTS RESERVEDRWD 5 Speed5R55N / 5R55S / 5R55W862981971961560961971985879565126106146861*229964974877564285872962972104124552894Intermediate Sprag690074266Park Gear264847Park Pawl Assy995-1995-2995-3995916-2916-3919922915916-2916-3919922916263EDA181554770Ext. Hsg.781493305678Output ShaftO.Dr. Band StrutInterm. Band Strut268841Internal Linkage991-2991-3994799991-4761P-4991072410992Yoke1642008 AUTOMATIC TRANSMISSION KIT & COMPONENTS CATALOG©2008 PARKER HANNIFIN CORP. ALL RIGHTS RESERVED*Prefix Letter ‘T’ denotes Toledo-Trans Kit (TTK) Brand Transmission Kits *Prefix Letter ‘B’ denotes Bryco Brand Transmission Kits002.............T16002AP......Overhaul Kit, 5R55N (With Bonded Pistons) 1999-Up ..............................................................1..........002.............T16002GP......Overhaul Kit, 5R55S/5R55W (With Bonded Pistons) 2002-Up..................................................1..........004.............T16004AP......Master L/Steels Kit, 5R55N (With Bonded Pistons) 1999-Up ....................................................1..........004.............T16004GP......Master L/Steels Kit, 5R55S/5R55W (With Bonded Pistons) 2002-Up .......................................1..........006.............T16006AP......Master W/Steels Kit, 5R55N (With Bonded Pistons) 1999-Up...................................................1..........006.............T16006GP......Master W/Steels Kit, 5R55S/5R55W (With Bonded Pistons) 2002-Up ......................................1..........E300...........45019............Gasket, 5R55N Bottom Pan (Plastic With Silicon Bead) OE Style (With Large Holes) 1999-Up 1..........XW4Z-7A191CA D305...........45097668......Gasket, 5R55N/5R55S/5R55W Extension Housing To Case 1999-Up......................................1..........XW4Z-7086-AA A309..........41217............Gasket, 5R55N/5R55S/5R55W Pump Bolt Washer...................................................................AR ........A310..........45097667......Gasket, 5R55N/5R55S/5R55W Pump 1999-Up..........................................................................1..........XW4Z-7A136AB A311...........1988096........O-Ring, 5R55N/5R55S/5R55W Pump Cover 1999-Up ...............................................................1..........XW4Z-7A248AA A313..........1994747........O-Ring, 5R55N Inner Pump Gear 1999-Up.................................................................................1..........F77Z-7L323AA E320...........45097692......Gasket, 5R55N Valve Body Separator Plate To Case 1999-Up ................................................1..........XW4Z-7D100-BF E320...........45097738......Gasket, 5R55S/5R55W Valve Body Separator Plate To Case (Upper) 2002-Up......................1..........1L2Z-7Z490AB-1A070..........70243V..........Seal, 5R55N/5R55S/5R55W Front (No Flange) (Rubber Coated) 1999-Up ..............................1..........F77Z-7A248AA D072...........70083............Seal, 5R55N Linkage 1999-Up ..................................................................................................1..........D5AZ-7B498A D074...........70283............Seal, 5R55N Rear 2WD 2000-Up ...............................................................................................1..........XW4Z-7052AA D074...........70205............Seal, 5R55S/5R55W Rear (W/Long Boot) 2WD 2002-Up .........................................................1..........F6UZ-7052A D074...........70282............Seal, 5R55S/5R55W Extension Housing 4X4 2002-Up .............................................................1..........1L2Z-7052BA175.............6358..............Ring Kit, 5R55N/5R55S/5R55W (2 Metal 4PTFE 2 Torlon Rings) 1999-Up ...............................1..........A178..........45060279......Ring, 5R55N, 5R55W, 5R55S Pump Support (Lock-Up) 1999-Up .............................................1..........B181...........TAW- 2212....Ring, 5R55N, 5R55W, 5R55S Forward Clutch Cylinder 1999-Up .............................................2..........D184...........45060265......Ring, 5R55N, 5R55W, 5R55S Output Shaft 1999-Up.................................................................1..........A179..........30308............Ring, 5R55N, 5R55W, 5R55S Overdrive Brake Drum 1999-Up.................................................2..........B179...........30308P ..........Ring, 5R55N, 5R55W, 5R55S Direct Clutch (Center Support) 1999-Up Torlon .........................2..........119.............45082NR........Friction Module, 5R55N 1999-Up................................................................................................1..........119.............45082LR........Friction Module, 5R55S/5R55W 2002-Up...................................................................................1..........E010...........45040N ..........Filter, 5R55N (3/8” Tall Pick-up Tube) 1999-Up ..........................................................................1..........XW4Z-7A098BB E010...........F-340.............Filter, 5R55S/5R55W (2 1/4” Tall Pick-Up Tube) 2002-Up..........................................................1..........1L2Z-7A098AC5R55N / 5R55S / 5R55WRWD 5 Speed1652008 AUTOMATIC TRANSMISSION KIT & COMPONENTS CATALOG ©2008 PARKER HANNIFIN CORP. ALL RIGHTS RESERVEDB022...........45090............Band, 5R55N Overdrive/Intermediate (Hi-Energy) 1999-Up......................................................2..........XW4Z-7D034BA 030.............45030G..........Bushing Kit, 5R55N/5R55S/5R55W 1999-Up.............................................................................1..........A034..........31530............Bushing, 5R55N/5R55S/5R55W Pump Cover 1999-Up .............................................................1..........A036..........31531............Bushing, 5R55N/5R55S/5R55W Overdrive Sun Gear 1999-Up................................................1..........A036..........45039............Bushing, 5R55N/5R55S/5R55W Stator (Front) 1999-Up ...........................................................1..........A037..........31532............Bushing, 5R55N/5R55S/5R55W Stator (Rear) 1999-Up............................................................1..........A046..........31533............Bushing, 5R55N/5R55S/5R55W Coast Clutch Drum e 56036A................................................................................................................................1..........B211...........45176A..........Washer, 5R55N/5R55S/5R55W Pump To Coast Clutch Drum .063" (Plastic) 1999-Up.............1..........F7TZ-7D014TA B211...........45176B ..........Washer, 5R55N/5R55S/5R55W Pump To Coast Clutch Drum .071" (Plastic) 1999-Up.............1..........F7TZ-7D014MA B211...........45176C ..........Washer, 5R55N/5R55S/5R55W Pump To Coast Clutch Drum .075" (Plastic) 1999-Up.............1..........F7TZ-7D014NA B211...........45176D ..........Washer, 5R55N/5R55S/5R55W Pump To Coast Clutch Drum .079" (Plastic) 1999-Up.............1..........F7TZ-7D014PA B211...........45176E ..........Washer, 5R55N/5R55S/5R55W Pump To Coast Clutch Drum .083" (Plastic) 1999-Up.............1..........F7TZ-7D014RA B211...........45176F ..........Washer, 5R55N/5R55S/5R55W Pump To Coast Clutch Drum .087" (Plastic) 1999-Up.............1..........F7TZ-7D014SA C232...........45145............Washer, 5R55N/5R55S/5R55W Bearing to Forward Hub (Solid Bronze) 1999-Up .................1..........FOTZ-7D090A D263...........45077............Washer, 5R55N/5R55S/5R55W Parking Gear To Case 1999-Up ..............................................1..........D4ZZ-7B368-AD410...........D56955J ........Switch, 5R55N Neutral Safety (12 Prong Connector) 1999-Up ...............................................1..........XW4Z-7F293AA E922...........33991............Nut, 5R55N/S/W Band 1999-Up .................................................................................................2..........380850-SRWD 5 Speed5R55N / 5R55S / 5R55W。

dfn8封装的e-marker芯片规格书

尊敬的读者:感谢您阅读本文。

本文将为您详细介绍dfn8封装的e-marker芯片规格书,帮助您更好地了解该产品的性能和特点。

1. 产品概述dfn8封装的e-marker芯片是一款集成了电子标识功能的芯片,可用于USB Type-C和Thunderbolt接口的连接线缆中。

该芯片具有高精度的识别和通信能力,能够实现连接线缆与主机设备之间的智能通信和识别,确保连接线缆在不同设备之间的兼容性。

2. 技术规格- 封装类型:dfn8- 工作温度范围:-40℃ 到85℃- 工作电压范围:3.3V- 通信协议:I2C- 识别标识:唯一ID- 支持接口:USB Type-C、Thunderbolt3. 主要特点- 高精度识别:通过内置的唯一ID,可以准确识别连接线缆的型号和特性,确保设备间的匹配和兼容性。

- 智能通信:支持I2C通信协议,可实现连接线缆与主机设备之间的智能通信,实现功能扩展和优化。

- 稳定可靠:经过严格的质量控制和测试,确保产品的稳定性和可靠性。

4. 应用领域dfn8封装的e-marker芯片广泛应用于USB Type-C和Thunderbolt 接口的连接线缆中,可用于笔记本电脑、平板电脑、显示器、移动硬盘等设备,提升设备之间的连接稳定性和兼容性。

通过以上详细介绍,相信您对dfn8封装的e-marker芯片有了更深入的了解。

该产品以其高精度的识别能力、智能的通信功能和稳定可靠的性能,在USB Type-C和Thunderbolt接口领域具有广阔的应用前景。

如果您对该产品还有其他疑问或需求,欢迎随时与我们通联,我们将竭诚为您提供服务。

谨代表XX公司,对您的阅读表示衷心的感谢!此致敬礼尊敬的读者:在上文中,我们对dfn8封装的e-marker芯片进行了详细的介绍,包括产品概述、技术规格、主要特点和应用领域。

接下来,将进一步对该产品的性能和特点进行深入探讨,以便让您更全面地了解这款先进的芯片产品。

5. 技术优势dfn8封装的e-marker芯片具有以下几项技术优势,使其在连接线缆中起到关键作用:- 高精度识别技术:e-marker芯片采用了先进的识别算法和独特的ID 编码技术,能够精准识别连接线缆的型号、版本和性能特点。

AFUWIN

AFUWINAMIBIOS8 ROM Utility User GuideAFUWINDocument Revision 1.0.1 – Aug 28, 2009NDA REQUIREDCopyright (c) 2008 American Megatrends, Inc.All Rights Reserved.American Megatrends, Inc.5555 Oakbrook ParkwaySuite 200Norcross, GA 30093This publication contains proprietary information which is protected by copyright. No part of this publication may be reproduced, transcribed, stored in a retrieval system, translated into any language or computer language, or transmitted in any form whatsoever without the prior written consent of the publisher, American Megatrends, Inc. American Megatrends, Inc. retains the right to update, change, modify this publication at any time, without notice. For Additional InformationCall American Megatrends BIOS Sales Department at 1-800-828-9264 for additional information.Limitations of LiabilityIn no event shall American Megatrends be held liable for any loss, expenses, or damages of any kind whatsoever, whether direct, indirect, incidental, or consequential, arising from the design or use of this product or the support materials provided with the product.Limited WarrantyNo warranties are made, either express or implied, with regard to the contents of this work, its merchantability, or fitness for a particular use. American Megatrends assumes no responsibility for errors and omissions or for the uses made of the material contained herein or reader decisions based on such use.Trademark and Copyright AcknowledgmentsAll product names used in this publication are for identification purposes only and are trademarks of their respective Companies.DisclaimerThis manual describes the operation of the AMIBIOS8 ROM Utilities. Although efforts have been made to insure the accuracy of the information contained here, American Megatrends expressly disclaims liability for any error in this information, and for damages, whether direct, indirect, special, exemplary, consequential or otherwise, that may result from such error, including but not limited to the loss of profits resulting from the use or misuse of the manual or information contained therein (even if American Megatrends has been advised of the possibility of such damages). Any questions or comments regarding this document or its contents should be addressed to American Megatrends at the address shown on the cover.American Megatrends provides this publication “as is” without warranty of any kind, either expressed or implied, including, but not limited to, the implied warranties of merchantability or fitness for a specific purpose.Some states do not allow disclaimer of express or implied warranties or the limitation or exclusion of liability for indirect, special, exemplary, incidental or consequential damages in certain transactions; therefore, this statement may not apply to you. Also, you may have other rights which vary from jurisdiction to jurisdiction.This publication could include technical inaccuracies or typographical errors. Changes are periodically made to the information herein; these changes will be incorporated in new editions of the publication. American Megatrends may make improvements and/or revisions in the product(s) and/or the program(s) described in this publication at any time. Requests for technical information about American Megatrends products should be made to your American Megatrends authorized reseller or marketing representative.Revision InformationOverviewAFUWIN is an updating system BIOS utility with command line and GUI interface. It has same parameters and behavior as AFUWIN, and further, GUI feature starting from v4.10can provide you a friendly environment to visualize BIOS update procedure. By the way, do not forget that target board MUST be AMIBIOS system while using this utility. FeaturesThis utility offers the following features:Small executable file sizeQuickly updateClear updating information and statusFully compatible with previous version (See Appendix B AFUWIN v3.xx Commands)RequirementsSupported Operating SystemAFUWIN Utility is supported in following operating system:Microsoft Windows 98Microsoft Windows MEMicrosoft Windows 2000Microsoft Windows NT 4.0Microsoft Windows XP/XP64Microsoft Windows PEMicrosoft Windows Vista 32/64Microsoft Windows PE 2.0 x64 (AFUWINx64.EXE)Microsoft Windows 7 32/64BIOS RequirementsSystem BIOS should have the followings:AMIBIOS CORE version 8.xx.xx.SMIFlash eModule with “8.00.00_SMIFlash-1.00.07” label or later.Token: SDSMGR_IN_RUNTIME = ON.Token: SMI_INTERFACE_FOR_SDSMGR_FUNC = ON.Operating System Driver RequirementsFollowing drivers for different operation system are required by this utility:UCOREVXD.VXD Driver for Microsoft Windows 98/MEUCORESYS.SYS Driver for Microsoft Windows NT/2000/XP/PEUCOREW64.SYS Driver for Microsoft Windows XP64 Getting Started InstallationCopies AFUWIN.EXE, AFUWINx64.EXE (for Microsoft Windows PE 2.0 x64), UCOREVXD.VXD, UCORESYS.SYS and UCOREW64.SYS to any storage location accessible by the host system and then run AFUWIN in command prompt. Remember that three files MUST be in same directory. For launching GUI mode, you can just double-click on the icon.UsageFor previous usage, see Appendix B AFUWIN v3.xx Commands to know details. AFUWIN [Option 1] [Option 2]……….OrAFUWINOrAFUWIN /MOrAFUWIN /MAIBIOS ROM File NameThe mandatory field is used to specify path/filename of the BIOS ROM filewith extension.CommandsThe mandatory field is used to select an operation mode:/O Save current ROM image to file/U Get and display ROM ID from ROM file/Ln Refer to option: /Ln/M Refer to option: /M/MAI Display current system and ROM file's MA/HOLE Update specific ROM hole by given name/HOLEOUT Save specific ROM holedata by given name/D Verification test of given ROM file withoutflashing/EC Flash EC firmware BIOS (Refer to OFBDspec)Path: $BIOS/Corebin/800/ROMUtils/On FlashBlock Description Specification.PDF.Sample Code Module Path:$BIOS/Examples/On Flash Block Description ?/NCB Flash NCB data by given name/NCBOUT Output NCB data by given name/C Destroy CMOS checksumOptionsThe optional field used to supply more information for flashing BIOS ROM.Following lists the supported optional parameters and format:?/P Program main bios image /B Program Boot Block/N Program NVRAM/C Destroy CMOS after update BIOS done/E Program Embedded Controller block if present /K Program all non-critical blocks/Kn Program n’th non-critical block only (n=0 – 7)/Q Quiet mode enable/REBOOT Reboot after update BIOS done/X Do not check ROM ID/S Display current system’s BIOS ROM ID/Ln Load CMOS default (n=0 - 1)L0: Load current CMOS optimal settingsL1: Load current CMOS failsafe settingsL2: Load CMOS optimal settings from ROMfileL3: Load CMOS failsafe settings from ROMfile/MUpdate BootBlock MAC address if exists/R Preserve all SMBIOS structures duringNVRAM programming/Rn Preserve specific SMBIOS structure duringNVRAM programming/ECUF Update EC BIOS when newer version isdetected./ShutDown Shutdown system after programming./clnevnlog Clean Event Log./DeDftCfg Delete all default settings from BIOS./-Command Name Delete certain command’s default setting.[OEM Uses Only.]/MEUF Update Intel ME ignition firmware./ME Update entire Intel ME region.(WinPE only)Note : Running AFUWIN under command prompt directly will display help message. ExamplesExamples on how to update BIOS using the command prompt are shown infollowing:Save current BIOS ROM to fileAFUWIN /OGet and display ROM ID from BIOS ROM fileAFUWIN /UUpdate main BIOS image onlyAFUWINOrAFUWIN /pUpdate Boot Block onlyAFUWIN /BUpdate NVRAM onlyAFUWIN /NUpdate Embedded Controller Block onlyAFUWIN /EUpdate Embedded Controller Block if newer version is detected AFUWIN /ECUFUpdate 2nd non-critical block onlyAFUWIN /K2Update main BIOS image, Boot Block and NVRAM at onceAFUWIN /P /B /NUpdate whole BIOS ROMAFUWIN /P /B /N /C /E /KUpdate whole BIOS ROM and load current CMOS optimal settings AFUWIN /P /B /N /C /E /K /L0 Update whole BIOS without checking ROM IDAFUWIN /P /B /N /C /E /K /XUpdate whole BIOS with quiet executionAFUWIN /P /B /N /C /E /K /QUpdate whole BIOS in quiet mode and REBOOT quietlyAFUWIN /P /B /N /C /E /K /Q /REBOOTUpdate BootBlock MAC addressAFUWIN /MUpdate whole BIOS and BootBlock MAC addressAFUWIN /P /B /N /C /E /K /M?Update whole BIOS except existing SMBIOS structuresAFUWIN /P /B /N /C /E /K /RUpdate whole BIOS but preserve SMBIOS type 0 and 11AFUWIN /P /B /N /C /E /K /R0 /R11Update dedicate ROM Hole AreaAFUWIN /Hole:NameUpdate dedicate NCB AreaAFUWIN /NCB:NameOutput dedicate ROM Hole FileAFUWIN /HOLEOUTt:NameOutput dedicate NCB FileAFUWIN /NCBOUT:NameCancel Embedded AFU default commands- Below sample cancels B & P commands if BIOS has embedded B & P commands in OFBD.AFUWIN /-B /-PNotice: if /p & /b are set as default command only and /-B /-P commands are issued then P command will still be issued because if none of command is issued then /p will still issue as AFU default.Cancel ALL Embedded AFU default commandsAFUWIN /DeDftCfgMain WindowButtonsClick this button to search for BIOS ROM file from any disk drive.Click this button to starting update BIOS.Click this button to save BIOS ROM image to disk drive.Click this button to exit this program.Function FrameInformation TabThis tab displays system BIOS information for your reference before flashingBIOS.FieldSetup TabThis tab allows you to change the settings for flashing BIOS.FieldFailsafe BIOS after flashing.Select to destroy CMOS checksum after flashing.Destroy CMOSThis is default setting in CMOS Option block.CheksumThis tab displays the updating status.FieldFunctionsTo launch into AFUWIN with GUI mode, you can double-click the executable file icon to open the operating window:Usually, system BIOS information will be displayed first, but you may see a pop-up dialog if the system does not support AMIBIOS update function. After open this program successfully, you can refer to following steps to finish the operation what you need: Saving system BIOS ROM image to file1.Press button to open file dialog box.2.Select path and input a file name.3.Click on OK button to save system BIOS ROM image into specific file.4.Press button to exit this program.Flashing system BIOS with given file1.Press button to search for BIOS ROM image file from any disk driver andload it into memory.2.Switch to Setup Tab to check and change necessary settings.3.Press button to start the operation.4.Progess Tab will be switched automatically and display the programming status.5.After BIOS updated, you can press button to exit this program or systemwill restart automatically if the Restart After Programming option enabled. Error Code ListAppendix B : AFUDOS v3.xx CommandsUsage : AFUDOS /i [/o] [/n] [/p[b][n][c][e]] [/s] [kN] [/c[N]] [/q] [/h] [/t] [/u[ROM File Name]]Following table lists the description of previous version of AFUDOS commands.。

am08模块参数

am08模块参数随着科技的发展,电子元器件的性能与功能越来越强大,而模块作为其中的重要组成部分,其参数设置对于整体性能的影响不容忽视。

本文将针对AM08模块参数进行深入探讨,以期为相关领域的从业者提供有价值的参考。

一、AM08模块简介AM08模块是一款由知名制造商开发的多功能模块,广泛应用于各种电子设备中。

该模块具有高度的集成度和稳定性,可满足多种复杂应用的需求。

了解AM08模块的参数,有助于更好地发挥其性能,提高设备的整体表现。

二、AM08模块参数详解1.工作电压与电流AM08模块的工作电压范围为9V-36V,而工作电流则根据不同型号有所差异。

在实际使用过程中,应确保模块的工作电压与电流在合理范围内,以避免对模块造成损坏。

2.输入与输出接口AM08模块支持多种类型的输入与输出接口,如I2C、SPI、UART 等。

这些接口可实现与其他模块或设备的无缝连接,提高系统的整体性能。

3.工作温度AM08模块的工作温度范围为-40℃-85℃。

在高温环境下使用时,应注意散热问题,以保证模块的正常运行。

4.尺寸与重量AM08模块的尺寸与重量根据不同型号有所差异。

在选择模块时,应充分考虑其安装空间及设备重量限制。

5.保护功能AM08模块具备过流、过压、欠压等保护功能,可在异常情况下自动切断电源,保护设备免受损坏。

三、参数配置注意事项1.正确配置电压与电流:根据设备需求选择合适的电压与电流范围,避免对AM08模块造成过载或欠载。

2.选择合适的接口类型:根据与其他模块或设备的连接需求,选择合适的输入与输出接口类型。

3.注意工作温度范围:在高或低温度环境下使用时,应确保设备散热良好,避免因过热而导致性能下降或损坏。

4.考虑尺寸与重量因素:在满足性能需求的前提下,尽量选择尺寸较小、重量较轻的模块,以便于设备的集成与搬运。

5.利用保护功能:熟悉并充分利用AM08模块的保护功能,确保设备在异常情况下能够得到及时保护。

四、总结通过对AM08模块参数的深入探讨,我们对其性能特点有了更全面的了解。

恩智浦半导体i.MX 8M Mini应用处理器数据手册说明书

恩智浦半导体数据手册:技术数据文件编号:IMXBMMCEC第0.2版,2019年4月MIMX8MM6DVTLZAAMIMX8MM4DVTLZAAMIMX8MM2DVTLZAAMIMX8MM5DVTLZAAMIMX8MM3DVTLZAAMIMX8MM1DVTLZAA适用于消费电子产品的i.MX 8M Mini应用处理器数据手册封装信息塑料封装FCBGA 14 x 14 mm,0.5 mm间距订购信息参见第6页的表21 i.MX 8M Mini简介i.MX 8M Mini应用处理器是能够带来最新视频和音频体验的恩智浦产品,具有最先进的特定媒体功能,采用高性能处理技术,同时优化了功耗。

i.MX 8M Mini系列处理器采用先进的四核Arm® Cortex®-A53内核,运行速度高达1.8 GHz。

一个通用型Cortex®-M4 400 MHz内核处理器用于低功耗处理。

DRAM控制器支持32位/16位LPDDR4、DDR4和DDR3L存储器。

可提供多种音频接口,包括I2S、AC97、TDM和S/PDIF。

提供许多其他接口用于连接外围设备,如USB、PCIe和以太网。

1. i.MX 8M Mini简介 (1)1.1. 功能框图 (5)1.2. 订购信息 (6)2. 模块列表 (8)2.1. 未使用的输入/输出的推荐连接 (12)i.MX 8M Mini简介表1. 特性i.MX 8M Mini简介表1. 特性(续)i.MX 8M Mini简介表1. 特性(续)注意实际功能集取决于产品型号(如表2所述)。

某些特定产品型号可能并未启用某些功能,如显示器和摄像头接口以及连接接口。

i.MX 8M Mini简介1.1 功能框图图1显示了i.MX 8M Mini应用处理器系统的功能模块。

图1. i.MX 8M Mini系统功能框图i.MX 8M Mini简介1.2 订购信息表2所示为本数据手册中包含的可订购样品型号的示例。

HY27US08281A资料