IS61LV 216L中文资料

中英文国家对照表

中英文国家对照表相信大部分Aff跑的offer不仅仅局限于几个熟悉的国家,那当我们遇到不熟悉的国家和地区,或者想知道中文国家名称对应的英文名称,抑或反过来想知道英文国家名称对应的中文名称时,我们就需要到处查找与这有关的资料,这往往消耗掉了我们大量的时间和精力。

现在金橙子海外联属营销网用一个表格集成了大部分数据,包括全球所有国家和地区的中英文、国家代码、以及人口数据。

表格是基于ISO3166标准整理而来,一起来看看。

序号ISO英文名称中文名称人口数据(默认:万)人均GDPE-Packet1AD Andorra安道尔72AE United Arab Em.阿联酋927 3AF Afghanistan阿富汗3,3374AG Antigua andBarbuda安提瓜和巴布达95AI Anguilla安圭拉16AL Albania阿尔巴尼亚290 7AM Armenia亚美尼亚3038AN NetherlandsAntilles荷属安的列斯群岛189AO Angola安哥拉2,583 10AR Argentina阿根廷4,385 11AS American Samoa美属萨摩亚612AT Austria奥地利857序号ISO英文名称中文名称(默认:万)均GDPE-Packet13AU Australia澳大利亚2,431Yes 14AW Aruba阿鲁巴群岛1015AZ Azerbaijan阿塞拜疆98716BA Bosnia波斯尼亚38017BB Barbados巴巴多斯2918BD Bangladesh孟加拉16,29119BE Belgium比利时1,13720BF Burkina Faso布基纳法索1,86321BG Bulgaria保加利亚71022BH Bahrain巴林14023BI Burundi布隆迪1,15524BJ Benin贝宁1,11725BL Saint Barthelemy 圣巴瑟米(法)26BM Bermuda百慕大627BN Brunei文莱4328BO Bolivia玻利维亚1,08929BQ Bonaire SintEustatius Saba荷兰加勒比区30BR Brazil巴西20,957 31BS Bahamas巴哈马3932BT Bhutan不丹7833BV Bouvet Island 布韦岛(挪)序号ISO英文名称中文名称(默认:万)均GDPE-Packet34BW Botswana博茨瓦纳23035BY Belarus白俄罗斯94836BZ Belize伯利兹3737CA Canada加拿大3,629Yes38CC Cocos (Keeling)Islands科科斯群岛039CD The DemocraticRepublic of theCongo刚果民主共和国7,97240CF Central AfricanRepublic中非共和国50051CG Congo刚果47442CH Switzerland瑞士83843CI Côte d'Ivoire科特迪瓦2,325 44CK Cook Islands库克群岛245CL Chile智利1,813 46CM Cameroon喀麦隆2,392 47CN China中国138,232 48CO Colombia哥伦比亚4,865 49CR Costa Rica哥斯达黎加48650CU Cuba古巴1,139 51CV Cape Verde佛得角5352CW Curacao库拉索1653CX Christmas Island圣诞岛054CY Cyprus塞浦路斯118序号ISO英文名称中文名称(默认:万)均GDPE-Packet55CZ Czech捷克1,055 56DE Germany德国8,068 57DJ Djibouti吉布提9058DK Denmark丹麦56959DM Dominica多米尼克760DO Dominican Rep多米尼加1,065 61DZ Algeria阿尔及利亚4,038 62EC Ecuador厄瓜多尔1,639 63EE Estonia爱沙尼亚13164EG Egypt埃及9,338 65EH Western Sahara西撒哈拉5866ER Eritrea厄立特里亚53567ES Spain西班牙4,606 68ET Ethiopia埃塞俄比亚10,185 69EU EU欧盟70FI Finland芬兰55271FJ Fiji斐济9072FK Falkland Islands (Malvinas)福克兰群岛(马尔维纳斯群岛)73FM Micronesia,Federated Statesof密克罗尼西亚联邦1074FO Faroe Islands法罗群岛575FR France法国6,467序号ISO英文名称中文名称(默认:万)均GDPE-Packet76GA Gabon加蓬17677GB Great Britain英国6,511Yes 78GD Grenada格林纳达1179GE Georgia格鲁吉亚39880GF French Guiana法属圭亚那2881GG Guernsey格恩西岛782GH Ghana加纳2,80383GI Gibraltar直布罗陀384GL Greenland格陵兰685GM Gambia冈比亚20586GN Guinea几内亚1,29587GP Guadeloupe瓜德罗普4788GQ Equatorial Guinea赤道几内亚8789GR Greece希腊1,09290GS South Georgia andthe Islands南乔治亚岛091GT Guatemala危地马拉1,667 92GU Guam关岛1793GW Guinea-Bissau几内亚比绍189 94GY Guyana圭亚那7795HK Hong Kong中国香港73596HM Heard Island andMcDonald Islands赫德岛和麦克唐纳群岛97HN Honduras洪都拉斯819序号ISO英文名称中文名称(默认:万)均GDPE-Packet98HR Croatia克罗地亚42399HT Haiti海地1,085 100HU Hungary匈牙利982101ID Indonesia印度尼西亚26,058 102IE Ireland爱尔兰471103IL Israel以色列819104IN India印度132,680105IO British IndianOcean Territory英属印度洋领地106IQ Iraq伊拉克3,755 107IR Iran伊朗8,004 108IS Iceland冰岛33109IT Italy意大利5,980 110JM Jamaica牙买加280 111JO Jordan约旦775 112JP Japan日本12,632 113KE Kenya肯尼亚4,725114KG Kyrgyzstan 吉尔吉斯斯坦603115KH Cambodia柬埔寨1,583 116KI Kiribati基里巴斯11 117KM Comoros科摩罗81118KN Saint Kitts andNevis圣基茨和尼维斯6序号ISO英文名称中文名称(默认:万)均GDPE-Packet119KP DemocraticPeople's Republicof Korea朝鲜2,528120KR South Korea韩国5,050121KV The Republic ofKosovo科索沃180122KW Kuwait科威特401 123KY Cayman Islands开曼群岛6124KZ Kazakhstan哈萨克斯坦1,786 125LA Laos老挝692 126LB Lebanon黎巴嫩599 127LC Saint Lucia圣卢西亚19 128LI Liechtenstein列支敦士登4129LK Sri Lanka斯里兰卡2,081 130LR Liberia利比里亚462 131LS Lesotho莱索托216 132LT Lithuania立陶宛285 133LU Luxembourg卢森堡58 134LV Latvia拉脱维亚196 135LY Libya利比亚633 136MA Moroco摩洛哥3,482 137MC Monaco摩纳哥4138MD Republic ofMoldova摩尔多瓦406139ME Montenegro黑山63序号ISO英文名称中文名称(默认:万)均GDPE-Packet140MG Madagascar马达加斯加2,492 141MH Marshall Islands马绍尔群岛5142MK Republic ofMacedonia马其顿208143ML Mali马里1,813 144MM Myanmar缅甸5,436 145MN Mongolia蒙古301 146MO Macau中国澳门60147MP Northern MarianaIslands北马里亚纳群岛6148MQ Martinique马提尼克40149MR Mauritania毛里塔尼亚417 150MS Montserrat蒙特塞拉特1151MT Malta马耳他42152MU Mauritius毛里求斯128 153MV Maldives马尔代夫37154MW Malawi马拉维1,775 155MX Mexico墨西哥12,863 156MY Malaysia马来西亚3,075 157MZ Mozambique莫桑比克2,875 158NA Namibia纳米比亚251159NC New Caledonia 新喀里多尼亚27160NE Niger尼日尔2,072序号ISO英文名称中文名称(默认:万)均GDPE-Packet161NF Norfolk Island诺福克岛0162NG Nigeria尼日利亚18,699163NI Nicaragua尼加拉瓜615164NL Netherlands荷兰1,698165NO Norway挪威527166NP Nepal尼泊尔2,885167NR Nauru瑙鲁1168NU Niue纽埃0169NZ New Zealand新西兰457Yes 170OM Oman阿曼465171PA Panama巴拿马399172PE Peru秘鲁3,177173PF French Polynesia 法属波利尼西亚29174PG Papua New Guinea 巴布亚新几内亚778175PH Philippines菲律宾10,225 176PK Pakistan巴基斯坦19,283 177PL Poland波兰3,859178PM Saint Pierre andMiquelon圣皮埃尔和密克隆1179PN Pitcairn皮特凯恩0 180PR Puerto Rico波多黎各368 181PS Gaza Strip加沙地带220序号ISO英文名称中文名称(默认:万)均GDPE-Packet182PT Portugal葡萄牙1,030 183PW Palau帕劳2184PY Paraguay巴拉圭673 185QA Qatar卡塔尔229 186RE Reunion留尼旺群岛87187RO Romania罗马尼亚1,937 188RS Serbia塞尔维亚881 189RU Russia俄罗斯14,344 190RW Rwanda卢旺达1,188 191SA Saudi Arabia沙特阿拉伯3,216 192SB Solomon Islands所罗门群岛59193SC Seychelles塞舌尔10194SD Sudan苏丹4,118 195SE Sweden瑞典985 196SG Singapore新加坡570197SH Saint Helena,Ascension andTristan Da Cunha圣赫勒拿,阿森松岛和特里斯坦达库尼亚198SI Slovenia斯洛文尼亚207199SJ Svalbard 斯瓦尔巴特群岛200SK Slovakia斯洛伐克543 201SL Sierra Leone塞拉利昂659 202SM San Marino圣马力诺3序号ISO英文名称中文名称(默认:万)均GDPE-Packet203SN Senegal塞内加尔1,559 204SO Somalia索马里1,108 205SR Suriname苏里南55 206SS South Sudan南苏丹1,273207ST Sao Tome andPrincipe圣多美和普林西比19208SV El Salvador萨尔瓦多615 209SX Sint Maarten荷属圣马丁4210SY Syrian ArabRepublic叙利亚1,856211SZ Swaziland斯威士兰130212TC Turks and CaicosIslands特克斯和凯科斯群岛3213TD Chad乍得1,450 214TG Togo多哥750 215TH Thailand泰国6,815 216TJ Tajikistan塔吉克斯坦867 217TK Tokelau托克劳群岛0218TL East Timor东帝汶121 219TM Turkmenistan土库曼斯坦544 220TN Tunisia突尼斯1,138 221TO Tonga汤加11 222TR Turkey土耳其7,962223TT Trinidad andTobago特里尼达和多巴哥136序号ISO英文名称中文名称(默认:万)均GDPE-Packet224TV Tuvalu图瓦卢1225TW Taiwan中国台湾2,340226TZ Tanzania, UnitedRepublic of坦桑尼亚5,516227UA Ukraine乌克兰4,462 228UG Uganda乌干达4,032229UM United StatesMinor OutlyingIslands美国本土外小岛屿230US USA美国32,412Yes 231UY Uruguay乌拉圭344232UZ Uzbekistan 乌兹别克斯坦3,030233VA Vatican CityState梵蒂冈0234VC Saint Vincent andthe Grenadines圣文森特和格林纳丁斯11235VE Venezuela委内瑞拉3,152236VG British Virginlslands英属维尔京群岛3237VI Virgin Islands维京群岛11 238VN Vietnam越南9,444 239VU Vanuatu瓦努阿图27240WF Wallis and Futuna 瓦利斯群岛和富图纳群1序号ISO英文名称中文名称(默认:万)均GDPE-Packet岛241WS Samoa萨摩亚19 242YE Yemen也门2,748 243YT Mayotte马约特岛25 244ZA South Africa南非5,498 245ZM Zambia赞比亚1,672 246ZW Zimbabwe津巴布韦1,597。

ISSIIS61LV25616AL中文

20

20

25

25

15

15

20

20

单位 mA mA mA mA

电容(1)

符号

参数

条件

最大

CIN

输入电容

VIN=0V

6

COUT

输入/输出电容

VOUT=0V

8

注

1. 这两个参数均在最开始时测得 设计或处理的任何变化都将影响它们的值

单位 pF pF

4

电子发烧友 电子技术论坛 广州周立功单片机发展有限公司 Tel 020 38730976 38730977 Fax 38730925 http //

2

电子发烧友 电子技术论坛 广州周立功单片机发展有限公司 Tel 020 38730976 38730977 Fax 38730925 http //

管脚配置

44 脚 LQFP

读周期变化特性(1) 工作范围内

符号

参数

10

12

单位

最小

最大

最小

最大

tRC tAA tOHA tACE tDOE tHZOE(2) tLZOE(2) tHZCE(2) tLZCE(2) tBA tHZB(2) tLZB(2) tPU tPD 注

读周期时间 地址访问时间 输出保持时间

CE 访问时间 OE 访问时间 OE 到高阻输出 OE 到低阻输出 CE 到高阻输出 CE 低阻输出 LB , UB 访问时间 LB , UB 到高阻输出 LB , UB 到低阻输出 上电时间 掉电时间

其可靠性

3

电子发烧友 电子技术论坛 广州周立功单片机发展有限公司 Tel 020 38730976 38730977 Fax 38730925 http //

ISSI异步SRAM存储芯片IS61LV25616AL功能简介

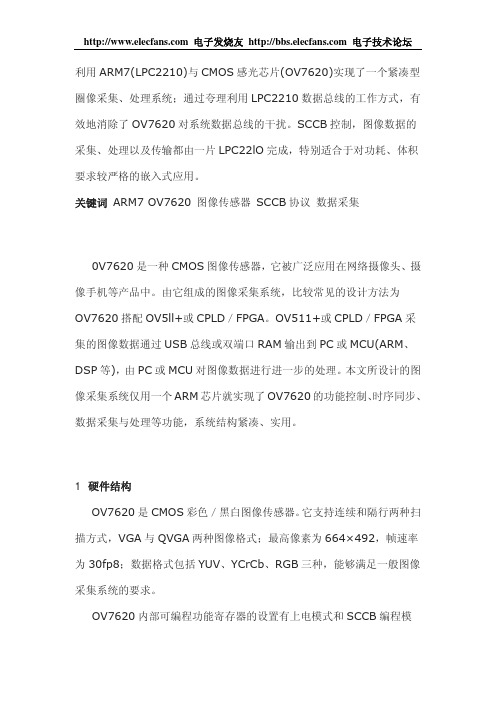

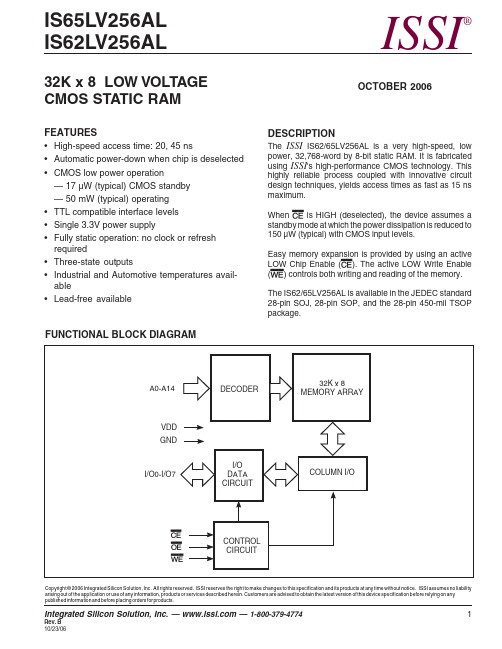

ISSI异步SRAM存储芯片IS61LV25616AL功能简介IS61LV25616AL是ISSI公司的一款容量为256Kx 16bits的且引脚功能彻低兼容的4Mb的异步SRAM。

也是一款大容量且存储时光相对较短的存储器。

对其控制要求相对容易。

由一个高速、4,194,304 位的静态RAM,可组成262,144个字(16位)。

该器件由ISSI的高性能技术创造而成。

将这种高牢靠性的处理技术与创新的设计技术相结合,就产生了高性能和低功耗的IS61LV25616AL器件。

ISSI代理英尚微提供完美的产品解决计划以及技术指导等一体系产品服务。

特性

●高速拜访时光: 10,12ns

●CMOS低功耗工作

●低等待模式功率:小于CMOS 5mA (典型值)的等待

●TTL兼容接口电平●单个3.3V电源

●彻低静态操作:无需时钟和刷新

●三态输出.

●凹凸字节数据控制

●可用的工业级温度

IS61LV25616AL存储器的结构框图

当OE为高电平(不选)时,器件处于等待模式,功耗随着CMOS输入电平-起降低。

芯片使能输入CE和输出访能输入OE可便利实现存储器的扩展。

低电平有效的写使能( WE )控制着存储器的写和读操作。

高字节(UB)和低

第1页共2页。

ARMFLY STM32F103ZE-EK 开发板 说明书

S T M32F103Z E-E K开发板用户手册版本:V1.0安富莱电子开发网W W W.A R M F L Y.C O M1.产品规格简介STM32F103ZE-EK开发板以STM32F103ZET6(LQFP144)为核心。

STM32F103ZE 是ST(意法半导体)公司推出的ARM Crotex-M3产品线中功能最强大的一款CPU。

片内集成512kB Flash、64kB RAM、1个USB、1个CAN、 8个定时器、5个USART、3个ADC、2个DAC、3个SPI、2个I2C、2个I2S、1个SDIO、112个GPIO、FSMC总线(支持NOR,NAND,SRAM)。

CPU主频72MHz,广泛适用于各种应用场合。

本开发板具备丰富的硬件资源,配套的试验例程均提供源代码,文档齐备,非常适合于学习和项目评估。

硬件资源■ 8M晶振作为MCU的时钟,32768晶振用于RTC ■ 1M字节SRAM,16M字节NOR Flash,128M字节NADN Flash■ 2M字节串行Flash,256字节串行EEPROM■ 1个SD/MMC卡座■ 1个CAN2.0A/B接口■ 2个RS232串口■ 1个RS485接口■ 1个USB2.0全速DEVICE接口■ 1个USB2.0全速HOST接口■ 1个100M/10M以太网接口■ I2S音频DAC(24bit,96kHz),1个立体声耳机插座,1个扬声器■ 3.0寸TFT真彩触摸LCD(WQVGA,400x240)■ 1个5向摇杆,1个Reset按钮、1个wakeup按钮、1个自定义按钮 ■ 4个自定义LED,1个电源LED,1个音频LED ■ 1个CR1220电池座■ 1个精密可调电阻连接到ADC输入■ 所有的GPIO引到2.54mm间距焊盘■ 1个DAC引出端子,1个PWM引出端子■ 标准2.54mm间距JTAG插座■ 2个BNC输入端子,集成双通道示波器电路,具备AC/DC切换、输入增益切换开关■ 3种供电方式:USB电缆、外接5V电源、JTAG 调试接口(J-LINK仿真器)■ 1个电源开关,上下电时无需拔插电缆■ 3种启动方式:用户Flash、系统存储器、SRAM ■ 用拨码开关取代跳线帽,避免跳线帽丢失■ 板子规格:14cm x 12cm软件资源■ 提供100多个试验例程■ 提供uCOS_II+ucGUI例程和文档■ 即将展开USB虚拟示波器项目源码■ 即将移植ucLinux (硬件资源已满足要求) ■ 更多的软件资源将在发布标配清单■STM32F103ZE-EK开发板1块■ 3.0寸TFT触摸显示模块1块■1根串口线、1根网线、1根USB电缆■资料光盘1张可选的配件:■60M示波器探头1对■USB转串口线1根2.快速入门2.1.注意事项(1)外接电源必须是5.0V 的直流电源,插头有极性,内正外负。

IS61LV51216(外扩RAM)

Integrated Silicon Solution, Inc. — — 1-800-379-4774

1

Rev. B

03/10/05

IS61LV51216

TRUTH TABLE

Mode Not Selected Output Disabled Read

Write

WE CE OE LB UB

2

Integrated Silicon Solution, Inc. — — 1-800-379-4774

Rev. B

பைடு நூலகம்

03/10/05

IS61LV51216

ISSI ®

PIN CONFIGURATIONS 48-Pin mini BGA (9mmx11mm)

1 23 45 6

I/O DATA CIRCUIT

CE

OE

CONTROL

WE

CIRCUIT

UB

LB

512K x 16 MEMORY ARRAY

COLUMN I/O

Copyright © 2005 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.

IS61LV6416

Copyright © 2003 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.Integrated Silicon Solution, Inc.1Rev. C 10/14/03IS61LV6416IS61LV6416LISSI®FEATURES•High-speed access time: 8, 10, 12 ns •CMOS low power operation — 61LV6416:75 mW (typical) operating current 0.5 mW (typical) standby current — 61LV6416L:65 mW (typical) operating current 50 µW (typical) standby current •TTL compatible interface levels •Single 3.3V power supply•Fully static operation: no clock or refresh required•Three state outputs•Data control for upper and lower bytes •Industrial temperature availableDESCRIPTIONThe ISSI IS61LV6416/IS61LV6416L is a high-speed,1,048,576-bit static RAM organized as 65,536 words by 16bits. It is fabricated using ISSI 's high-performance CMOS technology. This highly reliable process coupled with innovative circuit design techniques, yields access times as fast as 8 ns with low power consumption.When CE is HIGH (deselected), the device assumes a standby mode at which the power dissipation can be reduced down with CMOS input levels.Easy memory expansion is provided by using Chip Enable and Output Enable inputs, CE and OE . The active LOW Write Enable (WE ) controls both writing and reading of the memory. A data byte allows Upper Byte (UB ) and Lower Byte (LB ) access.The IS61LV6416/IS61LV6416L is packaged in the JEDEC standard 44-pin 400-mil SOJ, 44-pin TSOP-II, and 48-pin mini BGA (6mm x 8mm).FUNCTIONAL BLOCK DIAGRAMOCTOBER 200364K x 16 HIGH-SPEED CMOS STATIC RAM WITH 3.3V SUPPL YIS61LV6416IS61LV6416L2Integrated Silicon Solution, Inc.Rev.C 10/14/03ISSI®PIN CONFIGURATIONS 44-Pin SOJ (K)1234567891011121314151617181920212244434241403938373635343332313029282726252423A15A14A13A12A11CE I/O0I/O1I/O2I/O3VDD GND I/O4I/O5I/O6I/O7WE A10A9A8A7NCA0A1A2OE UB LB I/O15I/O14I/O13I/O12GND VDD I/O11I/O10I/O9I/O8NC A3A4A5A6NC1234567891011121314151617181920212244434241403938373635343332313029282726252423A15A14A13A12A11CE I/O0I/O1I/O2I/O3V DD GND I/O4I/O5I/O6I/O7WE A10A9A8A7NCA0A1A2OE UB LB I/O15I/O14I/O13I/O12GND V DD I/O11I/O10I/O9I/O8NC A3A4A5A6NC44-Pin TSOP-II (T)48-Pin mini BGA (6mm x 8mm) (B)PIN DESCRIPTIONSA0-A15Address Inputs I/O0-I/O15Data Inputs/Outputs CE Chip Enable Input OE Output Enable Input WE Write Enable InputLB Lower-byte Control (I/O0-I/O7)UB Upper-byte Control (I/O8-I/O15)NC No Connection V DD Power GNDGround1 2 3 4 5 6A B C D E F G HLB OE A0A1A2NC I/O 8UB A3A4CE I/O 0I/O 9I/O 10A5A6I/O 1I/O 2GND I/O 11NC A7I/O 3V DD V DD I/O 12NC NC I/O 4GND I/O 14I/O 13A14A15I/O 5I/O 6I/O 15NC A12A13WE I/O 7NCA8A9A10A11NCIS61LV6416IS61LV6416LIntegrated Silicon Solution, Inc.3Rev.C 10/14/03ISSI®OPERATING RANGERangeAmbient TemperatureV DD (8,10 ns)V DD (12 ns)Commercial 0°C to +70°C 3.3V+10%,-5% 3.3V ± 10%Industrial–40°C to +85°C3.3V+10%,-5%3.3V ± 10%DC ELECTRICAL CHARACTERISTICS (Over Operating Range)Symbol ParameterTest ConditionsMin.Max.Unit V OH Output HIGH Voltage V DD = Min., I OH = –4.0 mA 2.4—V V OL Output LOW Voltage V DD = Min., I OL = 8.0 mA—0.4V V IH Input HIGH Voltage 2V DD + 0.3V V IL Input LOW Voltage (1)–0.30.8V I LI Input Leakage GND ≤ V IN ≤ V DD–22µA I LOOutput LeakageGND ≤ V OUT ≤ V DD , Outputs Disabled –22µANotes:1.V IL (min.) = –2.0V for pulse width less than 10 ns.ABSOLUTE MAXIMUM RATINGS (1)Symbol ParameterValueUnit V TERM Terminal Voltage with Respect to GND –0.5 to V DD +0.5V T STG Storage Temperature –65 to +150°C P T Power Dissipation1.5W I OUTDC Output Current (LOW)20mANote:1.Stress greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.TRUTH TABLEI/O PINModeWE CE OE LB UB I/O0-I/O7I/O8-I/O15V DD Current Not Selected X H X X X High-Z High-Z I SB 1, I SB 2Output Disabled H L H X X High-Z High-Z I CCX L X H H High-Z High-Z ReadH L L L H D OUT High-Z I CCH L L H L High-Z D OUT H L L L L D OUT D OUT Write L L X L H D IN High-Z I CCL L X H L High-Z D IN LLXLLD IND INIS61LV6416IS61LV6416L4Integrated Silicon Solution, Inc.Rev.C 10/14/03ISSI®CAPACITANCE (1)Symbol Parameter Conditions Max.Unit C IN Input Capacitance V IN = 0V 6pF C OUTInput/Output CapacitanceV OUT = 0V8pFNote:1.Tested initially and after any design or process changes that may affect these parameters.IS61LV6416POWER SUPPLY CHARACTERISTICS (1) (Over Operating Range)-8 ns -10 ns -12 ns Symbol Parameter Test Conditions Min.Max.Min.Max.Min.Max.Unit I CCV DD Dynamic Operating V DD = Max.,Com.—140—120—100mASupply Current I OUT = 0 mA, f = f MAX Ind.—150—130—110typ.(2)—105—95—75I SB 1TTL Standby Current V DD = Max.,Com.—15—15—15mA(TTL Inputs)V IN = V IH or V IL Ind.—20—20—20CE ≥ V IH , f = 0I SB 2CMOS StandbyV DD = Max.,Com.—5—5—5mACurrent (CMOS Inputs)CE ≥ V DD – 0.2V,Ind.—10—10—10V IN ≥ V DD – 0.2V, or typ.(2)—0.5—0.5—0.5V IN ≤ 0.2V, f = 0Note:1.At f = f MAX , address and data inputs are cycling at the maximum frequency, f = 0 means no input lines change.2. Typical values are measured at V DD =3.3V, T A =25o C. Not 100% Tested.IS61LV6416LPOWER SUPPLY CHARACTERISTICS (1) (Over Operating Range)-8 ns -10 ns Symbol Parameter Test Conditions Min.Max.Min.Max.Unit I CCV DD Dynamic Operating V DD = Max.,Com.—100—95mASupply Current I OUT = 0 mA, f = f MAX Ind.—110—105typ.(2)—75—70I SB 1TTL Standby Current V DD = Max.,Com.—15—15mA(TTL Inputs)V IN = V IH or V IL Ind.—20—20CE ≥ V IH , f = 0I SB 2CMOS StandbyV DD = Max.,Com.—1—1mACurrent (CMOS Inputs)CE ≥ V DD – 0.2V,Ind.— 1.5— 1.5V IN ≥ V DD – 0.2V, or typ.(2)—0.05—0.05V IN ≤ 0.2V, f = 0Note:1.At f = f MAX , address and data inputs are cycling at the maximum frequency, f = 0 means no input lines change.2. Typical values are measured at V DD =3.3V, T A =25o C. Not 100% Tested.IS61LV6416IS61LV6416LIntegrated Silicon Solution, Inc.5Rev.C 10/14/03ISSI®READ CYCLE SWITCHING CHARACTERISTICS (1) (Over Operating Range)-8 ns -10 ns -12 ns SymbolParameter Min.Max.Min.Max.Min.Max.Unit t RC Read Cycle Time 8—10—12—ns t AA Address Access Time —8—10—12ns t OHA Output Hold Time 3—3—3—ns t ACE CE Access Time —8—10—12ns t DOE OE Access Time —5—5—6ns t HZOE (2)OE to High-Z Output —5—5—6ns t LZOE (2)OE to Low-Z Output 0—0—0—ns t HZCE (2CE to High-Z Output 040506ns t LZCE (2)CE to Low-Z Output 3—3—3—ns t BA LB , UB Access Time —6—6—6ns t HZB LB , UB to High-Z Output 040506ns t LZBLB , UB to Low-Z Output———nsNotes:1.Test conditions assume signal transition times of 3 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V and output loading specified in Figure 1a.2.Tested with the load in Figure 1b. Transition is measured ±500 mV from steady-state voltage. Not 100% tested.3.Not 100% tested.AC TEST CONDITIONSParameterUnit Input Pulse Level0V to 3.0V Input Rise and Fall Times 3 ns Input and Output Timing 1.5V and Reference Level Output LoadSee Figures 1a and 1bAC TEST LOADSFigure 1a.Figure 1b.IS61LV6416IS61LV6416L6Integrated Silicon Solution, Inc.Rev.C 10/14/03ISSI®(1,3)AC WAVEFORMSREAD CYCLE NO. 1(1,2) (Address Controlled) (CS = OE = V IL , UB or LB = V IL )Notes:1.WE is HIGH for a Read Cycle.2.The device is continuously selected. OE , CE , UB , or LB = V IL .3.Address is valid prior to or coincident with CE LOW transition.IS61LV6416IS61LV6416LIntegrated Silicon Solution, Inc.7Rev.C 10/14/03ISSI®WRITE CYCLE SWITCHING CHARACTERISTICS (1,3) (Over Operating Range)-8 ns -10 ns -12 ns SymbolParameter Min.Max.Min.Max.Min.Max.Unit t WC Write Cycle Time 8—10—12—ns t SCE CE to Write End 6—8—9—ns t AW Address Setup Time 8—8—9—ns to Write Endt HA Address Hold from Write End 0—0—0—ns t SA Address Setup Time 0—0—0—ns t PBW LB , UB Valid to End of Write 7—8—9—ns t PWE 1/t PWE 2WE Pulse Width (OE = HIGH/LOW)6—8—9—ns t SD Data Setup to Write End 6—6—6—ns t HD Data Hold from Write End 0—0—0—ns t HZWE (2)WE LOW to High-Z Output —4—5—6ns t LZWE (2)WE HIGH to Low-Z Output3—3—3—nsNotes:1.Test conditions assume signal transition times of 3 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V and output loading specified in Figure 1a.2.Tested with the load in Figure 1b. Transition is measured ±500 mV from steady-state voltage. Not 100% tested.3.The internal write time is defined by the overlap of CE LOW and UB or LB , and WE LOW. All signals must be in valid states to initiate a Write, but any one can go inactive to terminate the Write. The Data Input Setup and Hold timing are referenced to the rising or falling edge of the signal that terminates the write.IS61LV6416IS61LV6416L8Integrated Silicon Solution, Inc.Rev.C 10/14/03ISSI®WRITE CYCLE NO. 1(1,2) (CE Controlled, OE = HIGH or LOW)IS61LV6416IS61LV6416LIntegrated Silicon Solution, Inc.9Rev.C 10/14/03ISSI®WRITE CYCLE NO. 3 (WE Controlled: OE is LOW During Write Cycle)WRITE CYCLE NO. 2(1) (WE Controlled, OE = HIGH during Write Cycle)IS61LV6416IS61LV6416L10Integrated Silicon Solution, Inc.Rev.C 10/14/03ISSI®WRITE CYCLE NO. 4 (LB , UB Controlled, Back-to-Back Write)(1,3)1.The internal Write time is defined by the overlap of CE = LOW, UB and/or LB = LOW, and WE = LOW. All signals must be in valid states to initiate a Write, but any can be deasserted to terminate the Write. The t SA , t HA , t SD , and t HD timing is referenced to the rising or falling edge of the signal that terminates the Write.2.Tested with OE HIGH for a minimum of 4 ns before WE = LOW to place the I/O in a HIGH-Z state.3.WE may be held LOW across many address cycles and the LB , UB pins can be used to control the Write function.IS61LV6416IS61LV6416LISSI®DATA RETENTION WAVEFORM (CE Controlled)DATA RETENTION SWITCHING CHARACTERISTICSSymbolParameterTest ConditionOptions Min.Typ.(1)Max.Unit V DRV DD for Data Retention See Data Retention Waveform 2.0— 3.6V I DRData Retention Current V DD = 2.0V, CE ≥ V DD – 0.2V IS61LV6416—0.510mA IS61LV6416L—0.05 1.5t SDR Data Retention Setup Time See Data Retention Waveform 0——ns t RDRRecovery TimeSee Data Retention Waveformt RC——nsNote 1: Typical values are measured at V DD = 3.0V, T A = 25OC and not 100% tested.IS61LV6416IS61LV6416L ISSI®IS61LV6416ORDERING INFORMATIONSpeed (ns)Order Part No.Package Temperature Range 8IS61LV6416-8T Plastic TSOP Commercial (0°C to +70°C )8IS61LV6416-8BI mini BGA(6mm x 8mm)Industrial (-40°C to +85°C )8IS61LV6416-8TI Plastic TSOP Industrial (-40°C to +85°C )10IS61LV6416-10T Plastic TSOP Commercial (0°C to +70°C )10IS61LV6416-10B mini BGA(6mm x 8mm)Commercial (0°C to +70°C )10IS61LV6416-10K400-mil Plastic SOJ Commercial (0°C to +70°C )10IS61LV6416-10BI mini BGA(6mm x 8mm)Industrial (-40°C to +85°C )10IS61LV6416-10TI Plastic TSOP Industrial (-40°C to +85°C )10IS61LV6416-10KI400-mil Plastic SOJ Industrial (-40°C to +85°C )12IS61LV6416-12B mini BGA(6mm x 8mm)Commercial (0°C to +70°C )12IS61LV6416-12T Plastic TSOP Commercial (0°C to +70°C )12IS61LV6416-12K400-mil Plastic SOJ Commercial (0°C to +70°C )12IS61LV6416-12BI mini BGA(6mm x 8mm)Industrial (-40°C to +85°C )12IS61LV6416-12TI Plastic TSOP Industrial (-40°C to +85°C )12IS61LV6416-12KI400-mil Plastic SOJ Industrial (-40°C to +85°C )IS61LV6416LORDERING INFORMATIONSpeed (ns)Order Part No.Package Temperature Range 8IS61LV6416L-8T Plastic TSOP Commercial (0°C to +70°C )8IS61LV6416L-8BI mini BGA(6mm x 8mm)Industrial (-40°C to +85°C )8IS61LV6416L-8TI Plastic TSOP Industrial (-40°C to +85°C )8IS61LV6416L-8KI400-mil Plastic SOJ Industrial (-40°C to +85°C )10IS61LV6416L-10T Plastic TSOP Commercial (0°C to +70°C )10IS61LV6416L-10BI mini BGA(6mm x 8mm)Industrial (-40°C to +85°C )10IS61LV6416L-10TI Plastic TSOP Industrial (-40°C to +85°C )10IS61LV6416L-10KI400-mil Plastic SOJ Industrial (-40°C to +85°C )PACKAGING INFORMATIONISSI®Copyright © 2003 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time Mini Ball Grid ArrayPackage Code: B (48-pin)PACKAGING INFORMATIONISSI®Copyright © 2002 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time K-400 mil SOJ PACKAGE OUTLINEPACKAGING INFORMATION ISSI®Copyright © 2002 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any timePACKAGING INFORMATIONISSI®Copyright © 2003 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any timePlastic TSOPPackage Code: T (Type II)。

IS64WV102416BLL中文资料

48 A5 47 A6 46 A7 45 A8 44 OE 43 UB 42 LB 41 I/O15 40 I/O14 39 I/O13 38 I/O12 37 GND 36 VDD 35 I/O11 34 I/O10 33 I/O9 32 I/O8 31 NC 30 A9 29 A10 28 A11 27 A12 26 A13 25 A14

Integrated Silicon Solution, Inc. — — 1-800-379-4774

1

Rev.102416ALL IS61WV102416BLL IS64WV102416BLL

48-pin mini BGA (9mmx11mm)

The device is packaged in the JEDEC standard 48-pin TSOP Type I and 48-pin Mini BGA (9mm x 11mm).

A0-A19

DECODER

1024K x 16 MEMORY ARRAY

VDD GND

I/O0-I/O7 Lower Byte

1 23 45 6

A

LB

OE

A0

A1

A2

NC

B

I/O8

UB

A3

A4

CE

I/O0

C

I/O9 I/O10 A5

IS61S6432-166PQ中文资料

IS61S6432ISSI®ISSI reserves the right to make changes to its products at any time without notice in order to improve design and supply the best possible product. We assume no responsibility for any errors which may appear in this publication. © Copyright 2001, Integrated Silicon Solution, Inc.FEATURES•Internal self-timed write cycle•Individual Byte Write Control and Global Write •Clock controlled, registered address, data and control•Pentium™ or linear burst sequence control using MODE input•Three chip enables for simple depth expansion and address pipelining•Common data inputs and data outputs •Power-down control by ZZ input•JEDEC 100-Pin TQFP and PQFP package •Single +3.3V power supply•Two Clock enables and one Clock disable to eliminate multiple bank bus contention •Control pins mode upon power-up:– MODE in interleave burst mode – ZZ in normal operation modeThese control pins can be connected to GNDQ or VCCQ to alter their power-up state •Industrial temperature availableDESCRIPTIONThe ISSI IS61S6432 is a high-speed, low-power synchronous static RAM designed to provide a burstable,high-performance, secondary cache for the Pentium™,680X0™, and PowerPC™ microprocessors. It is organized as 65,536 words by 32 bits, fabricated with ISSI 's advanced CMOS technology. The device integrates a 2-bit burst counter, high-speed SRAM core, and high-drive capability outputs into a single monolithic circuit. All synchronous inputs pass through registers controlled by a positive-edge-triggered single clock input.Write cycles are internally self-timed and are initiated by the rising edge of the clock input. Write cycles can be from one to four bytes wide as controlled by the write control inputs.Separate byte enables allow individual bytes to be written.BW1 controls DQ1-DQ8, BW2 controls DQ9-DQ16, BW3controls DQ17-DQ24, BW4 controls DQ25-DQ32,conditioned by BWE being LOW. A LOW on GW input would cause all bytes to be written.Bursts can be initiated with either ADSP (Address Status Processor) or ADSC (Address Status Cache Controller)input pins. Subsequent burst addresses can be generated internally by the IS61S6432 and controlled by the ADV (burst address advance) input pin.Asynchronous signals include output enable (OE ), sleep mode input (ZZ), clock (CLK) and burst mode input (MODE).A HIGH input on the ZZ pin puts the SRAM in the power-down state. When ZZ is pulled LOW (or no connect), the SRAM normally operates after three cycles of the wake-up period. A LOW input, i.e., GND Q , on MODE pin selects LINEAR Burst. A V CCQ (or no connect) on MODE pin selects INTERLEAVED Burst.64K x 32 SYNCHRONOUS PIPELINE STATIC RAMJUNE 2001FAST ACCESS TIME1.ADVANCE INFORMATION ONLY.元器件交易网元器件交易网IS61S6432ISSI®BLOCK DIAGRAMPB Integrated Silicon Solution, Inc. • 1-800-379-4774Rev.BIS61S6432ISSI®PIN CONFIGURATION100-Pin TQFP and PQFP (Top View)PIN DESCRIPTIONSA0-A15Address InputsCLK ClockADSP Processor Address Status ADSC Controller Address StatusADV Burst Address AdvanceBW1-BW4Synchronous Byte Write Enable BWE Byte Write EnableGW Global Write EnableCE1, CE2, CE3Synchronous Chip Enable OE Output EnableDQ1-DQ32Data Input/OutputZZ Sleep ModeMODE Burst Sequence ModeV CC+3.3V Power SupplyGND GroundV CCQ Isolated Output Buffer Supply: +3.3V GND Q Isolated Output Buffer GroundNC No Connect元器件交易网元器件交易网IS61S6432ISSI®TRUTH TABLEAddressOperation Used CE1CE2CE3ADSP ADSC ADV WRITE OE DQ Deselected, Power-down None H X X X L X X X High-Z Deselected, Power-down None L L X L X X X X High-Z Deselected, Power-down None L X H L X X X X High-Z Deselected, Power-down None L L X H L X X X High-Z Deselected, Power-down None L X H H L X X X High-Z Read Cycle, Begin Burst External L H L L X X X L Q Read Cycle, Begin Burst External L H L L X X X H High-Z Write Cycle, Begin Burst External L H L H L X L X D Read Cycle, Begin Burst External L H L H L X H L Q Read Cycle, Begin Burst External L H L H L X H H High-Z Read Cycle, Continue Burst Next X X X H H L H L Q Read Cycle, Continue Burst Next X X X H H L H H High-Z Read Cycle, Continue Burst Next H X X X H L H L Q Read Cycle, Continue Burst Next H X X X H L H H High-Z Write Cycle, Continue Burst Next X X X H H L L X D Write Cycle, Continue Burst Next H X X X H L L X D Read Cycle, Suspend Burst Current X X X H H H H L Q Read Cycle, Suspend Burst Current X X X H H H H H High-Z Read Cycle, Suspend Burst Current H X X X H H H L Q Read Cycle, Suspend Burst Current H X X X H H H H High-Z Write Cycle, Suspend Burst Current X X X H H H L X D Write Cycle, Suspend Burst Current H X X X H H L X D Notes:1.All inputs except OE must meet setup and hold times for the Low-to-High transition of clock (CLK).2.Wait states are inserted by suspending burst.3."X" means don't care. WRITE=L means any one or more byte write enable signals (BW1-BW4) and BWE are LOW or GW isLOW. WRITE=H means all byte write enable signals are HIGH.4.For a Write operation following a Read operation, OE must be HIGH before the input data required setup time and held HIGHthroughout the input data hold time.5.ADSP LOW always initiates an internal READ at the Low-to-High edge of clock. A WRITE is performed by setting one ormore byte write enable signals and BWE LOW or GW LOW for the subsequent L-H edge of clock.PARTIAL TRUTH TABLEFunction GW BWE BW1BW2BW3BW4READ H H X X X XREAD H X H H H HWRITE Byte 1H L L H H HWRITE All Bytes X L L L L LWRITE All Bytes L X X X X XPB Integrated Silicon Solution, Inc. • 1-800-379-4774Rev.BIS61S6432ISSI®INTERLEAVED BURST ADDRESS TABLE (MODE = V CCQ or No Connect)External Address1st Burst Address2nd Burst Address3rd Burst AddressA1A0A1A0A1A0A1A000011011010011101011000111100100ABSOLUTE MAXIMUM RATINGS (1,2,3)Symbol ParameterValue Unit T BIAS Temperature Under Bias –40 to +85°C T STG Storage Temperature –55 to +150°C P D Power Dissipation1.8W I OUTOutput Current (per I/O)100mA V IN , V OUT Voltage Relative to GND for I/O Pins–0.5 to V CCQ + 0.3V V INVoltage Relative to GND for for Address and Control Inputs–0.5 to 5.5VNotes:1.Stress greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.2. This device contains circuity to protect the inputs against damage due to high static voltages or electric fields; however, precautions may be taken to avoid application of any voltage higher than maximum rated voltages to this high-impedance circuit.3. This device contains circuitry that will ensure the output devices are in High-Z at power up.LINEAR BURST ADDRESS TABLE (MODE = GND Q )OPERATING RANGERangeAmbient TemperatureV CCCommercial 0°C to +70°C 3.3V +10%, –5%Industrial–40°C to +85°C3.3V +10%, –5%元器件交易网PB Integrated Silicon Solution, Inc. • 1-800-379-4774Rev.B IS61S6432ISSI®POWER SUPPLY CHARACTERISTICS (Operating Range)1.ADVANCE INFORMATION ONLY.DC ELECTRICAL CHARACTERISTICS (1,2) (Over Operating Range)Symbol Parameter Test Conditions Min.Max.UnitV OH Output HIGH Voltage I OH = –5.0 mA 2.4—V V OL Output LOW Voltage I OL = 5.0 mA—0.4V V IH Input HIGH Voltage 2.0V CCQ + 0.3V V IL Input LOW Voltage –0.30.8V I LI Input Leakage Current GND - V IN - V CCQ (2)Com.–55µA Ind.–1010I LOOutput Leakage CurrentGND - V OUT - V CCQ , OE = V IHCom.–55µAInd.–1010Notes:1.MODE pin have an internal pull-up. ZZ pin has an internal pull-down. These pins may be a No Connect,tied to GND,or tied to V CCQ .2.MODE pin should be tied to Vcc or GND. They exhibit ±30 µA maximum leakage current when tied to - GND + 0.2V or • Vcc – 0.2V.-5-6-7-8Symbol Parameter Test ConditionsMin.Max.Min.Max.Min.Max.Min.Max.Unit I CCAC Operating Device Selected,Com.—175—165—150—140mASupply CurrentAll Inputs = V IL or V IH Ind.—185—175—160—150OE = V IH , Cycle Time • t KC min.I SBStandby Current Device Deselected,Com.—25—25—25—25mAV CC = Max.,Ind.—35—35—35—35CLK Cycle Time • t KC min.I ZZ Power-Down ZZ = V CCQ , CLK Running Com.—5—5—5—5mAMode CurrentAll Inputs - GND + 0.2V Ind.—10—10—10—10or • V CC – 0.2V元器件交易网IS61S6432ISSI®CAPACITANCE (1,2)Symbol Parameter Conditions Max.Unit C IN Input Capacitance V IN = 0V 6pF C OUTInput/Output CapacitanceV OUT = 0V8pFNotes:1.Tested initially and after any design or process changes that may affect these parameters.2.Test conditions: T A = 25°C, f = 1 MHz, Vcc =3.3V.AC TEST CONDITIONSParameterUnit Input Pulse Level0V to 3.0V Input Rise and Fall Times 1.5 ns Input and Output Timing 1.5V and Reference Level Output LoadSee Figures 1 and 2Figure 1Figure 2AC TEST LOADS元器件交易网元器件交易网IS61S6432ISSI®READ CYCLE SWITCHING CHARACTERISTICS (Over Operating Range)1.ADVANCE INFORMATION ONLY.2.Guaranteed but not 100% tested. This parameter is periodically sampled.3.Tested with load in Figure 2.4.Configuration signal MODE is static and must not change during normal operation.PB Integrated Silicon Solution, Inc. • 1-800-379-4774Rev.B元器件交易网IS61S6432ISSI®READ CYCLE SWITCHING CHARACTERISTICS (Over Operating Range) (Continued)-5-6-7-8 Symbol Parameter Min.Max.Min.Max.Min.Max.Min.Max Unitt KC Cycle Time10—12—13—15—nst KH Clock High Time 3.5—4—6—6—nst KL Clock Low Time 3.5—4—6—6—nst KQ Clock Access Time—5—6—7—8nst KQX(1)Clock High to Output Invalid 1.5— 1.5—2—2—nst KQLZ(1,2)Clock High to Output Low-Z0—0—0—0—nst KQHZ(1,2)Clock High to Output High-Z 1.56 1.562626nst OEQ Output Enable to Output Valid—5—6—6—6nst OEQX(1)Output Disable to Output Invalid0—0—0—0—nst OELZ(1,2)Output Enable to Output Low-Z0—0—0—0—nst OEHZ(1,2)Output Disable to Output High-Z—4—5—6—6nst AS Address Setup Time 2.5— 2.5— 2.5— 2.5—nst SS Address Status Setup Time 2.5— 2.5— 2.5— 2.5—nst WS Write Setup Time 2.5— 2.5— 2.5— 2.5—nst CES Chip Enable Setup Time 2.5— 2.5— 2.5— 2.5—nst AVS Address Advance Setup Time 2.5— 2.5— 2.5— 2.5—nst AH Address Hold Time0.5—0.5—0.5—0.5—nst SH Address Status Hold Time0.5—0.5—0.5—0.5—nst WH Write Hold Time0.5—0.5—0.5—0.5—nst CEH Chip Enable Hold Time0.5—0.5—0.5—0.5—nst AVH Address Advance Hold Time0.5—0.5—0.5—0.5—nst CFG(3)Configuration Setup35—45—66.7—80—nsNotes:1.Guaranteed but not 100% tested. This parameter is periodically sampled.2.Tested with load in Figure 2.3.Configuration signal MODE is static and must not change during normal operation.元器件交易网IS61S6432ISSI®READ CYCLE TIMING: PIPELINEPB Integrated Silicon Solution, Inc. • 1-800-379-4774Rev.BWRITE CYCLE SWITCHING CHARACTERISTICS (Over Operating Range)-5-6-7-8 Symbol Parameter Min.Max.Min.Max.Min.Max.Min.Max.Unit t KC Cycle Time10—12—13—15—ns t KH Clock High Time 3.5—4—6—6—ns t KL Clock Low Time 3.5—4—6—6—ns t AS Address Setup Time 2.5— 2.5— 2.5— 2.5—ns t SS Address Status Setup Time 2.5— 2.5— 2.5— 2.5—ns t WS Write Setup Time 2.5— 2.5— 2.5— 2.5—ns t DS Data In Setup Time 2.5— 2.5— 2.5— 2.5—ns t CES Chip Enable Setup Time 2.5— 2.5— 2.5— 2.5—ns t AVS Address Advance Setup Time 2.5— 2.5— 2.5— 2.5—ns t AH Address Hold Time0.5—0.5—0.5—0.5—ns t SH Address Status Hold Time0.5—0.5—0.5—0.5—ns t DH Data In Hold Time0.5—0.5—0.5—0.5—ns t WH Write Hold Time0.5—0.5—0.5—0.5—ns t CEH Chip Enable Hold Time0.5—0.5—0.5—0.5—ns t AVH Address Advance Hold Time0.5—0.5—0.5—0.5—ns t CFG(2)Configuration Setup35—45—52—60—ns Note:1.ADVANCE INFORMATION ONLY.2. Configuration signal MODE is static and must not change during normal operation.WRITE CYCLE TIMINGPB Integrated Silicon Solution, Inc. • 1-800-379-4774Rev.BREAD/WRITE CYCLE SWITCHING CHARACTERISTICS (Over Operating Range)1.ADVANCE INFORMATION ONLY.2.Guaranteed but not 100% tested. This parameter is periodically sampled.3.Tested with load in Figure 2.4.Configuration signal MODE is static and must not change during normal operation.READ/WRITE CYCLE SWITCHING CHARACTERISTICS (Over Operating Range) (Continued)-5-6-7-8 Symbol Parameter Min.Max.Min.Max.Min.Max.Min.Max.Unit t KC Cycle Time10—12—13—15—ns t KH Clock High Time 3.5—4—6—6—ns t KL Clock Low Time 3.5—4—6—6—ns t KQ Clock Access Time—5—6—7—8ns t KQX(1)Clock High to Output Invalid 1.5— 1.5—2—2—ns t KQLZ(1,2)Clock High to Output Low-Z0—0—0—0—ns t KQHZ(1,2)Clock High to Output High-Z 1.56 1.562626ns t OEQ Output Enable to Output Valid—5—6—6—6ns t OEQX(1)Output Disable to Output Invalid0—0—0—0—ns t OELZ(1,2)Output Enable to Output Low-Z0—0—0—0—ns t OEHZ(1,2)Output Disable to Output High-Z—4—5—6—6ns t AS Address Setup Time 2.5— 2.5— 2.5— 2.5—ns t SS Address Status Setup Time 2.5— 2.5— 2.5— 2.5—ns t WS Write Setup Time 2.5— 2.5— 2.5— 2.5—ns t CES Chip Enable Setup Time 2.5— 2.5— 2.5— 2.5—ns t AH Address Hold Time0.5—0.5—0.5—0.5—ns t SH Address Status Hold Time0.5—0.5—0.5—0.5—ns t WH Write Hold Time0.5—0.5—0.5—0.5—ns t CEH Chip Enable Hold Time0.5—0.5—0.5—0.5—ns t CFG(3)Configuration Setup35—45—52—60—ns Notes:1.Guaranteed but not 100% tested. This parameter is periodically sampled.2.Tested with load in Figure 2.3.Configuration signal MODE is static and must not change during normal operation.PB Integrated Silicon Solution, Inc. • 1-800-379-4774Rev.BREAD/WRITE CYCLE TIMING: PIPELINESNOOZE AND RECOVERY CYCLE SWITCHING CHARACTERISTICS(1)(Over Operating Range)1.Configuration signal MODE is static and must not change during normal operation.2.ADVANCE INFORMATION ONLY.3.Guaranteed but not 100% tested. This parameter is periodically sampled.4.Tested with load in Figure 2.5.The assertion of ZZ allows the SRAM to enter a lower power state than when deselected within the time specified. Dataretention is guaranteed when ZZ is asserted and clock remains active.6.ADSC and ADSP must not be asserted for at least two cycles after leaving ZZ state.PB Integrated Silicon Solution, Inc. • 1-800-379-4774Rev.BSNOOZE AND RECOVERY CYCLE SWITCHING CHARACTERISTICS(1)(Over Operating Range) (Continued)-5-6-7-8 Symbol Parameter Min.Max.Min.Max.Min.Max.Min.Max.Unit t KC Cycle Time10—12—13—15—ns t KH Clock High Time 3.5—4—6—6—ns t KL Clock Low Time 3.5—4—6—6—ns t KQ Clock Access Time—5—6—7—8ns t KQX(2)Clock High to Output Invalid 1.5— 1.5—2—2—ns t KQLZ(2,3)Clock High to Output Low-Z0—0—0—0—ns t KQHZ(2,3)Clock High to Output High-Z 1.56 1.562626ns t OEQ Output Enable to Output Valid—5—6—6—6ns t OEQX(2)Output Disable to Output Invalid0—0—0—0—ns t OELZ(2,3)Output Enable to Output Low-Z0—0—0—0—ns t OEHZ(2,3)Output Disable to Output High-Z—4—5—6—6ns t AS Address Setup Time 2.5— 2.5— 2.5— 2.5—ns t SS Address Status Setup Time 2.5— 2.5— 2.5— 2.5—ns t CES Chip Enable Setup Time 2.5— 2.5— 2.5— 2.5—ns t AH Address Hold Time 2.5— 2.5— 2.5— 2.5—ns t SH Address Status Hold Time 2.5— 2.5— 2.5— 2.5—ns t CEH Chip Enable Hold Time 2.5— 2.5— 2.5— 2.5—ns t ZZS(4)ZZ Standby2—2—2—2—cyc t ZZREC(5)ZZ Recovery2—2—2—2—cyc Notes:1.Configuration signal MODE is static and must not change during normal operation.2.Guaranteed but not 100% tested. This parameter is periodically sampled.3.Tested with load in Figure 2.4.The assertion of ZZ allows the SRAM to enter a lower power state than when deselected within the time specified. Dataretention is guaranteed when ZZ is asserted and clock remains active.5.ADSC and ADSP must not be asserted for at least two cycles after leaving ZZ state.SNOOZE AND RECOVERY CYCLE TIMINGPB Integrated Silicon Solution, Inc. • 1-800-379-4774Rev.BORDERING INFORMATIONCommercial Range: 0°C to +70°CFrequency (MHz)Order Part NumberPackage 200IS61S6432-200TQ TQFP IS61S6432-200PQ PQFP 166IS61S6432-166TQ TQFP IS61S6432-166PQ PQFP 133IS61S6432-133TQ TQFP IS61S6432-133PQ PQFP 117IS61S6432-117TQ TQFP IS61S6432-117PQ PQFP 100IS61S6432-5TQ TQFP IS61S6432-5PQ PQFP 83IS61S6432-6TQ TQFP IS61S6432-6PQ PQFP 75IS61S6432-7TQ TQFP IS61S6432-7PQ PQFP 66IS61S6432-8TQ TQFP IS61S6432-8PQPQFPNOTICEIntegrated Silicon Solution, Inc., reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. Integrated Silicon Solution, Inc. assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contained herein reflect representative operating parameters, and may vary depending upon a user's specific application. While the information in this publication has been carefully checked, Integrated Silicon Solution, Inc.shall not be liable for any damages arising as a result of any error or omission.Integrated Silicon Solution, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless Integrated Silicon Solution, Inc. receives written assurances, to its satisfaction, that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; and (c) potential liability of Integrated Silicon Solution, Inc. is adequately protected under the circumstances.Copyright 1998 Integrated Silicon Solution, Inc.Reproduction in whole or in part, without the prior written consent of Integrated Silicon Solution, Inc., is prohibited.ORDERING INFORMATIONIndustrial Range: –40°C to +85°CFrequency (MHz)Order Part Number Package 117IS61S6432-117TQI TQFP IS61S6432-117PQI PQFP 100IS61S6432-5TQI TQFP IS61S6432-5PQI PQFP 83IS61S6432-6TQI TQFP IS61S6432-6PQI PQFP 75IS61S6432-7TQI TQFP IS61S6432-7PQI PQFP 66IS61S6432-8TQI TQFP IS61S6432-8PQIPQFPISSI®Integrated Silicon Solution, Inc.2231 Lawson Lane Santa Clara, CA 95054Tel: 1-800-379-4774Fax: (408) 588-0806E-mail: sales@。

IS64WV12816BLL中文资料

IS61WV12816BLL®2Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev. C ISSI®IS61WV12816BLL IS64WV12816BLL1234567891011121314151617181920212244434241403938373635343332313029282726252423A4A3A2A1A0CE I/O0I/O1I/O2I/O3V DD GND I/O4I/O5I/O6I/O7WE A16A15A14A13A12A5A6A7OE UB LB I/O15I/O14I/O13I/O12GND V DD I/O11I/O10I/O 9I/O8NC A8A 9A10A11NC44-Pin TSOP (Type II) (T)PIN DESCRIPTIONSA0-A16Address Inputs I/O0-I/O15Data Inputs/Outputs CE Chip Enable Input OE Output Enable Input WE Write Enable InputLB Lower-byte Control (I/O0-I/O7)UB Upper-byte Control (I/O8-I/O15)NC No Connection V DD Power GNDGroundTRUTH TABL EI/O PINModeWE CE OE LB UB I/O0-I/O7I/O8-I/O15V DD Current Not Selected X H X X X High-Z High-Z I SB 1, I SB 2Output Disabled H L H X X High-Z High-Z I CCX L X H H High-Z High-Z ReadH L L L H D OUT High-Z I CCH L L H L High-Z D OUT H L L L L D OUT D OUT Write L L X L H D IN High-Z I CCL L X H L High-Z D IN LLXLLD IND INPIN CONFIGURATIONISSI®IS61WV12816BLL IS64WV12816BLLPIN DESCRIPTIONSA0-A16Address Inputs I/O0-I/O15Data Inputs/Outputs CEChip Enable Input OE Output Enable Input WE Write Enable InputLB Lower-byte Control (I/O0-I/O7)UB Upper-byte Control (I/O8-I/O15)NC No Connection V DD Power GNDGround48-Pin mini BGA (B)PIN CONFIGURATION1 2 3 4 5 6A B C D E F G HLB OE A0A1A2NC I/O 8UB A3A4CE I/O 0I/O 9I/O 10A5A6I/O 1I/O 2GND I/O 11NC A7I/O 3V DD V DD I/O 12NC A16I/O 4GND I/O 14I/O 13A14A15I/O 5I/O 6I/O 15NC A12A13WE I/O 7NCA8A 9A10A11NC4Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev. C ISSI®IS61WV12816BLL IS64WV12816BLLOPERATING RANGE (V DD )Range Ambient TemperatureV DD (15 n S )V DD (12 n S )Industrial –40°C to +85°C 2.5V-3.6V 3.3V + 10%Automotive–40°C to +125°C2.5V-3.6VABSOLUTE MAXIMUM RATINGS (1)Symbol ParameterValue Unit V DD Power Supply Voltage Relative to GND –0.5 to 4.0V V V TERM Terminal Voltage with Respect to GND –0.5 to V DD + 0.5V T STG Storage Temperature –65 to + 150°C P T Power Dissipation1.0WNote:1. Stress greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the opera-tional sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.DC ELECTRICAL CHARACTERISTICS (Over Operating Range)V DD = 2.5V-3.6VSymbol ParameterTest ConditionsMin.Max.Unit V OH Output HIGH Voltage V DD = Min., I OH = –1.0 mA 1.8—V V OL Output LOW Voltage V DD = Min., I OL = 1.0 mA—0.4V V IH Input HIGH Voltage 2.0V DD + 0.3V V IL Input LOW Voltage (1)–0.30.4V I LI Input Leakage GND ≤ V IN ≤ V DD–11µA I LO Output LeakageGND ≤ V OUT ≤ V DD , Outputs Disabled–11µANote:1.V IL (min.) = –0.3V DC; V IL (min.) = –2.0V AC (pulse width - 2.0 ns). Not 100% tested.V IH (max.) = V DD + 0.3V DC; V IH (max.) = V DD + 2.0V AC (pulse width - 2.0 ns). Not 100% tested.DC ELECTRICAL CHARACTERISTICS (Over Operating Range)V DD = 3.3V + 10%Symbol ParameterTest ConditionsMin.Max.Unit V OH Output HIGH Voltage V DD = Min., I OH = –4.0 mA 2.4—V V OL Output LOW Voltage V DD = Min., I OL = 8.0 mA—0.4V V IH Input HIGH Voltage 2V DD + 0.3V V IL Input LOW Voltage (1)–0.30.8V I LI Input Leakage GND ≤ V IN ≤ V DD–11µA I LO Output LeakageGND ≤ V OUT ≤ V DD , Outputs Disabled–11µANote:1.V IL (min.) = –0.3V DC; V IL (min.) = –2.0V AC (pulse width - 2.0 ns). Not 100% tested.V IH (max.) = V DD + 0.3V DC; V IH (max.) = V DD + 2.0V AC (pulse width - 2.0 ns). Not 100% tested.ISSI®IS61WV12816BLL IS64WV12816BLLPOWER SUPPLY CHARACTERISTICS (1) (Over Operating Range)-12ns -15 ns Symbol Parameter Test Conditions Min.Max.Min.Max.Unit I CCV DD Operating V DD = Max., CE = V IL Com.—35—30mASupply CurrentI OUT = 0 mA, f = Max.Ind.—40—35Auto —40typ.(2)—25—20I SB 1TTL Standby V DD = Max.,Com.—20—20mACurrent V IN = V IH or V IL Ind.—20—20(TTL Inputs)CE ≥ V IH , f = max Auto —30I SB 2CMOS Standby V DD = Max.,Com.—750—750μA CurrentCE ≥ V DD – 0.2V,Ind.—900—900μA (CMOS Inputs)V IN ≥ V DD – 0.2V, or Auto —6mA V IN ≤ 0.2V , f = 0typ.(2)—400—400μANote:1.At f = f MAX , address and data inputs are cycling at the maximum frequency, f = 0 means no input lines change.2.Typical values are measured at V DD =3.3V, T A =250C. Not 100% tested.CAPACITANCE (1)Symbol Parameter Conditions Max.Unit C IN Input Capacitance V IN = 0V 6pF C OUT Input/Output CapacitanceV OUT = 0V8pFNote:1. Tested initially and after any design or process changes that may affect these parameters.6Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev. C ISSI®IS61WV12816BLL IS64WV12816BLLAC TEST LOADSFigure 1.Figure 2.READ CYCLE SWITCHING CHARACTERISTICS (1) (Over Operating Range)-12 ns -15 ns SymbolParameter Min.Max.Min.Max.Unit t RC Read Cycle Time 12—15—ns t AA Address Access Time —12—15ns t OHA Output Hold Time 3—3—ns t ACE CE Access Time —12—15ns t DOE OE Access Time —5—7ns t HZOE (2)OE to High-Z Output —5—6ns t LZOE (2)OE to Low-Z Output 0—0—ns t HZCE (2)CE to High-Z Output 0506ns t LZCE (2)CE to Low-Z Output 3—3—ns t BA LB , UB Access Time —5—7ns t HZB (2)LB , UB to High-Z Output 0506ns t LZB (2)LB , UB to Low-Z Output——nsNotes:1.Test conditions assume signal transition times of 3 ns or less, timing reference levels of 1.5V, input pulse levels of 0V to 3.0V and output loading specified in Figure 1.2.Tested with the load in Figure 2. Transition is measured ±500 mV from steady-state voltage. Not 100% tested.AC TEST CONDITIONSParameterUnit Unit (2.5V-3.6V)(3.3V + 10%)Input Pulse Level0.4V to V DD -0.3V0.4V to V DD -0.3VInput Rise and Fall Times 1.5ns 1.5ns Input and Output Timing V DD /2V DD /2 + 0.05and Reference Level (V Ref )Output LoadSee Figures 1 and 2See Figures 1 and 2ISSI®IS61WV12816BLL IS64WV12816BLLREAD CYCLE NO. 2(1,3)AC WAVEFORMSREAD CYCLE NO. 1(1,2) (Address Controlled) (CE = OE = V IL , UB or LB = V IL )1. WE is HIGH for a Read Cycle.2. The device is continuously selected. OE , CE , UB , or LB = V IL .3. Address is valid prior to or coincident with CE LOW transition.ISSI®IS61WV12816BLLIS64WV12816BLLWRITE CYCLE SWITCHING CHARACTERISTICS(1,3)(Over Operating Range)-12 ns-15 nsSymbol Parameter Min.Max.Min.Max.Unitt WC Write Cycle Time12—15—nst SCE CE to Write End8—10—nst AW Address Setup Time8—10—nsto Write Endt HA Address Hold from Write End0—0—nst SA Address Setup Time0—0—nst PBW LB, UB Valid to End of Write9—10—nst PWE1WE Pulse Width (OE = HIGH)8—10—nst PWE2WE Pulse Width (OE = LOW)10—12—nst SD Data Setup to Write End6—7—nst HD Data Hold from Write End0—0—nst HZWE(3)WE LOW to High-Z Output—5—7nst LZWE(3)WE HIGH to Low-Z Output0—0—nsNotes:1.Test conditions assume signal transition times of 3 ns or less, timing reference levels of 1.5V, input pulse levels of 0V to3.0V and output loading specified in Figure 1.2.The internal write time is defined by the overlap of CE LOW and UB or LB, and WE LOW. All signals must be in valid statesto initiate a Write, but any one can go inactive to terminate the Write. The Data Input Setup and Hold timing are referenced to the rising or falling edge of the signal that terminates the write.3.Tested with the load in Figure 2. Transition is measured ±500 mV from steady-state voltage. Not 100% tested.8Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev. CISSI®IS61WV12816BLL IS64WV12816BLLWRITE CYCLE NO. 1(1,2) (CE Controlled, OE = HIGH or LOW)ISSI®IS61WV12816BLLIS64WV12816BLLWRITE CYCLE NO. 2(1)(WE Controlled, OE = HIGH during Write Cycle)10Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev. CISSI®IS61WV12816BLL IS64WV12816BLLWRITE CYCLE NO. 4 (LB , UB Controlled, Back-to-Back Write) (1,3)1. The internal Write time is defined by the overlap of CE = LOW, UB and/or LB = LOW, and WE = LOW. All signals must be in valid states to initiate a Write, but any can be deasserted to terminate the Write. The t SA , t HA , t SD , and t HD timing is referenced to the rising or falling edge of the signal that terminates the Write.2. Tested with OE HIGH for a minimum of 4 ns before WE = LOW to place the I/O in a HIGH-Z state.3. WE may be held LOW across many address cycles and the LB , UB pins can be used to control the Write function.ISSI®IS61WV12816BLL IS64WV12816BLLDATA RETENTION WAVEFORM (CE Controlled)DATA RETENTION SWITCHING CHARACTERISTICSSymbolParameterTest ConditionOptions Min.Typ.(1)Max.Unit V DRV DD for Data Retention See Data Retention Waveform 1.8— 3.6V I DRData Retention Current V DD = 2.0V, CE ≥ V DD – 0.2V Ind.—0.40.9mA Auto—0.46mA t SDR Data Retention Setup Time See Data Retention Waveform 0——ns t RDRRecovery TimeSee Data Retention Waveformt RC——nsNote 1: Typical values are measured at V DD = 3.3V, T A = 25OC. Not 100% tested.ISSI®IS61WV12816BLL IS64WV12816BLLORDERING INFORMATION:Industrial Range: –40°C to +85°CSpeed (ns)Order Part No.Package12 (151)IS61WV12816BLL-12BI mini BGA (6mm x 8mm)IS61WV12816BLL-12BLI mini BGA (6mm x 8mm), Lead-free IS61WV12816BLL-12TI Plastic TSOP (Type II)IS61WV12816BLL-12TLIPlastic TSOP (Type II), Lead-freeNote:1.Speed = 12ns for V DD = 3.3V + 10%. Speed = 15ns for V DD =2.5V-3.6VAutomotive Range: –40°C to +125°CSpeed (ns)Order Part No.Package15IS64WV12816BLL-15BA3mini BGA (6mm x 8mm)IS64WV12816BLL-15TA3Plastic TSOP (Type II)IS64WV12816BLL-15TLA3Plastic TSOP (Type II), Lead-freePACKAGING INFORMATIONISSI®Copyright © 2003 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to Mini Ball Grid ArrayPackage Code: B (48-pin)PACKAGING INFORMATIONISSI®Copyright © 2003 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any timewithout notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to Plastic TSOPPackage Code: T (Type II)。

芯片命名规则

电子元器件命名- -电子元器件,又叫电子芯片,半导体集成电路,广泛应用于各种电子电器设备上.封装形式:封装形式是指安装半导体集成电路芯片用的外壳.它不仅起着安装,固定,密封,保护芯片及增强电热性能等方面的作用,而且还通过芯片上的接点用导线连接到封装外壳的引脚上,这些引脚又通过印刷电路板上的导线与其他器件相连接.衡量一个芯片封装技术先进与否的重要指标是芯片面积与封装面积之比,这个比值越接近1越好.封装大致经过了如下发展进程:结构方面:TO->DIP->LCC->QFP->BGA ->CSP;材料方面:金属,陶瓷->陶瓷,塑料->塑料;引脚形状:长引线直插->短引线或无引线贴装->球状凸点;装配方式:通孔插装->表面组装->直接安装.英文简称英文全称中文解释图片DIPDouble In-line Package双列直插式封装.插装型封装之一,引脚从封装两侧引出,封装材料有塑料和陶瓷两种.DIP是最普及的插装型封装,应用范围包括标准逻辑IC,存贮器LSI,微机电路等.PLCCPlastic Leaded Chip CarrierPLCC封装方式,外形呈正方形,32脚封装,四周都有管脚,外形尺寸比DIP封装小得多.PLCC封装适合用SMT表面安装技术在PCB上安装布线,具有外形尺寸小,可靠性高的优点.PQFPPlastic Quad Flat PackagePQFP封装的芯片引脚之间距离很小,管脚很细,一般大规模或超大规模集成电路采用这种封装形式,其引脚数一般都在100以上.SOPSmall Outline Package1968~1969年菲为浦公司就开发出小外形封装(SOP).以后逐渐派生出SOJ(J型引脚小外形封装),TSOP(薄小外形封装),VSOP(甚小外形封装),SSOP(缩小型SOP),TSSOP(薄的缩小型SOP)及SOT(小外形晶体管),SOIC(小外形集成电路)等.模拟滤波器光纤通信高速信号处理和转换无线/射频光线通讯,模拟显示支持电路高频模拟和混合信号ASIC数字转换器,接口,电源管理,电池监控DC/DC电源电压基准MAXIM前缀是"MAX".DALLAS则是以"DS"开头.MAX×××或MAX××××说明:1后缀CSA,CWA 其中C表示普通级,S表示表贴,W 表示宽体表贴.2 后缀CWI表示宽体表贴,EEWI宽体工业级表贴,后缀MJA或883为军级.3 CPA,BCPI,BCPP,CPP,CCPP,CPE,CPD,ACPA后缀均为普通双列直插.举例MAX202CPE,CPE普通ECPE普通带抗静电保护MAX202EEPE 工业级抗静电保护(-45℃-85℃) 说明E 指抗静电保护MAXIM数字排列分类1字头模拟器2字头滤波器3字头多路开关4字头放大器5字头数模转换器6字头电压基准7字头电压转换8字头复位器9字头比较器DALLAS命名规则例如DS1210N.S. DS1225Y-100IND N=工业级S=表贴宽体MCG=DIP封Z=表贴宽体MNG=DIP工业级IND=工业级QCG=PLCC封Q=QFP 下面是MAXIM的命名规则:三字母后缀:例如:MAX358CPDC = 温度范围P = 封装类型D = 管脚数温度范围:C = 0℃至70℃(商业级)I = -20℃至+85℃(工业级)E = -40℃至+85℃(扩展工业级)A = -40℃至+85℃(航空级)M = -55℃至+125℃(军品级)封装类型:A SSOP(缩小外型封装)B CERQUADC TO-220, TQFP(薄型四方扁平封装)D 陶瓷铜顶封装E 四分之一大的小外型封装F 陶瓷扁平封装H 模块封装, SBGA(超级球式栅格阵列, 5x5 TQFP) J CERDIP (陶瓷双列直插)K TO-3 塑料接脚栅格阵列L LCC (无引线芯片承载封装)M MQFP (公制四方扁平封装)N 窄体塑封双列直插P 塑封双列直插Q PLCC (塑料式引线芯片承载封装)R 窄体陶瓷双列直插封装(300mil)S 小外型封装T TO5,TO-99,TO-100U TSSOP,μMAX,SOTW 宽体小外型封装(300mil)X SC-70(3脚,5脚,6脚)Y 窄体铜顶封装Z TO-92,MQUAD/D 裸片/PR 增强型塑封/W 晶圆DSP信号处理器放大器工业用器件通信电源管理移动通信视频/图像处理器等模拟A/D D/A 转换器传感器模拟器件AD产品以"AD","ADV"居多,也有"OP"或者"REF","AMP","SMP","SSM","TMP","TMS"等开头的.后缀的说明:1,后缀中J表示民品(0-70℃),N表示普通塑封,后缀中带R表示表示表贴。

电子元件封装大全及封装常识

电子元件封装大全及封装常识一、什么叫封装封装,就是指把硅片上的电路管脚,用导线接引到外部接头处,以便与其它器件连接.封装形式是指安装半导体集成电路芯片用的外壳。

它不仅起着安装、固定、密封、保护芯片及增强电热性能等方面的作用,而且还通过芯片上的接点用导线连接到封装外壳的引脚上,这些引脚又通过印刷电路板上的导线与其他器件相连接,从而实现内部芯片与外部电路的连接。

因为芯片必须与外界隔离,以防止空气中的杂质对芯片电路的腐蚀而造成电气性能下降。

另一方面,封装后的芯片也更便于安装和运输。

由于封装技术的好坏还直接影响到芯片自身性能的发挥和与之连接的PCB(印制电路板)的设计和制造,因此它是至关重要的。

衡量一个芯片封装技术先进与否的重要指标是芯片面积与封装面积之比,这个比值越接近1越好。

封装时主要考虑的因素:1、芯片面积与封装面积之比为提高封装效率,尽量接近1:1;2、引脚要尽量短以减少延迟,引脚间的距离尽量远,以保证互不干扰,提高性能;3、基于散热的要求,封装越薄越好。

封装主要分为DIP双列直插和SMD贴片封装两种。

从结构方面,封装经历了最早期的晶体管TO(如TO-89、TO92)封装发展到了双列直插封装,随后由PHILIP 公司开发出了SOP小外型封装,以后逐渐派生出SOJ(J型引脚小外形封装)、TSOP(薄小外形封装)、VSOP(甚小外形封装)、SSOP(缩小型SOP)、TSSOP (薄的缩小型SOP)及SOT(小外形晶体管)、SOIC(小外形集成电路)等。

从材料介质方面,包括金属、陶瓷、塑料、塑料,目前很多高强度工作条件需求的电路如军工和宇航级别仍有大量的金属封装。

封装大致经过了如下发展进程:结构方面:TO->DIP->PLCC->QFP->BGA ->CSP;材料方面:金属、陶瓷->陶瓷、塑料->塑料;引脚形状:长引线直插->短引线或无引线贴装->球状凸点;装配方式:通孔插装->表面组装->直接安装二、具体的封装形式1、 SOP/SOIC封装SOP是英文Small Outline Package 的缩写,即小外形封装。

IS61LPS51236A中文资料