LM4991MA 规格书,Datasheet 资料

MBS4991中文资料

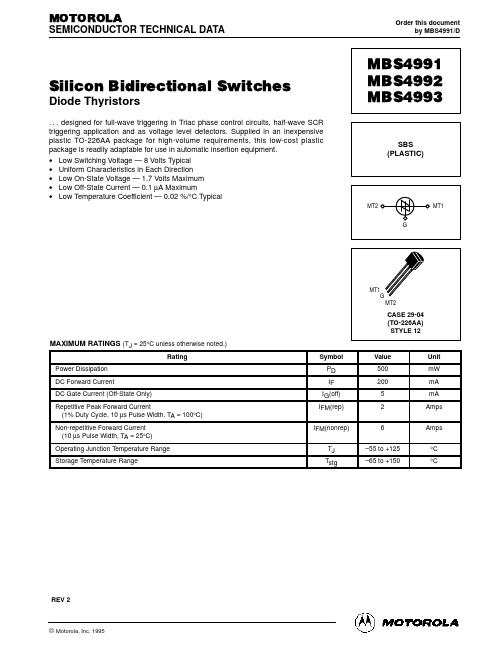

MBS4991 MBS4992 MBS4993

SBS (PLASTIC)

MT2 G

MT1

MT1 G MT2 CASE 29-04 (TO-226AA) STYLE 12

MAXIMUM RATINGS (TJ = 25°C unless otherwise noted.)

Rating Power Dissipation DC Forward Current DC Gate Current (Off-State Only) Repetitive Peak Forward Current (1% Duty Cycle, 10 µs Pulse Width, TA = 100°C) Non-repetitive Forward Current (10 µs Pulse Width, TA = 25°C) Operating Junction Temperature Range Storage Temperature Range Symbol PD IF IG(off) IFM(rep) IFM(nonrep) TJ Tstg Value 500 200 5 2 6 –55 to +125 –65 to +150 Unit mW mA mA Amps Amps °C °C

CHARACTERISTICS Motorola Thyristor Device Data

元器件交易网

PACKAGE DIMENSIONS

MBS4991 MBS4992 MBS4993

A R P

SEATING PLANE

B

STYLE 12: PIN 1. MAIN TERMINAL 1 2. GATE 3. MAIN TERMINAL 2

TYPICAL ELECTRICAL CHARACTERISTICS

MT9M001C12STM;中文规格书,Datasheet资料

PDF: 09005aef81c2856f/Source: 09005aef80a3e031Micron Technology, Inc., reserves the right to change products or specifications without notice.MT9M001_DS_1.fm -Rev. F 5/06 EN©2004 Micron Technology, Inc. All rights reserved.1/2-Inch Megapixel CMOS Digital Image SensorMT9M001C12STM (Monochrome)For the latest data sheet, refer to Micron’s Web site: \imagingFeatures•Micron ® DigitalClarity ™ CMOS imaging technology •Array Format (5:4): 1,280H x 1,024V (1,310,720 active pixels). Total (incl. dark pixels): 1,312H x 1,048V (1,374,976 pixels)•Frame Rate: 30 fps progressive scan; programmable •Shutter: Electronic Rolling Shutter (ERS)•Window Size: SXGA; programmable to any smaller format (VGA, QVGA, CIF, QCIF, etc.)•Programmable Controls: Gain, frame rate, frame sizeApplications•Digital still cameras •Digital video cameras •PC camerasGeneral DescriptionThe Micron ® Imaging MT9M001 is an SXGA-format with a 1/2-inch CMOS active-pixel digital image sen-sor. The active imaging pixel array of 1,280H x 1,024V. It incorporates sophisticated camera functions on-chip such as windowing, column and row skip mode, and snapshot mode. It is programmable through a simple two-wire serial interface.This megapixel CMOS image sensor features Digital-Clarity—Micron’s breakthrough low-noise CMOS imaging technology that achieves CCD image quality (based on signal-to-noise ratio and low-light sensitiv-ity) while maintaining the inherent size, cost, and inte-gration advantages of CMOS.Table 1: Key Performance ParametersThe sensor can be operated in its default mode or pro-grammed by the user for frame size, exposure, gain set-ting, and other parameters. The default mode outputs an SXGA-size image at 30 frames per second (fps). An on-chip analog-to-digital converter (ADC) provides 10 bits per pixel. FRAME_VALID and LINE_VALID signals are output on dedicated pins, along with a pixel clock that is synchronous with valid data.Ordering InformationParameterValueOptical format 1/2-inch (5:4)Active imager size 6.66mm(H) x 5.32mm(V)Active pixels 1,280H x 1,024V Pixel size 5.2µm x 5.2µmShutter typeElectronic rolling shutter (ERS)Maximum data rate/master clock 48 MPS/48 MHzFrame rate SXGA (1280 x 1024)30 fps progressive scan;programmable ADC resolution 10-bit, on-chip Responsivity 2.1 V/lux-sec Dynamic range 68.2dB SNR MAX45dBSupply voltage3.0V −3.6V, 3.3V nominal Power consumption 363mW at 3.3V (operating);294mW (standby)Operating temperature 0°C to +70°C Packaging48-pin CLCCTable 2:Available Part NumbersPart Number DescriptionMT9M001C12STM48-pin CLCC (lead free)Table of ContentsApplications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 List of Tables. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3 List of Figures. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4 General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5 Pixel Data Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7 Pixel Array Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7 Output Data Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 Output Data Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 Frame Timing Formulas . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10 Serial Bus Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11 Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11 Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11 Bus Idle State. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11 Start Bit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11 Stop Bit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12 Slave Address. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12 Data Bit Transfer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12 Acknowledge Bit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12 No-Acknowledge Bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12 Two-Wire Serial Interface Sample Write and Read Sequences. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13 16-Bit Write Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13 16-Bit Read Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14 Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14 Feature Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21 Signal Path. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21 Programmable Gain Stage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21 Programmable Analog Offset Stage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22 Column and Row Mirror Image . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22 Column and Row Skip. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22 Black Level Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25 Still Image Capture with External Synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27 LINE_VALID Signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27 Electrical Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28 Data Output and Propagation Delays . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28 Two-wire Serial Bus Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30 Quantum Efficiency. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32 Image Center Offset and Orientation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32 Revision History. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35List of TablesTable 1:Key Performance Parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Table 2:Available Part Numbers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Table 3:Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6 Table 4:Frame Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10 Table 5:Frame Time—Long Integration Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10 Table 6:Register List and Default Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14 Table 7:Register Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15 Table 8:Recommended Gain Settings at 48 MHz. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21 Table 9:Black Level Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25 Table 10:DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28 Table 11:AC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29 Table 12:Absolute Maximum Ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29 Table 13:Optical Area Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33List of FiguresFigure 1:48-Pin CLCC Package Pinout Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5 Figure 2:Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5 Figure 3:Pixel Array Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7 Figure 4:Pixel Pattern Detail (Top Right Corner) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7 Figure 5:Spatial Illustration of Image Readout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 Figure 6:Timing Example of Pixel Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 Figure 7:Row Timing and FRAME_VALID/LINE_VALID Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9 Figure 8:Timing Diagram Showing a Write to Reg0x09 with the Value 0x0284 . . . . . . . . . . . . . . . . . . . . . . . . . .13 Figure 9:Timing Diagram Showing a Read from Reg0x09; Returned Value 0x0284 . . . . . . . . . . . . . . . . . . . . . .13 Figure 10:Signal Path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21 Figure 11:Readout of Six Columns in Normal and Column Mirror Output Mode . . . . . . . . . . . . . . . . . . . . . . . . .22 Figure 12:Readout of Six Rows in Normal and Row Mirror Output Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22 Figure 13:Readout of Eight Pixels in Normal and Column Skip Output Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . .23 Figure 14:Black Level Calibration Flow Chart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24 Figure 15:General Timing for Snapshot Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27 Figure 16:Different LINE_VALID Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27 Figure 17:Data Output Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28 Figure 18:Serial Host Interface Start Condition Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30 Figure 19:Serial Host Interface Stop Condition Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30 Figure 20:Serial Host Interface Data Timing for Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30 Figure 21:Serial Host Interface Data Timing for Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30 Figure 22:Acknowledge Signal Timing After an 8-Bit Write to the Sensor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31 Figure 23:Acknowledge Signal Timing After an 8-Bit Read from the Sensor . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31 Figure 24:Quantum Efficiency—Monochrome . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32 Figure 25:Image Center Offset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32 Figure 26:Optical Orientation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33 Figure 27:48-pin CLCC Package Outline Drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34General DescriptionFigure 1: 48-Pin CLCC Package Pinout DiagramFigure 2:Block DiagramTable 3: Pin DescriptionsPin Numbers Symbol Type Description29CLKIN Input Clock in. Master clock into sensor (48 MHz maximum).13OE#Input Output enable. OE# when HIGH places outputs D OUT<0:9>,FRAME_VALID, LINE_VALID, PIXCLK, and STROBE into a tri-stateconfiguration.10RESET#Input Reset. Activates (LOW) asynchronous reset of sensor. All registersassume factory defaults.46SCLK Input Serial clock. Clock for serial interface.7STANDBY Input Standby. Activates (HIGH) standby mode, disables analog bias circuitryfor power saving mode.8TRIGGER Input Trigger. Activates (HIGH) snapshot sequence.45S DATA Input/Output Serial data. Serial data bus, requires 1.5KΩ resistor to 3.3V for pull-up. 24–28, 32–36D OUT<0–9>Output Data out. Pixel data output bits 0:9, D OUT<9> (MSB), D OUT<0> (LSB).41FRAME_VALID Output Frame valid. Output is pulsed HIGH during frame of valid pixel data.40LINE_VALID Output Line valid. Output is pulsed HIGH during line of selectable valid pixeldata (see Reg0x20 for options).31PIXCLK Output Pixel clock. Pixel data outputs are valid during falling edge of thisclock. Frequency = (master clock).39STROBE Output Strobe. Output is pulsed HIGH to indicate sensor reset operation ofpixel array has completed.15,17,18,21, 47,48A GND Supply Analog ground. Provide isolated ground for analog block and pixelarray.5, 23, 38, 43D GND Supply Digital ground. Provide isolated ground for digital block.16, 20V AA Supply Analog power. Provide power supply for analog block, 3.3V ±0.3V.1VAAPIX Supply Analog pixel power. Provide power supply for pixel array, 3.3V ±0.3V(3.3V).4, 22, 37V DD Supply Digital power. Provide power supply for digital block, 3.3V ±0.3V.2, 3 ,6, 9, 11,12,14, 19, 30,42, 44NC—No connect. These pins must be left unconnected.Pixel Data FormatPixel Array StructureThe MT9M001 pixel array is configured as 1,312 columns by 1,048 rows (shown inFigure3). The first 16 columns and the first eight rows of pixels are optically black, andcan be used to monitor the black level. The last seven columns and the last seven rows ofpixels are also optically black. The black row data is used internally for the automaticblack level adjustment. However, the black rows can also be read out by setting thesensor to raw data output mode (Reg0x20, bit 11 = 1). There are 1,289 columns by 1,033rows of optically active pixels, which provides a four-pixel boundary around the SXGA(1,280x1,024) image.Figure 3: Pixel Array DescriptionFigure 4: Pixel Pattern Detail (Top Right Corner)Output Data FormatThe MT9M001 image data is read out in a progressive scan. Valid image data issurrounded by horizontal blanking and vertical blanking, as shown in Figure 5. The amount of horizontal blanking and vertical blanking is programmable through Reg0x05 and Reg0x06, respectively. LINE_VALID is HIGH during the shaded region of the figure. FRAME_VALID timing is described in “Output Data Timing” on page 8.Figure 5: Spatial Illustration of Image ReadoutOutput Data TimingThe data output of the MT9M001 is synchronized with the PIXCLK output. When LINE_VALID is HIGH, one 10-bit pixel datum is output every PIXCLK period.Figure 6: Timing Example of Pixel DataThe rising edges of the PIXCLK signal are nominally timed to occur on the rising D OUT edges. This allows PIXCLK to be used as a clock to latch the data. D OUT data is valid on the falling edge of PIXCLK. The PIXCLK is HIGH while master clock is HIGH and then LOW while master clock is LOW. It is continuously enabled, even during the blanking period. The parameters P1, A P2, and Q in Figure 7 are defined in Table4.Figure 7: Row Timing and FRAME_VALID/LINE_VALID SignalsFrame Timing FormulasNotes:1.Row skip mode should have no effect on the integration time. Column skip mode changes the effective value of Column Size (Reg0x04) as follows:Column Skip 2 => R4eff = (int(R4 / 4) x 2) + 1Column Skip 4 => R4eff = (int(R4 / 8) x 2) + 1Column Skip 8 => R4eff = (int(R4 / 16) x 2) + 1where the int() function truncates to the next lowest integer. Now use R4eff in the equa-tion for row time instead of R42.Default for Reg0x05 = 9. However, sensor ignores any value for Reg0x05 less than 19.Sensor timing is shown above in terms of pixel clock and master clock cycles (please refer to Figure 6). The recommended master clock frequency is 48 MHz. The vertical blank and total frame time equations assume that the number of integration rows (bits 13 through 0 of Reg0x09) is less than the number of active plus blanking rows (Reg0x03 + 1 + Reg0x06 + 1). If this is not the case, the number of integration rows must be used instead to determine the frame time, as shown in Table 5.Table 4:Frame TimingParameter NameEquation (MASTER CLOCK)Default Timing Notes A Active Data Time(Reg0x04 + 1)1,280 pixel clocks = 26.7µs1P 1Frame Start Blanking (242)242 pixel clocks = 5.04µsP 2Frame End Blanking (2 + Reg0x05 - 19)(MIN Reg0x05 value = 19) 2 pixel clocks = 0.042µs2Q = P 1 + P 2Horizontal Blanking (244 + Reg0x05 - 19)(MIN Reg0x05 value = 19)244 pixel clocks = 5.08µs2A + Q Row Time ((Reg0x04 + 1) + (244 + Reg0x05 - 19))1,524 pixel clocks = 31.75µsVVertical Blanking (Reg0x06 + 1) x (A + Q)(MIN Reg0x06 value = 15)39,624 pixel clocks = 825.5µsN ROWS x (A + Q)Frame Valid Time (Reg0x03 + 1) x (A + Q)1,560,576 pixel clocks = 32.51msFTotal Frame Time (Reg0x03 + 1 + Reg0x06 + 1) x (A + Q)1,600,200 pixel clocks = 33.34msTable 5:Frame Time —Long Integration TimeParameterNameEquation (master clock)Default Timing V’Vertical Blanking (long integration time)(Reg0x09 – Reg0x03) x (A + Q)39,624 pixel clocks = 82.5µsF’Total Frame Time (long integration time)(Reg0x09 + 1) x (A + Q)1,600,200 pixel clocks = 33.34ms分销商库存信息: APTINA-LLCMT9M001C12STM。

MJL21193G;MJL21194G;MJL21194;MJL21193;中文规格书,Datasheet资料

Max

Unit

VCEO(sus)

250

−

−

Vdc

ICEO

−

−

100

mAdc

IEBO

−

−

100

mAdc

ICEX

−

−

100

mAdc

IS/b

hFE VBE(on) VCE(sat)

THD

fT Cob

Adc

4.0

−

−

2.25

−

−

25

−

75

8

−

−

−

−

2.2

Vdc

Vdc

−

−

1.4

−

−

4

−

0.8

−

−

0.08

−

4

−

0

0.1

1.0

10

IC COLLECTOR CURRENT (AMPS)

Figure 2. Typical Current Gain Bandwidth Product

/

2

MJL21193, MJL21194

TYPICAL CHARACTERISTICS

1.5 A 25

1A

20

15

0.5 A

10

5.0 TJ = 25°C

0

0

5.0

10

15

20

25

VCE, COLLECTOR-EMITTER VOLTAGE (VOLTS)

Figure 8. Typical Output Characteristics

/

3

Temperature Range

Symbol VCEO VCBO VEBO VCEX IC

LM321MF 规格书,Datasheet 资料

LM321LM321 Low Power Single Op AmpLiterature Number: SNOS935A 芯天下--/LM321Low Power Single Op AmpGeneral DescriptionThe LM321brings performance and economy to low power systems.With a high unity gain frequency and a guaranteed 0.4V/µs slew rate,the quiescent current is only 430µA/amplifier (5V).The input common mode range in-cludes ground and therefore the device is able to operate in single supply applications as well as in dual supply applica-tions.It is also capable of comfortably driving large capaci-tive loads.The LM321is available in the SOT23-5package.Overall the LM321is a low power,wide supply range performance op amp that can be designed into a wide range of applications at an economical price without sacrificing valuable board space.Features(V CC =5V,T A =25˚C.Typical values unless specified).n Gain-Bandwidth product 1MHz n Low supply current 430µA n Low input bias current 45nA n Wide supply voltage range +3V to +32V n Stable with high capacitive loads n Single version of LM324Applicationsn Chargersn Power suppliesn Industrial:controls,instruments n DesktopsnCommunications infrastructureConnection DiagramSOT23-520007601Top ViewApplication CircuitDC Summing Amplifier (V IN’s ≥0V DC and V O ≥V DC )20007607Where:V 0=V 1+V 2-V 3-V 4,(V 1+V 2)≥(V 3+V 4)to keep V O>0V DCOrdering InformationPackage Part Number Package MarkingTransport Media NSC Drawing5-Pin SOT-23LM321MF A63A1k Units Tape and Reel MF05ALM321MFX3k Units Tape and ReelApril 2001LM321Low Power Single Op Amp©2001National Semiconductor Corporation Absolute Maximum Ratings(Note 1)If Military/Aerospace specified devices are required,please contact the National Semiconductor Sales Office/Distributors for availability and specifications.Differential Input Voltage±Supply VoltageInput Current (V IN <−0.3V)(Note 6)50mA Supply Voltage (V +-V −)32VInput Voltage−0.3V to +32V Output Short Circuit to GND,V +≤15V and T A =25˚C (Note 2)Continuous Storage Temperature Range−65˚C to 150˚CJunction Temperature (Note 3)150˚C Mounting TemperatureLead Temp (Soldering,10sec)260˚C Infrared (10sec)215˚C Thermal Resistance to Ambient (θJA )265˚C/WESD Tolerance (Note 10)300VOperating Ratings (Note 1)Temperature Range −40˚C to 85˚CSupply Voltage3V to 30VElectrical CharacteristicsUnless otherwise specified,all limits guaranteed for at T A =25˚C;V +=5V,V −=0V,V O =1.4V.Boldface limits apply at temperature extremes.Symbol ParameterConditionsMin (Note 5)Typ (Note 4)Max (Note 5)Units V OS Input Offset Voltage (Note 7)279mV I OS Input Offset Current 550150nA I B Input Bias Current (Note 8)45250500nA V CM Input Common-Mode Voltage Range V +=30V (Note 9)For CMRR >=50dB 0V +-1.5V +-2V A V Large Signal Voltage Gain (V +=15V,R L =2k ΩV O =1.4V to 11.4V)2515100V/mV PSRR Power Supply Rejection Ratio R S ≤10k Ω,V +≤5V to 30V 65100dB CMRR Common Mode Rejection Ratio R S ≤10k Ω6585dB V OOutput SwingV OH V +=30V,R L =2k Ω26V V +=30V,R L =10k Ω2728V OLV +=5V,R L =10k Ω520mV I SSupply Current,No LoadV +=5V 0.4300.7 1.151.2mAV +=30V0.6601.52.853I SOURCE Output Current Sourcing V ID =+1V,V +=15V,V O =2V20104020mAI SINKOutput Current SinkingV ID =−1VV +=15V,V O =2V 105208mA V ID =−1VV +=15V,V O =0.2V12100µA I O Output Short Circuit to Ground (Note 2)V +=15V4085mASRSlew RateV +=15V,R L =2k Ω,V IN =0.5to 3VC L =100pF,Unity Gain 0.4V/µsGBW Gain Bandwidth ProductV +=30V,f =100kHz,V IN =10mV,R L =2k Ω,C L =100pF1MHz φm Phase Margin60degL M 321 2Electrical Characteristics Unless otherwise specified,all limits guaranteed for at TA=25˚C;V+=5V,V−= 0V,V O=1.4V.Boldface limits apply at temperature extremes.(Continued)Symbol Parameter Conditions Min(Note5)Typ(Note4)Max(Note5)UnitsTHD Total Harmonic Distortion f=1kHz,A V=20dBR L=2kΩ,V O=2V PP,C L=100pF,V+=30V0.015%e n Equivalent Input Noise Voltage f=1kHz,R S=100ΩV+=30V40nV/Typical Performance CharacteristicsUnless otherwise specified,V S =+5V,single supply,T A =25˚C.Small Signal Pulse ResponseLarge Signal Pulse Response2000760420007605Supply Current vs.Supply Voltage Sinking Current vs.Output Voltage2000761220007613Source Current vs.Output Voltage Open Loop Frequency Response2000761720007614L M 321 4Application HintsThe LM321op amp can operate with a single or dual power supply voltage,has true-differential inputs,and remain in the linear mode with an input common-mode voltage of0V DC. This amplifier operates over a wide range of power supply voltages,with little change in performance characteristics.At 25˚C amplifier operation is possible down to a minimum supply voltage of3V.Large differential input voltages can be easily accommo-dated and,as input differential voltage protection diodes are not needed,no large input currents result from large differ-ential input voltages.The differential input voltage may be larger than V+without damaging the device.Protection should be provided to prevent the input voltages from going negative more than−0.3V DC(at25˚C).An input clamp diode with a resistor to the IC input terminal can be used.To reduce the power supply drain,the amplifier has a class A output stage for small signal levels which converts to class B in a large signal mode.This allows the amplifiers to both source and sink large output currents.Therefore both NPN and PNP external current boost transistors can be used to extend the power capability of the basic amplifiers.The output voltage needs to raise approximately1diode drop above ground to bias the on-chip vertical PNP transistor for output current sinking applications.For AC applications,where the load is capacitively coupled to the output of the amplifier,a resistor should be used,from the output of the amplifier to ground to increase the class A bias current and to reduce distortion.Capacitive loads which are applied directly to the output of the amplifier reduce the loop stability margin.Values of50pF can be accommodated using the worst-case non-inverting unity gain rge closed loop gains or resistive isolation should be used if large load capacitance must be driven by the amplifier.The bias network of the LM321establishes a supply current which is independent of the magnitude of the power supply voltage over the range of from3V DC to30V DC.Output short circuits either to ground or to the positive power supply should be of short time duration.Units can be de-stroyed,not as a result of the short circuit current causing metal fusing,but rather due to the large increase in IC chip dissipation which will cause eventual failure due to exces-sive junction temperatures.The larger value of output source current which is available at25˚C provides a larger output current capability at elevated temperatures than a standard IC op amp.The circuits presented in the section on typical applications emphasize operation on only a single power supply voltage. If complementary power supplies are available,all of the standard op amp circuits can be used.In general,introduc-ing a pseudo-ground(a bias voltage reference of V+/2)will allow operation above and below this value in single power supply systems.Many application circuits are shown which take advantage of the wide input common-mode voltage range which includes ground.In most cases,input biasing is not required and input voltages which range to ground can easily be accommodated.Typical ApplicationsNon-Inverting DC Gain(0V Input=0V Output)20007606LM3215Typical Applications(Continued)Amplitude Modulator CircuitDC Summing Amplifier (V IN’s ≥0V DC and V O ≥V DC )2000760220007607Where:V 0=V 1+V 2-V 3-V 4,(V 1+V 2)≥(V 3+V 4)to keep V O >0V DCPower Amplifier LED Driver20007608V 0=0V DC for V IN =0V DC ,A V =1020007609Fixed Current Sources Lamp Driver2000761020007611L M 321 6SOT23-5Tape and Reel SpecificationTAPE DIMENSIONS200076158mm0.130(3.3)0.124(3.15)0.130(3.3)0.126(3.2)0.138±0.002(3.5±0.05)0.055±0.004(1.4±0.11)0.157(4)0.315±0.012(8±0.3)Tape Size DIM A DIM Ao DIM B DIM Bo DIM F DIM Ko DIM P1DIM WLM3217SOT23-5Tape and Reel Specification(Continued)REEL DIMENSIONS200076168mm 7.00330.000.0591.500.51213.000.79520.20 2.16555.000.331+0.059/−0.0008.40+1.50/−0.000.56714.40W1+0.078/−0.039W1+2.00/−1.00Tape SizeABCDNW1W2W3L M 321 8Physical Dimensionsinches (millimeters)unless otherwise noted5-Pin SOT23NS Package Number MF05ALIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION.As used herein:1.Life support devices or systems are devices or systems which,(a)are intended for surgical implant into the body,or (b)support or sustain life,and whose failure to perform when properly used in accordance with instructions for use provided in the labeling,can be reasonably expected to result in a significant injury to the user.2.A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system,or to affect its safety or effectiveness.National Semiconductor Corporation AmericasTel:1-800-272-9959Fax:1-800-737-7018Email:support@National Semiconductor EuropeFax:+49(0)180-5308586Email:europe.support@Deutsch Tel:+49(0)6995086208English Tel:+44(0)8702402171Français Tel:+33(0)141918790National Semiconductor Asia Pacific Customer Response Group Tel:65-2544466Fax:65-2504466Email:ap.support@National Semiconductor Japan Ltd.Tel:81-3-5639-7560Fax:81-3-5639-7507LM321Low Power Single Op AmpNational does not assume any responsibility for use of any circuitry described,no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAudio /audio Communications and Telecom /communicationsAmplifiers Computers and Peripherals /computersData Converters Consumer Electronics /consumer-appsDLP®Products Energy and Lighting /energyDSP Industrial /industrialClocks and Timers /clocks Medical /medicalInterface Security /securityLogic Space,Avionics and Defense /space-avionics-defense Power Mgmt Transportation and Automotive /automotiveMicrocontrollers Video and Imaging /videoRFID OMAP Mobile Processors /omapWireless Connectivity /wirelessconnectivityTI E2E Community Home Page Mailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2011,Texas Instruments Incorporated芯天下--/。

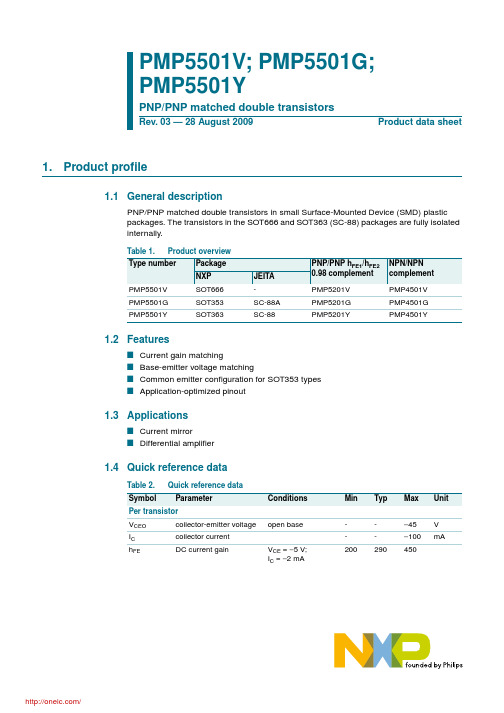

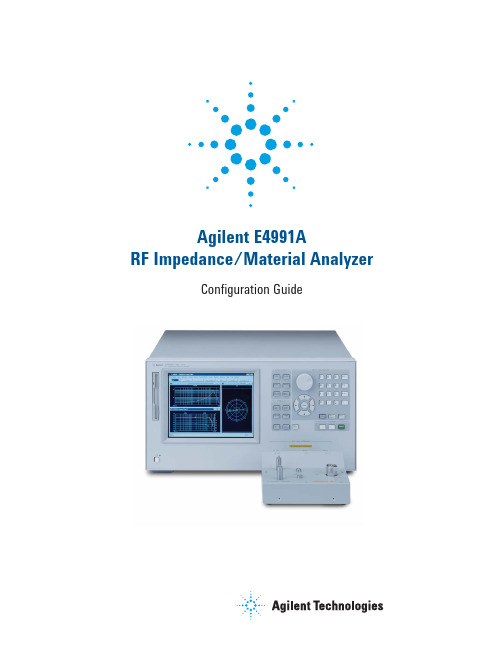

安捷伦E4991A(射频阻抗、材料分析仪)替代:4291A

图 7. 分段扫描列表

可以使用多种测量夹具

图 7-1. 用分段扫描方法得到的测量结果

保存测量结果和数据

● 内置 3.5 英寸软盘驱动器,内置硬盘。 ● 可以保存 VBA 程序,校准数据, 测量结果的数据。 ● 对于使用自动化工具的用户,支持 CITIFILE 格式的数据。

网络接口

● 控制其它仪表或简化共享数据的过程。 ● 使用异地用户接口软件 与 PC 相连接。

图 1. 片状电感的 Ls-Q 特性的测量结果 表 2. Q 值的测量精度 (典型值)

Q 值测量精度

测量频率

表 3. E4991A 和网路分析仪的各项关键特性的比较

E4991A

网络分析仪

测量的器件的类型 1 端口器件, 例如电感器、 电容器, 以及其它器件

2 端口器件, 例如滤波器、 放大器, 以及其它器件

图 5. 使用 16200B 直流偏置适配器扩展 E4991A 的 直流偏置范围

提取器件的等效电路参数

E 4 9 9 1 A 的 等 效 电 路 分 析 功 能 比起标准的两参数模型来能给工程 师们提供更为详细的电路模型。 E4991A 提供了 5 种不同类型的多参 数模型来满足对不同类型的器件 — 例如陶瓷电容器或晶体谐振器等 — 进行分析的需要。您可以根据等效 参数值通过仿真得出一个阻抗轨 迹,然后把仿真结果与实际测量得 到的轨迹进行对比。所提取的参数 还可以应用到自动电路设计 (EDA) 工 具中来提高器件建模的精确度。

对于应用于移动通信设备中的 器件来说,他们的品质因数 (Q 值)和 等效串联电阻 (ESR) 都是极为重要的 参数,测量这两个参数需要极高的 精度。在安捷伦推出 E4991A 之前, 在 2 GHz 以上的测量频率范围内一直 没有一个很好解决方案。用 E4991A 测量 Q 值和 ESR 比起用传统的矢量网 络分析仪测量精度大有提高,这是 因为 E4991A 采用了增强型的 RF I-V 测 量技术来测量被测器件 (DUT) 的电压 和电流,同时还采用了使用 小损耗 电容器对夹具误差进行校准的创新 技术。

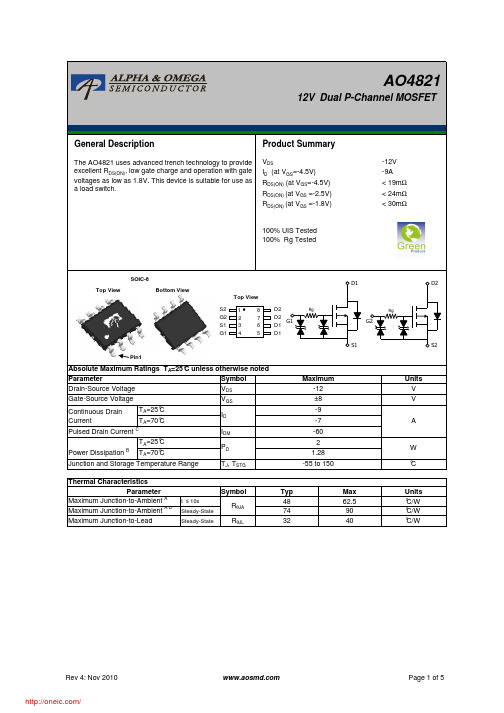

AO4821;中文规格书,Datasheet资料

100% UIS Tested 100% Rg TestedSymbol V DS V GSI DM T J , T STGSymbolt ≤ 10s Steady-State Steady-StateR θJLW 2Maximum Junction-to-Lead°C/W°C/W Maximum Junction-to-Ambient A D 329040Maximum Junction-to-Ambient A T A =25°C T A =70°C Power DissipationBP D Pulsed Drain Current CContinuous Drain CurrentT A =25°C AI D -9-7-60V MaximumUnits Parameter Absolute Maximum Ratings T A =25°C unless otherwise noted V ±8Gate-Source Voltage Drain-Source Voltage -12°C/W R θJA 487462.5°CThermal Characteristics Units ParameterTyp Max 1.28T A =70°CJunction and Storage Temperature Range -55 to 150G1S1G2S2D1D1D2D224513867 Top ViewSOIC-8Top View Bottom ViewPin1G1D11S1RgG2D2S2RgSymbolMin Typ Max Units BV DSS -12VV DS =-12V, V GS =0V-1T J =55°C-5I GSS ±10µA V GS(th)Gate Threshold Voltage -0.35-0.53-0.85V I D(ON)-60A 1619T J =125°C22271924m Ω2330m Ωg FS 45S V SD -0.56-1V I S-3A C iss 139017402100pF C oss 230334435pF C rss 120200280pF R g0.9 1.3 1.7k ΩQ g (4.5V)151923nC Q gs 3.6 4.5 5.4nC Q gd 35.37.4nC t D(on)240ns t r 580ns t D(off)7µs t f 4.2µst rr 182226ns Q rr141720nCTHIS PRODUCT HAS BEEN DESIGNED AND QUALIFIED FOR THE CONSUMER MARKET. APPLICATIONS OR USES AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS ARE NOT AUTHORIZED. AOS DOES NOT ASSUME ANY LIABILITY ARISING OUT OF SUCH APPLICATIONS OR USES OF ITS PRODUCTS. AOS RESERVES THE RIGHT TO IMPROVE PRODUCT DESIGN,FUNCTIONS AND RELIABILITY WITHOUT NOTICE.Body Diode Reverse Recovery TimeDrain-Source Breakdown Voltage On state drain currentI D =-250µA, V GS =0V V GS =-4.5V, V DS =-5V V GS =-4.5V, I D =-9AReverse Transfer Capacitance I F =-9A, dI/dt=500A/µsV GS =0V, V DS =-6V, f=1MHz SWITCHING PARAMETERS Electrical Characteristics (T J =25°C unless otherwise noted)STATIC PARAMETERS ParameterConditions I DSS µA V DS =V GS I D =-250µA V DS =0V, V GS = ±8V Zero Gate Voltage Drain Current Gate-Body leakage current Forward Transconductance Diode Forward VoltageR DS(ON)Static Drain-Source On-Resistancem ΩI S =-1A,V GS =0VV DS =-5V, I D =-9A V GS =-1.8V, I D =-6AV GS =-2.5V, I D =-8A Gate resistanceV GS =0V, V DS =0V, f=1MHzTurn-Off Fall TimeTotal Gate Charge V GS =-4.5V, V DS =-6V, I D =-9AGate Source Charge Gate Drain Charge Body Diode Reverse Recovery Charge I F =-9A, dI/dt=500A/µsMaximum Body-Diode Continuous CurrentInput Capacitance Output CapacitanceTurn-On DelayTime DYNAMIC PARAMETERS Turn-On Rise Time Turn-Off DelayTime V GS =-4.5V, V DS =-6V, R L =0.67Ω,R GEN =3ΩA. The value of R θJA is measured with the device mounted on 1in 2FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The value in any given application depends on the user's specific board design.B. The power dissipation P D is based on T J(MAX)=150°C, using ≤ 10s junction-to-ambient thermal resistance.C. Repetitive rating, pulse width limited by junction temperature T J(MAX)=150°C. Ratings are based on low frequency and duty cycles to keep initialT J =25°C.D. The R θJA is the sum of the thermal impedence from junction to lead R θJL and lead to ambient.E. The static characteristics in Figures 1 to 6 are obtained using <300µs pulses, duty cycle 0.5% max.F. These curves are based on the junction-to-ambient thermal impedence which is measured with the device mounted on 1in 2 FR-4 board with 2oz. Copper, assuming a maximum junction temperature of T J(MAX)=150°C. The SOA curve provides a single pulse ratin g.TYPICAL ELECTRICAL AND THERMAL CHARACTERISTICS5101520Q g (nC)Figure 7: Gate-Charge Characteristics-V G S (V o l t s )24681012-V DS (Volts)Figure 8: Capacitance Characteristics C a p a c i t a n c e (p F )VdsCharge Gate Charge Test Circuit & WaveformD iode RVVddVddVR esistive S w itching Test C ircuit & W aveform s分销商库存信息: AOSAO4821。

LTC4411ES5#TRMPBF;LTC4411ES5#TR;LTC4411ES5#TRPBF;LTC4411ES5#TRM;中文规格书,Datasheet资料

IFWD

Figure 1. Automatic Switchover of Load Between a Battery and a Wall Adapter

VFWD

/

U

LTC4411 vs Schottky Diode Forward Voltage Characteristics

LTC4411 2.6A Low Loss Ideal Diode in ThinSOTTM

FEATURES

■ ■ ■ ■ ■ ■ ■ ■ ■ ■ ■ ■

ቤተ መጻሕፍቲ ባይዱ

DESCRIPTIO

Low Loss Replacement for PowerPathTM OR’ing Diodes Small Regulated Forward Voltage (28mV) 2.6A Maximum Forward Current Low Forward ON Resistance (140mΩ Max) Low Reverse Leakage Current (<1µA) 2.6V to 5.5V Operating Range Internal Current Limit Protection Internal Thermal Protection No External Active Components Pin-Compatible Monolithic Replacement for the LTC4412 Low Quiescent Current (40µA) Low-Profile (1mm) 5-lead SOT-23 Package

●

ELECTRICAL CHARACTERISTICS

STAT Output IS(SNK) IS(OFF) tS(ON) tS(OFF) CTL Input VTH VHYST ICTL IOC IQOC

222,AL,222,BK,222,GY, 规格书,Datasheet 资料

/Products/Accessories/CircuitBoard/drawings/CB_12X.pdf

A

1.85 Insert Area .09 typ. for #4 screw

TOP

.10 typ.

.26 2 plc's

.31 4 plc's

BOTTOM

1.28

2.81

PART NO. 2-2 22 1095 6005 DESCRIPTION (Included) TOP BOTTOM Battery Cover #4X3/8” self tapping (2) ACCSESSORIES (Optional) PART NO. 319 419 DESCRIPTION Prototype grid board (Bottom) Prototype clad board (Bottom)

3D model options: a) Zoom in & out with center wheel. b) Pause at any moment to view and or print views. c) Change the views to ortho and section views if needed from the Views pull down menu. d) Explore options included in the tool bar like: Views, Transparency of model, Lighting type, etc.

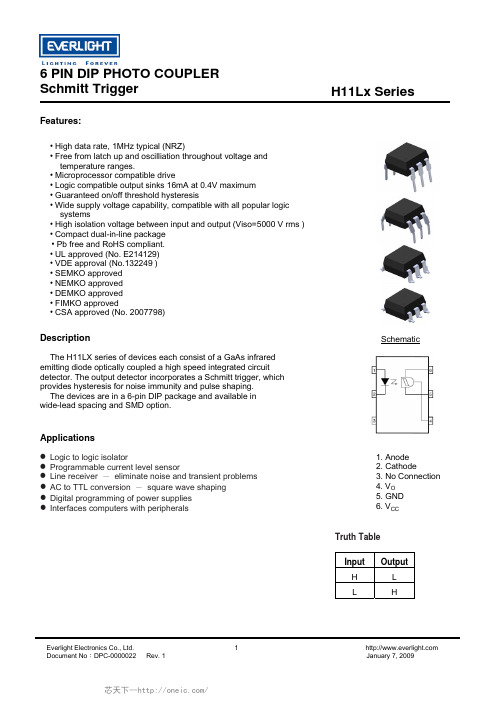

H11L1S(TA),H11L1S(TA),H11L1S(TA),H11L1M,H11L1,H11L2M,H11L2,H11L3M, 规格书,Datasheet 资料

Schmitt TriggerH11Lx SeriesFeatures:• High data rate, 1MHz typical (NRZ)• Free from latch up and oscilliation throughout voltage and temperature ranges.• Microprocessor compatible drive• Logic compatible output sinks 16mA at 0.4V maximum • Guaranteed on/off threshold hysteresis• Wide supply voltage capability, compatible with all popular logic systems• High isolation voltage between input and output (Viso=5000 V rms ) • Compact dual-in-line package • Pb free and RoHS compliant. • UL approved (No. E214129) • VDE approval (No.132249 ) • SEMKO approved • NEMKO approved • DEMKO approved• FIMKO approved• CSA approved (No. 2007798)SchematicDescriptionThe H11LX series of devices each consist of a GaAs infrared emitting diode optically coupled a high speed integrated circuit detector. The output detector incorporates a Schmitt trigger, which provides hysteresis for noise immunity and pulse shaping. The devices are in a 6-pin DIP package and available in wide-lead spacing and SMD option.Applications1. Anode2. Cathode3. No Connection4. V O5. GND6. V CCz Logic to logic isolatorz Programmable current level sensorz Line receiver - eliminate noise and transient problems z AC to TTL conversion - square wave shaping z Digital programming of power supplies z Interfaces computers with peripheralsTruth TableInput Output H L L HSchmitt Trigger H11Lx SeriesAbsolute Maximum Ratings (T a =25°C)Parameter Symbol Rating Unit Forward currentI F 60 mA Reverse voltage V R 6 V InputPower dissipation P D 120 mW V 45 Allowed RangeV o 0 to 16 V V 65 Allowed Range V CC3 to 16VOutput Current I 0 50 mA Outputpower dissipationP D 150 mW Total power dissipation P tot 250 mW Isolation voltage *1 V iso 5000 V rms Operating temperature T opr -55~+100 °C Storage temperature T stg -55~+150 °C Soldering temperature *2 T sol260 °CNotes*1 AC for 1 minute, R.H.= 40 ~ 60% R.H. In this test, pins 1, 2 & 3 are shorted together, and pins 4, 5 & 6 are shorted together. *2 For 10 seconds.Schmitt Trigger H11Lx SeriesElectrical Characteristics (T a =25°C unless specified otherwise)InputParameter Symbol Min. Typ.* Max. Unit ConditionForward voltageV F - 1.15 1.5 V I F = 10mA Reverse Leakage current I R - - 10 µA V R = 5VCapacitanceC J- - 100 pF V=0, f=1MHzOutputParameter Symbol Min. Typ.* Max. Unit ConditionOperation Voltage Range V CC 3 - 15 V Supply Current I CC(off) - 1.6 5 mA I F =0mA, Vcc=5V Output Current, High I OH- - 100 µA I F =0mA, Vcc=Vo=15VIsolation ResistanceR ISO 1011- -Ω V I-O =500VDCTransfer CharacteristicsParameter Symbol Min. Typ.* Max. Unit ConditionSupply Current I CC(on) - 1.6 5 mA I F =10mA, Vcc=5V Output Voltage .lowV OL- - 0.4 VVcc=5V, I F =I Fon (max.), R L =270ΩH11L1 - -1.6 H11L2 - - 10Turn on ThresholdCurrent 1H11L3I Fon- - 5 mA Vcc=5V, R L =270Ω Turn off Threshold Current I Foff - 1 - mA Vcc=5V, R L =270Ω Hysteresis Ratio I Fon /I Foff 0.5 - 0.9 Vcc=5V, R L =270ΩTurn on Time t on - - 4 μS Fall Time t r - 0.1 - μS Turn off Time t off - - 4 μS Rise Time t r - 0.1 - μS Vcc=5V, I F =I Fon , R L =270ΩData Rate- 1 - MHz* Typical values at T a = 25°C 1. Max. I F(ON) is the maximum current required to trigger the output. For examples, a 1.6mA maximum trigger current would require the LED to be driven at a current greater than 1.6mA to guarantee the device will turn on. A 10% guard band is recommended to account for degradation of the LED over its lifetime. The maximum allowable LED drive current is 60mA.Schmitt TriggerH11Lx SeriesTypical Performance CurvesSchmitt TriggerH11Lx SeriesOrder InformationPart NumberH11LXY(Z)-VNoteX = Part No. for 1, 2 or 3Y = Lead form option (S, S1, M or none)Z = Tape and reel option (TA, TB or none).V = VDE (optional)quantity Option Description PackingNone Standard DIP-6 65 units per tubeM Wide lead bend (0.4 inch spacing) 65 units per tubeS + TA Surface mount lead form + TA tape & reel option 1000 units per reelS + TB Surface mount lead form + TB tape & reel option 1000 units per reelS1 + TA Surface mount lead form (low profile) + TA tape & reel option 1000 units per reelS1 + TB Surface mount lead form (low profile) + TB tape & reel option 1000 units per reelSchmitt Trigger H11Lx SeriesPackage Drawings(Dimensions in mm)Standard DIP TypeOption M TypeSchmitt Trigger H11Lx Seriesption S1 TypeOSchmitt Trigger H11Lx Series Recommended pad layout for surface mount leadformevice Markingotesdenotes EverlightberDELH11L3YW WVNLEH11L3 denotes Device NumY denotes 1 digit Year codeWW denotes 2 digit Week codeV denotes VDE (optional)Schmitt Trigger H11Lx SeriesTape & Reel Packing Specificationsape dimensionsE FTDimension No. A B Do D1 Dimension (mm)10.4±0.1 7.52±0.1 1.5±0.1 1.5+0.1/-0 1.75±0.1 7.5±0.1Dimension No. Po P1 P2 tW KDimension (mm)4.0±0.15 1.6±0.1 2.0±0.1 0.35±0.03 16.0±0.2 4.5±0.1Schmitt Trigger H11Lx Series Solder Reflow Temperature ProfileTIME (S)6 PIN DIP PHOTO COUPLERSchmitt Trigger Everlight Electronics Co., Ltd. 11 Document No :DPC-0000022 Rev. 1 January 7, 2009H11Lx Series DISCLAIMERThe specifications in this datasheet may be changed without notice. EVERLIGHT reserves the authority . When using this product, please observe the absolute maximum ratings and the instructions for use as the 3. hese specification sheets include materials protected under copyright of EVERLIGHT. Reproduction in1.on material change for above specification.2outlined in this datasheet. EVERLIGHT assumes no responsibility for any damage resulting from use of product which does not comply with the absolute maximum ratings and the instructions included in this datasheet.T any form is prohibited without the specific consent of EVERLIGHT.芯天下--/。

SE5004L-R;SE5004L-EK1;中文规格书,Datasheet资料

DATA SHEETSE5004L: 5 GHz, 26dBm Power Amplifier with Power DetectorApplicationsDSSS 5 GHz WLAN (IEEE802.11a) DSSS 5 GHz WLAN (IEEE802.11n) Access Points, PCMCIA, PC cardsFeaturesHigh output power amplifier- 26dBm at 5VExternal Analog Reference Voltage (V REF ) for maximum flexibilityBuffered, temperature compensated power detector3% EVM, @26dBm, 64 QAM, 54 Mbps 32 dB GainLead Free, RoHS compliant, halogen free MSL3 package20 pin 4 mm x 4 mm x 0.9 mm QFNOrdering InformationPart Number Package Remark SE5004L 20 Pin QFN Samples SE5004L-R 20 Pin QFN Tape and Reel SE5004L-EK1Evaluation KitStandardProduct DescriptionThe SE5004L is a 5GHz power amplifier offering high linear power for wireless LAN applications. The SE5004L incorporates a power detector for closed loop monitoring and control of the output power.The SE5004L offers high integration for a simplified design, providing quicker time to market and higher application board production yield. The device integrates the input match, the inter-stage match, the output match, the power detectorwith 15dB of dynamic range and a 3.8GHz notch filter. Only 6 external decoupling capacitors are required to complete the design.For wireless LAN applications, the device meets the requirements of IEEE802.11a & 802.11n, and delivers approximately 26dBm of linear output power at 5V.The SE5004L integrates temperature compensated bias voltage generators. A 2.85V reference voltage on VREF is all that is required to enable or disable the power amplifier.Functional Block DiagramRFIN and RFOUT include DC shunt to Ground. External blocking capacitors are recommended.Figure 1: Functional Block DiagramDATA SHEETSE5004L: 5 GHz, 26dBm Power Amplifier with Power DetectorFigure 2: SE5004L Pin Out (Top View Through Package) Pin Out DescriptionPin No. Name Description1 NU Pin is not used, and is open circuit in the package2 GND Ground3 RFin Power Amplifier RF input, DC block required4 GND Ground5 V REF Reference Voltage6 SP1 Port for optional capacitor to improve dynamic EVM7 SP2 Port for optional capacitor to improve dynamic EVM8 VCC2 Second Stage Supply Voltage9 VCC3 Third Stage Supply Voltage10 DET Analog Power Detector Output11,12 GND Ground13 RF OUT Power Amplifier RF Output14-17 GND Ground18 VCC3 Third Stage Supply Voltage19 VCC2 Second Stage Supply Voltage20 VCC1 First Stage Supply VoltageDATA SHEETSE5004L: 5 GHz, 26dBm Power Amplifier with Power DetectorAbsolute Maximum RatingsThese are stress ratings only. Exposure to stresses beyond these maximum ratings for a long period of time may cause permanent damage to, or affect the reliability of the device. Avoid operating the device outside the recommended operating conditions defined below. This device is ESD sensitive. Handling and assembly of this device should be at ESD protected workstations.Symbol Definition Min. Max. UnitV CC Supply Voltage on pins VCC3 -0.3 +6V Supply Voltage on pins VCC1, VCC2 -0.3 VCC3V REF Power Amplifier Enable and Reference Voltage -0.3 3.6 V RF IN RF Input Power, RFout into 50Ω match, T CASE_MAX = 85C - 6 dBm T STG Storage Temperature Range -40 160 °C T j Maximum Junction Temperature - 160 °C ESD HBM JEDEC JESD22-A114 all pins - 500 VRecommended Operating ConditionsSymbol Parameter Min. Max. UnitV CC Supply Voltage VCC3 3.0 5.5V Supply Voltage VCC1, VCC2 3.0 VCC3T CASE_MAX Maximum Case Temperature -40 85 °C V REF Reference Voltage 2.8 2.9 VDC Electrical CharacteristicsConditions: V CC= 5.0V, V REF = 2.85 V, T A = 25 °C, as measured on Skyworks Solutions’ SE5004L-EK1 evaluation board, unless otherwise noted.Symbol Parameter Conditions Min. Typ. Max. Unit I CC-802.11a Supply Current P OUT = 26 dBm, 54 Mbps, 64 QAM - 600 800 mAI QC Quiescent Current No RF - 300 - mAI OFF Supply Current V REF = 0 V, No RF - 0.5 10 µAIEN Bias ControlCurrentV REF = V REF HInternal 2KΩ pull down resistor- 10 - mAV REF H Reference VoltageEnabled- 2.80 2.85 2.9 VV REF L Reference VoltageDisabled- 0 - 0.5 VDATA SHEETSE5004L: 5 GHz, 26dBm Power Amplifier with Power DetectorAC Electrical Characteristics802.11a AC Electrical CharacteristicsConditions: V CC = 5.0 V, V REF = 2.85 V, f = 5.4 GHz, T A = 25 °C, as measured on Skyworks Solutions’ SE5004L-EK1 evaluation board, unless otherwise notedSymbol Parameter Conditions Min. Typ. Max. Unitf L-U Frequency Range - 5.15 - 5.85 GHzP OUT Output Power 802.11a, 54Mbps, 64 QAM, 3% EVM 25.5 26 -dBm 802.11a, 54Mbps, 64 QAM, 2.5% EVM 24.5 25802.11n, MCS0, Mask Compliant - 29 -P1dB Output 1dBcompression pointNo modulation 30 34 - dBmS21Small Signal Gain P IN = -25 dBm 30 32 - dB∆S21Gain Variation Within each UNII Band - 3 - dB∆S21 3.8Gain at 3.8GHz P IN = -25 dBm - - 0 dB 2fHarmonic P OUT = 26 dBm, 5V - - -45 dBm/MHz 3ft r, t f Rise and Fall Time - - 0.15 0.3 usSTAB Stability P OUT = 26 dBm, VCC = 5V, 54 Mbps,64 QAM, VSWR = 6:1, all phasesAll non-harmonically related outputsless than -50 dBc/100 kHzRugged Tolerance toconstant inputpower into amismatch loadP IN = -10dBm, CW,VSWR = 6:1, all phasesNo damageDATA SHEETSE5004L: 5 GHz, 26dBm Power Amplifier with Power DetectorPower DetectorConditions: V CC= 5.0 V, V REF=2.85V, f = 5.4 GHz, T A = 25 °C, as measured on Skyworks Solutions’ SE5004L-EK1Figure 3: SE5004L Power Detector Characteristic over FrequencyDATA SHEETSE5004L: 5 GHz, 26dBm Power Amplifier with Power Detector Package DiagramFigure 4: SE5004L Package InformationDATA SHEETSE5004L: 5 GHz, 26dBm Power Amplifier with Power Detector Recommended Land and Solder PatternFigure 5: SE5004L Recommended Land PatternPackage Handling InformationBecause of its sensitivity to moisture absorption, instructions on the shipping container label must be followed regarding exposure to moisture after the container seal is broken, otherwise, problems related to moisture absorption may occur when the part is subjected to high temperature during solder assembly. The SE5004L is capable of withstanding a Pb free solder reflow. Care must be taken when attaching this product, whether it is done manually or in a production solder reflow environment. If the part is manually attached, precaution should be taken to insure that the device is not subjected to temperatures above its rated peak temperature for an extended period of time. For details on both attachment techniques, precautions, and handling procedures recommended, please refer to:“Quad Flat No-Lead Module Solder Reflow & Rework Information”, Document Number QAD-00045“Handling, Packing, Shipping and Use of Moisture Sensitive QFN”, Document Number QAD-00044 Caution! Class 1B ESD sensitive deviceDATA SHEETSE5004L: 5 GHz, 26dBm Power Amplifier with Power DetectorBranding InformationFigure 6: SE5004L Branding InformationTape and Reel InformationParameterValue Devices Per Reel 3000 Reel Diameter 13 inches Tape Width12 millimetersFigure 7: SE5004L-R Tape and Reel InformationDATA SHEETSE5004L: 5 GHz, 26dBm Power Amplifier with Power Detector Document Change HistoryRevision Date Notes1.0 Aug 18, 2009 Created1.1 Jan 14, 2010 Updated Pinout1.2 May 4, 2010 Updated harmonic specification1.3 May 7, 2010 Update T RISE and T FALL time Added MSL rating1.4 May 20, 2010 Update Recommended Land and Solder Pattern Update detector plot.1.5 Jul 20, 2010 Extended operating temperature range to -40C to +85C Updated absolute maximum ratings for VCC1 and VCC2 Updated EN pull down resistor value1.6 Nov 20, 2010 Update Maximum Junction Temperature Updated ESD rating1.7 Feb 25, 2011 Added Mask complianceAdded Vref min/max limits to recommended operating conditions1.8 Apr 02, 2012 Updated with Skyworks logo and disclaimer statement1.9 Apr 12, 2012 Added min/max limits to Gain, P1dB, EVM, ICCCopyright © 2012 Skyworks Solutions, Inc. All Rights Reserved.Information in this document is provided in connection with Skyworks Solutions, Inc. (“Skyworks”) products or services. These materials, including the information contained herein, are provided by Skyworks as a service to its customers and may be used for informational purposes only by the customer. Skyworks assumes no responsibility for errors or omissions in these materials or the information contained herein. Skyworks may change its documentation, products, services, specifications or product descriptions at any time, without notice. Skyworks makes no commitment to update the materials or information and shall have no responsibility whatsoever for conflicts, incompatibilities, or other difficulties arising from any future changes.No license, whether express, implied, by estoppel or otherwise, is granted to any intellectual property rights by this document. Skyworks assumes no liability for any materials, products or information provided hereunder, including the sale, distribution, reproduction or use of Skyworks products, information or materials, except as may be provided in Skyworks Terms and Conditions of Sale.THE MATERIALS, PRODUCTS AND INFORMATION ARE PROVIDED “AS IS” WITHOUT WARRANTY OF ANY KIND, WHETHER EXPRESS, IMPLIED, STATUTORY, OR OTHERWISE, INCLUDING FITNESS FOR A PARTICULAR PURPOSE OR USE, MERCHANTABILITY, PERFORMANCE, QUALITY OR NON-INFRINGEMENT OF ANY INTELLECTUAL PROPERTY RIGHT; ALL SUCH WARRANTIES ARE HEREBY EXPRESSLY DISCLAIMED. SKYWORKS DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. SKYWORKS SHALL NOT BE LIABLE FOR ANY DAMAGES, INCLUDING BUT NOT LIMITED TO ANY SPECIAL, INDIRECT, INCIDENTAL, STATUTORY, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS THAT MAY RESULT FROM THE USE OF THE MATERIALS OR INFORMATION, WHETHER OR NOT THE RECIPIENT OF MATERIALS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.Skyworks products are not intended for use in medical, lifesaving or life-sustaining applications, or other equipment in which the failure of the Skyworks products could lead to personal injury, death, physical or environmental damage. Skyworks customers using or selling Skyworks products for use in such applications do so at their own risk and agree to fully indemnify Skyworks for any damages resulting from such improper use or sale.Customers are responsible for their products and applications using Skyworks products, which may deviate from published specifications as a result of design defects, errors, or operation of products outside of published parameters or design specifications. Customers should include design and operating safeguards to minimize these and other risks. Skyworks assumes no liability for applications assistance, customer product design, or damage to any equipment resulting from the use of Skyworks products outside of stated published specifications or parameters.Skyworks, the Skyworks symbol, and “Breakthrough Simplicity” are trademarks or registered trademarks of Skyworks Solutions, Inc., in the United States and other countries. Third-party brands and names are for identification purposes only, and are the property of their respective owners. Additional information, including relevant terms and conditions, posted at , are incorporated by reference.分销商库存信息:SKYWORKS-SOLUTIONSSE5004L-R SE5004L-EK1。

m1ma141kt1g, m1ma142kt1g 单片硅开关二极管 数据表说明书

M1MA141KT1G,M1MA142KT1GSingle Silicon Switching DiodeThis Silicon Epitaxial Planar Diode is designed for use in ultra high speed switching applications.This device is housed in the SC--70 package which is designed for low power surface mount applications. Features∙Fast t rr,<3.0ns∙Low C D,<2.0pF∙These Devices are Pb--Free,Halogen Free/BFR Free and are RoHS CompliantMAXIMUM RATINGS(T A=25︒C)Rating Symbol Value UnitReverse VoltageM1MA141KT1M1MA142KT1V R4080VdcPeak Reverse VoltageM1MA141KT1M1MA142KT1V RM4080VdcForward Current I F100mAdc Peak Forward Current I FM225mAdcPeak Forward Surge Current I FSM(Note1)500mAdcTHERMAL CHARACTERISTICSRating Symbol Max Unit Power Dissipation P D150mW Junction Temperature T J150︒C StorageTemperature T stg--55~+150︒C Stresses exceeding Maximum Ratings may damage the device.MaximumRatings are stress ratings only.Functional operation above the Recommended Operating Conditions is not implied.Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.1.t=1secSC--70(SOT--323)CASE419STYLE2MARKING DIAGRAMMx=Device Codex=H for141I for142M=Date Code*G=Pb--Free PackageDevice Package Shipping†ORDERING INFORMATION†For information on tape and reel specifications, including part orientation and tape sizes,please refer to our Tape and Reel Packaging Specifications Brochure,BRD8011/D.Mx M GGM1MA142KT1G SC--70(Pb--Free)3000/Tape&Reel M1MA141KT1G SC--70(Pb--Free)3000/Tape&Reel (Note:Microdot may be in either location)*Date Code orientation may vary depending upon manufacturing location.CATHODE12ELECTRICAL CHARACTERISTICS(T A=25 C)Characteristic Condition Symbol Min Max Unit Reverse Voltage Leakage CurrentM1MA141KT1 M1MA142KT1V R=35VV R=75VI R--0.1m AdcForward Voltage I F=100mA V F-- 1.2VdcReverse Breakdown VoltageM1MA141KT1M1MA142KT1I R=100m A V R4080--VdcDiode Capacitance V R=0,f=1.0MHz C D-- 2.0pFReverse Recovery Time(Figure1)I F=10mA,V R=6.0V,R L=100Ω,I rr=0.1I Rt rr(Note2)-- 3.0ns2.t rr Test CircuitRt p =2m s t r =0.35nsrr RI F =10mA V R =6V R L =100ΩRECOVERY TIME EQUIVALENT TEST CIRCUITINPUT PULSEOUTPUT PULSEFigure 1.Recovery Time Equivalent Test Circuit100V F ,FORWARD VOLTAGE (VOLTS)101.00.110V R ,REVERSE VOLTAGE (VOLTS)1.00.10.010.0010.680V R ,REVERSE VOLTAGE (VOLTS)0.640.60.560.52C D ,D I O D E C A P A C I T A N C E (p F )2468I F ,F O R W A R D C U R R E N T (m A )Figure 2.Forward Voltage Figure 3.Reverse CurrentFigure 4.Diode CapacitanceI R ,R E V E R S E C U R R E N T (μA )SC −70 (SOT −323)CASE 419ISSUE PDATE 07 OCT 2021SCALE 4:1STYLE 3:PIN 1.BASE2.EMITTER3.COLLECTOR STYLE 4:PIN 1.CATHODE2.CATHODE3.ANODE STYLE 2:PIN 1.ANODE2.N.C.3.CATHODE STYLE 1:CANCELLEDSTYLE 5:PIN 1.ANODE 2.ANODE 3.CATHODE STYLE 6:PIN 1.EMITTER 2.BASE3.COLLECTORSTYLE 7:PIN 1.BASE 2.EMITTER 3.COLLECTORSTYLE 8:PIN 1.GATE 2.SOURCE 3.DRAINSTYLE 9:PIN 1.ANODE 2.CATHODE3.CATHODE-ANODESTYLE 10:PIN 1.CATHODE 2.ANODE3.ANODE-CATHODEXX M G G XX = Specific Device Code M = Date CodeG= Pb −Free PackageGENERICMARKING DIAGRAM1STYLE 11:PIN 1.CATHODE2.CATHODE3.CATHODE*This information is generic. Please refer to device data sheet for actual part marking.Pb −Free indicator, “G” or microdot “G ”, may or may not be present. Some products maynot follow the Generic Marking.MECHANICAL CASE OUTLINEPACKAGE DIMENSIONSPUBLICATION ORDERING INFORMATIONTECHNICAL SUPPORTNorth American Technical Support:Voice Mail: 1 800−282−9855 Toll Free USA/Canada Phone: 011 421 33 790 2910LITERATURE FULFILLMENT :Email Requests to:*******************onsemi Website: Europe, Middle East and Africa Technical Support:Phone: 00421 33 790 2910For additional information, please contact your local Sales Representative。

TL499开关电源芯片

IMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.Customers are responsible for their applications using TI components.In order to minimize risks associated with the customer’s applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI’s publication of information regarding any third party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 2000, Texas Instruments Incorporated。

LM4992中文资料