IP核(LPM模块)的EDA软件应用

EDA技术与应用_EDA工具软件的使用

EDA技术与应用_EDA工具软件的使用EDA(Electronic Design Automation)是电子设计自动化的缩写,它是指利用计算机及相关软件来进行电子系统的设计、验证、优化和制造的技术。

在电子系统设计领域,EDA技术的发展极大地提高了设计效率和设计质量,成为现代电子系统设计的基础工具。

本文将介绍EDA工具软件的使用。

EDA工具软件是指用于辅助电子系统设计的计算机软件。

这些软件通常包括电子系统设计的各个阶段,如系统级设计、高层次合成、逻辑综合、布局布线、时序验证等。

以下是几种常见的EDA工具软件及其使用方法。

1. Cadence OrCAD:Cadence OrCAD是一款综合性的PCB设计软件。

它包括原理图设计、仿真、PCB布局和布线等功能。

使用者可以通过绘制原理图、添加元器件、进行仿真和布局布线,完成电路设计的各个阶段。

该软件支持多种电路仿真和分析方法,如时域仿真、频域仿真和信号完整性分析等。

2. Mentor Graphics PADS:Mentor Graphics PADS是一款专业的PCB设计软件。

它提供了全面的电路板设计解决方案,包括原理图设计、PCB布局和布线、验证和制造输出等功能。

使用者可以通过绘制原理图、进行布局布线、进行信号完整性分析等,完成整个电路板设计的过程。

4. Cadence Allegro:Cadence Allegro是一款专业的PCB布局和布线软件。

它提供了全面的设计环境,包括原理图设计、PCB布局和布线、SI分析和制造输出等功能。

使用者可以通过绘制原理图、进行PCB布局和布线,完成电路板的设计和优化。

5. Synopsis PrimeTime:Synopsis PrimeTime是一款静态时序验证工具。

它能够对电路设计进行时序分析,确定电路的最大工作频率和最小工作延迟。

使用者可以通过提供设计约束和输入电路网表,运行时序验证的脚本,获取电路设计的时序分析结果。

集成电路芯片设计中的EDA工具分析与应用

集成电路芯片设计中的EDA工具分析与应用随着科技的不断发展,电子信息产业日益壮大,而集成电路芯片作为其中重要的一环,更是日新月异地更新换代。

因此,如何提高设计效率,缩短设计周期,保证设计质量成为许多芯片设计人员重要的任务。

在众多的芯片设计工具中,EDA(Electronic Design Automation)工具更是广受芯片设计人员的欢迎和选择。

本文将就EDA工具在集成电路芯片设计中的应用进行分析和阐述,力求为芯片设计人员提供一些有用的参考和启示。

一、EDA工具的基本概念和分类EDA工具是计算机辅助电子设计的软件工具,主要用于电子系统设计、电路设计、布图设计等方面。

EDA工具主要包括逻辑设计、物理布局和模拟仿真工具。

其中逻辑设计工具包括逻辑合成器、逻辑优化器、逻辑仿真器等;物理布局工具包括版图画图工具、版图编辑器和版图布局工具等;模拟仿真工具包括SPICE仿真器、数字仿真器和混合仿真器等。

在EDA工具的分类中,常见的包括ASIC工具、FPGA工具和PCB工具三种。

ASIC工具主要用于设计大规模集成电路(LSI)和超大规模集成电路(VLSI),主要包括逻辑合成器、布图编辑器、仿真器等。

ASIC工具的主要作用是将逻辑电路转化为物理电路,削减设计周期,缩小设计代价,保证设计质量。

FPGA工具主要用于设计可重构逻辑电路(FPGA),主要包括RTL设计工具、版本管理工具、FPGA逻辑合成器等。

FPGA工具的主要作用是提供硬件逻辑模拟、快速开发逻辑电路的设计、快速验证功能正确与否的载板测试,以及对标准接口的支持等功能。

PCB工具主要用于设计PCB电路板,主要包括电路板布图软件、PCB制造软件等。

PCB工具的主要作用是将芯片设计的电路板经过布图之后制作成PCB板,为芯片的后续步骤做好准备。

二、EDA工具在集成电路芯片设计中的应用分析EDA工具在集成电路芯片设计中的应用,主要有以下几个方面:1.简化设计流程EDA工具能够有效地简化芯片设计的流程。

EDA技术及应用第3章-LPM

(3)保存文件

要保存文件,选择 File\Save As 选项,弹出 Save As 对话 框。如图所示。

(4). 电路仿真

(1)MAX PLUS /Compiler 编译电路图 (2)MAX PLUS / Waver form-editer 编译波形图 (3)选择 Enter Node from SNF 选项并按鼠标左键 确认,出现如图所示对话框

第三章[2]

第3章 LPM兆功能块使用方法

LPM兆功能块使用方法 1》常用LPM兆功能块 P64--65 1)常用LPM兆功能块 LPM_AND ; LPM_OR ; 2)常用LPM兆功能块 LPM_MUX ; LPM_COUNTER 3)常用LPM兆功能块 LPM_ADD_SUB; 4)常用LPM兆功能块

LPM_FF; LPM_LATCH; LPM_SHIFTREG;

LPM兆功能块使用方法 1)常用LPM兆功能块 LPM_AND ;

LPM兆功能块使用方法 1)常用LPM兆功能块 LPM_OR ;

LPM兆功能块使用方法 2)常用LPM兆功能块 LPM_MUX ;

LPM兆功能块使用方法 2)常用LPM兆功能块 LPM_COUNTER

3)பைடு நூலகம்成60分频器

1)使用LPM兆功能块做6分频器

1)使用LPM兆功能块做6分频器

2)使用LPM兆功能块做10分频器

2)使用LPM兆功能块做10分频器

3)合成60分频器

3)合成60分频器

波形输入法:

1》

XXX . WDF

波形输入法: 1》

波形输入法: 1》

【1】原理图设计方法 (1)创建一个新文件

《EDA技术应用》IP核分类与MC8051 IP核

2. MC8051 IP核

(3)顶层结构

每个模块源代码由二 个文件构成,文件名以 ‘ _’下划线结束的为模 块实体定义,文件名 以”_rtl”或”_struc” 结束的为模块结构体定义。

MC8051 IP Core 的设计层次

11

2. MC8051 IP核

(4)彩灯控制器MC8051处理器的顶层原理图设计

顶层设计由MC8051内核、内部ROM和RAM、PLL四部分构成

12

谢谢 !

13

Байду номын сангаас

《EDA技术应用》

IP核分类与MC8051 IP核

1

目录

1

IP 核的分类

2

MC8051 IP核

2

1. IP核分类

根据IP核存在的形式可以分为HDL语言、网表、 版图三种不同的类型,即对应人们常说的软IP核、固IP 核和硬IP核三种IP核。

3

1. IP核分类

(1)软IP核

软IP核是用VHDL等硬件描述语言描述的功能块,并通过了行 为级设计优化和功能验证,但不包含任何具体的物理信息。软IP核 通一般以硬件描述语言HDL源文件的形式出现,应用开发过程与普 通的HDL设计相似,通常以加密形式提供,其实际的RTL对用户不 可见。软IP核设计周期短,设计投入少。

7

2. MC8051 IP核

(1)MC8051简介

MC8051 IP核是由德国的Oregano Systems公司与维也纳理 工大学CAD工作组合作开发的开源项目,采用完全同步的方式进行 设计,指令集和MCS-51系列微控制器完全兼容。

标准的MCS-51单片机为2个定时器/计数器,1个串口和2个外 部中断。MC8051中,这些单元根据实际的需要最多可增加到 256 组。MC8051广泛用于SoC应用系统。

EDA实验5报告 - 副本

对D/A的接口和控制技术;

1、 画出波形发生器的系统结构图,分别说明波形发生 器控制模块和波形数据存储模块的作用和设计要 求;**

2、 根据示例,完成波形发生器和扫频信号源的设计和 仿真测试;**

3、 定制数据宽度为8、地址宽度为6的ROM元件,及其 64点正弦波数据文件;**

输出信号幅度

(V)“滤波1”

(2) 系统时钟(CLK)与输出信号频率范围的关系(波形数据点数: ) 系统时钟CLK 12MHz 6MHz 3MHz 1.5MHz 50MHz

输出信号最高频 率

输出信号最低频 率

(3) 输出信号幅频特性(波形数据点数: 128)

a. 测试条件:系统时钟CLK=12 MHz,“滤波1”模式;

2、 硬件验证:实

(1) 输出信号幅频特性

a. 测试条件:系统时钟CLK=12

MHz,滤波模

式“0”和“1”;

b. 波形数据点数: ;输出信号频率范围:

;

输出信号频率 1Hz 10Hz 100Hz 500 1KHz 5KHz 10KHz Hz

输出信号幅度 (V)“滤波0”

正弦波数据文件;** 9、 用定制的ROM元件替换示例中的内部ROM,然后对新设计

进行仿真测试;** 10、 在4基础上选择合适的电路结构,在实验系统上对新设

计进行硬件测试。

实验报告要求

画出本项设计的完整电路图,说明其工作原理;叙述示例的工作 原理,以及基于LPM_ROM的VHDL电路设计内容和测试、验证内容。 系统设计说明: 3、 波形发生器的系统结构图

b. 输出信号频率范围:

;幅度范围:

基于EDA 工具评测数字IP 软核

基于EDA工具评测数字IP软核许海辉张溯章伟合肥工业大学微电子设计研究所(230009)Email:xuhaihuixp@摘要:伴随着集成电路IP的推广和使用,面临着如何衡量一个IP质量的好坏、如何准确快速地选择IP等问题。

因此需要一种有效的手段对IP质量进行评测,这也就要求有一套操作性强的评测标准,并实现对IP质量进行客观、快速地评测。

针对以上要求,本文探索了可供EDA工具度量的评测指标以及这些指标的评测方法,然后根据提出的指标和方法,完成了三个IP的量化评测,从而说明了这种质量评测方法的可操作性和有效性。

关键词:IP; 质量; 评测; EDA.1.引言现在IP市场保持快速增长,据调查,每年增长40%。

因为上市时间仍然是一项产品成功的重要因素,所以要求快速有效地对IP进行选择。

如果对IP质量的评估不到位,那么就很难进行快速选择。

另外IP的质量标准和IP的开发规范,业界还没有统一。

因此需要一种新的方法学来统一IP质量评测标准,而且需要自动化的工具来支持评测过程。

美国IP标准组织VSIA[1]开发了一种技术方法来改进IP的质量,并且使IP更容易集成到SoC平台中。

同时《可重用方法学》(RMM)起到了同样的效果,并指导IP产品化。

但是所有的准则和建议项都需要手动来进行检查。

现在还没有非常全面的能自动度量IP质量的方法。

现在大部分IP开发商和用户都按照VSIA和VCX的标准进行交易,但是IP开发商并没有提供工具来展示他们交付的IP的质量。

除了VSIA和RMM提供的准则指南以外,还有一些独立的工具对IP准则进行检查,例如代码覆盖率和综合工具等。

这些工具可以用来对IP 部分质量指标进行评估。

1现在对IP质量评测手段主要有三种:一是基于Web的回答问题的方式[2];二是电子表格度量程序,如OpenMORE和QIP[ 3][4];三是基于EDA工具度量过程。

前两种都是以IP质量标准为基础,但是现有的IP核质量标准都不是很全面、客观,而且可操作性不是很强、自动化程度不高。

EDA选择题(含答案)

一、选择题:(20分)1.大规模可编程器件主要有FPGA、CPLD两类,下列对CPLD结构与工作原理的描述中,正确的是:___D__A. CPLD是基于查找表结构的可编程逻辑器件B. CPLD即是现场可编程逻辑器件的英文简称C. 早期的CPLD是从FPGA的结构扩展而来D. 在Xilinx公司生产的器件中,XC9500系列属CPLD结构2.基于VHDL设计的仿真包括有①门级时序仿真、②行为仿真、③功能仿真和④前端功能仿真这四种,按照自顶向下的设计流程,其先后顺序应该是:_________DA.①②③④ B.②①④③C.④③②①D.②④③①3.IP核在EDA技术和开发中具有十分重要的地位,IP分软IP、固IP、硬IP;下列所描述的IP核中,对于固IP的正确描述为:__________DA.提供用VHDL等硬件描述语言描述的功能块,但不涉及实现该功能块的具体电路B.提供设计的最总产品——模型库C.以可执行文件的形式提交用户,完成了综合的功能块D.都不是4.下面对利用原理图输入设计方法进行数字电路系统设计,哪一种说法是正确的:__________BA.原理图输入设计方法直观便捷,很适合完成较大规模的电路系统设计B.原理图输入设计方法一般是一种自底向上的设计方法C.原理图输入设计方法无法对电路进行功能描述D.原理图输入设计方法不适合进行层次化设计5.在VHDL语言中,下列对进程(PROCESS)语句的语句结构及语法规则的描述中,不正确的是:_______DA.PROCESS为一无限循环语句B.敏感信号发生更新时启动进程,执行完成后,等待下一次进程启动C.当前进程中声明的变量不可用于其他进程D.进程由说明语句部分、并行语句部分和敏感信号参数表三部分组成6.对于信号和变量的说法,哪一个是不正确的:_________AA.信号用于作为进程中局部数据存储单元B.变量的赋值是立即完成的C.信号在整个结构体内的任何地方都能适用D.变量和信号的赋值符号不一样7.下列状态机的状态编码,_________方式有“输出速度快、难以有效控制非法状态出现”这个特点。

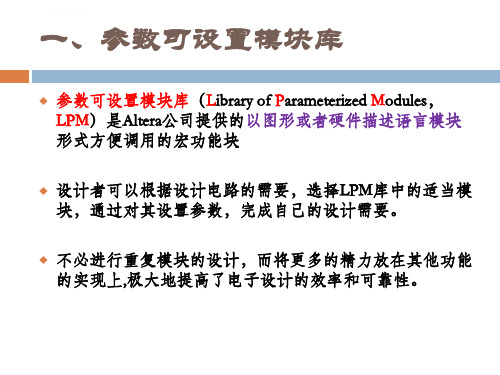

第7章 LPM宏模块的应用

E D A 技 术 与 应 用

通过Quartus II设置DSP模块构建:Assignments→Setting,在 左栏选择Analysis&Synthesis Settings项,在对话框中按More Settings按钮,在弹出的对话框中选择DSP Block Balancing项 的DSP blocks。

(2)文件直接编辑法:

使用Quartus II以外的编辑器设计.mif文件

E D A 技 术 与 应 用

例7-5:编辑器设计.mif文件

DEPTH=128; :数据深度,即存储的数据个数 WIDTH=8; :输出数据宽度 ADDRESS_RADIX=HEX;:地址数据类型,HEX表示选择十六进制 数据类型 DATA_RADIX=HEX;:存储数据类型,HEX表示选择十六进制数据 类型 CONTENT :此为关键词 BEGIN :此为关键词 0000 : 0080; 0001 : 0086; 0002 : 008C; …(数据略去) 007E : 0073; 007F : 0079; END;

1. .mif格式文件

E D A 技 术 mif数据表格中键入数据。 表格中的数据格式可通过右击 窗口边缘的地址数据所弹出的 窗口中选择。

表中任一数据对应的地址为左 列数与顶行数之和。

完成数据输入后,选择 File→Save As,保存此数据文 件,如取名为data7X8.mif。

E D A 技 术 与 应 用

例化语句中,未设定的端口必须接上特定的电平。

计数器模块lpm_counter是一个可设定参数的封闭模块,只 能通过参数传递说明语句defparam将用户设定的参数通过 文件CNT4B.v传递进lpm_counter中。

参数可设置宏功能模块lpm的应用ppt课件

end component;

begin

u1:rom0 port map (clock=>clk,address(7 downto 4)=>b,address(3 downto 0)=>a,q=>q);

end;

为了规范事业单位聘用关系,建立和 完善适 应社会 主义市 场经济 体制的 事业单 位工作 人员聘 用制度 ,保障 用人单 位和职 工的合 法权益

二、利用lpm-rom设计一个乘法器

波形仿真

➢ 新建波形文件→调入节点端口→设置仿真激励(过程同全 加器波形仿真) 设置时钟信号

分离窗口 选择工具

全屏 查找 未初始化 设置低电平0 高阻态 弱逻辑0 无关 数据总线设置

文字编辑 移动工具

未定义信号 设置高电平1

弱未知 弱逻辑1

反转 时钟设置 随机值

二、利用lpm-rom设计一个乘法器

设置存储单元数目与数据宽度

存储单 元数目 数据位 宽

为了规范事业单位聘用关系,建立和 完善适 应社会 主义市 场经济 体制的 事业单 位工作 人员聘 用制度 ,保障 用人单 位和职 工的合 法权益

二、利用lpm-rom设计一个乘法器

3、实验步骤

配置乘法表数据文件 File→New→Memory Files→Memory Initialization File (或者Hexadecimal Intel Format File)

为了规范事业单位聘用关系,建立和 完善适 应社会 主义市 场经济 体制的 事业单 位工作 人员聘 用制度 ,保障 用人单 位和职 工的合 法权益

二、利用lpm-rom设计一个乘法器

定制lpm_rom元件 Tools→MegaWizard Plug-In Manager

教学课件:第7章-LPM参数化宏模块应用

导出数据

用户可以将LPM中的数据导出到 Excel中,以便进行更深入的数据 分析和可视化。

共享数据

通过集成,LPM和Excel可以共享数 据,确保两个工具中的数据保持一 致,提高工作效率。

与Power BI的集成

数据可视化

数据交互

LPM参数化宏模块可以与Power BI集 成,将数据从LPM中导入到Power BI 中进行数据可视化。

的共享和传输。

自动化流程

通过集成,用户可以使用其他应 用程序中的自动化功能,实现

LPM参数化宏模块的自动化运行, 提高工作效率。

插件扩展

LPM参数化宏模块可以通过插件 扩展与其他应用程序进行集成, 实现更广泛的应用场景和功能。

05

总结与展望

总结

LPM参数化宏模块应用是教学课件第7章的核心内容,通过这一章节的学习,学生可以了解 LPM参数化宏模块的基本概念、原理和应用方法。

功能

LPM参数化宏模块具有高度的可 配置性和可扩展性,能够满足用 户多样化的需求,同时提高软件 开发的效率和灵活性。

应用场景与优势

应用场景

LPM参数化宏模块广泛应用于各种 软件领域,如游戏开发、仿真软件、 工业控制软件等。

优势

LPM参数化宏模块的优势在于其可定 制性和灵活性,能够快速适应不同的 应用场景和需求,同时减少软件开发 的时间和成本。

教学课件:第7章-lpm参 数化宏模块应用

• 引言 • LPM参数化宏模块概述 • LPM参数化宏模块应用实例 • LPM参数化宏模块与其他工具的集成 • 总结与展望

01

引言

主题介绍

lpm参数化宏模块应用

介绍lpm参数化宏模块的基本概念、功能和特点。

EDA工具在电子设计中的应用

EDA工具在电子设计中的应用EDA工具(Electronic Design Automation)是指通过计算机辅助设计来快速、高效地完成电子产品设计的一种工具。

它主要涉及到电路设计、PCB设计、芯片设计等方面,已经成为现代电子设计中不可或缺的重要工具。

下面将详细介绍EDA工具在电子设计中的应用。

一、电路设计方面的应用1. 电路仿真EDA工具提供了丰富的电路仿真功能,可以通过虚拟实验来验证电路的性能和稳定性,节省了大量的实验时间和成本。

2. 电路自动布局EDA工具提供了自动布局功能,可以根据设计需求自动放置和布线,简化了设计过程,提高了设计效率和准确度。

3. 电路优化EDA工具可以通过优化算法对电路进行优化,提高电路的性能和可靠性,减少功耗和成本,并满足设计约束条件。

二、PCB设计方面的应用1. PCB布局EDA工具可以根据设计要求进行PCB元件的布局,包括引脚分配、尺寸匹配、信号线长度匹配等,确保电路板的稳定性和可靠性。

2. PCB布线EDA工具提供了智能布线功能,可以根据设计规范和限制条件自动完成信号线的布线,减少信号干扰和噪声,提高信号完整性。

3. PCB仿真EDA工具可以进行PCB的电磁仿真,评估电路板的电磁兼容性和抗干扰性能,避免信号串扰和电磁泄漏的问题。

三、芯片设计方面的应用1. 逻辑综合EDA工具可以将高层次的逻辑电路描述转换成低层次的综合电路,实现逻辑功能的实现和优化。

2. 物理设计EDA工具可以进行芯片的物理布局和布线,确保电路的性能和可靠性,并满足功耗和面积的要求。

3. 时序分析EDA工具可以进行芯片的时序分析,保证芯片的稳定性和正常工作,避免时钟延迟和时序冲突的问题。

四、EDA工具的详细步骤1. 设计准备在进行电子设计前,需要明确设计目标和需求,并做好相应的准备工作,包括电路元件的选型、PCB板的材料和尺寸等。

2. 电路设计根据设计目标和需求,使用EDA工具进行电路设计,包括电路的拓扑结构、元件的参数和标号等。

基于EDA软件和FPGA的IP核保护技术

基于EDA软件和FPGA的IP核保护技术随着规模不断扩大,以及竞争带来的上市时光的压力,越来越多的电路设计者开头利用设计良好的、经反复验证的电路功能模块来加快设计进程。

这些电路功能模块被称为IP(Intellectual Property)核。

IP核由相应领域的专业人员设计,并经反复验证。

IP核的拥有者可通过出售IP猎取利润。

利用IP核,设计者只需做很少设计就可实现所需系统。

基于IP核的模块化设计可缩短设计周期,提高设计质量。

现场可编程门阵列具有可编程特性,用户按照特定的应用定制电路结构,因此其处理速度大大超过通用处理器。

与ASIC相比,FPGA的缺点是在提供灵便的可编程同时,则以芯片的面积、功耗和速度做为代价。

近年来,单个FPGA实现电路规模不断扩大,设计者可以在单个FPGA 上实现一个完整的系统(System on Pro—grammablb Chip,简称SoPC)。

IP核的浮现为SoPC的设计提供极大方便,利用IP核,设计者通过模块化设计。

轻松迅速地实现系统复杂的功能。

当设计者从第三方购买IP,需要一定的庇护机制防止设计者在非授权IP核用法,以庇护IP核全部者的利益。

同时,对于设计者完成的设计,也需要相应的庇护机制防止设计被非法复制、窃取或篡改。

为此,提出一种结合设计(Electronic Design Automation,简称)软件和FPGA 的IP核庇护机制。

通过在EDA工具中加入庇护机制防止设计者非授权用法IP核,在FPGA中加入庇护机制防止设计被非法复制、窃取或篡改。

2 EDA软件中实现IP庇护FPGA的设计开发流程主要包括行为综合、规律综合、技术映射和布局布线。

普通状况,设计者用法硬件描述语言(如,Velilog)描述电路,然后由EDA软件对其处理。

在EDA软件处理流程中,行为综合把算法级或寄存器传输级(Register Transfer Level,简称RTL)的电路描述转换为门级的网表,规律综合优化门级网表,技术映射是将优化后的网表映射为FPGA中的详细实现第1页共5页。

IP在EDA技术的应用和发展中的意义

IP在EDA技术的应用和发展中的意义IP在EDA技术的应用和发展中的意义1、前言人类社会已进入到高度发达的信息化社会,信息社会的发展离不开电子产品的进步。

现代电子产品在性能提高、复杂度增大的同时,价格却一直呈下降趋势,而且产品更新换代的步伐也越来越快,实现这种进步的主要原因就是生产制造技术和电子设计技术的发展。

前者以微细加工技术为代表,目前已进展到深亚微米阶段,可以在几平方厘米的芯片上集成数千万个晶体管;后者的核心就是EDA技术。

EDA是指以计算机为工作平台,融合了应用电子技术、计算机技术、智能化技术最新成果而研制成的电子CAD通用软件包,主要能辅助进行三方面的设计工作:IC设计,电子电路设计以及PCB设计。

没有EDA技术的支持,想要完成上述超大规模集成电路的设计制造是不可想象的,反过来,生产制造技术的不断进步又必将对EDA技术提出新的要求。

2、EDA技术的发展回顾近30年电子设计技术的发展历程,可将EDA技术分为三个阶段。

七十年代为CAD阶段,这一阶段人们开始用计算机辅助进行IC版图编辑和PCB布局布线,取代了手工操作,产生了计算机辅助设计的概念。

八十年代为CAE阶段,与CAD相比,除了纯粹的图形绘制功能外,又增加了电路功能设计和结构设计,并且通过电气连接网络表将两者结合在一起,以实现工程设计,这就是计算机辅助工程的概念。

CAE的主要功能是:原理图输入,逻辑仿真,电路分析,自动布局布线,PCB后分析。

九十年代为ESDA阶段。

尽管CAD/CAE技术取得了巨大的成功,但并没有把人从繁重的设计工作中彻底解放出来。

在整个设计过程中,自动化和智能化程度还不高,各种EDA软件界面千差万别,学习使用困难,并且互不兼容,直接影响到设计环节间的衔接。

基于以上不足,人们开始追求贯彻整个设计过程的自动化,这就是ESDA 即电子系统设计自动化。

3、ESDA技术的基本特征ESDA代表了当今电子设计技术的最新发展方向,它的基本特征是:设计人员按照"自顶向下"的设计方法,对整个系统进行方案设计和功能划分,系统的关键电路用一片或几片专用集成电路(ASIC)实现,然后采用硬件描述语言(HDL)完成系统行为级设计,最后通过综合器和适配器生成最终的目标器件。

用EDA设计全数字三相昌闸管触发器IP软核

用EDA设计全数字三相昌闸管触发器IP软核 IP(Intellectual Propcrty)就是常说的知识产权。

美国Dataquest咨询公司将半导体产业的IP定义为用于ASIC、ASSP和PLD等当中,并且是预先设计好的电路模块。

IP核模块有行为(Behavior)、结构(Structure)和物理(Physical)_三级不同程度的设计。

根据描述功能行为的不同,IP核分为三类。

即软核(Soft IP Corc)、完成结构描述的固核(Firm IP Core)和基于物理描述并经过工艺验证的硬核(Hard IP Core)。

IP软核通常是用HDL文奉形式提交给用户,它经过RTL级设计优化和功能验证,但其中不含有任何具体的物理信息。

据此,用户可以综合出正确的门电路级设计网表,并可以进行后续的结构设计,具有很大的灵活性;借助于EDA综合工具可以很容易地与其他外部逻辑电路合成一体,根据各种不同半导体工艺,设计成具有不同性能的器件。

本文利用先进的EDA软件,用VHDL硬件描述语言采用自顶向下的模块化设计方法,完成了具有相序自适应功能的双脉冲数字移相触发器的IP软核设计。

1 三相全控桥整流电路 如图1所示,三相全控桥整流电路由6只晶闸管组成。

共阴极组侧和共阳级组侧的各3只晶闸管相互换流,在电源的一个周期内获得6次换流的脉动波形。

三相全控桥整流电路在任何时刻必须保证有两个不同组别的晶闸管同时导通才能构成回路。

换流只在本组内进行,每隔120°换流一次。

由于共阴级组与共阳级组的换流点相隔60°,所以每隔60°有一个元件换流。

同组内各晶闸管的触发脉冲相位差为120°,接在同一相的两个元件的触发脉冲相位差为180°,而相邻两脉冲的相位差是60°。

2 IP软核设计。

IP核(LPM模块)的EDA软件应用

班级:10集成、姓名:崔冰、学号:1015251005 实验四、IP核(LPM模块)的EDA软件应用一、工作原理:正弦波信号发生器的结构由4部分组成:计数器或地址发生器(6位);正弦信号数据ROM(6位地址线,8位数据线),含有64个8位数据VHDL顶层设计;8位D/A。

顶层文件Singt。

Vhdl在FPGA中实现,包含两个部分:ROM的地址发生器,由6位计数器担任;正弦数据ROM,由LPM ROM模块构成;LPM_ROM底层是FPGA中的EAB 或M9K等模块。

地址发生器的时钟CLK的输入频率f0下每周期的波型数据点数,以及D/A 输出的频率f的关系是:f=f0/64。

二、定制初始化数据文件:使用mif型或hex型,例如:三、定制ROM:-- megafunction wizard: %ROM: 1-PORT%-- GENERATION: STANDARD-- VERSION: WM1.0-- MODULE: altsyncram-- ============================================================-- File Name: ROM.vhd-- Megafunction Name(s):-- altsyncram---- Simulation Library Files(s):-- altera_mf-- ============================================================-- ************************************************************-- THIS IS A WIZARD-GENERA TED FILE. DO NOT EDIT THIS FILE!---- 7.2 Build 151 09/26/2007 SJ Full Version-- ************************************************************--Copyright (C) 1991-2007 Altera Corporation--Your use of Altera Corporation's design tools, logic functions--and other software and tools, and its AMPP partner logic--functions, and any output files from any of the foregoing--(including device programming or simulation files), and any--associated documentation or information are expressly subject--to the terms and conditions of the Altera Program License--Subscription Agreement, Altera MegaCore Function License--Agreement, or other applicable license agreement, including,--without limitation, that your use is for the sole purpose of--programming logic devices manufactured by Altera and sold by--Altera or its authorized distributors. Please refer to the--applicable agreement for further details.LIBRARY ieee;USE ieee.std_logic_1164.all;LIBRARY altera_mf;USE altera_mf.all;ENTITY ROM ISPORT(address : IN STD_LOGIC_VECTOR (5 DOWNTO 0);clock : IN STD_LOGIC ;q : OUT STD_LOGIC_VECTOR (7 DOWNTO 0) );END ROM;ARCHITECTURE SYN OF rom ISSIGNAL sub_wire0 : STD_LOGIC_VECTOR (7 DOWNTO 0);COMPONENT altsyncramGENERIC (clock_enable_input_a : STRING;clock_enable_output_a : STRING;init_file : STRING;intended_device_family : STRING;lpm_hint : STRING;lpm_type : STRING;numwords_a : NATURAL;operation_mode : STRING;outdata_aclr_a : STRING;outdata_reg_a : STRING;widthad_a : NATURAL;width_a : NATURAL;width_byteena_a : NATURAL);PORT (clock0 : IN STD_LOGIC ;address_a : IN STD_LOGIC_VECTOR (5 DOWNTO 0);q_a : OUT STD_LOGIC_VECTOR (7 DOWNTO 0) );END COMPONENT;BEGINq <= sub_wire0(7 DOWNTO 0);altsyncram_component : altsyncramGENERIC MAP (clock_enable_input_a => "BYPASS",clock_enable_output_a => "BYPASS",init_file => "dizhi.hex",intended_device_family => "Cyclone II",lpm_hint => "ENABLE_RUNTIME_MOD=NO",lpm_type => "altsyncram",numwords_a => 64,operation_mode => "ROM",outdata_aclr_a => "NONE",outdata_reg_a => "UNREGISTERED",widthad_a => 6,width_a => 8,width_byteena_a => 1)PORT MAP (clock0 => clock,address_a => address,q_a => sub_wire0);END SYN;-- ============================================================-- CNX file retrieval info-- ============================================================-- Retrieval info: PRIV ATE: ADDRESSSTALL_A NUMERIC "0"-- Retrieval info: PRIV ATE: AclrAddr NUMERIC "0"-- Retrieval info: PRIV ATE: AclrByte NUMERIC "0"-- Retrieval info: PRIV ATE: AclrOutput NUMERIC "0"-- Retrieval info: PRIV ATE: BYTE_ENABLE NUMERIC "0"-- Retrieval info: PRIV ATE: BYTE_SIZE NUMERIC "8"-- Retrieval info: PRIV ATE: BlankMemory NUMERIC "0"-- Retrieval info: PRIV ATE: CLOCK_ENABLE_INPUT_A NUMERIC "0"-- Retrieval info: PRIV ATE: CLOCK_ENABLE_OUTPUT_A NUMERIC "0"-- Retrieval info: PRIV ATE: Clken NUMERIC "0"-- Retrieval info: PRIV ATE: IMPLEMENT_IN_LES NUMERIC "0"-- Retrieval info: PRIV ATE: INIT_FILE_LAYOUT STRING "PORT_A"-- Retrieval info: PRIV ATE: INIT_TO_SIM_X NUMERIC "0"-- Retrieval info: PRIV ATE: INTENDED_DEVICE_FAMIL Y STRING "Cyclone II"-- Retrieval info: PRIV ATE: JTAG_ENABLED NUMERIC "0"-- Retrieval info: PRIV ATE: JTAG_ID STRING "NONE"-- Retrieval info: PRIV ATE: MAXIMUM_DEPTH NUMERIC "0"-- Retrieval info: PRIV ATE: MIFfilename STRING "dizhi.hex"-- Retrieval info: PRIV ATE: NUMWORDS_A NUMERIC "64"-- Retrieval info: PRIV ATE: RAM_BLOCK_TYPE NUMERIC "0"-- Retrieval info: PRIV ATE: RegAddr NUMERIC "1"-- Retrieval info: PRIV ATE: RegOutput NUMERIC "0"-- Retrieval info: PRIV ATE: SYNTH_WRAPPER_GEN_POSTFIX STRING "0"-- Retrieval info: PRIV ATE: SingleClock NUMERIC "1"-- Retrieval info: PRIV ATE: UseDQRAM NUMERIC "0"-- Retrieval info: PRIV ATE: WidthAddr NUMERIC "6"-- Retrieval info: PRIV ATE: WidthData NUMERIC "8"-- Retrieval info: PRIV ATE: rden NUMERIC "0"-- Retrieval info: CONSTANT: CLOCK_ENABLE_INPUT_A STRING "BYPASS"-- Retrieval info: CONSTANT: CLOCK_ENABLE_OUTPUT_A STRING "BYPASS"-- Retrieval info: CONSTANT: INIT_FILE STRING "dizhi.hex"-- Retrieval info: CONSTANT: INTENDED_DEVICE_FAMIL Y STRING "Cyclone II" -- Retrieval info: CONSTANT: LPM_HINT STRING "ENABLE_RUNTIME_MOD=NO" -- Retrieval info: CONSTANT: LPM_TYPE STRING "altsyncram"-- Retrieval info: CONSTANT: NUMWORDS_A NUMERIC "64"-- Retrieval info: CONSTANT: OPERATION_MODE STRING "ROM"-- Retrieval info: CONSTANT: OUTDA TA_ACLR_A STRING "NONE"-- Retrieval info: CONSTANT: OUTDA TA_REG_A STRING "UNREGISTERED"-- Retrieval info: CONSTANT: WIDTHAD_A NUMERIC "6"-- Retrieval info: CONSTANT: WIDTH_A NUMERIC "8"-- Retrieval info: CONSTANT: WIDTH_BYTEENA_A NUMERIC "1"-- Retrieval info: USED_PORT: address 0 0 6 0 INPUT NODEFVAL address[5..0]-- Retrieval info: USED_PORT: clock 0 0 0 0 INPUT NODEFV AL clock-- Retrieval info: USED_PORT: q 0 0 8 0 OUTPUT NODEFV AL q[7..0]-- Retrieval info: CONNECT: @address_a 0 0 6 0 address 0 0 6 0-- Retrieval info: CONNECT: q 0 0 8 0 @q_a 0 0 8 0-- Retrieval info: CONNECT: @clock0 0 0 0 0 clock 0 0 0 0-- Retrieval info: LIBRARY: altera_mf altera_mf.altera_mf_components.all-- Retrieval info: GEN_FILE: TYPE_NORMAL ROM.vhd TRUE-- Retrieval info: GEN_FILE: TYPE_NORMAL ROM.inc FALSE-- Retrieval info: GEN_FILE: TYPE_NORMAL ROM.cmp TRUE-- Retrieval info: GEN_FILE: TYPE_NORMAL ROM.bsf FALSE-- Retrieval info: GEN_FILE: TYPE_NORMAL ROM_inst.vhd FALSE-- Retrieval info: GEN_FILE: TYPE_NORMAL ROM_waveforms.html TRUE-- Retrieval info: GEN_FILE: TYPE_NORMAL ROM_wave*.jpg FALSE-- Retrieval info: LIB_FILE: altera_mf四、正弦波的顶层文件:LIBRARY IEEE; --正弦信号发生器源文件USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY SINGT ISPORT ( CLK : IN STD_LOGIC; --信号源时钟DOUT : OUT STD_LOGIC_VECTOR (7 DOWNTO 0) );--8位波形数据输出END;ARCHITECTURE DACC OF SINGT ISCOMPONENT ROM --调用波形数据存储器LPM_ROM文件:data_rom.vhd声明PORT(address : IN STD_LOGIC_VECTOR (5 DOWNTO 0);--6位地址信号clock : IN STD_LOGIC ;--地址锁存时钟q : OUT STD_LOGIC_VECTOR (7 DOWNTO 0) );END COMPONENT;SIGNAL Q1 : STD_LOGIC_VECTOR (5 DOWNTO 0); --设定内部节点作为地址计数器BEGINPROCESS(CLK ) --LPM_ROM地址发生器进程BEGINIF CLK'EVENT AND CLK = '1' THEN Q1<=Q1+1; --Q1作为地址发生器计数器END IF;END PROCESS;u1 : ROM PORT MAP(address=>Q1, q => DOUT,clock=>CLK);--例化END;五、1、功能仿真图:2、时序仿真图:分析:随着clk时钟每一个上升沿的到来,ROM中存放的数据依次送出,经历64位时钟上升沿,正弦波洽为一个周期。

eda 基于IP的设计

5.1 IP核 5.2 触发器IP核的VHDL设计应用 5.3 存储器IP核的VHDL设计应用 5.4 锁相环IP核的VHDL设计应用 5.5 运算电路IP核的VHDL设计应用

5.1 IP核

IP(Intellectual Property)本来是指知识产 权、著作权等,在IC设计领域通常被理解为 实现某种功能的设计。

Altera公司及其IP合作伙伴提供的IP功能模块

免费的LPM宏功能模块(Megafunctions/LPM) 需要授权使用的IP知识产权(MEGACORE)。

通过菜单Tools > Megawizard Plug-In Manager可以启动 Altera LPM宏功能模块设计功能

图5-1 MegaWizard Plug-In Manager启动界面

2.单端口RAM的参数设置如图所示,包括4个部分:

存储器内容初始化文件: 新建“Memory Initialization File”文件 设置内存大小

填写初始内容并保存

存储器是FPGA设计中常用模块,包括RAM、ROM 等。

如果需要对存储器初始化,首先要建立内存初 始化文件(*.mif);

C0是inclk0的3倍频 C1是inclk0的3/4分频

仿真结果如下:

图5-17 锁相环PLL的仿真结果

5.5运算电路IP核的VHDL设计应用

Quartus II软件的参数化模块库对运算单元IP模块有 很好的支持,常用数学运算都可以在这里完成。

利用参数化模块库调用运算IP可以很好的利用 FPGA芯片内部集成的乘法器等资源。

IP核则是完成某种常用但是比较复杂的算法 或功能功能的参数可修改的电路模块,又 称为IP模块。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

班级:10集成、姓名:崔冰、学号:1015251005 实验四、IP核(LPM模块)的EDA软件应用一、工作原理:正弦波信号发生器的结构由4部分组成:计数器或地址发生器(6位);正弦信号数据ROM(6位地址线,8位数据线),含有64个8位数据VHDL顶层设计;8位D/A。

顶层文件Singt。

Vhdl在FPGA中实现,包含两个部分:ROM的地址发生器,由6位计数器担任;正弦数据ROM,由LPM ROM模块构成;LPM_ROM底层是FPGA中的EAB 或M9K等模块。

地址发生器的时钟CLK的输入频率f0下每周期的波型数据点数,以及D/A 输出的频率f的关系是:f=f0/64。

二、定制初始化数据文件:使用mif型或hex型,例如:三、定制ROM:-- megafunction wizard: %ROM: 1-PORT%-- GENERATION: STANDARD-- VERSION: WM1.0-- MODULE: altsyncram-- ============================================================-- File Name: ROM.vhd-- Megafunction Name(s):-- altsyncram---- Simulation Library Files(s):-- altera_mf-- ============================================================-- ************************************************************-- THIS IS A WIZARD-GENERA TED FILE. DO NOT EDIT THIS FILE!---- 7.2 Build 151 09/26/2007 SJ Full Version-- ************************************************************--Copyright (C) 1991-2007 Altera Corporation--Your use of Altera Corporation's design tools, logic functions--and other software and tools, and its AMPP partner logic--functions, and any output files from any of the foregoing--(including device programming or simulation files), and any--associated documentation or information are expressly subject--to the terms and conditions of the Altera Program License--Subscription Agreement, Altera MegaCore Function License--Agreement, or other applicable license agreement, including,--without limitation, that your use is for the sole purpose of--programming logic devices manufactured by Altera and sold by--Altera or its authorized distributors. Please refer to the--applicable agreement for further details.LIBRARY ieee;USE ieee.std_logic_1164.all;LIBRARY altera_mf;USE altera_mf.all;ENTITY ROM ISPORT(address : IN STD_LOGIC_VECTOR (5 DOWNTO 0);clock : IN STD_LOGIC ;q : OUT STD_LOGIC_VECTOR (7 DOWNTO 0) );END ROM;ARCHITECTURE SYN OF rom ISSIGNAL sub_wire0 : STD_LOGIC_VECTOR (7 DOWNTO 0);COMPONENT altsyncramGENERIC (clock_enable_input_a : STRING;clock_enable_output_a : STRING;init_file : STRING;intended_device_family : STRING;lpm_hint : STRING;lpm_type : STRING;numwords_a : NATURAL;operation_mode : STRING;outdata_aclr_a : STRING;outdata_reg_a : STRING;widthad_a : NATURAL;width_a : NATURAL;width_byteena_a : NATURAL);PORT (clock0 : IN STD_LOGIC ;address_a : IN STD_LOGIC_VECTOR (5 DOWNTO 0);q_a : OUT STD_LOGIC_VECTOR (7 DOWNTO 0) );END COMPONENT;BEGINq <= sub_wire0(7 DOWNTO 0);altsyncram_component : altsyncramGENERIC MAP (clock_enable_input_a => "BYPASS",clock_enable_output_a => "BYPASS",init_file => "dizhi.hex",intended_device_family => "Cyclone II",lpm_hint => "ENABLE_RUNTIME_MOD=NO",lpm_type => "altsyncram",numwords_a => 64,operation_mode => "ROM",outdata_aclr_a => "NONE",outdata_reg_a => "UNREGISTERED",widthad_a => 6,width_a => 8,width_byteena_a => 1)PORT MAP (clock0 => clock,address_a => address,q_a => sub_wire0);END SYN;-- ============================================================-- CNX file retrieval info-- ============================================================-- Retrieval info: PRIV ATE: ADDRESSSTALL_A NUMERIC "0"-- Retrieval info: PRIV ATE: AclrAddr NUMERIC "0"-- Retrieval info: PRIV ATE: AclrByte NUMERIC "0"-- Retrieval info: PRIV ATE: AclrOutput NUMERIC "0"-- Retrieval info: PRIV ATE: BYTE_ENABLE NUMERIC "0"-- Retrieval info: PRIV ATE: BYTE_SIZE NUMERIC "8"-- Retrieval info: PRIV ATE: BlankMemory NUMERIC "0"-- Retrieval info: PRIV ATE: CLOCK_ENABLE_INPUT_A NUMERIC "0"-- Retrieval info: PRIV ATE: CLOCK_ENABLE_OUTPUT_A NUMERIC "0"-- Retrieval info: PRIV ATE: Clken NUMERIC "0"-- Retrieval info: PRIV ATE: IMPLEMENT_IN_LES NUMERIC "0"-- Retrieval info: PRIV ATE: INIT_FILE_LAYOUT STRING "PORT_A"-- Retrieval info: PRIV ATE: INIT_TO_SIM_X NUMERIC "0"-- Retrieval info: PRIV ATE: INTENDED_DEVICE_FAMIL Y STRING "Cyclone II"-- Retrieval info: PRIV ATE: JTAG_ENABLED NUMERIC "0"-- Retrieval info: PRIV ATE: JTAG_ID STRING "NONE"-- Retrieval info: PRIV ATE: MAXIMUM_DEPTH NUMERIC "0"-- Retrieval info: PRIV ATE: MIFfilename STRING "dizhi.hex"-- Retrieval info: PRIV ATE: NUMWORDS_A NUMERIC "64"-- Retrieval info: PRIV ATE: RAM_BLOCK_TYPE NUMERIC "0"-- Retrieval info: PRIV ATE: RegAddr NUMERIC "1"-- Retrieval info: PRIV ATE: RegOutput NUMERIC "0"-- Retrieval info: PRIV ATE: SYNTH_WRAPPER_GEN_POSTFIX STRING "0"-- Retrieval info: PRIV ATE: SingleClock NUMERIC "1"-- Retrieval info: PRIV ATE: UseDQRAM NUMERIC "0"-- Retrieval info: PRIV ATE: WidthAddr NUMERIC "6"-- Retrieval info: PRIV ATE: WidthData NUMERIC "8"-- Retrieval info: PRIV ATE: rden NUMERIC "0"-- Retrieval info: CONSTANT: CLOCK_ENABLE_INPUT_A STRING "BYPASS"-- Retrieval info: CONSTANT: CLOCK_ENABLE_OUTPUT_A STRING "BYPASS"-- Retrieval info: CONSTANT: INIT_FILE STRING "dizhi.hex"-- Retrieval info: CONSTANT: INTENDED_DEVICE_FAMIL Y STRING "Cyclone II" -- Retrieval info: CONSTANT: LPM_HINT STRING "ENABLE_RUNTIME_MOD=NO" -- Retrieval info: CONSTANT: LPM_TYPE STRING "altsyncram"-- Retrieval info: CONSTANT: NUMWORDS_A NUMERIC "64"-- Retrieval info: CONSTANT: OPERATION_MODE STRING "ROM"-- Retrieval info: CONSTANT: OUTDA TA_ACLR_A STRING "NONE"-- Retrieval info: CONSTANT: OUTDA TA_REG_A STRING "UNREGISTERED"-- Retrieval info: CONSTANT: WIDTHAD_A NUMERIC "6"-- Retrieval info: CONSTANT: WIDTH_A NUMERIC "8"-- Retrieval info: CONSTANT: WIDTH_BYTEENA_A NUMERIC "1"-- Retrieval info: USED_PORT: address 0 0 6 0 INPUT NODEFVAL address[5..0]-- Retrieval info: USED_PORT: clock 0 0 0 0 INPUT NODEFV AL clock-- Retrieval info: USED_PORT: q 0 0 8 0 OUTPUT NODEFV AL q[7..0]-- Retrieval info: CONNECT: @address_a 0 0 6 0 address 0 0 6 0-- Retrieval info: CONNECT: q 0 0 8 0 @q_a 0 0 8 0-- Retrieval info: CONNECT: @clock0 0 0 0 0 clock 0 0 0 0-- Retrieval info: LIBRARY: altera_mf altera_mf.altera_mf_components.all-- Retrieval info: GEN_FILE: TYPE_NORMAL ROM.vhd TRUE-- Retrieval info: GEN_FILE: TYPE_NORMAL ROM.inc FALSE-- Retrieval info: GEN_FILE: TYPE_NORMAL ROM.cmp TRUE-- Retrieval info: GEN_FILE: TYPE_NORMAL ROM.bsf FALSE-- Retrieval info: GEN_FILE: TYPE_NORMAL ROM_inst.vhd FALSE-- Retrieval info: GEN_FILE: TYPE_NORMAL ROM_waveforms.html TRUE-- Retrieval info: GEN_FILE: TYPE_NORMAL ROM_wave*.jpg FALSE-- Retrieval info: LIB_FILE: altera_mf四、正弦波的顶层文件:LIBRARY IEEE; --正弦信号发生器源文件USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY SINGT ISPORT ( CLK : IN STD_LOGIC; --信号源时钟DOUT : OUT STD_LOGIC_VECTOR (7 DOWNTO 0) );--8位波形数据输出END;ARCHITECTURE DACC OF SINGT ISCOMPONENT ROM --调用波形数据存储器LPM_ROM文件:data_rom.vhd声明PORT(address : IN STD_LOGIC_VECTOR (5 DOWNTO 0);--6位地址信号clock : IN STD_LOGIC ;--地址锁存时钟q : OUT STD_LOGIC_VECTOR (7 DOWNTO 0) );END COMPONENT;SIGNAL Q1 : STD_LOGIC_VECTOR (5 DOWNTO 0); --设定内部节点作为地址计数器BEGINPROCESS(CLK ) --LPM_ROM地址发生器进程BEGINIF CLK'EVENT AND CLK = '1' THEN Q1<=Q1+1; --Q1作为地址发生器计数器END IF;END PROCESS;u1 : ROM PORT MAP(address=>Q1, q => DOUT,clock=>CLK);--例化END;五、1、功能仿真图:2、时序仿真图:分析:随着clk时钟每一个上升沿的到来,ROM中存放的数据依次送出,经历64位时钟上升沿,正弦波洽为一个周期。