Actel基于Flash架构的FPGA讲座(17) 基于Actel FPGA的多串口扩展方案

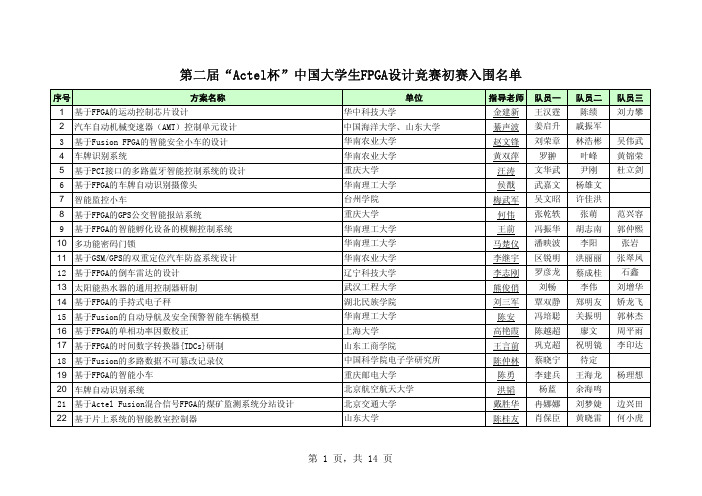

第二届“Actel杯”中国大学生FPGA设计竞赛初赛入围名单

第二届“Actel杯”中国大学生FPGA设计竞赛初赛入围名单序号方案名称单位指导老师队员一队员二队员三1基于FPGA的运动控制芯片设计华中科技大学金建新王汉霆陈绩刘力攀2汽车自动机械变速器(AMT)控制单元设计中国海洋大学、山东大学綦声波姜启升戚振军3基于Fusion FPGA的智能安全小车的设计华南农业大学赵文锋刘荣章林浩彬吴伟武4车牌识别系统华南农业大学黄双萍罗翀叶峰黄锦荣5基于PCI接口的多路蓝牙智能控制系统的设计重庆大学汪涛文华武尹刚杜立剑6基于FPGA的车牌自动识别摄像头华南理工大学侯戬武嘉文杨雄文7智能监控小车台州学院梅武军吴文昭许佳洪8基于FPGA的GPS公交智能报站系统重庆大学何伟张乾轶张萌范兴容9基于FPGA的智能孵化设备的模糊控制系统华南理工大学王前冯振华胡志南郭仲熙10多功能密码门锁华南理工大学马楚仪潘映波李阳张岩11基于GSM/GPS的双重定位汽车防盗系统设计华南农业大学李继宇区锐明洪丽丽张翠凤12基于FPGA的倒车雷达的设计辽宁科技大学李志刚罗彦龙蔡成桂石鑫13太阳能热水器的通用控制器研制武汉工程大学熊俊俏刘畅李伟刘增华14基于FPGA的手持式电子秤湖北民族学院刘三军覃双静郑明友矫龙飞15基于Fusion的自动导航及安全预警智能车辆模型华南理工大学陈安冯培聪关振明郭林杰16基于FPGA的单相功率因数校正上海大学高艳霞陈越超廖文周平雨17基于FPGA的时间数字转换器{TDCs}研制山东工商学院王言前巩克超祝明镜李印达18基于Fusion的多路数据不可篡改记录仪中国科学院电子学研究所陈仲林蔡晓宁待定19基于FPGA的智能小车重庆邮电大学陈勇李建兵王海龙杨理想20车牌自动识别系统北京航空航天大学洪韬杨蓝余海鸣21基于Actel Fusion混合信号FPGA的煤矿监测系统分站设计北京交通大学戴胜华冉娜娜刘梦婕边兴田22基于片上系统的智能教室控制器山东大学陈桂友肖保臣黄晓雷何小虎第二届“Actel杯”中国大学生FPGA设计竞赛初赛入围名单序号方案名称单位指导老师队员一队员二队员三23便携式智能多路脉搏测量仪重庆大学廖孝勇罗双才邓闳屿黄勇辉24基于FPGA的麦克风阵列语音信号增强系统东北大学秦皇岛分校刘志刚苏福正李智张昊25基于FPGA的家用型睡眠呼吸监测仪浙江大学张宏任无畏雷旭平吴隆谊26基于FPGA硬件电路的新型无刷直流电机无位置传感器控制系统哈尔滨工业大学杨春玲李宪全孙奎许传明27基于SOC的浴室智能水表金陵科技学院叶崧刘庆荣倪中英28基于ActelFPGA的多功能家用病患监护仪南方医科大学林霖骆毅斌李庆标郑毅29基于GPSOne技术的便携式跌倒报警及远程定位装置设计方案天津大学余辉程旸蔡伟超贾朔30基于模糊神经网络技术的火灾报警系统西北工业大学张萌李兆文王冶陈杰31基于Actel FPGA 的多功能车载GPS监控终端重庆大学何伟杨剑王珏随文杰32基于Fusion的三相伏安相位测量算法设计海南大学张永辉黄金兰周增光33公交车站台预报系统湖南理工学院胡文静李焱尹慧戴永辉34超市自主询价计费系统湖南人文科技学院方智文李凯军柯丽君肖捷文35基于FPGA的交流电机矢量控制系统华中科技大学许强陈彦伶王平36基于FPGA的三维医学超声探头控制华中科技大学张日欣安然程祥37基于FPGA的旋转变压器解码装置华中科技大学陈冰周沛宋帆赵飞38基于FPGA的微弱信号检测系统设计淮海工学院田锦明朱桂祥张祥满沈志鹏39基于FPGA的虚拟逻辑分析仪设计南昌航空大学吴国辉段招辉王芳杰王必众40基于FPGA的矿井水位监测系统的设计山东大学陈桂友王志华刘海伟康超41铁路信号联锁与控制系统的研究北京交通大学戴胜华叶敬贤王剑秋42基于FPGA的指纹采集和识别系统广东工业大学徐荣华陈凯旋方豪方丙涛43单芯片电池化成检测分容系统的设计哈尔滨工业大学(威海)赵涛吴鹏张凯峰44基于FUSION与433M无线数传的太阳能水质监测浮标系统哈尔滨工业大学(威海)赵涛王勇苏有路潘培峰第二届“Actel杯”中国大学生FPGA设计竞赛初赛入围名单序号方案名称单位指导老师队员一队员二队员三45基于FPGA的六自由度测量系统设计合肥工业大学余晓芬司炯陈香兰杨秀荣46基于FPGA的模糊控制智能交通系统华南农业大学陈楚孔繁波罗雄宇徐志辉47面向电动自行车无位置传感器无刷电机控制器的设计华南农业大学张建瓴赖佳良刘建文石峻48基于FPGA的苹果果径检测华中农业大学高云王硕成陈建源曾德秋49基于焊缝跟踪的5自由度焊接机器人平台山东大学李振华潘俊梅高青50基于Fusion FPGA的无刷直流电机伺服系统的设计上海理工大学李正吴阳刘新刚51基于Actel FPGA局域网智能孵化监控系统武汉工业学院李战胜熊家宏方箫郑旭标52基于Fusion StartKit的驴友电子伴侣西安电子科技大学史江一王焱龙徐度乔爽53基于FPGA的便携式PRT检测仪中国科学院武汉岩土力学研究所刘明贵袁杰于謇梁昊54基于FPGA的无线搜索定位机器人小车中国人民解放军防空兵指挥学院张春生黄洋张阳55轨道移频信息采集智能传感器北京交通大学戴胜华侯铁竹吴福刚朱兆俊56基于Fusion FPGA与GSM的温度远程监控与报警系统电子科技大学于鸿洋邹小东张实磊杜星德57基于激光测距的汽车防撞预警系统电子科技大学王老师何浩郭旭斌龙淼58基于FPGA的分户供暖收费系统计量仪器设计河南理工大学崔立志李自华田运涛赵帅兵59基于等效采样方案的数字存储示波器湖北师范学院皮大能胡水涛鲁湛刘颖60基于Actel Fusion FPGA 开发板的心电数据采集系统湖南大学罗朝明宋东谟刘杰李斌61便携式太阳能逆变电源的设计与实现华南理工大学吴朝晖黄穗彪王智欣蔡春潮62基于FPGA的双电压全桥电流矢量恒幅细分驱动器江苏大学黄振跃乔磊林阿平林思和63基于GSM网络的家庭防盗报警及智能控制系统南阳理工学院徐源黄奇瑞王向阳高兴俊64基于Fusion FPGA的短距离无线通信网络的设计重庆大学胡又文胡恩伟魏国项勇65无主机硬盘复制器(Clone-disk)重庆邮电大学徐洋徐辉张虎荣涛66三相电参数智能传感器的设计北京交通大学戴胜华曾鹏戴金梁志勇第二届“Actel杯”中国大学生FPGA设计竞赛初赛入围名单序号方案名称单位指导老师队员一队员二队员三67基于Fusion FPGA 开发板的心电数据采集成都信息工程学院邹云海曾锐于海胡凯68无位置传感器无刷电机控制湖南现代物流职业技术学院陈进军翁倪俊朱宇潘志海69基于Fusion 的仓库温湿度远程监控华南农业大学吴敏叶远雄何文略邓卓健70基于FPGA的家电无线音控系统华南农业大学周志艳郑暖程嘉俊何兆麟71基于Fusion StartKit FPGA的高速公路汽车防追尾系统模型南阳理工学院徐源何慧清杨攀峰王振72全数字MIG逆变焊接电源山东大学孙同景田崇翼王海全73基于FPGA高速数据流的下变频实现太原工业学院楼国洪王勇勇刘俊杰刘佳74基于Actel Fusion的智能轮椅上海大学蓝箭王磊李东明戴烨75简易智能多功能医疗服务设备武汉工业学院肖忠王少杰陈孟荣赵海江76基于FPGA的CAN总线光纤传输接口设计武汉理工大学吴友宇王涛简平超77突发光功率计武汉理工大学通信技术研究所周鹏于连睿陈慧马超78基于Fusion器件的数字音频处理系统及PWM变换电路的实现郑州轻工业学院孙冬吕效军张晋宇王培胜79基于AFS600的智能车辆安全系统中国地质大学(武汉)王家豪欧阳虎肖万源刘凯80公交车自动报站系统重庆大学胡又文陈磊孙凌张文浩81基于Actel Fusion的二乘二取二安全系统北京交通大学戴胜华敖俊秋李翔杨帆82多路数字和模拟信号采集系统的设计黑龙江大学杨自恒周平叶爱平罗辉83基于FPGA的电力参数测量华中科技大学李开成周勇郭盼宋强84基于FPGA的直流无刷电机控制实验装置华中科技大学陈冰饶巍胡超85基于Actel FPGA的频响特性分析仪的设计西安邮电学院王曙光马战国郭伟峰86基于FPGA的音频采集卡中国海洋大学宋大雷柴瀛朱仲本褚壮壮87基于Fusion StartKit的室内环境监测、评价与调节系统重庆工学院余成波杨数强谢东坡88数字存储示波器设计方案北京航空航天大学李丽何钐刘洪泉任熙明序号方案名称单位指导老师队员一队员二队员三第二届“Actel杯”中国大学生FPGA设计竞赛初赛入围名单89基于Fusion的多蓄电池充放电管理和多路系统供电管理北京航空航天大学王莉娜肖鲲罗文裴晓宇90基于Fusion的智能小车设计哈尔滨工业大学机器人研究所王伟东田立志郑晓彬胡庆龙91基于FPGA 技术的变压器油中微水超声检测河海大学常州校区朱昌平武晓刚尹惠根吕金超92基于混合信号FPGA的智能超声功率源的设计河海大学常州校区单鸣雷王其张振曾晓阳93基于FPGA的内燃机电子调速器山东建筑大学于海鹰刘杰顾岩王锦妍94基于Fusion实现电源的精确管理四川大学李小根张仁建王超王敏95基于FPGA和无线传输的介质损耗因数 检测仪中南大学曹建吴金红陈孔阳曾德文96智能声控+键控密码锁湖北师范学院皮大能田野颜昱高银97基于FPGA的电动车电池监测系统湖南理工学院陈松周新云王立何华梁98基于Actel Fusion FPGA 开发板的“新型”脉搏分析仪南方医科大学曾斯坚程允俊杨铭涛吕晓玲99基于FPGA的异步电动机变频调速系统设计山东科技大学黄鹤松王丽丽毕京鹏高圆圆100基于Fusion StartKit FPGA 的远程健康医疗监护系统西南交通大学杨斌陈法海张裕强101中医脉象诊断仪成都信息工程学院曾祥萍李扬唐慧王琴102基于FPGA拥有电子琴和红外遥控功能的数码相框系统设计电子科技大学中山学院邓春健陈龙光黄作珍103基于FPGA声音搜索定位机器人小车湖南师范大学兰浩苏欢胡浩徐双华104基于Fushion FPGA的多功能谐波分析仪在单相电力系统中的应用南京邮电大学李晓飞任怀平牟崧友朱东进105基于FPGA的三相光伏逆变器的设计山东大学杜春水王文强吕增强程飞106光纤耦合器熔锥制作控制器上海大学张伟成郭霞霞张丽田进进107基于FPGA的自动输液控制西北工业大学安建峰何向栋周洪任嵘108基于FPGA的多通道数据采集系统郑州铁路职业技术学院巩恩福鈡晓辉江兴盟李明李国军李春燕tanα序号方案名称单位指导老师队员一队员二队员三第二届“Actel杯”中国大学生FPGA设计竞赛初赛入围名单109基于ACTEL FPGA的指纹识别数据加密系统广西师范大学王志高苏检徳王力虎甘宇健王明娟秦力110基于FPGA的温湿度控制系统湖北民族学院易金桥陈光堂张磊龚伟111基于GSM远程控制的网络LED显示终端山东大学徐同一刘博阳柳紫璇112基于Actel Fusion的小区光纤-以太网收发器上海大学徐昱琳谢维磊吕振彬113客运车辆跟踪与报站系统沈阳理工大学马平全李称林李然李明114基于Leon2的SOPC设计与验证西安理工大学张发存胡林林雷雪艳黄金亮115便携式太阳能逆变电源的设计与实现烟台大学陈智育张吉勇韩凡116声控密码门禁系统烟台大学文经学院张昌州史小明宋庆宽刘丕言117基于FPGA的PCI扩展卡设计中北大学杨瑞峰王智沈国华118基于FPGA(AFS600)的时间服务器中国地质大学(武汉)王家豪张杰张祥游钊119基于Fusion开发平台的公交车自动报站系统重庆大学朱文嘉陈永忠崔道鑫殷欢120基于Fusion FPGA的短距离无线通信系统成都信息工程学院陆继庆陈代强叶晓文夏奇辉121应用于未来智能卡的自动指纹识别系统设计东华大学赵曙光陈亮郭星明熊斌122基于FPGA的指纹识别门禁系统哈尔滨工业大学王立欣张玉霞朱宝峰丁印福123基于FPGA的公交智能语音报站系统河池学院彭建盛周永祥徐胜红韦锦平124基于FPGA的出租车计费系统河海大学常州校区陶剑锋董玉慧史夏洁辛元雪125简易电子架子鼓设计湖南人文科技学院陈新胡建发王政芳126基于FPGA的智能型公交车站牌的设计南京邮电大学孙科学葛立扬陈华王苏亚127智能逻辑分析仪宁波大学邬杨波傅晓东沈伟伟张金龙128基于FPGA的DES加密芯片设计与实现西北工业大学张捷闻有禄包刚129多功能瓦斯监测报警系统中北大学沈三民张鹏飞孔陈杰燕洪成第二届“Actel杯”中国大学生FPGA设计竞赛初赛入围名单序号方案名称单位指导老师队员一队员二队员三130声控密码锁中国地质大学(武汉)王家豪高正刘诗阳叶艳131基于FPGA的多路客流量分析系统中州大学马宇晓李泽宇刘培132基于Actel fusion FPGA的软件无线电综合数字调制系统湖北汽车工业学院江学焕李承运李飞庆关新133声控密码锁哈尔滨工业大学徐玉滨刘菁宇吴迪孙彦良134基于FPGA的手持式沼气检测仪湖北民族学院廖红华向宏艳喻学梅王书洋135多功能智能跑步机华南农业大学可欣荣蓝武强莫秀英梁超文136基于Internet的远程实验系统华南师范大学张旭骆华根张永超李旋丰137基于红外探测的自动定点灭火系统华中科技大学陈晶田陈彦彰王远138基于FPGA的分布式无线水文监测系统南昌工程学院魏静波胡斌郭红伟高黔139基于FPGA的信号发生器设计南昌航空大学易宏杜志明赵汝波帅倩140基于Actel Fusion的救灾抢险冲锋车上海大学蓝箭王国钦蔡兴旺陈源141基于CPLD/FPGA的出租车计费器系统的设计实现华东交通大学杨云曾宪洲付济良谢飞142基于FPGA的基站功放实时监控系统电子科技大学沈晓峰付秋华张巍褚兆文143未来超市自主购物系统哈尔滨工业大学郭庆赵岩彭浪魏一舟144基于FPGA&RFID的自助超市模拟系统华东理工大学吴清岑弘璋丁晓锋王涛145基于FPGA的健康游戏系统华南理工大学李磊陈政才陈明戴声146基于Actel FPGA的便携式脱机无线手持扫描仪华中科技大学肖看刘鬯陈才溢147基于FPGA的智能化盲人拐杖江西农业大学周华茂谢柳明杨海勇黄志欢148基于FPGA的箱式变电站关键参数检测系统南京工程学院汪力纯郭壮林井凯149基于FPGA的多点温度智能监控系统山东大学常军白亮陈广陈媛150基于FPGA的指纹识别系统山东轻工业学院汪宁王奎马连忠张海建151基于太阳能DC/AC直流逆变电源台州学院梅武军刘志虎刘良秀序号方案名称单位指导老师队员一队员二队员三第二届“Actel杯”中国大学生FPGA设计竞赛初赛入围名单152基于Fusion StartKit FPGA的汽车防盗系统西安理工大学邢楠郭瑞刘溪153基于FPGA的智能家居以太网控制器设计重庆大学仲元昌陈启键肖东海王军强154基于蚕种催青的环境自动监测系统重庆大学郭茂耘邢桂山袁克彬孙庆楠155基于Modbus(RTU)网络主机连接器北京建筑工程学院周庆辉刘光喆张继征156基于语音识别的智能密码锁华南理工大学贺前华肖建明唐正叶展行157基于FPGA_CPLD和USB技术的无损图像采集卡宁波大学李宏刘国峰张诚昊158便携式数字频谱分析仪设计西北工业大学孟昭红郭通王玉朝杨少华159车牌自动识别系统重庆大学胡又文吴晋成唐先成160基于Actel FPGA野外自动求救设备北京理工大学马忠梅王娟程万鹏魏王跃孟祥龙161基于Fusion FPGA的温室大棚参数测控系统辽宁科技大学程万胜孟永亮林伟段超162基于Fusion FPGA的短距离无线通信系统中科院上海微系统与信息技术研究所巩思亮巩思亮徐立洲163简易失真度测试仪电子科技大学唐续叶健王丁164基于FPGA的车牌自动识别系统的研制湖北工业大学廖冬初夏华东刘鑫徐威165分布式城市环境实时监控系统山东大学测试计量技术研究所司书春王俊纪存亮谢祎166直流电机驱动控制武汉科技学院李宇胡磊王涛望习才167基于FPGA的多通道高速数据采集系统设计西安邮电学院亢红波侯瑞张灿振李蜜168基于Fusion器件的远程控制智能小车设计郑州轻工业学院王俊杰董旭王国波冯晓青169声控密码锁中北大学张斌珍王杰高杰170基于FPGA的电梯自动控制系统中国地质大学(武汉)王勇何东张伟张立欣171基于Actel Fusion 的感应同步器信号采集与处理系统的设计重庆工学院王先全娄莉娜李心一172智能化舞台照明跟踪系统东华大学吴赟朱汇中林远昊张航173多功能声控密码锁电子科技大学李辉常晓剑高立剑朱炯序号方案名称单位指导老师队员一队员二队员三第二届“Actel杯”中国大学生FPGA设计竞赛初赛入围名单174便携式胸阻抗血流图监测诊断系统东华大学赵曙光王洪亮张春潜翁文田175基于FPGA的多功能智能小车探测搜救平台北京航空航天大学刘劲猛邱祺王嫣然雷正东176基于FPGA的交流电动机直接转矩控制的无速度传感器设计安阳师范学院丁电宽杨宗义李淼177逻辑分析仪东华理工大学王海涛谢新虎李敏178基于模糊控制的智能风扇江西农业大学周华茂李明禄顾俊张勇勇179基于Actel Fusion FPGA 开发板的心电数据采集系统南方医科大学刘娅琴李世鑫张竣峰叶照晖180智能轮椅中山大学倪江群莫衍宋冬晓181基于FPGA的无土栽培温室环境控制系统华南农业大学魏德仙李锦秀林泠羚阮耀灿182基于FPGA无线语音控制台模型三峡大学施保华王振宇李云飞叶世旺183四相步进电机八细分控制山东大学姚福安王超单小明韩琦184高速工业CT机伺服控制和图像数据采集、压缩及传输系统山东大学钟麦英陶亮段彬185基于并行流水线技术的高速高精度A/D采样系统重庆大学戴欣秦运友张伟袁洁186基于FPGA的多功能生理参数监测仪上海大学徐昱琳费瑜朱卫杨奔187车况实时监测系统重庆大学王雪谭德超熊文兵韩愈188基于FPGA的新型多功能出租车计价器的设计湖南城市学院肖卫初邓曙光李稳国朱珍奇谭德周丽莎189声控密码锁宁波大学李宏尚鹏项峥嵘邵成刚190基于FPGA的自主超市收银系统北京理工大学王娟马忠梅朱溢薛佳鹏柳凯191基于FPGA的汽车安全系统设计长江师范学院朱斌钱江李前张军192交流电无功功率与谐波动态补偿装置辽宁科技大学吴庆洪闫红宇孙建聂连朋193基于Actel FPGA的建筑物安全性无损检测系统西安工业大学雷斌刘贞张亚薇王宁第二届“Actel杯”中国大学生FPGA设计竞赛初赛入围名单序号方案名称单位指导老师队员一队员二队员三194植物电信号采集分析仪西安理工大学刘锴梁元赵高翔李卿195基于FPGA的GPRS无线通信西南民族大学王一冰林凯李光鑫196基于Actel混合信号FPGA相控阵超声避障雷达西南交通大学白海峰刘保成顾如意杨翔197基于FPGA的声控密码锁华南农业大学班华林介奇黄振华崔志波198基于单片模数混合FPGA的永磁直线同步电机伺服控制系统设计华中科技大学陈冰闫光亚刘源远甘浩199基于Actel FPGA的智能探测小车设计重庆大学何伟游婧李经章郭志欢200基于FPGA的便携式电子血压计广东工业大学蔡述庭王义东陈汉锡余斯擎201基于FPGA的车牌自动识别系统华南理工大学贺前华范炜卢寅郑烁鹤202基于FPGA的等精度数字频率测量仪四川理工学院姚娅川王显海张海军黄周涛203基于FPGA的指纹识别系统天津工业大学隋修武廖勇耿宝龙付硕硕204办公室/家庭智能节能系统重庆邮电大学李小文李海文周侃林丹205基于FPGA的便携式心电数据采集器重庆邮电大学曾垂省沈扬张咏梅肖福勇206基于FPGA的酒精在线发酵监控系统山东大学王延伟李天平秦秀文李绍林207多路温度、湿度采集控制系统太原工业学院张剑平张星茹姚亚樊瑞涛208高精度粘度汁粘度测量系统中山大学保延翔毛劲松李宗叠209基于Actel FPGA的广告屏LED设计重庆工学院包明汤斌黄德翼周斌210基于Fusion的全自动火源探测车西北工业大学吴志强荣少巍周文杰雷亚龙211基于Fusion StartKit FPGA平台的无线手势识别系统华南理工大学李磊黄仁陈曦陈启沛212基于Fusion的校园智能公交车简易模型南京信息工程大学周旺平林涛潘建平张欢欢213车牌自动识别摄像头华南理工大学殷瑞祥刘凯明施华德苏伟强214车牌识别华南师范大学余炳雄梁展明何任飞傅小军215基于Actel Fusion FPGA的逻辑分析仪华中科技大学尹仕张柬贺威帅率第二届“Actel杯”中国大学生FPGA设计竞赛初赛入围名单序号方案名称单位指导老师队员一队员二队员三216基于Funsion的多路温度监测系统内蒙古科技大学陈波张辉郭健217基于ACTEL FPGA的车辆信息识别系统西华大学谢维成刘磊王成超218基于Fusion的智能电焊机军械工程学院郑立评屈夏光张彬松219智能孵化箱北京航空航天大学刘敬猛顾天宇张宇邢智慧220多路电压监测报警系统电子科技大学陈学英路杨罗继庞张仕超221公交站台预报系统南京工程学院刘传清吴云峰马亮沈曙明222基于FPGA的自习室自动分配及管理系统南通大学杨永杰仇业松仝良玉陈景223基于Fusion StartKit的数字音乐相册西安电子科技大学李康王庆成刘石壮李炎昭224数字示波器宁波大学李宏朱文戈虞天昊225基于FUSION FPGA的眼电轮椅成都信息工程学院杨波陈捷李世伟杨强226井下配电糸统的无线网络控制糸统设计河南理工大学崔立志孙云洋黄兆鑫何雷227智能管家华南农业大学魏德仙廖彬许达张耿波228智能化窗户控制系统江西农业大学周华茂何张辉曾乐平229数字示波器(VGA信号输出)桂林工学院南宁分院梁向东莫文益林芳王宽230基于ASF600的高性能可编程综合控制器福州大学吴景东吴络音傅月燕231基于Actel Fusion FPGA 开发板的自动指纹识别系统(AFIS)南方医科大学刘娅琴黄文鑫陈永兴王文化232基于FPGA的步进电机十六细分控制电路系统及寻源小车控制系统上海大学秦霆镐陈枭雄赵慧洁233基于Fusion的自主超市系统中国海洋大学刘滨顾宾滕梓洁234基于移动识别的家居智能灯光及报警系统重庆大学盛朝强白颖杰王壬235基于FPGA的CCD图像处理系统桂林电子科技大学王培培魏常伟胡鑫236基于Actel Fusion FPGA的家庭防盗综合报警系统上海应用技术学院汲伟明吴盛洁宋志敏杨晨啸237基于fpga的汽车预警/防盗/车窗升降,常用显示集一身的便携式汽车管理系统太原工业学院索静胡艳亮付利云吴随权。

如何解决Actel FPGA烧写两大难题?

如何解决Actel FPGA烧写两大难题?摘要Actel FPGA烧写的两大难题:Actel Flash构架特点、难点;批量烧写的稳定性,如何拆解?为什么Actel的FPGA烧写难?Actel的FPGA为全球独创的Flash构架的FPGA,独创就在于他不同于普通RAM构架,不需要外部的EPROM、PROM存储器来保存内部逻辑状态的配置信息。

Actel的FPGA配置信息都存放在内部的Flash里面,直接忽略外部存储器,从而保证他的高安全性。

这个Flash构架的特性就决定了,Actel的 FPGA的编程具有一定的难度。

拆解Actel FPGA烧写的两大难题难题一:Actel Flash构架特点、难点Actel FPGA内部Flash有个特点,配置数据不能读回,这样来保证芯片的高安全性。

对于编程者来讲,如何保证你写入的配置数据、加密密码是成功了呢?编程者的通常做法是,读出写入芯片的数据然后与缓冲区的数据进行对比,如果一致,就校验成功;如果不一致,就校验失败。

Actel FPGA是不允许读回的,通常的做法是无法校验的。

怎么办?难题二:批量烧写的稳定性任何批量烧写工具,裸片烧写或在线烧写,最关键的指标就是稳定性。

稳定性就需要对编程口线进行严格的电气控制,经常有客户反馈在线烧写时某I/O口被击穿了,其实就是由于在直接与PCB进行连接的过程中,线材可能会串扰进来一些其他电路的尖峰电压、瞬态大电流等,形成对电路板上IC的冲击,导致了损坏芯片的情况。

一旦烧写批量大起来,生产良率如何保证?一个工具解决两大难题AK100Pro-4P是一款一拖四的量产型在线编程器,可以支持四个通道同时烧写,只需连接 FPGA芯片的JTAG接口,即可完成在线烧写操作。

图1 AK100Pro-4P在线编程器AK100Pro-4P在Flash烧写上的一些巧办法上一节提到无法用通常的做法来校验Actel FPGA,AK100Pro-4P是如何实现的呢?AK100Pro-4P的做法是再发一次相同的数据给芯片,让Actel FPGA自己进行比对校验,并返回校验的结果,充分利用Actel FPGA本身的特性,既保证了代码的安全,又保证编程的可靠。

Actel FPGA介绍

Actel ProASIC3/E系列特性

先进的I/O

用户最多可用616个单端I/O或300个差分I/O,支持多种I/O电平 标准和Bank电压。

单端I/O最快速度可达 250MHZ,差分可达 350MHZ,DDR可达到 700MHZ

Actel ProASIC3/E系列特性

先进的I/O

用户最多可用616个单端I/O或300个差分I/O,支持多种I/O电平 标准和Bank电压。

四种布线资源

以最小的延时跨越整个器件,垂直方向可以跨越正负12个VersaTile,

超快速的局部连线资源

四 种 布 线 资 源

有效长线资源

高速的超长线资源

高新能全局网络

Actel FPGA的布线结构

为片上全局网络和象限全局网络。

四种布线资源

应用于需要低偏斜、低延时、低抖动、高扇出的网点。全局网络分

ProASIC3L

具有独特的

Flash*Freeze 技术,功耗低

Fusion

具有分辨率为

12位,转换速率 为600KSPS的 ADC

IGLOO

静态功耗低至

5UW,并保存 RAM数据

IGLOO+

应用于低功耗,

高性能I/O的场 合

Nano

成本低至1$

商业级温度范

围更广(-200c~ 700c)

应用于低功耗,

JTAG Port

Actel Fusion系列

GPIO

嵌入式Flash内存

Flash memory区块(2M)

MOSFET Outputs Analog Inputs

A/D

A3P FPGA Fabric (incl. SRAM, CCC/PLL, IO)

基于Fusion FPGA无刷直流电机的控制器设计

Microcomputer Applications V ol.27,No.8,2011研究与设计微型电脑应用2011年第27卷第8期文章编号:1007-757X(2011)08-0001-04基于Fusion FPGA 无刷直流电机的控制器设计薛鹏飞,张卫东摘要:微波成像扫描仪是气象卫星上的重要酬载,扫描仪的控制系统是扫描仪上的核心机构,其控制性能将对扫描仪的成像精度和卫星任务的完成情况产生重大影响。

采用Actel StartKit FPGA 开发板为微波成像扫描仪内的无刷直流电机设计了控制器,详细介绍了控制器中各模块的设计,包括PWM 波发生、换相控制、以及双闭环增量式数字PID 调节等模块。

基于SoPC 的设计思想,使得系统模块都集成在一片FPGA 上,提高了系统的可靠性和稳定性。

软件仿真和实验结果表明,设计的控制器精度高,运行稳定。

关键词:无刷直流电机;FPGA ;PWM 波调制;数字PID中图分类号:TP23文献标志码:A0引言在气象卫星上,微波成像扫描仪是非常重要的携带设备,而扫描仪的控制系统是扫描仪上的核心机构,其控制性能将对扫描仪的成像精度和卫星任务的完成情况产生重大影响。

无刷直流电机因为其稳定和调速性好已经逐渐成为扫描控制系统上的主要执行机构,在国内外卫星上得到了广泛的应用。

因此,研究并设计精度高、稳定好、抗干扰能力强的无刷直流电机控制系统具有重要的实际意义。

近年来,嵌入式设计开发技术、电力电子技术以及计算机控制技术得到了快速的发展,尤其是基于FPGA 硬件设计技术的兴起,为我们改进电机控制系统提供了强大的技术支撑。

在这样的背景下,本文将以Actel 公司基于Flash 架构的Fusion 系列FPGA 为控制核心来建立无刷直流电机的控制系统。

尽可能地利用FPGA 丰富的内部硬件资源,完成位置检测模块、PWM 波发生模块等控制系统主要环节的设计。

利用FPGA 进行纯硬件设计的好处是其并行处理方式可以不占用CPU 资源,使系统达到很高的性能。

FPGA在工业控制领域中的应用

FPGA 在工业控制领域中的应用学院:工学院专业:自动化姓名:白曙睿FPGA 在工业控制领域中的应用摘要:本文主要介绍现场可编程门阵列(FPGA)技术及其在工业控制领域的贡献。

首先介绍FPGA 在各个领域的一些有意义的应用。

随后介绍相应的设计工具及装置功能。

以下两个例子说明在复杂控制应用的情况下使用FPGA 的好处:一是通过处理一个基于扩展卡尔曼滤波的无传感器电动机控制器,这种专用的设计方法使其得到进一步发展;其二是神经网络系统。

一些案例研究的结果显示研究人员对于 FPGA 在这一领域充满兴趣。

关键词现场可编程门阵列,工业控制应用程序,系统芯片,设计工具,设计方法,无传感器电机控制器,扩展卡尔曼滤波,神经网络系统Ⅰ介绍现如今,为了保证市场的生产差异,新的工业控制系统需要具备高性能,高灵活度,高可靠性。

与此同时,成本是一个关键问题。

为了解决这个问题,必须缩短上市时间,降低控制器设备的价格以及减少控制系统的能源消耗。

然而,降低成本更具有挑战性,因为新的工业控制系统必须基于日益复杂的控制算法,这就需要大量的计算资源,并且减少执行时间。

为了应对这些挑战,设计人员可以依靠越来越成熟的数字电子技术,以及友好的软件开发工具。

为了实现高效的实时工业控制,设计人员需要在两个主要的数字设备技术系列中作出选择:第一个系列是基于纯软件平台。

相关的设备是微控制器和数字信号处理控制器(DSP控制器)。

这些部件集成了一个执行微处理器的核心和实时目标控制系统来进行工业环境通信所必需的若干外设。

微控制器[1]和DSP 控制器[2]之间的不同在于,对于一个给定的硅表面,处理单元和通信以及外设之间的比例。

微控制器包括一个通用16 位或32 位的精简指令集计算机(RISC)和多种外设,而 DSP 控制器集成了一个高性能处理器内核,基于硬件加速器的计算模块(乘法和累加逻辑运算单元MAC ALU)和一些外围设备。

然而,这两个概念之间的界限正在消失,因为微控制器的RISC 单元越来越强大,外设的数量和种类越来越多。

一种针对COTS器件的抗辐射加固方法

一种针对COTS器件的抗辐射加固方法梁健;张润宁;赵帅【摘要】随着商用现货(COTS)器件在空间任务中的广泛应用,COTS器件的抗辐射加固显得尤为重要,针对COTS器件在空间环境下易受宇宙射线和高能粒子冲击而产生辐射效应的特点,文章结合三模冗余(TMR)技术与现场可编程门阵列(FPGA)的重构技术,提出了一种基于TMR的可重构星载处理单元抗辐射加固方法.通过基于Markov过程的可靠度分析可知,冗余和重构技术相结合可以使处理单元具有更强的容错能力.文章利用实验模拟验证了该星载处理单元的各项关键技术,结果表明:此处理单元能够屏蔽单模故障,并能够定位和修复由空间复杂环境引发的软错误.【期刊名称】《航天器工程》【年(卷),期】2016(025)004【总页数】6页(P81-86)【关键词】星载处理单元;冗余;可重构;商用现货【作者】梁健;张润宁;赵帅【作者单位】航天东方红卫星有限公司,北京 100094;航天东方红卫星有限公司,北京 100094;西北工业大学,西安710072【正文语种】中文【中图分类】V473空间环境中存在较多的宇宙射线和高能粒子,运行在这种复杂环境下的航天器的计算系统很容易受到这些粒子和射线的冲击而产生辐射效应。

当前,在空间处理系统中,现场可编程门阵列(FPGA)以其低功耗、灵活性、通用性、高集成性等优点获得了广泛的应用。

基于静态随机存储器(SRAM)型的商用现货(COTS)FPGA器件很容易受到高能粒子的影响而产生辐射效应[1-3]。

而基于Flash架构的FPGA器件有较强的抗辐射性能,对由空间高能粒子引发的固件错误具有免疫能力,但是基于Flash架构的FPGA器件逻辑资源有限,不具备嵌入式软处理器的能力,故运算和处理能力受限,直接应用于复杂的星务管理和运算具有一定的局限性[4-5]。

传统的三模冗余(TMR)技术可以有效屏蔽单模故障,但表决器本身并不具备抗辐射能力,或者表决器由简单的逻辑开关组成,控制与协调能力不足[6-7]。

飞行控制系统

飞行控制系统为了使无人机飞行控制系统具有强大的数据处理能力、较低的功耗、较强的灵活性和更高的集成度,提出了一种以SmartFusion为核心的无人机飞行控制系统解决方案。

为满足飞控系统实时性和稳定性的要求,系统采用了μC/OS-Ⅱ实时操作系统。

与传统的无人机飞行控制系统相比,在具有很强的数据处理能力的同时拥有较小的体积和较低的功耗。

多次飞行证明,各个模块设计合理,整个系统运行稳定,可以用作下一代无人机高性能应用平台。

关键词:无人机;飞行控制系统;SmartFusion芯片;μC/OS-Ⅱ0引言???飞行控制系统是无人机的重要组成部分,是飞行控制算法的运行平台,它的性能好坏直接关系着无人机能否安全可靠的飞行。

随着航空技术的发展,无人机飞行控制系统正向着多功能、高精度、小型化、可复用的方向发展。

高精度要求无人机控制系统的精度高,稳定性好,能够适应复杂的外界环境,因此控制算法比较复杂,计算速度快,精度高;小型化则对控制系统的重量和体积提出了更高的要求,要求控制系统的性能越高越好,体积越小越好。

此外,无人机飞行控制系统还要具有实时、可靠、低成本和低功耗的特点。

基于以上考虑,本文从实际工程应用出发,设计了一种基于SmartFusion 的无人机飞行控制系统。

1飞控系统总体设计????飞行控制系统在无人机上的功能主要有两个:一是飞行控制,即无人机在空中保持飞机姿态与航迹的稳定,以及按地面无线电遥控指令或者预先设定好的高度、航线、航向、姿态角等改变飞机姿态与航迹,保证飞机的稳定飞行,这就是通常所谓的自动驾驶;二是飞行管理,即完成飞行状态参数采集、导航计算、遥测数据传送、故障诊断处理、应急情况处理、任务设备的控制与管理等工作。

???飞行控制系统主要完成3个功能任务,其层次构成为三层:最底层的任务是提高无人机运动和突风减缓的固有阻尼——三个轴方向的阻尼器功能;第2层的任务是稳定无人机的姿态角——基本驾驶仪的功能(主要进行角运动控制);第3层的任务是控制飞行高度、航迹和飞行速度,实现较高级自动驾驶功能。

FPGA几大厂商介绍,你知道的有哪些呢?

FPGA几大厂商介绍,你知道的有哪些呢?前言:有的同学在学习fpga,但是你知道fpga的几大厂商有哪些么,今天我们就来聊聊比较知名的fpga几大厂商。

在FPGA的世界内,你不可不知道Xilinx (赛灵思)和Altera(阿尔特拉)两家公司,两家巨头占据了90%的市场份额。

而Lattice 和Actel只能在特殊领域保持一定的份额。

但是随着FPGA市场风云变幻,并购事件层出不穷,连巨头Altera也被Intel收购了,Lattice也收购了SiliconBlue。

尽管如此,还有一家Achronix FPGA厂商依然不可小觑。

下面就让我们一起来了解了解吧。

一、Xilinx 赛灵思官网:http://xilinx 建立时间:1984 总部:加利福尼亚圣何塞市介绍:Xilinx是全球领先的可编程逻辑完整解决方案的供应商,也是目前排名第一的FPGA解决方案提供商。

开发工具:Vivado,ISE(出了vivado之后,xilinx已经不考虑去升级ISE的版本了) 其产品包括如下几个部分: 1、Spartan系列:定位与低端市场,目前最新器件为Spartan7,为28nm工艺,Spartan6以前都是45nm工艺,该系列器件价格实惠,逻辑规模相对较小。

2、Artix系列:Xilinx推出Artix系列产品,其目的应该是作为低端Spartan和高端Kintex的过渡产品,尤其在通信接口方面,相比Spartan有很大优势,所以,如果设计不是仅仅需要逻辑资源,而是需要先进的高速接口,不妨考虑Aritix系列。

3、Kintex和Virtex系列为Xilinx的高端产品,包含有28nm的Kintex7和Virtex7系列,还有16nm的Kintex7 Ultrascale+ 和Virtex7 Ultrascale+系列。

丰富的高速接口,主要用于通信,雷达,信号处理,IC验证等高端领域。

4、全可编程SoC 和MPSoC系列,包括有Zynq-7000 和Zynq UltraScale+ MPSoC系列FPGA,可嵌入ARM Cortex系列CPU,逐渐成为目前SOPC热门应用。

ACTEL半导体FPGA选型指南

CoreABC

CoreABC主要特性 ◎ 极快的I/O响应速度(<100ns); ◎ 高可配置性并且可轻易裁剪以满足用户

销售服务电话: (020) 38730619 38732221 技术支持电话: (020) 28872345 28267809 技术支持邮箱:zlgactel@ Actel.marketing@

Actel提供业界标准的处理器

Actel强大Leabharlann 理器平台:Cortex-M1在FPGA中的应用权衡了面积和速度的利益,提供了 一个折中的方案,采用三级流水线模式和ARMv6-M指令集,支持指 令和数据的TCM(Tightly Coupled Memories)模式,带有可配置的 中断控制器;可选择带有调试模块或不带有调试模块的内核;基于 CoreConsole的IP系统平台软件进行开发,可以将Cortex-M1内核无 缝连接到AHB总线上,并且非常容易的让用户裁减外设的部件。

SFR接口添加了高级外设总线(APB)接口。这样,设计人员 便可以搭建根据自己需要的8051系统,在APB总线上任意挂接 外设,并对其进行配置,以满足它们特殊的应用要求。 Core8051s的速率还非常快,且可以运行现有的8051代码和使 用现有的8051开发工具。

Core8051与Core8051s特性:

● 硬件支持 使 用 Actel公 司 提 供 的 FlashPro3 USB下 载 器 , 通 过

CoreConsole和 Libero软 件 对 器 件 下 载 编 程 以 及 使 用 基 于 SoftConsole软件在系统调试,同样也支持第三方厂商标准的 调试工具。

ACTEL公司及产品介绍

Xilinx

90nm

1,936

405

XC2V1000

SRAM

Altera

0.13µm

Not

453

EP1C20

SRAM Measured

Equivalent Functional Failure FIT Rates per Device

Ground-Level Applications

Commercial Military Aviation Aviation

30

ACTEL公司产品的 主要特点和优势

静态电流比较表

31

ACTEL公司产品的 主要特点和优势

动态功耗

• 是指FPGA在工作时,内部逻辑和I/O状态翻转引起 的功耗。

• SramFPGA中,一个开关由6个晶体管组成,导致 动态功耗较高。FlashFPGA动态功耗低。

32

ACTEL公司产品的 主要特点和优势

39

ACTEL公司产品的 主要特点和优势

7.真正的单芯片解决方案

• Flash架构的FPGA不需要外加一个配置芯片,而且 功耗更低。

• 为用户提供丰富的IP核资源。 • ACTEL的FUSION系列内部带模/数转换功能,有电

流监控,电压监控等。 • SmartFusion系列产品内部集成了Cortem-M3硬核,

28

ACTEL公司产品的 主要特点和优势

Spartan系列FPGA的配置电流

29

静态功耗

ACTEL公司产品的 主要特点和优势

• 又称待机功耗,是指在电源打开的情况下,I/O状态 没有翻转时器件的功耗。

• SramFPGA中,一个开关由6个晶体管组成,导致静 态功耗较高。FlashFPGA静态功耗低。

fpga设计大赛题目

1. 运动控制类

1.1 智能轮椅

功能描述

本设计完成了智能轮椅的功能。智能轮椅使用四轮二电机驱动,在手动控制方向的前提 下,使用自动控制算法保证轮椅准确、平稳地按照控制终端要求的方向运行,以方便肢体行 动不便人士的出行。轮椅安装有摄像头,可根据通道或房门、电梯门口的颜色标志柱快速、 准确地进行转向与对准,进出狭窄通道或房门、电梯门等。轮椅安装有语音识别模块,即便 是上肢活动不便人士也可以通过语言操控轮椅运动。另外,轮椅还安装有 GPS 系统,为驾 驶轮椅出行导航,也可为亲属和公安部门进行轮椅定位提供方便。控制终端采用 LCD,带 触摸屏、控制按钮,安装有语音识别使用的话筒。

“Actel 杯”FPGA 设计竞赛参考题目

1. 运动控制类...............................................................................................................2

1.1 智能轮椅.......................................................................................................................2 1.2 多功能智能跑步机.......................................................................................................2 1.3 多路、智能直流伺服电机运动控制器.......................................................................2 1.4 基于FPGA的无线音控小车.........................................................................................2 1.5 基于Fusion的智能小车的设计 ....................................................................................3 1.6 四相步进电机八细分控制...........................................................................................3 1.7 基于FPGA的焦炉自动控制...........................................................................................3 1.8 直流电机驱动控制.......................................................................................................3 1.9 无位置传感器无刷电机控制.......................................................................................3 1.10 基于FPGA的无线搜索定位机器人小车.....................................................................4

FPGA基础知识讲课文档

FPGA器件结构 可编程输入/输出单元

可编程逻辑单元 嵌入式块RAM

布线资源

底层嵌入功能单元

第十二页,共38页。

FPGA器件结构

Xilinx spatan-3器件结构

第十三页,共38页。

Altera cyclone II器件结构

LAB

第十四页,共38页。

FPGA器件结构 可编程输入/输出单元 可编程逻辑单元 嵌入式块RAM 布线资源 底层嵌入功能单元

第三十一页,共38页。

基于FPGA的DSP设计

基于FPGA的DSP设计

simulink

modelsim

Matlab *.m

system generator

Accel DSP

*.v

第三十二页,共38页。

FPGA与CPLD区别

区别[工艺/结构/延时/配置] FPGA基于SRAM工艺,集成度高,以LE(包括LUT、FF及其他)

SOPC

SOPC

PROM

PROM/EPROM/E2PROM

PROM:可编程只读存储器,通过专用的烧录器编程;编程后不可擦除信息; EPROM:紫外线可擦除只读存储器,可通过光擦除编程信息;

E2PROM:电可擦除存储器. PLD/GAL

PLD:可编程逻辑阵列;

GAL:通用逻辑阵列; PLD/GAL基于与或结构,采用e2prom工艺,主要用于替代早期的74系 列门电路芯片,灵活度相对要大

Altera:LE

Xilinx:SLICE

可编程逻辑块

LAB/CLB

LE

第二十二页,共38页。

Altera:LAB

Xilinx:CLB

FPGA器件结构

可编程输入/输出单元 可编程逻辑单元 嵌入式块RAM

Actel IGLOO和ProASIC3L FPGA设备Flash Freeze控制使用内部晶体震荡

Application Note AC332June 20091© 2009 Actel Corporation Flash*Freeze Control Using an Internal OscillatorIntroductionThe Actel IGLO O ® and ProASIC ®3L families of FPGA devices are based on Actel nonvolatile flash technology and single-chip ProASIC3 FPGA architecture. These devices are part of a 1.2 V to 1.5 V operating voltage, offering the industry’s lowest power consumption, smallest footprint, competitive prices, and many advanced features. The Flash*Freeze technology used in IGLOO and ProASIC3L devices enables entering and exiting Low Power mode, which consumes as little as 2 µW of power while retaining all SRAM and register data. Flash*Freeze technology simplifies power management through input/output (I/O ) and clock management, with rapid recovery to full operational mode. Refer to the IGLOO FPGA Fabric User’s Guide and the ProASIC3L FPGA Fabric User’s Guide for additional information on the device features and use of the Flash*Freeze pin.In applications where the device is in Flash*Freeze mode for most of the operation or in cases such as remote deployment with the Flash*Freeze pin asserted, there is a need to control the Flash*Freeze entry and exit from within the device to save power, simplify software, and avoid continuous toggling of the Flash*Freeze pin.In addition, IGLOO and ProASIC3L devices cannot be programmed while in Flash*Freeze mode and the logic that enables authentication for encrypted programming is turned off by default to save power.Therefore, a solution is needed to bring the device out of Flash*Freeze mode and to internally turn on the authentication circuit in applications where physical access to the Flash*Freeze pin is not available. This logic, which is programmed into the device along with the user application, acts as a Master for the Flash*Freeze mode. Two distinct use models have been developed to address this type of application. You can choose either one of these solutions, depending on the individual application requirements:•Flash*Freeze control with JTAG: This solution provides on-demand wake-up of the device for programming and also for authentication. •Flash*Freeze control using an internal oscillatorThis application note describes the internal oscillator for Flash*Freeze control for all IGLOO and ProASIC3L devices and addresses the following requirements:•Internal clock source for logic (counter) to control entry to and exit from Flash*Freeze mode, a ring oscillator •Modification required for the Flash*Freeze management IP coreFlash*Freeze control with JTAG is described in Flash*Freeze Control Using JTAG .Internal Oscillator for Flash*Freeze ControlThe functionality is accomplished using a macro which consists of the following elements:•Ring oscillator that acts as clock source •Counter used as a Master for Flash*Freeze mode •User low static ICC macro, ULSICC •Flash*Freeze Management (FFM) IP core with a minor modification, requiring the following:–2-input AND gate –2-input OR gate with one input invertedFlash*Freeze Control Using an Internal OscillatorFigure1 shows the block diagram for Flash*Freeze Master mode with the internal ring oscillator.Figure 1•Internal Ring Oscillator Block DiagramRing OscillatorWhen an IGLOO or ProASIC3L device is in Flash*Freeze mode, none of the input signals (external clock) are seen by the internal logic. The ring oscillator is the internal clock source to the design, which must providea reasonably reliable clock with minimum power consumption.The ring oscillator consists of an inverter loop with an odd number of inverters used to create a clock. One of the inverters is changed to NAND2, with one input tied to RESET, to prevent harmonics on the clock, which could result from uninitialized power-up values. The generated clock frequency is divided down using toggle flip-flops (T-FF) in series to form a clock divider chain.Use the flow below to arrive at the proper trade-off between power consumption, predictable delay, and optimal utilization:1.The three-input cell A014 is configured as an inverter by tying off inputs A and B to GND, as shownin the Verilog example below. This cell has the longest pin-to-pin delay among all cells in the library.You can use a chain of inverters with one NAND2 gate, as long as the total number of cells in the chain, including NAND2, are odd.module basic_macro( input a, output y);AO14 INV_DLY(.A(GND), .B(GND), .C(a), .Y(y)) /* synthesis syn_noprune = 1*/ ;endmodule2.T-FF is constructed with DFI1C0 to form the clock divider chain:module tffr( inout t, input clk, input clr);DFI1C0 T_FF(.D(t), .CLK(clk), .CLR(clr), .QN(t)) /* synthesis syn_noprune = 1*/ ;endmodule3.To prevent Designer from optimizing the inverter chain by converting AO14 to a regular inverter,and to preserve the number of inverters in the chain, use this compile directive:COB_DO_COB = 0.4.The placement forces the use of local routing resources between inverters in the chain and T-FFs.2Flash*Freeze Control Using an Internal Oscillator 3Figure2 shows the ring oscillator inverter loop placement.Figure 2•Ring Oscillator Inverter Loop PlacementFlash*Freeze Control Using an Internal Oscillator 4Figure 3 shows the ring oscillator T-FF chain placement.The number of inverters and T-FFs can be changed to achieve the desired ring-oscillator frequency. The goal is to have a clock frequency in the KHz range that is useful yet optimal in power consumption. The majority of the logic must be toggling in the KHz range to achieve this.Note: A configuration using 25 inverters (one NAND2 and 24 inverters) and 21 T-FFs was tested on an ActelIGLOO AGL600V2 device using a 1.2 V power supply. The resulting current consumption was 225 µA.ULSICC MacroThis user low static ICC macro has one LSICC input that controls entry to and exit from Flash*Freeze mode.This works in conjunction with the Flash*Freeze input pin.CounterThis is a simple binary up-counter that is clocked by the ring counter. The counter width is dependent on the application requirements—how often the device needs to transition into and out of Flash*Freeze mode. This counter acts as the Master for Flash*Freeze mode.Flash*Freeze Management IP CoreThe Flash*Freeze Management IP core is designed to manage entry to and exit from Flash*Freeze mode,as directed by the external Flash*Freeze input pin only. The Flash*Freeze Management IP core has the INBUF_FF and ULSICC Actel library cells embedded in the core. The core needs to be modified to respond to the internal Flash*Freeze control, so INBUF_FF and ULSICC are brought out and the their inputs modified to include the counter bit, which acts as the internal Flash*Freeze control.Use one of the MSB bits of the counter as an input to the 2-input AND gate that generates the LSICC input to the ULSICC macro. The second input to the AND gate is the Flash_Freeze_Enabled output from the Flash*Freeze Management IP core. This controls entry into Flash*Freeze mode.The same MSB bit is connected to the bubbled input of the 2-input OR gate. The second input to the OR gate is the Flash*Freeze input coming from the dedicated Flash*Freeze pad through INBUF_FF I/O buffer.The output of this OR gate becomes the effective Flash*Freeze input into the IP . This controls the exit from Flash*Freeze mode.Refer to the Flash*Freeze Technology and Low-Power Modes section of the IGLOO or ProASIC3L handbooks for additional information on the device features and use of the Flash*Freeze pin.Figure 3•Ring Oscillator T-FF Chain PlacementFlash*Freeze Control Using an Internal OscillatorTheory of OperationThe ring oscillator provides a free running clock used as the clock for the counter. Depending on the application requirements, any of the ring oscillator clock divider outputs can be used, along with an appropriate counter bit, to arrive at the required time delay for entry to and exit from Flash*Freeze mode. The device enters Flash*Freeze mode with the external Flash*Freeze pin asserted and when the selected count is reached. The device remains in Flash*Freeze mode as long as this bit remains High. Once that bit goes Low, the device exits Flash*Freeze mode. During this period, user logic is up and running, performs any scheduled tasks, and then returns to Flash*Freeze mode.ConclusionThis application demonstrates the usage of the internal oscillator for Flash*Freeze control without an external clock or physically toggling the Flash*Freeze pin. While the application note shows a counter used as a Master running off the internal clock, more involved logic such as a finite state machine (FSM) that takes into account multiple events in a design can easily be the Master running off the internal clock. Related DocumentsIGLOO FPGA Fabric User’s Guide/documents/IGLOO_UG.pdf.ProASIC3L FPGA Fabric User’s Guide/documents/PA3L_UG.pdfFlash*Freeze control with JTAG/documents/FlashFreeze_Ctrl_using_JTAG_AN.pdf.5Actel Corporation 2061 Stierlin Court Mountain View, CA 94043-4655USAPhone 650.318.4200 Fax 650.318.4600Actel Europe Ltd.River Court, Meadows Business ParkStation Approach, BlackwaterCamberley Surrey GU17 9ABUnited KingdomPhone +44 (0) 1276 609 300Fax +44 (0) 1276 607 540Actel JapanEXOS Ebisu Building 4F1-24-14 Ebisu Shibuya-kuTokyo 150 JapanPhone +81.03.3445.7671Fax +81.03.3445.7668Actel Hong KongRoom 2107, China Resources Building26 Harbour RoadWanchai, Hong KongPhone +852 2185 6460Fax +852 2185 6488Actel and the Actel logo are registered trademarks of Actel Corporation.All other trademarks are the property of their owners.Actel is the leader in low power and mixed signal FPGAs and offers the most comprehensive portfolio of system and power management solutions. Power Matters. Learn more at .51900200-0/6.09。

FPGA中flash使用教程(极力推荐)

图1 (二) 完成 Generate Programming File 以后,.bit 文件就生成了。然后打开 iMPACT。如图 2 所示。

版权所有,不得转载,违者必究

图2

图3 点击左上角的 Boundary Scan,会出现图 3 的界面。 在右半区点击鼠标左键,然后点击 Initialize Chain。如图 4 所示。

图6 所用 flash 为 Xilinx 公司的 xcf128x 点击顺序,自左向右: BPI flash(Configure Mutiboot FPGA)-Target FPGA(Virtex5)Storage device(xcf128x)。 然后选择存储路径,命名 mcs 文件。点击 OK 按钮。

版权所有,不得转载,违者必究

FPGA 中 flash 使用教程

(XXXXX 嵌入式公司内部教材,欢迎下载学习,但未经作者同意,不得转载,违者需要承担 法律责任) 。适合 FPGA 初学者,那些大虾们就不要看了。

所用 flash 为 Xilinx 公司的 xcf128x。软件为 Xilinx ISE Design Suite 13.2。 (一) 生成.bit 文件,过程不再赘述。按照图 1 中左下角的顺序依次执行就可以了。

版权所有,不得转载,违者必究

图4 在 Xilinx 图标上点击右键,选择 Assign New Configuration File。选择刚才生成的.bit 文件,点击打开,会出现图 5。

图5 提示是否添加 flash 文件。选择否。

版权所有,不得转载,违者必究

接下来生成 flash 文件,格式为.mcs。 点击左侧的 Create PROM File。界面如图 6 所示。

关于此问题,Xilinx 官方论坛有不少建议。罗里啰嗦说了一大堆,无非就是 usb cable 的问题。换一根 usb 下载线,问题解决!