基于动态二进制翻译技术的仿真器研究

基于二进制翻译的仿真器关键技术研究

[ ywod Is ltrbnr as t n is cinst i lt n Ke r s i ao;ia t nl i ;nt t esmuai mu y r ao u r o o

1 概 述

随着集成电路技术以及通信技术的飞速发展 ,嵌入式系 统的研究与开发 已经成为当今计算机科学的一 个重要分支。

中 圈分类号: P1 T31

基 于二进 制 翻译 的仿 真 器 关键 技 术研 究

张 激,李宁波

( 东 计 算技 术 研 究 所 ,上海 2 0 3 ) 华 0 2 3

摘

要 :介绍基于 构件化 的仿真器设 计方法 ,比较动态二进制翻译 和静态二进制翻译的区别 ,分析 动态二进制翻译技术在仿真器开发中的

翻 译 的 局 限性 ,具 有 较好 的透 明 性 。

二进制翻译把一种 指令集的二进 制可执行代码翻译为可 以在另一种指令集体系结构上的可执行二进制代码 ,实现了 跨平台的指令之间的转换 ,屏蔽了因为指令集而造成 的底层 平台的异构性 ,实现 了体系结构 的虚拟化 ,因此,二进制翻

为解决上述 问题 ,基于软件 的仿真器 已经成为嵌入式系

软 硬件 接 口的 有效 性 ,提 高 了软 硬 件 的并 行开 发 能 力 ,缩 短

译技术在仿真器研发 中被广泛采 用,为实现多平 台仿真提供

了技 术 解 决 方案 。

3 仿真器 的结构

传统仿真器通 常只支持具体的处理器型号或同一系列处 理器 ,而随着 电子技术 的发展 ,目前处理器的种类繁多 ,体 系结构和指令集各不相 同,越来越复杂的应 用对外部设备 的 仿真也提出了新的需求,因此 , 在保证仿真器性能的前提下,

由于 应 用领 域 的特 点 ,嵌 入式 系 统 研 发往 往 依 赖于 特 定 的硬 件 环 境 。对 硬 件 环境 的过 度 绑 定 导致 传 统 的系 统研 发模 式 具 有 明显 的缺 陷 ,即软 硬 件 开 发 无 法并 行 开 展 ,造 成 系 统 开 发 周 期过 长 ,使得 设 计 工 作 缺 乏灵 活 性 。

二进制翻译技术

3 有代表性的二进制翻译系统

目前,二进制翻译已经得到了广泛的重视和研究,一些有代表性的系统见表 2。 表 2 所列出的多数翻译器都与机器特性高度相关,重利用是非常困难的。其中 1994 年 AT&T 公 司开发的 Flashport 二进制翻译器可以运用到多个源、目标平台,但不能完全自动化,需要专 业用户通过图形用户界面(GUI)进行交互。昆士兰(Queensland)大学开发的 UQBT 以及 UQDBT,

代码翻译

MPE XL)

Mimic

IBM

(1987)

[6] 对每条源机器指令代码扩 IBM system /370 IBM RT PC 展倍数为 4 的软件模拟器

Accelera- Tandem tor (1991)

[7] 将 CISC 移植到 RISC 的静 态翻译器,采用解释器作 为补充

TNS CISC

动态翻译

FX!32 UQBT

JVMs JITs BOA Aries

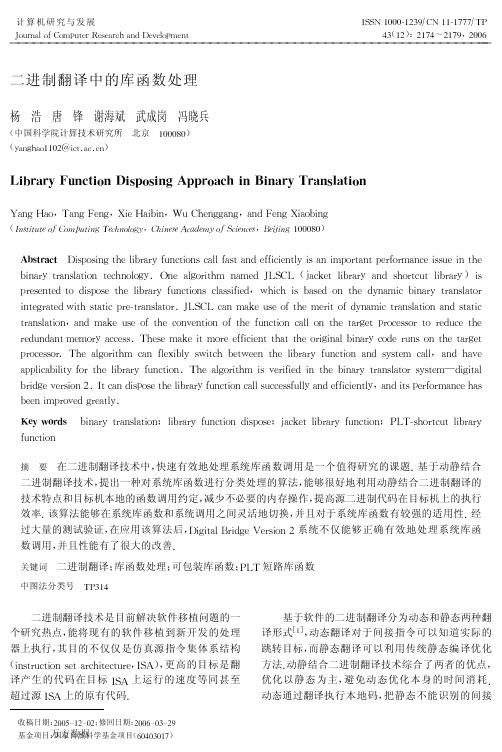

图 1 二进制翻译的三种方法

解释执行对源处理器代码中的每条指令实时解释执行,系统不保存也不缓存解释过的指令,不 需要用户干涉,也不进行任何优化。解释器相对容易开发,比较容易与老的体系结构高度兼容, 但代码执行效率很差[1] 。 [14]

Alpha 的混合模拟器和二

NT)

NT)

进制翻译器

Daisy (1996)

IBM [9] [10] 利用二进制翻译调度

(PowerPC,

PowerPC 代码到超长指令

UnixV)

字(VLIW)处理器,增加并

行性

பைடு நூலகம்

VLIW

Aries

HP

[4] 解释和动态翻译相结合, HP Precision

二进制翻译中的库函数处理

中图法分类号 ,-($A

二进制翻译技术是目前解决软件移植问题的一 个研究热点,能将现有的软件移植到新开发的处理 器上执行,其目的不仅仅是仿真源指令集体系结构 (H2;810<8H/2;9831<=H89<8019,!"X),更高的目标是翻 译产生的代码在目标!"X 上运行的速度等同甚至 超过源!"X 上的原有代码I

译器,结合了解释执行和静态翻译两种翻译模式,能

将运行在(?CD,E,0F:)系统下的应用程序运行在 ($+<3&,E,0F:)下!它主要是用内存模拟 ?CD上的

堆 栈 及 其 参 数 压 栈 和 取 返 回 值 的 行 为,对 大 约

GAHHH个 E,0@A$9"进行包装,一些包装还要对被 调用程序语义进行修改,同时也对 8IJ 组件进行 了包装!

K,0*.&02[@]是应用级动态二进制翻译器! 主要 是对系统调用进行包装!用内存模拟源机器的参数 传递行为,并且还要消除源与目标机器在系统调用

上的语义差 别! 因 为 处 理 系 统 调 用,因 此 相 比 处 理 库函数减少了很多工作量,但是也因此降低了性能!

LB#:[M]和 NO[M]是 ;B8 开发的两个二进制翻 译器,目的是为了使已有的 L$?和 J"9#代码能够 在新的 $+<3&$?9机器上运行!翻译界面定在需要 翻译的主文件和系统库之间,模拟源二进制程序所

TU;K:[D]和 E&+(&-45*[V]分 别 是 U5))02+&01 大学和#50公司开发的可变源和可变目标的动态二 进制翻译器!TU;K: 是对库函数进行包装来处理 系统库函数调用,对一些特殊的库函数要手写修改

动态二进制分析技术概述说明书

Dynamic Binary Instrumentation TechnologyOverviewKunping DuNational Digital Switching System Engineering & Technological Research CenterZhengzhou,China**************Hui ShuNational Digital Switching System Engineering & Technological Research CenterZhengzhou,China*****************************Fei KangNational Digital Switching System Engineering & Technological Research CenterZhengzhou,China**************Li DaiNational Digital Switching System Engineering & Technological Research CenterZhengzhou,China**************Abstract—The Dynamic Binary Analysis technology is a newly emerged technology which can analysis program execution dynamicly. Using this technology, the process of program analysis became more simple and accurate. Foreign researchers had put forward several Dynamic Binary Analysis Platform in recent 10 years. Based on these platforms, users can easily build useful analysis tools which satisfy their own needs. This paper introduces five most representative Dynamic Binary Analysis platforms first. Then, four significant fields and existing applications closely related with Dynamic Binary Analysis technology are explored. In the end of this paper, the feature research hot spots are discussed.Keywords- Dynamic Binary Analysis, program analysis technology, Dynamic Binary InstrumentI.FOREWORDDynamic Binary Analysis[1](DBA) technology is a kind of dynamic program analysis method which can analyze program's memory structure and add specific instructions for monitoring and testing program's execution.The DBA technology enables users to monitor program's behavior under the premise of not affecting the results of program execution by inserting additional appropriate analysis code into the target program, this procedure called Dynamic Binary Instrument(DBI).In addition,using DBA technology,the analysis can complete without source code, no need to recompile and link,so that this technology can be used in many cases.The research on DBA technology began in the 1990s, initially applied to the dynamic optimization and testing of the program.Due to its versatility and accuracy of the analysis process,it has been used for memory testing,software behavior monitoring,reverse engineering and some other research areas recently..This paper first introduces five most widely used DBA platform,they are Shade, DynamoRIO, Valgrind, Pin and Nirvana. On this basis, summarizes the application status and popular tools build on DBA platform in the field of memory testing and optimization, data flow tracking, software behavior analysis, reverse engineering and parallel program analysis. Finally, the application prospects of DBA technology are discussed.II.D YNAMIC B INARY A NALYSIS P LATFORM So far, the foreign researchers had put forward a number of DBA platform, such as Shade, DynamoRIO, Valgrind etc. Based on these platforms, users can easily develop their own Dynamic Binary Instrumentation(DBI) tool. Below, we will detail the Shade, DynamoRIO, Valgrind, Pin, and Nirvana.A.Shade[2]It is the first the DBI platform which implements in Solaris system. Shade uses binary translation and cache technology, it has inner support of recording the register state and opcode information..B.DynamoRIO[3]DynamoRIO is an open-source dynamic binary optimization and analysis platform which evolves from Dynamo. It is available both in Windows and Linux system, and can record the execution instruction information efficiently, but doesn't support data flow recording. This platform is mainly used for the dynamic optimization of program in instruction level.C.Valgrind[4]An open source DBI platform under Linux which can efficiently record the instructions flow and data flow information of executable file in Linux. But because of the different operation mechanism of Linux and Windows system, this platform is still difficult to transplant to Windows system. D.Pin[5]Pin is a dynamic binary instrumentation framework for the IA-32 and x86-64 instruction-set architectures that enables the creation of dynamic program analysis tools. The tools createdNational Conference on Information Technology and Computer Science (CITCS 2012)using Pin, called Pintools, can be used to perform program analysis on user space applications in Linux and Windows. Pin provides a rich API that abstracts away the underlying instruction-set idiosyncrasies and allows context information such as register contents to be passed to the injected code as parameters. Pin automatically saves and restores the registers that are overwritten by the injected code so the application continues to work. Limited access to symbol and debug information is available as well. Pin was originally created as a tool for computer architecture analysis, but its flexible API and an active community (called "Pinheads") have created a diverse set of tools for security, emulation and parallel program analysis. Pin is proprietary software developed and supported by Intel and is supplied free of charge for non-commercial use. Pin includes the source code for a large number of example instrumentation tools like basic block profilers, cache simulators, instruction trace generators, etc. It is easy to derive new tools using the rich API it provides.E.Nirvana[6]Microsoft's latest development DBI platform, mainly includes two key module: program simulation execution module and JIT (just in time) binary translation module. But it has not been to market, only for Microsoft internal use. According to relevant data, the platform can well support tracking and playback function of Windows executable files in instruction level. There will be very good application prospects especially in software reverse engineering.III.DBI A PPLICATION FIELDA.Memory testing and optimizationDBI framework developed up to now, the most widely used application is for the building of memory monitoring tools. DBI-based memory testing tools have obvious advantages than the common memory detection tool in the detection efficiency and detection accuracy, as well as the support of the underlying system. Therefore, there have been a lot of DBI based memory monitoring tools since DBI technologies emerged. Most of those tools can not only detect the memory using situation of a program, memory errors that may exist in the program, illegal use of memory, memory leaks, but also can detect buffer overflow accurately. The following details on several of BDI-based memory monitoring tools and related research.a)Memcheck: Memcheck is a memory error detector based on Valgrind. It can detect many common problems appear in C and C++ programs, such as: accessing memory you shouldn't, using undefined values, incorrect freeing of heap memory, memory leaks etc.b)Dr.Memory: Dr. Memory is built on the open-source dynamic instrumentation platform DynamoRIO. It is an excellent memory checking tool that supports both Windows and Linux. Dr. Memory uses memory shadowing to track properties of a target application’s data during execution. So that it can detect memory error more accurately. In addition, Dr. Memory provide two instrumentation paths: the fast-path and the slow-path. The fast-path is implemented as a set of carefully hand-crafted machine-code sequences or kernels covering the most performance-critical actions. Fast-path kernels are either directly inlined or use shared code with a fast subroutine switch. Rarer operations are not worth the effort and extra maintenance costs of using hand-coded kernels and are handled in the slow-path in C code with a full context switch used to call out to the C function. Through using different path in different situation, the efficiency of detection is increased greatly.B.Dynamic Taint AnalysisThe dynamic taint analysis technology is a common technique in the field of application security detection. By analysis of the data used in the program, the program's data is marked as “contaminated”(Tainted), and “not contaminated” (UnTainted) categories, while in the process of implementation of the procedures to control the spread of contaminated properties by analyzing the illegal use of the data propagation path of the contaminated property to find the loopholes that exist of the program. DBI based platform, you can build a dynamic data flow tracking tools, such data flow tracking tool with a wide tracking range, and analysis results are accurate. Here are two methods based on DBI data flow tracking tool.a)TaintCheck: TaintCheck is a dynamic taint analysis tool based on Valgrind, for the automatic detection, analysis, and signature generation of exploits on commodity software. TaintCheck's default policy detects format string attacks, and overwrite attacks that at-tempt to modify a pointer used as a return address, function pointer,or function pointer offset. Its policy can also be extended to detect other overwrite attacks, such as those that attempt to overwrite data used in system calls or security-sensitive variables. TaintCheck gave no false positives in its default configuration. in many cases when a false positive could occur, it is a symptom of a potentially exploitable bug in the monitored program. For programs where the default policy of TaintCheck could generate a false positive. Once TaintCheck detects an overwrite attack, it can automatically provide information about the vulnerability and how the vulnerability is exploited. By back-tracing the chain of tainted data structure rooted at the detection point, TaintCheck automatically identifies which original flow and which part of the original flow have caused the attack.b)Dytan: A Generic dynamic taint analysis framework based on Pin. The goal of this tool is to be a generalized tainting framework that can be used to perform dataflow and control-flow analysis on an x86 executable. The dynamic tainting of Dytan consists of: (1)associating a taint label with data values;(2)propagating taint labels as data values flow through the program during execution.As long as user provides XML configuration file, in which specify: taint sources, propagation policy, and sinks.C.Reverse engineering applicationDynamic tracking is one of the commonly used method in reverse engineering. The procedure of dynamic tracking is like this: using dynamic debugging software (eg: OllyDebug) load the program, then follow the tracks of program executionstep-by-step. This approach can be summarized in a word:analysis when tracking. And the analysis relies heavily onmanual, it is difficult to automate it. By means of DBI platform,one can separate the analysis work to the tracking process byusing DBI tool recording the execution information of targetsoftware, analyzing the recorded information by other a utomatic tools. Such processing procedure can save a lot of human labor. And the automatic analysis of the recordedinformation also can greatly reduce the software reversingcycle.In 2008 blackhat Danny Quist. etc propose a DBI basedtemporal reverse engineering. By DBI platform Pin, they getthe basic block execution sequence. By analyzing andvisualizing these block information, it help analyst understandthe program behavior quickly. In addition, in reference[7], theauthor proposed a DBI based protocol reverse method, themain idea of the paper is recording the data-flow of a softwarewith DynamoRIO, then parse the protocol field with their ownautomatic tool.D.Parallel program analysis[8]With the development of high performance computingtechnology, the design of parallel programs is becomingincreasingly important. Parallel debugging and performanceevaluation of parallel programs are difficult problems in thefield. The traditional Parallel debugging and performance evaluation tools are mostly based on source code instrumentation, which makes the workload of analyzing parallel programs very huge, and as the coding language and software upgrade, testers need to do some modifications. The most deadly is if you can’t get the source code of the parallel program, the test can’t be conducted. DBA technology making the analysis of parallel programs has nothing to do with the source code, the analysis process is more transparent and more efficient. The following is several parallel program analysis tools based on DBI framework.a)Intel Parallel Inspector: The Intel Parallel Inspector analyzes the multithreaded programs’ execution to find memory and threading errors, such as memory leaks, references to uninitialized data, data races, and deadlocks. Intel Parallel Inspector uses Pin to instrument the running program and collect the information necessary to detect errors. The instrumentation requires no special test builds or compilers, so it’s easier to test code more often. Intel Parallel Inspector combines threading and memory error checking into one powerful error checking tool. It helps increase the reliability, security, and accuracy of C/C++ applications from within Microsoft Visual Studio.b)CMP$im: Memory system behavior is critical to parallel program performance. Computational bandwidth increases faster than memory bandwidth, especially for multi-core systems. Programmers must utilize as much bandwidth as possible for programs to scale to many processors. Hardware-based monitors can report summary statistics such as memory references and cache misses; however, they are limited to the existing cache hierarchy and are not well suited for collecting more detailed information such as the degree of cache line sharing or the frequency of cache misses because of false sharing. CMP$im uses Pin to collect the memory addresses of multithreaded and multiprocessor programs, then uses a memory system’s software model to analyze program behavior. It reports miss rates, cache line reuse and sharing, and coherence traffic, and its versatile memory system model configuration can predict future systems’ application performance. While CMP$im is not publicly available, the Pin distribution includes the source for a simple cache model, dcache.cpp.IV.F UTURE RESEARCHDBA technology as a new program analysis method, have not yet been widely used. As people get more comprehensive understanding on its properties and advantages, it will play a role in more areas in more fields. Future research on dynamic binary analysis techniques are mainly concentrated in the following aspects:a)Improvement of performance for DBI platform:Based on DBI build tools have a common weakness: a certain degreeof reduction on efficiency to instrumentation program. In general, the use of DBI make the original program run rate 3-5 times lower, in future studies, how to improve the performance and efficiency of the DBI platform is an important research direction.b)The combination of static analysis methods:DBA method has many advantages, but it is essentially a dynamic analysis method that can not overcome the shortcoming of only one execution path can be passed by a time. In the future, how to combine the dynamic binary analysis with the static analysis methods is a future research focus.c)solve the problem of huge amount of record information: Using DBI instrument a program ,weather in instruction level or function level, the record set could be very huge. How to reduce the volume of the record set in the premise of ensure enough information, how to improve the efficiency of information processing, how to visualize those information are all the research spot in the future.DBA technology, with the advantages of extensive (needn't source code) and accuracy (run-time instrument), has already come to the forefront in several areas, and provides new idea to solve the problems in related field. The DBA technology would bring more breakthrough for more field in the future.R EFERENCES[1]Nicholas Nethercote. Dynamic Binary Analysis and Instrumentation orBuilding Tools is Easy [D]. PhD thesis. University of Cambridge, 2004. [2]Bob Cmelik and David Keppel. Shade: a fast instruction-set simu lateorfor execution profiling [R]. In:ACM SIGMETRICS, 2004.[3]Derek L. Bruening. Efficient, Transparent, and Comprehensive RuntimeCode Manipulation [D]. PhD thesis, M.I.T, 2004. /. [4]hercote. Valgrind: A Framework for Heavyweight DynamicBinary Instrumentation [C]. In:Proceedings of the 2007 ACM SIGPLAN conference on Programming language design and implemention, San Diego,California,USA: 2007. 89-100..[5]Chi-Keung Luk. Pin: building customized program analysis tools withdynamic instrumentation [C]. In:Programming Language Design and Implementation. 2005: 190-200.[6]Sanjay Bhansali. Framework for Instruction-level Tracing and Analysisof Program Executions [C]. Second International Conference on Virtual Execution Environments VEE, 2006. [7]HE Yong-jun, SHU Hui, XIONG Xiao-bing. Network Protocol ReverseParsing Based on Dynamic Binary Analysis.[J]. Computer Engineering.2010.36(9):268-270[8]Moshe Bach, Mark Charney, Robert Cohn, etc. Analyzing ParallelPrograms with Pin. [J]. IEEE Computer. 2010:34-41.。

二进制翻译系统BATSUP中的动态翻译器的设计与实现

二进制翻译系统BATSUP中的动态翻译器的设计与实现黄英兰;杨晋兴;钟珊

【期刊名称】《航空计算技术》

【年(卷),期】2005(035)003

【摘要】针对目前航电系统硬件的升级换代而导致老的软件的不可用的问题,提出了一个用于航电系统软件升级的二进制翻译系统(BTASUP系统).该系统能把解释执行和动态翻译结合起来,在PowerPC处理器上实现对1750A处理器的二进制可执行代码的透明执行.介绍了系统的结构和工作原理,重点讨论了作为系统重要组成部分的动态翻译器的设计与实现.

【总页数】5页(P50-53,58)

【作者】黄英兰;杨晋兴;钟珊

【作者单位】中国航空计算技术研究所,陕西,西安,710068;中国航空计算技术研究所,陕西,西安,710068;中国航空计算技术研究所,陕西,西安,710068

【正文语种】中文

【中图分类】TP314

【相关文献】

1.系统级动态二进制翻译系统中访存异常的制导技术研究 [J], 张龙龙;董卫宇;王立新

2.一个用户级动态二进制翻译系统的设计与实现 [J], 曹宏嘉;俞磊;邓鹍;周兴铭

3.动态二进制翻译器QEMU中冗余指令消除技术研究 [J], 宋强;陈香兰;陈华平

4.间接转移指令在动态二进制翻译器中的预测方法 [J], 徐超豪;臧斌宇

5.一个动态二进制翻译系统的设计与实现 [J], 刘毅;臧红伟;谢克嘉;杨晋兴

因版权原因,仅展示原文概要,查看原文内容请购买。

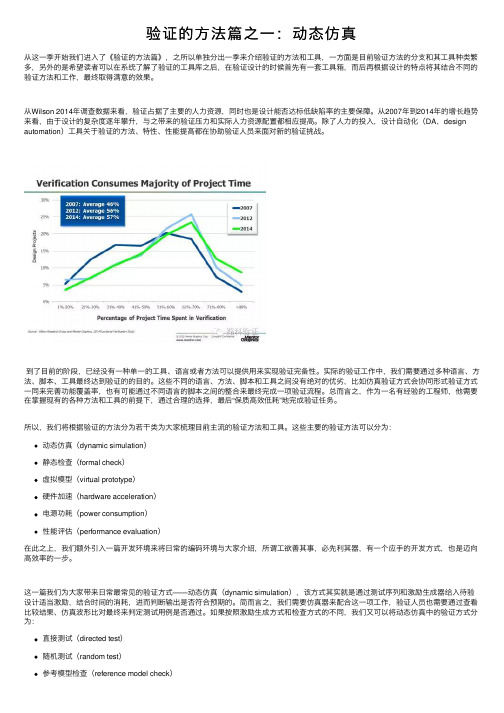

验证的方法篇之一:动态仿真

验证的⽅法篇之⼀:动态仿真从这⼀季开始我们进⼊了《验证的⽅法篇》,之所以单独分出⼀季来介绍验证的⽅法和⼯具,⼀⽅⾯是⽬前验证⽅法的分⽀和其⼯具种类繁多,另外的是希望读者可以在系统了解了验证的⼯具库之后,在验证设计的时候⾸先有⼀套⼯具箱,⽽后再根据设计的特点将其结合不同的验证⽅法和⼯作,最终取得满意的效果。

从Wilson 2014年调查数据来看,验证占据了主要的⼈⼒资源,同时也是设计能否达标低缺陷率的主要保障。

从2007年到2014年的增长趋势来看,由于设计的复杂度逐年攀升,与之带来的验证压⼒和实际⼈⼒资源配置都相应提⾼。

除了⼈⼒的投⼊,设计⾃动化(DA,design automation)⼯具关于验证的⽅法、特性、性能提⾼都在协助验证⼈员来⾯对新的验证挑战。

到了⽬前的阶段,已经没有⼀种单⼀的⼯具、语⾔或者⽅法可以提供⽤来实现验证完备性。

实际的验证⼯作中,我们需要通过多种语⾔、⽅法、脚本、⼯具最终达到验证的的⽬的。

这些不同的语⾔、⽅法、脚本和⼯具之间没有绝对的优劣,⽐如仿真验证⽅式会协同形式验证⽅式⼀同来完善功能覆盖率,也有可能通过不同语⾔的脚本之间的整合来最终完成⼀项验证流程。

总⽽⾔之,作为⼀名有经验的⼯程师,他需要在掌握现有的各种⽅法和⼯具的前提下,通过合理的选择,最后“保质⾼效低耗”地完成验证任务。

所以,我们将根据验证的⽅法分为若⼲类为⼤家梳理⽬前主流的验证⽅法和⼯具。

这些主要的验证⽅法可以分为:动态仿真(dynamic simulation)静态检查(formal check)虚拟模型(virtual prototype)硬件加速(hardware acceleration)电源功耗(power consumption)性能评估(performance evaluation)在此之上,我们额外引⼊⼀篇开发环境来将⽇常的编码环境与⼤家介绍,所谓⼯欲善其事,必先利其器,有⼀个应⼿的开发⽅式,也是迈向⾼效率的⼀步。

基于X86平台的ARM指令集模拟器的设计

基于X86平台的ARM指令集模拟器的设计贾少波【摘要】With the development of embedded system software as well as the wide use of embedded applications in all kinds of fields for business,the embedded system development has beenemphasized.Nowadays,the refreshing rate of embedded software becomes faster.Therefore,it requests that the customized applications be developed during a shorter period.However,in general,the environment of embedded system run time is customized by consumers; hence the implementation of simulation for embedded hardware environment can highly improve the efficiency for embedded development.Aiming at this problem,considering the current study of ARM instruction set simulator in embedded system development,this article provides a design of ARM instruction set simulator.%随着嵌入式系统软件的发展,以及嵌入式应用在各个行业的普及,嵌入式系统开发已经被越来越多的人所关注.目前,嵌入式软件更新频率快,因此要求开发者在短期内能开发出具有针对型的应用程序,然而嵌入式系统运行环境往往是用户制定,并且运行在特定的硬件环境中.常规的软件开发方法往往导致嵌入式系统开发效率低下,同时大幅提高了开发成本.因此,实现对嵌入式系统硬件环境的仿真能有效提高嵌入式系统开发效率.本文针对此问题,结合现有ARM体系架构和指令集模拟器实现原理,提出了一套基于X86平台的ARM指令集模拟器的设计方案.【期刊名称】《电子设计工程》【年(卷),期】2013(021)012【总页数】4页(P164-166,169)【关键词】嵌入式系统开发;ARM体系架构;指令集模拟技术;ARM指令集模拟器【作者】贾少波【作者单位】西安财经学院信息与教育技术中心,陕西西安 710061【正文语种】中文【中图分类】TP302如今,仿真技术和虚拟技术被广泛应用各个领域,特别在嵌入式系统的开发过程中,由于在不同应用领域中,嵌入式开发要求的硬件体系差别很大,用软件进行系统仿真或虚拟硬件非常必要。

用户级动态二进制翻译系统设计

被 翻译程 序的二进制代码 即可 , 而不必 要求将 被翻译 程序 的源

代码作 为翻译 系统的输入 , 样就 可 以实 现兼容 非本 机 IA应 这 S

来进行优化 。动态翻译器 采用 边 翻译 边执行 的方 法 , 只需要 保存一部 分将要执行的代码 。运行 时对输 入的源二进制文件动

用 户 级 动 态 二进 制 翻 译 系统 设 计

吴 浩 管海兵 梁阿磊

( 上海交通大学 信息安全学院 上海 20 4 ) 0 20

摘 要

介 绍 了一个 用户级动态二进制翻译 系统的结构设计 , 系统实现 了 a 到 x6的用 户级 动态翻译 。详细介 绍该 系统各 该 r m 8

维普资讯

第2 4卷 第 1 0期

20 0 7年 1 月 0

计算机 应 用 与软件

Co utrAp lc to sa d S f r mp e p i ai n n o t e wa

V0 . 4 No 1 12 . 0 0c . 0 t 2 07

1 系统 总体 结构

本系统是一个动态 的用户级二进制翻译 系统 。其基 本设 计

思想如 图 2所 示 , 系 统 的 功能 是 将 一 ( 时 支 持 a 7与 本 同 m r

am ) 的 E F格式 的可 执行 文 件翻 译 到中 间代 码 ( r9下 L 由标 准 C 实现 ) 然后编译 到 目标 IA上 , x6的 I 一2上运行 。 , S 即 8 A3 系统 由控制核 心 、 释器 、 解 翻译器 、 编译 器 和翻译缓 存几 部 分组成 。运行 时 , 控制核心 会维 护一个 软件 的 目标 机虚拟 C U P 状态 , 成为 ev 它 包 括通 用 寄存 器 、 n, 段寄 存 器 、 志 位 寄存 器 标

动态二进制翻译优化研究的开题报告

动态二进制翻译优化研究的开题报告一、选题的背景和意义随着计算机技术的不断发展,人们越来越依赖于计算机软件来提高工作效率和准确性,因此,计算机软件的开发和优化成为了一个重要的研究领域。

在编写软件时,我们通常使用高级编程语言来描述算法和程序,但这些高级语言通常需要经过复杂的编译和链接处理才能生成可执行文件,而这个过程中存在许多性能瓶颈,例如二进制代码的优化、代码翻译等。

因此,研究如何优化二进制代码翻译的问题是非常重要的,具有广泛的应用前景。

二、选题的研究现状动态二进制翻译(Dynamic Binary Translation,DBT)是一种通过执行中间代码来翻译二进制代码的技术,在计算机系统中广泛应用。

目前,DBT 的实现主要有两种方式:JIT(Just-in-Time)编译和从解释执行。

JIT 编译是指在第一次遇到某段代码时将其翻译成可执行的机器码,之后再执行这段机器码。

而从解释执行则是执行一段代码时,通过解释器来进行翻译。

这两种方法在翻译二进制代码的性能和准确性方面有不同的表现。

目前,DBT 的优化研究主要包括以下方面:指令翻译技术、动态指令选择、动态指令调度、缓存管理等。

三、选题的研究内容和研究方法本课题旨在研究如何通过优化动态二进制翻译来提高计算机系统的性能。

具体研究内容包括以下几个方面:1、指令翻译技术。

研究如何构造更高效的指令翻译器,提高机器码的翻译效率和准确性,以及如何处理复杂指令。

2、动态指令选择。

研究如何在不同上下文中选择最优的指令,提高指令的执行效率。

3、动态指令调度。

研究如何根据指令之间的依赖关系来进行指令调度,避免指令执行时的冲突。

4、缓存管理。

研究如何利用缓存技术提高动态二进制翻译的效率和准确性。

本课题所使用的研究方法主要包括理论分析、仿真实验和实际测试三种。

在理论分析阶段,我们主要是根据相关的研究文献来进行模型的构建和理论推导,在仿真实验阶段,我们将根据理论分析的结果,使用相应的仿真工具来进行实验;在实际测试阶段,我们将设计相应的实验系统,通过实际测试来验证我们的理论分析和仿真实验结果。

动态模拟与仿真

▪ 并行计算与高性能计算

1.并行计算:利用并行计算技术,可以将大规模模拟任务分配 给多个计算节点同时进行,大幅提高计算效率。 2.高性能计算:利用高性能计算设备,可以处理更复杂的模型 和更大的数据量,进一步提升模拟的精度和效率。

动态模拟与仿真的关键技术

▪ 可视化技术与用户交互

1.数据可视化:通过可视化技术,可以将模拟结果以直观的方 式呈现给用户,便于用户理解和分析。 2.用户交互:提供良好的用户交互界面,可以让用户方便地设 置参数、观察结果、调整模型,提高用户体验。

智能交通

1.在智能交通系统中,动态模拟与仿真可用于交通流量管理、路况预测和信号控制优化。 2.通过模拟不同交通场景,评估交通规划方案的有效性,提高道路通行效率。 3.结合车联网技术,实现智能交通系统的智能化和自适应。

动态模拟与仿真的应用领域

▪ 能源系统

1.动态模拟与仿真在能源系统中的应用主要包括电源调度、电网优化和新能源接入。 2.通过模拟能源系统的运行,提高电源的稳定性和经济性。 3.结合大数据技术,实现能源系统的智能化管理和预测。

动态模拟与仿真

目录页

Contents Page

1. 动态模拟与仿真简介 2. 动态模拟与仿真的应用领域 3. 动态模拟与仿真的基本原理 4. 动态模拟与仿真的关键技术 5. 动态模拟与仿真的建模过程 6. 动态模拟与仿真的软件工具 7. 动态模拟与仿真的案例分析 8. 动态模拟与仿真的未来展望

动态模拟与仿真

动态模拟与仿真的软件工具

▪ COMSOLMultiphysics

SOLMultiphysics是一款多物理场仿真软件,具有强大的动态模拟和仿真功能。该软件可以进行多种物理场 的耦合模拟,如电磁场、流体动力学、热传导等。 SOLMultiphysics具有丰富的材料库和边界条件设置,可以根据实际需求进行精确模拟。同时,该软件支持 多种网格划分和求解器选择,以保证计算精度和效率。 SOLMultiphysics具有良好的用户界面和前后处理功能,方便用户进行操作和数据分析。同时,该软件还支 持多种编程语言接口,方便用户进行二次开发和定制化应用。 以上介绍了Ansys、Simulink和COMSOLMultiphysics三款动态模拟与仿真软件工具的。这些软件工具在各自领域 具有广泛的应用和认可,可以根据实际需求选择合适的工具进行动态模拟与仿真分析。

dynamorio工作原理

dynamorio工作原理DynamoRIO是一款动态二进制工具集(Dynamic Binary Instrumentation,简称DBI),用于创建和使用二进制插装工具。

它提供了一个灵活的框架,可以在应用程序运行时对其进行修改和监视,而无需重新编译和重新链接代码。

DynamoRIO的工作原理可以分为几个关键步骤:加载、翻译、执行和卸载。

下面将详细介绍每个步骤的工作原理。

1.加载:DynamoRIO通过注入到目标进程中的方式来加载。

在目标进程运行期间,在内存中的适当位置分配内存并写入DynamoRIO代码。

然后,将控制权传递给DynamoRIO,它开始执行以下步骤。

2.翻译:在翻译阶段,DynamoRIO会将目标进程的二进制代码动态翻译成可以修改和监视的中间表示(IR)。

为了实现这一点,DynamoRIO使用一种称为DynamoRIO指令集(DynamoRIO Instruction Set)的IR。

该IR具有与原生二进制代码相同的语义,但比原始代码更易于解析和修改。

3.执行:执行阶段是最关键的阶段,其中DynamoRIO通过插入附加的仪器代码来修改目标进程的行为。

DynamoRIO提供了一组API来允许开发者在主要的指令执行前后插入自定义的代码。

这允许在执行每一条指令时动态修改和监视寄存器、内存和其他关键状态。

通过这种方式,DynamoRIO可以实现功能如性能分析、内存检测、代码覆盖率测试等。

此外,DynamoRIO还实现了一种称为基本块工具的优化技术。

基本块是一段连续的指令序列,没有分支和跳转。

DynamoRIO可以事先静态分析应用代码,将其划分为基本块,并对这些基本块进行优化。

例如,它可以将几个基本块的代码合并以减少内存访问或减少分支预测错误,从而提高性能。

4.卸载:卸载阶段是在动态二进制工具完成工作后将其从目标进程中删除的过程。

在此阶段,DynamoRIO负责进行内存释放和恢复目标进程的原始状态。

动态二进制翻译优化研究的开题报告

动态二进制翻译优化研究的开题报告一、选题背景随着计算机技术的不断发展,二进制翻译技术在计算机系统中扮演着越来越重要的角色。

动态二进制翻译技术是一种基于虚拟化技术的二进制翻译技术,它能够在不修改原始二进制代码的情况下,将其翻译成目标平台的指令集,从而实现跨平台的应用程序运行。

然而,由于动态二进制翻译技术需要在运行时进行指令翻译,因此其性能往往受到较大的影响。

为了提高动态二进制翻译技术的性能,研究者们提出了各种优化方法。

其中,基于翻译缓存的优化方法是一种比较有效的方法,它通过缓存已经翻译过的指令,避免重复翻译,从而提高翻译效率。

然而,由于翻译缓存的大小和命中率对性能影响较大,因此如何优化翻译缓存成为了动态二进制翻译优化的一个重要研究方向。

二、研究目的和意义本文旨在探究动态二进制翻译优化中基于翻译缓存的优化方法,分析不同的翻译缓存替换策略对性能的影响,并提出一种优化策略,以提高动态二进制翻译技术的性能。

本研究的意义在于:1.对动态二进制翻译技术进行深入研究,提高对其原理和性能的理解。

2.分析不同的翻译缓存替换策略对性能的影响,为动态二进制翻译技术的优化提供参考。

3.提出一种优化策略,以提高动态二进制翻译技术的性能,为跨平台应用程序的运行提供更好的支持。

三、研究内容和方法本文将分为以下几个部分:1.介绍动态二进制翻译技术的原理和实现方法。

2.分析翻译缓存的基本原理和不同的替换策略,并比较它们的性能。

3.提出一种基于翻译缓存的优化策略,以提高动态二进制翻译技术的性能。

4.使用模拟器对不同的翻译缓存替换策略和优化策略进行实验,并分析实验结果。

本研究将采用实验和理论相结合的方法,通过模拟器进行实验,分析不同的翻译缓存替换策略和优化策略对性能的影响,并基于理论分析提出相应的优化策略。

四、论文结构本文将分为以下几个部分:第一章:选题背景和研究意义,介绍本研究的背景和研究目的。

第二章:相关技术介绍,介绍动态二进制翻译技术的原理和实现方法,以及翻译缓存的基本原理和不同的替换策略。

浅析计算机体系结构模拟技术现状、挑战与展望

浅析计算机体系结构模拟技术现状、挑战与展望1 引言计算机系统日益复杂,其研制难度不断增加,开发风险不断加大,研制周期越来越长,体系结构模拟技术在计算机体系结构研究和系统设计中的作用愈加显著. 通过对计算机系统的建模、仿真及评估,科研人员可以验证新型体系结构设计;将该技术导入产品设计则可优化系统方案、降低开发风险并提升开发效率.作为一种系统评估手段,体系结构模拟器运行在宿主机上,通过加载测试程序来验证新的设计方案,发现其中潜在的缺陷,从而改进设计并有效控制风险. 体系结构模拟器通常使用软件方式对部分或全部计算机系统硬件建模,对体系结构的指令集架构、处理器、存储系统、网络传输拓扑结构等进行模拟,验证系统的功能和性能. 体系结构模拟器已成为系统研究和设计开发中不可或缺的工具.早期体系结构模拟采用分析验证技术,如数据驱动验证,即跟踪收集性能测试程序在目标计算机上运行所产生的数据信息,通过分析该数据信息来评估体系结构的性能.这是一种后验证方法,不利于在项目早期开展系统架构分析和风险评估. 为在项目早期论证系统设计方案,在数据驱动验证的基础上又提出了模型分析技术,该技术使用数学工具对计算机系统各部件间的接口进行建模,通过评估资源利用率和相应时序特性来验证目标系统的性能. 模型分析技术可在体系结构设计初期发现影响系统性能指标的关键因素,从而指导方案设计和改进. 但由于模型建立及求解过程复杂,为了简化模型,必须将部分细节特征抽象化,导致模型分析结果精度低,测试结果不能准确反应真实系统特性. 软件模拟技术则可以较好的解决这一问题.模拟器使用软件的方式模拟真实硬件的功能及时序特性. 软件模拟技术可模拟程序执行的全过程,获得程序运行过程中系统的动态行为及特性. 然而,软件模拟技术在表现出较高精度和灵活性的同时,也存在模拟速度过慢的问题. 为了提高模拟速度,软件模拟与硬件加速相结合的技术即混合模拟技术应运而生. 混合模拟技术将体系结构中的部分或全部部件用FPGA 或硬件仿真器( emulator) 实现,从而提高模拟性能.2 模拟精度模拟器精度主要受三个方面因素影响:1) 系统建模精确程度;2) 输入参数拟合程度;3) 指令执行时序的精确程度.模型要精确的匹配真实系统设计,需开发者准确的理解建模任务,并正确的开发出相应模型; 在此基础上,要针对系统具体行为设计输入参数集. 为了实现性能模型的简洁和快速执行,开发者往往将一些细节特征抽象化,导致系统时序出现偏差,降低模拟精度. 在实际应用中,还存在其它因素影响模拟精度,如缓存控制指令的精确性、I /O 系统模拟的准确性等.2. 1 踪迹驱动模拟技术早期的体系结构模拟器主要采用踪迹驱动( trace-driven)、数学建模分析等方法. 踪迹驱动技术收集指令在已有计算机系统中执行所产生的踪迹数据,并将这些信息作为输入驱动模拟器运行. 这种技术的优点在于可仅对系统的局部进行细致模拟而无需关注系统的其它部分,从而降低了开发复杂度并提升了执行速度. 缺点是踪迹本身过滤了系统的动态信息,如分支预测错误等,因而无法观察系统的动态特征,并且踪迹一般是基于特定参数的固定序列,因此无法代表不同参数对应的多种执行情况. 典型的轨迹驱动模拟器包括磁盘系统模拟器DiskSim、Cache 模拟器Dinero等. 数学建模分析方法通过建立数学模型来描述目标系统特征,由于不能精确的获得性能数据,因此这种方法的误差较大.2. 2 执行驱动模拟技术执行驱动( execution-driven) 模拟技术建立目标系统的功能和性能模型,通过应用程序的执行获取性能数据,从而获得较高的模拟精度,执行驱动的模拟器使用目标程序的二进制代码作为输入来驱动模拟过程. 在模拟过程中,模拟器模拟指令的动态执行( 如分支预测等) 过程,从而在不需要目标系统硬件的情况下获得更接近真实目标系统运行的结果,并能够精确的模拟不同部件对系统性能的影响. 相对于踪迹驱动等技术,执行驱动减小了存储空间的开销,模拟器的输入数据量只与程序的静态指令数成比例,动态指令则在模拟过程中由模拟器生成,一定程度上会影响执行速度. 采用执行驱动的模拟器可以运行完整的操作系统和应用程序,是实现全系统模拟的一种常用方法. 执行驱动技术已经成为体系结构模拟的主流技术,典型的应用有SimpleScalar、SimOS、Proteus等.3 模拟速度模拟速度是衡量模拟器性能的重要指标. 精确的性能模拟是非常耗时的过程,特别是随着系统中处理器核心数的迅猛增长,模拟大规模计算机系统所需要的时间会变得难以接受. 以200KIPS 的模拟执行速度模拟单核1 秒运行需要数小时,而模拟千核系统的 1 秒运行需要耗时一年以上,这显然不能满足现代体系结构的研究与设计需求. 模拟加速一直以来都是模拟技术研究领域重点关注的问题. 典型的加速方法包括动态二进制翻译( DBT) 、穿线码加速、采样加速、同构加速、并行模拟加速、硬件加速等.3. 1 动态二进制翻译动态二进制翻译( DBT) 将某个指令集上可执行的二进制代码翻译到宿主机指令集执行. 二进制翻译最初采用解释执行,它对源处理器代码中的每条指令实时解释执行,系统不保存解释后的代码,翻译一条便执行一条指令. 解释器相对容易开发,但对代码执行不做任何优化,执行效率低. 静态翻译技术解决了这一问题,它在源处理器代码执行之前对其进行翻译,有足够的时间对翻译后的代码做完整细致的优化,并且一次翻译的结果可以多次使用,避免了多次解释操作带来的时间开销. 但是,静态翻译无法很好的解决代码自修改、间接过程调用、间接跳转等问题.动态翻译是一种实时编译技术,即在程序运行过程中对执行到的片断进行翻译,解决了静态翻译存在的问题. 程序运行时,DBT 翻译器在其本地地址空间开始执行指令、逐行解码,遇到系统调用指令则采用翻译器自身的调用函数进行替换,在调用点接替操作系统内核的职能. 当程序中有频繁重复的指令片段时,DBT 将直接执行已经翻译好的相应代码,从而省去了重新编译的过程. 高速缓存中放置翻译后程序片断的位置称为翻译缓存,当该缓存填满时,DBT 采用两种方式处理: 清空翻译缓存区域、重新加载; 或者增加缓存区的大小. 如果程序的一个运行指令集合超出翻译缓存空间,则第一种方法将会失效; 而第二种方法会降低cache 的利用率,因为大多情况下需要一次翻译的片断长度有限; 具体策略根据需求进行选择. 动态二进制翻译可以解决代码自修改问题,利用执行时的动态信息去发掘优化机会,对用户能做到完全透明. 将DBT 应用于体系结构模拟器,编译器可以选择只翻译那些频繁执行的程序和用户需要详细模拟的程序,这样既能提高cache 利用率,也能让编译器更好的优化目标代码,有效提高模拟速度.3. 2 采样技术采样技术是通过减少模拟运行的指令数来达到模拟加速的目的,具体分为随机采样、周期采样和统计采样. 随机采样是指随机选择一些程序片断进行模拟运行,将模拟结果以某种方式合并起来,用于代表整个测试程序的运行. 随机采样的片断长度一般是固定值,采样片断之间的距离则是随机的,可以通过反复重新采样后求模拟结果的平均值,使其尽可能的接近整个程序的运行结果. 周期采样是在程序中周期性的选择片断进行模拟运行,用户可以灵活的设置周期长短和间隔大小. 统计采样是基于统计学的方法推测出测试程序的特征,通过测量变化差异使采样片断能够反映出程序的变化,从而确保采样集是代表整个程序的最小采样集. 采用该类技术的模拟器有SimPoint、SMARTS等.采样技术的关键在于程序片段的选取. 随机采样不确定性较大,该方式测试结果与整个程序结果之间存在偏差,反复采样取平均方法可以提升准确度,但验证过程耗时. 周期采样同样难以选择合适的采样频率和片断长度以使取得的采样集是最小集合. 统计采样技术需要通过合适的方法找到最佳采样集. SMARTS 模拟器就是采用基于统计的采样方法,采样片断是周期性采样,长度基本固定但允许有轻微的变化以对齐时钟周期边界. 为保证片断执行时宿主机的cache 以及分支预测器等处于正确的状态,SMARTS 在详细执行片断程序之前先粗略的模拟片断之间的代码以完成Cache 及分支预测器等部件的初始化. 模拟过程分为功能模拟和详细模拟阶段,功能模拟执行间隔代码,这个阶段模拟器忽略许多内部状态的记录,程序快速向前推进,为下一阶段的详细模拟建立正确的部件状态; 详细模拟阶段则精确执行程序片断. FFX + WUY + Run Z 也是一种基于统计的采样方法,FFX( Fast-ForwardX) 是指测试程序运行开始后快速执行X 百万条指令,粗略模拟; WU Y 指详细模拟之后的Y 百万条指令,以便建立起符合详细模拟情况的运行环境,但该阶段的模拟结果并不作为整个模拟结果的参照; 接下来的Z 百万条才是模拟器真正详细执行的程序段. 该方法可极大的减少模拟运行时间,但Z 百万条指令往往不能代表整个程序的执行结果,从而导致模拟误差.4 可用性对于体系结构模拟技术,可用性包括两个方面: 一方面模拟器应能适应各种系统应用场景,如: 单核单任务、单核多任务与多核多任务等; 另一方面,加载到模拟器的测试程序可用度高,支持多个平台和多种编译器,使模拟器能够发挥最大的验证功效.4. 1 用户级虚拟化随着计算机系统处理器核数的迅猛增长,千核系统成为现实,给模拟器技术带来了巨大挑战. 由于千核系统规模庞大,能加载的测试程序类型有限,无法全面的评估千核系统特性,进而影响了千核系统的研究、开发. 为解决该问题,需要新的技术使模拟器能够加载更广泛的测试程序.Daniel 等人使用轻量用户级虚拟化技术( lightweight userlevel virtualization) 构建了ZSim 模拟器,实现千核系统测试程序的灵活加载. 用户级虚拟化技术使用动态二进制翻译给用户进程提供虚拟系统视图来支持多程序并发执行,并支持运行管理及客户-服务器类型负载. 常规的用户级模拟器通常不能模拟此类程序.为实现千核系统的模拟,模拟器利用了宿主机上的多个处理器,突破了传统模拟器仅能在单处理器上运行的局限. 为适应多处理器并行架构,ZSim 每个进程利用共享内存段作为一个全局堆,所有的仿真状态都存储在全局堆中. 通过调整共享堆和库代码段的映射地址,实现跨进程无缝信息传递. 尽管线程来自不同的处理器,ZSim 也可被视为一个简单的多线程应用,并可使用轮换调度算法( round-robin) 来创建任意数量的线程. 为避免模拟器操作系统出现死锁现象,ZSim 舍弃传统模拟器使用的修改测试程序的办法,而是识别出阻塞的系统调用的子集,通过调整内部同步点使得线程加入和退出来避免死锁. 为摆脱程序运行依赖精确的时间,模拟器虚拟化了rdtsc( 读时间戳计数器) 指令、只有少数内核接口、睡眠处理和超时处理调用返回时间信息,使得宿主机与模拟器的时间相互独立. 通过引入上述技术,ZSim 实现了多种类型测试程序的加载运行、如客户端-服务器类程序,并可模拟完整的千核系统.4. 2 优化测试程序优化测试程序是通过精简基准测试程序集,使模拟测试更具有针对性,以提高模拟的效率. 对于基准测试程序集,其初衷是将一些基准测试程序集中化、规范化,以有效评测系统在各种应用场景下的性能. 该程序集可以弥补基准测试程序个体的不足. 但也存在以下几个问题:1) 缺少可信度,基准程序的运行往往与实际程序运行存在差异;2) 每个程序有不同的运行条件,用户为改善测试程序的性能常使用专用标记,但这些标记又容易引起许多程序的不合法转换或降低其他程序的性能;3) 完整程序集的运行时间长. 由于研究侧重点不同,研究者往往采用精简代码的方式来获得更好的系统性能测试结果. 以SPEC xxxx 为例,它是SPEC 中面向处理器的基准测试程序集,为处理器研发人员广泛使用,其包含多组性能测试程序,能测试多处理器计算机系统的整数运算性能和浮点数运算性能. 其中,整数运算基准程序以C 语言开发为主,浮点运算基准程序主要用Fortran 语言开发,用于各种CPU 的性能评价. 为了优化基准测试程序,众多处理器研究者致力于研究如何精简代码使得模拟评估处理器过程更为高效,所做的工作包括减少代码运行、减少输入的数据等.Timothy 等人通过分析测试程序的基础模块分布( Basic Block Distribution) ,试图运行一些程序片断去代替整个程序的运行. 他认为不同的基础模块能唯一标识不同的指令执行阶段,基础模块的周期运行反映了计算机系统各个构件的周期运行,如IPC、分支命中率、缓存命中率、预测值、预测地址、重排序缓存占用等. 由于基本块的频度信息可以使用工具快速收集,因此该方法提供了一种寻找程序模拟点及周期性特征的实用方法. KleinOsowski 等人在xxxx2000 的基础上开发了MinneSPEC 测试程序,该程序精简了模拟输入的参数集,但保留原数据集内部函数的运行权重分布,包括初始化、主要计算功能和复位功能等,极大的降低了模拟运行时间. 但是,MinneSPEC 测试程序所模拟出的结果与原测试指令集有较大差异,取得的优化效果有限. Erez 等人通过选择执行部分程序来代表完整的程序执行,使用统计驱动算法生成模拟点集合,并使用检验算法去选定代码执行初期的模拟点. 该方法的难点在于如何给出一个指标以选择合适的模拟点,该指标基于程序基本块的分布,通过研究它们的块矢量差分布情况来决定运行的代码.5模拟器技术面临的挑战现有的计算机体系结构模拟器在精度、速度、可用性和易用性等方面均存在不同程度的不足. 一直以来,研究人员不断努力改进模拟技术. 如踪迹驱动的较大误差使得执行驱动技术得到重视和发展,基准测试程序的漫长运行时间促使人们对采样技术进行研究,计算机系统规模的日渐庞大推进了并行模拟技术的发展. 随着计算机系统逐步进入千核时代,模拟技术又迎来了新的重大挑战.体系结构模拟器面临的首要挑战是系统建模复杂度急剧增加. 因功耗和散热等因素的限制已不能继续采用提升单一处理器频率的方式提升系统性能,计算机系统多采用多核、多处理器方式构建. 即使每个处理器、核心均在较低的频率、功耗下运行,其系统整体性能依然大幅超越单核处理器系统.Intel 的实验结果表明,单核处理器每提高20% 的时钟频率,仅能提升13%的性能,但增加73% 的功耗; 而当增加第二个核心时,可在降低20% 时钟频率的同时提高73% 的性能. 对于通用CPU,在上个世纪90 年代末, IBM、惠普、SUN 等服务器厂商就相继推出了多核服务器CPU. 2006 年, Intel 推出了双核处理器,接下来陆续推出了面向服务器、工作站和个人电脑的4 核、8 核处理器. 2014 年2 月, Intel 又发布具有15 核心的至强通用处理器,基于该处理器构建的64 路分布式共享内存系统已经接近1000 核心. 对于众核处理器,2007 年Tilera公司发布的嵌入式处理器TILE64 包含了64 个核心,在2010年Supercomputer 会议上Intel 公布了单芯片48 核的云处理器架构,并声称其理论上可达到1000 个核心,而GPU 已经具有数千核心.计算机系统已经步入千核时代,但现有的体系结构模拟器大都不能胜任千核系统模拟,如单线程运行的Gem5、Flexus、MARSS 等模拟器虽然理论上可以模拟千核系统,但其在可用资源、模拟速度等方面均不能满足千核系统的模拟需求. Hypersim 能较好的模拟HPP 高性能计算机体系结构,但只针对集群系统,适用范围有限; ZSim 采用多处理器并行化方法提高了千核系统模拟的速度,相比单线程模拟器取得了显著的进步,但由于采取了较多的精简策略,影响了其模拟精度.体系结构模拟器面临的第二个挑战是模拟速度与精度难以兼顾. 现有的模拟加速技术如采样技术、动态二进制翻译等均是以牺牲模拟精度为代价. 模拟器执行全部的基准测试程序集能够获得完整的系统特征数据,但耗时巨大,执行部分测试程序或者程序的部分代码能加快模拟速度,但影响测试结果的精度,故体系结构模拟需要在精度和速度间权衡. 即使以大幅损失精度为代价,现有模拟器的模拟速度依然无法满足千核系统的模拟需求. 硬件加速方案是一种选择,但软硬件混合模拟器的开发难度大、周期长,因此硬件加速还不能成为主流的模拟器技术.模拟器技术面临的第三个挑战是对异构多核系统支持不足. 一些计算密集型应用如图形处理、气候模拟、分子动力学计算等对系统处理性能要求高,通用处理器系统无法满足其需求,而GPU 拥有超强的浮点处理、矢量计算能力,特别适合大规模、低耦合度并行计算任务. 相比于通用处理器,GPU 在图形处理、气候模拟、分子动力学计算等应用处理上有百倍甚至上千倍的性能提升. 因此采用CPU + GPU 并行模式,占用系统绝大部分性能的密集型计算将由GPU 执行,而少量控制型任务( 如运行操作系统、处理数据交互等) 将由CPU 执行.根据Amdahl 定律,采用GPU 加速密集型计算任务处理措施后,系统可以获得较好的加速比,CPU + GPU 模式在高性能计算中获得了广泛应用. 但是当前,面向CPU + GPU 异构系统的模拟研究极为有限.大多数模拟器虽然集成了多种处理器模型,但在模拟时只能使用单一处理器模型,尚缺乏对异构多核系统并行模拟的支持. LIN 等人构造的异构多核架构模拟器虽然实现了在多个SimpleScalar 进程中运行不同处理器模型,但其系统结构与真实异构系统存在较大差异,不能精确的模拟异构系统.6 研究展望为了更好支持未来计算机系统的研究和设计,体系结构模拟技术需要从4个方面取得更多的创新和突破. 针对归纳4A 理论示意图Fig. 1 4A theory schematic diagram的模拟器 4 个特征,本文提出4A 理论( accuracy,acceleration, availabilityand adaptability ) ,即未来体系结构模拟技术需在精度、速度、可用性、易用性4 个方面均取得重大突破,理想的模拟器将会是这4 类技术发展的交集.基于4A理论,本文认为如下几个研究方向需要重点关注:6. 1 基准测试程序集优化基准测试程序优化是一种提升模拟效率的重要方法. 基准测试程序应能准确、高效的测试目标系统,同时具备一定的灵活性,允许用户对源代码进行修改. 基准测试程序集需要面向多种类型应用,尽可能覆盖各个应用场景.6. 2 模型组件化体系结构性能模拟要求建立精确的时序模型,各部件模型之间需要频繁的通信和同步,成为并行模拟器设计的难点.若将并行模拟器中通信和同步功能分别独立实现,各部件模块内部进行功能模拟,通过调用统一接口模型进行交互,则可使设计者更专注于部件模块的建模与设计,而较少考虑它们之间的通信和同步问题.6. 3 大规模并行模拟当前大规模计算机系统能够提供大容量内存、IO 带宽和强大的计算能力,现有绝大部分模拟器还基于单线程运行,无法充分利用大规模计算机系统提供的资源. 并行化模拟技术尚未成熟,仍然需要深入的研究和探索.6. 4 异构系统模拟异构多处理器架构在解决科学计算、图形处理、加解密等高性能计算问题中已经发挥出巨大的作用,但异构模拟技术研究相对滞后,模拟器支持有限,异构模拟技术是未来体系结构模拟技术重要发展方向之一.6. 5 硬件加速技术FPGA 或者硬件仿真器( emulator,如cadence 公司的Palladium等) 加速技术已经得到普遍应用,利用上述技术可实现单个部件或者全系统的模拟,不仅大大加快了模拟器的速度,而且提高了基准测试程序的执行效率. 但是随着计算机系统规模越来越大,单片FPGA 或单台硬件仿真器无法容纳全系统甚至主要部件逻辑,而采用多片FPGA 或多台硬件仿真器加速方案依然存在诸多协同、交互难题,故硬件加速技术仍需要进一步发展.7 结束语计算机系统已步入千核时代,规模庞大、结构复杂、开发周期长、风险高,迫切需要计算机体系结构模拟技术提供强有力的支撑. 本文首先按照精度、速度、可用性和易用性4 个方面的特征对计算机体系结构模拟技术现状进行了分析和归纳,并总结其不足之处. 随后论述了大规模计算机系统模拟面临的若干挑战,并提出了未来理想模拟器应是精度、速度、可用性及易用性技术发展交集的4A 理论,据此对体系结构模拟技术未来发展进行展望.<!--。

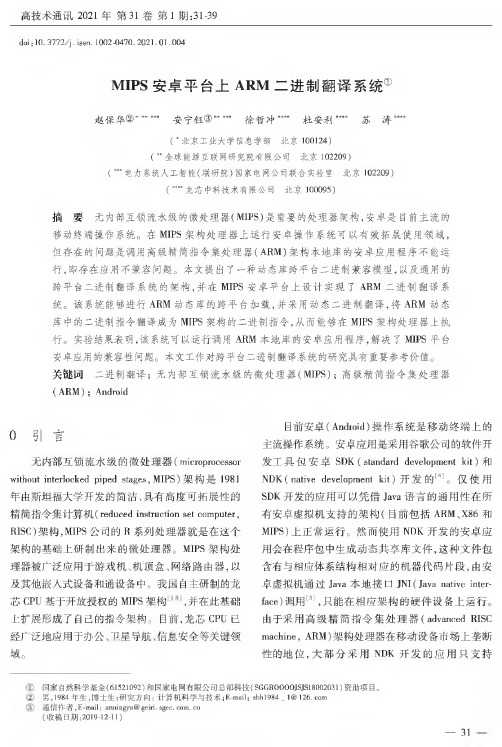

MIPS安卓平台上ARM二进制翻译系统

doi:10.3772/j.issn.1002-0470.2021.01.004MIPS安卓平台上ARM二进制翻译系统①赵保华②……杯安宁饪③*…**徐哲冲**杜安利**苏涛“「北京工业大学信息学部北京100124)("全球能源互联网研究院有限公司北京102209)(”"电力系统人工智能(联研院)国家电网公司联合实验室北京102209)(**“龙芯中科技术有限公司北京100095)摘要无内部互锁流水级的微处理器(MIPS)是重要的处理器架构,安卓是目前主流的移动终端操作系统。

在MIPS架构处理器上运行安卓操作系统可以有效拓展使用领域,但存在的问题是调用高级精简指令集处理器(ARM)架构本地库的安卓应用程序不能运行,即存在应用不兼容问题。

本文提出了一种动态库跨平台二进制兼容模型,以及通用的跨平台二进制翻译系统的架构,并在MIPS安卓平台上设计实现了ARM二进制翻译系统。

该系统能够进行ARM动态库的跨平台加载,并采用动态二进制翻译,将ARM动态库中的二进制指令翻译成为MIPS架构的二进制指令,从而能够在MIPS架构处理器上执行。

实验结果表明,该系统可以运行调用ARM本地库的安卓应用程序,解决了MIPS平台安卓应用的兼容性问题。

本文工作对跨平台二进制翻译系统的研究具有重要参考价值。

关键词二进制翻译;无内部互锁流水级的微处理器(MIPS);高级精简指令集处理器(ARM);Android0引言无内部互锁流水级的微处理器(microprocessor without interlocked piped stages,MIPS)架构是1981年由斯坦福大学开发的简洁、具有高度可拓展性的精简指令集计算机(reduced instruction set computer, RISC)架构,MIPS公司的R系列处理器就是在这个架构的基础上研制岀来的微处理器。

MIPS架构处理器被广泛应用于游戏机、机顶盒、网络路由器,以及其他嵌入式设备和通设备中。

一种动静态结合的代码反汇编技术

中图 分类号: P0 T39

种 动 静 态结 合 的代 码 反 汇编 技 术

宋 威 ,曾勇军 ,奚 琪

(.中 国通 用技术 ( 团) 1 集 控股有限责任公司 ,北京 10 5 ; 0 0 5

2 解放军信息工程大学信息工程学 院,郑州 4 0 0 ) . 502 摘 要: 为在不修改二进制代码的情况下提 高反汇编的准确性和覆盖率 ,提出一种静态分析 与动态仿真相结合 的反汇编技术 。在传统静态

பைடு நூலகம்

令的 目标 ;() 5紧跟在 j 、cl e mp al t等指令后的地址 。上述 、r

样本根 据其特征赋 予不 同的权值 ( 函数序 言权值较高 ,而 如 jp a m 、cl l指令后的地址权值 较低) ,在指令识别过程中可结

动态执行阶段完成 目标 C U指令 的仿真执行 。 P 当被仿真

第3 8卷 第 1 期

V 1 o 38 ..

・

计

算

机

工

程

21 0 2年 1月

J n a y 01 a u r 2 2

NO. 1

Co u e n i e r g mp t r g n e i E n

软件 技术 与数 据库 ・

一

文章编号: 0o-2( 10—06—o 10—3 802 1_ 8_ 文献标识码: 4 2 ) 0 3 A

基于QEMU的动态二进制插桩技术

计算机研究与发展Journal of Computer Research and Development D OI:10. 7544/issnl000-1239. 2019. 2018016656"): 730-7)1,2019基于QEMU的动态二进制插桩技术邹伟高峰颜运强(中国工程物理研究院计算机应用研究所四川绵阳621999)(weighzou@163. com)Dynamic Binary Instrumentation Based on QEMUZou W ei,Gao Feng,and Yan Yunqiang(Institute o f Computer A pplication,China Academy o f Engineering Ph ysics,M ianyang,Sichuan621999)Abstract Software instrumentation is a basic technology of software dynamic analysis,such as program optimization,debugging,testing,fault location and so on.The dynamic binary instrumentation technology,because of its non-invasive,which does not need to modify the source code to compile,and does no t need t o reassemble t h e binary program,will not cause the expansion of the object code,and is widely used in software dynamic analysis,especially in resource constrained,low power consumption,high real-time embedded field,so dynamic binary instrumentation is the very key technology.However,the e xisting binary instrumentation tool can only be applied to user mode software,and the embedded whole system software also needs a corresponding bin tool.In order to solve this problem,this paper based on the dynamic b in instruction set simulator QEMU(quick emulator),breaks through run time statistics collection on the basic blocks,and eliminates interrupt^s adverse effects of control flow analysis in the embedded the system software,and achieves the implementation of instrumentation on the intermediate code level to the embedded system software code,full completion of the embedded system software running control flow tracking,and the development of log information processing tool.Experiments show that the me t h od proposed in this paper can accomplish call graph,function profile,cov analysis and so on,which can solve the problem of dynamic binary analysis of embedded system software. Key words dynamic analysis%dynamic binary instrumentation%QEMU%binary code%software testing摘要软件插桩是程序优化、软件调试、软件测试、故障定位等软件动态分析的基础技术.而其中,动态 二进制插桩技术,因其无侵入性,即既不需要对源代码进行修改编译,又不需要重新组装二进制程序,不会引起目标码膨胀,而广泛应用于软件动态分析,特别是在资源受限、功耗低、实时性高的嵌入式软件领 域,动态二进制插桩技术十分关键.然而,现有的二进制插桩工具仅能应用于用户态软件分析,在嵌入式 全系统软件领域,还没有相应的二进制插桩工具.针对上述问题,在基于动态二进制翻译的开源指令集仿真器QEMU(quick emulator)基础上,研究突破基本块运行时间统计收集,并消除中断对嵌入式系统 软件控制流分析的不良影响,实现了在中间码上对嵌入式全系统软件的动态二进制插桩,完成嵌入式全 系统软件运行控制流跟踪,并开发日志处理工具.实验表明,该方法能完成目标码的调用图、函数剖面、覆盖率、控制流等分析,可以解决了嵌入式全系统软件动态二进制分析问题.收稿日期!018—03—13 ;修回日期:2018—08—27基金项目:国防基础科研计划重点项目(JCKY2016212B004)This work was supported by the National Defense Basic Scientific Research Project of China (JCKY2016212B004).邹伟等:基于Q E M U的动态二进制插桩技术 731关键词动态分析;动态二进制插桩;Q EM U;二进制目标码;软件测试中图法分类号TP391近年来,嵌人式软件的规模与复杂度愈发增加,如何进一步通过软件测试、分析与验证提高其可靠性,一直是学术界关注的焦点.其中,软件插桩是一 项十分重要的应用于该领域的动态分析技术.通过软件插桩技术'.可有效收集程序执行过程信息,如 路径覆盖信息、函数调用关系信息,能用于软件性能 分析、程序优化、测试覆盖分析、测试用例生成与约 简、软件缺陷检测与修复.当前,软件插桩技术包含源代码级[3]和二进制 级[42] 2种插桩方式,其中二进制插桩技术又分为动 态方式和静态方式.研究表明7:源代码级插桩技术 对软件具有很强的侵人性,无法应用于逆向工程或软件测试;在二进制插桩技术方面,静态二进制插桩 技术,由于其较强的侵人性和代码数据难以区分等 难题,在实际工程中极少使用;和静态二进制插桩不 同的是,动态二进制插桩[1—2,] (dynamic binary instrumentation)技术通过接管目标程序控制流,为 目标程序提供虚拟运行环境,进而监视收集目标程序运行信息.因而,动态二进制插桩技术既不需要重 新编译生成目标码,又不会改变目标码的执行流程,完全不影响原程序执行逻辑,具有很好的实用性.目 前,动态二进制插桩工具主要包含Pin'-9],Valgrind'1。

二进制数字调制的MATLAB仿真

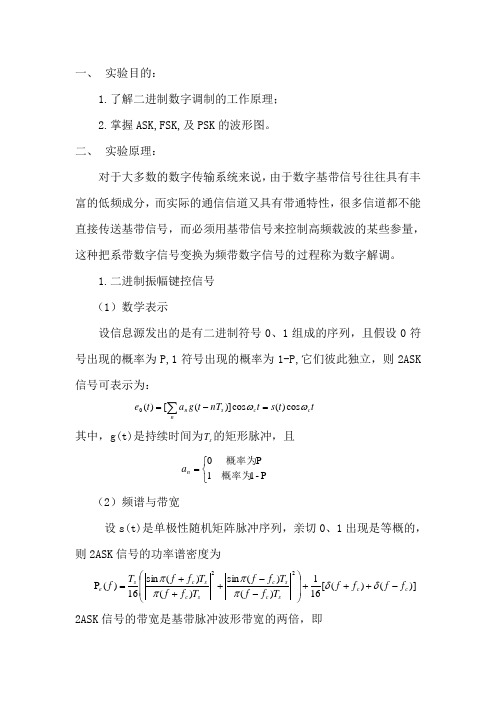

一、 实验目的:1.了解二进制数字调制的工作原理;2.掌握ASK,FSK,及PSK 的波形图。

二、 实验原理:对于大多数的数字传输系统来说,由于数字基带信号往往具有丰富的低频成分,而实际的通信信道又具有带通特性,很多信道都不能直接传送基带信号,而必须用基带信号来控制高频载波的某些参量,这种把系带数字信号变换为频带数字信号的过程称为数字解调。

1.二进制振幅键控信号 (1)数学表示设信息源发出的是有二进制符号0、1组成的序列,且假设0符号出现的概率为P,1符号出现的概率为1-P,它们彼此独立,则2ASK 信号可表示为:t t s t nT t g a t e c c ns n ωωcos )(cos )]([)(0=-=∑其中,g(t)是持续时间为s T 的矩形脉冲,且 ⎩⎨⎧=P-11P 0概率为概率为n a(2)频谱与带宽设s(t)是单极性随机矩阵脉冲序列,亲切0、1出现是等概的,则2ASK 信号的功率谱密度为)]()([161)()(sin )()(sin 16)(P 22cc sc sc sc sc s e f f f f T f f T f f T f f T f f T f -+++⎪⎪⎭⎫⎝⎛--+++=δδππππ2ASK 信号的带宽是基带脉冲波形带宽的两倍,即s f 2B ASK 2=2.二进制移频键控信号 (1)数学表示设信息源发出的是有二进制符号0、1组成的序列,且假定0符号对应于载频w1,1符号对应于载频w2,则2FSK 信号可表示为:)cos()]()cos()]()(210n ns n n ns n t nT t g a t nT t g a t e ϕωϕω+-++-=∑∑其中,g(t)是单个矩形脉冲,脉宽为s T 且⎩⎨⎧=P -11P概率为概率为n a ⎩⎨⎧-=P1P 10概率为概率为n a(2)频谱与带宽])()()()([161])()(sin )()(sin )()(sin )()(sin [16)(P 2211222222211211E f f f f f f f f T f f T f f T f f T f f T f f T f f T f f T f f T f sssssssss -+++-+++--++++--+++=δδδδππππππππ传输2FSK 信号所需频带约为s f f f 2B 12FSK2+-=3.二进制相移键控 (1)数学表示设信息源发出的是有二进制符号0、1组成的序列,其信号一般形式可表示为:t nT t g a t e c ns n ωcos )]([)(0∑-=这里,g(t)是单个矩形脉冲,脉宽为s T 且⎩⎨⎧-+=P-11P 1概率为概率为n a(2)频谱与带宽设s(t)是双极性矩形基带信号,且0、1等概出现,则2PSK 信号的功率谱密度为⎪⎪⎭⎫ ⎝⎛--+++=22)()(sin )()(sin 4)(P sc sc sc sc s e T f f T f f T f f T f f T f ππππ 2PSK 信号的带宽为s f 2B PSK 2=三、 实验程序: A=1; fc=2; N_sample=20; N=500; Ts=1;dt=Ts/fc/N_sample; t=0:dt:N*Ts-dt; Lt=length(t); d=sign(randn(1,N));dd=sigexpand((d+1)/2,fc*N_sample); gt=ones(1,fc*N_sample); figure(1) subplot(2,2,1); d_NRZ=conv(dd,gt);plot(t,d_NRZ(1:length(t))); axis([0,10,0,1.2]);xlabel('(a)输入信号');subplot(2,2,2);[f,d_NRZf]=T2F(t,d_NRZ(1:length(t))); plot(f,10*log10(abs(d_NRZf).^2/Ts)); axis([-2,2,-50,10]);xlabel('(b)输入信号功率谱密度(dB/HZ)'); ht=A*cos(2*pi*fc*t);s_2ask=d_NRZ(1:Lt).*ht;subplot(2,2,3);plot(t,s_2ask);axis([0,10,-1.2,1.2]);xlabel('(c)2ask');[f,s_2askf]=T2F(t,s_2ask);subplot(2,2,4);plot(f,10*log10(abs(s_2askf).^2/Ts)); xlabel('(d)2ask功率谱密度(dB/HZ)'); figure(2)d_2psk=2*d_NRZ-1;s_2psk=d_2psk(1:Lt).*ht;subplot(2,2,1);plot(t,s_2psk);axis([0,10,-1.2,1.2]);xlabel('(e)2psk');subplot(2,2,2);[f,s_2psk]=T2F(t,s_2psk);plot(f,10*log10(abs(s_2psk).^2/Ts));axis([-fc-4,fc+4,-50,10]);xlabel('(f)2psk功率谱密度(dB/HZ)');sd_2fsk=2*d_NRZ-1;s_2fsk=A*cos(2*pi*fc*t+2*pi*sd_2fsk(1:length(t)).*t); subplot(2,2,3);plot(t,s_2fsk);axis([0,10,-1.2,1.2]);xlabel('(g)2fsk');subplot(2,2,4);[f,s_2fskf]=T2F(t,s_2fsk);plot(f,10*log10(abs(s_2fskf).^2/Ts));axis([-fc-4,fc+4,-50,10]);xlabel('(h)2fsk功率谱密度(dB/HZ)');子函数:①F2T.mfunction [t,st]=F2T(f,sf)%反傅立叶变换df=f(2)-f(1);Fmx=(f(end)-f(1)+df);df=1/Fmx;N=length(sf);T=dt*N;t=0:dt:T-dt;sff=fftshift(sf);st=Fmx*ifft(sff)②T2F.mfunction[f,sf]=T2F(t,st)dt=t(2)-t(1);T=t(end);df=1/T;N=length(st);f=-N/2*df:df:N/2*df-df;sf=fft(st);sf=T/N*fftshift(sf);③ sigexpand.mfunction[out]=sigexpand(d,M)%将输入的序列扩展成间隔N—1个0 N=length(d);out=zeros(M,N);out(1,:)=d;out=reshape(out,1,M*N);四、实验结果及分析:。

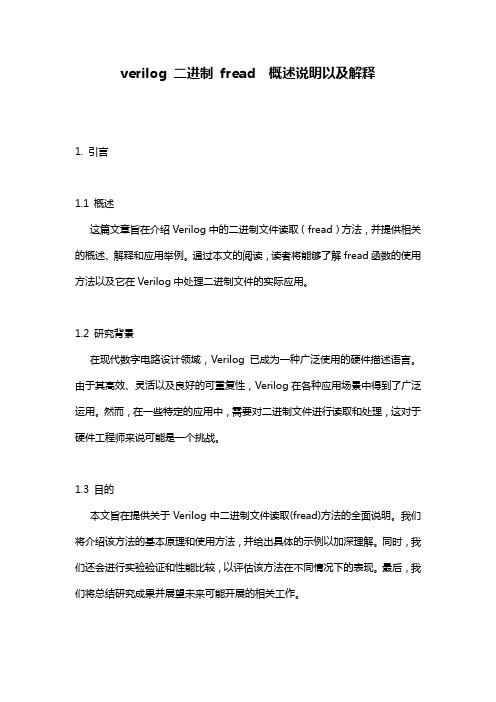

verilog_二进制_fread__概述说明以及解释

verilog 二进制fread 概述说明以及解释1. 引言1.1 概述这篇文章旨在介绍Verilog中的二进制文件读取(fread)方法,并提供相关的概述、解释和应用举例。

通过本文的阅读,读者将能够了解fread函数的使用方法以及它在Verilog中处理二进制文件的实际应用。

1.2 研究背景在现代数字电路设计领域,Verilog已成为一种广泛使用的硬件描述语言。

由于其高效、灵活以及良好的可重复性,Verilog在各种应用场景中得到了广泛运用。

然而,在一些特定的应用中,需要对二进制文件进行读取和处理,这对于硬件工程师来说可能是一个挑战。

1.3 目的本文旨在提供关于Verilog中二进制文件读取(fread)方法的全面说明。

我们将介绍该方法的基本原理和使用方法,并给出具体的示例以加深理解。

同时,我们还会进行实验验证和性能比较,以评估该方法在不同情况下的表现。

最后,我们将总结研究成果并展望未来可能开展的相关工作。

以上是“引言”部分内容。

请您根据需要进行修改和完善。

2. Verilog 二进制文件读取(fread)2.1 Verilog简介Verilog是一种硬件描述语言,用于描述和设计数字电路和系统。

它是一种建模语言,允许设计者通过声明性的方式来描述他们想要实现的功能和行为。

2.2 二进制文件读取概述在Verilog中,二进制文件读取是指从磁盘或其他存储设备中加载二进制数据到Verilog代码中的过程。

这些数据可以包含不同类型的信息,例如图像、音频、视频以及其他任何需要处理的数据。

在进行二进制文件读取之前,需要使用fopen函数来打开一个文件,并将其与一个逻辑文件变量关联起来。

逻辑文件变量用于表示已打开的文件,并作为后续操作的参数。

2.3 fread函数详解fread函数是Verilog中用于从逻辑文件变量中读取二进制数据的函数。

它接受以下参数:- 数据目标:指定将数据读入哪个变量。

- 数据类型:指定要读取的数据类型,如整数、浮点数等。

iverilog和modelsim语法

iverilog和modelsim是两种常用的硬件描述语言(HDL)仿真工具。

iverilog是一种基于C语言编写的开源的仿真器,可以将Verilog语言翻译成仿真运行的二进制文件。

modelsim是由美国Mentor Graphics公司开发的一款基于Verilog和VHDL语言的仿真工具,具有较强的仿真能力和支持。

iverilog和modelsim语法有相似之处,但也存在一些不同,下面分别对两者的语法特点进行介绍:1.iverilog语法特点:iverilog的语法规范符合IEEE-1364标准,支持Verilog-1995、Verilog-2001和Verilog-2005三种语言标准。

iverilog语法主要包括模块定义、数据类型、运算符、控制语句等内容:(1) 模块定义:iverilog中的模块定义使用module关键字,语法结构类似于C语言中的函数定义。

例如:```module adder (input a, input b, output sum);assign sum = a + b;endmodule```(2) 数据类型:iverilog支持多种数据类型,包括bit、byte、int、reg 等,可以根据需要进行声明和使用。

(3) 运算符:iverilog支持包括算术运算符、逻辑运算符、位运算符等多种运算符,可以满足不同的运算需求。

(4) 控制语句:iverilog支持if-else、for、while等多种控制语句,可以实现复杂的逻辑控制。

2.modelsim语法特点:modelsim作为一款业界知名的仿真工具,其语法规范符合IEEE-1076标准,主要支持VHDL语言。

其语法特点包括实体声明、信号赋值、过程语句等内容:(1) 实体声明:modelsim中的实体声明使用entity关键字,语法结构包括端口声明和内部信号声明。

例如:```entity adder isport (a, b: in std_logic;sum: out std_logic);end entity;```(2) 信号赋值:modelsim支持对信号进行赋值操作,包括变量赋值、信号延迟赋值等操作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

中 分 号 P15 圈 类 t 3 ・ T 14

基 于动 态二进制翻译技 术 的仿 真 器研 究

陈 乔 ,蒋烈辉 ,董卫宇 ,徐金龙 ,方 明

( 军信 息工程大学信息工程学院 ,郑州 400) 解放 502 摘 要 :以动态 二进 制仿真器 Q MU 为平台 ,分析 动态二进制翻译技术在仿真器开 发中的应 用 ,研究 Q MU 的翻译机制 、优化策 略、关 E E

DOI 1.9 9 .s.0 03 2 .0 2 .9 : 03 6 0i n10 —4 82 1.00 4 s 1

1 概述

计算 机发 展 的历程 是软硬 件相 互矛 盾、相 互统 一 的过

进制翻译模 块 ,从而明显地提 高了仿真速度 。

3 动态二进剖翻译器 Q MU E

Q MU是一套多源多 目的开源跨平台翻译器 。Q MU有 E E 2种主要运行模 式 :进 程模式和系统模式 J 系统模式中 。在 Q MU 能仿真整 个硬件 系统 ,包 括中央处 理器 及其他 周边 E

[ sr c]Us gte y a cbn r asao MU s sac lt r ,hs a e nlz s e y a c iayt n lintcn lg sd Abta t i n mi iayt nltr n hd r QE a r erhpa o tipp r a e nmi n r asa o h ooyu e ae fm a y t d h b r t e

和关键技术 。

31 Q MU 系统 的基 本结构 . E 系统 由控制核 心、解释器、翻译器和翻译缓存等组成 。 控制器负责整个翻译过程 的调度 ,解释器负责完成指令 的匹 配工作 ,翻译器主要完成源二进制指令流到 中间指令和 中间 指令到 目标二进制指令流 的转换 ,最后翻译缓存负责存放翻 译后 的基本块 。在运行 时,控制核心会维护一个软件 的 目标 机虚拟 C U状态 , P 称为 e v n ,它包括通 用寄 存器 、段寄存器 、 标志位寄存器等。 目标机 的所有资源都通过 e v基址加上特 n

i edv lp n ftesmuao, tde nd ti Q MU t et sao c ai o t zt n s aey ad ky t h oo isad nt eeo meto i l r s isi eal E h h t u wi t a lt nmeh s hh r n i n m, pi ai t tg , e e n lge n mi o r n c

CHE a , I G i- u , N Qio J AN L eh iDON W e・ u XU J n ln , AN M i g G i , i — g F G n y o

( o lg f no ma o n i e r g P A f r t nE gn e n ie s y Z e g h u4 0 0 , h n ) C l e fr t nE g n e n , L I omai n ie r gUnv ri , h n z o 5 0 2 C i a e oI i i n o i t

键技术 ,并对相 关重 要代码 进行解析 。对仿真 C U的性能进行测试 ,结合分 阶段 的测 试结果 ,从中找出制约仿真 C U性 能的关键 阶段 , P P 为后续 的优化工作提供 参考依据。 关健词 :动态 二进制翻 译 ;软件移植 ;中间指令 ;精确 异常 ;自 改代码 修

Sm ua o s a c sd0 i l t rRe e r h Ba e n Dy a i n r r n l to e h o o y n m cBi a y T a sa i n T c n ayt nlt n sf r gain itr e i en t cin; rcs x et n slmo ie o e Ke r s y a cbn r a s i ;ot e rt ;ne da s ut spei ecpi ;ef df dc d r ao wa mi o m ti r o e o - i

设备 。

程。传统的计算机软件和硬件都依赖于特 定的体系结构 ,不 同的指令集体系结构 的软件和硬件不 能相 互结合 ,降低 了计 算机系统 的互操作性 。动态二进制翻译技术解 决了软件移植

问题 ,不仅对软件重 用有重大意义 ,而且 还可以开阔处理器

研发 的思路 ,促进新 的处理器 的创新 。本文以动态二进制仿 真器 Q MU 为平 台,研究 了 Q MU 的翻译机制、优化策略 E E

n lz si a ay e mpo t n e a e od .Si ra trltd c e multo e t e p ro a c f CPU,a d c mb n n h s s t s e u t ,fn s t e r src i n o e CP a i n t ss t e f r n e o h m n o i i g p a e e t r s ls i d e ti t f t U h o h p ro a c i l to e t g s i p o i e e e e c o p i z t n. e r n e smu ai n k y s e , t r v d sr f r n ef ro t f m a mi a i o

第3 7卷 第 2 0期

、0 -7 ,l3

・

计

算

机

工

程

21 0 1年 1 0月

Oc o e 2 t b r 01 1

No.O 2

Co mpu e t rEng n e i g i e rn

开发研究与设计技术 ・

文章 : o 一 4 ( 12_ 2 _ 3 文 标 码: 编号 1 3 8 o ) _ 7 _ 0 22 1 0 7 0 献 识 A