AK4366VTP中文资料

AK4367VN资料

元器件交易网ASAHI KASEI[AK4367]AK4367Low Power 24-Bit 2ch DAC with HP-AMP & Output MixerGENERAL DESCRIPTION The AK4367 is 24bit DAC with built-in Headphone Amplifier. The AK4367 features an analog mixing circuit that allows easy interfacing in mobile phone and portable communication designs. The integrated headphone amplifier features “pop-free” power-on/off, a mute control and delivers 50mW of power at 16Ω. The AK4367 is housed in a 20pin QFN package, making it suitable for portable applications. FEATURE Multi-bit ∆Σ DAC Sampling Rate: 8kHz∼48kHz 64x Oversampling On chip perfect filtering 8 times FIR interpolator - Passband: 20kHz - Passband Ripple: ±0.02dB - Stopband Attenuation: 54dB Digital De-emphasis Filter: 32kHz, 44.1kHz and 48kHz System Clock: 256fs/384fs/512fs - AC Couple Input Available Audio I/F Format: MSB First, 2’s Compliment - I2S, 24bit MSB justified, 24bit/20bit/16bit LSB justified Digital ATT Analog Mixing Circuit Mono Lineout µP Interface: 3-wire/I2C Bass Boost Function Headphone Amplifier - Output Power: 50mW x 2ch @16Ω, 3.3V - S/N: 92dB@2.4V - Pop Noise Free at Power-ON/OFF and Mute Power Supply: 2.2V ∼ 3.6V Power Supply Current: 2.8mA@2.4V (@HP-AMP no-output) Ta: −40 ∼ 85°C Small Package: 20pin QFNMS0247-E-02 -1-2005/10元器件交易网ASAHI KASEI[AK4367]MCLKLINMINVDDBICK LRCK SDATAAudio InterfaceClock Divider VCOM HDP AmpVCOMDAC(Lch)MUTEHPLATT & Bass BoostDEM & Digital Filter DAC(Rch)MOUTHDP AmpMUTEHPRPDN I2C CAD0/CSN SCL/CCLK SDA/CDTI RIN VSS Serial I/F HVDD MUTETFigure 1. AK4367 Block DiagramMS0247-E-02 -2-2005/10元器件交易网ASAHI KASEI[AK4367]Ordering GuideAK4367VN AKD4367 −40 ∼ +85°C 20pin QFN (0.5mm pitch) Evaluation board for AK4367Pin LayoutMUTET 12HPR HPL MIN RIN LIN11151413VCOMHVDDVDDVSS16 17 18 19 20 1 2 3 4 510MOUT I2C PDN MCLK BICKAK4367Top View9 8 7 6CAD0/CSNSCL/CCLKSDA/CDTISDATAMS0247-E-02 -3-LRCK2005/10元器件交易网ASAHI KASEI[AK4367]PIN/FUNCTIONNo. 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 Pin Name SDA CDTI SCL CCLK CAD0 CSN SDATA LRCK BICK MCLK PDN I2C MOUT VCOM MUTET VDD VSS HVDD HPR HPL MIN RIN LIN I/O I/O I I I I I I I I I I I O O O O O I I I Function Control Data Input/Output Pin (I2C pin = “H”) Control Data Input Pin (I2C pin = “L”) Control Data Clock Pin (I2C pin = “H”) Control Data Clock Pin (I2C pin = “L”) Chip Address 0 Select Pin (I2C pin = “H”) Control Data Chip Select Pin (I2C pin = “L”) Audio Serial Data Input Pin L/R Clock Pin This clock determines which audio channel is currently being input on SDATA pin. Serial Bit Clock Pin This clock is used to latch audio data. Master Clock Input Pin Power-down & Reset Pin When at “L”, the AK4367 is in power-down mode and is held in reset. The AK4367 should always be reset upon power-up. Control Mode Select Pin (Internal Pull-down Pin) “H”: I2C Bus, “L”: 3-wire Serial Mono Analog Output Pin Common Voltage Output Pin Normally connected to VSS pin with 0.1µF ceramic capacitor in parallel with a 2.2µF electrolytic capacitor. Mute Time Constant Control Pin Connected to VSS pin with a capacitor for mute time constant. Power Supply Pin Ground Pin Power Supply Pin for Headphone Amp Rch Headphone Amp Output Pin Lch Headphone Amp Output Pin Mono Analog Input Pin Rch Analog Input Pin Lch Analog Input PinNote: All digital input pins except analog input pins (MIN, RIN and LIN) and internal pull-down pin must not be left floating.Handling of Unused PinThe unused I/O pins should be processed appropriately as below. Classification Analog Digital Pin Name MOUT, MUTET, HPR, HPL, MIN, RIN, LIN CAD0 Setting These pins should be open. These pins should be connected to VSS.MS0247-E-02 -4-2005/10元器件交易网ASAHI KASEI[AK4367]ABSOLUATE MAXIMUM RATING (VSS=0V; Note 1) Parameter Symbol min Power Supplies Analog, Digital VDD −0.3 HP-AMP HVDD −0.3 Input Current (any pins except for supplies) IIN Input Voltage VIN −0.3 Ambient Temperature Ta −40 Storage Temperature Tstg −65 Note 1. All voltages with respect to ground.max 4.6 4.6 ±10 VDD+0.3 or 4.6 85 150Units V V mA V °C °CWARNING: Operation at or beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.RECOMMEND OPERATING CONDITIONS (VSS=0V; Note 1) Parameter Symbol min typ Power Supplies Analog, Digital VDD 2.2 2.4 (Note 2) HP-AMP HVDD 2.2 2.4 Note 1. All voltages with respect to ground. Note 2. VDD should be same voltage as HVDD.* AKM assumes no responsibility for usage beyond the conditions in this datasheet.max 3.6 3.6Units V VMS0247-E-02 -5-2005/10元器件交易网ASAHI KASEI[AK4367]ANALOG CHARACTERISTICS (Ta=25°C; VDD=HVDD=2.4V, VSS=0V; fs=44.1kHz; BOOST OFF; Signal Frequency =1kHz; Measurement band width=10Hz ∼ 20kHz; Headphone-Amp: Load impedance is a serial connection with RL =16Ω and CL=220µF. (Refer to Figure 33); Mono output: RL =16Ω; unless otherwise specified) Parameter min typ max Units 24 bit DAC Resolution Headphone-Amp: (HPL/HPR pins) (Note 3) Analog Output Characteristics THD+N dB −4.8dBFS Output, Po=10mW@16Ω, 2.4V −55 −45 dB −3dBFS Output, Po=28mW@16Ω, 3.3V −55 dB −3dBFS Output, Po=14mW@32Ω, 3.3V −57 D-Range −60dBFS Output, A-weighted, 2.4V 84 92 dB 94 dB −60dBFS Output, A-weighted, 3.3V S/N A-weighted, 2.4V 84 92 dB A-weighted, 3.3V 94 dB Interchannel Isolation 60 80 dB DC Accuracy Interchannel Gain Mismatch 0.2 dB Gain Drift 200 ppm/°C Load Resistance (Note 4) 16 Ω Load Capacitance 300 Output Voltage (Note 5) 1.02 1.13 1.24 Vpp (−4.8dBFS Output) Max Output Power 26 mW RL=16Ω, 2.4V 50 mW RL=16Ω, 3.3V Mono Output: (MOUT pin) (Note 6) Analog Output Characteristics: THD+N (0dBFS Output) dB −60 −50 S/N (A-weighted) 84 92 dB DC Accuracy Gain Drift 200 ppm/°C Load Resistance (Note 4) 10 kΩ Load Capacitance 25 pF Output Voltage (Note 7) 1.42 1.58 1.74 Vpp Output Volume: (MOUT pin) Step Size 1 2 3 dB Gain Control Range 0 dB −30 Note 3. DACL=DACR bits = “1”, MINL=MINR=LINL=RINR bits = “0”, ATTL=ATTR=0dB. Note 4. AC Load Note 5. Output voltage is proportional to VDD voltage. Vout = 0.47 x VDD(typ)@−4.8dBFS. Note 6. DACM bit = “1”, DACL=DACR bits = “0”, LINM=RINM=MINM bits = “0”, ATTL=ATTR=ATTM=0dB, and common mode signal is input to L/Rch of DAC. Note 7. Output voltage is proportional to VDD voltage. Vout = 0.66 x VDD(typ).MS0247-E-02 -6-2005/10元器件交易网ASAHI KASEI[AK4367]Parameter min typ max LINEIN: (LIN/RIN/MIN pins) Analog Input Characteristics Input Resistance (See Figure 31 and Figure 32.) LIN pin LINL bit = “1”, LINM bit = “1” 23 33 LINL bit = “1”, LINM bit = “0” 40 LINL bit = “0”, LINM bit = “1” 200 RIN pin RINR bit = “1”, RINM bit = “1” 23 33 RINR bit = “1”, RINM bit = “0” 40 RINR bit = “0”, RINM bit = “1” 200 MIN pin MINL bit = “1”, MINR bit = “1”, MINM bit = “1” 11 17 MINL bit = “1”, MINR bit = “0”, MINM bit = “0” 40 MINL bit = “0”, MINR bit = “1”, MINM bit = “0” 40 MINL bit = “0”, MINR bit = “0”, MINM bit = “1” 100 Gain LIN/RIN→MOUT −7 −6 −5 0 +1 MIN→MOUT −1 +0.8 +1.8 +2.8 LIN/MIN→HPL, RIN/MIN→HPR Power Supplies Power Supply Current Normal Operation (PDN pin = “H”) (Note 8) VDD 1.8 3.0 HVDD 1.0 2.0 Power-Down Mode (PDN pin = “L”) (Note 9) 1 100 Note 8. PMDAC=PMHPL=PMHPR=PMMO bits = “1”, MUTEN bit = “1” and HP-Amp output is off. Note 9. All digital input pins including clock pins (MCLK, BICK and LRCK) are held at VSS.UnitskΩ kΩ kΩ kΩ kΩ kΩ kΩ kΩ kΩ kΩ dB dB dBmA mA µAMS0247-E-02 -7-2005/10元器件交易网ASAHI KASEI[AK4367]FILTER CHARACTERISTICS (Ta=25°C; VDD, HVDD=2.2 ∼ 3.6V; fs=44.1kHz; De-emphasis = “OFF”) Parameter Symbol min typ max Units DAC Digital Filter: (Note 10) Passband PB 0 20.0 kHz −0.05dB (Note 11) 22.05 kHz −6.0dB Stopband (Note 11) SB 24.1 kHz Passband Ripple PR dB ±0.02 Stopband Attenuation SA 54 dB Group Delay (Note 12) GD 20.8 1/fs Group Delay Distortion 0 µs ∆GD DAC Digital Filter + Analog Filter: (Note 10) (Note 13) Frequency Response FR dB 0 ∼ 20.0kHz ±0.5 Analog Filter: (Note 14) Frequency Response FR dB 0 ∼ 20.0kHz ±1.0 BOOST Filter: (Note 13) (Note 15) Frequency Response 20Hz FR dB 5.76 MIN 100Hz dB 2.92 1kHz dB 0.02 20Hz FR dB 10.80 MID 100Hz dB 6.84 1kHz dB 0.13 20Hz FR dB 16.06 MAX 100Hz dB 10.54 1kHz dB 0.37 Note 10. BOOST OFF (BST1-0 bit = “00”) Note 11. The passband and stopband frequencies scale with fs. For example, PB=0.4535*fs(@±0.05dB), SB=0.546*fs(@−54dB). Note 12. This is the calculated delay time caused by digital filtering. This time is measured from the setting of the 24bit data of both channels to the input registers to the output of the analog signal. Note 13. DAC HPL, HPR, MOUT Note 14. MIN HPL/HPR/MOUT, LIN HPL/MOUT, RIN HPR/MOUT Note 15. These frequency responses scale with fs. If high-level signal is input, the AK4367 clips at low frequency.Boost Filter (fs=44.1kHz) 20 15 Level [dB] MID 10 MIN 5 0 -5 10 100 Frequency [Hz] 1000 10000MAXFigure 2. Boost Frequency (fs=44.1kHz)MS0247-E-02 -8-2005/10元器件交易网ASAHI KASEI[AK4367]DC CHARACTERISTICS (Ta=25°C; VDD, HVDD=2.2 ∼ 3.6V) Parameter Symbol min High-Level Input Voltage VIH 70%DVDD Low-Level Input Voltage VIL Input Voltage at AC Coupling (Note 16) VAC 1.0 Low-Level Output Voltage (Iout = 3mA) VOL Input Leakage Current (Note 17) Iin Note 16. Only MCLK pin. (Figure 33) Note 17. I2C pin has internal pull-down device, nominally 100kΩ.typ -max 30%DVDD 0.4 ±10Units V V Vpp V µASWITCHING CHARACTERISTICS (Ta=25°C; VDD, HVDD=2.2 ∼ 3.6V; CL = 20pF) Parameter Symbol min typ max Units Master Clock Timing Frequency fCLK 2.048 24.576 MHz Pulse Width Low (Note 18) tCLKL 0.4/fCLK ns Pulse Width High (Note 18) tCLKH 0.4/fCLK ns AC Pulse Width (Note 21) tACW 20 ns LRCK Timing Frequency fs 8 44.1 48 kHz Duty Cycle: Duty 45 55 % Serial Interface Timing (Note 19) BICK Period tBCK 1/(64fs) ns BICK Pulse Width Low tBCKL 130 ns Pulse Width High tBCKH 130 ns (Note 20) tLRB 50 ns LRCK Edge to BICK “↑” (Note 20) tBLR 50 ns BICK “↑” to LRCK Edge SDATA Hold Time tSDH 50 ns SDATA Setup Time tSDS 50 ns Control Interface Timing (3-wire Serial mode) CCLK Period tCCK 200 ns CCLK Pulse Width Low tCCKL 80 ns Pulse Width High tCCKH 80 ns CDTI Setup Time tCDS 40 ns CDTI Hold Time tCDH 40 ns CSN “H” Time tCSW 150 ns tCSS 50 ns CSN “↑” to CCLK “↑” tCSH 50 ns CCLK “↑” to CSN “↑” Note 18. Except AC coupling. Note 19. Refer to “Serial Data Interface”. Note 20. BICK rising edge must not occur at the same time as LRCK edge. Note 21. Pulse width to ground level when MCLK is connected to a capacitor in series and a resistor is connected to ground. (Refer to Figure 3.)MS0247-E-02 -9-2005/10元器件交易网ASAHI KASEI[AK4367]Parameter Control Interface Timing (I2C Bus mode): (Note 22) SCL Clock Frequency Bus Free Time Between Transmissions Start Condition Hold Time (prior to first clock pulse) Clock Low Time Clock High Time Setup Time for Repeated Start Condition SDA Hold Time from SCL Falling (Note 23) SDA Setup Time from SCL Rising Rise Time of Both SDA and SCL Lines Fall Time of Both SDA and SCL Lines Setup Time for Stop Condition Pulse Width of Spike Noise Suppressed by Input Filter Power-down & Reset Timing PDN Pulse Width (Note 24)Symbol fSCL tBUF tHD:STA tLOW tHIGH tSU:STA tHD:DAT tSU:DAT tR tF tSU:STO tSP tPDmin 4.7 4.0 4.7 4.0 4.7 0.25 4.0 0 150typ -max 100 1.0 0.3 50 -Units kHz µs µs µs µs µs µs µs µs µs µs ns nsNote 22. I2C is a registered trademark of Philips Semiconductors. Note 23. Data must be held long enough to bridge the 300ns-transition time of SCL. Note 24. The AK4367 can be reset by bringing PDN pin = “L” to “H” only upon power up.Purchase of Asahi Kasei Microsystems Co., Ltd I2C components conveys a license under the Philips I2C patent to use the components in the I2C system, provided the system conform to the I2C specifications defined by Philips.MS0247-E-02 - 10 -2005/10ASAHI KASEI [AK4367]Timing DiagramMCLK Input Measurement PointVSS1000pFFigure 3. MCLK AC Coupling TimingVIHMCLKVILVIH LRCKVILVIH BICKVILFigure 4. Clock TimingLRCKVIH BICKVILVIH SDATAVIL VIH VILFigure 5. Serial Interface TimingASAHI KASEI [AK4367]CSNVIH CCLKVILVIH CDTI VILVIHVILFigure 6. WRITE Command Input TimingCSNVIH CCLKVILVIH CDTI VILVIHVILD3D2D1D0Figure 7. WRITE Data Input TimingVIHVILVIHVILFigure 8. I 2C Bus Mode TimingVILPDNFigure 9. Power-down & Reset TimingASAHI KASEI [AK4367]OPERATION OVERVIEWSystem ClockThe external clocks required to operate the AK4367 are MCLK(256fs/384fs/512fs), LRCK(fs) and BICK. The master clock (MCLK) should be synchronized with sampling clock (LRCK). The phase between these clocks does not matter. The frequency of MCLK is detected automatically, and the internal master clock becomes the appropriate frequency. Table 1 shows system clock example.LRCK MCLK (MHz) BICK (MHz) fs 256fs 384fs 512fs 64fs 8kHz 2.048 3.072 4.096 0.512 11.025kHz 2.8224 4.2336 5.6448 0.7056 12kHz 3.072 4.608 6.144 0.768 16kHz 4.096 6.144 8.192 1.024 22.05kHz 5.6448 8.4672 11.2896 1.4112 24kHz 6.144 9.216 12.288 1.536 32kHz 8.192 12.288 16.384 2.048 44.1kHz 11.2896 16.9344 22.5792 2.8224 48kHz 12.288 18.432 24.576 3.072Table 1. System Clock ExampleAll external clocks (MCLK, BICK and LRCK) should always be present whenever the DAC is in normal operation mode (PMDAC bit = “1”). If these clocks are not provided, the AK4367 may draw excess current and will not operate properly because it utilizes these clocks for internal dynamic refresh of registers. If the external clocks are not present, the DAC should be placed in power-down mode (PMDAC bit = “0”). When MCLK is input with AC coupling, the MCKAC bit should be set to “1”.For low sampling rates, DR and S/N degrade because of the outband noise. DR and S/N are improved by setting DFS1 bit to “1”. Table 2 shows S/N of DAC output for both the HP-amp and MOUT. When the DFS1 bit is “1”, MCLK needs 512fs.S/N (fs=8kHz, A-weighted) DFS1 DFS0 Over SampleRate fs MCLKHP-amp MOUT0 0 64fs 8kHz ∼48kHz 256fs/384fs/512fs 56dB 56dB Default 0 1 128fs 8kHz ∼24kHz 256fs/384fs/512fs 75dB 75dB 1 x 256fs 8kHz ∼12kHz512fs 92dB 90dB Table 2. Relationship among fs, MCLK frequency and S/N of HP-amp and MOUTASAHI KASEI [AK4367]Serial Data InterfaceThe AK4367 interfaces with external system via the SDATA, BICK and LRCK pins. Five data formats are available and are selected by setting DIF2, DIF1 and DIF0 bits (Table 3). Mode 0 is compatible with existing 16bit DACs and digital filters. Mode 1 is a 20bit version of Mode 0. Mode 4 is a 24bit version of Mode 0. Mode 2 is similar to AKM ADCs and many DSP serial ports. Mode 3 is compatible with the I 2S serial data protocol. In Modes 2 and 3 with BICK ≥48fs, the following formats are also valid: 16-bit data followed by eight zeros (17th to 24th bits) and 20-bit data followed by four zeros (21st to 24th bits). In all modes, the serial data is MSB first and 2’s complement format.DIF2 bit DIF1 bit DIF0 bit MODE BICK Figure 0 0 0 0: 16bit, LSB justified 32fs ≤ BICK ≤ 64fs Figure 10 0 0 1 1: 20bit, LSB justified 40fs ≤ BICK ≤ 64fs Figure 11 0 1 0 2: 24bit, MSB justified 48fs ≤ BICK ≤ 64fsFigure 12Default 0 1 1 3: I 2S Compatible BICK=32fs or 48fs ≤ BICK ≤ 64fs Figure 13 1 0 0 4: 24bit, LSB justified 48fs ≤ BICK ≤ 64fsFigure 11 Table 3. Audio Data FormatSDATA BICK LRCKSDATA BICK (32fs)Mode 0Mode 0Figure 10. Mode 0 TimingSDATA LRCK BICK Mode 1SDATA Mode 4Figure 11. Mode 1, 4 TimingASAHI KASEI [AK4367]LRCKBICK SDATA 16bitSDATA 20bit SDATA 24bitFigure 12. Mode 2 TimingLRCK BICKSDATA 16bit SDATA 20bit SDATA 24bit BICK SDATA 16bit(32fs) Figure 13. Mode 3 TimingASAHI KASEI [AK4367]Digital AttenuatorThe AK4367 has a channel-independent digital attenuator (256 levels, 0.5dB step). This digital attenuator is placed before the D/A converter. ATTL/R7-0 bits set the attenuation level (0dB to −127dB or MUTE) for each channel (Table 4). At DATTC bit = “1”, ATTL7-0 bits control both Lch and Rch attenuation levels. At DATTC bit = “0”, ATTL7-0 bits control the Lch level and ATTR7-0 bits control the Rch level. When HPM bit = “1”, (L+R)/2 summation is done after volume control.ATTL7-0AttenuationATTR7-0DefaultFFH 0dBFEH −0.5dBFDH −1.0dBFCH −1.5dB: :: :02H −126.5dB01H −127.0dB00H MUTE (−∞)Table 4. Digital Volume ATT valuesThe ATS bit sets the transition time between set values of ATT7-0 bits as either 1061/fs or 7424/fs (Table 5). When ATS bit = “0”, a soft transition between the set values occurs(1062 levels). It takes 1061/fs (24ms@fs=44.1kHz) from FFH(0dB) to 00H(MUTE). The ATTs are 00H when the PMDAC bit is “0”. When the PMDAC returns to “1”, the ATTs fade to their current value. Digital attenuator is independent of the soft mute function.ATT speedATS0dB to MUTE 1 stepDefault0 1061/fs 4/fs1 7424/fs 29/fsTable 5. Transition time between set values of ATT7-0 bitsMOUT volume is controlled by ATTM3-0 bits when MMUTE bit = “0” (Table 6). Pop noise occurs when ATT3-0 bits are changed.MMUTE ATTM3-0 Attenuation0FH 0dB0EH −2dB0DH −4dB0CH −6dB: :: :01H −28dB00H −30dBDefault1 x MUTETable 6. MOUT Volume ATT valuesASAHI KASEI [AK4367] Soft MuteSoft mute operation is performed at digital domain. When the SMUTE bit goes to “1”, the output signal is attenuated by −∞ during ATT_DATA×ATT transition time (Table 5) from the current ATT level. When the SMUTE bit is returned to “0”, the mute is cancelled and the output attenuation gradually changes to the ATT level during ATT_DATA×ATT transition time. If the soft mute is cancelled before attenuating to −∞ after starting the operation, the attenuation is discontinued and returned to ATT level by the same cycle. The soft mute is effective for changing the signal source without stopping the signal transmission.Attenuation-∞Analog OutputFigure 14. Soft Mute FunctionNotes:(1) ATT_DATA×ATT transition time (Table 5). For example, this time is 3712LRCK cycles (3712/fs) at ATS bit =“1” and ATT_DATA = “128”.(2) The analog output corresponding to the digital input has a group delay, GD.(3) If the soft mute is cancelled before attenuating to −∞ after starting the operation, the attenuation is discontinuedand returned to ATT level by the same cycle.ASAHI KASEI [AK4367] De-emphasis FilterThe AK4367 includes a digital de-emphasis filter (tc = 50/15µs) by IIR filter corresponding to three sampling frequencies (32kHz, 44.1kHz and 48kHz). The de-emphasis filter is enabled by setting DEM1-0 bits (Table 7).DEM1 bit DEM0 bit De-emphasis44.1kHz0 0Default0 1 OFF48kHz1 01 132kHzTable 7. De-emphasis Filter Frequency SelectBass Boost FunctionBy controlling BST1-0 bits, the low frequency boost signal can be output from DAC. The setting value is common in Lch and Rch (Table 8).BST1 bit BST0 bit BOOSTDefault0 0 OFF0 1 MIN1 0 MID1 1 MAXTable 8. Low Frequency Boost SelectSystem ResetThe AK4367 should be reset once by bringing PDN pin “L” upon power-up. After exiting reset, VCOM, DAC, HPL, HPR and MOUT switch to the power-down state. The contents of the control register are maintained until the reset is done.DAC exits reset and power down state by MCLK after PMDAC bit is changed to “1”, and then DAC is powered up and the internal timing starts clocking by LRCK “↑”. DAC is in power-down mode until MCLK and LRCK are input.ASAHI KASEI [AK4367]Headphone OutputPower supply voltage for the Headphone-amp is supplied from the HVDD pin and centered on the MUTET voltage. The Headphone-amp output load resistance is min.16Ω. When the MUTEN bit is “1” at PMHPL=PMHPR= “1”, the common voltage rises to 0.45 x VDD. When the MUTEN bit is “0”, the common voltage of Headphone-amp falls and the outputs (HPL and HPR pins) go to VSS.A capacitor between the MUTET pin and ground reduces pop noise at power-up/down. It isrecommended that the capacitor with small variation of capacitance and low ESR (Equivalent Series Resistance) over all temperature range, since the rise and fall time in Table 9 depend on the capacitance and ESR of the external capacitor at MUTET pin. In case only one path is connected, DAC or LIN/RIN/MIN. In case both paths are connected,DAC and LIN/RIN/MIN.t r : Rise Time up to VCOM/2 100k x C (typ) 120k x C (typ) t f : Fall Time down to 0V 200k x C (typ) 150k x C (typ)Table 9. Headphone-Amp Rise/Fall Time[Example] : A capacitor between the MUTET pin and ground = 1.0µF, and only DAC path is connected:Time constant of rise time: t r = 100k Ω x 1µF = 100ms(typ) Time constant of fall time: t f = 200k Ω x 1µF = 200ms(typ)When PMHPL and PMHPR bits are “0”, the Headphone-amp is powered-down, and the outputs (HPL and HPR pins) go to VSS.MUTEN bitPMHPL/R bitHPL/R pin(1) (2)(4)(3)t rt f VCOM/2VCOMFigure 15. Power-up/Power-down Timing for Headphone-amp(1) Headphone-amp power-up (PMHPL and PMHPR bits = “1”). The outputs are still VSS.(2) Headphone-amp common voltage rises up (MUTEN bit = “1”). Common voltage of Headphone-amp is rising. This rise time depends on the capacitor value connected with the MUTET pin. The rise time up to VCOM/2 is t r = 100k x C(typ) when the capacitor value on MUTET pin is “C”.(3) Headphone-amp common voltage falls down (MUTEN bit = “0”). Common voltage of Headphone-amp is falling to VSS. This fall time depends on the capacitor value connected with the MUTET pin. The fall time down to 0V is t f = 200k x C(typ) when the capacitor value on MUTET pin is “C”.(4) Headphone-amp power-down (PMHPL, PMHPR bits = “0”). The outputs are VSS. If the power supply is switched off or Headphone-amp is powered-down before the common voltage goes to VSS, some pop noise occurs.ASAHI KASEI [AK4367]The cut-off frequency of Headphone-amp output depends on the external resistor and capacitor used. Table 10 shows the cut off frequency and the output power for various resistor/capacitor combinations. The headphone impedance R L is 16Ω. Output powers are shown at HVDD = 2.4, 3.0 and 3.3V. The output voltage of headphone is 0.47 x VDD (Vpp) @−4.8dBFS.Figure 16. External Circuit Example of HeadphoneOutput Power [mW]R [Ω] C [µF] fc [Hz] BOOST=OFF fc [Hz] BOOST=MIN 2.4V 3.0V 3.3V220 45 170 100 100 43 15 24 28100 70 286.8 47 149 78 7 12 14100 50 191647 106 474 6 7Table 10. Relationship of external circuit, output power and frequency responseASAHI KASEI [AK4367]Power-Up/Down Sequence1) DAC → HP-ampPower Supply PDN pinPMVCM bitClock InputSDTI pin PMDAC bit DAC Internal State HPL/R pinPMHPL, PMHPR bit ATTL7-0 ATTR7-0 bitMUTEN bitDACL, DACR bitFigure 17. Power-up/down sequence of DAC and HP-amp(1) PDN pin should be set to “H” at least 150ns after the power is supplied.(2) PMVCM and PMDAC bits should be changed to “1” after PDN pin goes to “H”.(3) External clocks (MCLK, BICK, LRCK) are needed to operate DAC. When PMDAC bit = “0”, these clocks can bestopped. Headphone amp can operate without these clocks.(4) DACL and DACR bits should be changed to “1” after PMDAC bit is changed to “1”.(5) PMHPL, PMHPR and MUTEN bits should be changed to “1” at least 2ms (in case external capacitance at VCOM pinis 2.2µF) after DACL and DACR bits are changed to “1”.(6) Rise time of headphone amp is determined by external capacitor (C) of MUTET pin. The rise time up to VCOM/2 ist r = 100k x C(typ). When C=1µF, time constant is 100ms(typ).(7) Fall time of headphone amp is determined by external capacitor (C) of MUTET pin. The fall time down to 0V is t f =200k x C(typ). When C=1µF, time constant is 200ms(typ).PMHPL, PMHPR, DACL and DACR bits should be changed to “0” after HPL and HPR pins go to VSS. (8) Analog output corresponding to digital input has the group delay (GD) of 20.8/fs(=472µs@fs=44.1kHz). (9) ATS bit sets transition time of digital attenuator. Default value is 1061/fs(=24ms@fs=44.1kHz).(10) Power supply should be switched off after headphone amp is powered down (HPL/R pins become “L”).ASAHI KASEI [AK4367]2) DAC → MOUTPower SupplyPDN pinPMVCM bitClock InputSDTI pin PMDAC bit DAC Internal State PMMO bit ATTL/R7-0 bit MOUT pinMMUTE, ATTM3-0 bitDACM bitFigure 18. Power-up/down sequence of DAC and MOUT(1) PDN pin should be set to “H” at least 150ns after the power is supplied. (2) PMVCM bit should be changed to “1” after PDN pin goes to “H”.(3) DACM bit should be changed to “1” after PMVCM bit is changed to “1”.(4) PMDAC and PMMO bits should be changed to “1” after DACM bit is changed to “1”.(5)External clocks (MCLK, BICK, LRCK) are needed to operate DAC. When PMDAC bit = “0”, these clocks can be stopped. MOUT buffer can operate without these clocks.(6) When PMMO bit is changed, pop noise is output from MOUT pin.(7) Analog output corresponding to digital input has the group delay (GD) of 20.8/fs(=472µs@fs=44.1kHz). (8) ATS bit sets transition time of digital attenuator. Default value is 1061/fs(=24ms@fs=44.1kHz).ASAHI KASEI [AK4367]3) LIN/RIN/MIN → HP-ampPower SupplyPDN pinPMVCM bitHPL/R pinLIN/RIN/MIN pinPMHPL/R bitMUTEN bitFigure 19. Power-up/down sequence of LIN/RIN/MIN and HP-amp(1) PDN pin should be set to “H” at least 150ns after the power is supplied. MCLK, BICK and LRCK can be stoppedwhen DAC is not used.(2) PMVCM bit should be changed to “1” after PDN pin goes to “H”.(3) LINL, MINL, RINR and MINR bits should be changed to “1” after PMVCM bit is changed to “1”.(4) When LINL, MINL, RINR or MINR bit is changed to “1”, LIN, RIN or MIN pin is biased to 0.45 x VDD voltage. (5) PMHPL, PMHPR and MUTEN bits should be changed to “1” at least 2ms (in case external capacitance at VCOM pinis 2.2µF) after LINL, MINL, RINR and MINR bits are changed to “1”.(6) Rise time of headphone amp is determined by external capacitor (C) of MUTET pin. The rise time up to VCOM/2 ist r = 100k x C(typ). When C=1µF, time constant is 100ms(typ).(7) Fall time of headphone amp is determined by external capacitor (C) of MUTET pin. The fall time down to 0V is t f =200k x C(typ). When C=1µF, time constant is 200ms(typ).PMHPL, PMHPR, LINL, MINL, RINR and MINR bits should be changed to “0” after HPL and HPR pins go to VSS.ASAHI KASEI [AK4367]4) LIN/RIN/MIN → MOUTPower SupplyPDN pinPMVCM bitMOUT pinMMUTE, ATTM3-0 bitLIN/RIN/MIN pin MUTEN bitPMMO bitFigure 20. Power-up/down sequence of LIN/RIN/MIN and MOUT(1) PDN pin should be set to “H” at least 150ns after the power is supplied. MCLK, BICK and LRCK can be stoppedwhen DAC is not used.(2) PMVCM bit should be changed to “1” after PDN pin goes to “H”.(3) LINM, RINM and MINM bits should be changed to “1” after PMVCM bit is changed to “1”.(4) When LINM, RINM or MINM bit is changed to “1”, LIN, RIN or MIN pin is biased to 0.45 x VDD voltage.(5) MUTEN and PMMO bits should be changed to “1” at least 2ms (in case external capacitance at VCOM pin is 2.2µF)after LINM, RINM and MINM bits are changed to “1”.(6) When PMMO bit is changed, pop noise is output from MOUT pin.。

AKD4367中文资料

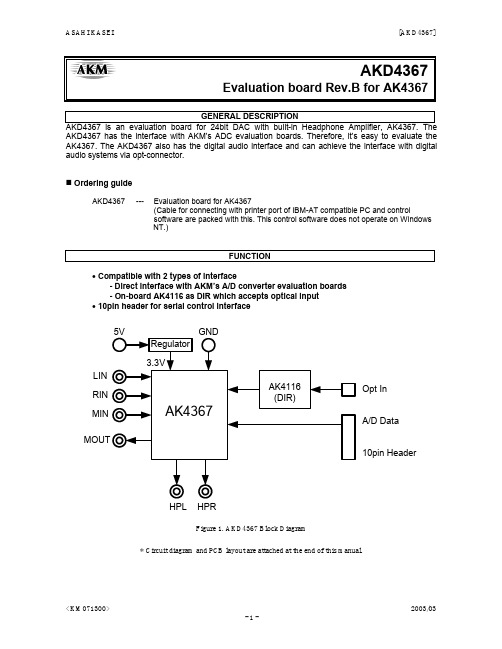

GENERAL DESCRIPTIONAKD4367 is an evaluation board for 24bit DAC with built-in Headphone Amplifier, AK4367. The AKD4367 has the interface with AKM’s ADC evaluation boards. Therefore, it’s easy to evaluate the AK4367. The AKD4367 also has the digital audio interface and can achieve the interface with digital audio systems via opt-connector.n Ordering guideAKD4367 --- Evaluation board for AK4367(Cable for connecting with printer port of IBM-AT compatible PC and controlsoftware are packed with this. This control software does not operate on Windows NT.)FUNCTION• Compatible with 2 types of interface- Direct interface with AKM’s A/D converter evaluation boards - On-board AK4116 as DIR which accepts optical input• 10pin header for serial control interfaceLIN RIN Opt In A/D Data 10pin HeaderHPRHPL MIN MOUTFigure 1. AKD4367 Block Diagram* Circuit diagram and PCB layout are attached at the end of this manual.Evaluation board Rev.B for AK4367AKD43671. Evaluation Board Manualn Operation sequence1) Set up the power supply lines.[+5V] (red) = 5V[AGND] (black) = 0V : for analog ground[DGND] (black) = 0V : for logic groundEach supply line should be distributed from the power supply unit.2) Set up the evaluation mode, jumper pins.(See the followings.)3) Power on.The AK4367 and AK4116 should be resets once bringing SW1 (DAC_PDN) and SW2 (DIR_PDN) “L” upon power-up.n Evaluation modeApplicable Evaluation Mode(1) In case of using DIR (Optical Link) <default>(2) In case of connecting AK4367 with a external DSP(1) In case of using DIR (Optical Link) <default>PORT1 (DIR) is used. DIR generates MCLK, BICK, LRCK and SDATA from the received data through optical connector (TORX141). Nothing should be connected to PORT3 (DSP).JP5 MCLKJP7LRCKJP84116_SDTO JP6BICKn How to evaluate AK4367 by connecting CD playerAKD4367 can evaluate tone quality easily by connecting CD Player (fs=44.1kHz).1). Connection Diagram2). Jumper and Switch SettingPORT1 (DIR) is used. DIR generates MCLK, BICK, LRCK and SDATA from the received data through optical connector (TORX141). Nothing should be connected to PORT3 (DSP).JP5MCLKJP7LRCKJP84116_SDTOJP6BICKCD Player(2) In case of connecting AK4367 with a external DSPAKD4367 can be connected with an external DSP through PORT3 (DSP).(1) When BICK, LRCK and SDATA are supplied from DSP, and MCLK is supplied from AK4116.JP5 MCLKJP7LRCKJP84116_SDTO JP6BICK(2) When MCLK, BICK, LRCK and SDATA are all supplied from DSP.JP5 MCLKJP7LRCKJP84116_SDTO JP6BICKn The function of the toggle SWUpper-side is “H” and lower-side is “L”.[SW1] (DAC_PDN) : Resets the AK4367. Keep “H” during normal operation.[SW2] (DIR_PDN) : Resets the AK4116. Keep “H” during normal operation.n Indication for LED[LED1] (ERF): Monitor INT0 pin of the AK4116. LED turns on when unlock or parity error occurs.n Serial ControlThe AK4367 can be controlled via the printer port (parallel port) of IBM-AT compatible PC. Connect PORT2 (uP-I/F) with PC by 10 wire flat cable packed with the AKD4367.ConnectCSNCCLKCDTI10pin Header10pinConnector10 wireflat cablePC AKD4367CDTOFigure 2. Connection of 10 wire flat cablen Input / Output circuit & Set-up jumper pin for Input / Output circuits(1) Input CircuitExternal analog signal is fed through the BNC connector. R21 are resistors to terminate the signal source. This resistors is not assembled on the board.MIN, LIN, RIN Input circuitsFigure 3. MIN, LIN, RIN Input circuitsJP2 (AIN) : Input pins are selected for the signals from BNC (J1). MIN : Input to MIN pin. LIN : Input to LIN pin.RIN: Input to RIN pin.(2) Output Circuit(a) MOUT Output circuitFigure 4. MOUT Output circuitsJ1MINLINC18RINJP2MIN J5MOUTR24MOUT(b) HPL, HPR Output circuitFigure 5. HPL, HPR Output circuit1. Outputs of HPL and HPR pins are applied via J2 and J4.JP4HPRLINEHP JP3HPLHP LINE2. Outputs of HPL and HPR pins are applied via J3 (mini jack).JP4HPRLINEHP JP3HPLHP LINE(3) Other Jumper Pins(a) JP1 (GND) : Analog ground and digital ground open :separatedshort :common (The connector “DGND” can be open.) <default>* AKM assumes no responsibility for the trouble when using the circuit examples.HPLHPRJ2HPLJ3HP2. Control Software Manualn Set-up of evaluation board and control software1. Set up the AKD4367 according to previous term.2. Connect IBM-AT compatible PC with AKD4367 by 10-line type flat cable (packed with AKD4367). Take care of thedirection of 10pin header. (Please install the driver in the CD-ROM when this control software is used on Windows 2000/XP. Please refer “Installation Manual of Control Software Driver by AKM device control software”. In case of Windows95/98/ME, this installation is not needed. This control software does not operate on Windows NT.)3. Insert the CD-ROM labeled “AK4367 Evaluation Kit” into the CD-ROM drive.4. Access the CD-ROM drive and double-click the icon of “akd4367.exe” to set up the control program.5. Then please evaluate according to the follows.n Operation flowKeep the following flow.1. Set up the control program according to explanation above.2. Click “Port Setup” button.3. Click “Write default” button.Then set up the dialog and input data.n Explanation of each buttons1. [Port Setup] : Set up the printer port.2. [Write default] : Initialize the register of AK4367.3. [Function1] : Dialog to write data by keyboard operation.4. [Function2] : Dialog to evaluate ATT.5. [Write] : Dialog to write data by mouse operation.n Explanation of each dialog1. [Function1 Dialog] : Dialog to write data by keyboard operationAddress Box: Input register address in 2 figures of hexadecimal.Data Box: Input register data in 2 figures of hexadecimal.If you want to write the input data to AK4367, click “OK” button. If not, click “Cancel” button.2. [Function2 Dialog] : Dialog to evaluate ATTThis dialog corresponds to only addr=04H, 05H and 08H.Address Box: Input register address in 2 figures of hexadecimal.Start Data Box: Input start data in 2 figures of hexadecimal.End Data Box: Input end data in 2 figures of hexadecimal.Interval Box: Data is written to AK4367 by this interval.Step Box: Data changes by this step.Mode Select Box:If you check this check box, data reaches end data, and returns to start data.[Example] Start Data = 00, End Data = 09Data flow: 00 01 02 03 04 05 06 07 08 09 09 08 07 06 05 04 03 02 01 00If you do not check this check box, data reaches end data, but does not return to start data.[Example] Start Data = 00, End Data = 09Data flow: 00 01 02 03 04 05 06 07 08 09If you want to write the input data to AK4367, click “OK” button. If not, click “Cancel” button.3. [Write Dialog] : Dialog to write data by mouse operationThere are dialogs corresponding to each register.Click the “Write” button corresponding to each register to set up the dialog. If you check the check box, data becomes “H” or “1”. If not, “L” or “0”.If you want to write the input data to AK4367, click “OK” button. If not, click “Cancel” button.n Indication of dataInput data is indicated on the register map. Red letter indicates “H” or “1” and blue one indicates “L” or “0”. Blank is the part that is not defined in the datasheet.n Attention on the operationIf you set up Function1 or Function2 dialog, input data to all boxes. Attention dialog is indicated if you input data or address that is not specified in the datasheet or you click “OK” button before you input data. In that case set up the dialog and input data once more again. These operations does not need if you click “Cancel” button or check the check box.MEASUREMENT RESULTS[Measurement condition]• Measurement unit : Audio Precession System Two Cascade• MCLK : 12.2896MHz• BICK : 64fs• fs : 44.1kHz• Bit : 24bit• Power Supply : VDD = HVDD = 3.3V• Measurement Filter : 10Hz ∼ 20kHz• Temperature : RoomParameter Result (Lch / Rch) UnitDAC Analog Output CharacteristicsTHD+N (-3dBFS Output) 56.8 / 56.1 dBD-Range (-60dB Output, A-weighted) 93.0 / 93.0 dBS/N (A-weighted) 94.9 / 93.8 dBMonaural Output CharacteristicsTHD+N (0dBFS Output) 64.5 dBS/N (A-weighted) 95.4 dB[Plot of Headphone Amplifier]AKMAK4367 HP-Amp THD+N vs. Input Level (fs=44.1kHz, fIn=1kHz)d B r A-140+0-130-120-110-100-90-80-70-60-50-40-30-20-10dBFSFigure 1. THD+N vs. Input LevelAKMAK4367 HP-Amp THD+N vs. fin (fs=44.1kHz, Input Level=-3dB)d B r AHzFigure 2. THD+N vs. Input FrequencyAKMAK4367 HP-Amp Linearity (fs=44.1kHz, fin=1kHz)d B r A-140+0-130-120-110-100-90-80-70-60-50-40-30-20-10dBFSFigure 3. LinearityAKMAK4367 HP-Amp Frequency Response (fs=44.1kHz, Input Level=-3dB)d B r A2020k501002005001k 2k 5k 10k HzFigure 4. Frequency Response (Boost off)(including external HPF)AKMAK4367 HP-Amp FFT Out-of-band Noise-120-110-100-90-80d B r A20100k501002005001k2k 5k 10k 20k 50k HzFigure 5. Out-band NoiseAKMAK4367 HP-Amp FFT (fs=44.1kHz, fin=1kHz, Input Level=-3dB)+0-130-120-110-100-90-80-70-60-50-40-30-20-10d B r A2020k501002005001k2k5k10kHzFigure 6. FFT Plot-130-120-110-100-90-80-70-60d B r A2020k501002005001k 2k 5k 10k HzFigure 7. FFT PlotAKMAK4367 HP-Amp FFT Noise Floor (No data Input)-130-120d B r A2020k501002005001k2k5k10kHzFigure 8. FFT PlotUpper@1kHz:Lch-->Rch, Lower@1kHz:Rch-->LchdB2020k 501002005001k2k5k10kHzFigure 9. Crosstalk PlotIMPORTANT NOTICE• These products and their specifications are subject to change without notice. Before considering any use or application, consult the Asahi Kasei Microsystems Co., Ltd. (AKM) sales office or authorized distributor concerning their current status.• AKM assumes no liability for infringement of any patent, intellectual property, or other right in the application or use of any information contained herein.• Any export of these products, or devices or systems containing them, may require an export license or other official approval under the law and regulations of the country of export pertaining to customs and tariffs, currency exchange, or strategic materials.• AKM products are neither intended nor authorized for use as critical components in any safety, life support, or other hazard related device or system, and AKM assumes no responsibility relating to any such use, except with the express written consent of the Representative Director of AKM. As used here:(a) A hazard related device or system is one designed or intended for life support or maintenance ofsafety or for applications in medicine, aerospace, nuclear energy, or other fields, in which its failure to function or perform may reasonably be expected to result in loss of life or in significant injury or damage to person or property.(b) A critical component is one whose failure to function or perform may reasonably be expected toresult, whether directly or indirectly, in the loss of the safety or effectiveness of the device or system containing it, and which must therefore meet very high standards of performance and reliability.• It is the responsibility of the buyer or distributor of an AKM product who distributes, disposes of, or otherwise places the product with a third party to notify that party in advance of the above content and conditions, and the buyer or distributor agrees to assume any and all responsibility and liability for and hold AKM harmless from any and all claims arising from the use of said product in the absence of such notification.。

AK4626VQP资料

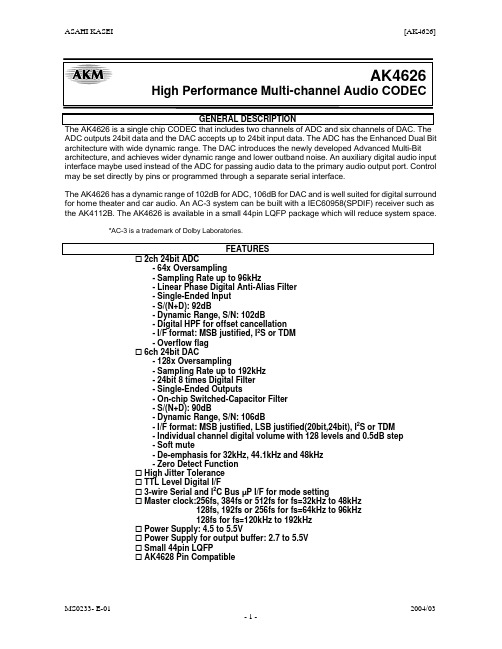

ASAHI KASEI[AK4626]AK4626High Performance Multi-channel Audio CODECGENERAL DESCRIPTION The AK4626 is a single chip CODEC that includes two channels of ADC and six channels of DAC. The ADC outputs 24bit data and the DAC accepts up to 24bit input data. The ADC has the Enhanced Dual Bit architecture with wide dynamic range. The DAC introduces the newly developed Advanced Multi-Bit architecture, and achieves wider dynamic range and lower outband noise. An auxiliary digital audio input interface maybe used instead of the ADC for passing audio data to the primary audio output port. Control may be set directly by pins or programmed through a separate serial interface. The AK4626 has a dynamic range of 102dB for ADC, 106dB for DAC and is well suited for digital surround for home theater and car audio. An AC-3 system can be built with a IEC60958(SPDIF) receiver such as the AK4112B. The AK4626 is available in a small 44pin LQFP package which will reduce system space.*AC-3 is a trademark of Dolby Laboratories.FEATURES 2ch 24bit ADC - 64x Oversampling - Sampling Rate up to 96kHz - Linear Phase Digital Anti-Alias Filter - Single-Ended Input - S/(N+D): 92dB - Dynamic Range, S/N: 102dB - Digital HPF for offset cancellation - I/F format: MSB justified, I2S or TDM - Overflow flag 6ch 24bit DAC - 128x Oversampling - Sampling Rate up to 192kHz - 24bit 8 times Digital Filter - Single-Ended Outputs - On-chip Switched-Capacitor Filter - S/(N+D): 90dB - Dynamic Range, S/N: 106dB - I/F format: MSB justified, LSB justified(20bit,24bit), I2S or TDM - Individual channel digital volume with 128 levels and 0.5dB step - Soft mute - De-emphasis for 32kHz, 44.1kHz and 48kHz - Zero Detect Function High Jitter Tolerance TTL Level Digital I/F 3-wire Serial and I2C Bus µP I/F for mode setting Master clock:256fs, 384fs or 512fs for fs=32kHz to 48kHz 128fs, 192fs or 256fs for fs=64kHz to 96kHz 128fs for fs=120kHz to 192kHz Power Supply: 4.5 to 5.5V Power Supply for output buffer: 2.7 to 5.5V Small 44pin LQFP AK4628 Pin CompatibleMS0233- E-01 -1-2004/03ASAHI KASEI[AK4626]Block DiagramLINADC ADCHPF HPFAudio I/FRINRX1 RX2 RX3 RX4 XTILOUT1LPFDACDATTMCLK LRCK BICKMCLK LRCK BICK DAUXXTO MCKO LRCK BICK SDTODIR AK4112BROUT1LPFDACDATTLOUT2LPFDACDATTFormat ConverterROUT2LPFDACDATTSDOUT SDOS SDTO LRCK BICK SDIN SDOUT1 SDOUT2 SDOUT3AC3LOUT3LPFDACDATTSDIN1 SDIN2 SDIN3ROUT3LPFDACDATTSDTI1 SDTI2 SDTI3AK4626Block Diagram (DIR and AC-3 DSP are external parts)MS0233- E-01 -2-2004/03ASAHI KASEI[AK4626]Ordering GuideAK4626VQ AKD4626 -40 ∼ +85°C 44pin LQFP(0.8mm pitch) Evaluation Board for AK4626Pin LayoutLOOP0/SDA/CDTIDIF1/SCL/CCLKDIF0/CSNVREFH 35MCLK444143424037AVSSAVDDDZF1P/S3938SDOS I2C SMUTE BICK LRCK SDTI1 SDTI2 SDTI3 SDTO DAUX DFS01 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 Top View3634 33 32 31VCOMTDM0DZF2/OVF RIN LIN NC TST5 ROUT1 LOUT1 ROUT2 LOUT2 ROUT3 LOUT3AK4626VQ30 29 28 27 26 25 24 23DVDDDVSSTVDDCAD1CAD0DZFETST1TST2TST3MS0233- E-01 -3-TST4PDN2004/03ASAHI KASEI[AK4626]Compatibility with AK4527B1. Functions Functions DAC Sampling frequency TDM128 (96kHz) Digital Attenuator Soft Mute Analog Input (ADC) 2. Pin Configurationpin# 11 12 18 19 20 21 22 29 30 31 32 44 AK4527B DFS NC TEST NC ADIF CAD1 CAD0 LINLIN+ RINRIN+ LOOP1 AK4626 DFS0 TST1 TST2 CAD1 CAD0 TST3 TST4 TST5 NC LIN RINAK4527B Up to 96kHz Not available 256 levels Soft mute function is independent of Digital attenuator. Differential inputAK4626 Up to 192kHz Available 128 levels Soft mute function is not independent of Digital attenuator. Single-ended InputTDM03. RegisterAddr 00H 00H 01H 01H 09H 0AH AK4527B Not available Not available DFS Not available Not available Not available AK4626 TDM0 TDM1 DFS0 DFS1 ATS1, ATS0 DZFM3MS0233- E-01 -4-2004/03ASAHI KASEI[AK4626]PIN/FUNCTIONNo. 1 Pin Name SDOS I/O I Function SDTO Source Select Pin (Note 1) “L”: Internal ADC output, “H”: DAUX input SDOS pin should be set to “L” when TDM= “1”. Control Mode Select Pin “L”: 3-wire Serial, “H”: I2C Bus Soft Mute Pin (Note 1) When this pin goes to “H”, soft mute cycle is initialized. When returning to “L”, the output mute releases. Audio Serial Data Clock Pin Input Channel Clock Pin DAC1 Audio Serial Data Input Pin DAC2 Audio Serial Data Input Pin DAC3 Audio Serial Data Input Pin Audio Serial Data Output Pin AUX Audio Serial Data Input Pin Double Speed Sampling Mode Pin (Note 1) “L”: Normal Speed, “H”: Double Speed Test Pin This pin should be connected to DVSS. Zero Input Detect Enable Pin “L”: mode 7 (disable) at parallel mode, zero detect mode is selectable by DZFM3-0 bits at serial mode “H”: mode 0 (DZF1 is AND of all six channels) Output Buffer Power Supply Pin, 2.7V∼5.5V Digital Power Supply Pin, 4.5V∼5.5V Digital Ground Pin, 0V Power-Down & Reset Pin When “L”, the AK4626 is powered-down and the control registers are reset to default state. If the state of P/S or CAD1-0 changes, then the AK4626 must be reset by PDN. Test Pin This pin should be connected to DVSS. Chip Address 1 Pin Chip Address 0 Pin Test Pin This pin should be left floating. Test Pin This pin should be left floating.2 3I2C SMUTEI I4 5 6 7 8 9 10 11 12 13BICK LRCK SDTI1 SDTI2 SDTI3 SDTO DAUX DFS0 TST1 DZFEI I I I I O I I I I14 15 16 17TVDD DVDD DVSS PDNI18 19 20 21 22TST2 CAD1 CAD0 TST3 TST4I I I O OMS0233- E-01 -5-2004/03ASAHI KASEI[AK4626]No. 23 24 25 26 27 28 29 30 31 32 33Pin Name LOUT3 ROUT3 LOUT2 ROUT2 LOUT1 ROUT1 TST5 NC LIN RIN DZF2I/O O O O O O O I I I OOVF 34 35 36 37 38 VCOM VREFH AVDD AVSS DZF1O O I O39 40 41MCLK P/S DIF0 CSN DIF1 SCL/CCLK LOOP0 SDA/CDTII I I I I I I I/O I424344TDM0Function DAC3 Lch Analog Output Pin DAC3 Rch Analog Output Pin DAC2 Lch Analog Output Pin DAC2 Rch Analog Output Pin DAC1 Lch Analog Output Pin DAC1 Rch Analog Output Pin Test pin (Internal pull-down pin) This pin should be left floating or connected to AVSS. No Connect No internal bonding. Lch Analog Input Pin Rch Analog Input Pin Zero Input Detect 2 Pin (Note 2) When the input data of the group 1 follow total 8192 LRCK cycles with “0” input data, this pin goes to “H”. And when RSTN bit is “0”, PWDAN pin is “0”, this pin goes to “H”. It always is in “L” when P/S is “H”. Analog Input Overflow Detect Pin (Note 3) This pin goes to “H” if the analog input of Lch or Rch overflows. Common Voltage Output Pin, AVDD/2 Large external capacitor around 2.2µF is used to reduce power-supply noise. Positive Voltage Reference Input Pin, AVDD Analog Power Supply Pin, 4.5V∼5.5V Analog Ground Pin, 0V Zero Input Detect 1 Pin (Note 2) When the input data of the group 1 follow total 8192 LRCK cycles with “0” input data, this pin goes to “H”. And when RSTN bit is “0”, PWDAN pin is “0”, this pin goes to “H”. Output is selected by setting DZFE pin when P/S is “H”. Master Clock Input Pin Parallel/Serial Select Pin “L”: Serial control mode, “H”: Parallel control mode Audio Data Interface Format 0 Pin in parallel control mode Chip Select Pin in 3-wire serial control mode This pin should be connected to DVDD at I2C bus control mode Audio Data Interface Format 1 Pin in parallel control mode Control Data Clock Pin in serial control mode I2C = “L”: CCLK (3-wire Serial), I2C = “H”: SCL (I2C Bus) Loopback Mode 0 Pin in parallel control mode Enables digital loop-back from ADC to 3 DACs. Control Data Input Pin in serial control mode I2C = “L”: CDTI (3-wire Serial), I2C = “H”: SDA (I2C Bus) TDM I/F Format Mode Pin (Note 1) “L”: Normal mode, “H”: TDM modeNotes: 1. SDOS, SMUTE, DFS0, and TDM0 pins are ORed with register data if P/S = “L”. 2. The group 1 and 2 can be selected by DZFM3-0 bits if P/S = “L” and DZFE = “L”. 3. This pin becomes OVF pin if OVFE bit is set to “1” at serial control mode. 4. All digital input pins except for pull-down should not be left floating.MS0233- E-01 -6-2004/03ASAHI KASEI[AK4626]ABSOLUTE MAXIMUM RATINGS (AVSS, DVSS=0V; Note 5) Parameter Symbol min AVDD -0.3 Power Supplies Analog DVDD -0.3 Digital TVDD -0.3 Output buffer |AVSS-DVSS| (Note 6) ∆GND Input Current (any pins except for supplies) IIN Analog Input Voltage VINA -0.3 Digital Input Voltage (Expect LRCK, BICK pins) VIND1 -0.3 (LRCK, BICK pins) VIND2 -0.3 Ambient Temperature (power applied) Ta -40 Storage Temperature Tstg -65Notes: 5. All voltages with respect to ground. 6. AVSS and DVSS must be connected to the same analog ground plane.max 6.0 6.0 6.0 0.3 ±10 AVDD+0.3 DVDD+0.3 TVDD+0.3 85 150Units V V V V mA V V V °C °CWARNING: Operation at or beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.RECOMMENDED OPERATING CONDITIONS (AVSS, DVSS=0V; Note 5) Parameter Symbol min typ Power Supplies Analog AVDD 4.5 5.0 (Note 7) Digital DVDD 4.5 5.0 Output buffer TVDD 2.7 5.0max 5.5 5.5 5.5Units V V VNotes: 5. All voltages with respect to ground. 7. The power up sequence between AVDD, DVDD and TVDD is not critical. Do not turn off only the AK4626 under the condition that a surrounding device is powered on and the I2C bus is in use. WARNING: AKM assumes no responsibility for the usage beyond the conditions in this datasheet.MS0233- E-01 -7-2004/03ASAHI KASEI[AK4626]ANALOG CHARACTERISTICS (Ta=25°C; AVDD, DVDD, TVDD=5V; AVSS, DVSS=0V; VREFH=AVDD; fs=48kHz; BICK=64fs; Signal Frequency=1kHz; 24bit Data; Measurement Frequency=20Hz∼20kHz at 48kHz, 20Hz~40kHz at fs=96kHz, 20Hz~40kHz at fs=192kHz; unless otherwise specified) Parameter min typ max Units ADC Analog Input Characteristics Resolution 24 Bits S/(N+D) (-0.5dBFS) fs=48kHz 84 92 dB fs=96kHz 86 dB DR (-60dBFS) fs=48kHz, A-weighted 94 102 dB fs=96kHz 88 96 dB fs=96kHz, A-weighted 93 102 dB dB 102 94 S/N (Note 8) fs=48kHz, A-weighted dB 96 88 fs=96kHz dB 102 93 fs=96kHz, A-weighted Interchannel Isolation 90 110 dB DC Accuracy Interchannel Gain Mismatch 0.2 0.3 dB Gain Drift 20 ppm/°CInput Voltage AIN=0.62xVREFH 2.90 3.10 3.30 VppInput Resistance (Note 9) Power Supply Rejection (Note 10) DAC Analog Output Characteristics Resolution S/(N+D) fs=48kHz fs=96kHz fs=192kHz DR (-60dBFS) fs=48kHz, A-weighted fs=96kHz fs=96kHz, A-weightedfs=192kHz fs=192kHz, A-weighted1525 50 24kΩ dB Bits dB dB dB dB dB dB dB dB dB dB dB dB dB dB dB ppm/°C Vpp kΩ dBS/N(Note 11)fs=48kHz, A-weighted fs=96kHz fs=96kHz, A-weightedfs=192kHz fs=192kHz, A-weightedInterchannel Isolation DC Accuracy Interchannel Gain Mismatch Gain Drift Output Voltage AOUT=0.6xVREFH Load Resistance Power Supply Rejection Notes:80 78 95 88 94 95 88 94 9090 88 88 106 100 106 100 106 106 100 106 100 106110 0.2 20 3.0 50 0.5 3.252.75 5 (Note 10)8. S/N measured by CCIR-ARM is 98dB(@fs=48kHz). 9. Input resistance is 16kΩ typically at fs=96kHz. 10. PSR is applied to AVDD, DVDD and TVDD with 1kHz, 50mVpp. VREFH pin is held a constant voltage. 11. S/N measured by CCIR-ARM is 102dB(@fs=48kHz).MS0233- E-01 -8-2004/03ASAHI KASEI[AK4626]Parameter Power SuppliesPower Supply Current (AVDD+DVDD+TVDD) Normal Operation (PDN = “H”) AVDD fs=48kHz,96kHz fs=192kHz DVDD+TVDD fs=48kHz fs=96kHz fs=192kHz Power-down mode (PDN = “L”) TST=”L”mintypmaxUnits(Note 12)(Note 13)45 34 18 24 27 8067 51 27 36 40 200mA mA mA mA mA µANotes: 12. TVDD=0.1mA(typ). 13. In the power-down mode. All digital input pins including clock pins (MCLK, BICK, LRCK) are held DVSS.MS0233- E-01 -9-2004/03ASAHI KASEI[AK4626]FILTER CHARACTERISTICS (Ta=25°C; AVDD, DVDD=4.5∼5.5V; TVDD=2.7∼5.5V; fs=48kHz) Parameter Symbol min ADC Digital Filter (Decimation LPF): PB 0 Passband (Note 14) ±0.1dB -0.2dB -3.0dB Stopband SB 28 Passband Ripple PR Stopband Attenuation SA 68 Group Delay (Note 15) GD Group Delay Distortion ∆GD ADC Digital Filter (HPF): Frequency Response (Note 14) -3dB FR -0.1dB DAC Digital Filter: Passband (Note 14) -0.1dB PB 0 -6.0dB Stopband SB 26.2 Passband Ripple PR Stopband Attenuation SA 54 Group Delay (Note 15) GD DAC Digital Filter + Analog Filter: FR Frequency Response: 0 ∼ 20.0kHz FR 40.0kHz (Note 16) FR 80.0kHz (Note 16)typmax 18.9 ±0.04Units kHz kHz kHz kHz dB dB 1/fs µs Hz Hz20.0 23.016 0 1.0 6.5 21.8 ±0.02 19.2±0.2 ±0.3 ±1.024.0kHz kHz kHz dB dB 1/fs dB dB dBNotes: 14. The passband and stopband frequencies scale with fs. For example, 21.8kHz at –0.1dB is 0.454 x fs. 15. The calculating delay time which occurred by digital filtering. This time is from setting the input of analog signal to setting the 24bit data of both channels to the output register for ADC. For DAC, this time is from setting the 20/24bit data of both channels on input register to the output of analog signal. 16. 40.0kHz; fs=96kHz , 80.0kHz; fs=192kHz.DC CHARACTERISTICS (Ta=25°C; AVDD, DVDD=4.5∼5.5V; TVDD=2.7∼5.5V) Parameter Symbol min High-Level Input Voltage VIH 2.2 Low-Level Input Voltage VIL High-Level Output Voltage (SDTO, LRCK, BICK pin: Iout=-100µA) VOH TVDD-0.5 (DZF1, DZF2/OVF pins: Iout=-100µA) VOH AVDD-0.5 Low-Level Output Voltage (SDTO, DZF1, DZF2/OVF pins: Iout= 100µA) VOL (SDA, LRCK, BICK pin: Iout= 3mA) VOL Input Leakage Current (Note 17) Iin Note 17: TST2 pin has an internal pull-down device, nominally 100kohm.typ -max 0.8 0.5 0.4 ±10Units V V V V V V µAMS0233- E-01 - 10 -2004/03SWITCHING CHARACTERISTICS(Ta=-40°C∼85°C; AVDD, DVDD=4.5∼5.5V; TVDD=2.7∼5.5V; C L=20pF)Parameter SymbolmintypmaxUnits Master Clock Timing256fsn, 128fsd: Pulse Width Low Pulse Width High 384fsn, 192fsd: Pulse Width Low Pulse Width High 512fsn, 256fsd: Pulse Width Low Pulse Width High fCLKtCLKLtCLKHfCLKtCLKLtCLKHfCLKtCLKLtCLKH8.192272712.288202016.384151512.28818.43224.576MHznsnsMHznsnsMHznsnsLRCK TimingNormal mode (TDM0= “0”, TDM1= “0”)Normal Speed Mode Double Speed Mode Quad Speed Mode Duty Cycle fsnfsdfsqDuty326412045489619255kHzkHzkHz%TDM256 mode (TDM0= “1”, TDM1= “0”)LRCK frequency “H” time“L” time fsntLRHtLRL321/256fs1/256fs48 kHznsnsTDM128 mode (TDM0= “1”, TDM1= “1”)LRCK frequency “H” time“L” timefsdtLRHtLRL641/128fs1/128fs96 kHznsnsAudio Interface TimingNormal mode (TDM0= “0”, TDM1= “0”)BICK PeriodBICK Pulse Width LowPulse Width HighLRCK Edge to BICK “↑” (Note 18) BICK “↑” to LRCK Edge (Note 18) LRCK to SDTO(MSB)BICK “↓” to SDTOSDTI1-3,DAUX Hold TimeSDTI1-3,DAUX Setup Time tBCKtBCKLtBCKHtLRBtBLRtLRStBSDtSDHtSDS813232202020204040nsnsnsnsnsnsnsnsnsnsTDM256 mode (TDM0= “1”, TDM1= “0”)BICK PeriodBICK Pulse Width LowPulse Width HighLRCK Edge to BICK “↑” (Note 18) BICK “↑” to LRCK Edge (Note 18) BICK “↓” to SDTOSDTI1 Hold TimeSDTI1 Setup Time tBCKtBCKLtBCKHtLRBtBLRtBSDtSDHtSDS8132322020101020nsnsnsnsnsnsnsnsnsTDM128 mode (TDM0= “1”, TDM1= “1”)BICK PeriodBICK Pulse Width LowPulse Width HighLRCK Edge to BICK “↑” (Note 18) BICK “↑” to LRCK Edge (Note 18) BICK “↓” to SDTOSDTI1-2 Hold TimeSDTI1-2 Setup Time tBCKtBCKLtBCKHtLRBtBLRtBSDtSDHtSDS8132322020101020nsnsnsnsnsnsnsnsnsNotes: 18. BICK rising edge must not occur at the same time as LRCK edge.Parameter SymbolmintypmaxUnitsControl Interface Timing (3-wire Serial mode):CCLK PeriodCCLK Pulse Width LowPulse Width High CDTI Setup Time CDTI Hold TimeCSN “H” TimeCSN “↓” to CCLK “↑” CCLK “↑” to CSN “↑” tCCKtCCKLtCCKHtCDStCDHtCSWtCSStCSH200808040401505050nsnsnsnsnsnsnsnsControl Interface Timing (I2C Bus mode):SCL Clock FrequencyBus Free Time Between TransmissionsStart Condition Hold Time (prior to first clock pulse) Clock Low TimeClock High TimeSetup Time for Repeated Start ConditionSDA Hold Time from SCL Falling (Note 19) SDA Setup Time from SCL RisingRise Time of Both SDA and SCL LinesFall Time of Both SDA and SCL LinesSetup Time for Stop ConditionPulse Width of Spike Noise Suppressed by Input Filter fSCLtBUFtHD:STAtLOWtHIGHtSU:STAtHD:DATtSU:DATtRtFtSU:STOtSP-4.74.04.74.04.70.25--4.0100-------1.00.3-50kHzµsµsµsµsµsµsµsµsµsµsnsPower-down & Reset TimingPDN Pulse Width (Note 20) PDN “↑” to SDTO valid (Note 21) tPDtPDV150522ns1/fsNotes: 19. Data must be held for sufficient time to bridge the 300 ns transition time of SCL.20. The AK4626 can be reset by bringing PDN “L” to “H” upon power-up.21. These cycles are the number of LRCK rising from PDN rising.22. I2C is a registered trademark of Philips Semiconductors.Purchase of Asahi Kasei Microsystems Co., Ltd I2C components conveys a license under the Philips I2C patent to use the components in the I2C system, provided the system conform to the I2Cspecifications defined by Philips.Timing DiagramVIHMCLKVILLRCKVIH VILVIH BICKVILClock Timing (TDM= “0”)VIH MCLKVILLRCKVIH VILVIH BICKVILClock Timing (TDM= “1”)LRCKVIH BICKVILSDTO50%TVDDVIH VILSDTIVIH VILAudio Interface Timing (TDM= “0”)LRCKVIH BICKVILSDTO50%TVDDVIH VILSDTIVIH VILAudio Interface Timing (TDM= “1”)CSNVIH CCLKVILVIH CDTI VILVIHVILWRITE Command Input Timing (3-wire Serial mode)CSNVIH CCLKVILVIH CDTI VILVIHVILD3D2D1D0WRITE Data Input Timing (3-wire Serial mode)VIHVILVIHVILI 2C Bus mode TimingVILPDNSDTO 50%TVDDVIHPower-down & Reset TimingOPERATION OVERVIEWSystem ClockThe external clocks, which are required to operate the AK4626, are MCLK, LRCK and BICK. MCLK should be synchronized with LRCK but the phase is not critical. There are two methods to set MCLK frequency. In Manual Setting Mode (ACKS = “0”: Default), the sampling speed is set by DFS0, DFS1 (Table 1). The frequency of MCLK at each sampling speed is set automatically. (Table 2, 3, 4). In Auto Setting Mode (ACKS = “1”), as MCLK frequency is detected automatically (Table 5), and the internal master clock becomes the appropriate frequency (Table 6), it is not necessary to set DFS.External clocks (MCLK, BICK) should always be present whenever the AK4626 is in normal operation mode (PDN = “H”). If these clocks are not provided, the AK4626 may draw excess current because the device utilizes dynamic refreshed logic internally. If the external clocks are not present, the AK4626 should be in the power-down mode (PDN = “L”) or in the reset mode (RSTN = “0”). After exiting reset at power-up etc., the AK4626 is in the power-down mode until MCLK and LRCK are input.(fs)SpeedDFS1 DFS0 SamplingDefaultMode 32kHz~48kHzSpeed0 0 Normal0 1 DoubleMode 64kHz~96kHzSpeedMode 120kHz~192kHz1 0 QuadSpeedTable 1. Sampling Speed (Manual Setting Mode)(MHz) BICK(MHz) LRCK MCLKfs 256fs 384fs 512fs 64fs32.0kHz 8.1920 12.2880 16.3840 2.048044.1kHz 11.2896 16.9344 22.5792 2.822448.0kHz 12.2880 18.4320 24.5760 3.0720Table 2. System Clock Example (Normal Speed Mode @Manual Setting Mode)LRCK MCLK (MHz) BICK (MHz)fs 128fs 192fs 256fs 64fs88.2kHz 11.2896 16.9344 22.5792 5.644896.0kHz 12.2880 18.4320 24.5760 6.1440Table 3. System Clock Example (Double Speed Mode @Manual Setting Mode)(Note: At Double speed mode(DFS1= “0”, DFS0 = “1”), 128fs and 192fs are not available for ADC.)LRCK MCLK (MHz) BICK (MHz)fs 128fs 192fs 256fs 64fs176.4kHz 22.5792 - - 11.2896192.0kHz 24.5760 - - 12.2880Table 4. System Clock Example (Quad Speed Mode @Manual Setting Mode)(Note: At Quad speed mode(DFS1= “1”, DFS0 = “0”) are not available for ADC.)MCLK Sampling Speed512fs Normal 256fs Double 128fs QuadTable 5. Sampling Speed (Auto Setting Mode)LRCK MCLK (MHz) fs 128fs 256fs 512fs Sampling Speed 32.0kHz - - 16.384044.1kHz - - 22.579248.0kHz - - 24.5760 Normal 88.2kHz - 22.5792 -96.0kHz - 24.5760 - Double176.4kHz 22.5792 - -192.0kHz 24.5760 - -QuadTable 6. System Clock Example (Auto Setting Mode)De-emphasis FilterThe AK4626 includes the digital de-emphasis filter (tc=50/15µs) by IIR filter. De-emphasis filter is not available in Double Speed Mode and Quad Speed Mode. This filter corresponds to three sampling frequencies (32kHz, 44.1kHz, 48kHz). De-emphasis of each DAC can be set individually by register data of DEMA1-C0 (DAC1: DEMA1-0, DAC2: DEMB1-0, DAC3: DEMC1-0, see “Register Definitions”).Mode Sampling Speed DEM1 DEM0 DEM 0 Normal Speed 0 0 44.1kHz 1 Normal Speed 0 1 OFF2 Normal Speed 1 0 48kHz3 Normal Speed 1 1 32kHzDefaultTable 7. De-emphasis controlDigital High Pass FilterThe ADC has a digital high pass filter for DC offset cancel. The cut-off frequency of the HPF is 1.0Hz at fs=48kHz and scales with sampling rate (fs).Audio Serial Interface FormatWhen TDM= “L”, four modes can be selected by the DIF1-0 as shown in Table 8. In all modes the serial data is MSB-first, 2’s compliment format. The SDTO is clocked out on the falling edge of BICK and the SDTI/DAUX are latched on the rising edge of BICK.Figures 1∼4 shows the timing at SDOS = “L”. In this case, the SDTO outputs the ADC output data. When SDOS = “H”, the data input to DAUX is converted to SDTO’s format and output from SDTO. Mode 2, 3, 6, 7, 10, 11 in SDTI input formats can be used for 16-20bit data by zeroing the unused LSBs.LRCK BICK ModeTDM 1TDM0 DIF1 DIF0SDTOSDTI1-3, DAUXI/O I/O0 0 0 0 024bit, Left justified 20bit, Rightjustified H/L I ≥ 48fs I 1 0 0 0 1 24bit, Left justified 24bit, Rightjustified H/LI ≥ 48fs I 2 0 0 1 0 24bit, Left justified 24bit, LeftjustifiedH/LI≥ 48fsI Default 3 0 0 1 1 24bit, I 2S 24bit, I 2S L/HI ≥ 48fsITable 8. Audio data formats (Normal mode)The audio serial interface format becomes the TDM mode if TDM0 pin is set to “H”. In the TDM256 mode, the serial data of all DAC (six channels) is input to the SDTI1 pin. The input data to SDTI2-3 pins are ignored. BICK should be fixed to 256fs. “H” time and “L” time of LRCK should be 1/256fs at least. Four modes can be selected by the DIF1-0 as shown in Table 9. In all modes the serial data is MSB-first, 2’s compliment format. The SDTO is clocked out on the falling edge of BICK and the SDTI1 are latched on the rising edge of BICK. SDOS and LOOP1-0 should be set to “0” at the TDM mode. TDM128 Mode can be set by TDM1 as show in Table10. In Double Speed Mode, the serial data of DAC (four channels; L1, R1, L2, R2) is input to the SDTI1 pin. Other two data (L3, R3) are input to the SDTI2. TDM0 pin and TDM0 register should be set to “H” if TDM256 Mode is selected. TDM0 pin and TDM0 register, TDM1 register should be set to “H” if Double Speed Mode is selected in TDM128 Mode.LRCK BICKMode TDM 1 TDM0 DIF1 DIF0SDTOSDTI1I/O I/O4 0 1 0 024bit, Left justified 20bit, Rightjustified ↑ I 256fs I5 0 1 0 124bit, Left justified 24bit, Rightjustified ↑ I 256fs I 6 0 1 1 024bit, Left justified 24bit, Leftjustified↑ I 256fs I 7 0 1 1 1 24bit, I 2S 24bit, I 2S↓I 256fs ITable 9. Audio data formats (TDM256 mode)LRCK BICK Mode TDM 1 TDM0 DIF1 DIF0SDTOSDTI1,SDTI2I/O I/O8 1 1 0 024bit, Left justified 20bit, Rightjustified ↑ I 128fs I9 1 1 0 124bit, Left justified 24bit, Rightjustified ↑ I 128fs I 10 1 1 1 024bit, Left justified 24bit, Leftjustified↑ I 128fs I 11 1 1 1 1 24bit, I 2S 24bit, I 2S↓I 128fs ITable 10. Audio data formats (TDM128 mode)BICK(64fs)SDTO(o)SDTI(i)Figure 1. Mode 0 Timing Array LRCKBICK(64fs)SDTO(o)SDTI(i)Figure 2. Mode 1 TimingLRCKSDTO(o)SDTI(i)Figure 3. Mode 2 Timing ArrayLRCKSDTO(o)SDTI(i)Figure 4. Mode 3 TimingLRCKBICK(256fs)SDTO(o)SDTI1(i)Figure 5. Mode 4 TimingLRCKBICK(256fs)SDTO(o)SDTI1(i)Figure 6. Mode 5 TimingLRCKBICK(256fs)SDTO(o)SDTI1(i)Figure 7. Mode 6 TimingLRCKBICK(256fs)SDTO(o)SDTI1(i)Figure 8. Mode 7 TimingLRCKBICK(128fs)SDTO(o)SDTI1(i)SDTI2(i)Figure 9. Mode 8 TimingLRCKBICK(128fs)SDTI1(i)SDTI2(i)Figure 10. Mode 9 TimingLRCKBICK(128fs)SDTO(o)SDTI1(i)SDTI2(i)Figure 11. Mode 10 TimingBICK(128fs)SDTO(o)SDTI1(i)SDTI2(i)Figure 12. Mode 11 TimingOverflow DetectionThe AK4626 has overflow detect function for analog input. Overflow detect function is enable if OVFE bit is set to “1” at serial control mode. OVF pin goes to “H” if analog input of Lch or Rch overflows (more than -0.3dBFS). OVF output for overflowed analog input has the same group delay as ADC (GD = 16/fs = 333µs @fs=48kHz). OVF is “L” for 522/fs (=11.8ms @fs=48kHz) after PDN = “↑”, and then overflow detection is enabled.Zero DetectionThe AK4626 has two pins for zero detect flag outputs. Channel grouping can be selected by DZFM3-0 bits if P/S = “L” and DZFE = “L” (Table 11). DZF1 pin corresponds to the group 1 channels and DZF2 pin corresponds to the group 2 channels. However DZF2 pin becomes OVF pin if OVFE bit is set to “1”. Zero detection mode is set to mode 0 if DZFE= “H” regardless of P/S pin. DZF1 is AND of all six channels and DZF2 is disabled (“L”) at mode 0. Table 12 shows the relation of P/S, DZFE, OVFE and DZF.When the input data of all channels in the group 1(group 2) are continuously zeros for 8192 LRCK cycles, DZF1(DZF2) pin goes to “H”. DZF1(DZF2) pin immediately goes to “L” if input data of any channels in the group 1(group 2) is not zero after going DZF1(DZF2) “H”.DZFM AOUT Mode3 2 1 0 L1 R1 L2 R2 L3 R3 0 0 0 0 0 DZF1DZF1DZF1DZF1DZF1DZF1 1 0 0 0 1 DZF1DZF1DZF1DZF1DZF1DZF2 2 0 0 1 0 DZF1DZF1DZF1DZF1DZF2DZF2 3 0 0 1 1 DZF1DZF1DZF1DZF2DZF2DZF24 0 1 0 0 DZF1DZF1DZF2DZF2DZF2DZF25 0 1 0 1 DZF1DZF2DZF2DZF2DZF2DZF26 0 1 1 0 DZF2DZF2DZF2DZF2DZF2DZF27 0 1 1 1 disable (DZF1=DZF2 = “L”)8 1 0 0 09 1 0 0 1 Not Available10 1 0 1 0 11 1 0 1 1 12 1 1 0 013 1 1 0 1 14 1 1 1 0 15 1 1 1 1disable (DZF1=DZF2 = “L”)DefaultTable 11. Zero detect controlP/S pin DZFE pin OVFE bit DZF mode DZF1 pin DZF2/OVF pin “L” disable Mode 7 “L” “L”“H” (parallel mode) “H” disable Mode 0 AND of 6ch “L”“0” Selectable Selectable Selectable“L” “1” Selectable Selectable OVF output “0” Mode 0 AND of 6ch “L” “L” (serial mode) “H”“1” Mode 0 AND of 6ch OVF outputTable 12. DZF1-2 pins outputs。

TP4366同步四灯显1A移动电源方案_TP4366规格书_TP4366 PDF

注:上表中电池电压是 Typical 情况下标准电压。

Ver1.0

TPOWER Semiconductor

5

TP4366 1A 同步移动电源方案

封装外形尺寸

SOP8L

符号 A A1 A2 b c D E E1 e L

最小值 1.35 0.08 1.20 0.33 0.17 4.70 5.80 3.70 0.38 0

极限参数(注 1)

参数 所有引脚对 GND 储存环境温度 工作结温范围 HBM MM 额定值 -0.3~+7 -50~+150 -40~150 3000 300 单位 V ℃ ℃ V V

推荐工作范围

符号 VDD TOP 参数 充电输入电压 工作环境温度 参数范围 4.5~5.5 -20~85 单位 V ℃

毫米 标准值 1.60 0.15 1.40 4.90 6.00 3.90 1.27BSC. 0.60 -

最大值 1.77 0.28 1.65 0.51 0.26 5.10 6.20 4.10 1.27 8

注明:本公司对本文档有修改的权利,本公司对本文档的修改恕不另行通知。

Ver1.0

TPOWER Semiconductor

公司名:深圳市升邦科技(TPOWER一级代理商) 联系人:胡先生 Q Q: 13322930472

应用

移动电源

2355540888 0755-85298367

电 话:

典型应用电路

Ver1.0

TPOWER Semiconductor

1

TP4366 1A 同步移动电源方案

管脚

管脚描述

管脚号 1 2 3 4 5 6 7 8 管脚名 称 OUT BAT SW GND SWT VDD LED2 LED1 描述 升压输出正极端以及输出电压采样端 锂离子电池正极 升压功率 NMOS 的漏极 芯片地 接按键和手电筒 LED 灯,短按按键显示电量,长按按键 2S 手电筒打开或关闭 电源输入端 LED 驱动端 LED 驱动端

AK4556VT中文资料

- Slave mode: 256fs, 384fs, 512fs or 768fs (Normal Speed)

256fs or 384fs

(Double Speed)

128fs or 192fs

(Quad Speed)

- Master mode: 256fs or 512fs

(Normal Speed)

Input/Output Voltage: ADC = 2.1Vpp @ VA=3.0V

Master/Slave mode Sampling Rate:

DAC = 2.1Vpp @ VA=3.0V

- Normal Speed: 8kHz to 54kHz

(256fs or 512fs)

8kHz to 48kHz

5 VD

- Digital Power Supply Pin

6 DEM0

I De-emphasis Control Pin

7 DEM1

I De-emphasis Control Pin

8 SDTO

9 CKS0 10 CSK1 11 CSK2

Audio Serial Data Output Pin O

1

20

ROUT

LIN

2

19

LOUT

VSS

3

18

VCOM

VA

4

Top

17

PDN

View

VDBiblioteka 516BCLK

DEM0

6

15

MCLK

DEM1

7

14

LRCK

SDTO

8

13

SDTI

CKS0

9

12

LTC4366高压浪涌抑制器详细学习资料大全

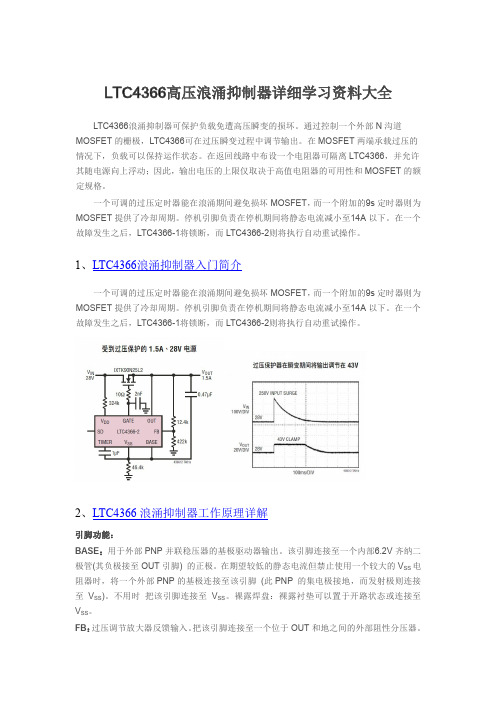

LTC4366高压浪涌抑制器详细学习资料大全LTC4366浪涌抑制器可保护负载免遭高压瞬变的损坏。

通过控制一个外部N沟道MOSFET的栅极,LTC4366可在过压瞬变过程中调节输出。

在MOSFET两端承载过压的情况下,负载可以保持运作状态。

在返回线路中布设一个电阻器可隔离LTC4366,并允许其随电源向上浮动;因此,输出电压的上限仅取决于高值电阻器的可用性和MOSFET的额定规格。

一个可调的过压定时器能在浪涌期间避免损坏MOSFET,而一个附加的9s定时器则为MOSFET提供了冷却周期。

停机引脚负责在停机期间将静态电流减小至14A以下。

在一个故障发生之后,LTC4366-1将锁断,而LTC4366-2则将执行自动重试操作。

1、LTC4366浪涌抑制器入门简介一个可调的过压定时器能在浪涌期间避免损坏MOSFET,而一个附加的9s定时器则为MOSFET提供了冷却周期。

停机引脚负责在停机期间将静态电流减小至14A以下。

在一个故障发生之后,LTC4366-1将锁断,而LTC4366-2则将执行自动重试操作。

2、LTC4366浪涌抑制器工作原理详解引脚功能:BASE:用于外部PNP并联稳压器的基极驱动器输出。

该引脚连接至一个内部6.2V齐纳二极管(其负极接至OUT引脚)的正极。

在期望较低的静态电流但禁止使用一个较大的V SS电阻器时,将一个外部PNP的基极连接至该引脚(此PNP的集电极接地,而发射极则连接至V SS)。

不用时把该引脚连接至V SS。

裸露焊盘:裸露衬垫可以置于开路状态或连接至V SS。

FB:过压调节放大器反馈输入。

把该引脚连接至一个位于OUT和地之间的外部阻性分压器。

过压调节放大器负责控制外部N沟道MOSFET的栅极,以把FB引脚电压调节在OUT以下1.23V。

在发生快速过压的情况下,过压放大器将启动GATE引脚上的一个200mA下拉电流源。

LTC4366引脚图3、LTC4366高压浪涌抑制器应用深入讲解应用信息LTC4366的典型应用是一种需要过压保护的系统,该系统可在过压瞬变期间安全地向负载分配功率。

AK4365中文资料