Lattice ECP5-5G系列低功耗无缝连接解决方案

5G电源白皮书

All rights reserved 版权所有,侵权必究

Page 3 , Total 17 第3页,共17页

5G电源白皮书

内部公开

1 5G时代的变化

1.1 网络的变化

5G时代是全移动和全连接的智慧时代,人与人、人与物、物与物都需要进行联接和通信,2025 年全球连接数量将会超过1000亿。

5G 电源白皮书

文档版本 发布日期

01 2019-01-30

华为技术有限公司

正文目录

1 5G时代的变化 ..................................................................................................................................... 4 1.1 网络的变化 .................................................................................................................................... 4 1.2 功耗的变化 .................................................................................................................................... 4 1.3 能源行业的变化............................................................................................................................. 5 1.4 电源行业的变化............................................................................................................................. 5 2 5G网络演进对能源的挑战................................................................................................................... 6 2.1 站点能源建设和改造的挑战 .......................................................................................................... 6 2.2 能源运维的挑战............................................................................................................................. 7 3 5G能源的需求及设计理念................................................................................................................... 7 3.1 5G能源总体需求 ........................................................................................................................... 7 3.2 5G能源设计理念 ........................................................................................................................... 8 4 5G电源细分场景及产品特征 ............................................................................................................... 8 4.1 改造和叠加场景............................................................................................................................. 8 4.2 新建或搬迁场景........................................................................................................................... 11 4.3 小站场景...................................................................................................................................... 12 4.4 能源智能化 .................................................................................................................................. 12 4.5 高效节能...................................................................................................................................... 15 4.6 智能锂电...................................................................................................................................... 16 4.7 智能运维...................................................................................................................................... 16

不同场景下5G电源部署解决方案

不同场景下5G电源部署解决方案基于客户需求及面临的挑战,5G部署存在多种场景:存量站点升级改造或叠加、新建或搬迁站,点、小站等多个场景。

基于“极简”、“智能”、“高效”的理念,针对不同场景提出最优解决方案。

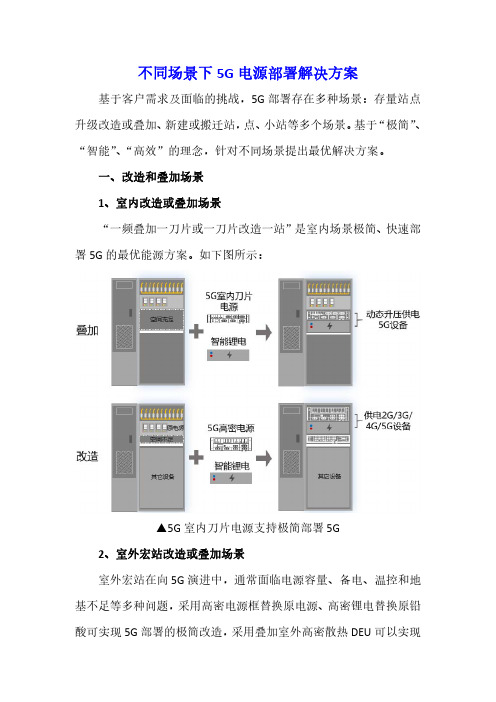

一、改造和叠加场景1、室内改造或叠加场景“一频叠加一刀片或一刀片改造一站”是室内场景极简、快速部署5G的最优能源方案。

如下图所示:▲5G室内刀片电源支持极简部署5G2、室外宏站改造或叠加场景室外宏站在向5G演进中,通常面临电源容量、备电、温控和地基不足等多种问题,采用高密电源框替换原电源、高密锂电替换原铅酸可实现5G部署的极简改造,采用叠加室外高密散热DEU可以实现不增机柜/免土建收容5G BBU。

方案如下图所示:▲高密电源、高密锂电、高密温控实现极简改造或叠加3、室外AAU叠加场景在5G AAU拉远场景下只考虑AAU供备电,高防护等级的全系列室外刀片可实现与AAU同场景应用,支持零占地极简部署。

方案如下图所示:▲全系列室外刀片电源支持极简叠加AAU二、新建或搬迁场景针对新建或搬迁站点,在2G/3G/4G基础上,需要考虑向5G平滑演进,“一站一柜”是全场景新建或搬迁的理想模式。

1、室外场景一站一柜兼容2G/3G/4G,支持功率、配电、备电、温控向5G平滑演进。

方案如下图所示:▲室外场景新建5G智能电源支持平滑演进2、室内场景一站一柜兼容2G/3G/4G,支持功率、配电、备电向5G平滑演进。

方案如下图所示:▲室内场景新建5G智能电源支持平滑演进三、小站场景小站设备安装灵活,场景多样,配套采用体积小、重量轻的刀片电源,支持抱杆/挂墙等多场景的安装,设备与环境实现完美融合。

在5G时代,对于业务连续性的要求会增大,对小站供备电可靠性要求提升,电源需要备电接口,支持按需备电。

▲室内场景新建5G智能电源支持平滑演进。

5G-MEC方案赋能行业应用

数据来源:CEDA,安信证券研究中心

边缘计算潜力巨大

智慧港口

智感安防

智慧医疗

智能制造

智慧交通

电力能源

智能教育

1个业务运营中心

1000个边缘节点

100个行业应用

新媒体

+ M E C :乘势起航, 八大行业重点推广

10个业务孵化基地

创新产品研发不运营

网络和平台系统建维

技术试验和产品储备

打造全国运营队伍

+ M E C :智慧城市

智慧工地

广州

深圳

完成广州、深圳等超10个边缘云节点建设,承载自动驾驶、智慧园区等10多个应用

自动驾驶智慧法院

智慧工业

智慧教育云游戏

智慧制造

智慧物业智能制造

珠海

佛山

湛江

中山

广东M E C 应用初显规模

时延降低43%下载速率提升9.29倍

直播内容本地分发 端到端时延降低65%

云端(公/私有云)APPPaaS(业务编排/生命周期管理)

IaaS(基础资源监控和管理)

基础设施(通用硬件)

端(终端设备)

企业园区

AR/VR

高清视频

车联网

协同

差异化体验

5G4GWiFi…业务诉求

中心MEC

200km~ 500km

50km

~

150km <30km

区域MEC

边缘MEC

核心

汇聚

接入

建设行业新生态

构筑商业新模式

广东运营中心助推

+ M E C 战略

规 建 维 研 运

端 管 边 云 协 同 满 足 丌 同 业 务 需 求

边缘云ME-APP ME-PaaS(ME-APP业务编排/生命周期管理/容器/微服务)ME-IaaS(计算、存储、网络等资源调度)

5G技术的低功耗通信

5G技术的低功耗通信随着科技的快速发展和人们对高速、高质量通信需求的不断增长,第五代移动通信技术(5G)已成为当前的热点话题。

在这个信息爆炸的时代,人们希望可以随时随地利用移动设备进行高速的数据传输和无缝连接,而5G技术正是应时而生。

然而,与以往不同的是,5G技术注重的不仅是高速通信,更是低功耗通信。

本文将简要介绍5G技术和其低功耗通信的基本原理。

一、5G技术概述5G技术作为第五代移动通信技术的代表,将带来前所未有的通信体验。

相较于前几代移动通信技术,5G技术具有更高的数据传输速度、更低的延迟和更大的网络容量,可以更好地支持各类应用场景,如智能家居、工业自动化、自动驾驶等。

二、低功耗通信的重要性随着各类移动设备的普及和互联网的蓬勃发展,人们对通信服务的需求越来越高。

然而,传统的通信技术在实现高速通信的同时却牺牲了大量的能源消耗,这对环境和可持续发展带来了一定的压力。

因此,低功耗通信成为5G技术中不可或缺的一部分。

三、5G技术的低功耗通信原理1. 省电型硬件设计:5G技术采用了新一代的通信芯片和射频模块,能够更有效地管理能源消耗,降低功耗并延长设备的续航时间。

2. 智能省电机制:5G技术中的智能省电机制能够根据网络负载和使用情况来动态调整功率,以最小化能源消耗,并确保通信的稳定性和可靠性。

3. 网络优化与协议改进:5G技术通过优化网络架构和对通信协议进行改进来实现低功耗通信。

例如,引入了多用户接入技术,使多个设备能够在同一频段上同时通信,减少了设备之间的干扰和能源消耗。

4. 能源管理系统:5G技术引入了先进的能源管理系统,对设备的能源消耗进行精确监控和管理,通过合理调配资源和控制功耗,实现了低功耗通信。

四、低功耗通信的优势1. 环境友好:低功耗通信可以减少能源消耗和碳排放,对环境具有积极影响。

2. 节能经济:低功耗通信可以降低设备的能源消耗和维护成本,为用户和企业节省了大量的开支。

3. 长续航时间:低功耗通信使移动设备能够更长时间地使用而不需要频繁充电,提升了用户的使用体验和便利性。

5G网络完整技术结构及应用

主要内容

• 模块一:架构篇—5G网络系统架构及网元设备组成 • 模块二:无线网—5G无线网架构及技术原理与应用 • 模块三:核心网—5G核心网架构及技术原理与应用 • 模块四:承载网—5G承载网架构及技术原理与应用 • 模块五:设备篇—5G网络基站设备介绍及安装示例 • 模块六:建设篇—5G网络建设与部署方案实例分析 • 模块七:物联篇—5G物联网的体系架构及关键技术 • 模块八:终端篇—5G物联网终端、芯片与模组介绍 • 模块九:应用篇—5G物联网的行业应用与典型案例 • 模块十:项目篇—5G物联网的项目规划与设计方法

• gNB:NR Node B(NR基站)

• NR:新无线

第12页

5G网络与4G网络的关键需求差异对比分析

功耗需求 前传带宽需求 回传带宽需求 回传端口需求

时延需求

时间同步需求 L3需求 切片需求

5G网络

5倍左右 25GE/2*10GE/100GE

3-5G DU 10GE上联端口

根据业务差异明显,大量业 务对时延要求≦10ms

5G物联网关键技术与应用

第1页

问题与思考

• 5G网络采用全新的、革命性的、全IT技术架构重构未来网络,以用户和业务需求为 导向、以云架构为基础设施搭建下一代智能IT平台,构建全联接型社会。

• 5G网络的发展目标是做强移动互联网,做大移动物联网,主要面向增强移动宽带 (eMBB)(面向人)、海量机器类型通信(mMTC)(面向物联网)与超高可靠 低时延(uRLLC)(面向工业互联网)三大应用场景。

(3)分布式部署

边缘TIC

TIC:形成网络基

础设施资源池,承

载不同网络功能。

接入层

50GE/100GE

DU 10GE

《5G车联网与终端直通》笔记

《5G车联网与终端直通》读书随笔目录一、内容概括 (2)1.1 车联网的发展背景 (2)1.2 5G技术的特点与应用 (4)1.3 终端直通的概念与重要性 (5)二、5G技术在车联网中的应用 (7)2.1 5G网络的高速率与低延迟特性 (8)2.2 V2X(车与一切的通信)技术 (9)2.3 车联网的安全性与隐私保护 (11)2.4 5G在智能交通系统中的作用 (12)三、终端直通的技术实现 (13)3.1 终端设备的演变与智能化 (14)3.2 车载通信模块的技术发展 (15)3.3 终端直通的协议与标准 (16)3.4 实时性与稳定性的保障措施 (18)四、5G车联网的实际应用场景 (19)4.1 智慧交通与自动驾驶 (21)4.2 车联网在智能物流中的应用 (22)4.3 公共安全与应急响应 (24)4.4 车联网在智慧城市建设中的角色 (25)五、面临的挑战与未来展望 (27)5.1 技术与标准化的挑战 (28)5.2 数据安全与隐私保护的挑战 (29)5.3 商业模式与市场接受度的挑战 (30)5.4 未来发展趋势与机遇 (32)六、结论 (33)6.1 5G车联网与终端直通的重要意义 (34)6.2 对未来车联网产业的期待 (36)一、内容概括《5G车联网与终端直通》是一本关于5G车联网技术的专著,作者通过对5G车联网的原理、关键技术、应用场景等方面进行了深入剖析,旨在为读者提供一个全面了解5G车联网发展的视角。

本书共分为五个部分:第一部分主要介绍了5G车联网的基本概念和发展历程;第二部分重点阐述了5G车联网的关键技术,如边缘计算、低延迟、高可靠性等;第三部分详细分析了5G车联网在智能交通、自动驾驶。

展示了5G车联网在国内外的成功案例和挑战。

通过阅读本书,读者可以全面了解5G车联网的技术特点、应用前景以及面临的挑战,为进一步研究和应用5G车联网技术奠定坚实的基础。

1.1 车联网的发展背景随着科技的飞速发展和人们生活水平的不断提高,汽车行业正在经历一场前所未有的变革。

瑞智联方案原理

瑞智联方案原理瑞智联方案是一种基于物联网技术的智能家居解决方案,通过将各种家居设备连接到互联网上,实现设备之间的互联互通,从而实现家居的智能化控制和管理。

该方案的原理主要包括设备连接、数据传输、数据处理和智能控制四个方面。

设备连接是瑞智联方案的基础。

通过将各种家居设备连接到互联网上,可以实现设备之间的数据交换和互动。

这些设备可以包括智能灯具、智能插座、智能门锁、智能家电等,通过无线通信技术(如Wi-Fi、蓝牙、ZigBee等)将设备与网关连接起来,形成一个智能家居网络。

数据传输是瑞智联方案的核心。

通过设备之间的数据传输,可以实现设备之间的信息交换和共享。

当用户通过智能手机或其他终端设备发送指令时,这些指令会通过互联网传输到对应的设备,然后设备根据指令执行相应的操作。

同时,设备之间也可以通过数据传输来实现联动控制,例如当门锁打开时,可以自动开启灯光。

第三,数据处理是瑞智联方案的关键。

通过对设备传输的数据进行处理和分析,可以提取有用的信息,并进行智能化的决策和控制。

例如,通过分析家庭成员的作息规律和生活习惯,系统可以自动调节室内温度和照明亮度,提高居住的舒适性和节能效果。

同时,系统还可以根据用户的需求和偏好,自动推荐适合的音乐、电影等娱乐内容。

智能控制是瑞智联方案的目标。

通过上述的设备连接、数据传输和数据处理,系统可以实现对家居设备的智能化控制。

用户可以通过智能手机、智能音箱等终端设备,随时随地对家居设备进行控制和管理。

例如,在离家时可以通过手机远程关闭电器设备,确保家庭安全;在回家时可以通过语音指令打开门锁和灯光,提高生活便利性。

瑞智联方案通过设备连接、数据传输、数据处理和智能控制等环节,实现了家居的智能化管理和控制。

通过该方案,用户可以随时随地对家居设备进行控制,提高生活的便利性和舒适性。

同时,瑞智联方案也为家居设备制造商和服务提供商提供了一个可靠和安全的物联网平台,推动了智能家居产业的发展和创新。

AItairLTE芯片组集成到君正“冰淇淋三明治”平板电脑

经 验 以 及 来 自 A M 的 高 性 能 、高 效 率 处 理器 和 R

G U技术 的结合 , P 使得该平台能够提供令 人着迷的

3 D游戏 效果 和 流畅 的高 清视 频播 放 , 日具有 丰 富 并 .

的存 储 器接 口和外设 。 ( 自瑞 芯微 电子 ) 来

为筹备主办奥运会和残奥会所实施 的数字电视转换 升级 ,相信 T l n V将可帮助英国和欧洲的数百 ai T kg 万人士欣赏到奥运 比赛 。( 自 O en l 公司 ) 来 ca u Be

电脑制造商降低设计复杂性 , 加快产品 市时问 , 从

而更 好 地满 足快 速变 化 的消 费者 需求 。

瑞 芯微 电子 在移 动互 联 『终 端 市场领 , 的设 计 x x j 尢

开发 的技 术 的进 阶版 本 ,而且 即将还 会集 成 到

D B T reiwS B中。 项技 术 的发 布恰 逢英 国 V — 2Fev T e 这

到 90 z WC) 预计 2 l 第二 季 度 流 片 结束 0 MH ( , 02年 后 , 测结 果将 达 到 1 G z 【 F中芯 同际 ) 实 . H。 来 1 0

瑞 芯 获 得 A M l 权 用 于 为 A d o R P授 n ri d 平板 电脑 提 供 T r e 解 决 方 案 u nK y

集 成 到 君 正 集 成 电路 的 MIS B sdA o 。 . P — ae nri。 0 t d 4 “ 冰淇 淋 明治 ” 平 板 电脑 中 。结合 两家 公 司的处 理 器 ,可使 这款 新 型平 板 电脑成 为伞球第 一台基带 和 应 用 程 序 处 理 器 都 是 采 用 MIS架 构 的 移 动 设 P

四核 Ma  ̄ 4 0M P 以 及用 于 C d X A l - 0 PG U、 i o e — 9处 理 器 的 A M A t a ̄ 物 理 I 理 器优 化包 。R 3 x R r sn i P处 K 0x 是一 个 T r e 决 疗案 ,能 够 帮助 A dod 板 unK y解 n ri 平

5G赋能智慧电力行业场景应用

5G赋能智慧电力行业场景应用目录1. 5G驱动下的电力行业发展 (1)2. 5G电力行业主要应用场景 (2)2.1 控制类业务 (2)2.1.1精准负荷控制 (2)2.1.2配网差动保护业务 (4)2.2 采集类业务 (6)2.3 移动应用类业务 (8)2.4 电网新型业务 (9)1. 5G驱动下的电力行业发展在数字信息技术发展,未来大部分的电力场景将搭建在能源互联网之上,能量像信息一样在网络中随时随地产生和共享,其发展呈现出新的趋势和特征:发电清洁友好,融合多种清洁分布式电源,融合储能和电动汽车,融合分散可靠负荷,具备清洁低碳、网源协同、灵活高效的特征;输变电安全高效,具备态势感知、柔性可靠、协调优化的特征;配电灵活可靠,具备可观可控、开放兼容、经济适用的特征;用电多样互动,具备多元友好、双向互动、灵活多样、节约高效的特征。

通信技术是各项数字技术在电力行业应用的基础,是发展能源互联网的技术支撑。

目前,电网可以通过不同类型的通信网络进行互联,但日益多样化的电力需求需要一个更精密、包容和创新的系统以满足海量设备互联互通和数据传输。

5G 定义的三大场景——增强移动带宽(eMBB)、超可靠低时延通信(uRLLC)和大规模机器通信(mMTC),具备超高带宽、超低时延、超大连接的技术特点。

在电力系统的发电、输电、变电、配电、用电、调度,以及应急通信各个环节,均可发挥重要作用,能够深刻变革电力通信网,全面提升电力信息化水平。

根据相关行业估算,到2026年,5G将为全球十个主要产业带来万亿级美元的数字化市场规模,其中能源产业和公用事业(水、电、燃气等)占比最高,约为 19%。

从电力行业出发,5G通信特点与电力通信网络需求高度契合。

5G网络技术的峰值速率、区域速率、边缘速率,都比4G大幅提高。

5G峰值速率最高可达20Gbps,满足高清视频、虚拟现实等数据的大量传输。

5G的通信时延比4G少一个数量级,空中接口的时延在1ms左右,因此为电力差动保护、精准切负荷等超低时延业务应用创造了条件。

华为5G节能解决方案

5G 叠加建网,节能的同时需确保业务体验节能挑战•闲时休眠节能•降低空载功耗5G•需充分考虑制式、频段间的协同4G 3G 5G AAU 5G BBU 2G华为节能规划方向通过系统的解决方案,从设备、站点、网络三个级别,能效提升,降低能耗,构建低成本高效能的绿色网络设备级节能:工艺创新、极低功耗站点级节能:极简形态、能耗优化网络级节能:多网协同、动态调优设备级节能:材料、工艺新技术持续应用超高效绿色节能技术超宽带高集成,新工艺新型滤波器技术新型散热技术金属腔体滤波器陶瓷滤波器中频芯片/基带芯片等创新的散热技术,效率提升“主齿导热、副齿散热、烟囱强化对流”的仿生设计原理;华为在5G 产品研发与工程化过程中做了大量的创新,整体上实现5G 单站能耗优业界平均水平站点级节能:智能削峰协同调度,免市电改造免交流改造1234减少配置三相平衡释放储能价值节省3-6月改造周期及$10K 费用设备配置从峰值降为常规值避免每相带载不均衡拖垮市电不影响生命周期之下最大化备电电池价值智能削峰案例站点功耗曲线20kVA16kVACAPEX 细项Cost(¥)空开改造2,019变压器& 线缆50,027人工费用50,479CAPEX: $16k ↘1.5k TTM: 3mouths ↘3days网络级节能:实现最优节能和最佳网络体验的平衡典型网络典型场景场景忙闲话务特征差异大,节能策略如何匹配节能理念及关注点分析无线典型业务场景,识别网络话务模型及节能依赖,输出场景化节能策略有明显的潮汐效应,夜间话务低,用户体验要求高商业区居民区全天话务量大,话务波峰波谷不明显,对容量要求高郊区话务量低,站点稀疏,覆盖远,站点容量较低充分考虑网络间不同制式不同频段的协同,以及室内覆盖节能,提升节能广度及深度;降能耗的同时,在策略设计上需要识别网络忙闲时KPI走势及基线,保证节能的同时不影响KPI①②③场景化策略话务、体验、能耗平衡网络、站点协同00:0000:0000:0012:0012:00闲时低流量时间段,站点能耗居高不下,不随业务变化06:0006:00分层分级的节能技术应用,有效降低网络闲时能耗64T64R->32T32R->16T16R话务潮汐效应较明显的区域(学校、城区)基于不同话务场景,应用不同节能技术、动态设置节能门限TX RX 高速接口模块扩展接口PA LNA 双工器电源模块LTENR在线平台LTENR根据5G 话务情况,设置关断策协同与深度节能技术深度休眠当当通过UE 功耗一站一策,持续调优,节能效果10%+OMC策略下发使能,合适站点、合适时间、多网协同。

Lattice ECP5和ECP5-5GFPGA系列VIP处理器解决方案

lattice公司的ECP5/ECP5-5G FPGA系列提供了高性能特性如增强DSP架构,高速SERDES和高速源同步接口,采用40nm技术,使得器件非常适合于量大高速和低成本的应用.器件的查找表(LUT)高达48K逻辑单元,支持多达365个用户I/O,提供多达156个18x18乘法器和各种并行I/O标准,采用可配置SRAM逻辑技术,提供基于LUT的逻辑,分布式和嵌入式存储器,锁相环(PLL),延迟锁定环(DLL),支持预制源同步I/O,增强sysDSP slices和高挡配置,包括加密和双引导功能.本文介绍了ECP5和ECP5-5G FPGA系列主要特性,LFE5UM/LFE5UM5G-85器件简化框图以及ECP5 VIP 处理器板主要特性,框图,电路图和材料清单.The ECP5/ECP5-5G family of FPGA devices is optimized to deliver high performance features such as an enhanced DSP architecture, high speed SERDES (Serializer/Deserializer), and high speed source synchronousinterfaces, in an economical FPGA fabric. This combination is achievedthrough advances in device architecture and the use of 40 nm technology making the devices suitable for high-volume, high-speed, and low-costapplications.The ECP5/ECP5-5G device family covers look-up-table (LUT) capacity to 84K logic elements and supports up to 365 user I/Os. The ECP5/ECP5-5G device family also offers up to 156 18 x 18 multipliers and a wide range of parallel I/O standards.The ECP5/ECP5-5G FPGA fabric is optimized high performance with low power and low cost in mind.The ECP5/ ECP5-5G devices utilize reconfigurable SRAM logictechnology and provide popular building blocks such as LUT-basedlogic, distributed and embedded memory, Phase-Locked Loops (PLLs),Delay-Locked Loops (DLLs), pre-engineered source synchronous I/Osupport, enhanced sysDSP slices and advanced configuration support,including encryption and dual-boot capabilities.The pre-engineered source synchronous logic implemented in theECP5/ECP5-5G device family supports a broad range of interface standards including DDR2/3, LPDDR2/3, XGMII, and 7:1 LVDS.The ECP5/ECP5-5G device family also features high speed SERDES with dedicated Physical Coding Sublayer (PCS) functions. High jitter tolerance and low transmit jitter allow the SERDES plus PCS blocks to be configured to support an array of popular data protocols including PCI Express,Ethernet (XAUI, GbE, and SGMII) and CPRI. Transmit De-emphasis with pre- and post-cursors, and Receive Equalization settings make the SERDESsuitable for transmission and reception over various forms of media.The ECP5/ECP5-5G devices also provide flexible, reliable and secureconfiguration options, such as dual-boot capability, bit-stream encryption, and TransFR field upgrade features.ECP5-5G family devices have made some enhancement in the SERDES compared to ECP5UM devices. These enhancements increase theperformance of the SERDES to up to 5 Gb/s data rate.Lattice ECP5和ECP5-5G FPGA系列VIP处理器解决方案The ECP5-5G family devices are pin-to-pin compatible with theECP5UM devices. These allows a migration path for users to port designs from ECP5UM to ECP5-5G devices to get higher performance.The Lattice Diamond™ design software allows large complex designs to be efficiently implemented using the ECP5/ECP5-5G FPGA family. Synthesis library support for ECP5/ECP5-5G devices is available for popular logicsynthesis tools. The Diamond tools use the synthesis tool output alongwith the constraints from its floor planning tools to place and route thedesign in the ECP5/ECP5-5G device. The tools extract the timing from the routing and back-annotate it into the design for timing verification.Lattice provides many pre-engineered IP (Intellectual Property)modules for the ECP5/ECP5-5G family. By using these configurable softcore IPs as standardized blocks, designers are free to concentrate on the unique aspects of their design, increasing their productivity.Each ECP5/ECP5-5G device contains an array of logic blockssurrounded by Programmable I/O Cells (PIC). Interspersed between therows of logic blocks are rows of sysMEM™ Embedded Block RAM (EBR) and rows of sysDSP™ Digital Signal Processing slices, as shown in Figure 2.1 on page 13. The LFE5-85 devices have three rows of DSP slices, the LFE5-45devices have two rows, and both LFE5-25 and LFE5-12 devices have one. In addition, the LFE5UM/LFE5UM5G devices contain SERDES Duals on thebottom of the device.The Programmable Functional Unit (PFU) contains the building blocks for logic, arithmetic, RAM and ROM functions. The PFU block is optimized for flexibility, allowing complex designs to be implemented quickly andefficiently. Logic Blocks are arranged in a two-dimensional array.The ECP5/ECP5-5G devices contain one or more rows of sysMEM EBR blocks. sysMEM EBRs are large, dedicated 18 Kb fast memory blocks. Each sysMEM block can be configured in a variety of depths and widths as RAM or ROM. In addition, ECP5/ECP5-5G devices contain up to three rows ofDSP slices. Each DSP slice has multipliers and adder/accumulators, which are the building blocks for complex signal processing capabilities.The ECP5 devices feature up to four embedded 3.2 Gb/s SERDESchannels, and the ECP5-5G devices feature up to four embedded 5 Gb/s SERDES channels. Each SERDES channel contains independent 8b/10bencoding / decoding, polarity adjust and elastic buffer logic. Each group of two SERDES channels, along with its Physical Coding Sublayer (PCS) block, creates a dual DCU (Dual Channel Unit). The functionality of theSERDES/PCS duals can be controlled by SRAM cell settings during device configuration or by registers that are addressable during device operation. The registers in every dual can be programmed via the SERDES ClientInterface (SCI). These DCUs (up to two) are located at the bottom of thedevices.Each PIC block encompasses two PIOs (PIO pairs) with their respective sysI/O buffers. The sysI/O buffers of the ECP5/ECP5-5G devices arearranged in seven banks (eight banks for LFE5-85 devices in caBGA756 and caBGA554 packages), allowing the implementation of a wide variety of I/O standards. One of these banks (Bank 8) is shared with the programminginterfaces. Half of the PIO pairs on the left and right edges of the devicecan be configured as LVDS transmit pairs, and all pairs on left and right can be configured as LVDS receive pairs. The PIC logic in the left and rightbanks also includes pre-engineered support to aid in the implementation of high speed source synchronous standards such as XGMII, 7:1 LVDS,along with memory interfaces including DDR3 and LPDDR3.The ECP5/ECP5-5G registers in PFU and sysI/O can be configured to be SET or RESET. After power up and the device is configured, it enters intouser mode with these registers SET/RESET according to the configuration setting, allowing the device entering to a known state for predictablesystem function.Other blocks provided include PLLs, DLLs and configuration functions. The ECP5/ECP5-5G architecture provides up to four Delay-Locked Loops (DLLs) and up to four Phase-Locked Loops (PLLs). The PLL and DLL blocks are located at the corners of each device.The configuration block that supports features such as configurationbit-stream decryption, transparent updates and dual-boot support islocated at the bottom of each device, to the left of the SERDES blocks.Every device in the ECP5/ECP5-5G family supports a sysCONFIG™ ports located in that same corner, powered by Vccio8, allowing for serial orparallel device configuration.In addition, every device in the family has a JTAG port. This family also provides an on-chip oscillator and soft error detect capability. The ECP5devices use 1.1 V and ECP5UM5G devices use 1.2 V as their core voltage. ECP5和ECP5-5G FPGA系列主要特性:Higher Logic Density for Increased System Integration12K to 84K LUTs197 to 365 user programmable I/OsEmbedded SERDES270 Mb/s, up to 3.2 Gb/s, SERDES interface(ECP5)270 Mb/s, up to 5.0 Gb/s, SERDES interface (ECP5-5G)Supports eDP in RDR (1.62 Gb/s) and HDR (2.7 Gb/s)Up to four channels per device: PCI Express, Ethernet (1GbE, SGMII, XAUI), and CPRI sysDSP™Fullycascadable slice architecture12 to 160 slices for high performance multiply and accumulatePowerful 54-bit ALU operationsTime Division Multiplexing MAC SharingRounding and truncationEach slice supportsHalf 36 x 36, two 18 x 18 or four 9 x 9 multipliersAdvanced 18 x 36 MAC and 18 x 18 Multiply-Multiply-Accumulate (MMAC) operations Flexible Memory ResourcesUp to 3.744 Mb sysMEM™ Embedded Block RAM (EBR)194K to 669K bits distributed RAMsysCLOCK Analog PLLs and DLLsFour DLLs and four PLLs in LFE5-45 and LFE5-85; two DLLs and two PLLs in LFE5-25 and LFE5-12Pre-Engineered Source Synchronous I/ODDR registers in I/O cellsDedicated read/write levelling functionalityDedicated gearing logicSource synchronous standards supportADC/DAC, 7:1 LVDS, XGMIIHigh Speed ADC/DAC devicesDedicated DDR2/DDR3 and LPDDR2/LPDDR3 memory support with DQS logic, up to 800 Mb/s data-rateProgrammable sysI/O™ Buffer Supports Wide Range of InterfacesOn-chip terminationLVTTL and LVCMOS 33/25/18/15/12SSTL 18/15 I, IIHSUL12LVDS, Bus-LVDS, LVPECL, RSDS, MLVDS subLVDS and SLVS, MIPI D-PHY input interfacesFlexible Device ConfigurationShared bank for configuration I/OsSPI boot flash interfaceDual-boot images supportedSlave SPITransFR™ I/O for simple field updatesSingle Event Upset (SEU) Mitigation SupportSoft Error Detect – Embedded hard macroSoft Error Correction – Without stopping user operationSoft Error Injection – Emulate SEU event to debug system error handling System Level SupportIEEE 1149.1 and IEEE 1532 compliantReveal Logic AnalyzerOn-chip oscillator for initialization and general use1.1 V core power supply for ECP5, 1.2 V core power supply for ECP5UM5G图1. LFE5UM/LFE5UM5G-85器件简化框图ECP5 VIP 处理器板This document describes the Lattice Semiconductor ECP5 VIP Processor Board which is a key component of Lattice’s Video Interface Platform (VIP) board interconnect. Lattice VIP boards can be interconnected to create solutions for MIPI® CSI-2/DSI, SERDES, LVDS and more.The content of this user guide includes descriptions of onboard jumper settings, programming circuit, a complete set of schematics, and bill of materials for ECP5 VIP processor board.ECP5 VIP 处理器板主要特性:ECP5/5G SERDES interface Dual DDR3 interfaceLVDS/MIPI Transmitter/Receiver interface SPI flash configuration General Purpose Input/Output Programming CircuitMini-B USB connector to FTDI FTDI to ECP5 using JTAG FTDI to ispClock using JTAG ispClockSERDES reference clock generation interface图2:ECP5 VIP 处理器板主要元件分布图(顶层)图4:ECP5 VIP 处理器板可编程框图Array图3:ECP5 VIP 处理器板主要元件分布图(底层)图5:ECP5 VIP 处理器板框图图6:ECP5 VIP 处理器板电路图(1):FTDI 和编程接口图7:ECP5 VIP 处理器板电路图(2):电源稳压器接口。

5G锚点相关规划原则-重要ppt模板

典型移动性场景#2- MeNB站内/站间移动性管理

LTE和NR在相同的MeNB内或不同的MeNB间时,该功能可以提供灵活的移动性管理策略。

①

LTE MeNB 1 NR SgNB 1

②

NR SgNB2

① Intra-MN Handover without SN Change 辅节点不变的主节点站内切换

• 高通X50/X55芯片支持850M/900M /1.8G /2.1G /2.6G 这些全球广泛应用的LTE频点 作为锚点,下面仅列举部分组合

• DC_1A _n77A/n78A/n79A • DC_3A_ _n77A/n78A/n79A • DC_5A_n78A • DC_7A/7C_n78A • DC_8A_n78A

④Inter-MN Handover with SN Change 主节点站间切换,辅节点变更

典型移动性管理#3- MeNB和eNB间的移动性管理

如果某些基站不支持NSA功能,则此功能MeNB和eNB之间的服务连续性提供移动性管理。

MN

LTE覆盖

SN

NR覆盖

LTE MeNB 1 NR SgNB 1

NR

Anchor LTE Non-Anchor LTE

频点优选策略

• 原有4G流程保持不变

NSA UE

• 尽量切到锚点小区 • NSA用户专用频选优先级,优选锚点小区驻留

连接态

负荷均衡策略

• LTE锚点网络负荷高时,优先对普 通UE进行负荷均衡,将普通UE从 锚点网络切到非锚点网络

• 连接态业务建立后:如非锚点小区有锚点邻区,则尽量 将NSA UE切换到锚点小区,便于触发EN-DC双链接

LTE ? CSFB方案

itu在5g mec和5g移动通信方面工作的内容

itu在5g mec和5g移动通信方面工作的内容ITU作为国际电信联盟,致力于推动和规范全球电信和信息通信技术的发展。

在5G MEC(多边缘计算)和5G移动通信方面,ITU扮演着重要的角色。

首先,ITU在5G MEC方面的工作主要包括如下几个方面:1.标准制定:ITU在5G MEC标准化方面发挥了重要作用。

ITU-T (ITU电信标准化部门)制定和更新一系列5G MEC相关的国际标准。

这些标准将帮助促进5G MEC的全球部署和互操作性,为行业提供参考和指导。

2.技术研究和推进:ITU开展了大量的研究和实验工作,以推动5G MEC技术的发展。

ITU组织了技术论坛、研讨会和研究组,使各国专家和科研机构能够共享技术进展和最佳实践。

3.频谱管理:ITU负责管理和分配无线电频谱资源,以支持5G MEC的全球发展。

ITU通过协调各国政府、无线电频谱管理机构和运营商的合作,确保全球5G MEC设备和系统的频谱需求得到满足。

4.测试和验证:ITU还致力于制定5G MEC设备和系统的测试和验证规范。

这些规范将有助于确保5G MEC设备和系统的互操作性和性能,并为行业提供可靠的技术基础。

5.制定政策和规章制度:ITU通过国际会议和研讨会,为各国政府和利益相关方提供政策制定的建议和指导。

ITU通过制定政策和规章制度,促进5G MEC在全球范围内的部署和应用。

其次,ITU在5G移动通信方面的工作主要包括如下几个方面:1. 5G标准制定:ITU-T负责制定5G移动通信的国际标准。

ITU-T将各国提出的需求和技术方案进行协调和整合,制定出符合全球需求的5G移动通信标准,以推动全球范围内5G移动通信的发展和应用。

2.频谱管理:ITU负责协调全球范围内的无线电频谱资源的分配和利用,以支持5G移动通信的发展。

ITU通过制定和更新频谱管理规定,确保5G移动通信设备和系统能够获得可靠的频谱资源支持。

3.技术研究和推进:ITU通过开展技术研究和实验,推动5G移动通信的技术创新和进步。

5G新基建背景下MEC系统关键技术的应用

I G I T C W技术 应用Technology Application128DIGITCW2023.101 概述1.1 5G新基建5G 新基建是指在5G 技术基础上建设的新一代信息基础设施,包括5G 网络、5G 应用、5G 设备等。

5G 新基建是我国提出的重大战略,旨在推动数字经济发展、促进产业升级、提升国家竞争力。

5G 新基建的推进涉及基础设施建设、产业发展、人才培养、政策制定等多个方面。

目前,我国已经启动了5G 新基建计划,并陆续发布了一系列支持政策,吸引了众多企业和投资者的关注。

1.2 MEC系统关键技术MEC (Multi-access Edge Computing )系统是一种面向5G 网络的边缘计算技术,它在网络边缘部署计算、存储、网络等资源,提供低时延、高带宽的边缘计算服务,为5G 应用提供支持。

其主要是从移动核心网内将云平台迁移到移动接入网边缘,从而更加合理地实现计算资源、存储资源等的利用,实现传统运营商蜂窝网络与互联网等的更深度融合,提升移动用户的访问效率[1]。

1.2.1 整体架构如图1所示,在M E C 系统整体架构中的服务器是其核心,由多台或一台服务器组成,通过在无线接入网、核心网之间部署服务器,在网络近端的无线网络侧为客户提供高效、低延时的计算和存储等服务,提升移动终端用户的满意度。

M EC 服务器是由路由子系统、平台管理系统、能力开放子系统等组件组成,实现与无线接入网、企业网、软件基础环境等的相互融合,并进行数据信息动态交互。

MEC 系统的主要应用场景包括AR 、VR 视频、车辆网、辅助计算等。

比如在车辆网中,利用M EC 系统分析车辆及路测传感器的数据,可以将危险等时延敏感性信息分享给周边的车辆,有利于减少行车完全事故的发生概率,缓解交通拥堵等问题,具有较高的应用优势和前景。

5G新基建背景下MEC系统关键技术的应用杜玉红1,侯守明2(1.鹤壁职业技术学院,河南 鹤壁 458030;2.河南理工大学,河南 焦作 454003)摘要:文章阐述了5G新基建、MEC系统关键技术的内涵及其关键技术,分析了5G新基建背景下MEC系统关键技术面临的挑战,提出了5G新基建背景下MEC系统关键技术的应用方案。

Lattice ECP3-ECP5器件中的SerDes-PCS简要介绍

Lattice ECP3/ECP5 器件中的SerDes/PCS 简要介绍

FPGA 发展到今天,SerDes (Serializer - Deserializer) 基本上是标配了。

从PCI 到PCI Express,从ATA 到SATA,从并行ADC 接口到JESD204,从RIO 到Serial RIO,……等等,都是在借助SerDes 来提高性能。

SerDes 是非常复杂的数模混合设计,用户手册的内容只是描述了森林里面的一棵小树,

并不能够解释SerDes 是怎幺工作的。

而本文也主要是基于Lattice ECP3 和ECP5 的SerDes UG,来简单地介绍一下Lattice ECP3&ECP5 SerDes 的一些基本特性。

废话不多说,进入正题。

Lattice 的ECP3/ECP5 系列FPGA 内部集成了SerDes/PCS 的硬核(Hard Core),其速率最高可达3.2Gbps,而ECP5-5G 系列的SerDes 最高可达

5Gbps。

Lattice 的SerDes 是基于CML 信号的,借助PCS(物理编码子层,Physical Coding Sublayer)可以支持PCI Express、JESD204A/B、SD-SDI、HD-SDI、3G-SDI、GbE、CPRI、Gigabit Ethernet (1GbE and SGMII)和XAUI 等多种串行通信协议,具体如下图所示。

就PCIe(PCI Express)而言,ECP3/ECP5 可支持1.0/1.1 版本(2.5Gbps),而ECP5-5G 还可支持2.0 版本(5Gbps)。

借助Lattice 提供的。

莱迪思iCE40 Ultra和ECP5:满足多功能、灵活性设计需求

莱迪思iCE40 Ultra和ECP5:满足多功能、灵活性设计需求韩霜

【期刊名称】《世界电子元器件》

【年(卷),期】2014(0)9

【摘要】在低功耗、小尺寸、低成本FPGA领域,莱迪思(Lattice)半导体公司向来拥有自己的优势,从通信领域到消费电子领域,莱迪思在产品线扩展的同时,对客户的支持也愈加全面。

如今,莱迪思半导体可以为用户提供从基础设施到移动设备的适用于各大领域的客制化解决方案,包括:为通信应用提供低功耗、低成本、可替代ASIC和ASSP的新选择,实现智能的工业自动化、视频和图像处理应用,以及为消费类移动电子产品提供差异化功能。

莱迪思半导体公司总裁兼CEO Darin G.Billerbeck先生指出,公司在2013财年的营收实现了19%的增长,其中消费类电子产品市场营收增长了180%。

【总页数】1页(P43)

【作者】韩霜

【作者单位】

【正文语种】中文

【相关文献】

1.莱迪思iCE40 UltraLite FPGA推动移动应用优化 [J], 王颖

2.莱迪思半导体高效节能iCE40 UltraPlus FPGA器件 [J],

3.莱迪思针对可穿戴设备推出ICE40 ULTRA平台 [J],

4.莱迪思半导体宣布推出全新的iCE40 UltraPlus^TM器件 [J],

5.莱迪思推出用于可穿戴设备开发的ICE40 ULTRA平台 [J], 叶木子

因版权原因,仅展示原文概要,查看原文内容请购买。

5G优化案例创新“五阶十步”精细优化方法打造5G精品示范区

5G优化案例创新“五阶十步”精细优化方法打造5G精品示范区随着5G技术的不断发展,各行各业都在积极探索如何利用5G技术实现创新和提升效率。

而在5G网络优化方面,如何有效地实施精细优化,打造出更加优质的5G网络示范区,是当前亟待解决的重要问题。

一、前期准备阶段:1.确定目标:明确5G网络优化的目标和需求,同时确定精细优化的范围和重点。

2.调研分析:对5G网络的现状进行全面调研和分析,了解网络问题和瓶颈,并对网络资源和性能进行评估。

3.制定规划:根据调研结果,制定5G网络优化的具体规划和实施方案,明确优化的策略和措施。

二、精细调优阶段:4.调整参数:根据规划方案,对5G网络的参数进行调整和优化,包括信道设置、功率控制、频率规划等。

5.优化频谱:对5G网络的频谱资源进行优化利用,确保信号传输质量和覆盖范围。

6.优化接入:优化5G网络的接入设备和接入方式,提高用户接入速度和稳定性。

7.优化传输:对5G网络的传输链路进行优化,提高数据传输效率和稳定性。

8.优化核心网:对5G核心网进行优化,提高数据处理能力和响应速度。

9.优化终端:优化5G终端设备和协议,提高用户体验和设备性能。

三、监测调优阶段:10.系统优化:建立5G网络优化的监测系统,实时监测网络性能和用户体验,及时调整优化策略和措施。

11.用户体验:定期对用户体验进行调查和评估,根据用户反馈对网络进行调优和改进。

12.故障处理:建立快速故障处理机制,及时处理网络故障和问题,确保5G网络稳定运行。

四、总结完善阶段:13.优化总结:结合实际效果和用户反馈,总结5G网络优化的经验和教训,不断完善优化方案。

14.技术升级:随着技术的不断发展,及时跟进5G技术的最新进展,不断提升网络性能和服务质量。

15.成果展示:及时展示5G网络优化的成果和效果,吸引更多用户和企业参与和合作。

通过以上“五阶十步”的精细优化方法,我们可以有效地打造出5G 精品示范区,为各地区提供优质的5G网络服务和体验,推动5G技术在各行各业的广泛应用和发展。

智能制造中的5G通信技术应用案例分析

智能制造中的5G通信技术应用案例分析5G通信技术是当前智能制造领域中一项重要的技术创新,它可以实现高速、低延迟和大容量的通信传输,为智能制造提供了强有力的支持。

本文将结合实际案例,探讨在智能制造中5G通信技术的应用。

一、智能工厂的无线控制网络在传统的制造工厂中,通常采用有线方式进行设备之间和设备与控制中心之间的通信,但是这种布线方式成本高、维护不方便,不适应快速变化的制造环境。

而引入5G通信技术后,可以建立无线控制网络,实现设备之间的实时通信,提高生产效率和灵活性。

以某汽车制造厂为例,该厂引入了5G通信技术,实现了完全的无线控制网络覆盖。

通过5G通信技术,不同车间的设备可以实时进行数据交换和通信,提高了制造过程的协同性和智能化水平。

例如,在生产线上,通过5G通信技术可以实现对机器人的远程控制和调度,大大提高了生产线的运行效率。

二、智能物流管理系统在智能制造中,物流管理是一个关键的环节,它涉及到物料的采购、储存、运输和交付等多个环节。

而随着制造过程的数字化和智能化,物流管理也需要更高效、更精准的通信技术来支持。

5G通信技术的引入,为智能物流管理系统提供了强大的支持。

以某电子产品制造企业为例,该企业采用了基于5G通信技术的智能物流管理系统。

通过5G通信技术,企业可以实时监控物料的仓储情况、运输状态及交付进度,并对整个物流过程进行智能调度和优化。

这样可以提高物流效率,减少运营成本,提高客户满意度。

三、智能设备远程维护在传统的制造环境中,设备的维护通常需要现场工程师到达现场进行,存在效率低、成本高的问题。

而通过5G通信技术,可以实现智能设备的远程维护,大大提高维护效率和降低成本。

以某化工企业为例,该企业生产过程中涉及到大量的设备,维护工作较为繁琐。

但是通过引入5G通信技术,企业可以实现远程监控和维护。

工程师可以通过远程连接设备,实时监测设备的运行状态,进行故障诊断和排除,并做出相应的维护计划。

通过5G通信技术,企业可以实现设备的及时维护,减少停机时间,提高生产效率。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

lattice公司的ECP5-5G系列是支持5G SERDES和有多达85K LUT的FPGA,支持的5G协议包括PCI Express Gen 2.0, CPRI和JESD204B,能无缝地连接

到ASIC和ASSP,主要应用包括照相机,显示器,游戏平台,小性和低端路由器本文介绍了ECP5-5G系列主要特性和优势,以及ECP5™ PCI Express板主要特性框图,电路图和材料清单.

Lattice’s ECP5-5G family is the only FPGA product line supporting 5G SERDES and up to 85K LUTs in a small 10x10 mm package. The ECP5-5G devices support multiple 5G protocols including PCI Express Gen 2.0, CPRI, and JESD204B. This product family enables seamless connectivity to ASICs and ASSPs in a wide array of applications including cameras, displays,

gaming platforms, small cells and low-end routers. Numerous resources including software, device samples, soft IP and hardware boards are

available upon request.

Designers of equipment for many emerging high volumeapplications are blending FPGAs with ASICs and ASSPs torapidly build flexible systems that meet tight cost, power and formfactor constraints. In developing the ECP5TM FPGA family, Latticebreaks the rule that all FPGAs should be the highest density,power hungry, and expensive. With a focus on compact,

highvolume applications, Lattice optimized the ECP5 architecture forlow cost, small form factor and low power consumption. Thesecharacteristics make the ECP5/ECP5-5G devices ideal fordelivering programmable

connectivity solutions to complementASICs and ASSPs.

With up to 85K LUTs, 3.7Mbits embedded memory, 156 sysDSP blocks with DDR support, four 3.2Gbps/5Gbps SERDES channelsand 365 user IO, the ECP5/ECP5-5G devices provide a low-cost solution that meets the

common connectivity requirements forcomplementing ASICs and ASSPs. A broad range of interface standards are supported including DDR3, LPDDR3, XGMII and7:1 LVDS, PCI Express, Ethernet (XAUI, GbE, SGMII) and CPRI. The devices are offered in multiple package options, and alsoinclude support for encryption and dual boot capabilities. Smart depopulation of balls

simplifies PCB board routing and reducescost by utilizing fewer layers. Low power enhancements include stand-by mode operation of the individual blocks including SERDES,dynamic IO bank controllers and reduced

operating voltage. The ECP5 family is supported by the Lattice DiamondTM designsoftware, the leading-edge design and implementation tool

optimized for cost sensitive, low-power Lattice FPGA architectures.

ECP5-5G系列主要特性和优势:

Cost Optimized Architecture

• Focused on providing best value below 100K LUTs.

• Smart ball depopulation simplifies package integration withexisting PCB technology.

• Double Data Rate capability improves DSP block utilization.

Small Packages with High Functional Density

Lattice ECP5-5G系列低功耗无缝连接解决方案

Low Power Consumption

• Single channel SERDES functions below 0.25W.

• Quad channel SERDES functions below 0.5W.

ECP5™ PCI Express板

The ECP5™ PCI Express Board allows designers to investigate and

experiment with the features of the ECP5 Field-Programmable Gate Array. The features of the ECP5 PCI Express Board can assist engineers with rapid prototyping and testing of their specific designs. The guide is intended to be referenced in conjunction with demo user’s guides to demonstrate the

ECP5 FPGA.

图1:ECP5™ PCI Express板外形图。