扫描驱动显示电路设计CPLD-3

基于CPLD的LED显示屏扫描控制模块的设计_图文(精)

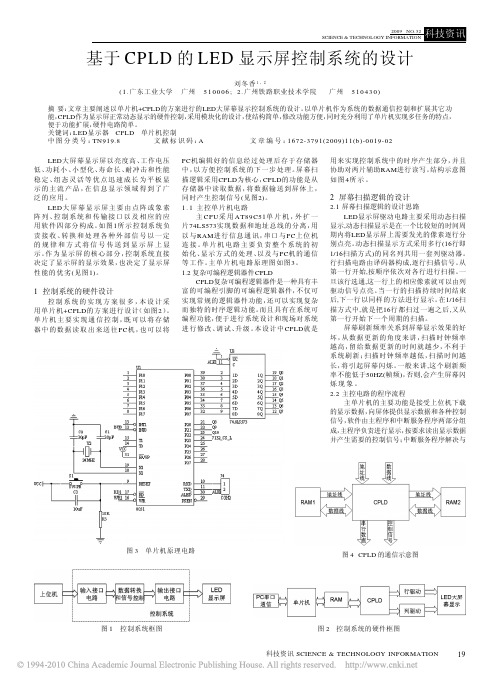

PLDCPLDFPGA应用中文核心期刊《微计算机信息》(嵌入式与SOC)2007年第23卷第6-2期文章编号:1008—0570(2007)06…2019803基于CPLD的LED显示屏扫描控制模块的设计DesignofTheScanningControlModuleofLEDScreenBasedonCPLDf广西大学)聂雄NIEXIONG摘要:基于AT89S52单片机和ATFl508AS可编程逻辑器件实现LED显示屏的硬件设计。

采用VerilogHDL对ATFl508AS进行编程,实现LED显示屏扫描控制模块的硬件描述语言程序设计。

ATFl508AS的应用,简化了LED显示屏的系统结构,提高了显示屏的刷新率。

关键字:V啦HDL;LED显示屏;双口RAM中图分类号:TN27文献标识码:BAbstract:TheLEDscreensystemisimplementedbasedonAT89S52andATFl508AS.VeilingHDLprogramofthescanningcontml-lingmoduleofLEDscreenisimplementedbasedonATFl508ASchip.TheusingofATFl508ASmakestheLEDscreensystemsim—pierandimprovesthescanningrate.Keyword:VerilogHDL,LEDscreen,Dual-PortedRAM引言LED显示屏主要由电流驱动电路及LED点阵阵列、控制系统和Pc端管理软件三部分构成(图1)。

控制系统负责接收、转换和处理各种外部信号,并实现扫描控制,然后驱动LED点阵显示需要的文字或图案。

控制系统作为LED显示屏的核心部分,直接决定了显示屏的显示效果和性能的优劣。

本文详细分析采用VerilogHDL对ATFl508AS进行编程,实现双口RAM访问和产生LED点阵驱动电路所需的各种时序信号。

cpld课程设计报告

cpld课程设计报告一、教学目标本课程的教学目标是让学生掌握CPLD(Complex Programmable Logic Device,复杂可编程逻辑器件)的基本原理、编程方法和应用技巧。

通过本课程的学习,学生应能理解CPLD的工作原理,熟练使用相关软件进行编程,并能够运用CPLD设计简单的数字电路系统。

1.了解CPLD的基本结构和工作原理。

2.掌握CPLD的编程语言和编程方法。

3.理解CPLD在数字电路设计中的应用。

4.能够使用CPLD相关软件进行编程。

5.能够设计简单的数字电路系统。

6.能够进行CPLD的硬件编程和调试。

情感态度价值观目标:1.培养学生对电子技术的兴趣和热情。

2.培养学生动手实践能力和团队协作精神。

3.培养学生勇于探索和创新的精神。

二、教学内容本课程的教学内容主要包括CPLD的基本原理、编程方法和应用。

1.CPLD的基本原理:介绍CPLD的基本结构、工作原理和特点。

2.CPLD的编程方法:介绍CPLD的编程语言、编程步骤和相关软件。

3.CPLD的应用:介绍CPLD在数字电路设计中的应用实例,如数字信号处理器、数字通信系统等。

三、教学方法为了提高教学效果,本课程将采用多种教学方法相结合的方式进行教学。

1.讲授法:通过讲解CPLD的基本原理、编程方法和应用,使学生掌握相关知识。

2.案例分析法:通过分析具体的CPLD应用实例,使学生更好地理解CPLD的应用。

3.实验法:安排实验室实践环节,让学生亲自动手进行CPLD编程和调试,提高学生的动手能力。

四、教学资源为了保证教学效果,我们将准备以下教学资源:1.教材:选择合适的教材,为学生提供全面、系统的学习资源。

2.参考书:提供相关的参考书籍,丰富学生的知识体系。

3.多媒体资料:制作课件、教学视频等多媒体资料,提高学生的学习兴趣。

4.实验设备:准备CPLD实验设备,为学生提供实践操作的机会。

五、教学评估本课程的评估方式将采用多元化、全过程的评价体系,以全面、客观、公正地评估学生的学习成果。

基于CPLD的彩色线阵CCD驱动设计

信 号 转移 到 相应 的移 位单 元 中 。S 为低 电平 时候 H 上 述转 移过 程完 成 ,光 敏单 元进 入下 一行周 期感 光

采取 自顶向下的设计方法。在完成程序 的输入 ,在 Q a u 软件平台进行编译和仿真从而验证设计的功 ur s t

占空 比约为 1 : 5的方波 ; 积分时间内,至少有 光 32 个 R 82 S脉冲。P I H 的频率 2MH ,占空比约为 5 z

1 的方波 ;但是其相位与 R 信号不 同。在保证基 : 5 S

4 2

长春理工大学学报( 自然科学版 )

2 1年 01

图 2 Qu r s 境下的原理 图 at 环 u

4 1

蓝 ;两相 5 V脉冲驱动 ,1 路驱动信号的最高频率 4

为 2MH ; 5 z 三色信号奇偶并行 ,共六路输出信号; 供电电源为 1V。扫描A 页面可以有 2 e m 2 3 4 i s m l / n

的分 辨力 。

1 驱 动 时序分 析 . 2

各时序信号的时间关系要求 。如 图 1 所示 ,规定了 这些时间意义 。注意 :在 “o ”标示 的时间内保 nt e

Ab t a t n o d rt e tt en e so o o c n ig l e ra r y CCD h p TCD2 0 D ,t i a e r s n sa d i i g s r c :I r e om e e d fc lrs a n n a ra h n i c i 73 h sp p r e e t r n p v pa rie l f n a CCD a e n CP D ,c mb n ss h mai dVHDL d sg g a et e i ed i e ,u e 4 n o l r b sdo L o ie e t a c cn e i n l u g d sg t rv r n a o n h s s7 AHC0 4

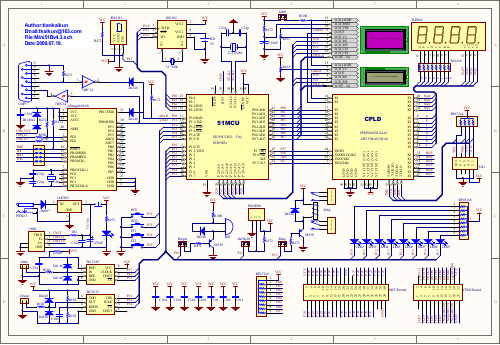

51单片机CPLD综合开发板完整电路图

IO IO IO IO

40 Seg4 39 Seg3 37 Seg2 36 Seg1

IO IO IO IO IO IO IO IO

8 5 11 12 9 6 4 14

p g f e d c b a

IO IO IO IO IO IO

33 34 31 29 28 27

IO33 IO34 IO31 IO29 IO28 IO27

XTAL2 XTAL1

P2.0/A8 P2.1/A9 P2.2/A10 P2.3/A11 P2.4/A12 P2.5/A13 P2.6/A14

EA/VP P VCC

P0.0/AD0 P0.1/AD1 P0.2/AD2 P0.3/AD3 P0.4/AD4 P0.5/AD5 P0.6/AD6 P0.7/AD7

22.1184M VCC

VCC R103

35 44

20 21

RST 10 GND

PSEN 32

R472

P40 23 P41 34 P42 1 P43 12

uRxD uTxD

P30 11 P31 13 P32 14 P33 15 P34 16 P35 17

P10 2 P11 3 P12 4 P13 5 P14 6 P15 7 P16 8 P17 9

B

JTAG VCC

TMS 13 TCK 32 TDO 38 TDI 7

P20 24 P21 25 P22 26 P23 27 P24 28 P25 29 P26 30

C

PWR2.5

LM7805

1 IN

OUT 3

D4007

GND

VCC R472

2 VC C in

USB1

VBUS DD+

基于CPLD的三相多波形函数发生器任务书

3 工艺制作任务

完成VHDL程序编写和下载;制作、调试CPLD下载板及调试程序;写出完整的设计说明书。

4 设计基本要求

设计出来的函数发生器功能数据基本符合技术指标;各种功能能够实现;论文撰写符合标准。

[5]蔡明生.电子设计[M].北京:高等教育出版社.2003

[6]李东升.电子设计自动化与IC设计[M].北京:高等教育出版社.2004

[7]李洋.EDA技术实用教程[M].北京:机械工业出版社.2005

2.毕业设计(论文)工作进度计划:

周 次

工作内容

早进入阶段

第1周

第2周

3-5周

6-8周

9-10周

毕业设计(论文)任务书

题目

(包括副标题)

基于CPLD的三相多波形函数发生器

XXX

学生姓名

XXX

学号

XXX

班级

XXX

成果形式

A论文B设计说明书C实物D软件E作品

□■■□■

任务下达时间

1.毕业设计(论文)课题任务的内容和要求:

1 应完成的任务

设计制作一个基于CPLD的三相多波形函数发生器,能输出正弦波、三角波、方波等波形的信号源电路,波形间的相位差均为120°。

2 主要技术指标

对三种波形的输出频率要求为:频率范围在20Hz-20kHz之间可调;三种波形之间的相位差均为120°。

a.对正弦波信号的要求为:步长为10Hz;频率稳定度:优于1/10000;非线性失真系数≤3%。

b.对方波信号的要求是:频率上升和下降时间<1µs;

可编程器件cpld-3

例如:

PROCESS(A,B,C,D) BEGIN D<=A; X<=B+D; D<=C; Y<=B+D; END PROCESS; 结果: X=B+C Y=B+C PROCESS(A,B,C) VARIABLE D:STD_LOGIC; BEGIN D:=A; X<=B+D; D:=C; Y<=B+D; END PROCESS; 结果: X=B+A Y=B+C

信号赋值语句表达式为: 目标信号名 <= 表达式;

符号 “<=” 表示赋值操作,即将数据信息传入。数据 信息传入时可以设置延时过程,这与器件的实际传播 延时十分接近。因此信号值的代入采用“<=”代入符, 而不是像变量赋值时那样用“:=”。 例如: a <= ‘1’; ; s1 <= s2 AFTER 10 ns; ;

例如:

architecture a of start is signal tmp : std_logic; begin process(a_bus) begin tmp <= '1'; for i in 3 downto 0 loop tmp <= a_bus(i) and tmp; end loop; carryout <= tmp; end process; end a; architecture a of start is begin process(a_bus) variable tmp:std_logic; begin tmp := '1'; for i in 3 downto 0 loop tmp := a_bus(i) and tmp; end loop; carryout <= tmp; end process; end a;

第1章cpld学习教程课件

PLD的分类

• CPLD/FPGA不仅受到系统设计者的青睐, 而且在半导体领域中呈现出一支独秀的增 长态势,成为系统级平台设计的首选。随 着PLD向更高速、更高集成度、更强功能 和更灵活的方向发展,使CPLD/FPGA器件 既适用于短研制周期、小批量产品开发, 也可用于大批量产品的样品研制,且项目 开发前期费用低,开发时间短,有利于新 产品占领市场,是目前ASIC设计所使用的 最主要的器件。

第1章cpld学习教程

2023/10/8

第1章cpld学习教程

二、什么叫EDA

. EDA:

电子设计自动化(

Electroni

Design Automation )是电子设计技术和

电子制造技术的核心, EDA技术的发展

和推广应用极大的推动了电子信息行业

的发展。

第1章cpld学习教程

我们认识的EDA技术

Foundation 、PAC) . 5.IC设计 . 6.SOC设计

第1章cpld学习教程

第一节 EDA技术的发展及其未来

. EDA技术是现代电子信息工程领域的一门新技术; . 今天的EDA技术更多的是指芯片内的电子系统设计自动

化,即片上系统(SOC ,System On Chip)设计。 . 在SOC设计过程中,除系统级设计、行为级描述及对功

能的描述以外均可由计算机自动完成,同时设计人员借 助开发软件的帮助,可以将设计过程中的许多细节问题 抛开,而将注意力集中在电子系统的总体开发上。这样 大大减轻了工作人员的工作量,提高了设计效率,减少 了以往复杂的工序,缩短了开发周期,实现了真正意义 上的电子设计自动化。

第1章cpld学习教程

一、EDA技术的发展进程

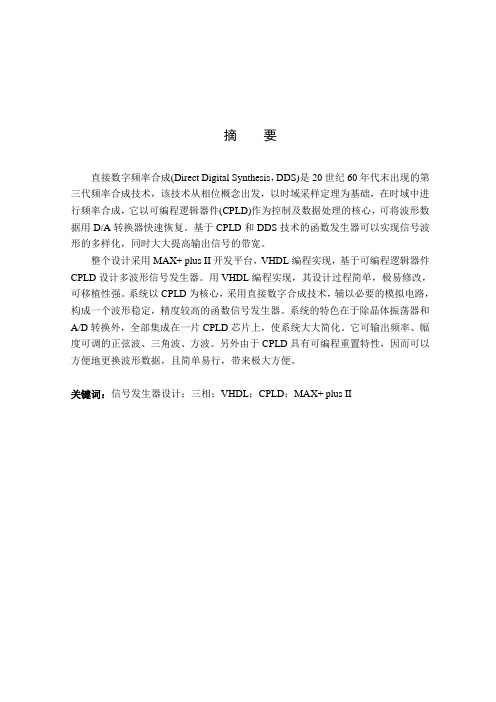

基于CPLD的三相多波形函数发生器资设计资料

摘要直接数字频率合成(Direct Digital Synthesis,DDS)是20世纪60年代末出现的第三代频率合成技术,该技术从相位概念出发,以时域采样定理为基础,在时域中进行频率合成,它以可编程逻辑器件(CPLD)作为控制及数据处理的核心,可将波形数据用D/A转换器快速恢复。

基于CPLD和DDS技术的函数发生器可以实现信号波形的多样化,同时大大提高输出信号的带宽。

整个设计采用MAX+ plus II开发平台,VHDL编程实现,基于可编程逻辑器件CPLD设计多波形信号发生器。

用VHDL编程实现,其设计过程简单,极易修改,可移植性强。

系统以CPLD为核心,采用直接数字合成技术,辅以必要的模拟电路,构成一个波形稳定,精度较高的函数信号发生器。

系统的特色在于除晶体振荡器和A/D转换外,全部集成在一片CPLD芯片上,使系统大大简化。

它可输出频率、幅度可调的正弦波、三角波、方波。

另外由于CPLD具有可编程重置特性,因而可以方便地更换波形数据,且简单易行,带来极大方便。

关键词:信号发生器设计;三相;VHDL;CPLD;MAX+ plus IIABSTRACTDirect digital frequency synthesize(DDFS) is a recently and rapidly developed technology which features high frequency resolution.This paper briefly introduces the basic principle of DDS. The basic principle and performance of CPLD chip.Then it mainly describes how to use CPLD chip to design a function generator of high accuracy.The principle of three-phase multi-signal generator based on CPLD and DDS technology is introduced.Based on these,the modules of CPLD design are given.The multi-wave signal generator is designed based on program-mable logical component CPLD.The VHDL programming realization and the MAX+ plus II development platform. Besides the crystal oscillator and the A/D transformation,the entire system completely integrates on the CPLD chip.The multi-wave signal generator may output the sine-wave,the triangle-wave,the square-wave.Then downloaded under the situation which the entire system hardware connects do not change,and finally output the special profile which user needs.The multi-wave signal generator generates wave which the conventional function signal generators can’t make.Moreover because of the programmable reset feature of the CPLD,the generator can change the wave data conveniently and practice easily.The whole design realizes by the VHDL programmer.Its design process has simple feature,easy modification and high transportation.Keywords:Signal Generator Design;Three-phase;VHDL;CPLD;MAX+ plus II目录1 引言 (1)2基于CPLD的三相多波形函数发生器设计 (3)2.1波形发生器系统的设计方法及其技术指标 (3)2.1.1设计方式概述 (3)2.1.2三相函数多波形发生器技术指标 (5)2.1.3三相波形发生器设计方法概述 (5)2.2设计方案 (6)2.2.1三相函数发生器设计原理 (6)2.2.2多波形发生器的各个波形模块设计方式简介 (9)2.3调试部分 (12)2.3.1CPLD在使用中遇到的问题 (12)2.3.2控制电路的调试 (13)2.3.3DAC电路的调试 (13)2.3.4程序的调试 (13)2.3.5硬件电路的调试 (13)结论 (15)参考文献 (16)附录1三相多波形函数发生器各模块的程序 (17)附录2元件介绍 (23)1DAC0832 (23)2LM324 (24)3PM7128SLC84-15芯片 (25)附录3电路原理图 (26)附录4英文资料及译文 (27)1英文资料 (27)2英文译文 (36)致谢 (43)1引言现代电子技术的核心技术是EDA(Electronic Design Automation)。

基于CPLD的线阵CCD驱动电路设计方法的研究与实现

.

Iske e t e , prn i e a sg de ft e t i g s q n e t y faur s i cpl nd dei i a o i n e ue c n s h m

0 引言

C D( h reC u l e ie) C C ag o pe D vcs,电荷 耦合器件 ,是 d 七十年代初 发展起来 的新型半导体 器件 ,它是 美国 贝尔 实 验 室 的 w..o l G..mi SB ye和 ES t h于 1 7 首 先 提 出 9 0年 的 …。后 来很快 被 Ama o等 人的 实验 所证 实 。在 经历 l l 了几年 的研 究阶段之 后 ,建立 了以一维势 阱模 型为基础 的非稳态 C D基本理 论。3 C 0年来 ,C CD器件理论及其 应用技术 等的研究取 得了极大 的发展 ,尤其在 图像传感

i egn en e sT id v rs ee pdo e as f P D,adr hitrc g a e rvddfr srw t n n er g l . hs r e vl e nt s L i i fd i i id o h b io C n c e ae i la o i es i i n f s srp n e ou h

摘 要 :以典型 的线阵 C DI C  ̄像传 感器件 T D3D C 1 为例 ,设计和开发 了一种 线阵C D  ̄ 2 C  ̄ 动电路。电路主要采用 了复杂 可编程逻辑器件 (P D ,充分发挥其 “ CL) 可编程 ”的技术 特性 ,为用户提供 了丰富的接 口信号 。介 绍了

该驱 动电路 的主 要特性 、工 作原理和驱 动时序 的设 计思想 ,阐述 了逻辑 设计原理 ,给出 了cP D实现 电路和 L

cpld频率计课程设计

cpld频率计课程设计一、课程目标知识目标:1. 理解 CPLD 的基本概念、结构和工作原理;2. 掌握频率计的设计原理和实现方法;3. 学会运用 CPLD 技术设计简单的数字电路系统。

技能目标:1. 能够运用 CPLD 设计并实现一个功能完整的频率计;2. 培养学生动手实践能力,提高电路搭建和调试技巧;3. 提高学生分析问题、解决问题的能力。

情感态度价值观目标:1. 培养学生热爱科学,积极探索的精神;2. 培养团队合作意识,增强沟通与协作能力;3. 提高学生的创新意识,激发创新潜能。

课程性质:本课程为电子信息类专业的实践课程,旨在让学生通过实际操作,掌握 CPLD 技术及其在数字电路设计中的应用。

学生特点:学生已具备一定的电子技术和数字电路基础知识,具有一定的动手能力和探究精神。

教学要求:结合课程特点和学生实际情况,注重理论与实践相结合,强调实践操作和创新能力培养,确保学生能够达到课程目标所要求的知识和技能水平。

通过课程学习,使学生能够将所学知识应用于实际工程设计中,提高学生的职业素养和综合能力。

二、教学内容1. CPLD 基础知识回顾:CPLD 的基本概念、结构、工作原理及其特点,涉及课本第三章第一、二节内容。

2. 频率计设计原理:频率计的工作原理、电路组成和设计方法,包括课本第四章第三节内容。

3. CPLD 设计流程:设计输入、综合、布局布线、仿真和下载等步骤,参考课本第五章内容。

4. 频率计电路设计:使用 CPLD 设计频率计电路,包括时钟信号产生、计数器、显示驱动等模块,结合课本实例进行讲解。

5. 实践操作:分组进行频率计电路的搭建、调试和测试,培养学生动手实践能力。

6. 教学大纲:(1)第1周:CPLD 基础知识回顾,频率计设计原理学习。

(2)第2周:CPLD 设计流程讲解,频率计电路设计方法学习。

(3)第3周:分组进行频率计电路设计,教师指导与答疑。

(4)第4周:实践操作,完成频率计电路搭建、调试和测试。

cpld vga工作原理

cpld vga工作原理

VGA(视频图形阵列)是IBM在1987年随PS/2机一起推出的一种视频传输标准,具有分辨率高、显示速率快、颜色丰富等优点,在彩色显示器领域得到了广泛的应用。

通过CPLD芯片可以实现VGA彩条信号的显示,其工作原理是通过对CPLD编程可输出RGB三基色信号和HS、VS行场扫描同步信号。

CPLD是整个系统的核心,通过它对RGB信号、行同步信号、场同步信号等的控制,可以实现对VGA显示器的控制。

在设计VGA系统时,了解接口标准、控制时序和设定恰当的参数是关键。

VGA显示原理与设计还包含了显示缓存区和视频BIOS程序等部分。

如果你想要了解更多关于VGA工作原理的信息,可以补充相关细节继续向我提问。

CPLD电子线路课程设计报告(7篇)

CPLD电子线路课程设计报告(7篇)通过这一周的课程设计,我对一些专业学问和电子设计有了更深的了解,同时也尝试着去应用自己的所把握的学问。

本次电子课程设计主要是对本学年学习的模拟电子技术和数字电子技术的应用,同时加上电路等学问,设计一些课题。

经过几天的奋战,我感受很深.我和客某某、沈某某三个人在参与学校电子设计大赛并获奖后,便成了参与明年的北京市电子深感自己在培育动手力量这方面还需很大的努力。

于是,这次我们在积存参与电子设计大赛和培训的根底上,在教师的指导下,预备把这个课程设计作为一次练兵,争取为明年的北京市电子设计大赛做足预备,取得一个好成绩。

电子课程设计不仅给我们供应了一个很好的呈现应用自己所把握的学问的平台,又是检验自己所学学问的一次考核. 我们运用各拘束各方面的优势中和起来,形成了一个团队.通过团队力气,才使设计得以完成.可以说,我们三个人是一个不行或缺的整体,少了任何一个人都是无法完成任务的.单片机是我们下学期要学的一门很重要的课程,它具有强大的功能.由于我们对单片机的应用有了肯定的了解,同时也为了下学期学习单片机打好根底,于是这次设计主要是以单片机为主的.一个是单片机编程器,另一个便是对单片机的一个应用电母鸡.在设计的过程中我们也不行避开的遇到了许多的问题.尤其是在调试过程中,会由于某些缘由出不来结果,或三个人之间消失了意见分歧,但在最终都达成了全都. 最终在调试结果出来后,我们更是无比的兴奋,无比的骄傲.总之,通过这次电子课程设计,我不仅对自己的学问有了更好的把握和应用,更了解到团队精神的力气.在以后的学习和生活中受用终身。

CPLD电子线路课程设计报告二时间匆忙而过,一周转瞬即逝。

在过去的这一周时间里面,原本以为会比拟简洁的设计任务却让我觉得有点措手不及。

虽然困难重重,但是在遇到的各种各样的问题中,我学会了急躁,学会了坚持,也学会了以前把握得不太坚固的数电和模电学问。

收获颇丰。

在这次电子课程设计中,我们小组的设计题目是汽车尾灯掌握。

基于CPLD的超声探测器发射控制电路设计

基于CPLD的超声探测器发射控制电路设计超声探测器是一种利用超声波进行物体探测的设备。

它通常由一个发射器和一个接收器组成,其中发射器用于产生超声波信号,接收器则用于接收和处理返回的信号。

本文将基于CPLD(可编程逻辑器件)设计一个超声探测器的发射控制电路。

CPLD是一种可编程的数字逻辑器件,它可以根据设计需求编程实现各种功能。

在这个控制电路中,CPLD将用于控制超声波信号的发射。

首先,我们需要确定超声探测器的工作频率。

超声波通常在20kHz-200kHz的范围内工作,我们可以选择一个适当的频率,例如40kHz。

然后,我们需要确定发射超声波的脉冲宽度和重复频率。

脉冲宽度决定了超声波信号的有效时间,而重复频率决定了信号发射的频率。

接下来,我们可以开始设计电路。

首先,我们将使用CPLD编程工具在CPLD芯片中创建一个逻辑电路。

这个电路将包括一个计数器和一个控制逻辑。

计数器用于生成一个计数信号,该信号将用于控制发射超声波的脉冲宽度。

计数器应该从0开始计数,当达到预定的脉冲宽度时,发射信号将停止。

控制逻辑将负责将计数信号与发射信号进行逻辑操作,并将结果发送到发射器。

为了将CPLD与发射器连接起来,我们需要一个输出接口电路。

这个电路将包括一个输出缓冲器和一个电平转换电路。

输出缓冲器将接收来自CPLD的控制信号,并将其放大到可以控制发射器的电平。

电平转换电路将确保CPLD和发射器之间的电平兼容。

最后,我们需要一个时钟源来提供计数器所需的时钟信号。

这可以是一个独立的晶振电路或由CPLD提供的内部时钟源。

通过这个设计,我们可以实现一个基于CPLD的超声探测器发射控制电路。

该电路将能够控制超声波信号的脉冲宽度和重复频率,以适应不同的应用需求。

当然,为了实现一个完整的超声探测器系统,我们还需要设计一个接收电路和信号处理电路。

这些电路将用于接收返回的超声波信号,并将其转换为可用的数字信号。

然后,我们可以使用微处理器或其他逻辑电路来处理和分析这些数字信号,以实现各种应用。

pld译码驱动-7页精选文档

CPLD设计的数码管驱动显示电路类别:EDA/PLDCPLD设计的数码管驱动显示电路1.1 显示原理:八段数码显示管如图1.1 所示,八段数码管每一段为一发光二极管,共有a~g 以及小数点dp 八个发光二极管。

将八段数码管中的每个二极管的阴极并联在一起,组成公共阴极端。

这样把共阴极管脚接地,此时哪个管脚输入高电平,对应发光二极管就被点亮。

图1.1 八段数码显示管CL5461AS 数码管管脚图如图1.2 所示,它将四个数码显示管的a~g 及小数点dp 管脚并联在一起,作为数码管数据输入端;分别引出各个数码管的阴极A1~A4。

图1.2 CL5461AS 数码管管脚图只要在A1~A4 管脚上轮流加低电平其频率大于40Hz,可实现四个数码管同时被点亮的视觉效果。

在点亮不同数码管的同时输入不同的数据,即可在数码管上同时显示四位不同的数字。

例如:四个数码管要显示9876 数字。

第一个数码管A1 加低电平,其余A2、A3、A4高电平,同时数码管输入和9 对应的数据;然后第二个数码管A2 加低电平,其余A1、A3 、A4 高电平,同时数码管输入和8 对应的数据;然后第三个数码管A3 加低电平,其余A1、A2 、A4 高电平,同时数码管输入和7 对应的数据;然后第四个数码管A4 加低电平,其余A1、A2 、A3 高电平,同时数码管输入和6 对应的数据;周而复始重复上述过程,四个数码管就显示9876 数字。

1.2 驱动八位数码管显示电路框图用CPLD 设计一个驱动八位数码管显示电路。

八位数码管管脚图如图1.2 所示。

用两个CL5461AS 数码管接成一个八位数码管显示,将两个CL5461AS 数码管的a~g 及小数点dp 管脚并联在一起,两个CL5461AS 数码管的阴极A1~A4 定义为Vss0、Vss1、Vss2、Vss3、Vss4、Vss5、Vss6、Vss7。

用CPLD 设计一个驱动八位数码管显示电路的框图如图1.4 所示。

基于CPLD的LED显示屏控制系统的设计

科技资讯 SCIENCE & TECHNOLOGY INFORMATION

19

科技资讯 2009 NO.32 SCIENCE & TECHNOLOGY INFORMATION

信 息 技 术

图 6 CPLD 的模块化设计框图

图 5 主单片机控制程序图

上 位 机 进 行 通 信 的 问 题 ( 见 图 5 、6) 。 2.3 CPLD的程序设计框图

2 屏幕扫描逻辑的设计

2.1 屏幕扫描逻辑的设计思路 LED显示屏驱动电路主要采用动态扫描

显示,动态扫描显示是在一个比较短的时间周 期内将LED显示屏上需要发光的像素逐行分 别点亮。动态扫描显示方式采用多行(16行即 1/16扫描方式)的同名列共用一套列驱动器。 行扫描电路由译码器构成,逐行扫描信号。从 第一行开始,按顺序依次对各行进行扫描。一 旦该行选通,这一行上的相应像素就可以由列 驱动信号点亮。当一行的扫描持续时间结束 后,下一行以同样的方法进行显示。在1/16扫 描方式中,就是把16行都扫过一遍之后,又从 第一行开始下一个周期的扫描。

屏幕刷新频率关系到屏幕显示效果的好 坏 ,从 数 据 更 新 的 角 度 来 讲 ,扫 描 时 钟 频 率 越 高 ,留 给 数 据 更 新 的 时 间 就 越 少 ,不 利 于 系 统 刷 新 ;扫 描 时 钟 频 率 越 低 ,扫 描 时 间 越 长 ,将 引 起 屏 幕 闪 烁 。一 般 来 讲 , 这 个 刷 新 频 率不能低于50HZ(帧频),否则,会产生屏幕闪 烁现象。 2.2 主控电路的程序流程

基于CPLD的三相多波形函数发生器设计

基于CPLD的三相多波形函数发生器设计文章作者:尹佳喜尹仕文章出处:国外电子元器件摘要:介绍了基于可编程逻辑器件CPLD和直接数字频率合成技术(DDS)的三相多波形函数发生器的基本原理,并在此基础上给出了基于CPLD的各模块设计方法及其VHDL源程序。

关键词:CPLD;直接数字频率合成;函数发生器;VHDL1 引言直接数字频率合成 Direct Digital Synthesis ,DDS 是20世纪60年代末出现的第三代频率合成技术。

该技术从相位概念出发,以Nyquist时域采样定理为基础,在时域中进行频率合成。

DDS频率转换速度快,频率分辨率高,并在频率转换时可保持相位的连续,因而易于实现多种调制功能。

DDS是全数字化技术,其幅度、相位、频率均可实现程控,并可通过更换波形数据灵活实现任意波形。

此外,DDS易于单片集成,体积小,价格低,功耗小,因此DDS技术近年来得到了飞速发展,其应用也越来越广泛。

基于CPLD和DDS技术的函数发生器可以实现信号波形的多样化,而且方便可靠,简单经济,系统易于扩展,同时可大大提高输出信号的带宽。

2 系统原理2.1 CPLD内部设计CPLD的内部结构框图如图1所示,图中,首先由控制寄存器将外部控制器(如单片机)送入的数据转换为频率和幅度控制字;然后再由分频器根据频率控制字进行分频并将输出作为寻址计数器的时钟;寻址计数器的寻址空间为360字节,可对ROM中的查找表进行寻址;而通过模360加法器可以产生120°的相位差。

2.2 CPLD的外围电路图2所示是CPLD的外围电路连接图。

图中,CPLD幅度控制字经D/A转换输出后,可作为查找表输出DAC的参考电压,该参考电压可通过改变幅度控制字来进行改变,从而改变输出信号的幅度。

3 CPLD各模块的设计3.1 控制寄存器的设计控制寄存器设计主要是将外部控制器输入的数据转换为频率和幅度控制字。

其程序代码如下:--////////////调库////////////--entity controller isport(clk:in std_logic;datain:in std_logic;ad:out std_logic_vector(16 down to 0);freq:out std_logic_ vector(16 down to 0));end;architecture dataflow of controller issignal out1:std_logic_vector(16 down to 0);begins2p:process(clk,datain)variable temp:std_logic_vector(16 down to 0); beginif clk'event and clk=‘1’ thentemp:=temp(15 down to 0)&datain;end if;out1<=temp;end process s2p;mux:process(out1(16))beginif out1(16)=‘1’ thenad<=out1(15 down to 0); --1号寄存器为幅度控制字elsefreq<=out1(15 downto 0); --0号寄存器为频率控制字end if;end process mux;end;3.2 分频比可变的分频器模块设计该设计主要是根据频率控制字决定分频倍数,从而输出与频率控制字相对应的频率时钟,此模块的输出可作为寻址计数器的时钟。

基于CPLD的大屏幕扫描电路设计

基于CPLD的大屏幕扫描电路设计

郑宝华

【期刊名称】《现代电子技术》

【年(卷),期】2008(31)24

【摘要】为了能显示稳定的图像,对扫描电路的速度要求很高,特别是在实现灰度控制时,要求更高.所以,精心地设计扫描电路是提高图像稳定性的关键.介绍LED大屏幕显示电路结构及扫描电路的设计方法,给出Altera公司的EPM7128在大屏幕扫描电路中的设计实例,阐述可编程逻辑器件在高速数字系统应用中的优点.通过实验,扫描图像非常稳定,充分体现了可编程逻辑器件在高速复杂数学系统中的优势.【总页数】3页(P17-19)

【作者】郑宝华

【作者单位】吉林大学,仪器科学与电气工程学院,吉林,长春,130026;吉林化工学院,吉林,吉林,132022

【正文语种】中文

【中图分类】TP311.1

【相关文献】

1.基于CPLD的LED大屏幕显示控制系统 [J], 郭志冬

2.基于CPLD的LED大屏幕视频控制系统 [J], 林春燕;周晓中

3.基于单片机和CPLD共同控制的LED大屏幕显示系统的设计与实现 [J], 唐扬波

4.基于CPLD的脉冲激光探测装置信号处理电路设计 [J], 刘晨峰

5.基于CPLD的LED大屏幕视频控制系统 [J], 周晓中; 阳春华; 刘伟群

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

内蒙古工业大学信息工程学院实验报告

课程名称: CPLD/FPGA应用开发技术

实验名称:扫描驱动显示电路设计

实验类型:验证性□ 综合性□设计性■

实验室名称:

班级:学号:

姓名:组别:

同组人:成绩:

实验日期: 2012-5-9

月日

预习报告

一、实验目的:

1.了解实验箱中8位七段数码管显示模块的工作原理。

2.熟悉VHDL 硬件描述语言及设计专用数字集成电路的自顶向下的设计思想。

3.掌握利用CPLD/FPGA设计8位七段数码管扫描显示驱动电路的方法。

二、实验设备:

1.计算机(配置为:P4 CPU 128M内存);

2. MAX+plusⅡ开发工具软件;

3. EL教学实验箱;

4.万用表;

5. DS 5022M型双踪数字示波器;

三、实验内容:

本实验要求在给定子模块程序的基础上,画出设计原理图。

自行编写顶层模块程序,完成扫描显示驱动电路的设计,实现在8个数码管上轮流显示字符0-F的功能。

四、设计要求

1.要求在Max+plusⅡ平台上用VHDL语言编写顶层模块程序,调试、仿真成功后,下

载至ALTER EPM7128SLC84-15 芯片,再利用外接电路实现以上设计功能。

2.扫描驱动显示电路有 2 个输入端(clk,reset),14 个输出端(a,b,c,d,e,f,g)

和(y0,y1,y2,y3,y4,y5,y6,y7),全部为TTL 电平,管脚分配任意,如下图所示。

3.根据芯片特点,管脚分配时将时钟信号分配给83 脚,复位信号分配给1 脚,使能信号分配给84 脚。

月日

实验报告

一、实验内容:

本实验要求在给定子模块程序的基础上,画出设计原理图。

自行编写顶层模块程序,完

成扫描显示驱动电路的设计,实现在8 个数码管上轮流显示字符0-F 的功能。

二、实验程序:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY XS IS

PORT(CLK,RESET: IN STD_LOGIC;

A,B,C,D,E,F,G: OUT STD_LOGIC;

Y: OUT STD_LOGIC_VECTOR(2 DOWNTO 0));

END XS;

ARCHITECTURE BEHA OF XS IS

COMPONENT COUNTER16

PORT(CLK,CLR: IN STD_LOGIC;

COUNT: OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END COMPONENT;

COMPONENT DECDISP

PORT(DATAIN: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

A,B,C,D,E,F,G: OUT STD_LOGIC);

END COMPONENT;

COMPONENT YIMA3

PORT(X: IN STD_LOGIC_VECTOR(2 DOWNTO 0);

Y: OUT STD_LOGIC_VECTOR(2 DOWNTO 0));

END COMPONENT;

SIGNAL CONT: STD_LOGIC_VECTOR(3 DOWNTO 0);

SIGNAL SEL3: STD_LOGIC_VECTOR(2 DOWNTO 0);

BEGIN

D1:COUNTER16 PORT MAP(CLK=>CLK,CLR=>RESET,COUNT=>CONT);

D2:DECDISP PORT MAP(DATAIN=>CONT,A=>A,B=>B,C=>C,D=>D,E=>E,F=>F,G=>G);

D3:YIMA3 PORT MAP(X=>CONT(2 DOWNTO 0),Y=>Y);

END BEHA;

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY YIMA3 IS

PORT( X: IN STD_LOGIC_VECTOR(2 DOWNTO 0);

Y: OUT STD_LOGIC_VECTOR(2 DOWNTO 0));

END YIMA3 ;

ARCHITECTURE BEHA OF YIMA3 IS

BEGIN

Y<=X;

END BEHA;

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY DECDISP IS

PORT(DATAIN: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

A,B,C,D,E,F,G: OUT STD_LOGIC);

END DECDISP;

ARCHITECTURE BEHA OF DECDISP IS

SIGNAL DATAOUT: STD_LOGIC_VECTOR(6 DOWNTO 0);

BEGIN

A<=DATAOUT(6);

B<=DATAOUT(5);

C<=DATAOUT(4);

D<=DATAOUT(3);

E<=DATAOUT(2);

F<=DATAOUT(1);

G<=DATAOUT(0);

PROCESS(DATAIN)

BEGIN

CASE DATAIN IS

WHEN "0000"=> DATAOUT<="1111110"; WHEN "0001"=> DATAOUT<="0110000"; WHEN "0010"=> DATAOUT<="1101101"; WHEN "0011"=> DATAOUT<="1111001"; WHEN "0100"=> DATAOUT<="0110011"; WHEN "0101"=> DATAOUT<="1011011"; WHEN "0110"=> DATAOUT<="1011111"; WHEN "0111"=> DATAOUT<="1110000"; WHEN "1000"=> DATAOUT<="1111111"; WHEN "1001"=> DATAOUT<="1111011"; WHEN "1010"=> DATAOUT<="1110111"; WHEN "1011"=> DATAOUT<="0011111"; WHEN "1100"=> DATAOUT<="1001110"; WHEN "1101"=> DATAOUT<="0111101"; WHEN "1110"=> DATAOUT<="1001111"; WHEN "1111"=> DATAOUT<="1000111"; WHEN OTHERS=> DATAOUT<="XXXXXXX"; END CASE;

END PROCESS;

END BEHA;

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY COUNTER16 IS

PORT(CLK,CLR: IN STD_LOGIC;

COUNT: OUT STD_LOGIC_VECTOR(3 DOWNTO 0); SEL: OUT STD_LOGIC_VECTOR(2 DOWNTO 0)); END COUNTER16;

ARCHITECTURE BEHA OF COUNTER16 IS

SIGNAL CNT: STD_LOGIC_VECTOR(3 DOWNTO 0); BEGIN

PROCESS(CLK,CLR)

BEGIN

IF CLR='0'THEN

CNT<="0000";

ELSIF CLK='1' AND CLK'EVENT THEN

CNT<=CNT+'1';

END IF;

COUNT<=CNT;

SEL<=CNT(2 DOWNTO 0);

END PROCESS;

三、仿真结果:

四、管脚分配:。