DSP的160个经典问题

DSP常见问题及解决

问:我测试你们的程序的时候,go main 进不去主函数,进入的是一段汇编。

是怎么回事?答:程序如果要进行设断点,观察变量等操作,要先调入project文件,然后再调入out文件。

如果是可以直接执行能看到结果的,就直接调入out文件,run就可以。

问:CY68013的固件程序怎么修改?答:在把QQ2812都研究清楚了,有精力有兴趣自己可以买一本EZ-USB的书好好看看。

在此之前,请不要随便更改固件代码,因为一旦出错,可能带来不必要的麻烦。

固件代码是通过USBControlPanel,使用USB接口进行下载的。

:2812的主频是最大150M,我如果想设为100M是在那里设置?答:打开工程,在Source文件夹下,打开DSP28_SysCtro.c文件,找到如下语句,修改即可。

// Initalize PLLSysCtrlRegs.PLLCR = 0x02;///锁相环产生的时钟频率定标,这里配置为30M问:为什么我的程序在SRAM中正常,烧入Flash后不对?答:1、请先确认你编译的时候使用了flash.cmd,推荐使用我们提供的flash.cmd,如果自己更改了这个文件,请先确认cmd文件的正确性;2、编译的时候,如果选择release模式,请检查一下build option,把其中的opt level改为none,即取消编译优化选项,很多语句在优化的时候可能会产生错误的优化结果。

或者选择debug模式编译,烧写正确后再改为release模式,通过对比两种模式的编译选项也能看出其中的区别。

3、程序在flash中运行会比在ram中运行大概慢20%,因此对于一些时序敏感的外设,比如usb总线,就有可能需要调整时序,否则就会有问题。

问:数码管LED显示的时候发送的数据是怎么规定和产生的?答:其实如果自己看程序和原理图自己就可以知道是怎么产生的。

数码管数据如下:Uint16SpiCode[]={0x7E7E,0x2929,0x2c2c,0x6666,0xa4a4,0xa0a0,0x3e3e,0x2020,0x2424,0x22 22,0xe0e0,0xb1b1,0x6868,0xa1a1,0xa3a3,0xffff,0xdfdf};数码管的笔画对应关系如下:63 742 01 5就是说0~7分别对应笔画的a~h,在原理图看就是分别连接的Q0~Q7这个数码管的型号是LG3611BH,是共阳级的,也就是说某个笔画为0的时候,这个笔画被点亮。

DSP常见问题及解决

问:我测试你们的程序的时候,go main 进不去主函数,进入的是一段汇编。

是怎么回事?答:程序如果要进行设断点,观察变量等操作,要先调入pro ject文件,然后再调入ou t文件。

如果是可以直接执行能看到结果的,就直接调入ou t文件,run就可以。

问:CY68013的固件程序怎么修改?答:在把QQ2812都研究清楚了,有精力有兴趣自己可以买一本EZ-USB的书好好看看。

在此之前,请不要随便更改固件代码,因为一旦出错,可能带来不必要的麻烦。

固件代码是通过USBCon trolPa nel,使用USB接口进行下载的。

:2812的主频是最大150M,我如果想设为100M是在那里设置?答:打开工程,在Source文件夹下,打开DSP28_SysCt ro.c文件,找到如下语句,修改即可。

// Initali ze PLLSysCtrl Regs.PLLCR = 0x02;///锁相环产生的时钟频率定标,这里配置为30M问:为什么我的程序在SRAM中正常,烧入Flash后不对?答:1、请先确认你编译的时候使用了flash.cmd,推荐使用我们提供的flas h.cmd,如果自己更改了这个文件,请先确认cmd文件的正确性;2、编译的时候,如果选择rel ease模式,请检查一下bu ild option,把其中的opt level改为none,即取消编译优化选项,很多语句在优化的时候可能会产生错误的优化结果。

或者选择deb ug模式编译,烧写正确后再改为relea se模式,通过对比两种模式的编译选项也能看出其中的区别。

3、程序在flas h中运行会比在ram中运行大概慢20%,因此对于一些时序敏感的外设,比如usb总线,就有可能需要调整时序,否则就会有问题。

DSP习题和解答(精)

非标准答案,仅供参考!简答题非绿色部分的自己组织答案!y(n)为输出。

1、设系统差分方程为y(n)=ay(n-1)+x(n),其中x(n)是输入,当y(0)=0时,试判断系统是否是线性时不变的。

解:按照线性是不变系统定义判断。

由题意可归纳出y(n)=∑an-1-ix(i)i=0n对于线性时不变系统应有线性性:T[α1x1(n)+α2x2(n)]=α1y1(n)+α2y2(n)时不变性:T[x(n-k)]=y(n-k)对于y(n)=∑an-1-ix(i),分别验证是否满足线性性和时不变性。

i=0nT[α1x1(n)+α2x2(n)]=∑an-1-i[α1x1(i)+α2x2(i)]i=0n=∑an-1-iα1x1(i)+∑an-1-iα2x2(i)=α1y1(n)+α2y2(n)i=0i=0nn故知满足线性性。

T[x(n-k)]=∑a(n-k)-1-ix(i)=y(n-k)i=0n-k故知满足时不变性。

所以该系统是线性时不变系统。

y(n)为输出。

2、设系统差分方程为y(n)=ay(n-1)+x(n),其中x(n)是输入,当y(0)=0时,试判断系统是否是线性时不变的。

3、用FFT来分析信号的频谱,若已知信号的最高频率为f h =1.25kHz,要求频率分辨率为△F≤5Hz,试确定:(1)采样间隔 T ;(2)采用基-2FFT的最小样点数 N ,以及与此相对应的最小记录长度;(3)按您确定的参数所获得的实际分辨率。

解:(1)由那奎斯特采样定理知fC≥2fH=2⨯1 .25kHz=2.5kHz,且fC=T,所以T≤4⨯10-5s。

(2)归一化角频率与物理角频率的关系ω=ΩT,其中T为采样周期,自然有 1∆ω=∆ΩT,且∆Ω=2π⨯∆F,由频域采样理论知∆ω=2πN,最终得到:∆ω=2πN=2π⨯∆FT=2π⨯5⨯T⇒N=(5T)显然,当T越大N越小,故而此处取T=4⨯10-5s,上式后得到N=5⨯103。

DSP面试常见问题

DSP常见问题1.DSP与普通的微处理器的不同?单周期指令:大多数DSP都拥有流水结构,即每条指令都由片内多个功能单元分别完成取指、译码、取数、执行等步骤,这样可以大大提高系统的执行效率。

它可以在一个时钟周期内执行一条语句。

快速乘法器:信号处理算法往往大量用到乘加(multiply-accumulate,MAC)运算。

DSP有专用的硬件乘法器,它可以在一个时钟周期内完成MAC运算。

硬件乘法器占用了DSP芯片面积的很大一部分。

(与之相反,通用微处理器采用一种较慢的、迭代的乘法技术,它可以在多个时钟周期内完成一次乘法运算,但是占用了较少了硅片资源)。

多总线:DSP有分开的代码和数据总线(一般用术语“哈佛结构”表示),这样在同一个时钟周期内可以进行多次存储器访问——这是因为数据总线也往往有好几组。

有了这种体系结构,DSP就可以在单个时钟周期内取出一条指令和一个或者两个(或者更多)的操作数。

地址发生器:DSP有专用的硬件地址发生单元,这样它可以支持许多信号处理算法所要求的特定数据地址模式。

这包括前(后)增(减)、环状数据缓冲的模地址以及FFT 的比特倒置地址。

地址发生器单元与主ALU和乘法器并行工作,这就进一步增加了DSP 可以在一个时钟周期内可以完成的工作量。

硬件辅助循环:信号处理算法常常需要执行紧密的指令循环。

对硬件辅助循环的支持,可以让DSP高效的循环执行代码块而无需让流水线停转或者让软件来测试循环终止条件。

数据格式:除了标准的整数型格式外,DSP一般支持定点和(或)浮点数。

对数据格式和精度的选择取决于应用程序所需,例如:16位定点DSP可以满足语音信号处理和控制所需24位和32位定点DSP可以满足高质量音频信号处理所需32位浮点DSP可以满足图形和图像处理所需1:DSP采用改进的Harvard结构,程序与数据存储空间分开,各有独立的地址总线和数据总线,取指和读数可以同时进行,而单片机多数采用的是冯•罗依曼结构,所有的操作都必须经过累加器A,很容易造成瓶颈效应。

学习DSP遇到的问题

1,什么是分页机制?2,typedef interrupt void(*PINT)(void);这句话完成了一个类型的定义,以后使用PINT 将定义一个函数的地址。

再来看TINT0 的位置,它位于该结构体的第39 个字节处,对照PIE 中断向量表,第39 个字节处正好是CPU 定时器0 的中断向量,因此完成了的定义之后,当CPU 定时器0的中断发生后,CPU 从中断向量表0x00000D4C处取中断向量,0x00000D4C 处正好放的是中断函数interrupt void ISRTimer0(void)的地址,因为interrupt 关键字的定义,执行该中断函数之前先保护寄存器,然后执行函数功能,执行完后弹出保护寄存器,实现了CPU 定时器0 的中断响应。

上面以CPU定时器0 的中断为例进行了详细的介绍,其他的中断可以参考以上的描述。

3,什么是双缓冲结构??4,0欧姆电阻指阻值为零的电阻。

电路板设计中两点不能用印刷电路连接,常在正面用跨线连接,这在普通板中经常看到,为了让自动贴片机和自动插件机正常工作,用零电阻代替跨线5,RPT #10 || NOP是否可以等价为RPT #10NOP;NOP;这样就是12个周期因||为双目运算符,从左至右执行,执行完RPT #10后还要再执行一次NOP不知我的理解是否正确,求指导~~6,在程序的末尾都要加入一段看门狗复位的死循环,这样做的作用是什么?解决:防止程序跑飞,保留当前输出结果7,what are the meanings of the non-BIOS project and BIOS project?解决:BIOS是TI公司专为DSP设计的实时操作系统。

为TI的DSP编程时,可以采用BIOS,也可以不采用BIOS。

non-BIOS project 就是不采用BIOS的工程文件。

8,我看到dsp2812中有这几个cmd文件:F2812.cmd2812_EzDSP_RAM_lnk.cmdF2812_XintfBoot.cmdDSP281x_Headers_nonBIOS.cmdDSP281x_Headers_BIOS.cmd不知道这几个cmd文件有什么别,到底用哪两个?解决:F2812.cmd:F2812 memory linker command file. Include all FLASH,OTP and CSM password protected memory locations, this linker command file is valid for F2811 as well. 2812_EzDSP_RAM_lnk.cmd: memory map that only allocates SARAM locations. NoFlash,OTP,or CSM password protected locations are used.F2812_XintfBoot.cmd: F2812 boot from XINTF Zone 7.DSP281x_Headers_nonBIOS.cmd: Linker .cmd file to assign the header file variables in a non-BIOS project. This file must bu include in an non-BIOS project that use the header files.DSP281x_Headers_BIOS.cmd: Linker .cmd file to assign the header file variables in a BIOS project. This file must bu include in an BIOS project that use the header files.In most cases, we used 2812_EzDSP_RAM_lnk.cmd and DSP281x_Headers_nonBIOS.cmd for debug or F2812.cmd and DSP281x_Headers_nonBIOS.cmd for Flash if in a non-BIOS project. That all.9,什么是强制高和强制低?解决:如果你设置为强制高,那么PWM的输出始终为高电平,同理,如果你设置为强制低,那PWM的输出始终为低电平。

DSP考试题全解

每个空间都可以独立地设置访问建立、有效和跟踪时间,同时还可以通过

XREADY 信号来与外设的访

问速度和时序匹配。

4 针对 CY7C1021V33 与 DSP 接口的时序分析结果,考虑硬件电路实现时还受那些因素影 响?

磁路饱和 天气 湿度

第四章 3 、串行通信接口(如 RS-232 )与并行接口(如 XINTF )相比,各有何特点 ?

DSP 与扩展板及其他芯片通信的目的

8 设计一个基于 TMS320F2812 的 dsp 应用系统, 系统包括 64kw 的扩展 sram,一路 rs-232 通信接口, 4 路 12 位 D/A 转换器 .

SCIB

电源 3.3v/1.8v

RS-232

复位电路 时钟电路

TMS320F2812 XINF

37.5Mbps ,信号线少( 2- 4

3 采用 DAC 芯片和微处理器产生周期信号波形的方法也称作直接数字合成(

DDS ),与采

用振荡器产生的波形(如文氏电桥正弦波振荡器)相比,

DDS 方法有何优缺点?

优点:频率分辨率高,输出频点多,可达 2 的 n 次方个频点 (N 为相位累加器位数 );频率切换速度快,可达

当 LSPCLK=37.5MHz 时, SCI 的实际波特率范围是 2400—312500,对应的波特率选择寄存器的值 BSR 为 1952 —14。由 SCI 模块的波特率计算公式: 波特率 = LSPCLK/[ (BSR+1 ) *8]

思考题: 1 与 RS232 串行通信相比,采用 RS485/422 串行接口有何优点?

us 量级;频率切换时相位连续;可以输出宽带正交信号;输出相位噪声低,对参考频率源的相位噪声有改 善作用;可以产生任意波形;全数字化实现,便于集成,体积小,重量轻。

DSP的160个经典问题

[原创]做DSP最应该懂得157个问题(回答)做DSP最应该懂得157个问题(回答)一.DSP系统设计100问一、时钟和电源问:DSP的电源设计和时钟设计应该特别注意哪些方面?外接晶振选用有源的好还是无源的好?答:时钟一般使用晶体,电源可用TI的配套电源。

外接晶振用无源的好。

问:TMS320LF2407的A/D转换精度保证措施。

答:参考电源和模拟电源要求干净。

问:系统调试时发现纹波太大,主要是哪方面的问题?答:如果是电源纹波大,加大电容滤波。

问:请问我用5V供电的有源晶振为DSP提供时钟,是否可以将其用两个电阻进行分压后再接到DSP的时钟输入端,这样做的话,时钟工作是否稳定?答:这样做不好,建议使用晶体。

问:一个多DSP电路板的时钟,如何选择比较好?DSP电路板的硬件设计和系统调试时的时序问题?答:建议使用时钟芯片,以保证同步。

硬件设计要根据DSP芯片的时序,选择外围芯片,根据时序设定等待和硬件逻辑。

二.干扰与板的布局问:器件布局应重点考虑哪些因素?例如在集中抄表系统中?答:可用TMS320VC5402,成本不是很高。

器件布局重点应是存贮器与DSP的接口。

问:在设计DSP的PCB板时应注意哪些问题?答:1.电源的布置;2.时钟的布置;3.电容的布置;4.终端电路;5.数字同模拟的布置。

问:请问DSP在与前向通道(比如说AD)接口的时候,布线过程中要注意哪些问题,以保证AD采样的稳定性?答:模拟地和数字地分开,但在一点接地。

问:DSP主板设计的一般步骤是什么?需要特别注意的问题有哪些?答:1.选择芯片;2.设计时序;3.设计PCB。

最重要的是时序和布线。

问:在硬件设计阶段如何消除信号干扰(包括模拟信号及高频信号)?应该从那些方面着手?答:1.模拟和数字分开;2.多层板;3.电容滤波。

问:在电路板的设计上,如何很好的解决静电干扰问题。

答:一般情况下,机壳接大地,即能满足要求。

特殊情况下,电源输入、数字量输入串接专用的防静电器件。

dsp遇到问题及处理方案

Dsp遇到的问题集锦1:仿真器驱动没有装好,可以查看“Studio_v3.3/cc/bin”路径下的“xdsfast3.dll”文件,如果这个文件是160K大小那么驱动就是没有装好的。

如果出现这样的问题,即使重装驱动往往也不能成功。

需要删除该“xdsfast3.dll”文件,然后断开PC和仿真器,重新装仿真器驱动。

安装后查看“xdsfast3.dll”文件大小为352K即表示驱动安装成功。

2:Error:Error 0xA0002020/-1044Error during: Execution, Control,Device driver: Cannot acquire emulator processPossible conflict for device driver usage3:Error connecting to the target:Error 0x80000244/-2131Fatal Error during: Register, Initialization, OCS,Cannot access register at 0x00000000Sequence ID: 0Error Code: -2131Error Class: 0x800002444:Error:Error 0xA0003020/-1137Error during: Execution, Target, Control,It appears that the target is being held in reset. This may be due to Wait-In-Reset (WIR) configuration set by the EMU0=0 and EMU1=1 pin settings. If this is the case, DISCONNECTall CONNECTED devices including icepick and then select RETRY to clear the WIR configuration.If this is a multi-core system, the master CPU may not be releasing the DSP/MCU from reset. Please check your configuration in CC_setup and/or your GEL file to ensure that nothing is blocking the DSP/MCU from being released from resetSequence ID: 16Error Code: -1137Error Class: 0xA0003020。

(完整word版)DSP答案(20200807021432)

绪论部分:1,解释DSP的含义。

数字信号处理(Digital Signal Processing):以数字形式对信号进行采集、变换、滤波、估值、增强、压缩、识别等处理数字信号处理器(Digital Signal Processor):是一种特别适合于进行数字信号处理运算的微处理器芯片,其主要应用是实时快速地实现各种数字信号处理算法2,为什么DSP特别适合用于数字信号处理,简述其主要特点。

主要体现在以下几个方面:①、在一个指令周期内可完成一次乘法和一次加法;②、程序和数据空间分开,可以同时访问指令和数据;③、片内具有快速RAM通常可通过独立的数据总线在两块中同时访问;④、具有低开销或无开销循环及跳转的硬件支持;⑤、快速的中断处理和硬件I/O支持;⑥、具有在单周期内操作的多个硬件地址产生器;⑦、可以并行执行多个操作;⑧、支持流水线操作,使取指、译码和执行等操作可以重叠执行。

另外,DSP实际上是一个微型计算机,它按照指令对二进制的数字信号进行计算,因此,运算速度非常快。

3,简述Havard结构与Von Neumanr结构的不同,DSP采用的哪种结构?DSP采用的哈佛结构(Harvard Architecture ),数据空间和存储空间是分开的,通过独立的数据总线在程序空间和数据空间同时访问。

而MCI采用的冯•诺伊曼结构(Von NeumannArchitecture ),数据空间和存储空间共用一个存储器空间,通过一组总线(地址总线与数据总线)连接到CPU显然,运算能力上MCI不如DSP但MCE格便宜,对性能要求不高的场合MCU具有很大的优势。

4, 目前市场上主要的DSP T商有哪些?试用搜索工具查阅其主要DSP的处理器产品。

目前,在生产通用DSP的厂家中,最有影响的公司有:TI公司(美国德州仪器公司)ADI公司(美国的模拟器件公司)AT&T公司(现在的Luce nt公司)Motorola 公司NEC公司5, TI公司目前应用较广的3个DSP S列是什么?,各自适用于什么领域?TMS320C200D数字控制控制优化:硬盘&采暖、通风空调电机控制家用电器变频电源控制TMS320C5000消费、便携类低功耗:手机便携式电子产品生物识别电信和VoIPTMS320C60C?通信基站、数字图像处理高性能:无线基站视频流、视频会议视频安防/监控医疗成像6, TMS320F2833是哪个公司DSP 试解释其型号命名含义TMS 320 F 2S12 PBK A技术参数F —F1 讪 EEROM (核屯乐 1 舌 W1.9” , I/O 口 电H33 V )C —ROM (fe 电压 1.8 V/1.9 V t I/O IJ 也压3.3 V )7, 简述TMS320F2833主要性能。

DSP面试题_面试试题

DSP面试题1、请用方框图描述一个你熟悉的实用数字信号处理系统,并做简要的分析;如果没有,也可以自己设计一个简单的数字信号处理系统,并描述其功能及用途.(仕兰微面试题目)2、数字滤波器的分类和结构特点.(仕兰微面试题目)3、iir,fir滤波器的异同.(新太硬件面题)4、拉氏变换与z变换公式等类似东西,随便翻翻书把如.h(n)=-a*h(n-1)+b*δ(n) a.求h(n)的z变换;b.问该系统是否为稳定系统;c.写出fir数字滤波器的差分方程;(未知)5、dsp和通用处理器在结构上有什么不同,请简要画出你熟悉的一种dsp结构图.(信威dsp软件面试题)6、说说定点dsp和浮点dsp的定义(或者说出他们的区别)(信威dsp软件面试题)7、说说你对循环寻址和位反序寻址的理解.(信威dsp软件面试题)8、请写出【-8,7】的二进制补码,和二进制偏置码.用q15表示出0.5和-0.5.(信威dsp软件面试题)9、dsp的结构(哈佛结构);(未知)10、嵌入式处理器类型(如arm),操作系统种类(vxworks,ucos,wince,linux),操作系统方面偏cs方向了,在cs篇里面讲了;(未知)11、有一个ldo芯片将用于对手机供电,需要你对他进行评估,你将如何设计你的测试项目?12、某程序在一个嵌入式系统(200m cpu,50m sdram)中已经最优化了,换到零一个系统(300m cpu,50m sdram)中是否还需要优化? (intel)13、请简要描述huffman编码的基本原理及其基本的实现方法.(仕兰微面试题目)14、说出osi七层网络协议中的四层(任意四层).(仕兰微面试题目)15、a) (仕兰微面试题目)。

DSP第一章题目及答案

DSP第一章题目及答案1.DSP应用系统模型包括哪些主要部分?一个典型的DSP系统应包括抗混叠滤波器、数据采集A/D转换器、数字信号处理器DSP、D/A转换器和低通滤波器等。

2.DSP系统有何特点?(1)多总线结构。

DSP芯片内部一般采用的是哈佛结构,其主要特点是将程序和数据存储在不同的存储空间,每个存储器独立编址,独立访问。

在片内有相应的程序总线和数据总线,程序总线和数据总线可以允许同时获取指令字和操作数,而互不干涉。

这意味着在一个机器周期内可以同时准备好指令和操作数,从而使数据的吞吐率提高了1倍。

为了进一步提高运行速度和灵活性,DSP也采用了改进的哈佛结构和超级哈佛结构。

(2)流水线操作。

流水线操作技术使两个或更多不同的操作可以重叠执行,从而在不减小时钟周期的条件下缩短了每条指令的执行时间,增强了处理器的数据处理能力。

要执行一条DSP指令,需要通过取指令、指令译码、取操作数和执行指令等若干阶段,每一阶段称为一级流水。

DSP的流水线操作是指它的这几个阶段在程序执行过程中是重叠的,在执行本条指令的同时,下面的几条指令已依次完成了取指令、解码、取操作数的操作。

(3)专用的硬件乘法器。

硬件乘法器的功能是在一个指令周期内完成一次乘法运算,是DSP实现快速运算的重要保证。

可以说几乎所有的DSP器件内部都有硬件乘法器。

(4)特殊的DSP指令。

数字信号处理器芯片为了对数字信号进行更为高效、快速的处理,专门设计了一套相应的特殊指令。

这些特殊指令节省了指令的条数,缩短了指令的执行时间,提高了运算速度。

(5)多机并行运行特性。

DSP芯片的单机处理能力是有限的,而随着DSP芯片价格的不断降低和应用的广泛,多个DSP芯片并行处理已成为可能,可以运用这一特性,达到良好的高速实时处理的要求。

(6)快速的指令周期。

随着的不断发展,DSP芯片采用了CMOS技术、先进的工艺和集成电路的优化设计,工作电压的下降,使得DSP芯片的主频不断提高。

dsp简答题大全

1.什么是定点DSP 芯片和浮点DSP 芯片?各有什么优缺点?解:按数据的定点格式工作的DSP 芯片称为定点DSP ;按数据的浮点格式工作的DSP 芯片称为浮点DSP ;定点DSP 的价格便宜,功耗低,但运算精度低;浮点DSP 的价格较高,C 语言编程调试方便,运算精度高。

2. 简述流水线操作的基本原理。

解:流水线操作是各指令以机器周期为单位相差一个时钟周期,连续并行工作的情况。

其本质是DSP 多条总线彼此独立地同时工作,使得同一条指令在不同机器周期内占用不同总线资源。

同时,不同指令在同一机器周期内占用不同总线资源。

3. ’C54x DSP 有哪些重复操作?各有什么优点?解:有单条指令重复执行和程序块重复执行两种重复操作。

单条指令重复操作功能,可以使乘法/累加和数据块传送那样的多周期指令在执行一次之后变成单周期指令,大大提高了这些指令的执行速度。

利用块重复操作进行循环,是一种零开销循环。

4. 软件可编程等待状态发生器的功能是什么?解:软件可编程等待状态产生器可以将外部总线周期扩展到7个机器周期(C549、C5402、C5410和C5420为14个机器周期),这样’C54x DSP 可以方便地与慢速的片内存储器和I/O 器件接口。

1. ’C54x DSP 的串行口有哪些类型?各有什么特点?解:有标准同步串口SP 、缓冲同步串口BSP 、多路缓冲串口McBSP 、时分多路同步串口TMD 四种。

缓冲串口(BSP )是一个增强型的标准串口,它由一个全双工双缓冲串口和一个自动缓冲单元(ABU )组成。

由于其中的串行口与标准串口的功能相同,因此在标准模式下,缓冲串口的操作与标准串口的工作方式是一样的。

不过无论是标准模式还是自动缓冲模式,BSP 都提供了一些增强功能。

主要包括了可编程控制的串口时钟、可选择时钟和帧同步信号的正负极性,能够以每帧8位、10位、12位和16位传输数据。

通过配置BSP 的控制寄存器,BSP 还能实现忽略帧同步信号的数据传输。

DSP问答汇总

DSP问答汇总DSP问答汇总一、仿真器问题1、TI公司的仿真器同SEED仿真器的区别?1)SEED-XDS同TI的XDS-510完全兼容,可以完全替代XDS-510。

2)SEED-XDSPP同TI的XDS-510PP完全兼容,可以完全替代XDS-510PP。

3)SEED-XDSUSB和SEED-XDSPCI是合众达独创的产品,它们具有SEED-XDS的全部功能,更加便于使用。

4)SEED仿真器的JTAG/MPSD仿真电缆不同于TI,无需另外投资,可以方便更换。

5)SEED的仿真器同TI的仿真器一样,可以仿真所有TI的DSP和ARM。

2、DSP仿真器为什么必须连接目标系统(Target)?DSP的仿真器同单片机的不同,仿真器中没有DSP,提供IEEE标准的JTAG口对DSP进行仿真调试,所以仿真器必须有仿真对象,及目标系统。

目标系统就是你的产品,上面必须有DSP。

仿真器提供JTAG 同目标系统的DSP相接,通过DSP实现对整个目标系统的调试。

3、SEED-XDS仿真器安装的常见问题?请认真阅读“安装手册”。

常见问题是硬件的I/O口地址同主机的声卡或网卡有冲突,你可以改变仿真器的I/O口地址,也可以改变声卡或网卡的I/O口地址仿真工作正常对于DSP的基本要求1)DSP电源和地连接正确。

2)DSP时钟正确。

3)DSP的主要控制信号,如RS和HOLD信号接高电平。

4)C2000的watchdog关掉。

5)不可屏蔽中断NMI上拉高电平。

4、CCS或Emurst运行时提示“Can't Initialize Target DSP”1)仿真器连接是否正常?2)仿真器的I/O设置是否正确?3)XDSPP仿真器的电源是否正确?4)目标系统是否正确?5)仿真器是否正常?6)DSP工作的基本条件是否具备。

建议使用目标板测试。

5、为什么CCS需要安装Driver?CCS是开放的软件平台,它可以支持不同的硬件接口,因此不同的硬件接口必须通过标准的Driver 同CCS连接。

DSP测试题及答案

DSP测试题及答案1、什么是哈佛结构和冯·诺伊曼(VonNeuman)结构?它们有什么区别?答:(1)冯·诺伊曼(VonNeuman)结构该结构采用单存储空间,即程序指令和数据共用一个存储空间,使用单一的地址和数据总线,取指令和取操作数都是通过一条总线分时进行。

(2)哈佛(Harvard)结构该结构采用单存储空间,即程序指令和数据共用一个存储空间,使用单一的地址和数据总线,取指令和取操作数都是通过一条总线分时进行。

当进行高速运算时,不但不能同时进行取指令和取操作数,而且还会造成数据传输通道的瓶颈现象,其工作速度较慢。

两者区别:哈佛(Harvard)结构:该结构采用双存储空间,程序存储器和数据存储器分开,有各自独立的程序总线和数据总线,可独立编址和独立访问,可对程序和数据进行独立传输,使取指令操作、指令执行操作、数据吞吐并行完成,大大地提高了数据处理能力和指令的执行速度,非常适合于实时的数字信号处理。

冯·诺伊曼(VonNeuman)结构:当进行高速运算时,不但不能同时进行取指令和取操作数,而且还会造成数据传输通道的瓶颈现象,其工作速度较慢。

2、TMS320VC5416-160的指令周期是多少毫秒?它的运算速度是多少MIPS?答:TMS320VC5416-160的指令周期16n,它的运算速度是160MIPS。

3、TMS320C54某芯片的流水线操作共有多少个操作阶段?每个阶段执行什么任务?完成一条指令都需要哪些操作周期?答:(1)六个操作阶段。

(2)各个阶段执行的任务:①预取指P:将PC中的内容加载到PAB②取指F:将读取到的指令字加载到PB③译码D:将PB的内容加载IR,对IR的内容译码④寻址A:CPU将数据1或数据2的读地址或同时将两个读地址分别加载到数据地址总线DAB和CAB中,并对辅助寄存器或堆栈指针进行修正。

⑤读数R:将读出的数据1和数据2分别加载到数据总线DB和CB中。

dsp习题及答案

dsp习题及答案

DSP习题及答案

数字信号处理(DSP)是一门重要的电子学科,它涉及数字信号的获取、处理和传输。

在学习DSP的过程中,习题是非常重要的一部分,通过习题的练习可以加深对知识点的理解和掌握。

下面我们将为大家提供一些常见的DSP习题及答案,希望能够帮助大家更好地学习和掌握这门学科。

1. 什么是数字信号处理?

答:数字信号处理是指对数字信号进行获取、处理和传输的过程,它涉及到数字信号的采样、量化、编码和解码等过程。

2. 什么是数字滤波器?

答:数字滤波器是一种用于处理数字信号的滤波器,它可以对数字信号进行滤波处理,包括低通滤波、高通滤波、带通滤波和带阻滤波等。

3. 什么是数字信号的采样频率?

答:数字信号的采样频率是指每秒钟对信号进行采样的次数,它决定了信号的带宽和分辨率。

4. 什么是数字信号的傅里叶变换?

答:数字信号的傅里叶变换是指将信号从时域转换到频域的过程,它可以将信号分解成不同频率的正弦波和余弦波的叠加。

5. 什么是数字信号的量化误差?

答:数字信号的量化误差是指信号经过模数转换后与原始信号之间的差异,它会对信号的质量产生影响。

通过以上习题及答案的学习,我们可以更好地理解和掌握数字信号处理的基本

概念和原理。

希望大家在学习DSP的过程中能够多加练习,不断提高自己的理解和应用能力,为将来的工作和学习打下坚实的基础。

DSP面试题目

1、请用方框图描述一个你熟悉的实用数字信号处理系统,并做简要的分析;如果没有,也可以自己设计一个简单的数字信号处理系统,并描述其功能及用途.(仕兰微面试题目)2、数字滤波器的分类和结构特点.(仕兰微面试题目)3、IIR,FIR滤波器的异同.(新太硬件面题)4、DSP和通用处理器在结构上有什么不同,请简要画出你熟悉的一种DSP结构图.(信威dsp软件面试题)6、说说定点DSP和浮点DSP的定义(或者说出他们的区别)(信威dsp软件面试题)7、说说你对循环寻址和位反序寻址的理解.(信威dsp软件面试题)8、请写出【-8,7】的二进制补码,和二进制偏置码.用Q15表示出0.5和-0.5.(信威dsp软件面试题)9、DSP的结构(哈佛结构);(未知)10、嵌入式处理器类型(如ARM),操作系统种类(Vxworks,ucos,winCE,linux),操作系统方面偏CS方向了,在CS篇里面讲了;(未知)11、请简要描述HUFFMAN编码的基本原理及其基本的实现方法.(仕兰微面试题目)12、A) (仕兰微面试题目)#i ncludevoid testf(int*p){*p+=1;}main(){int *n,m[2];n=m;m[0]=1;m[1]=8;testf(n);printf("Data value is %d ",*n);}------------------------------B)#i ncludevoid testf(int**p){*p+=1;}main(){int *n,m[2];n=m;m[0]=1;m[1]=8;testf(&n);printf(Data value is %d",*n);}下面的结果是程序A还是程序B的?Data value is 8那么另一段程序的结果是什么?16、那种排序方法最快? (华为面试题)17、写出两个排序算法,问哪个好?(威盛)18、编一个简单的求n!的程序 .(Infineon笔试试题)19、用一种编程语言写n!的算法.(威盛VIA 上海笔试试题)20、用C语言写一个递归算法求N!;(华为面试题)21、给一个C的函数,关于字符串和数组,找出错误;(华为面试题)22、防火墙是怎么实现的? (华为面试题)23、你对哪方面编程熟悉?(华为面试题)24、冒泡排序的原理.(新太硬件面题)25、操作系统的功能.(新太硬件面题)26、学过的计算机语言及开发的系统.(新太硬件面题)27、一个农夫发现围成正方形的围栏比长方形的节省4个木桩但是面积一样.羊的数目和正方形围栏的桩子的个数一样但是小于36,问有多少羊?(威盛)28、C语言实现统计某个cell在某.v文件调用的次数(这个题目真bt) (威盛VIA 上海笔试试题)29、用C语言写一段控制手机中马达振子的驱动程序.(威胜)30、用perl或TCL/Tk实现一段字符串识别和比较的程序.(未知)31、给出一个堆栈的结构,求中断后显示结果,主要是考堆栈压入返回地址存放在低端地址还是高端.(未知)32、一些DOS命令,如显示文件,拷贝,删除.(未知)33、设计一个类,使得该类任何形式的派生类无论怎么定义和实现,都无法产生任何对象实例.(IBM)34、What is pre-emption? (Intel)35、What is the state of a process if a resource is not available? (Intel)36、三个 float a,b,c;问值(a+b)+c==(b+a)+c, (a+b)+c==(a+c)+b.(Intel)37、把一个链表反向填空. (lucent)38、x^4+a*x^3+x^2+c*x+d 最少需要做几次乘法? (Dephi)____________________________________________________________________________主观题1、你认为你从事研发工作有哪些特点?(仕兰微面试题目)2、说出你的最大弱点及改进方法.(威盛VIA 上海笔试试题)3、说出你的理想.说出你想达到的目标. 题目是英文出的,要用英文回答.(威盛VIA上海笔试试题)4、我们将研发人员分为若干研究方向,对协议和算法理解(主要应用在网络通信、图象语音压缩方面)、电子系统方案的研究、用MCU、DSP编程实现电路功能、用ASIC设计技术设计电路(包括MCU、DSP本身)、电路功能模块设计(包括模拟电路和数字电路)、集成电路后端设计(主要是指综合及自动布局布线技术)、集成电路设计与工艺接口的研究.你希望从事哪方面的研究?(可以选择多个方向.另外,已经从事过相关研发的人员可以详细描述你的研发经历).(仕兰微面试题目)5、请谈谈对一个系统设计的总体思路.针对这个思路,你觉得应该具备哪些方面的知识?(仕兰微面试题目)6、设想你将设计完成一个电子电路方案.请简述用EDA软件(如PROTEL)进行设计(包括原理图和PCB图)到调试出样机的整个过程.在各环节应注意哪些问题?电源的稳定,电容的选取,以及布局的大小.(汉王笔试)电子类工程师笔试题(呵呵,网上zz的,比较乱就没有再归纳了)2007-10-17 23:06汉王笔试下面是一些基本的数字电路知识问题,请简要回答之。

dsp答案整理

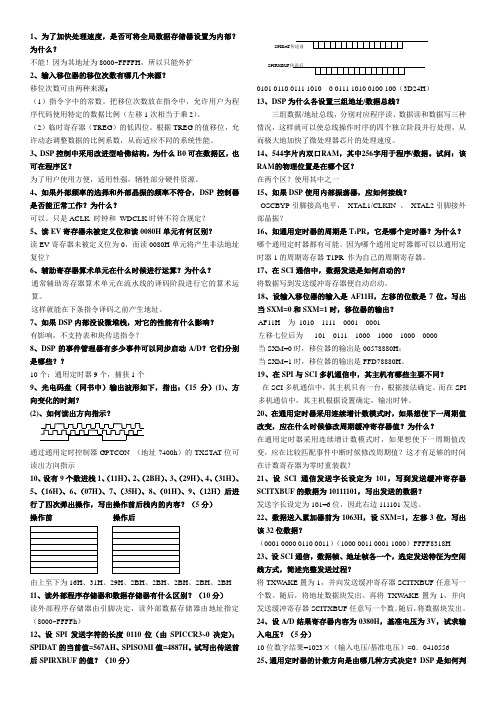

1、为了加快处理速度,是否可将全局数据存储器设置为内部?为什么?不能!因为其地址为8000~FFFFH,所以只能外扩2、输入移位器的移位次数有哪几个来源?移位次数可由两种来源:(1)指令字中的常数。

把移位次数放在指令中,允许用户为程序代码使用特定的数据比例(左移1次相当于乘2)。

(2)临时寄存器(TREG)的低四位。

根据TREG的值移位,允许动态调整数据的比例系数,从而适应不同的系统性能。

3、DSP控制中采用改进型哈佛结构,为什么B0可在数据区,也可在程序区?为了用户使用方便,适用性强,牺牲部分硬件资源。

4、如果外部频率的选择和外部晶振的频率不符合,DSP控制器是否能正常工作?为什么?可以。

只是ACLK 时钟和WDCLK时钟不符合规定?5、读EV寄存器未被定义位和读0080H单元有何区别?读EV寄存器未被定义位为0,而读0080H单元将产生非法地址复位?6、辅助寄存器算术单元在什么时候进行运算?为什么?通常辅助寄存器算术单元在流水线的译码阶段进行它的算术运算。

这样就能在下条指令译码之前产生地址。

7、如果DSP内部没设微堆栈,对它的性能有什么影响?有影响,不支持表和块传送指令?8、DSP的事件管理器有多少事件可以同步启动A/D?它们分别是哪些??10个;通用定时器9个,捕获1个9、光电码盘(同书中)输出波形如下,指出:(15分)(1)、方向变化的时刻?(2)、如何读出方向指示?通过通用定时控制器GPTCON (地址7400h)的TXSTA T位可读出方向指示10、设有9个数进栈1、(11H)、2、(2BH)、3、(29H)、4、(31H)、5、(16H)、6、(07H)、7、(35H)、8、(01H)、9、(12H)后进行了四次弹出操作,写出操作前后栈内的内容?(5分)操作前操作后由上至下为16H、31H、29H、2BH、2BH、2BH、2BH、2BH 11、读外部程序存储器和数据存储器有什么区别?(10分)读外部程序存储器由引脚决定,读外部数据存储器由地址指定(8000~FFFFh)12、设SPI发送字符的长度0110位(由SPICCR3~0决定);SPIDAT的当前值=567AH、SPISOMI值=4887H。

DSP详细版简答题

DSP详细版简答题详细版1.数字信号处理算法一般的实现方法有哪些(详见课本P2)(1)在通用的微机上用软件实现。

这种方法速度慢,不便于实时完成,适于教学与仿真研究,如MATLAB几乎可以实现所有数字信号处理算法的仿真。

(2)利用特殊用途的DSP芯片来实现。

如用于FFT运算,FIR滤波的专用芯片,其特点是速度快,可用于速度高、实时处理的场合,缺点是灵活性差。

(3)利用专门用于信号处理的通用DSP芯片来实现。

通用DSP芯片以高速计算为目标进行芯片设计,如采用改进的哈佛结构、内部有硬件乘法器、使用流水线结构、具有良好的并行性,并具有专门适于数字信号处理的指令,既具有灵活性,又具有一定的处理能力和处理速度。

DSP芯片的问世及飞速发展,为数字信号技术应用于工程实际提供了可能。

(4)用FPGA/CPLD用户可编程器件来实现。

和使用专用DSP芯片一样,该方法也是利用硬件完成数字信号处理,其特点是速度快,但无软件可编程能力、无自适应信号处理能力,只适用于某单一运算。

关于什么是FPGAFPGA(Field Programmable Gate Array)即现场可编程门阵列,它是在PAL、GAL、EPLD等可编程器件的基础上进一步发展的产物。

它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

FPGA的使用非常灵活,同一片FPGA通过不同的编程数据可以产生不同的电路功能。

FPGA在通信、数据处理、网络、仪器、工业控制、军事和航空航天等众多领域得到了广泛应用。

随着功耗和成本的进一步降低,FPGA还将进入更多的应用领域。

2.什么是可编程DSP芯片它有什么特点采用FPGA实现的DSP可以并行或顺序工作。

在并行工作方面,FPGA与ASIC 相当,优于DSP处理器。

而在顺序执行方面,FPGA也优于DSP处理器,因为FPGA中可以使用各种状态机或使用嵌入式微处理器来完成,且每一顺序工作的时钟周期中都能同时并行完成许多执行。

做DSP最应该懂得157个问题

做DSP最应该懂得157个问题发表于2006-10-12 15:47:38 做DSP最应该懂得157个问题(回答)四.5V/3.3V如何混接?TI DSP的发展同集成电路的发展一样,新的DSP都是3.3V的,但目前还有许多外围电路是5V的,因此在DSP系统中,经常有5V和3.3V的DSP混接问题。

在这些系统中,应注意:1)DSP输出给5V的电路(如D/A),无需加任何缓冲电路,可以直接连接。

2)DSP输入5V的信号(如A/D),由于输入信号的电压>4V,超过了DSP的电源电压,DSP的外部信号没有保护电路,需要加缓冲,如74LVC245等,将5V信号变换成3.3V的信号。

3)仿真器的JTAG口的信号也必须为3.3V,否则有可能损坏DSP。

五.为什么要片内RAM大的DSP效率高?目前DSP发展的片内存储器RAM越来越大,要设计高效的DSP系统,就应该选择片内R AM较大的DSP。

片内RAM同片外存储器相比,有以下优点:1)片内RAM的速度较快,可以保证DSP无等待运行。

2)对于C2000/C3x/C5000系列,部分片内存储器可以在一个指令周期内访问两次,使得指令可以更加高效。

3)片内RAM运行稳定,不受外部的干扰影响,也不会干扰外部。

4)DSP片内多总线,在访问片内RAM时,不会影响其它总线的访问,效率较高。

六.为什么DSP从5V发展成3.3V?超大规模集成电路的发展从1um,发展到目前的0.1um,芯片的电源电压也随之降低,功耗也随之降低。

DSP也同样从5V发展到目前的3.3V,核心电压发展到1V。

目前主流的DSP 的外围均已发展为3.3V,5V的DSP的价格和功耗都价格,以逐渐被3.3V的DSP取代。

七如何选择DSP的电源芯片?TMS320LF24xx:TPS7333QD,5V变3.3V,最大500mA。

TMS320VC33:TPS73HD318PWP,5V变3.3V和1.8V,最大750mA。

DSP问答题

DSP问答题第一章绪论1、简述DSP系统的构成和工作过程。

答:DSP系统的构成:一个典型的DSP系统应包括抗混叠滤波器、数据采集A/D转换器、数字信号处理器DSP、D/A转换器和低通滤波器等。

DSP系统的工作过程:①将输入信号x(t)经过抗混叠滤波,滤掉高于折叠频率的分量,以防止信号频谱的混叠。

②经过采样和A/D转换器,将滤波后的信号转换为数字信号x(n)。

③数字信号处理器对x(n)进行处理,得数字信号y(n)。

④经D/A转换器,将y(n)转换成模拟信号;⑤经低通滤波器,滤除高频分量,得到平滑的模拟信号y(t)。

2、简述DSP系统的设计步骤。

答:①明确设计任务,确定设计目标。

②算法模拟,确定性能指令。

③选择DSP芯片和外围芯片。

④设计实时的DSP芯片系统。

⑤硬件和软件调试。

⑥系统集成和测试。

3、什么是流水线技术?简述流水线的6个独立阶段并介绍其功能。

流水线技术指每条指令可通过片内多功能单元完成取指、译码、取操作数和执行等多个步骤,实现多条指令的并行执行,从而在不提高系统时钟频率的条件下减少每条指令的执行时间。

流水线操作是指各条指令以及其周期为单位,相差一个时间周期而连续并行工作的情况。

其原理是:将指令分成几个子操作,每个子操作由不同的操作阶段完成。

这样,每隔一个机器周期,每个操作阶段就可以进入一条新指令。

因此在同一个周期内,在不同操作阶段可处理多条指令,相当于并行执行了多条指令。

①程序预取指:将所要取指的地址放在程序地址总线上②取指:从程序总线上取指令字,并装入指令寄存器③指令译码:对IR中的内容译码,产生执行指令所需要的一系列控制信号④寻址:数据地址产生单元在数据地址总线上输出读操作数的地址⑤读:从数据总线和控制总线上读操作数⑥执行指令:从数据总线上写数据4、TMS320C54x芯片的流水线操作共有多少个操作阶段?每个阶段执行什么任务?完成一条指令都需要哪些操作周期?在C54x的流水线中,一条指令分为预取指、取指、译码、寻址、读数和执行6个操作阶段。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

[原创]做DSP最应该懂得157个问题(回答)做DSP最应该懂得157个问题(回答)一.DSP系统设计100问一、时钟和电源问:DSP的电源设计和时钟设计应该特别注意哪些方面?外接晶振选用有源的好还是无源的好?答:时钟一般使用晶体,电源可用TI的配套电源。

外接晶振用无源的好。

问:TMS320LF2407的A/D转换精度保证措施。

答:参考电源和模拟电源要求干净。

问:系统调试时发现纹波太大,主要是哪方面的问题?答:如果是电源纹波大,加大电容滤波。

问:请问我用5V供电的有源晶振为DSP提供时钟,是否可以将其用两个电阻进行分压后再接到DSP的时钟输入端,这样做的话,时钟工作是否稳定?答:这样做不好,建议使用晶体。

问:一个多DSP电路板的时钟,如何选择比较好?DSP电路板的硬件设计和系统调试时的时序问题?答:建议使用时钟芯片,以保证同步。

硬件设计要根据DSP芯片的时序,选择外围芯片,根据时序设定等待和硬件逻辑。

二.干扰与板的布局问:器件布局应重点考虑哪些因素?例如在集中抄表系统中?答:可用TMS320VC5402,成本不是很高。

器件布局重点应是存贮器与DSP的接口。

问:在设计DSP的PCB板时应注意哪些问题?答:1.电源的布置;2.时钟的布置;3.电容的布置;4.终端电路;5.数字同模拟的布置。

问:请问DSP在与前向通道(比如说AD)接口的时候,布线过程中要注意哪些问题,以保证AD采样的稳定性?答:模拟地和数字地分开,但在一点接地。

问:DSP主板设计的一般步骤是什么?需要特别注意的问题有哪些?答:1.选择芯片;2.设计时序;3.设计PCB。

最重要的是时序和布线。

问:在硬件设计阶段如何消除信号干扰(包括模拟信号及高频信号)?应该从那些方面着手?答:1.模拟和数字分开;2.多层板;3.电容滤波。

问:在电路板的设计上,如何很好的解决静电干扰问题。

答:一般情况下,机壳接大地,即能满足要求。

特殊情况下,电源输入、数字量输入串接专用的防静电器件。

问:DSP板的电磁兼容(EMC)设计应特别注意哪些问题?答:正确处理电源、地平面,高速的、关键的信号在源端串接端接电阻,避免信号反射。

问:用电感来隔离模拟电源和数字电源,其电感量如何决定?是由供电电流或噪音要求来决定吗?有没有计算公式?答:电感或磁珠相当于一个低通滤波器,直流电源可以通过,而高频噪声被滤除。

所以电感的选择主要决定于电源中高频噪声的成分。

问:讲座上的材料多是电源干扰问题,能否介绍板上高频信号布局(Layout)时要注意的问题以及数字信号对模拟信号的影响问题?答:数字信号对模拟信号的干扰主要是串扰,在布局时模拟器件应尽量远离高速数字器件,高速数字信号尽量远离模拟部分,并且应保证它们不穿越模拟地平面。

问:能否介绍PCB布线对模拟信号失真和串音的影响,如何降低和克服?答:有2个方面,1. 模拟信号与模拟信号之间的干扰:布线时模拟信号尽量走粗一些,如果有条件,2个模拟信号之间用地线间隔。

2. 数字信号对模拟信号的干扰:数字信号尽量远离模拟信号,数字信号不能穿越模拟地。

三.DSP性能问:1.我要设计生物图像处理系统,选用那种型号较好(高性能和低价格)?2.如果选定TI DSP,需要什么开发工具?答:1.你可采用C54x 或 C55x平台,如果你需要更高性能的,可采用C6x系列。

2.需要EVMs和XDS510仿真器。

问:请介绍一种专门用于快速富利叶变换(FFT),数字滤波,卷积,相关等算法的DSP,最好集成12bit以上的ADC功能。

答:如果你的系统是马达/能量控制的,我建议你用TMS320LF240x。

详情请参阅DSP选择指南:/dspguide。

问:有些资料说DSP比单片机好,但单片机用的比DSP广。

请问这两个在使用上有何区别?答:单片机一般用于要求低的场合,如4/8位的单片机。

DSP适合于要求较高的场合。

问:我想了解在信号处理方面DSP比FPGA的优点。

答:DSP是通用的信号处理器,用软件实现数据处理;FPGA用硬件实现数据处理。

DSP的成本便宜,算法灵活,功能强;FPGA的实时性好,成本较高。

问:请问减小电路功耗的主要途径有哪些?答:1.选择低功耗的芯片;2.减少芯片的数量;3.尽量使用IDLE。

问:用C55设计一个低功耗图像压缩/解压和无线传输的产品,同时双向传输遥控指令和其他信息,要求图像30帧/秒,TFT显示320*240,不知道能否实现?若能,怎样确定性能?选择周边元器件?确定最小的传输速率?能否提供开发的解决方案?软件核?答:1.有可能,要看你的算法。

2.建议先在模拟器上模拟。

问:用DSP开发MP3,比较专用MP3解码芯片如何,比如成本、难度、周期?谢谢。

答:1.DSP的功能强,可以实现附加的功能,如ebook等;2.DSP的性能价格比高;3.难度较大,需要算法,因此周期较长,但TI有现成的方案。

问:用DSP开发的系统跟用普通单片机开发的系统相比,有何优势?DSP一般适用于开发什么样的系统?其开发周期、资金投入、开发成本如何?与DSP的接口电路是否还得用专门的芯片?答:1.性能高;2.适合于速度要求高的场合;3.开发周期一般6个月,投入一般要一万元左右;4.不一定,但需要速度较高的芯片。

问:DSP会对原来的模拟电路产生什么样的影响?答:一方面DSP用数字处理的方法可以代替原来用模拟电路实现的一些功能;另一方面,DSP的高速性对模拟电路产生较大的干扰,设计时应尽量使DSP远离模拟电路部分。

问:请问支持MPEG-4芯片型号是什么?答:C55x或 C6000 或DSC2x问:DSP内的计算速度是快的,但是它的I/O口的交换速度有多快呢?答:主频的1/4左右。

四.技术性问题问:我有二个关于C2000的问题:1、C240或C2407的RS复位引脚既可输入,也可输出,直接用CMOS 门电路(如74ACT04)驱动是否合适,还是应该用OC门(集电极开路)驱动?2、大程序有时运行异常,但加一两条空指令就正常,是何原因?答:1、OC门(集电极开路)驱动。

2、是流水线的问题。

问:1.DSP芯片内是否有单个的随机函数指令?2.DSP内的计算速度是快的,但是它的I/O口的交换速度有多快呢?SP如何配合EPLD或FPGA工作呢?答:1.没有。

2.取决于你所用的I/O。

对于HPI,传输速率(字节)大约为CPU的1/4,对McBSP,位速率(kbps)大约为CPU的1/2。

3.你可以级联仿真接口和一个EPLD/FPGA在一起。

请参考下面的应用手册: /sc/docs/psheets/abstract/apps/spra439a.htm问:设计DSP系统时,我用C6000系列。

DSP引脚的要上拉,或者下拉的原则是怎样的?我经常在设计时为某一管脚是否要设置上/下拉电阻而犹豫不定。

答:C6000系列的输入引脚内部一般都有弱的上拉或者下拉电阻,一般不需要考虑外部加上拉或者下拉电阻,特殊情况根据需要配置。

问:我正在使用TMS320VC5402,通过HPI下载代码,但C5402的内部只提供16K字的存储区,请问我能通过HPI把代码下载到它的外部扩展存储区运行吗?答:不行,只能下载到片内。

问:电路中用到DSP,有时当复位信号为低时,电压也属于正常范围,但DSP加载程序不成功。

电流也偏大,有时时钟也有输出。

不知为什么?答:复位时无法加载程序。

问:DSP和单片机相连组成主从系统时,需要注意哪些问题?答:建议使用HPI接口,或者通过DPRAM连接。

问:原来的DSP的程序需放在EPROM中,但EPROM的速度难以和DSP匹配。

现在是如何解决此问题的?答:用BootLoad方法解决。

问:我在使用5402DSK时,一上电,不接MIC,只接耳机,不运行任何程序,耳机中有比较明显的一定频率的噪声出现。

有时上电后没有出现,但接MIC,运行范例中的CODEC程序时,又会出现这种噪声。

上述情况通常都在DSK工作一段时间后自动消失。

我在DSP论坛上发现别人用DSK时也碰到过这种情况,我自己参照5402DSK做了一块板,所用器件基本一样,也是这现象,请问怎么回事?如何解决?答:开始时没有有效的程序代码,所以上电后是随机状态,出现这种情况是正常的。

问:我使用的是TMS320LF2407,但是仿真时不能保证每次都能GO MAIN。

我想详细咨询一下,CMD 文件的设置用法,还有VECTOR的定义。

答:可能看门狗有问题,关掉看门狗。

有关CMD文件配置请参考《汇编语言工具》第二章。

问:我设计的TMS320VC5402板子在调试软件时会经常出现存储器错误报告,排除是映射的问题,是不是板子不稳定的因素?还是DSP工作不正常的问题?如何判别?答:你可以利用Memoryfill功能,填入一些数值,然后刷新一下,看是不是在变,如果是在变化,则Memory 是有问题。

问:如何解决Flash编程的问题:可不可以先用仿真器下载到外程序存储RAM中,然后程序代码将程序代码自己从外程序存储RAM写到F240的内部Flash ROM中,如何写?答:如果你用F240,你可以用下载TI做的工具。

其它的可以这样做。

问:C5510芯片如何接入E1信号?在接入时有什么需要注意的地方?答:通过McBSP同步串口接入。

注意信号电平必须满足要求。

问:请问如何通过仿真器把.HEX程序直接烧到FLASH中去?所用DSP为5402是否需要自己另外编写一个烧写程序,如何实现?谢谢!!答:直接写.OUT。

是DSP中写一段程序,把主程序写到FLASH中。

问:DSP的硬件设计和其他的电路板有什么不同的地方?答:1.要考虑时序要求;2.要考虑EMI的要求;3.要考虑高速的要求;4.要考虑电源的要求。

问:ADS7811,ADS7815,ADS8320,ADS8325,ADS8341,ADS8343,ADS8344,ADS8345中,哪个可以较方便地与VC33连接,完成10个模拟信号的AD转换(要求16bit,1毫秒内完成10个信号的采样,当然也要考虑价格)?答:作选择有下列几点需要考虑1. 总的采样率:1ms、10个通道,总采样率为100K ,所有A/D均能满足要求。

2. A/D与VC33的接口类型:并行、串行。

前2种A/D为并行接口,后几种均为串行接口。

3. 接口电平的匹配。

前2种A/D为5V电平,与VC33不能接口;后几种均可为3.3V电平,可与VC33直接接口。

问:DSP的电路板有时调试成功率低于50%,连接和底板均无问题,如何解决?有时DSP同CPLD产生不明原因的冲突,如何避免?答:看来你的硬件设计可能有问题,不应该这么小的成功率。

我们的板的成功率为95%以上。

问:我们的工程有两人参与开发,由于事先没有考虑周全,一人使用的是助记符方式编写汇编代码,另一人使用的是代数符号方式编写汇编代码,请问CCS5000中这二种编写方式如何嵌在一起调试?答:我没有这样用过,我想可以用下面的办法解决:将一种方式的程序先单独编译为.obj文件,在创建工程时,将这些.obj文件和另一种方式的程序一起加进工程中,二者即可一起编译调试了。