Common Flash Interface(CFI)_JESD68-01

数码管驱动与程序设计

数码管驱动与程序设计正文:一:引言数码管是一种常见的显示器件,广泛应用于各类电子设备中。

本文将介绍数码管驱动原理及程序设计方法。

二:数码管基础知识2.1 数码管结构和工作原理:包括共阳极与共阴极两种类型的接线方式以及其对应的工作原理。

2.2 数字编码格式:介绍BCD(Binary-Coded Decimal)和7段数字编码等常见数字表示形式。

三:数位扫描技术3.1 静态扫描法:详解静态扫描法实现多个数位同时显示,并给出相应示意图。

3.2 动态行列交替刷新法:讲解动态行列交替刷新法实现高亮度且节省IO口资源,并提供相关代码片段。

四:驱动芯片选择与使用指南4.1 常用驱动芯片推荐:4.1.a 具有集成锁存功能的74HC595;4.1.b 双向移位寄存器CD4099B;4.c 拓展型单通道LED控制IC MAX7219/722X系列。

五:程序设计方法论述5.1 C语言下直接操作I/O端口进行控制:通过C语言内嵌汇编或者直接操作寄存器的方式进行数码管驱动。

5.2使用Arduino库函数:介绍使用Arduino开发板及其相关库函数实现简单快捷的数码管控制。

六:案例分析6.1 数字时钟设计与实现: 详述数字时钟系统中涉及到的硬件电路和软件程序,并给出完整代码示例。

6.2 温度显示仪表盘设计与实现: 分析温度传感器数据采集以及相应显示方法,提供可参考代码片段。

七:附件:本文档所涉及内容包含以下附件:7.1 示意图:静态扫描法原理示意图;7.2 示例源代码:基于C语言编写的数位扫描程序;7.3 Arduino Library文件等。

注释:- BCD(Binary-Coded Decimal)二进制编码十进制表示形式,将每个十进制数字用4位二进制来表示。

- 共阳极(Common Anode)是指所有LED共享一个正级端口而各自独立地连接至负级或GND引脚;共阴极(Common Cathode)则反之。

浅析闪速存储器接口的类型与应用

浅析闪速存储器接口的类型与应用【摘要】本文主要对闪速存储器(闪存)的接口类型和应用进行浅析。

通过对闪速存储器的NOR型和NAND型所涉及到的各种接口分类、接口应用的时序和传输方式的比较,进一步的阐明了闪速存储器接口的特性和应用的趋势。

【关键词】闪速存储器;接口;闪存;NOR型;NAND型1.前言闪速存储器(Flash Memory),也称闪存,是存储类元器件的一种。

它具有EEPROM(Electrically Erasable Programmable Read-Only Memory电可擦写可编程只读存储器)、RAM(Random Access Memory 随机存储器)和ROM(Read-Only Memory只读存储器)的一些优势:存储容量较高、可更新存储数据以及非挥发性。

闪存主要被用来存放系统的启动程序和数据资料,在各种嵌入式平台及系统中起着重要的作用。

闪存的存储单元的架构主要分为NOR(或非)型和NAND (与非)型。

NOR型的存储单元分别连接在字线和位线上,如图(1),单元结构较为独立,但不利于生产制程的缩减,容量一般不太大。

NAND型存储单元为串列相连,如图(2),单元结构比较紧密,易于生产制程的缩减,通常容量可以做的比较大。

由于存储单元结构上的本质差异,也造成了存储接口上的差异和性能的不同。

当然,随着系统应用和存储要求的不同,闪速存存储器的接口也随之而改变。

下面以目前市场应用中所出现的几种类型的闪存接口来做进一步讨论。

2.闪存接口的类型2.1 数据地址并行接口(ADP:Address Data Parallel)NOR型闪存的并行接口,逻辑示意图如图(3)。

有独立的数据线和地址线以及控制线,易于随机读取,一般被视为存储系统指令和启动程序的最佳选择。

系统可以快速随机的读取并代码执行----芯片内执行(XIP:eXecute In Place)而无需将代码下载至RAM中执行。

在系统应用前,需要先根据CPU的工作模式,如Byte模式或Word模式来一一对应闪存的控制引脚以及地址和数据接口总线。

Common Flash memory Interface (CFI) Specification

Common Flash Memory InterfaceSpecificationRelease 2.0December 1, 2001AMD1 AMD Place, Sunnyvale, CA 94088-3453CFI SPECIFICATION AGREEMENTThis is a royalty-free, reciprocal patent license for parties wishing to adopt the CFI Specification in their products. By making use of this specification, you (“User”) are agreeing to be bound by the terms of this agreement. If you do not agree to them, then you have no license to use the specification, and you should destroy these materials or return them to the CFI Promoter from whom this Agreement was obtained.“CFI Specification” means a revision of the “Common Flash Interface Specification,” numbered 1.0 or greater, published and made available for industry licensing by the CFI Promoters.“CFI Promoters” means Intel Corporation, Advanced Micro Devices, Fujitsu Limited, and Sharp Corporation.Agreement: Effective as of User’s acceptance of this Agreement, and subject to its terms and conditions CFI Promoters and User agree as follows:License: CFI Promoters and User each grant to the other and its subsidiaries, under any claim of a patent or patent application otherwise infringed, a non-exclusive, royalty-free, non-transferable, world-wide license, without rights to sublicense, to make or have made such party’s products which comply with the CFI Specification solely in connection with meeting the CFI Specification, and to use, sell, offer to sell, and import such products, where infringement of such claims would not have occurred but for the incorporation of the CFI Specification in such products, and there is no feasible alternative to such infringement.No Other Licenses. Except for the rights expressly provided by this Agreement, neither party grants or receives, by implication, or estoppel, or otherwise, any rights under any patents or other intellectual property rights.LIMITATION OF LIABILITY: The CFI Specification is provided "AS IS" without warranty of any kind. THE CFI PROMOTERS OFFER NO WARRANTY EITHER EXPRESS OR IMPLIED INCLUDING THOSE OF MERCHANTABILITY, NONINFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY OR FITNESS FOR A PARTICULAR PURPOSE. THE CFI PROMOTERS SHALL NOT BE LIABLE FOR ANY DAMAGES WHATSOEVER (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF BUSINESS PROFITS, BUSINESS INTERRUPTION, LOSS OF BUSINESS INFORMATION, OR OTHER LOSS) ARISING OUT OF THE USE OF OR INABILITY TO USE THE CFI SPECIFICATION, EVEN IF THE CFI PROMOTERS HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. BECAUSE SOME JURISDICTIONS PROHIBIT THE EXCLUSION OR LIMITATION OF LIABILITY FOR CONSEQUENTIAL OR INCIDENTAL DAMAGES, THE ABOVE LIMITATION MAY NOT APPLY. TERMINATION OF THIS LICENSE: The CFI Promoters may terminate this license at any time if you are in breach of any of its terms and conditions. Upon termination, you will immediately destroy the CFI Specification or return all copies of the same you have made to the CFI Promoters.U.S. GOVERNMENT RESTRICTED RIGHTS: The CFI Specification is provided with "RESTRICTED RIGHTS." Use, duplication or disclosure by the Government is subject to restrictions set forth inFAR52.227-14 and DFAR252.227-7013 et seq. or its successor. Use of the CFI Specification by the Government constitutes acknowledgment of CFI Promoters’ rights in them .APPLICABLE LAWS: Any claim arising under or relating to this Agreement shall be governed by the laws of Delaware. You may not export the CFI Specification or products in compliance thereto in violation of applicable export laws.CFI SPECIFICATIONRevision RecordEdition Date Published Revised Contents1.00 07/25/1996 First Draft Release2.00 12/01/2001 Second Draft ReleaseNoticeThis Specification is hereby provided to you for your use subject to the terms of the enclosed CFI Specification Agreement.AMD retains the right to make changes to this document at any time, without notice.Table of Contents1. Introduction1.1. Purpose1.2.Scope2. CFI Overview2.1. CFI Operational Summary3. CFI Hardware Interface3.1. CFI Query Command Interface3.2. Query Structure Output3.3. CFI Query Structure4. Extensibility5. Appendix1. CFI Introduction1.1. PurposeThe Common Flash Interface (CFI) specification outlines device and host system software interrogation handshake that allows specific vendor-specified software algorithms to be used for entire families of devices. This allows device-independent, JEDEC ID-independent, and forward- and backward-compatible software support for the specified flash device families. It allows flash vendors to standardize their existing interfaces for long-term compatibility.1.2. ScopeThis release of the specification defines the basic Query interface for CFI-compliant devices. This allows parameterization of known and future flash Read/Write/Erase control interfaces. This Query structure attempts to define all the critical parameters relevant to a broad base of flash memory devices. The CFI specification will not specify detail command sets, status polling methods, and software algorithms of individual flash vendors. A 16-bit ID code is assigned to specific manufacturers’ interfaces, and it is up to that manufacturer to provide these detailed specifications.2. CFI Overview2.1. CFI Operational SummaryAfter the Query command code has been issued, the device enters the Query mode, allowing read output of the CFI Query data structure. The CFI Query data structure contains a 16-bit Command Set and Control Interface ID code that specifies a vendor-specific control interface for a family of flash devices. Query also contains general, common flash memory parameters and vendor-specified data areas. These provide all the necessary information for controlling Read/Write/Erase operations of a particular family of flash devices according to a vendor-specified interface. Any additional information not covered in the common CFI Query data structure is located in vendor-specific extended Query tables, the address location(s) of which is (are) contained in the general CFI Query structure.3. CFI Hardware Interface3.1. CFI Query Command InterfaceThe CFI Query structure is accessed similar to the existing “ID Mode” or “JEDEC ID”access for nonvolatile memories, but uses a different, non-conflicting command code. The Query access command is 98h, while the JEDEC ID mode access mode is 90h. The Query addressing is always relative to the device word (largest supported) with data always presented on the lowest order byte (D7 - D0 outputs).Nonvolatile memory devices are assumed to power up in a read-only state. Independent of that assumption, the Query structure contents must be able to be read at the specific address locations following a single system write cycle where: 1) a 98h Query command code is written to 55h address location within the device’s address space (in maximum device bus-width), and 2) the device is in any valid read state, such as “Read Array” or “Read ID Data.” Other device states may exist within a long sequence of commands or data input; such sequences must first be completed or terminated before the writing of the 98h Query command code will result in valid Query data structure output.Note that for devices wider than 8 bits, the valid Query access code has all zeroes (0’s) in upper bytes of the data bus. Thus the 16-bit Query command code is 0098h and the 32-bit Query command code is 00000098h.A CFI-compliant device must allow selection and de-selection of the Query output modeto and from normal read array operation with a single command write cycle so that the desired data are accessible in the second of two active bus cycles, i.e. bus cycles in which the devices Chip Enable(s) are active.Table 3.1 Command Write Cycles for Query Select & Deselect# of First Bus Cycle Second Bus CycleAddressOperData Command CyclesOperAddressDataRead AA ADRead Array ≥2 Write X FFh/F0hQuery ≥2 Write 55h 98H Read QA QDNotes:1. “Address” is the location in maximum device bus-width2. Flash devices may or may not have address sensitive query commands. Device drivers should alwayssupply 55h on the address bus and 98h on the data bus to enter query mode, however Flash devicesmay choose to ignore the address bus and enter query mode if 98h is seen on the data bus only3. A flash vendor must define other command sequences for other mode accesses as part of the Vendor-specific Algorithm and Control Interface specification referenced by the appropriate CFI ID code.Access to and from Query and Read Array modes from any other mode may require additionalcommand sequences.Abbreviations for inputs and outputs of the second cycle refer to address/data for the normal flash array (AA, AD) and Query structure (QA, QD), which may be accessed in random orderTable 3.1.1 Summary of Command Sequence as a function of device and modeDevice type / mode Command locationin maximum devicebus width addressesCommand data Commandaddresslocationin bytesCommand data withbyte addressingx8 device / x8 mode 55h 298h 55h98hx16 device / x16 mode 55h 20098h AAh AAh: 98hABh: 00hx16 device / x8 mode N/A 1 N/A1AAh AAh: 98hx32 device / x32 mode 55h 200000098h 154h 154h: 98h155h: 00h156h: 00h157h: 00hx32 device / x16 mode N/A 3 N/A3154h 154h: 98h155h: 00hx32 device / x8 mode N/A 1 N/A1154h 154h: 98hNotes:1. The system must drive the lowest order addresses to access all the device’s array data when the deviceis configured in x8 mode. Therefore, word or double addressing where the lower addresses are not toggled by the system is “Not Applicable” for x8-Configured devices.2. Flash devices may or may not have address sensitive query commands. Device drivers should alwayssupply 55h on the address bus (55h, AAh, and 154h respectively for command address location in bytes on x8, x16 and x32 data bus configured devices) and 98h on the data bus to enter query mode, however Flash devices may choose to ignore the address bus and enter query mode if 98h is seen on the data bus only.3. Same as note 1 above but change x8 references to x16.Table 3.1.2 Example of Query Command Sequence of a x8/x16 Capable Device with an address sensitive Query CommandBinary Address -- x16 Mode (BYTE#=1)Address : Data BinaryAddress-- x8 Mode (BYTE#=0)Address : DataA8A7A6A5A4A3A2A1A16 - A1 : D15 - D0A7A6A5A4A3A2A1A0A15 - A0 : D7 - D0 A7A6A5A4A3A2A1A0A15 - A0 : D15 - D0A6A5A4A3A2A1A0A-1A14 - A-1 : D7 - D0 0 1 0 1 0 1 0 1 0055h : 0098h 1 0 1 0 1 0 1 0 00AAh : 98h Note: Address examples provided for devices with least significant byte address of A0 or A-1Table 3.1.3 Example of Query Command Sequence of a x16/x32 Capable Devicewith an address sensitive Query CommandBinary Address -- x32 Mode (WORD#=1)Address : Data BinaryAddress-- x16 Mode (WORD#=0)Address : DataA9A8A7A6A5A4A3A2A33– A2 : D31 - D0A8A7A6A5A4A3A2A1A16– A1 : D15 - D0 A8A7A6A5A4A3A2A1A32– A1 : D31 - D0A7A6A5A4A3A2A1A0A15– A0 : D15 - D0 A7A6A5A4A3A2A1A0A31– A0 : D31 - D0A6A5A4A3A2A1A0A-1A14– A-1 : D15 - D0 0 1 0 1 0 1 0 1 0055h : 00000098h 1 0 1 0 1 0 1 0 00AAh : 0098h Note: Address examples provided for devices with least significant byte address of A1, A0, or A-13.2. Query Structure OutputQuery data are always presented on the lowest-order data outputs (D7 - D0) only. The numerical offset value is the address relative to the maximum bus width supported by the device. The Query table device starting address is a 10h byte address for a byte-wide(x8) device, 10h word address for word-wide (x16) device, 10h “d-word” address for ax32 device, etc.Thus for the byte-wide (x8) device, the first 2 bytes of the Query structure, “Q” and ”R”in ASCII, appear at device addresses 10h and 11h, which is the same as the absolute byte address. These same data appear on the low byte at word addresses 10h and 11h in a word-wide (x16) device. A CFI-compliant device must output 00H data on upper bytes. Thus, an x16 device outputs ASCII “Q” in the low byte (D7-D0) and 00h in the high byte (D15-D8). The same logic extends to x32 and larger devices, such that: 1) the data are presented in the lowest byte, 2) the data are addressed in maximum-bus-width-relative addresses, and 3) the upper bytes in each data word are filled with 00h data. Thus outputs D31 - D8 of a x32 device present 00h data during Query read, starting at d-word address 10h or byte-relative address 40h.In devices that are x8/x16 capable, the x8 data is still presented in word-relative (16-bit) addresses. However, the “fill data” (00h) is not the same as driven by the upper bytes in the x16 mode. As in x16 mode, the byte address (A0 or A-1 depending on pin-out) is ignored for Query output so that the “odd byte address” (A0 or A-1 high) repeats the “even byte address” data (A0 or A-1 low). Therefore, in x8 mode using byte addressing, such devices will output the sequence “Q”, “Q”, “R”, “R”, “Y”, “Y”, and so on, beginning at byte-relative address 20h (which is equivalent to word offset 10h in x16 mode). Again, this is extensible to x32 and wider devices in that byte addresses are ignored during Query output in x8 mode such that: 1) Query data appears to repeat at each byte address within a word and, 2) the Query data starts at the byte address 10h times the number of bytes of maximum device bus-width.Table 3.2.1 Summary of Query Structure Output as a Function of Device and ModeDevice type / mode Query startlocationin maximumdevicebus-widthaddressesQuery data withmaximum deviceBus-widthaddressing“x” = ASCIIequivalentQuery data withword addressingQuerystartaddress inbyteaddressingQuery datawithbyteaddressingx8 device / x8 mode 10h 10h: 51h “Q”11h: 52h “R”12h: 59h “Y”- 10h 10h: 51h “Q”11h: 52h “R”12h: 59h “Y”x16 device / x16 mode 10h 10h: 0051h “Q”11h: 0052h “R”12h: 0059h “Y”- 20h 20h: 51h “Q”21h: 00h null22h: 52h “R”x16 device / x8 mode N/A[Note 1]N/A[Note 1]- 20h 20h: 51h “Q”21h: 51h “Q”22h: 52h “R”x32 device / x32 mode 10h 10h: 00000051h“Q”11h: 00000052h“R”12h: 00000059h“Y”- 40h 40h: 51h “Q”41h: 00h null42h: 00h null43h: 00h null44h: 52h “R”x32 device / x16 mode N/A[Note 2]N/A[Note 2]20h: 0051h “Q”21h: 0051h “Q”22h: 0052h “R”23h: 0052h “R”40h 40h: 51h “Q”41h: 00h null42h: 51h “Q”43h: 00h null44h: 52h “R”45h: 00h null46h: 52h “R”x32 device / x8 mode N/A[Note 1]N/A[Note 1]40h 40h: 51h “Q”41h: 51h “Q”42h: 51h “Q”43h: 51h “Q”44h: 52h “R”Note 1: The system must drive the lowest order addresses to access all the device’s array data when the device is configured in x8 mode. Therefore, word or double-word addressing where these lower addresses are not toggled by the system is “Not Applicable” for x8-configured devices.Note 2: Same as note 1 above but change x8 references to x16.Table 3.2.2 Example of Query Structure Output of a x8/x16 Capable DeviceBinary Address -- x16 Mode (BYTE#=1)Address : DataBinaryAddress-- x8 Mode (BYTE#=0)Address : DataA6A5A4A3A2A1A16 - A1 : D15 - D0A5A4A3A2A1A0A7 - A0 : D7 - D0 A5A4A3A2A1A0A15 - A0 : D15 - D0A4A3A2A1A0A-1A6 - A-1 : D7 - D00 1 0 0 0 0 0 1 0 0 0 1 0 1 0 0 1 0 0 1 0 0 1 1 0 1 0 1 0 0 0 1 0 1 0 1 0 1 0 1 1 0 0 1 0 1 1 1 0 1 1 0 0 0 ... 0010h: 0051h “ Q”0011h: 0052h “ R”0012h: 0059h “ Y”0013h: P_ID LO PrVendor0014h: P_ID HI ID #0015h: P_ADR LO PrVendor0016h: P_ADR HI TblAdr0017h: A_ID LO AltVendor0018h: A_ID HI ID #...1 0 0 0 0 01 0 0 0 0 11 0 0 0 1 01 0 0 0 1 11 0 0 1 0 01 0 0 1 0 11 0 0 1 1 01 0 0 1 1 11 0 1 0 0 0...20h: 51h “Q”21h: 51h “Q”22h: 52h “R”23h: 52h “R”24h: 59h “Y”25h: 59h “Y”26h: P_ID LO PrVendor27h: P_ID LO ID #28h: P_ID HI“...Note: Address examples provided for devices with least significant byte address of A0 or A-1 Table 3.2.3 Example of Query Structure Output of a x16/x32 Capable DeviceBinary Address -- x32 Mode (WORD#=1)Address : DataBinaryAddress-- x16 Mode (WORD#=0)Address : DataA7A6A5A4A3A2A33– A2 : D31 - D0A6A5A4A3A2A1A16– A1 : D15 - D0 A6A5A4A3A2A1A32– A1 : D31 - D0A5A4A3A2A1A0A15– A0 : D15 - D0 A5A4A3A2A1A0A31– A0 : D31 - D0A4A3A2A1A0A-1A14– A-1 : D15 - D00 1 0 0 0 0 0 1 0 0 0 1 0 1 0 0 1 0 0 1 0 0 1 1 0 1 0 1 0 0 0 1 0 1 0 1 0 1 0 1 1 0 0 1 0 1 1 1 0 1 1 0 0 0 ... 0010h: 0051h “ Q”0011h: 0052h “ R”0012h: 0059h “ Y”0013h: P_ID LO PrVendor0014h: P_ID HI ID #0015h: P_ADR LO PrVendor0016h: P_ADR HI TblAdr0017h: A_ID LO AltVendor0018h: A_ID HI ID #...1 0 0 0 0 01 0 0 0 0 11 0 0 0 1 01 0 0 0 1 11 0 0 1 0 01 0 0 1 0 11 0 0 1 1 01 0 0 1 1 11 0 1 0 0 0...20h: 51h “Q”21h: 51h “Q”22h: 52h “R”23h: 52h “R”24h: 59h “Y”25h: 59h “Y”26h: P_ID LO PrVendor27h: P_ID LO ID #28h: P_ID HI“...Note: Address examples provided for devices with least significant word address of A1, A0, or A-1 AltVendor = Alernate VendorPrVendor = Primary VendorTblAdr = Table Address3.3. CFI Query Structure3.3.1. Query Structure OverviewThe Query command causes the flash component to display the CFI Query structure or “database.” The structure sub-sections and address locations are summarized as follows: Table 3.3.1 Query Structure OverviewOffset Sub-sectionName Description 00h Reserved Reserved for vendor-specific information 10h CFI Query Identification String Command set ID and vendor data offset1Bh System Interface Information Device timing & voltage information27h Device Geometry Definition Flash device layoutP Primary Vendor-specific Extended Query table Vendor-defined additional information specific to the Primary Vendor Algorithm (optional)A Alternate Vendor-specific ExtendedQuery table Vendor-defined additional information specific to the Alternate Vendor Algorithm (optional)The following sections describe the Query structure sub-sections in detail.3.3.2. CFI Query Identification StringThe Identification String provides verification that the component supports the Common Flash Interface specification. Additionally, it indicates which version of the spec and which Vendor-specified command set(s) is(are) supported.Table 3.3.2 CFI Query Identification StringOffset Length(bytes)Description10h 03h Query-uniqueASCIIstring“QRY“13h 02h Primary Vendor Command Set and Control Interface ID Code16-bit ID code defining a specific Vendor-specified algorithms[Refer to CFI Publication 100]15h 02hvalue = P Address for Primary Algorithm extended Query table Note: Address 0000h means that no extended table exists17h 02h Alternate Vendor Command Set and Control Interface ID Codesecond vendor-specified algorithm supported by the device[Refer to CFI Publication 100]Note: ID Code = 0000h means that no alternate algorithm is employed19h 02hvalue = A Address for Alternate Algorithm extended Query table Note: Address 0000h means that no alternate extended table existsNotes:1. Refer to Query Data Output section of Device Hardware interface for the detailed definition of offset address as a function of device word-width and mode.2. The CFI specification allows for replacement of the standard Query table contents. When the Vendor Primary Algorithm extended Query table address points to any address between 10h and 32h, thestandard Query table contents are assumed to be “replaced” at those address. Thus, all or somestandard Query may be replaced. For example, a Vendor Primary Algorithm extended Query tableaddress of 28h means that the standard Device Geometry definition has been replaced. The SystemInterface information at locations 1Bh to 27h may be assumed valid, but the ultimate definition must be spelled out in the appropriate specification for the particular vendor algorithm.3.3.3. CFI Query System Interface InformationThe following device information can be useful in optimizing system interface software.Table 3.3.3 CFI Query System Interface InformationDescriptionOffset Length(bytes)1Bh 01h Vcc Logic Supply Minimum Write/Erase voltagebits 7 - 4 BCD value in voltsbits 3 - 0 BCD value in 100 millivolts1Ch 01h Vcc Logic Supply Maximum Write/Erase voltagebits 7 - 4 BCD value in voltsbits 3 - 0 BCD value in 100 millivolts1Dh 01h Vpp [Programming] Supply Minimum Write/Erase voltagebits 7 - 4 HEX value in voltsbits 3 - 0 BCD value in 100 millivoltsNote: This value must be 0000h if no Vpp pin is present1Eh 01h Vpp [Programming] Supply Maximum Write/Erase voltagebits 7 - 4 HEX value in voltsbits 3 - 0 BCD value in 100 millivoltsNote: This value must be 0000h if no Vpp pin is present1Fh 01h Typical timeout per single byte/word write (buffer write count = 1),2N microsecond20h 01h Typical timeout for minimum-size buffer write, 2N microsecond(if supported; 00h=not supported)21h 01h Typical timeout per individual block erase, 2N millisecond22h 01h Typical timeout for full chip erase, 2N millisecond(if supported; 00h=not supported)23h 01h Maximum timeout for byte/word write, 2N times typical (offset 1Fh)24h 01h Maximum timeout for buffer write, 2N times typical (offset 20h)(00h=not supported)25h 01h Maximum timeout per individual block erase, 2N times typical (offset 21h) 26h 01h Maximum timeout for chip erase, 2N times typical (offset 22h)(00h=not supported)3.3.4. Device Geometry DefinitionThis field provides critical details of the flash device geometry.Table 3.3.4 Device Geometry DefinitionOffset Length (bytes)Description27h 01h Device Size = 2n in number of bytes.28h 02h Flash Device Interface description [Refer to Appendix] 2Ah 02h Maximum number of bytes in multi-byte write = 2n . 2Ch 01h Number of Erase Block Regions within devicebits 7-0 = x = number of Erase Block RegionsNotes:1. x = 0 means no erase blocking, i.e. the device erases at once in “bulk.”2. x specifies the number of regions within the device containing one or more contiguous Erase Blocks of the same size. For example, a 128KB device (1Mb) having blocking of 16KB, 8KB, four 2KB, two 16KB, and one 64KB is considered to have 5 Erase BlockRegions. Even though two regions both contain 16KB blocks, the fact that they are notcontiguous means they are separate Erase Block Regions.3. By definition, symmetrical block devices have only one blocking region.2Dh 04h Erase Block Region Informationbits 31- 16 = z , where the Erase Block(s) within this Region are (z) times 256 bytesin size. The value z = 0 is used for 128-byte block size.e.g. for 64KB block size, z = 0100h = 256 => 256 * 256 = 64Kbits 15 - 0 = y , where y+1 = Number of Erase Blocks of identical sizewithin the Erase Block Region:e.g. y = D15-D0 = FFFFh => y+1 = 64K blocks [maximum number]y = 0 means no blocking (# blocks = y+1 = “1 block ”)Note: y = 0 value must be used with # of block regionsof one as indicated by (x) = 0Notes:1. Erase Blocks always start at address 0 of the Bottom Boot or Uniform Low Version of the Flash Device31h -(k-1) 04h perentry Additional Erase Block Region Information, 4 bytes per region Notes: 1. The total number of blocks times individual block size must add up to the device size.2. The address k is next available Query address at end of the Device Geometry structure. It is the first possible starting address of the optional vendor-specific Query table(s) (i.e.Address “P,” the Primary Vendor-specific extended Query table offset, must be ≥ k). This address is equal to the CFI offset address 2Eh (address of Erase Block Region #1) plus 4*x, i.e. 4 bytes per entry times the number of Erase Block Region entries.3.3.5. Optional Vendor-Specific Extended Query TablesCertain flash features and commands may be optional in a vendor-specific algorithm specification. The optional vendor-specific Query table(s) may be used to specify this and other types of information. These structures are defined solely by the flash vendor(s). Table 3.3.5a Primary Vendor-Specific Extended Query TableOffset Length (bytes)Description(P)h 03h Primary Algorithm extended Query table unique ASCII string “PRI “ (P+3)h 01h Major version number, ASCII(P+4)h 01h Minor version number, ASCII(P+5)h variable Vendor-specific extended Query table contents for Primary Algorithm Table 3.3.5b Alternate Vendor-Specific Extended Query TableOffset Length (bytes)Description(A)h 03h Alternate Algorithm extended Query table unique ASCII string “ALT “ (A+3)h 01h Major version number, ASCII(A+4)h 01h Minor version number, ASCII(A+5)h variable Vendor-specific extended Query table contents for Alternate Algorithm4. ExtensibilityThe CFI specification supports extensibility for future device characteristics through the vendor-specific extended Query table(s). Anything not defined in the common CFIQuery database is to be defined in the vendor extended tables, with the detailed structure of such tables defined by the major and minor vendor revision numbers and the associated vendor-supplied Command Set and Control Interface specification. Note: This is the original CFI Primary Vendor-Specific Extended Query Tabledefinition agreed to by AMD and Fujitsu and was implemented in the initial CFI device (Am29LV160B).CFI Primary Vendor-Specific Extended Query TableMajor.Minor Version = 1.0 Table 4.0 (x8/x16 Device in x8-Mode Used as an Example) Addresses(Word Mode) Addresses (Byte Mode) Data Description(P)h (P*2)h 50h 52h49hQuery-unique ASCII string “PRI ” (3 bytes) (P+3)h ((P*2)+6)h 31hCFI Table - Major version number, ASCII (1 byte) (P+4)h ((P*2)+8)h 30h CFI Table - Minor version number, ASCII (1 byte)(P+5)h ((P*2)+A)h 00h Address Sensitive Unlock 0 = Required, 1 = Not Required(P+6)h ((P*2)+C)h 02h Erase Suspend (1 byte) 00 = Not Supported, 01 = To Read Only, 02 = To Read and Write(P+7)h ((P*2)+E)h 01h Sector Protect (1 byte) 00 = Not Supported, X = Number of sectors per group(P+8)h ((P*2)+10)h 01h Temporary Sector Unprotect (1 byte) 00 = Not Supported, 01 = Supported(P+9)h ((P*2)+12)h 04h Sector Protect/Unprotect scheme (1 byte)01 = 29F040 mode, 02 = 29F016 mode, 03 = 29F400 mode, 04 = 29LV800A mode[Refer to Appendix](P+A)h ((P*2)+14)h 00h Simultaneous Operation (1 byte) 00 = Not Supported, 01 = Supported(P+B)h ((P*2)+16)h 00h Burst Mode Type (1 byte) 00 = Not Supported, 01 = Supported(P+C)h ((P*2)+18)h 00h Page Mode Type (1 byte) 00 = Not Supported, 01 = 4 Word Page, 02 = 8 Word PageNote: This example of the CFI Primary Vendor-Specific Extended Query Tabledefinition was taken from Am29LV320D.CFI Primary Vendor-Specific Extended Query TableMajor.Minor Version = 1.1Table 4.1 (x8/x16 Device in x8-Mode Used as an Example) Addresses(Word Mode) Addresses (Byte Mode) Data Description(P)h (P*2)h 50h 52h 49h Query-unique ASCII string “PRI ” (3 bytes)(P+3)h ((P*2)+6)h 31h Major version number, ASCII (1 byte)(P+4)h ((P*2)+8)h 31hMinor version number, ASCII (1 byte)(P+5)h ((P*2)+A)h 00h Address Sensitive Unlock (DQ1, DQ0)00 = Required, 01 = Not RequiredProcess Technology (DQ7 – DQ2)(P+6)h ((P*2)+C)h 02h Erase Suspend (1 byte) 00 = Not Supported, 01 = To Read Only, 02 = To Read and Write(P+7)h ((P*2)+E)h 04h Sector Protect (1 byte) 00 = Not Supported, X = Number of sectors per group(P+8)h ((P*2)+10)h 01h Temporary Sector Unprotect (1 byte) 00 = Not Supported, 01 = Supported(P+9)h ((P*2)+12)h 04h Sector Protect/Unprotect scheme (1 byte)01 = 29F040 mode, 02 = 29F016 mode, 03 = 29F400 mode, 04 = 29LV800A mode[Refer to Appendix](P+A)h ((P*2)+14)h 00h Simultaneous Operation (1 byte)00 = Not Supported, X = Number of sectors in bank 2(uniform sector bank)(P+B)h ((P*2)+16)h 00h Burst Mode Type (1 byte) 00 = Not Supported, 01 = Supported(P+C)h ((P*2)+18)h 00h Page Mode Type (1 byte) 00 = Not Supported, 01 = 4 Word Page, 02 = 8 Word Page(P+D)h ((P*2)+1A)h B5h ACC [Acceleration] Supply Minimum (1 byte)Bits 7 – 4 = HEX Value in VoltsBits 3 – 0 = BCD Value in 100 Millivolts(P+E)h ((P*2)+1C)h C5hACC [Acceleration] Supply Maximum (1 byte)Bits 7 – 4 = HEX Value in Volts Bits 3 – 0 = BCD Value in 100 Millivolts(P+F)h ((P*2)+1E)h 0Xh Top/Bottom Boot Sector Flag (1 byte)02 = Bottom boot device,03 = Top boot device,04 = Uniform / Bottom WP Protect,05 = Uniform, Top WP Protect NOTE: Because early version CFI devices (prior to table revision 1.1) did notsupport this field:If number of erase block regions > 1:If this field is 00h: refer to device ID code for Top/Bottom boot version ofAm29LV160 or Am29LV116。

西门子技术问题总汇

文档标题

如何设置模拟量输入模板 SM 431-7KF00的温度补偿? 如何解决 SIMATIC BATCH 的 IL43基本设备上 hotfix 安装的问题? 如果通过 PCS7 V6.1 SP1 DVD 单独安装 SIMATIC BATCH Report 需要注意哪些设置? 为什么冗余模拟量输出模块的每个通道只有一半电流输出? 使用WinCC/Web Navigator V6.1 SP1需要什么样的操作系统和软件? 是否 COM PROFIBUS 可以使用所有版本的 GSD 文件? 如何在 WinCC flexible 中组态与S7 控制器的 Profinet 连接? 如何在操作面板上设定定时器时间, 同时如何输出定时器的剩余时间? 数据块初始值与实际值的含义 如何通过窗口对象滚动条步进调节过程值参数? 使用 SINAUT ST7 向电子邮箱接受方发送文本信息 SMS 需要做何设置? 可以使用CPU317-2PN/DP替代在iMap中组态的CPU315-2PN/DP吗? 什么情况下插入C-PLUG卡或者C-PLUG有什么作用? 通过一台PC,可以使用哪种方式访问与IWLAN/PB link PNIO或IE/PB link PNIO连接的PROFIBUS设备? 当在SINAUT网络中使用4线变压器应该注意哪些设置? 在 SINAUT 网络中,使用MD3拨号调制解调器作为专线调制解调器时,要进行哪些设置? 如何安装 DCF77 天线, 当选择 DCF77 天线时需要注意什么? 使用SINAUT ST7向传真机发送文本信息时,需要进行哪些设置? 在 SINAUT 项目中发送短消息必须进行哪些特殊服务的设置? 如何在S7-300 PN CPU和CP343-1之间建立一个open TCP 通讯连接,以及如何进行数据交换? 如何在两个S7-300 PN CPU之间建立一个open TCP 通讯连接,以及如何进行数据交换? 哪些控制系统可以成功与SINAUT ST7一起使用? 使用“零-Modem”电缆连接 TIM 模块应该注意什么? 当用 SINAUT 诊断工具的ST1协议进行诊断时,为什么TIM的状态不能显示? TIM 3V-IE 和 TIM 3V-IE Advanced 模块在以太网上通信时使用哪个端口号? 如何对没有接入网络的S7-200CPU编程? 掉电后,LOGO!的程序会丢失吗? 从 PCS7 V6.1 起,为什么没有分配任何 hierarchy (PH) 的 测量点(变量)通过编译不能在OS中自动创建相应的变量? 在SFC中,如何实现从一个 Sequencer 跳出后回到另一个 Sequencer 的某个固定位置并继续执行? 如何实现过程变量的平均值归档? 存储文件的目标路径和备份可选路径有何作用? WinCC变量归档中如何实现采集周期小于500ms的变量归档? 为什么在 OS 上会显示如下信息“时间跳变通知-永久切换为从站模式”? 在西门子A&D产品支持网站是否可以下载关于ET200M的手册? 在S7-400上怎样安装冗余电源? UDT改变后怎样更新使用UDT产生的数据块。 为什么在FB块中使用OUT变量赋值被调用FB块的IN变量时出现错误信息34:4469? 如何查看4-mation导入-导出错误 不能正确引导8212-1QU IBM/Lenovo M52 ThinkCentre 实时趋势更新缓慢的原因 如何保存变量名字典CSV文件的格式

DDU6871 DW6851 DX6831 DLP Projector Remote Communi

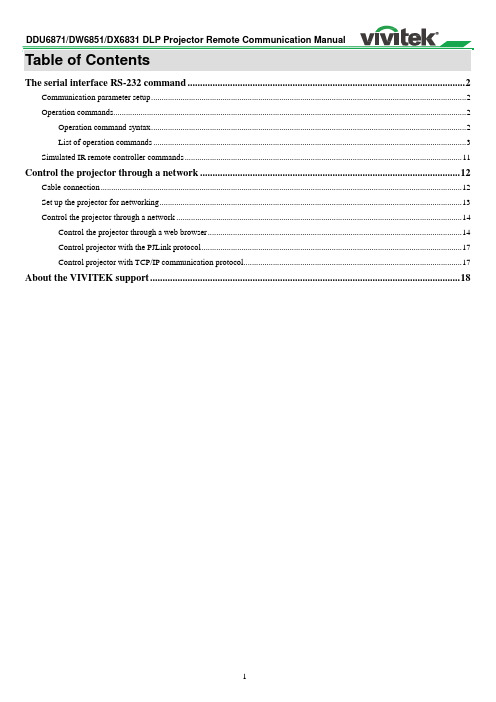

The serial interface RS-232 command (2)Communication parameter setup (2)Operation commands (2)Operation command syntax (2)List of operation commands (3)Simulated IR remote controller commands (11)Control the projector through a network (12)Cable connection (12)Set up the projector for networking (13)Control the projector through a network (14)Control the projector through a web browser (14)Control projector with the PJLink protocol (17)Control projector with TCP/IP communication protocol (17)About the VIVITEK support (18)This controller supports projectors with a RS-232 serial interface. There exist two types of serial commands:Operation command: Available menu options are INPUT, PICTURE, LAMP, ALIGNMENT, CONTROL, SERVICE, and OTHERS.Simulated IR remote controller commands: Controls projector with serial command analog IR remote controller and its control keys.Communication parameter setupYou can use the serial control command to input commands for projector control or retrieve its operational data through Windows client terminal software, e.g. Hyper Terminal, with ASCII characters.You need to set up the following communication parameters in advance:Item Parameter:Bit per Second 115200 (default), 57600, 38400, 19200, 14400, 9600, 4800, 2400, 1200bpsData Bit 8-bitParity NoneStop Bit 1Flow Control NonePort 7000Caution:The terminal software does not return every command input characterThe transmission performance varies with the matching length of RS-232 cable and transmission speed.Please select proper transmission from the OSD menu.Operation commandsOperation command syntaxAn operation command is prefixed by character "op", followed by control commands and settings separated by space blank [SP], and ended by carriage return pair "CR" and "ASCII hex 0D".Syntax of serial control commands: op[SP]<operation command>[SP]<Setting Value>[CR]op :A constant indicating this is an operation command.[SP] :Indicate one blank space.[CR] :Indicate the command ending carriage return pair "CR" and "ASCII hex 0D".Setting value : Settings of operation commandTypes of setup strings Characters of settings DescriptionQuery current setup ? Question mark "?" indicates querying current setup Setup = <settings> Syntax of settings: Symbol "=" suffixed with setupvaluesIncrease setup order of adjustment items + Some settings are changed in steps. Symbol "+"indicates changing one step upDecrease setup order of adjustment items - Some settings are changed in steps. Symbol "-"indicates changing one step downExecute operation command None Certain operation commands execute after inputwithout further setting or regulators. Examples:Control items Input command row Projector return messageQuery current brightnesssettingsop bright ? [CR] OP BRIGHT = 101Set up brightness op bright = 127 [CR] OP BRIGHT = 127Set up input signal source toHDMIop input.sel = 0 [CR] OP INPUT.SEL = 0Caution:When controlling the projector to execute multiple commands, make sure the return message of the last command is received before sending out the next one.List of operation commandsInputOSD function OperationcommandSettings/return values NoteInput Select input.sel ?= 0 = HDMI1 = DVI2 = VGA3 = Component / BNC4 = DisplayPort5 = Digital Do not apply when the project is in standby modea. Standby modeb. When the blank function is activatedTest Pattern pattern ?= 0 = Color Bar1 = Cross Hatch2 = Burst3 = Red (TI)4 = Green (TI)5 = Blue (TI)6 = WHITE (TI)7 = BLACK (TI)8 = HRamp (TI)9 = Red (uncorrected)10 = Green (uncorrected)11 = Blue (uncorrected)12 = White (uncorrected)13 = Black (uncorrected)14 = Off Do not apply when the project is in standby modeColor Space color.space ?= 0 = Auto1 = YcbCr (Rec. 601)2 = YPbPr (Rec. 709)3 = RGB-PC (0-255)4 = RGB-Video (16-235) Do not apply when the project is in standby mode or the input signal is not yet locked.Input Lock input.lock ?= 0 = Auto1 = 48 Hz2 = 50 Hz3 = 60 Hz Do not apply when the project is in standby mode or the input signal is not yet locked.Background no.signal ?= 0 = Logo1 = Blue2 = Black3 = White Do not apply when the project is in standby modeLAMPSOSD function OperationcommandSettings/return values NoteLamp Mode lamps ?= 0 = Dual1 = Lamp12 = Lamp23 = Singlea. Do not apply when the project is instandby modeb. Do not apply when the project is incooling or lighting up status.Please send control commandafter the said commands arecompleted.Lamp Power lamp.mode ?= 0 = Standard1 = Economy2 = Custom Power LevelDo not apply when the project is instandby modeCustom Lamp Power lamp.pwr ?= 0-31 (75 % ~ 100.0 %) Do not apply when the project is instandby modeHigh Altitude altitude ?= 0 = Off1 = OnDo not apply when the project is instandby modeLamp 1 Status lamp1.stat ? 0 = Off1 = On Do not apply when the project is in standby modeLamp 2 Status lamp2.stat ? 0 = Off1 = On Do not apply when the project is in standby modeALIGNMENTOSD function OperationcommandSettings/return values NoteProjection Mode proj.mode ?= 0 = Front1 = Rear2 = Ceiling + Front3 = Ceiling + Rear4 = Up + Front5 = Down + Front Do not apply when the project is in standby modeZoom zoomio+- The camera control command does not apply when the projector is in standby mode.CONTROLOSD function OperationcommandSettings/return values NoteStandby Mode .pow ?= 0 = Off (Standard StandbyMode)1 = On (ECO StandbyMode)Auto Power Off auto.powoff ?= 0 = Off1 = On Do not apply when the projector is in standby mode.Auto Power On auto.powon ?= 0 = Off1 = On IP Address net.ipaddr ?= <String> Subnet net.subnet ?= <String> Gateway net.gateway ?= <String> DHCP net.dhcp ?= 0 = Off1 = OnBaud Rate rs232.speed ?= 0 = 115200 bps1 = 57600 bps2 = 38400 bps3 = 19200 bps4 = 14400 bps5 = 9600 bps6 = 4800 bps7 = 2400 bps8 = 1200 bps This command is not required as the setting is default to "9600" whenRS232 commands are sent to the projector through RJ45 cable by external integrated video and control signal transmission box.OthersSettings/return values Note OSD function OperationcommandPower On power.on (execute)Power Off power.off (execute)Projector Status status ? 0 = standby1 = warm up2 = imaging3 = cooling4 = resetFocus focus +-Zoom zoomio +-Vertical Lens Shift Vert.offset +-Horizental Lens Shift horiz.offset +-Center Lens lens.center (execute)Shutter shutter +-Caution: The projector returns string "NA" when the input command does not apply to current projector status or setup.This control command simulates the IR remote controller and its control keys. It shares the same syntax of operation command. It begins with characters "ky", followed by control commands and settings separated by space blank [SP], and ended by carriage return pair "CR" and "ASCII hex 0D".Control command syntax:ky[SP]<operation command>[CR]Examples:Power On ky power.on [CR]Power Off ky power.off [CR]List of simulated IR remote controller commandsDescriptionItem Function Operationcommand1 Power On power.on Power On2 Power Off power.off Power OffOSDmenu3 Menu menu Display4 Exit exit Exitkey5 Enter enter ENTER6 Up up Move cursor upward or change upward7 Down down Move cursor downward or change downward8 Left left Move cursor to the left or change to the left9 Right right Move cursor to the right or change to the rightThis machine supports the following methods in remote controlling the projector through a network: Control projector through web browser.Control projector with RS-232 control or simulated IR commands via TCP/IP communication protocol.Control projector with PJLink standard commands.Cable connectionYou may connect the projector to a PC or to an external integrated video and control signal transmission box through LAN for remote control.Connect the projector to a PCSee figure below for connecting the projector to a PC in RJ-45 cable for control.For connection through LAN, connect the PC to a hub through to the projector's Digital/Lan port.Connect with an external integrated video and control signal transmission boxYou may connect the projector to an external integrated video and control signal transmission box with RJ-45 cable for concurrent video and networking control signal transmission.Please connect the PC to the input end of the transmission box with one RJ-45 cable and the output end of the transmission box to the Digital/LAN input end of the projector with another RJ-45 cable.In case the remote network control is not connected to LAN or DHCP or the LAN is not activated, connect as illustrated below:Caution:In case the remote network control is not connected to LAN or DHCP or the LAN is not activated, set DHCP option to Off and then select Apply.The DHCP service assigns IP address and settings to devices automatically and keeps IPAddress, Subnet, and Gateway options away from editing. In case the DHCP service of the LAN is not activated, set up the network manually.Use ▲▼ and the Enter button to select Network and network settings:IP Address: To specify an IP address, press the Enter button to show the IP address input window. Use the ◄► button to select the number in the address to be changed. Use the ▲▼ button to increase or decrease the number in the IP address.Subnet: Set the subnet. The input method is the same as the IP address. Gateway: Set the gateway. The input method is the same as the IP address.DHCP: Enable or disable the DHCP service.When DHCP is set to ON, the DHCP server of the domain will assign an IP address to the projector. The IP address will appear in the IP address window and you don't need to make anyinput.Otherwise, the domain does not or cannot assign any IP address, and 0. 0. 0. 0 is shown on the IP address window. Apply: Select this button and press Enter. It takes the projector several seconds to execute the change of the network setting till the following message disappears.Please contact your network administrator in case the network remains disconnected.Control the projector through a web browserOpen the web browser of your control PC, type the projector's IP address, the projector's web server homepage displays with the following four options:Projector Status: Current projector settings.Alert Mail Setup:Settings for projector abnormality email reminders.In case of any abnormality the project sends emails to preset users.Crestron: Crestron compatible web browser control pagesPJLink: Set up password for PJLink connection in this page.Projector StatusIllustration below goes with projector at IP address "192.168.0.100":SystemModel Name : Projector model name.Software Version : The version of the software installed in the projectorSystem Status : Current projector startup statusDisplay Source : Display the current source.Lamp 1 Hours : Display the usage hours of Lamp 1Lamp 2 Hours : Display the usage hours of Lamp 2Error Status : Indicate projector diagnosis messageNetwork control setup message (RJ-45 Version)LAN Version : Network control software version numberIP address : Projector IP address setupSubnet mask : Projector subnet address setupDefault gateway : Projector gateway setupDNS server : Projector DNS server setupMAC address : Projector MAC address setupThis projector can send emails with projector abnormality messages to preset users. Set up the projector before enabling this function:SMPT Server : Set up SMTP server name as the projector sends email via a SMTP server.Port : Set up transmission portUser Name : Input target user name for the projector to send the reminder email to, through a SMTP server. Password : Input user password.E-mail Alert : Enable or Disable reminder email.From : Set up email address of the email sender.To : Set up email address of the email recipient.CC : Set up email address of the email CC recipient.Projector Name : Set up projector name or ID.Location : Set up projector installation location.Apply : Confirm your settings.Press this button to save changes you have made.Send Test Mail : Send test email.The reminder email is sent only in the event of a projector error.Press this button to validate email settings after setup is completed.Power: Press this button to power on or off the projectorSource List: Switch projector input signal sources. Press the ▲ or ▼ arrow key to scroll through the dropdown list of available signal sourcesImage adjust optionsPress the ◄ or ► arrow key to scroll through available adjustment options.Freeze: Freeze current projection screen.The projection screen prompts the "Still open" message after the freeze function enabled.Press the Freeze button again to unfreeze the screen.Contrast: Click this button and the adjustment window displays. Click the ◄► arrow keys to adjust contrast.Brightness: Click this button and the adjustment window displays. Click the ◄► arrow keys to adjust brightness.Sharpness: Click this button and the adjustment window displays. Click the ◄► arrow key to adjust sharpness.Zoom: Zoom the projection image.Click the "+" key to zoom in and "-" to zoom out.You may click the four arrow keys in the window to move the zoomed projection image.Enter: Confirm and select function optionsMenu: Press to display OSD menu. Press again to exit it.Auto: Run the auto image adjustment function.Blank: Pause the image projection, i.e. the projection image is masked.Press again to resume the projection. Source: The signal source menu displays.Press to display signal source in the projection screen.Tool: See user manual included with the products you want to use together with your Crestron equipment for its setup Info: Display current projector status and Crestron setup.Control projector with the PJLink protocolPJLink is a standard designed by the Japan Business Machine and Information System Industries Association (JBMA) for controlling projectors with genuine commands.A PJLink standard compliant projector from any supplier can be controlled with these genuine commands.This product supports PJLink control commands. Please set up password for PJLink connection in this page.PJLink Security : Select On to enable PJLink password or Off to disable it.Password : Set up password at length up to 32 characters.For details on PJLink standard commands and connection methods, please visit the PJLink official web site.Control projector with TCP/IP communication protocolThis projector supports TCP/IP communication protocol which enables you to send RS-232 operation commands or simulated IR commands to control projectors connected with RJ45 cable via terminal connection application software, e.g. Tera Term.Please set up IP address and port number with the terminal connection application software before controlling your projector with TCP/IP communication protocol:IP Address: IP address of projectorPort: Please set transmission port number to 7000See the section on serial interface RS-232 control commands for details on RS-232 operation commands or simulated IR commands.If you cannot find solutions from this user guideline, please contact us using the contact information below: North AmericaVivitek Service Center15700 Don Julian Road, Suite BCity of Industry, CA. 91745U.S.ATel: 855-885-2378 (Toll-Free)Email:***************************URL: Europe and AfricaVivitek Service & SupportZandsteen 152132 MZ HoofddorpThe NetherlandsTel: +31 20 655 0960Email:******************URL: www.vivitek.euChinaVivitek Service Center201209, Room 1802, 18/F, Cimic Tower, No.1090, Century Avenue, Pudong, ShanghaiTel: 400-888-3526 (Toll-Free)Tel*************-142(Direct)Email:*******************.cnURL: Asia and TaiwanVIVITEK after-sales serviceVivitek Corporation, Co., Ltd.4F., No.186, Ruiguang Rd., Neihu Dist., Taipei City 11491TEL: 86-28-797-2088FAX: 86-26-600-2358E-mail:***********************.twURL: 。

NiosII常见问题解答

flash的数据线必须是双向引脚

地址线的连接需要小心,举个例子 对于地址线22位、数据线16位的flash器件而言,SOPC Builder生成 的NiosII系统顶层文件将包含23位的flash地址线:addr[22..0], 此时应当把flash器件地址线addr[21..0]与顶层文件的 addr[22..1]互连;

z 内建的CFI Table错误识别和重载

对于已知的某些flash器件的CFI Table问题,flash programmer已经 包含了校对代码来识别和纠正它们;此种情况下,对flash programmer使

本文档版权归作者所有,未经作者同意不得翻印、抄袭或公开传播;转载或引用请征求作者同意.

Value does not match;

运行NiosII IDE中内嵌的软件模板‘Memory Test’,执行‘Test Flash’

操作,如果该操作返回失败,则可能是下面两个原因导致的:

z 目标板的物理连接有问题,例如

flash器件的引脚与FPGA对应引脚互连不正确

flash器件的供电有问题

目 录 ......................................5

1 硬件开发....................................7

1.1 Flash Programmer ........................7

1.1.1 No CFI Table...........................7

作者:蔡伟纲

NiosII 之

常见问题解答

作者: 蔡伟纲

本文档版权归作者所有,未经作者同意不得翻印、抄袭或公开传播;转载或引用请征求作者同意.

CFI(CommonFlashInterface)简介

CFI(CommonFlashInterface)简介CFI(Common Flash Interface)简介【什么是CFI】CFI(Common Flash Interface),是JEDEC(Joint Electron Device Engineering Council,电子器件工程联合委员会)制定的一个接口,用来帮助程序读取Flash的制造商ID和设备ID,确定Flash的大小,获得flash的各个物理特性,比如block块的擦除时间等等。

【为什么需要这个CFI】在应用CFI之前,Flash器件的有关信息都储存在系统软件的表格中。

当有新的器件发布时,一般必须修改软件来添加该器件的描述信息。

CFI出现后,工程师们正在利用CFI来构建代码,它不仅能够运行在现在的Flash存储器上,而且随时准备着应用在下一代的低成本版本上。

这使得原始设备制造商能够在低成本Flash存储器设备可用时使用它而不必重写代码。

由于生产Flash Memory的半导体制造商众多,不同厂商Flash Memory产品的操作命令集和电气参数又千差万别,这些人在设计硬件的时候,已经在阵脚的兼容性等方面,做了足够多的文章,做得很好了,但是与此对应的软件方面,由于硬件升级,软件都要改动很大,这给Flash Memory的开发设计人员和OEM制造商带来许多不便。

为了对现有的Flash Memory的产品进行升级或使用其它公司的Flash Memory产品替换,必须对原有的程序代码和硬件结构进行修改。

所以,由Intel、AMD、Sharp和Fujutsu出面,通过JEDEC(Joint Electron Device Engineering Council,电子器件工程联合委员会)制定了这个CFI。

【CFI的好处】它可以使系统软件查询已安装的Flash Memory器件的各种参数,包括器件阵列结构参数、电气和时间参数以及器件支持的功能等。

龙丘线阵ccd模块串口程序

PORTB_PB1 SI

PTAD_AD0 AO

============================================

串口115200,n,8,1

============================================

TSL1401线性CCD测试步骤:

// ----------------------

//不是很精确,保证一定的数量级

void Dly_us(byte us)

{

byte ii;

for(ii=0;ii<us;ii++)

{

#ifdef BUSCLOCK32M

_asm(nop);_asm(nop);_asm(nop);_asm(nop);

#include <MC9S12XS128.h> /* derivative information */

#include "LQprintp.h"

#include <stdio.h>

#pragma LINK_INFO DERIVATIVE "mc9s12xs128"

byte ADV[128]={0,0}; //声明数组,用于存放采集的线性数值

TSL_CLK=1;//上升沿

Dly_us(8-i/8+1); //合理延时

}

for(i=0;i<64;i++)

{

TSL_CLK=0;//下降沿

Dly_us(i/8+1); //合理延时

while(!ATD0STAT0_SCF);//等待转换结束

MX29LV800CBXBI-70G

MX29LV800C T/B8M-BIT [1Mx8/512K x16] CMOS SINGLE VOLTAGE3V ONLY FLASH MEMORY•Ready/Busy# pin (RY/BY#)- Provides a hardware method of detecting program or erase operation completion •Sector protection- Hardware method to disable any combination of sectors from program or erase operations- Temporary sector unprotected allows code changes in previously locked sectors.•CFI (Common Flash Interface) compliant- Flash device parameters stored on the device and provide the host system to access•100,000 minimum erase/program cycles•Latch-up protected to 100mA from -1V to VCC+1V •Boot Sector Architecture - T = Top Boot Sector - B = Bottom Boot Sector •Package type:- 44-pin SOP - 48-pin TSOP- 48-ball CSP (6 x 8mm)- 48-ball CSP (4 x 6mm)- All Pb-free devices are RoHS Compliant •Compatibility with JEDEC standard- Pinout and software compatible with single-power supply Flash•10 years data retentionFEATURES•Extended single - supply voltage range 2.7V to 3.6V •1,048,576 x 8/524,288 x 16 switchable •Single power supply operation- 3.0V only operation for read, erase and program operation•Fast access time: 45R/55R/70/90ns •Low power consumption- 30mA maximum active current - 0.2uA typical standby current •Command register architecture- Byte/word Programming (9us/11us typical)- Sector Erase (Sector structure 16K-Bytex1,8K-Bytex2, 32K-Bytex1, and 64K-Byte x15)•Fully compatible with MX29LV800BT/BB device •Auto Erase (chip & sector) and Auto Program- Automatically erase any combination of sectors with Erase Suspend capability- Automatically program and verify data at specified address•Erase suspend/Erase Resume- Suspends sector erase operation to read data from,or program data to, any sector that is not being erased,then resumes the erase •Status Reply- Data# polling & Toggle bit for detection of program and erase operation completionGENERAL DESCRIPTIONThe MX29LV800C T/B is a 8-mega bit Flash memory organized as 1M bytes of 8 bits or 512K words of 16bits. MXIC's Flash memories offer the most cost-effec-tive and reliable read/write non-volatile random access memory. The MX29LV800C T/B is packaged in 44-pin SOP , 48-pin TSOP , and 48-ball CSP . It is designed to be reprogrammed and erased in system or in standard EPROM programmers.The standard MX29LV800C T/B offers access time as fast as 45ns, allowing operation of high-speed micropro-cessors without wait states. To eliminate bus conten-tion, the MX29LV800C T/B has separate chip enable (CE#) and output enable (OE#) controls.MXIC's Flash memories augment EPROM functionality with in-circuit electrical erasure and programming. The MX29LV800C T/B uses a command register to manage this functionality. The command register allows for 100%TTL level control inputs and fixed power supply levels during erase and programming, while maintaining maxi-mum EPROM compatibility.MXIC Flash technology reliably stores memory contents even after 100,000 erase and program cycles. The MXIC cell is designed to optimize the erase and programming mechanisms. In addition, the combination of advanced tunnel oxide processing and low internal electric fields for erase and program operations produces reliable cy-cling. The MX29LV800C T/B uses a 2.7V~3.6V VCC supply to perform the High Reliability Erase and auto Program/Erase algorithms.The highest degree of latch-up protection is achieved with MXIC's proprietary non-epi process. Latch-up pro-tection is proved for stresses up to 100 milliamperes on address and data pin from -1V to VCC + 1V.MX29LV800C T/BPIN CONFIGURATIONSPIN DESCRIPTIONSYMBOL PIN NAME A0~A18Address Input Q0~Q14Data Input/OutputQ15/A-1Q15(Word mode)/LSB addr(Byte mode)CE#Chip Enable Input WE#Write Enable Input BYTE#Word/Byte Selection input RESET#Hardware Reset Pin OE#Output Enable Input RY/BY#Ready/Busy OutputVCC Power Supply Pin (2.7V~3.6V)GND Ground PinNCPin Not Connected Internally48 TSOP (Standard Type) (12mm x 20mm)44 SOP(500 mil)234567891011121314151617181920212244434241403938373635343332313029282726252423RY/BY#A18A17A7A6A5A4A3A2A1A0CE#GND OE#Q0Q8Q1Q9Q2Q10Q3Q11RESET#WE#A8A9A10A11A12A13A14A15A16BYTE#GND Q15/A-1Q7Q14Q6Q13Q5Q12Q4VCCM X 29L V 800C T /C BA15A14A13A12A11A10A9A8NC NC WE#RESET#NC NC RY/BY#A18A17A7A6A5A4A3A2A1123456789101112131415161718192021222324A16BYTE#GND Q15/A-1Q7Q14Q6Q13Q5Q12Q4VCC Q11Q3Q10Q2Q9Q1Q8Q0OE#GND CE#A0484746454443424140393837363534333231302928272625MX29LV800CT/CBMX29LV800C T/BMX29LV800C T/BBLOCK STRUCTURETABLE 1: MX29LV800CT SECTOR ARCHITECTURE Note: Byte mode:address range A18:A-1, word mode:address range A18:A0.Sector Sector SizeAddress range Sector AddressByte Mode Word ModeByte Mode (x8)Word Mode (x16)A18A17A16A15A14A13A12SA064Kbytes 32Kwords 00000h-0FFFFh 00000h-07FFFh 0000X X X SA164Kbytes 32Kwords 10000h-1FFFFh 08000h-0FFFFh 0001X X X SA264Kbytes 32Kwords 20000h-2FFFFh 10000h-17FFFh 0010X X X SA364Kbytes 32Kwords 30000h-3FFFFh 18000h-1FFFFh 0011X X X SA464Kbytes 32Kwords 40000h-4FFFFh 20000h-27FFFh 0100X X X SA564Kbytes 32Kwords 50000h-5FFFFh 28000h-2FFFFh 0101X X X SA664Kbytes 32Kwords 60000h-6FFFFh 30000h-37FFFh 0110X X X SA764Kbytes 32Kwords 70000h-7FFFFh 38000h-3FFFFh 0111X X X SA864Kbytes 32Kwords 80000h-8FFFFh 40000h-47FFFh 1000X X X SA964Kbytes 32Kwords 90000h-9FFFFh 48000h-4FFFFh 1001X X X SA1064Kbytes 32Kwords A0000h-AFFFFh 50000h-57FFFh 1010X X X SA1164Kbytes 32Kwords B0000h-BFFFFh 58000h-5FFFFh 1011X X X SA1264Kbytes 32Kwords C0000h-CFFFFh 60000h-67FFFh 1100X X X SA1364Kbytes 32Kwords D0000h-DFFFFh 68000h-6FFFFh 1101X X X SA1464Kbytes 32Kwords E0000h-EFFFFh 70000h-77FFFh 1110X X X SA1532Kbytes 16Kwords F0000h-F7FFFh 78000h-7BFFFh 11110X X SA168Kbytes 4Kwords F8000h-F9FFFh 7C000h-7CFFFh 1111100SA178Kbytes 4Kwords FA000h-FBFFFh 7D000h-7DFFFh 1111101SA1816Kbytes8KwordsFC000h-FFFFFh7E000h-7FFFFh111111XMX29LV800C T/BTABLE 2: MX29L V800CB SECTOR ARCHITECTURESector Sector Size Address range Sector Address Byte Mode Word Mode Byte Mode (x8)Word Mode (x16)A18A17A16A15A14A13A12 SA016Kbytes8Kwords00000h-03FFFh00000h-01FFFh000000X SA18Kbytes4Kwords04000h-05FFFh02000h-02FFFh0000010 SA28Kbytes4Kwords06000h-07FFFh03000h-03FFFh0000011 SA332Kbytes16Kwords08000h-0FFFFh04000h-07FFFh00001X X SA464Kbytes32Kwords10000h-1FFFFh08000h-0FFFFh0001X X X SA564Kbytes32Kwords20000h-2FFFFh10000h-17FFFh0010X X X SA664Kbytes32Kwords30000h-3FFFFh18000h-1FFFFh0011X X X SA764Kbytes32Kwords40000h-4FFFFh20000h-27FFFh0100X X X SA864Kbytes32Kwords50000h-5FFFFh28000h-2FFFFh0101X X X SA964Kbytes32Kwords60000h-6FFFFh30000h-37FFFh0110X X X SA1064Kbytes32Kwords70000h-7FFFFh38000h-3FFFFh0111X X X SA1164Kbytes32Kwords80000h-8FFFFh40000h-47FFFh1000X X X SA1264Kbytes32Kwords90000h-9FFFFh48000h-4FFFFh1001X X X SA1364Kbytes32Kwords A0000h-AFFFFh50000h-57FFFh1010X X X SA1464Kbytes32Kwords B0000h-BFFFFh58000h-5FFFFh1011X X X SA1564Kbytes32Kwords C0000h-CFFFFh60000h-67FFFh1100X X X SA1664Kbytes32Kwords D0000h-DFFFFh68000h-6FFFFh1101X X X SA1764Kbytes32Kwords E0000h-EFFFFh70000h-77FFFh1110X X X SA1864Kbytes32Kwords F0000h-FFFFFh78000h-7FFFFh1111X X XNote: Byte mode:address range A18:A-1, word mode:address range A18:A0.MX29LV800C T/BBLOCK DIAGRAMCONTROL INPUT LOGICPROGRAM/ERASE HIGH VOLTAGEWRITE STATE MACHINE (WSM)STATE REGISTERFLASH ARRAYX-DECODERADDRESS LATCHAND BUFFERY-PASS GATEY -DECODERARRAY SOURCE HVCOMMAND DATADECODERCOMMAND DATA LATCHI/O BUFFERPGM DATA HVPROGRAM DATA LATCHSENSE AMPLIFIERQ0-Q15/A-1A0-A18CE#OE#WE#RESET#MX29LV800C T/BAUTOMATIC PROGRAMMINGThe MX29L V800C T/B is byte programmable using the Automatic Programming algorithm. The Automatic Pro-gramming algorithm makes the external system do not need to have time out sequence nor to verify the data programmed. The typical chip programming time at room temperature of the MX29LV800C T/B is less than 10 seconds.AUTOMATIC PROGRAMMING ALGORITHMMXIC's Automatic Programming algorithm requires the user to only write program set-up commands (including 2 unlock write cycle and A0H) and a program command (program data and address). The device automatically times the programming pulse width, provides the pro-gram verification, and counts the number of sequences.A status bit similar to DA TA# polling and a status bit toggling between consecutive read cycles, provide feed-back to the user as to the status of the programming operation. Refer to write operation status, table 8, for more information on these status bits.AUTOMATIC CHIP ERASEThe entire chip is bulk erased using 10 ms erase pulses according to MXIC's Automatic Chip Erase algorithm. T ypical erasure at room temperature is accomplished in less than 25 second. The Automatic Erase algorithm automatically programs the entire array prior to electri-cal erase. The timing and verification of electrical erase are controlled internally within the device. AUTOMATIC SECTOR ERASEThe MX29L V800C T/B is sector(s) erasable using MXIC's Auto Sector Erase algorithm. The Automatic Sector Erase algorithm automatically programs the specified sector(s) prior to electrical erase. The timing and verifi-cation of electrical erase are controlled internally within the device. An erase operation can erase one sector, multiple sectors, or the entire device.AUTOMATIC ERASE ALGORITHMMXIC's Automatic Erase algorithm requires the user to write commands to the command register using stan-dard microprocessor write timings. The device will auto-matically pre-program and verify the entire array. Then the device automatically times the erase pulse width, provides the erase verification, and counts the number of sequences. A status bit toggling between consecutive read cycles provides feedback to the user as to the sta-tus of the erasing operation.Register contents serve as inputs to an internal state-machine which controls the erase and programming cir-cuitry. During write cycles, the command register inter-nally latches address and data needed for the program-ming and erase operations. During a system write cycle, addresses are latched on the falling edge, and data are latched on the rising edge of WE# or CE#, whichever happens first.MXIC's Flash technology combines years of EPROM experience to produce the highest levels of quality, reli-ability, and cost effectiveness. The MX29LV800C T/B electrically erases all bits simultaneously using Fowler-Nordheim tunneling. The bytes are programmed by us-ing the EPROM programming mechanism of hot elec-tron injection.During a program cycle, the state-machine will control the program sequences and command register will not respond to any command set. During a Sector Erase cycle, the command register will only respond to Erase Suspend command. After Erase Suspend is completed, the device stays in read mode. After the state machine has completed its task, it will allow the command regis-ter to respond to its full command set.AUTOMATIC SELECTThe auto select mode provides manufacturer and device identification, and sector protection verification, through identifier codes output on Q7~Q0. This mode is mainly adapted for programming equipment on the device to be programmed with its programming algorithm. When pro-gramming by high voltage method, automatic select mode requires VID (11.5V to 12.5V) on address pin A9 and other address pin A6, A1 and A0 as referring to Table 3. In addition, to access the automatic select codes in-sys-tem, the host can issue the automatic select command through the command register without requiring VID, as shown in table 5.To verify whether or not sector being protected, the sec-tor address must appear on the appropriate highest orderMX29LV800C T/Baddress bit (see T able 1 and T able 2). The rest of addressbits, as shown in table 3, are don't care. Once all neces-sary bits have been set as required, the programmingequipment may read the corresponding identifier code onQ7~Q0.TABLE 3. MX29LV800C T/B AUTO SELECT MODE OPERATIONA18A11A9A8A6A5A1A0Description Mode CE#OE#WE#| | | |Q15~Q0A12A10A7A2Manufacturer Code L L H X X VID X L X L L C2H Read Device ID Word L L H X X VID X L X L H22DAH Silicon(Top Boot Block)Byte L L H X X VID X L X L H XXDAHID Device ID Word L L H X X VID X L X L H225BH (Bottom Boot Block)Byte L L H X X VID X L X L H XX5BHXX01H Sector Protection L L H SA X VID X L X H L(protected) Verification XX00H(unprotected) NOTE:SA=Sector Address, X=Don't Care, L=Logic Low, H=Logic HighMX29LV800C T/BQUERY COMMAND AND COMMON FLASH INTERFACE (CFI) MODEMX29L V800C T/B is capable of operating in the CFI mode.This mode all the host system to determine the manu-facturer of the device such as operating parameters and configuration. T wo commands are required in CFI mode.Query command of CFI mode is placed first, then the Reset command exits CFI mode. These are described in T able 4.TABLE 4-1. CFI mode: Identification Data Values(All values in these tables are in hexadecimal)DescriptionAddress Address Data (Byte Mode)(Word Mode)Query-unique ASCII string "QRY"201000512211005224120059Primary vendor command set and control interface ID code 2613000228140000Address for primary algorithm extended query table 2A1500402C160000Alternate vendor command set and control interface ID code (none)2E17000030180000Address for secondary algorithm extended query table (none)32190000341A0000TABLE 4-2. CFI Mode: System Interface Data Values(All values in these tables are in hexadecimal)DescriptionAddress Address Data (Byte Mode)(Word Mode)VCC supply, minimum (2.7V)361B 0027VCC supply, maximum (3.6V)381C 0036VPP supply, minimum (none)3A 1D 0000VPP supply, maximum (none)3C 1E 0000Typical timeout for single word/byte write (2N us)3E 1F 0004Typical timeout for Minimum size buffer write (2N us)40200000Typical timeout for individual block erase (2N ms)4221000A Typical timeout for full chip erase (2N ms)44220000Maximum timeout for single word/byte write times (2N X Typ)46230005Maximum timeout for buffer write times (2N X Typ)48240000Maximum timeout for individual block erase times (2N X Typ)4A 250004Maximum timeout for full chip erase times (not supported)4C 260000The single cycle Query command is valid only when the device is in the Read mode, including Erase Suspend,Standby mode, and Read ID mode; however, it is ignored otherwise.The Reset command exits from the CFI mode to the Read mode, or Erase Suspend mode, or read ID mode.The command is valid only when the device is in the CFI mode.MX29LV800C T/B TABLE 4-3. CFI Mode: Device Geometry Data Values(All values in these tables are in hexadecimal)Description Address Address Data(Byte Mode)(Word Mode) Device size (2N bytes)4E270014 Flash device interface code (refer to the CFI publication 100)5028000252290000 Maximum number of bytes in multi-byte write (not supported)542A0000562B0000 Number of erase block regions582C0004 Erase block region 1 information (refer to the CFI publication 100)5A2D00005C2E00005E2F004060300000 Erase block region 2 information62310001643200006633002068340000 Erase block region 3 information6A3500006C3600006E37008070380000 Erase block region 4 information7239000E743A0000763B0000783C0001 TABLE 4-4. CFI Mode: Primary Vendor-Specific Extended Query Data Values(All values in these tables are in hexadecimal)Description Address Address Data(Byte Mode)(Word Mode) Query-unique ASCII string "PRI"804000508241005284420049 Major version number, ASCII86430031 Minor version number, ASCII88440030 Address sensitive unlock (0=required, 1= not required)8A450000 Erase suspend (2= to read and write)8C460002 Sector protect (N= # of sectors/group)8E470001 Temporary sector unprotected (1=supported)90480001 Sector protect/unprotected scheme92490004 Simultaneous R/W operation (0=not supported)944A0000 Burst mode type (0=not supported)964B0000 Page mode type (0=not supported)984C0000MX29LV800C T/BTABLE 5. MX29L V800C T/B COMMAND DEFINITIONSFirst Bus Second Bus Third Bus Fourth Bus Fifth Bus Sixth Bus Command Bus Cycle Cycle Cycle Cycle Cycle CycleCycle Addr Data Addr Data Addr Data Addr Data Addr Data Addr Data Reset 1XXXH F0HRead1RA RDRead Silicon ID Word4555H AAH2AAH55H555H90H ADI DDIByte4AAAH AAH555H55H AAAH90H ADI DDISector Protect Word4555H AAH2AAH55H555H90H(SA)XX00HVerify x02H XX01HByte4AAAH AAH555H55H AAAH90H(SA)00Hx04H01HProgram Word4555H AAH2AAH55H555H A0H PA PDByte4AAAH AAH555H55H AAAH A0H PA PDChip Erase Word6555H AAH2AAH55H555H80H555H AAH2AAH55H555H10H Byte6AAAH AAH555H55H AAAH80H AAAH AAH555H55H AAAH10H Sector Erase Word6555H AAH2AAH55H555H80H555H AAH2AAH55H SA30H Byte6AAAH AAH555H55H AAAH80H AAAH AAH555H55H SA30H Sector Erase Suspend1XXXH B0HSector Erase Resume1XXXH30HCFI Query Word155H98Byte1AAH98Note:1.ADI = Address of Device identifier; A1=0, A0 = 0 for manufacturer code,A1=0, A0 = 1 for device code. A2-A18=do not care.(Refer to table 3)DDI = Data of Device identifier : C2H for manufacture code, 22DA/DA(T op), and 225B/5B(Bottom) for device code.X = X can be VIL or VIHRA=Address of memory location to be read.RD=Data to be read at location RA.2.P A = Address of memory location to be programmed.PD = Data to be programmed at location P A.SA = Address of the sector.3.The system should generate the following address patterns: 555H or 2AAH to Address A10~A0 in word mode/AAAH or555H to Address A10~A-1 in byte mode.Address bit A11~A18=X=Don't care for all address commands except for Program Address (PA) and Sector Address (SA).Write Sequence may be initiated with A11~A18 in either state.4.For Sector Protect Verify operation: If read out data is 01H, it means the sector has been protected. If read out data is 00H,it means the sector is still not being protected.5.Any number of CFI data read cycle are permitted.MX29LV800C T/BTABLE 6. MX29L V800C T/B BUS OPERATIONNOTES:1. Manufacturer and device codes may also be accessed via a command register write sequence. Refer to T able 5.2. VID is the Silicon-ID-Read high voltage, 11.5V to 12.5V .3. Refer to T able 5 for valid Data-In during a write operation.4. X can be VIL or VIH.5. Code=00H/XX00H means unprotected.Code=01H/XX01H means protected.6.A18~A12=Sector address for sector protect.7.The sector protect and chip unprotected functions may also be implemented via programming equipment.COMMAND DEFINITIONSDevice operations are selected by writing specific ad-dress and data sequences into the command register.Writing incorrect address and data values or writing them in the improper sequence will reset the device to theADDRESSQ8~Q15DESCRIPTION CE#OE#WE#RESET#A18A10A9A8A6A5A1A0Q0~Q7BYTE BYTE A12A11A7A2=VIH =VIL ReadLLHHAINDoutDoutQ8~Q14=High Z Q15=A-1Write L H L H AIN DIN(3)DIN ResetX X X L X High Z High Z High Z Temporary sector unlock X X X VID AIN DIN DIN High Z Output Disable L H H H X High Z High Z High Z Standby Vcc ±X X Vcc ± X High Z High Z High Z 0.3V 0.3V Sector Protect L H L VID SA X X X L X H L DIN X X Chip Unprotected L H L VID X X X X H X H L DIN X X Sector Protection VerifyLLHHSAXVIDXLXHLCODE(5)XXread mode. Table 5 defines the valid register command sequences. Note that the Erase Suspend (B0H) and Erase Resume (30H) commands are valid only while the Sector Erase operation is in progress.MX29LV800C T/BREQUIREMENTS FOR READING ARRAY DATAT o read array data from the outputs, the system must drive the CE# and OE# pins to VIL. CE# is the power control and selects the device. OE# is the output control and gates array data to the output pins. WE# should re-main at VIH.The internal state machine is set for reading array data upon device power-up, or after a hardware reset. This ensures that no spurious alteration of the memory con-tent occurs during the power transition. No command is necessary in this mode to obtain array data. Standard microprocessor read cycles that assert valid address on the device address inputs produce valid data on the de-vice data outputs. The device remains enabled for read access until the command register contents are altered. WRITE COMMANDS/COMMAND SEQUENCEST o program data to the device or erase sectors of memory , the system must drive WE# and CE# to VIL, and OE# to VIH.An erase operation can erase one sector, multiple sec-tors , or the entire device. T able indicates the address space that each sector occupies. A "sector address" consists of the address bits required to uniquely select a sector. The "Writing specific address and data commands or sequences into the command register initiates device operations. Table 1 defines the valid register command sequences. Writing incorrect address and data values or writing them in the improper sequence resets the device to reading array data. Section has details on erasing a sector or the entire chip, or suspending/resuming the erase operation.After the system writes the autoselect command se-quence, the device enters the autoselect mode. The sys-tem can then read autoselect codes from the internal register (which is separate from the memory array) on Q7-Q0. Standard read cycle timings apply in this mode. Refer to the Autoselect Mode and Autoselect Command Sequence section for more information.ICC2 in the DC Characteristics table represents the ac-tive current specification for the write mode. The "AC Characteristics" section contains timing specification table and timing diagrams for write operations.STANDBY MODEWhen using both pins of CE# and RESET#, the device enter CMOS Standby with both pins held at Vcc ± 0.3V. If CE# and RESET# are held at VIH, but not within the range of VCC ± 0.3V, the device will still be in the standby mode, but the standby current will be larger. During Auto Algorithm operation, Vcc active current (Icc2) is required even CE# = "H" until the operation is completed. The device can be read with standard access time (tCE) from either of these standby modes, before it is ready to read data.OUTPUT DISABLEWith the OE# input at a logic high level (VIH), output from the devices are disabled. This will cause the output pins to be in a high impedance state.RESET# OPERATIONThe RESET# pin provides a hardware method of reset-ting the device to reading array data. When the RESET# pin is driven low for at least a period of tRP, the device immediately terminates any operation in progress, tri-states all output pins, and ignores all read/write com-mands for the duration of the RESET# pulse. The device also resets the internal state machine to reading array data. The operation that was interrupted should be reinitiated once the device is ready to accept another command sequence, to ensure data integrityCurrent is reduced for the duration of the RESET# pulse. When RESET# is held at VSS±0.3V, the device draws CMOS standby current (ICC4). If RESET# is held at VIL but not within VSS±0.3V, the standby current will be greater.The RESET# pin may be tied to system reset circuitry.A system reset would that also reset the Flash memory, enabling the system to read the boot-up firmware from the Flash memory.If RESET# is asserted during a program or erase opera-tion, the RY/BY# pin remains a "0" (busy) until the inter-nal reset operation is complete, which requires a time of tREADY (during Embedded Algorithms). The system can thus monitor RY/BY# to determine whether the reset op-eration is complete. If RESET# is asserted when a pro-MX29LV800C T/Bgram or erase operation is completed within a time of tREADY (not during Embedded Algorithms). The system can read data tRH after the RESET# pin returns to VIH. Refer to the AC Characteristics tables for RESET# pa-rameters and to Figure 22 for the timing diagram.READ/RESET COMMANDThe read or reset operation is initiated by writing the read/ reset command sequence into the command register. Microprocessor read cycles retrieve array data. The de-vice remains enabled for reads until the command regis-ter contents are altered.If program-fail or erase-fail happen, the write of F0H will reset the device to abort the operation. A valid com-mand must then be written to place the device in the desired state.SILICON-ID READ COMMANDFlash memories are intended for use in applications where the local CPU alters memory contents. As such, manu-facturer and device codes must be accessible while the device resides in the target system. PROM program-mers typically access signature codes by raising A9 to a high voltage (VID). However, multiplexing high voltage onto address lines is not generally desired system de-sign practice.The MX29LV800C T/B contains a Silicon-ID-Read op-eration to supple traditional PROM programming meth-odology. The operation is initiated by writing the read silicon ID command sequence into the command regis-ter. Following the command write, a read cycle with A1=VIL, A0=VIL retrieves the manufacturer code of C2H/ 00C2H. A read cycle with A1=VIL, A0=VIH returns the device code of DAH/22DAH for MX29LV800CT, 5BH/ 225BH for MX29LV800CB.SET-UP AUTOMATIC CHIP/SECTOR ERASE COM-MANDSChip erase is a six-bus cycle operation. There are two "unlock" write cycles. These are followed by writing the "set-up" command 80H. T wo more "unlock" write cycles are then followed by the chip erase command 10H or sector erase command 30H.The Automatic Chip Erase does not require the device to be entirely pre-programmed prior to executing the Auto-matic Chip Erase. Upon executing the Automatic Chip Erase, the device will automatically program and verify the entire memory for an all-zero data pattern. When the device is automatically verified to contain an all-zero pat-tern, a self-timed chip erase and verify begin. The erase and verify operations are completed when the data on Q7 is "1" at which time the device returns to the Read mode. The system is not required to provide any control or tim-ing during these operations.When using the Automatic Chip Erase algorithm, note that the erase automatically terminates when adequate erase margin has been achieved for the memory array (no erase verification command is required).If the Erase operation was unsuccessful, the data on Q5 is "1" (see Table 8), indicating the erase operation ex-ceed internal timing limit.The automatic erase begins on the rising edge of the last WE# or CE# pulse, whichever happens first in the com-mand sequence and terminates when the data on Q7 is "1" at which time the device returns to the Read mode, or the data on Q6 stops toggling for two consecutive read cycles at which time the device returns to the Read mode.MX29LV800C T/BREADING ARRA Y DATAThe device is automatically set to reading array data after device power-up. No commands are required to re-trieve data. The device is also ready to read array data after completing an Automatic Program or Automatic Erase algorithm.After the device accepts an Erase Suspend command, the device enters the Erase Suspend mode. The sys-tem can read array data using the standard read tim-ings, except that if it reads at an address within erase-suspended sectors, the device outputs status data. Af-ter completing a programming operation in the Erase Suspend mode, the system may once again read array data with the same exception. See "Erase Suspend/Erase Resume Commands" for more information on this mode. The system must issue the reset command to re-en-able the device for reading array data if Q5 goes high, or while in the autoselect mode. See the "Reset Command" section, next.RESET COMMANDWriting the reset command to the device resets the de-vice to reading array data. Address bits are don't care for this command.The reset command may be written between the se-quence cycles in an erase command sequence before erasing begins. This resets the device to reading array data. Once erasure begins, however, the device ignores reset commands until the operation is complete.The reset command may be written between the se-quence cycles in a program command sequence before programming begins. This resets the device to reading array data (also applies to programming in Erase Sus-pend mode). Once programming begins, however, the device ignores reset commands until the operation is complete.The reset command may be written between the se-quence cycles in an SILICON ID READ command se-quence. Once in the SILICON ID READ mode, the reset command must be written to return to reading array data (also applies to SILICON ID READ during Erase Sus-pend).If Q5 goes high during a program or erase operation, writ-ing the reset command returns the device to reading ar-ray data (also applies during Erase Suspend).Pins A0A1Q15~Q8Q7Q6Q5Q4Q3Q2Q1Q0Code (Hex) Manufacture code Word VIL VIL00H1100001000C2HByte VIL VIL X11000010C2HDevice code Word VIH VIL22H1101101022DAHfor MX29L V800CT Byte VIH VIL X11011010DAHDevice code Word VIH VIL22H010********BHfor MX29L V800CB Byte VIH VIL X010110115BHSector Protection Word X VIH X0000000101H (Protected) Verification Byte X VIH X0000000000H (Unprotected) TABLE 7. SILICON ID CODE。

FC68(液晶显示手持单元的)程序注释