模 计数器verilog报告

verilog计数器实验报告

计数器1、实现目标及介绍实验实现了一个简易的计数器,计数范围可达899(0~899),通过key4按键计数,每按下一次,计数加一,百位数显示在led上,个位与十位显示在数码管上。

为十进制计数,数码管1计数到九后置零。

数码管2获得进位加一,数码管2到9后当再次获得个位进位时再次向百位进一,点亮led1,每百位点亮一个led。

此外key4为清零键,可随时按键清零。

2、效果展示计数99清零计数100视频展示(双击观看)3、代码实现与模块分析1.顶层模块module jishuqi(input wire clk,rst, //时钟和复位输入input wire key1, //拨码计output wire [7:0]led,output wire [8:0] segment_led_1,segment_led_2 //数码管输出);wire key_pulse;reg [7:0] cnt; //计时计数器reg [7:0] hud; //百位计数initial hud[7:0] <= 8'b11111111;always @(posedge clk or negedge rst)begin //数码管显示要按照十进制的方式显示if(!rst)begin cnt <= 8'h00;hud [7:0] <= 8'b11111111;endelse if(key_pulse)beginif(cnt[3:0] == 4'd9) //个位进位判断begincnt[3:0] <= 4'd0;if(cnt[7:4] == 4'd9 ) //十位进位判断begincnt[7:4] <= 4'd0;hud[7:0] <= hud[7:0] - 1'b1;endelsecnt[7:4] <= cnt[7:4] + 1'b1;endelse cnt[3:0] <= cnt[3:0] + 1'b1;endelsecnt <= cnt;endassign led = hud;//例化调用数码管显示模块segment u2(.seg_data_1 (cnt[7:4]), //g_data input.seg_data_2 (cnt[3:0]), //g_data input.seg_led_1 (segment_led_1), //MSB~LSB = SEG,DP,G,F,E,D,C,B,A.seg_led_2 (segment_led_2) //MSB~LSB = SEG,DP,G,F,E,D,C,B,A);//例化调用消抖模块debounce u1 (.clk (clk),.rst (rst),.key (key1),.key_pulse (key_pulse));endmodule2.数码管显示模块module segment(seg_data_1,seg_data_2,seg_led_1,seg_led_2);input [3:0] seg_data_1;//数码管需要显示0~9十个数字,所以最少需要4位输入做译码input [3:0] seg_data_2; //小脚丫上第二个数码管output [8:0] seg_led_1;//在小脚丫上控制一个数码管需要9个信号MSB~LSB=DIG、DP、G、F、E、D、C、B、A output [8:0] seg_led_2;//在小脚丫上第二个数码管的控制信号MSB~LSB=DIG、DP、G、F、E、D、C、B、Areg [8:0] seg [9:0];//定义了一个reg型的数组变量,相当于一个10*9的存储器,存储器一共有10个数,每个数有9位宽initial//在过程块中只能给reg型变量赋值,Verilog中有两种过程块always和initial//initial和always不同,其中语句只执行一次beginseg[0] = 9'h3f; //对存储器中第一个数赋值9'b00_0011_1111,相当于共阴极接地,DP点变低不亮,7段显示数字0seg[1] = 9'h06; //7段显示数字 1seg[2] = 9'h5b; //7段显示数字 2seg[3] = 9'h4f; //7段显示数字 3seg[4] = 9'h66; //7段显示数字 4seg[5] = 9'h6d; //7段显示数字 5seg[6] = 9'h7d; //7段显示数字 6seg[7] = 9'h07; //7段显示数字7seg[8] = 9'h7f; //7段显示数字8seg[9] = 9'h6f; //7段显示数字9endassign seg_led_1 = seg[seg_data_1]; //连续赋值,这样输入不同四位数,就能输出对于译码的9位输出assign seg_led_2 = seg[seg_data_2]; endmodule3.按键消抖模块//按键消抖module debounce (clk,rst,key,key_pulse);parameter N = 2; //要消除的按键的数量input clk;input rst;input [N-1:0] key; //输入的按键output [N-1:0] key_pulse; //按键动作产生的脉冲reg [N-1:0] key_rst_pre; //定义一个寄存器型变量存储上一个触发时的按键值reg [N-1:0] key_rst; //定义一个寄存器变量储存储当前时刻触发的按键值wire [N-1:0] key_edge; //检测到按键由高到低变化是产生一个高脉冲//利用非阻塞赋值特点,将两个时钟触发时按键状态存储在两个寄存器变量中always @(posedge clk or negedge rst)beginif (!rst)beginkey_rst <= {N{1'b1}}; //初始化时给key_rst赋值全为1,{}中表示N个1key_rst_pre <= {N{1'b1}};endelsebeginkey_rst <= key; //第一个时钟上升沿触发之后key的值赋给key_rst,同时key_rst的值赋给key_rst_prekey_rst_pre <= key_rst; //非阻塞赋值。

利用verilog设计计数显示报告

计数模块0-59秒,然后跳转源代码:module ct_clk(clk_50,reset,sech,secl);input clk_50;input reset;output sech;output secl;reg [3:0]sech,secl;always@(posedge clk_50)beginif(!reset){sech,secl}=8'h00;elseif(secl==4'h9)beginsecl<=0;if(sech==4'h5)sech<=4'h0;elsesech<=sech+1;endelsesecl<=secl+1;endendmodulemodule ct_clk_tb;reg clk_50;reg reset;wire [3:0]sech;wire [3:0]secl;ct_clk u(.clk_50(clk_50),.reset(reset),.sech(sech),.secl(secl));initialbeginclk_50=0;reset=0;# 20 reset=1;endalways # 10 clk_50=~clk_50; endmodule仿真结果显示模块源程序module ct_disp(clk_50,reset,seg_n,light_n,sech,secl,seg_n_secl,seg_n_sech,cnt); input clk_50;input reset;output [7:0]seg_n;reg [7:0]seg_n;output [1:0]light_n;reg[1:0]light_n;output [3:0]sech,secl;output [7:0]seg_n_secl,seg_n_sech;output cnt;reg [3:0]sech,secl;reg [7:0]seg_n_secl,seg_n_sech;reg cnt;always@(posedge clk_50 or negedge reset)if(!reset)cnt<=0;elsecnt<=cnt+1;// ji shualways@(posedge cnt or negedge reset)beginif(!reset){sech,secl}=8'h00;elseif(secl==4'h9)beginsecl<=0;if(sech==4'h5)sech<=4'h0;elsesech<=sech+1;endelsesecl<=secl+1;end//displayalways@(posedge clk_50 or negedge reset)//shu ma guan xian shi xuan zeif(!reset)beginlight_n<=2'b01;seg_n<=8'hc0;endelse begincase(light_n)2'b01:begin seg_n<=seg_n_secl;light_n<=2'b10;end2'b10:begin seg_n<=seg_n_sech;light_n<=2'b01;end//sec de xuan ze xian shi default:seg_n<=8'hc0;endcaseendalways@(secl)if(!reset)seg_n_secl<=8'hC0;elsebegincase(secl)4'h0:seg_n_secl<=8'hC0;4'h1:seg_n_secl<=8'hF9;4'h2:seg_n_secl<=8'hA4;4'h3:seg_n_secl<=8'hb0;4'h4:seg_n_secl<=8'h99;4'h5:seg_n_secl<=8'h92;4'h6:seg_n_secl<=8'h82;4'h7:seg_n_secl<=8'hF8;4'h8:seg_n_secl<=8'h80;4'h9:seg_n_secl<=8'h90;default: seg_n_secl<=8'hC0;endcaseendalways@(sech)if(!reset)seg_n_sech<=8'hC0;elsebegincase(sech)4'h0:seg_n_sech<=8'hC0;4'h1:seg_n_sech<=8'hF9;4'h2:seg_n_sech<=8'hA4;4'h3:seg_n_sech<=8'hb0;4'h4:seg_n_sech<=8'h99;4'h5:seg_n_sech<=8'h92;default: seg_n_secl<=8'hC0;endcaseendendmodulemodule ct_disp_tb;reg clk_50;reg reset;wire [7:0]seg_n;wire [1:0]light_n;wire [3:0]sech;wire [3:0]secl;wire [7:0]seg_n_secl;wire [7:0]seg_n_sech;wire cnt;ct_disp u1(.clk_50(clk_50),.reset(reset),.seg_n(seg_n),.light_n(light_n),.sech(sech),.secl(secl),.seg_n_secl(seg_n_secl),.seg_n_sech(seg_n_sech),.cnt(cnt));initialbeginclk_50=0;reset=0;#20 reset=1;endalways #10 clk_50=~clk_50;endmodule仿真。

计数器(1):Verilog常用写法

计数器(1):Verilog常⽤写法 计数器是⾮常基本的使⽤,没有计数器就⽆法处理时序。

我在学习时发现市⾯上有⼏种不同的计数器写法,⾮常有趣,在此记录下来:⼀、时序逻辑和组合逻辑彻底分开1.代码1//======================================================================2// --- 名称 : Count_13// --- 作者 : xianyu_FPGA4// --- ⽇期 : 2018-12-105// --- 描述 : 模10计数器,0到10循环累加6//======================================================================78module Count_19 (10input clk ,11input rst_n ,12output reg [ 3:0] cnt13 );1415//----------------------------------------------------------------------16//-- 组合电路17//----------------------------------------------------------------------18reg [ 3:0] cnt_n ;1920always @(*)begin21if(cnt == 4'd9)22 cnt_n = 4'd0;23else24 cnt_n = cnt + 1'b1;25end2627//----------------------------------------------------------------------28//-- 时序电路29//----------------------------------------------------------------------30always @(posedge clk or negedge rst_n)begin31if(!rst_n)32 cnt <= 4'b0;33else34 cnt <= cnt_n;35end3637endmodule3839/*40//----------------------------------------------------------------------41//-- 组合电路也可以这样写42//----------------------------------------------------------------------43wire [ 3:0] cnt_n ;4445assign cnt_n = (cnt==4'd9)? 4'd0 : cnt+1'b1;4647*/2.写法1的RTL视图3.写法2的RTL视图⼆、最常见的写法1.代码1//======================================================================2// --- 名称 : Count_23// --- 作者 : xianyu_FPGA4// --- ⽇期 : 2018-12-105// --- 描述 : 模10计数器,0到10循环累加6//======================================================================78module Count_29 (10input clk ,11input rst_n ,12output reg [ 3:0] cnt13 );1415always @(posedge clk or negedge rst_n)begin16if(!rst_n)17 cnt <= 4'd0;18else if(cnt==4'd9)19 cnt <= 4'd0;20else21 cnt <= cnt + 1'b1;22end23242526endmodule2.RTL视图三.代码⽚段写法1.代码1//====================================================================== 2// --- 名称 : Count_33// --- 作者 : xianyu_FPGA4// --- ⽇期 : 2018-12-105// --- 描述 : 模10计数器,0到10循环累加6//====================================================================== 78module Count_39//---------------------<端⼝声明>---------------------------------------10 (11input clk ,12input rst_n ,13output reg [ 3:0] cnt14 );15//---------------------<信号定义>---------------------------------------16wire add_cnt ;17wire end_cnt ;1819//----------------------------------------------------------------------20//-- 0-9计数21//----------------------------------------------------------------------22always @(posedge clk or negedge rst_n)begin23if(!rst_n)24 cnt <= 'd0;25else if(add_cnt)begin26if(end_cnt)27 cnt <= 'd0;28else29 cnt <= cnt + 1'b1;30end31else32 cnt <= cnt;33end3435assign add_cnt = 1;36assign end_cnt = add_cnt && cnt==10-1;3738394041endmodule2.RTL视图四、⾃减计数器(较少⽤到)1.代码1//====================================================================== 2// --- 名称 : Count_43// --- 作者 : xianyu_FPGA4// --- ⽇期 : 2018-12-195// --- 描述 : 模10⾃减计数器,10到0循环累减6//====================================================================== 78module Count_49//---------------------<端⼝声明>---------------------------------------10 (11input clk ,12input rst_n ,13output reg [ 3:0] cnt14 );15//---------------------<参数定义>---------------------------------------16parameter CNT_MAX = 10 ;1718//----------------------------------------------------------------------19//-- 10到0循环累减20//----------------------------------------------------------------------21always @(posedge clk or negedge rst_n)begin22if(!rst_n) begin23 cnt <= 0;24end25else if(cnt==0) begin26 cnt <= CNT_MAX;27end28else begin29 cnt <= cnt - 1;30end31end323334endmodule2.RTL视图3.仿真波形五、新学到的⼀种⾮常简洁的计数器 本以为计数器就是这样了,近来学习开源骚客《SDRAM那些事⼉》系列教程,⼜发现⼀种新的写法,对于特定功能的实现上⾮常简洁。

32位计数器verilog代码

32位计数器verilog代码以下是一个简单的 32 位计数器的 Verilog 代码示例。

该计数器每个时钟周期递增一次,当计数达到最大值时,重新从零开始。

module Counter(

input wire clk, // 时钟信号

input wire reset, // 复位信号

output reg [31:0] count // 32 位计数器

);

always @(posedge clk or posedge reset) begin

if (reset) begin

// 复位时,计数器清零

count <= 32'b0;

end else begin

// 在每个上升沿时递增计数器

count <= count + 1;

end

end

endmodule

在这个示例中,Counter 模块有一个时钟输入 clk 和一个复位输入 reset,以及一个 32 位的计数器输出 count。

计数器在每个时

1/ 2

钟上升沿或复位信号的上升沿触发。

当复位信号为高电平时,计数器被清零,否则,计数器递增。

请注意,这只是一个基本的示例。

实际应用中,你可能需要根据具体的需求添加一些功能,如计数器的最大值、启用/禁用等。

2/ 2。

verilog实验报告

verilog实验报告Verilog实验报告引言:Verilog是一种硬件描述语言(HDL),用于设计和模拟数字电路。

它是一种高级语言,能够描述电路的行为和结构,方便工程师进行数字电路设计和验证。

本实验报告将介绍我在学习Verilog过程中进行的实验内容和所获得的结果。

实验一:基本门电路设计在这个实验中,我使用Verilog设计了基本的逻辑门电路,包括与门、或门和非门。

通过使用Verilog的模块化设计,我能够轻松地创建和组合这些门电路,以实现更复杂的功能。

我首先创建了一个与门电路的模块,定义了输入和输出端口,并使用逻辑运算符和条件语句实现了与门的功能。

然后,我创建了一个测试模块,用于验证与门的正确性。

通过输入不同的组合,我能够验证与门的输出是否符合预期。

接下来,我按照同样的方法设计了或门和非门电路,并进行了相应的测试。

通过这个实验,我不仅学会了使用Verilog进行基本门电路的设计,还加深了对逻辑电路的理解。

实验二:时序电路设计在这个实验中,我学习了如何使用Verilog设计时序电路,例如寄存器和计数器。

时序电路是一种具有状态和时钟输入的电路,能够根据时钟信号的变化来改变其输出。

我首先设计了一个简单的寄存器模块,使用触发器和组合逻辑电路实现了数据的存储和传输功能。

然后,我创建了一个测试模块,用于验证寄存器的正确性。

通过输入不同的数据和时钟信号,我能够观察到寄存器的输出是否正确。

接下来,我设计了一个计数器模块,使用寄存器和加法电路实现了计数功能。

我还添加了一个复位输入,用于将计数器的值重置为初始状态。

通过测试模块,我能够验证计数器在不同的时钟周期内是否正确地进行计数。

通过这个实验,我不仅学会了使用Verilog设计时序电路,还加深了对触发器、寄存器和计数器的理解。

实验三:组合电路设计在这个实验中,我学习了如何使用Verilog设计组合电路,例如多路选择器和加法器。

组合电路是一种没有状态和时钟输入的电路,其输出只取决于当前的输入。

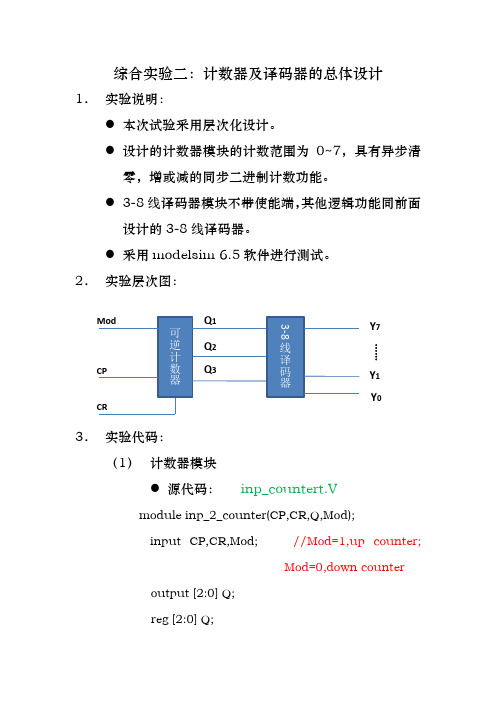

verilog综合设计实验:计数器及译码器的总体设计源代码

综合实验二:计数器及译码器的总体设计1. 实验说明:● 本次试验采用层次化设计。

● 设计的计数器模块的计数范围为0~7,具有异步清零,增或减的同步二进制计数功能。

● 3-8线译码器模块不带使能端,其他逻辑功能同前面设计的3-8线译码器。

● 采用modelsim 6.5软件进行测试。

2. 实验层次图:3. 实验代码:(1) 计数器模块● 源代码:inp_countert.Vmodule inp_2_counter(CP,CR,Q,Mod);inputCP,CR,Mod; //Mod=1,up counter;Mod=0,down counteroutput [2:0] Q;reg [2:0] Q; Y 7 Y 1 Y 0……always @ (posedge CP or negedge CR)if(~CR)Q<=3'b000;//CR=0,asynchronousclear else if (Mod==1) Q<=Q+1'b1;else Q<=Q-1'b1;endmodule●测试代码:test_inp_counter.Vmodule test_inp_2_counter;regCP,CR,Mod;wire [2:0] Q;inp_2_counter u0(CP,CR,Q,Mod);initialbeginCP=0;CR=0;Mod=1;#20 CR=1;Mod=1;#60 CR=0;Mod=1;#20 CR=1;Mod=1;#40 CR=1;Mod=0;#20 CR=0;Mod=1;endalways #10 CP=~CP;endmodule●测试结果:见inp2counter.WLF(2)译码器模块●源代码:3-8-decoder.Vmodule decoder_3to8(Q,Y);input [2:0] Q;output [7:0] Y;reg [7:0] Y;always @(Q)begin case(Q)3'b000:Y=8'b11111110;3'b001:Y=8'b11111101;3'b010:Y=8'b11111011;3'b011:Y=8'b11110111;3'b100:Y=8'b11101111;3'b101:Y=8'b11011111;3'b110:Y=8'b10111111;3'b111:Y=8'b01111111;endcaseendendmodule●测试代码:test_3_8_decoder.Vmodule test_decoder_3to8;reg [2:0] Q;wire [7:0] Y;decoder_3to8 u1(Q,Y);initialbeginQ=3'b000;endalways #20 Q=Q+1'b1;endmodule●测试结果:见decoder-3-8.WLF(3)顶层模块●源代码:top.Vmoduledec_counter(CP,CR,Mod,Y);inputCP,CR,Mod;output [7:0] Y;wire [2:0] Q; //intermediate carriesinp_2_counter f1(CP,CR,Q,Mod);decoder_3to8 f2(Q,Y);endmodule●测试代码:test_top.Vmoduledec_counter(CP,CR,Mod,Y);inputCP,CR,Mod;output [7:0] Y;wire [2:0] Q; //intermediate carriesinp_2_counter f1(CP,CR,Q,Mod);decoder_3to8 f2(Q,Y);endmodule测试结果:见top_dec_cn.WLF4.实验心得:本次实验为第一次使用分层次的电路设计方法来完成所需功能。

verilog实验报告 - 程超

西安邮电學院基于Verilog的数字电路模拟实验系部名称:通信与信息工程学院学生姓名:张宏扬专业名称:通信工程班级:通工0809学号:03081469(01)时间:2010年12月20号实验题目门级建模仿真实验一、实验内容设计的一个带有清零的顺序输出结果的计数器,q从0计数到15二、技术规范1、输入引脚:reset,clk;输出引脚:q。

2、功能:这时也个具有清零的计数器,从0到15输出的。

在其中用到了T触发器和D触发器来实现它的功能。

三、实验步骤1、在modulesim软件中对设计模块和验证模块进行书写和编译;2、对编译好的模块进行仿真。

四、源代码://脉动进位计数器顶层模块module ripple_carry_counter(q,clk,reset);output [3:0]q;input clk,reset;//生成了4个T触发器(T_FF)的实例,每个都有自己的名字T_FF tff0(q[0],clk,reset);T_FF tff1(q[1],q[0],reset);T_FF tff2(q[2],q[1],reset);T_FF tff3(q[3],q[2],reset);endmodule//触发器T_FFmodule T_FF(q,clk,reset);output q;input clk,reset;wire d;D_FF dff0(q,d,clk,reset);not n1(d,q); //非门(not)是Verilog语言的内置原语部件(primitive)endmodule//D触发器(D_FF)//带异步复位的D触发器(D_FF)module D_FF(q,d,clk,reset);output q;input d,clk,reset;reg q;//可以有许多种新结构,不考虑这些结构的功能,只需要注意设计块是如何以自顶向下的方式编写的always @(posedge reset or negedge clk)if (reset)q<= 1'b0;elseq<= d;endmodulemodule stimulus;reg clk;reg reset;wire [3:0]q;//引用已经设计好的模块实例ripple_carry_counter r1(q,clk,reset);//控制驱动设计块的时钟信号,时钟周期为10个时间单位initialclk = 1'b0; //把clk设置为0always#5 clk = ~clk; //每5个时间单位时钟翻转一次//控制驱动设计块的reset信号initialbeginreset = 1'b1;#15 reset = 1'b0;#180 reset = 1'b1;#10 reset = 1'b0;#20 $finish; //终止仿真end//监视输出initial$monitor($time, "Output q = %d",q);endmodule五、仿真结果及分析实验题目 RS锁存器一、实验内容带有延迟的RS锁存器,写出其带有延迟的Verilog门级描述。

verilog模4计数器实验报告

Lab 5 模4递增计数器王阳IS1102班U2011140661.实验目的学会用Quartus 9.1编译Verilog语言的方法和步骤;设计简单的程序,并能运行;了解触发器,并学会利用触发器制作模4递增计数器。

2.实验内容●在模4递增计数器中,由cp时钟信号控制输入;●由两个D触发器组合而得到模4递增计数器;●简单的模4计数器由cp作为开关控制输入,由Q0和Q1两个LED灯控制输出。

3.代码分析1)首先,定义module的输入输出接口;2)然后,建立程序,分为模4递增计数器主块和D触发器块;3)模4递增计数器的实现分为2个块,如下:模4递增计数器块:module mo4(Q0,Q1,cp);output Q0,Q1;input cp;d_ff f0(Q0,~Q0,cp);//调用D触发器d_ff f1(Q1,~Q1,Q0); //调用D触发器endmoduleD触发器块:module d_ff (Q,D,cp);//D触发器块output Q;input D,cp;reg Q;always @(posedge cp)Q<=D;endmodule4.实验步骤1)连接DE0板:连接DE0板的电源线和数据线或直接将数据线接到电脑主机上,打开开关。

2)创建项目:打开Quartus9.1软件,选择“File—>New Project Wizard”,在弹出的窗口中输入项目的名称和存储位置。

这里笔者将文件储存在桌面的临时文件夹中,并取名为chufaqi\mo4,如下:确定输入完成后,单击Next,出现下图:可以在File name中输入文件名,再次单击Next后,接着选择实验板的型号。

如图,实验时,一般选择Cyclone lll中的EP3C16F484C6型号即可。

继续单击Next,最后,单击Finish完成项目的创建。

3)建立Verilog HDL文件:在“File—>New”的窗口中选择建立Verilog HDL文件。

北航verilog实验报告

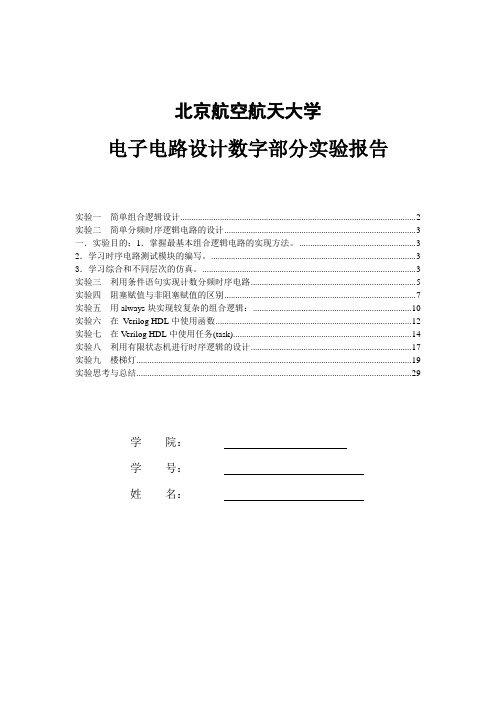

北京航空航天大学电子电路设计数字部分实验报告实验一简单组合逻辑设计 (2)实验二简单分频时序逻辑电路的设计 (3)一.实验目的:1.掌握最基本组合逻辑电路的实现方法。

(3)2.学习时序电路测试模块的编写。

(3)3.学习综合和不同层次的仿真。

(3)实验三利用条件语句实现计数分频时序电路 (5)实验四阻塞赋值与非阻塞赋值的区别 (7)实验五用always块实现较复杂的组合逻辑: (10)实验六在Verilog HDL中使用函数 (12)实验七在Verilog HDL中使用任务(task) (14)实验八利用有限状态机进行时序逻辑的设计 (17)实验九楼梯灯 (19)实验思考与总结 (29)学院:学号:姓名:实验一简单组合逻辑设计一.实验目的:1.掌握基本组合逻辑电路的实现方法。

2.初步了解两种基本组合逻辑电路的生成方法。

3.学习测试模块的编写。

4.通过综合和布局布线了解不同层次仿真的物理意义。

二.实验设备:安装Modelsim-6.5c的PC机。

三.实验内容:描述一个可综合的数据比较器,比较数据a 、b的大小,若相同,则给出结果1,否则给出结果0四.综合仿真结果实验二简单分频时序逻辑电路的设计一.实验目的:1.掌握最基本组合逻辑电路的实现方法。

2.学习时序电路测试模块的编写。

3.学习综合和不同层次的仿真。

二.实验设备:安装Modelsim-6.5c的PC机。

三.实验内容:用always块和@(posedge clk)或@(negedge clk)的结构表述一个1/2分频器的可综合模型,观察时序仿真结果四.实验代码module half_clk(reset,clk_in,clk_out);input clk_in,reset;output clk_out;reg clk_out;always@(posedge clk_in)beginif(!reset)clk_out=0;elseclk_out=~clk_out;endendmodule`timescale 1ns/100ps`define clk_cycle 50module top;reg clk,reset;wire clk_out;always #`clk_cycle clk=~clk;initialbeginclk=0;reset=-1;#10 reset=0;#110 reset=1;#100000 $stop;endhalf_clk m0(.reset(reset),.clk_in(clk),.clk_out(clk_out)); endmodule五.综合仿真结果实验三利用条件语句实现计数分频时序电路一.实验目的:1.掌握条件语句在简单时序模块设计中的使用。

verilog实验-计数器实验报告

v e r i l o g实验-计数器实验报告-CAL-FENGHAI-(2020YEAR-YICAI)_JINGBIAN计数器1、实现目标及介绍实验实现了一个简易的计数器,计数范围可达899(0~899),通过key4按键计数,每按下一次,计数加一,百位数显示在led上,个位与十位显示在数码管上。

为十进制计数,数码管1计数到九后置零。

数码管2获得进位加一,数码管2到9后当再次获得个位进位时再次向百位进一,点亮led1,每百位点亮一个led。

此外key4为清零键,可随时按键清零。

2、效果展示计数99清零计数100视频展示(双击观看)3、代码实现与模块分析1.顶层模块module jishuqi(input wire clk,rst, eg_data_1 (cnt[7:4]), eg_data_2 (cnt[3:0]), eg_led_1 (segment_led_1), eg_led_2 (segment_led_2) lk (clk),.rst (rst),.key (key1),.key_pulse (key_pulse));endmodule2.数码管显示模块module segment (seg_data_1,seg_data_2,seg_led_1,seg_led_2);input [3:0] seg_data_1;键消抖模块eg_data_1 (cnt[7:4]), eg_data_2 (cnt[3:0]), eg_led_1 (segment_led_1), eg_led_2 (segment_led_2) lk (clk),.rst (rst),.key (key1),.key_pulse (key_pulse));endmodule//按键消抖module debounce (clk,rst,key,key_pulse);parameter N = 2; //要消除的按键的数量input clk;input rst;input [N-1:0] key; //输入的按键output [N-1:0] key_pulse; //按键动作产生的脉冲reg [N-1:0] key_rst_pre; //定义一个寄存器型变量存储上一个触发时的按键值reg [N-1:0] key_rst; //定义一个寄存器变量储存储当前时刻触发的按键值wire [N-1:0] key_edge; //检测到按键由高到低变化是产生一个高脉冲//利用非阻塞赋值特点,将两个时钟触发时按键状态存储在两个寄存器变量中always @(posedge clk or negedge rst)beginif (!rst)beginkey_rst <= {N{1'b1}}; //初始化时给key_rst赋值全为1,{}中表示N个1key_rst_pre <= {N{1'b1}};endelsebeginkey_rst <= key; //第一个时钟上升沿触发之后key 的值赋给key_rst,同时key_rst的值赋给key_rst_prekey_rst_pre <= key_rst; //非阻塞赋值。

10进制计数器verilog代码

以下是一个简单的10进制计数器的Verilog代码。

这个计数器在每个时钟周期内递增,并在计数到10后回滚到0。

verilog复制代码

module counter_10 (

input wire clk,

input wire reset,

output reg [3:0] count

);

always @(posedge clk or posedge reset) begin

if (reset) begin

count <= 4'b0000;

end else begin

count <= count + 1;

end

end

endmodule

在这个模块中,clk是时钟输入,reset是复位输入,count是4位的输出,表示当前的计数值。

在每个时钟上升沿,count都会递增。

当count达到10(即二进制的1010)时,它会被复位回0。

如果复位信号被激活,无论时钟状态如何,count都会被立即复位。

请注意,这是一个非常基础的计数器设计,没有包括一些更复杂的功能,比如预置值、异步/同步复位等。

如果你需要这些功能,你可能需要修改或扩展这个设计。

Verilog 实验报告

练习三利用条件语句实现计数分频时序电路实验目的:1.掌握条件语句在简单时序模块设计中的使用;2.学习在Verilog模块中应用计数器;3.学习测试模块的编写、综合和不同层次的仿真。

实验理论:实验用到Verilog HDL提供的条件语句供分支判断,以描述较复杂的时序关系。

在可综合风格的Verilog HDL模型中,常用的条件语句有if-else和case-endcase两种结构。

两者相比,if-else 用于不是很复杂的分支关系,实际编写可综合风格的模块,特别是用状态机构成的模块时,更常用的是case-endcase风格的代码。

在多重if 嵌套语句中,else 与前面最近的if 相对应(即与前面最近的if 组成一对if-else 语句。

为确保程序的可读性和语句的对应性,请使用begin…end 块语句。

下面给出的范例也是一个可综合风格的分频器,可将10MB的时钟分频为500KB的时钟。

基本原理与1/2分频器是一样的,但是需要定义一个计数器,对于实现占空比为1:1分频,首先进行上升沿触发进行模J计数,计数从零开始,到19进行输出时钟翻转,然后经过19再次进行翻转得到一个占空比非1:1分频时钟。

再者同时进行下降沿触发的模19计数,到和上升沿过19时,输出时钟再次翻转生成占空比非1:1分频时钟。

两个占空比非1:1分频时钟相或运算,得到占空比为1:1分频时钟。

以准确获得1/20分频。

Verilog模块结构完全嵌在module和endmodule声明语句之间;每个Verilog程序包括四个主要部分:端口定义、I/O说明、内部信号声明、功能定义。

模块源代码://------------------ fdivision.v-------------------//module fdivision(RESET,F10MB,F500KB);input F10MB,RESET; output F500KB; //输出为500KB的输出端reg F500KB; //定义一位寄存器reg [7:0]j; //定义数据宽为8的计数寄存器jalways @(posedge F10MB)if(! RESET) //当RESET无效时,对输出端和计数器初始化beginF500KB<=0;j<=0;endelsebeginif(j==19) //当j=19时,将时钟翻转,并将计数器清零beginj<=0;F500KB=~F500KB;endelsej<=j+1; //当j不等于19时使j加1endendmodule测试模块常见的形式:module t;reg …; //被测模块输入/输出变量类型定义wire…; //被测模块输入/输出变量类型定义initial begin …; …; …; end … …//产生测试信号always #delay begin …; end … …//产生测试信号Testedmd m(.in1(ina), .in2(inb), .out1(outa), .out2(outb) );//被测模块的实例引用initial begin ….; ….; …. end //记录输出和响应endmodule测试模块源代码:`timescale 1ns/100ps`define clk_cycle 50module division_Top;reg F10MB,RESET;wire F500KB_clk;always #`clk_cycle F10MB=~F10MB;initialbeginRESET=1;F10MB=0;#100 RESET=0;#100 RESET=1;#10000 $stop;endfdivision fdivision (.RESET(RESET),.F10MB(F10MB),.F500KB(F500_clk));endmodule仿真结果:练习:利用10MB的时钟,设计一个单周期形状的周期波形。

用verilog HDL输入法设计十进制计数器 实验报告

实验名称:实验四:用verilog HDL输入法设计十进制计数器实验目的:硬件描述语言(HDL)就是可以描述硬件电路的功能、信号连接关系及定时(时序)关系的语言,也是一种用形式化方法来描述数字电路和设计数字系统的。

通过十进制计数器的设计,熟练掌握硬件描述语言的编程方法。

实验原理:module cout(clk,clear,qd,EN);input clk,clear,EN;output[3:0] qd;reg[3:0] cnt;assign qd=cnt;always @(posedge clk )begin if(clear ) cnt<=4'h0;//同步清0,高电平有效else if(EN)begin if(cnt==9) cnt<=4'h0;else cnt<=cnt+1; //加法计数endendEndmodule实验内容:为了能对此计数器进行硬件测试,应将其输入输出信号锁定在芯片确定的引脚上,编译后下载。

(1)选择Tools菜单中的Assignments项,即进入如图2-23所示的Assignment Editor编辑器窗。

在Category栏中选择Pin,或直接单击右上侧的Pin按钮。

(2)双击“TO”栏的《new》,在出现的如图2-24所示的下拉栏中分别选择本工程要锁定的端口信号名;然后双击对应的Location栏的《new》,在出现的下拉栏中选择对应端口信号名的器件引脚号,如对应CQ[3],选择42脚。

在此选择GW48-EDA系统的电路模式No.5,通过查阅附录有关”芯片引脚对照表”,GWAC3板确定引脚分别为:主频时钟clk接Clock0(第93脚,可接在4Hz上);计数使能EN可接电路模式No.5的键1(PIO0对应第1脚);复位clear则接电路模式No.5的键2(PIO1对应第2脚,注意键序与引脚号码并无对应关系);4位输出数据总线CQ[3..0]可由数码1来显示,通过分别接PIO19、PIO18、PIO17、PIO16(它们对应的引脚编号分别为42、41、40、39)。

模计数器verilog报告

实验名称模8计数器姓名:xxx班级:xxx学号:xxxxx报告日期:xxxxxx1.实验目的练习在modelsim下编写verilog程序,熟悉modelsim运行过程,并学会用verilog编写一个模八计数器。

2.实验任务编写一个模值为八的计数器的功能模块实现模为八带清零端的(异步清零);并且编写一激励模块来测试该模块。

3.实验内容及步骤3.1 实验内容编写模8计数器模块及激励模块3.2 本次所实现的功能描述模8计数器有两个输入端,分别为 clock (时钟控制输入端),和clear (异步清零端),一个输出端Q用来周期性的显示。

Clock:时钟信号,当上升沿到来时,计数器自动加一。

Clear:异步清零端,低电平到来时计数器自动清零。

Q:输出端,从000-111共八个状态。

3.3 本次实验的设计方案带有异步清零端的模8计数器共有8个状态,所以输出端Q 只需要三位(从000----111)共八个状态。

还需要一个输入端(clock )来输入时钟信号,另一个输入端(clear )来输入清零信号。

模8计数器的状态转移图如下:1.进入modelsim 后点击file ----> new ---->project.之后出现一个建立工程的对话框,键入counter_8工程名后,再在下面路径添加一个自己的文件夹。

确认后会弹出一个对话框,点击creat New File,在工程conuter_8下建立两个文件分别叫做counter_8的功能模块文件和test_counter_8的测试激励模块文件。

2.双击进入文件后编写程序3.编译,如果程序出错对程序进行修改。

之后再编译,编译成功后点击simulate进行仿真。

.4.观察仿真结果是否符合事先的设计。

不符合继续修改程序。

模8计数器的功能模块如下:module counter_8(clock,clear,q);input clock,clear;output[2:0] q;reg[2:0] q;always @(posedge clock or negedge clear)beginif(!clear)q<=0;elseq <= q +1;endendmodule测试激励如下:module test_counter8;reg clk,clr;wire[2:0] q;counter_8 counter(.clock(clk),.clear(clr),.q(q));initialclk = 0;always#100 clk = ~clk;initialbeginclr = 0;#50 clr = 1;#200 clr = 0;#50 clr = 1;endinitial$monitor($time,"clear= %b,clock= %b,q= %b",clr,clk,q);endmodule3.4 本次实验设计的结果测试结果波形如下:测试输出结果如下;4.实验总结这是第二次用modelsim编写程序,使用方面还不熟练,总是不知道点哪里。

verilog HDL十进制加减法计数器报告

十进制加减法计数器1.实验要求(1)在Modelsim环境中编写十进制加减法计数器程序;(2)编译无误后编写配套的测试程序;(3)仿真后添加信号,观察输出结果。

2.设计程序如下module decade_counter#(parameter SIZE=4)(input clock,load_n,clear_n,updown,input [SIZE-1:0]load_data,output reg [SIZE-1:0]q);always@(negedge load_n,negedge clear_n,posedge clock)if (!load_n)q<=load_data;else if (!clear_n)q<=0;else //clockif(updown)q<=(q+1)%10;elsebeginif(q==0)q<=9;elseq<=q-1;endendmodule3.测试程序如下`timescale 1ns/1nsmodule test_decade_counte;reg clock,load_n,clear_n,updown;reg [3:0]load_data;wire [3:0]q;decade_counter T1(clock,load_n,clear_n,updown,load_data,q);initialbeginclock=0;clear_n=0;#30 clear_n=1;load_n=0;load_data=7;#30 load_n=1;updown=0;#300 updown=1;#300 updown=0;#300 updown=1;#300 $stop;endalways#10 clock=~clock;always@(q)$display("At time%t,q=%d",$time,q);endmodule4.波形如下5.测试结果如下# At time 0,q= 0# At time 30,q= 7# At time 70,q= 6# At time 90,q= 5# At time 110,q= 4# At time 130,q= 3# At time 150,q= 2# At time 170,q= 1# At time 190,q= 0# At time 210,q= 9# At time 230,q= 8# At time 250,q= 7# At time 270,q= 6# At time 290,q= 5# At time 310,q= 4# At time 330,q= 3# At time 370,q= 3 # At time 390,q= 4 # At time 410,q= 5 # At time 430,q= 6 # At time 450,q= 7 # At time 470,q= 8 # At time 490,q= 9 # At time 510,q= 0 # At time 530,q= 1 # At time 550,q= 2 # At time 570,q= 3 # At time 590,q= 4 # At time 610,q= 5 # At time 630,q= 6 # At time 650,q= 7 # At time 670,q= 6 # At time 690,q= 5 # At time 710,q= 4 # At time 730,q= 3 # At time 750,q= 2 # At time 770,q= 1 # At time 790,q= 0 # At time 810,q= 9 # At time 830,q= 8 # At time 850,q= 7 # At time 870,q= 6 # At time 890,q= 5 # At time 910,q= 4 # At time 930,q= 3 # At time 950,q= 2 # At time 970,q= 3 # At time 990,q= 4 # At time 1010,q= 5 # At time 1030,q= 6 # At time 1050,q= 7 # At time 1070,q= 8 # At time 1090,q= 9 # At time 1110,q= 0 # At time 1130,q= 1 # At time 1150,q= 2 # At time 1170,q= 3 # At time 1190,q= 4 # At time 1210,q= 5# At time 1250,q= 7。

基于Verilog的任意模长可加减计数器设计

基于Verilog 的任意模长可加减计数器设计一、设计要求计数器是一种在时钟的触发下,完成计数功能的时序逻辑电路,输出结果由输入时钟和计数器上一状态的计数共同决定。

本设计要求实现的计数器,具有以下功能:(1)要求实现计数器工作状态的控制;(2)要求实现计数器的异步清零功能;(3)要求实现计数器递增和递减的功能;(4)要求实现计数器的计数范围(模长)任意改变;二、设计思路计数器工作状态的控制,可以设计一个使能端,在外部时钟的触发下,只有当使能端信号有效(高电平),才启动计数器的计数功能(递增或递减),否则计数器输出结果不变。

计数器的异步清零功能,可以设计一个外部输入的清零端,在外部输入信号有效(低电平)的情况下,直接清零计数器,不用等待下一个外部时钟的触发,即计数器的清零是异步的。

计数器计数方向的控制,设计一个加减可控的信号端口,在时钟的触发、异步清零无效以及计数器使能端有效的情况下,该输入端为高电平则计数器完成递增功能,低电平则完成递减功能。

实现计数器的任意模长,即进入下一个计数周期,其计数的最大值可以发生变化。

设计一个4位(最大模长为16)的输入端口,可以在当前计数周期结束,即计数器产生一个溢出信号的同时,判断该端口输入的信号是否发生变化,通过相邻两个计数周期的端口数据作异或运算,结果为高电平则代表模长发生变化,即进入的下一个计数周期,其计数最大值要发生变化。

三、程序设计本次设计使用的是Quartus 11.0开发环境,该软件没有自带仿真功能(9.0版本以后都没自带),需要使用第三方的Modelsim软件,故本设计的程序包括计数器的Verilog设计以及仿真测试需要的testbench激励文件两部分。

计数器的Verilog设计:module Prj(clk,rst_input,en,add_sub,data_input,full,data_output);input clk; // 外部时钟input rst_input; // 外部清零(异步)input en; // 计数使能input add_sub; // 计数方向input [3:0] data_input; // 计数器模长输入output reg full; // 计完当前模长output [3:0] data_output; // 计数器输出reg [3:0] current_counter;// 当前计数值(输出)reg update_length_en; // 改变模长的使能信号// 当前计数周期与上个计数周期的模长输入reg [3:0] current_clk_data_input,last_clk_data_in put;reg [3:0] counter_length; // 下个计数周期的模长reg [1:0] k;always @(posedge clk,negedge rst_input) beginif(!rst_input) // 异步清零beginfull=0;current_counter=0;endelse if(en) // 计数使能beginif(add_sub) // 加法器beginif(current_counter<(counter_length-1))begincurrent_counter=current_counter+1;full=0;endelse// 加法器计数完产生full脉冲以触发// 判断下个计数周期的模长是否变化begincurrent_counter=0;full=1; //full输出endendelse // 减法器beginif(current_counter>0)begincurrent_counter=current_counter-1;full=0;endelse // 减法器计数完begincurrent_counter=counter_length-1;full=1;endendendend//驱动当前计数输出assign data_output=current_counter;initialbegink=1; // k=1 表示启动计数器的第一个计数周期endalways @(posedge full) // 加法器/减法器完成当前周期计数// 计完当前周期(即full有效)才更新beginlast_clk_data_input<=data_input; // 上个周期的模长current_clk_data_input=data_input;//当前周期的模长update_length_en<=last_clk_data_input^current_clk_data_input;// update_length_en为更新计数器模长的使能端,// 异或运算使能端为0代表模长变化 1不变k=k+1; // k的初值为1,k变化说明计数模长更改过了if(k==2'd3)k=2;endalways @(posedge clk)beginif(update_length_en) // 使能有效计数模长变化counter_length=current_clk_data_input;elsebeginif(k>=2)// 下个周期计数器模长不变(保持上次更改的)counter_length=last_clk_data_input;if(k==1)// 整个计数器系统,最初的模长(一次没更改过)counter_length=data_input;endendendmodule测试激励文件testbench:`timescale 1 ps/ 1 psmodule Prj_vlg_tst();reg add_sub;reg clk;reg [3:0] data_input;reg en;reg rst_input;wire [3:0] data_output;wire full;Prj i1 (.add_sub(add_sub),.clk(clk),.data_input(data_input),.data_output(data_output),.en(en),.full(full),.rst_input(rst_input));parameter clk_period=10; // 时钟周期initial // 初始化使能端、清零端和时钟信号beginen=1;rst_input=1;clk=1;#(46*clk_period) en=0;#(3*clk_period) en=1;#(4*clk_period) rst_input=0;#(2*clk_period) rst_input=1;endalways #(clk_period/2) clk=~clk;initialbegin// 计数器模长分别为6 4 5 3// 左边为上一模长持续的时钟个数data_input=4'b0110;#(22*clk_period) data_input=4'b0100;#(12*clk_period) data_input=4'b0101;#(12*clk_period) data_input=4'b0011;#(5*clk_period);endinitialbegin// 计数器计数方向的改变// 左边为递增递减持续的时钟个数add_sub=1;#(9*clk_period) add_sub=0;#(10*clk_period) add_sub=1;#(13*clk_period) add_sub=0;#(4*clk_period) add_sub=1;endendmodule四、仿真结果如图1所示,最开始计数器输入的模长data_input为6,在计数方向控制端add_sub为高电平的情况下,可以从0计数到5,在add_sub为低电平的情况下,可以实现计数器的递减;当计数器模长data_input变为4的时候,先计完当前周期的模长(0到5),才开始模长为4的计数(0到3)。

模可变计数器设计Verilog语言

模可变计数器设计(一)实验目的1、进一步熟悉实验装置和QuartusⅡ软件的使用;2、进一步熟悉和掌握EDA设计流程;3、学习简单组合、时序电路的EDA设计;4、学习计数器中二进制码到BCD码的转换技巧;5、学习实验装置上数码管的输出方法。

(二)设计要求完成设计、仿真、调试、下载、硬件测试等环节,在EDA实验装置上实现模可变计数器功能,具体要求如下:1、设置一个按键控制改变模值,按键按下时模为10-99之间(具体数值自行确定)的数,没按下时模为100-199之间(具体数值自行确定)的数;2、计数结果用三位数码管十进制显示。

(三)主要仪器设备3、微机1台4、QuartusII集成开发软件1套5、EDA实验装置1套(四)实验步骤主要有三个模块1:一个模20和模119的计数器2:数码管的显示3:BCD的调整源程序:module count (clk,m,en,rst,a,sel,SG,d);input clk,m,en,rst;output [7:0] SG;output [2:0] sel;output a;(* synthesis, keep *) reg clk1;(* synthesis, keep *) wire [3:0] gw,sw,bw;/*(* synthesis, keep *) */reg [3:0]a;reg [11:0] q;reg [11:0] model;reg [7:0] cnt,SG;reg [2:0] sel;reg [0:0]d;output [0:0]d;always @(posedge clk)begin cnt=cnt+1;if (cnt==200) begin clk1=1'b1; cnt=0; endelse clk1=1'b0; //200分频,CLK为数码管扫描频率,CLK1为计数频率if (sel<2) sel=sel+1; else sel=0; end //sel为数码管选择always @(sel) begincase (sel)0: a=bw; //0数码管为百位1: a=sw; //1数码管为十位2: a=gw; //2数码管为个位default: a=0;endcasecase (a)0:SG<=8'b00111111; 1:SG<=8'b00000110;2:SG<=8'b01011011; 3:SG<=8'b01001111;4:SG<=8'b01100110; 5:SG<=8'b01101101;6:SG<=8'b01111101; 7:SG<=8'b00000111;8:SG<=8'b01111111; 9:SG<=8'b01101111; //8段译码值default: SG=8'b11111111;endcase endalways @(m)if (m) model=12'b000000100000; //模值20else model=12'b000100011001; //模值119assign gw=q[3:0];assign sw=q[7:4];assign bw=q[11:8];always @(posedge clk1,negedge rst)beginif (!rst) q=0;else if (en)beginif (q<model)beginif (gw==9) begin q=q+7; if (sw==9) q=q+96; end //BCD调整 else q=q+1;endelse q=0;endendalways @(q)if(q<model) d<=0;else d<=1;endmodule波形仿真:Clk1是计数频率,每来一个clk1信号q计数一次如图所示:rst=1有效时开始计数 clk为扫描频率sel=0时数码管显示百位a=0sel=1时数码管显示十位a=1sel=2时数码管显示个位a=3m=1 模20计数器m=0 模119计数器管脚分配:SG[0] PIN_F13SG[1] PIN_F14SG[2] PIN_F15SG[3] PIN_E15SG[4] PIN_F16SG[5] PIN_F17SG[6] PIN_E18SG[7] PIN_F18clk PIN_C13en PIN_H8m PIN_J9rst PIN_C5sel[0] PIN_G18sel[1] PIN_G17sel[2] PIN_G16d[0] PIN_G13(五)实验心得本实验主要是三大模块的编写,第一次的实验在老师给的参考代码下进行的,不过错误依然很多,主要有几个重点药掌握,一是首先要编写出能够计数的模块,用m来控制模值的变化m=1时模值为20 m=0时模值为119;二是计数模块都是二进制计数的,而要在数码管上显示计数的话就必须进行BCD调整,并且q是一个是十二位的寄存器,通过把gw=q[3:0]; sw=q[7:4]; bw=q[11:8]赋值的方法;一个个的显示在数码管上,由于clk的频率比较快,所以可以看到三位数码管显示的值,我觉得管脚分配也是比较关键的!一开始我就把个位和百位显示的值搞反了序列信号发生和检测器设计(一)实验目的1、进一步熟悉EDA实验装置和QuartusⅡ软件的使用方法;2、学习有限状态机法进行数字系统设计;3、学习使用原理图输入法进行设计。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验名称

模8计数器

姓名:xxx

班级:xxx

学号:xxxxx

报告日期:xxxxxx

1.实验目的

练习在modelsim下编写verilog程序,熟悉modelsim运行过程,并学会用verilog编写一个模八计数器。

2.实验任务

编写一个模值为八的计数器的功能模块实现模为八带清零端的(异步清零);并且编写一激励模块来测试该模块。

3.实验内容及步骤

实验内容

编写模8计数器模块及激励模块

本次所实现的功能描述

模8计数器有两个输入端,分别为clock (时钟控制输入端),和clear(异步清零端),一个输出端Q用来周期性的显示。

Clock:时钟信号,当上升沿到来时,计数器自动加一。

Clear:异步清零端,低电平到来时计数器自动清零。

Q:输出端,从000-111共八个状态。

本次实验的设计方案

带有异步清零端的模8计数器共有8个状态,所以输出端Q 只需要三位(从000----111)共八个状态。

还需要一个输入端(clock )来输入时钟信号,另一个输入端(clear )来输入清零信号。

模8计数器的状态转移图如下:

clock

Clear Q

具体方案如下:

1.进入modelsim后点击file ----> new ---->project.之后出现一个建立工程的对话框,键入counter_8工程名后,再在下面路径添加一个自己的文件夹。

确认后会弹出一个对话框,点击creat New File,在工程conuter_8下建立两个文件分别叫做counter_8的功能模块文件和test_counter_8的测试激励模块文件。

2.双击进入文件后编写程序

3.编译,如果程序出错对程序进行修改。

之后再编译,编译成功后点击simulate进行仿真。

.

4.观察仿真结果是否符合事先的设计。

不符合继续修改程序。

模8计数器的功能模块如下:

module counter_8(clock,clear,q);

input clock,clear;

output[2:0] q;

reg[2:0] q;

always @(posedge clock or negedge clear)

begin

if(!clear)

q<=0;

else

q <= q +1;

end

endmodule

测试激励如下:

module test_counter8;

reg clk,clr;

wire[2:0] q;

counter_8 counter(.clock(clk),.clear(clr),.q(q));

initial

clk = 0;

always

#100 clk = ~clk;

initial

begin

clr = 0;

#50 clr = 1;

#200 clr = 0;

#50 clr = 1;

end

initial

$monitor($time,"clear= %b,clock= %b,q= %b",clr,clk,q); endmodule

本次实验设计的结果

测试结果波形如下:

测试输出结果如下;

4.实验总结

这是第二次用modelsim编写程序,使用方面还不熟练,总是不知道点哪里。

之后慢慢的试,同时摸索着终于可以简单的使用了。

在程序编写方面,这个程序不难,因为以前学过C语言,所以在编写程序方面问题不是很大。

但是verilog不同于C语言一个很大的方面就是端口的链接要求比较严格,例如一开始我把测试激励的输出申明成了reg类型的就不行,后来改成了wire类型才对。

而且verilog 还得自己编写激励来测试。

Verilog很好,以后一定要学号。