s3c6410中文

S3C6410开发指南

S3C6410硬件开发指南1S3C6410综述S3C6410 是SAMSUNG公司基于ARM1176的16/32 位的高性能低功耗的RSIC 通用微处理器,适用于手持、移动等终端设备。

S3C6410 是一款低功率、高性价比、高性能的用于移动电话和通用处理RSIC 处理器。

为2.5G 和3G 通信服务提供了优化的硬件性能,采用64/32bit 的内部总线架构,融合了AXI、AHB、APB 总线。

还有很多强大的硬件加速器,包括运动视频处理、音频处理、2D加速、显示处理和缩放。

一个集成的MFC(Multi-Format video Codec)支持MPEG4/H.263/H.264 编解码和VC1 的解码,这个硬件编解码器支持实时的视频会议以及NTSC和PAL 制式的TV 输出。

此外还内置一个采用最先进技术的3D 加速器,支持OpenGL ES1.1/ 2.0 和D3DM API 能实现4M triangles/s 的3D 加速。

S3C6410 包括优化的外部存储器接口,该接口能满足在高端通信服务中的数据带宽要求。

接口分为两路,DRAM 和Flash/ROM/DRAM 端口。

DRAM 端口可以通过配置来支持Mobile DDR、DDR、Mobile SDRAM、SDRAM。

Flash/ROM/DRAM 端口支持NOR-Flash,NAND-Flash,OneNAND,CF,ROM 等类型的外部存储器和任意的Mobile DDR、DDR、Mobile SDRAM、SDRAM 存储器。

为了降低整个系统的成本和提升总体功能,S3C6410 包括很多硬件功能外设:Camera接口,TFT 24bit 真彩色LCD 控制器,系统管理单元(电源时钟等),4 通道的UART,32通道的DMA,4 通道定时器,通用I/O 口,I2S 总线,I2C 总线,USB Host,高速USB OTG,SD Host 和高速MMC 卡接口以及内部的PLL 时钟发生器。

cpu_modes®ister(S3C6410)

ARM 处理器模式和寄存器一、ARM处理器模式1.所有模式以及该模式对应的寄存器列表用户模式(User):ARM处理器正常的程序执行状态。

快速中断模式(FIQ):用于高速数据传输或通道处理。

外部中断模式(IRQ):用于通用的中断处理。

管理模式(Supervisor):操作系统使用的保护模式。

数据访问终止模式(Abort):当数据或指令预取终止时进入该模式,可用于虚拟存储及存储保护。

系统模式(System):运行具有特权的操作系统任务。

未定义指令中止模式(Undifined):当未定义的指令执行时进入该模式,可用于支持硬件协处理器的软件仿真。

2.中断类型及其对应的CPU模式二、ARM寄存器ARM共有37个32位寄存器,其中31个为通用寄存器,6个为状态寄存器.这些寄存器不能被同时访问,但在任何时候,通用寄存器R0~R14,程序计数器PC,一个或两个状态寄存器都是可访问的.通用寄存器包括R0~R15,可以分为3类:(1)未分组寄存器R0~R7(2)分组寄存器R8~R14(3)程序计数器PC(R15)1.未分组寄存器R0~R7在所有运行模式下,未分组寄存器都指向同一个物理寄存器,它们未被系统用作特殊的用途.因此在中断或异常处理进行运行模式转换时,由于不同的处理器运行模式均使用相同的物理寄存器,所以可能造成寄存器中数据的破坏.2.分组寄存器R8~R14对于分组寄存器,它们每一次所访问的物理寄存器都与当前处理器的运行模式有关.对于R8~R12来说,每个寄存器对应2个不同的物理寄存器,当使用FIQ(快速中断模式)时,访问寄存器R8_fiq~R12_fiq;当使用除FIQ模式以外的其他模式时,访问寄存器R8_usr~R12_usr.对于R13,R14来说,每个寄存器对应6个不同的物理寄存器,其中一个是用户模式与系统模式共用,另外5个物理寄存器对应其他5种不同的运行模式,并采用以下记号来区分不同的物理寄存器: R13_R14_其中mode可为:usr,fiq,irq,svc,abt,und.寄存器R13在ARM指令中常用作堆栈指针,用户也可使用其他的寄存器作为堆栈指针,而在Thumb指令集中,某些指令强制性的要求使用R13作为堆栈指针.寄存器R13在ARM指令中常用作堆栈指针,但这只是一种习惯用法,用户也可使用其他的寄存器作为堆栈指针。

基于S3C6410的多通道多功能无纸记录仪的设计与实现的开题报告

基于S3C6410的多通道多功能无纸记录仪的设计与实现的开题报告一、课题背景无纸记录仪是一种用于记录数据的仪器,主要用于工业生产、科学研究、环境监测等领域。

传统的无纸记录仪通常使用磁带或光盘等存储介质,数据采集方式单一,功能相对较为简单。

随着科技的发展,人们对无纸记录仪的要求越来越高,需要具备多通道、多功能、高精度、高可靠性等特点,同时还需要具备数据传输、存储、处理等功能。

本课题基于ARM9 MCU(S3C6410)平台,设计并实现了一种多通道多功能无纸记录仪。

该设备具有以下特点:1. 多通道数据采集采用ADC(模数转换器)芯片进行多通道数据采集,可实现温度、电压、电流、光照等多种信号采集。

2. 低功耗设计通过MCU的休眠和唤醒机制,实现低功耗设计,延长电池寿命。

3. 数据存储与传输采用SD卡存储数据,可支持大容量数据存储。

同时,实现了USB、串口等多种数据传输方式,方便数据导出和分析。

4. 可编程控制通过可编程控制实现自动化控制,可以根据不同需要设置不同的采样间隔和采样参数。

5. 友好的用户界面通过TFT-LCD显示屏展示采集数据和系统状态,实现友好的用户界面。

二、研究目的和意义本课题旨在设计并实现一种高性能、高可靠性的多通道多功能无纸记录仪,解决传统记录仪功能单一、数据采集精度低、易出现故障等问题,满足不同领域对于数据采集、存储和传输的需求。

同时,该记录仪采用低功耗设计,可以避免不必要的能源浪费,长时间稳定工作,具有重要的应用价值和普及意义。

三、研究内容和技术路线1. 设计记录仪硬件电路根据需求设计记录仪的硬件电路,包括MCU选型、数据采集电路、存储器、显示屏、电源等。

2. 开发记录仪的软件系统利用ARM9的评估板进行开发,基于嵌入式操作系统Linux搭建开发环境,开发记录仪的软件系统,包括数据采集、存储、传输、自动化控制等模块。

3. 系统调试和性能测试通过实验对记录仪的各项功能进行测试和调试,评估其性能和稳定性。

第13章S3C6410的IO口及操作

1.输出高电平。也就是引脚作为输出电压管 脚,输出高电平,简单的说就是3.3V电压。 2.输出低电平。也就是引脚作为输出电压管 脚,输出低电平。简单的说就是0V电压。 3.输入状态。这时,引脚高低电平完全由外 界对引脚的输入电压决定。 4 .高阻态。引脚什么都不接,或者说是悬 空。 GPIO 作为普通的输入输出引脚使用时,主要 使用输入、输出的功能。所以在开始的学习中, 主要考虑GPIO的输入和输出功能。其它功能根据 不同的使用条件下对其进行相应的设置。

硬件实验电路如图 13-1 所示,发光二极管 分别与GPK4~GPK7管脚相连接,发光二极管LE D 的一端连接到了 S3C6410 的 GPIO ,另一端经 过一个限流电阻接电源 VDD3V3 。当 GPIO 口为 低电平时, LED 两端产生电压降,这时 LED 有 电流通过并发光。反之当GPIO为高电平时,L ED 将熄灭。注意亮灭之间要有一定的延时, 以便人眼能够区分出来。 端口K控制寄存器包括四个控制寄存器,分 别是GPKCON0、GPKCON1、GPKDAT、GPKPUD。

//GPIO端口赋值 void LED_Display(int data) { rGPKDAT = (rGPKDAT & ~(0xf<<4)) | ((data & 0xf)<<4); } //延时函数 Void LedDelay(void) { int i; for(i=0 ; i < 100000 ; i++) { } }

13.3.2 实现功能和编程思路 编写程序实现 LED2 、 LED3 先亮, LED1 、 LED4 再 亮,如此交替循环亮灭,编写程序的思路如流程 图所示,先编写对 GPIO 初始化函数, GPIO 赋值的 函数、延时函数,再在主函数中调用相关函数进 行对I/O口控制,实现LED亮灭。

第17章S3C6410的实时时钟

17.2

RTC应用编程实例

本实例利用S3C6410的实时时钟功能,通过 超级终端显示实时时钟,包括RTC初始化、初 始时间设定、时间读取以及超级终端打印实 RTC实时时间等程序,以供参考。

#include "module_cfg.h" #include "s3c6410_addr.h" #include "interrupt.h" #include "rtc.h" #ifdef RTC_TEST int year, mon, date, weekday, hour, min, sec; char *week[7] = {"SUN", "MON", "TUES", "WED", "THURS", "FRI", "SAT"}; int led_index=0; void get_rtc(void) { rRTCCON = 0x1; if(rBCDYEAR == 99) year = 0x1999; else year = 0x2000 + rBCDYEAR; mon = rBCDMON;

17.3 习 题 1.S3C6410 RTC 具有哪些特点? 2 . S3C6410 RTC 控制寄存器 RTCCON 各位的 代表什么意思,如何使用? 3 . S3C6410 RTC 告警寄存器 RTCALM 各位的 代表什么意思,如何使用? 4.熟悉实例程序,学会按照自己思路设置 时间、读取时间、按照一定格式在超级终端 显示读取的时间。 5.实时时钟标记时间的周期如何计算?

date = rBCDDATE; weekday = rBCDDAY; hour = rBCDHOUR; min = rBCDMIN; sec = rBCDSEC; if(sec == 0){ if(rBCDYEAR == 0x99) year = 1999; else year = 0x2000 + rBCDYEAR; mon = rBCDMON; date = rBCDDATE; weekday = rBCDDAY; hour = rBCDHOUR; min = rBCDMIN; } rRTCCON = 0x0; }

28 S3C6410 MIPI HSI

2828.1 概述MIPI HIS 接口控制器MIPI HIS 接口是一种高速同步串行接口。

图 28-1MIPI HIS 信号定义模块图图 28-2MIPI HIS 传输实例模块图28.1.性能 性能MIPI HIS Rx/Tx 控制器主要性能如下: MIPI HIS 接口是单向接口。

MIPI HIS RX 最大带宽是 100Mbps,MIPI HIS Tx 控制器使用 PCLK 进行数据传输。

1. TX 模块 状态寄存器 ●FIFO 状态 ●MIPI 状态 配置寄存器 ●选择运行模式(流模式或帧模式) ●固定通道 ID 模式 ●通道序号 ●清除产生的错误 ●TxHOLD 状态定时器使能 ●TxIDLE 状态定时器使能 ●TxREQ 状态定时器使能 中断源寄存器 ●FIFO 空 ●打破帧转换完成 ●TxHOLD 状态超时 ●TxIDLE 状态超时 ●TxREQ 状态超时 中断屏蔽寄存器 软件复位寄存器 通道 ID 寄存器 数据寄存器 ●Tx FIFO 输入 ●Tx FIFO 尺寸:▼32 位宽度×32 位深度(128 字节)2.RX 模块 状态寄存器 ●FIFO 状态 ●MIPI 状态 配置寄存器 0 ●选择运行模式(流模式或帧模式) ●固定通道 ID 模式 ●通道序号 ●清除产生的错误 ●RxACK 状态定时器使能 ●Rx 状态 定时器 配置寄存器 1 ●Rx FIFO 清除●Rx FIFO 定时器使能 中断源寄存器 ●Rx FIFO 满 ●数据接收完成 ●Rx FIFO 超时 ●接收的打破帧 ●打破帧接收错误 ●RxACK 状态超时 ●丢失的时钟输入 ●增加的时钟输入 软件复位寄存器 通道 ID 寄存器 数据寄存器 ●Rx FIFO 输入●Rx FIFO 尺寸: ▼32 位宽度×64 位深度(128 字节)28.2.模块图 模块图1. 顶级模块图 Rx 模块部分基础架构与 Tx 模块部分相似图 28-3MIPI HIS 接口控制 Tx 模块顶层模块图图 28-4MIPI HIS 接口控制 Rx 模块顶层模块图Tx 模块部分并行-串行块图 28-5 并行-串行块(Tx 模块部分)Rx 模块部分串行-并行块图 28-6 串行-并行块(Rx 模块部分)28.2 I/O 描述1. TX 模块 I/O 列表表 28-1 Tx I/O 描述 名称 MIPI HSI 接口信号(Tx) TX_DATA TX_FLAG TX_WAKE TX_READY 1 1 1 1 I I I O MIPI HSI 数据行 MIPI HSI 标志行 MIPI HSI 从其它部分 Tx 的唤醒行 MIPI HSI 向其他部分 Tx 的准备行 #位 I/O 功能如果 DMA 请求使能位在中断和 DMA 请求屏蔽寄存器内使能,Tx 模块在 FIFO 为空闲状态时请求 DMA.2.RX 模块 I/O 列表表 28-2 Rx I/O 描述 名称 MIPI Hsi 接口信号(Tx) RX_DATA RX_FLAG RX_WAKE RX_READY 1 1 1 1 O O O I MIPI HSI 数据行 MIPI HSI 标志行 MIPI HSI 向其它部分 Rx 的唤醒行 MIPI HSI 从其他部分 Rx 的准备行 #位 I/O 功能如果 DMA 请求使能位在中断和 DMA 请求屏蔽寄存器内使能,以及配置寄存器 0 内的 DMA 请求阈 值位被设置为(0x00~0x11) ,Rx 模块在 Rx FIFO 数据数量大于阈值时,配置寄存器内的 Rx 模块将请求 DMA.28.3 时序图1.波形 波形图 28-7 波形模块图2. 信号时序 信号时序表 28-3 信号时序 参数 TNomBit TMinEdgeSep TNomBit tRise and tFall 额定位时间 DATA 和 FLAG 信号过度时间允许的最小间隔 允许的结合扭曲和抖动的最大时间。

第15章S3C6410的串口UART

2.数据接收 和数据发送一样,数据帧接收也是可编程 的。它是由一个起始位, 5 ~ 8 个数据位,一 个可选的奇偶位和 1 ~ 2 位停止位组成。实际 上 接 收 器 就 是 将 发 送 器 做 的 工 作 反过 来 执 行。接收器可以检测到溢出错误、奇偶错 误、帧错误和中断条件,并为它们设置错误 标志。溢出错误说明在数据被读取之前,新 的数据已经将原有的数据覆盖。奇偶错误说 明接收器已经检测到一个意外的奇偶条件。 帧错误表示收到的数据没有有效的停止位。 中断条件表明接收过程中置位逻辑状态 0的时 间比发送一帧的时间长。

15.1

S3C6410的串口概述

15.1.1 S3C6410串行通信单元 S3C6410具有四个独立的UART端口,每个端 口都可以通过中断或者 DMA ( Direct Memory Acess )模式来操作。 S3C6410 的 UART 可支持 高达3Mbps的传输速率,每个UART通道包含两 个64字节的FIFO缓冲寄存器。S3C6410的UART 通道 0 、 1 支持 nRTS0 , nCTS0 , nRTS1 和 nCTS1 引脚功能,能够通过它们实现自动流量控 制,如果需要将 UART 与调制解调器相连,则 必须在调制解调器控制寄存器 UMCONn 中将自 动流量控制功能禁止。

1.UART行控制寄存器 在UART模块包括四个行控制寄存器,即ULCON0、ULCON1、 ULCON2和ULCON3,下面就来看看行控制寄存器的位定义

5.UART 接 收 Rx/Tx 发 送 状 态 寄 存 器 UART 模 块 有 四 个 UART 接 收 / 发 送 状 态 寄 存 器 : UTRSTAT0 、 UTRSTAT1 、 UTRSTAT2 和 UTRT端口初始化设置 rGPACON &= ~0xff; rGPACON |= 0x22; rGPAPUD = (rGPAPUD & ~(0xf<<0)) | (0x1<<0); 2.UART串口初始化设置 rULCON0 = 0x3; rUCON0 = 0x5; rUFCON0 = 0x0; rUMCON0 = 0; // DIV_VAL = (PCLK / (bps x 16 ) ) - 1 = (66500000/(115200x16))-1 = 35.08 // DIV_VAL = 35.08 = UBRDIVn + (num of 1 s in UDIVSLOTn)/16 rUBRDIV0 = 35; rUDIVSLOT0 = 0x1;

基于S3C6410的视频采集卡设计

基于S3C6410的视频采集卡设计近年来,随着数字化技术的快速发展,视频采集卡作为重要的外设设备被广泛应用于监控、视频会议、教育等领域。

本文将介绍一种基于S3C6410的视频采集卡设计。

首先,我们简要介绍一下S3C6410芯片。

S3C6410是由韩国三星公司研发的一款高性能嵌入式处理器,采用了ARM Cortex-A8架构,主频可达667MHz。

该芯片具备较高的计算能力和丰富的外设接口,适合用于视频采集卡的设计。

基于S3C6410的视频采集卡设计的关键在于采集和传输视频信号。

设计中,我们选择了一款高性能的CCD摄像头作为视频信号的源头,并通过接口连接到S3C6410芯片的摄像头输入引脚。

芯片内部的视频采集模块可以将视频信号转换成数字信号,并进行处理和编码。

然后,通过S3C6410芯片的高速USB接口将编码后的视频数据传输到计算机端。

在设计过程中,我们需要考虑到视频信号的稳定性和传输速率的要求。

为了保证视频信号的质量,我们使用了一些滤波电路和放大电路来消除噪声并增强信号。

另外,为了实现高速数据传输,我们采用了USB 2.0接口,该接口具备较高的传输速率和较低的延迟。

在软件方面,我们需要编写驱动程序来控制摄像头和S3C6410芯片的视频采集模块。

驱动程序可以控制摄像头的曝光、对比度等参数,并将采集到的视频数据通过USB接口传输到计算机端。

在计算机端,我们可以使用相应的软件进行视频的实时显示、录制和处理。

通过基于S3C6410的视频采集卡设计,我们可以实现高质量、高速率的视频采集和传输。

这种设计可以广泛应用于监控系统、视频会议系统以及教育培训等领域。

同时,基于S3C6410芯片的设计还具备较高的灵活性和可扩展性,可以根据实际需求进行定制和升级。

总之,基于S3C6410的视频采集卡设计是一种高性能、高可靠性的解决方案。

它为视频采集和传输提供了强大的硬件支持,并且具备较好的软件适配能力。

相信随着技术的不断发展,基于S3C6410的视频采集卡将在各个领域发挥更加重要的作用。

三星S3C6410用户手册中文版

2.ARM1176JZFARM1176JZF-S 处理器 ARM1176JZF-S 处理器的特性包括: (1)TrustZone™安全扩展。 (2)具有超高速先进的微处理器总线架构(AMBA) 、先进的可扩展接口(AXI)电平,两个接口支持 的优先级顺序多处理机。 (3)8 阶管线。 (4)具有返回堆栈的分支预测。 (5)低中断延时配置。 (6)外部协处理器接口和协处理器 CP14 和 CP15 。

7.IrDA v1.1 IrDA v1.1 特性包括: (1)专用的 IrDA 作为 v1.1( 1.152Mb/s 和 4 Mb/s )。 (2)支持 FIR( 4Mb/s )。 (3)SIR( 111.5kb/s )模式是由 UART 的 IrDA 1.0 模块支持的。 (4)内部 64 字节的 Tx/Rx FIFO。 串行通行特性: (1)UART 4 通道 UART 具有基于 DMA 或基于中断操作。 支持 5 位, 6 位, 7 位,或 8 位串行数据传输/接收。

8.调制解调器接口 调制解调器接口特性包括: 并行调制解调器芯片接口 异步直接和间接 16 位 SRAM 式接口(i80 接口)。 片上 8KB 的双端口 SRAM 缓冲区直接接口。 片上写 FIFO 和读 FIFO (每 288 字),以支持间接脉冲数据传输。

9.GPIO GPIO 特性包括: 188 个灵活配置的 GPIO。 输入设备特性: (1)便携式键盘接口 支持 8×8 键盘矩阵转换电路。 提供内部去抖滤波器。 (2)A/D 转换和触摸屏接口 8 通道复用 ADC。 最大 500k 采样/S 和 10 位分辨率。

第一章

S3C6410 处理器概述

S3C6410 是一个 16/32 位 RISC 微处理器,旨在提供一个具有成本效益、功耗低,性能高的应用处理器 解决方案,像移动电话和一般的应用。它为 2.5G 和 3G 通信服务提供优化的 H /W 性能, S3C6410 采用了 64/32 位内部总线架构。该 64/32 位内部总线结构由 AXI、AHB 和 APB 总线组成。它还包括许多强大的硬件 加速器,像视频处理,音频处理,二维图形,显示操作和缩放。一个集成的多格式编解码器( MFC )支 持 MPEG4/H.263/H.264 编码、译码以及 VC1 的解码。这个 H/W 编码器/解码器支持实时视频会议和 NTSC、 PAL 模式的 TV 输出。 S3C6410 有一个优化的接口连线到外部存储器。存储器系统具有双重外部存储器端口、 DRAM 和 FLASH /ROM/ DRAM 端口。 DRAM 的端口可以配置为支持移动 DDR,DDR,移动 SDRAM 和 SDRAM 。FLASH/ROM/DRAM 端口支持 NOR-FLASH,NAND-FLASH,ONENAND,CF,ROM 类型外部存储器和移动 DDR,DDR,移动 SDRAM 和 SDRAM 。 为减少系统总成本和提高整体功能,S3C6410 包括许多硬件外设,如一个相机接口,TFT 24 位真彩色 液晶显示控制器,系统管理器(电源管理等) ,4 通道 UART,32 通道 DMA,4 通道定时器,通用的 I/O 端口, IIS 总线接口,IIC 总线接口,USB 主设备,在高速(480 MB/S)时 USB OTG 操作,SD 主设备和高速多媒 体卡接口、用于产生时钟的 PLL。 S3C6410 提供了丰富的内部设备,下面我们从它的整体特性、多媒体加速特性、视频接口、USB 特征、 存储器设备、系统外设以及它的系统管理等方面来详细的介绍 S3C6410 处理器的特性:

S3C6410X_ARM11_精简指令系统_省略_croprocessor_的特

setsockopt(sockfd ,SOL_SOCKET, SO_REUSEADDR, &j,sizeof(j) ); server_sockaddr.sin_family=AF_INET; server_sockaddr.sin_port=htons(SERVPORT); server_sockaddr.sin_addr.s_addr=INADDR_ANY; bzero(&(server_sockaddr.sin_zero),8); //端口绑定 if(bind(sockfd,(struct sockaddr 觹)&server_sockaddr,sizeof(struct sockaddr))==-1)

关 键 词 : RISC SIMD TrustZone IEM Dhrystone 中图分类号: TP332 文献标识码: A 文章编号:1002-2422(2009)06-0022-03

Introduction and An Application Instance of S3C6410(ARM11) Embedded RISC Microprocessor

在第五届 “博创杯” 全国大学生嵌入式大赛中使用 S3C6410,题目是“嵌入式肿瘤光子热疗系统”。

此系统采用分级分部式控制。各层次 Internet 连接采用 客户 / 服务器端 (Client / Server) 的形式,S3C6410 做服务 端,PC 机做客户端。上位机在 Delphi 程序中,使用流式套接 字控 CBClient。下位机在 C 语言中使用 Srver 套接字。使不

Hou Dianyou Liu Xiaoguang Ji He Abstract: The S3C6410X is a 16/32bit RISC micorprocessor,which is based on ARM11 core and produced by Samsung Elect-

S3C6410处理器的简介

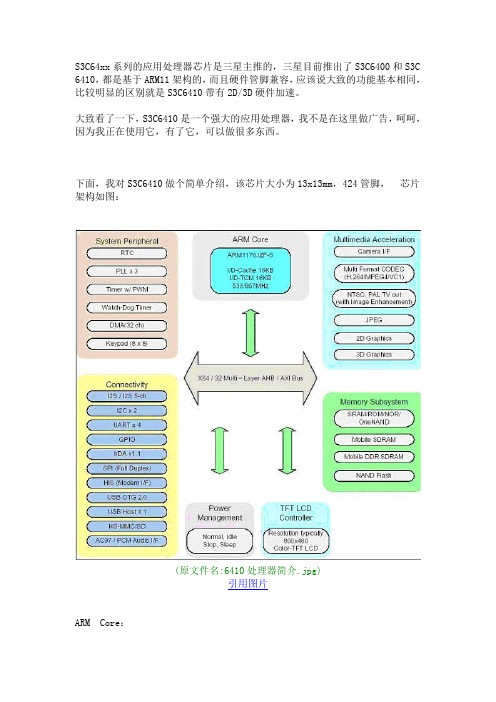

S3C64xx系列的应用处理器芯片是三星主推的,三星目前推出了S3C6400和S3C 6410,都是基于ARM11架构的,而且硬件管脚兼容,应该说大致的功能基本相同,比较明显的区别就是S3C6410带有2D/3D硬件加速。

大致看了一下,S3C6410是一个强大的应用处理器,我不是在这里做广告,呵呵,因为我正在使用它,有了它,可以做很多东西。

下面,我对S3C6410做个简单介绍,该芯片大小为13x13mm,424管脚,芯片架构如图:(原文件名:6410处理器简介.jpg)引用图片ARM Core:采用ARM1176JZF-S的核,包含16KB的指令数据Cache和16KB的指令数据TCM,ARM Core电压为1.1V的时候,可以运行到553MHz,在1.2V的情况下,可以运行到667MHz。

通过AXI,AHB和APB组成的64/32bit内部总线和外部模块相连。

Power Management:目前支持Normal,Idle,Stop和Sleep模式。

Normal是正常模式,其他模式都处于不同程度的低功耗模式下,说白了就是还有哪些模块在工作,可以被哪些中断唤醒。

Sleep模式是最低功耗模式了,可以被有限的中断唤醒。

关于在这几种模式下,芯片的功耗到底是多少,目前不得而知,将来一定要测试一下。

TFT LCD Controller:显示控制器,支持TFT 24Bit LCD屏,分辨率能支持到1024x1024。

显示输出接口支持RGB接口,I80接口,BT.601输出(YUV422 8Bit)和输出给TV Encoder 的接口。

支持最多5个图形窗口并可进行Overlay操作,从window0到window4,分别支持不同的图像输入源和不同的图像格式。

实际上,显示控制器可以接收来自Carema,Frame Buffer和其他模块的图像数据,可以对这些不同的图像进行Overlay,并输出到不同的接口,比如LCD,TV Encoder。

ARM11_s3c6410_和ARM9_2410^2240_的区别

ARM11(s3c6410)和ARM9(2410/2240)的区别推荐作为GPS、PDA、数字电视等手持设备的主要方案处理器提供方韩国Sumsung公司,推出ARM处理器S3C2450、S3C6410芯片。

1.这些平台又与S3C2440处理器有哪些区别优势,主频400MHz SDRam内存控制器;支持 Nor Flash和Nand Flash支持2种Flash 启动,内部LCD、I2C、Camera等控制器.2.S3C2450 主频533MHz 双总线架构,一路用于内存总线、一路用于Flash总线DDRII内存和DDR内存控制器;支持Nor Flash 和Nand Flash两种Flash,其中Nand Flash支持 SLC和MLC两种架构,从而大大扩C大存储空间.支持多种启动方式:主要包括SD、Nand Flash、Nor Flash和OnenandFlash等设备启势 8路DMA 通道,包括LCD、UART、Camera 等专用DMA通道USB2.0 从设备控制器内部LCD、I2C、Camera等控制器.3.S3C6410主频800MHz 双总线架构,一路用于内存总线、一路用于Flash总线DDR内存控制器;支持Nor Flash和Nand Flash 两种Flash,其中Nand Flash支持SLC和MLC两种架构,从而大大扩大存储空间;支持多种启动方式:主要包括SD、Nand Flash、Nor Flash和OneFlash等设备启势8路DMA通道,包括LCD、UART、Camera等专用DMA通道 USB2.0 OTG控制器;内部视频解码器,包括MPEG4、H.264、H.263等视频格式(硬件解码和编码);内部视频加速器,包括D1处理Tvout和S-Video输出,内部LCD、UART、SPI、I2C、 Camera、GPIO等控制器,S3C2450基于S3C2440除了提升主频外,主要增加DDR控制和MLC 架构Nand Flash控制器,这些主要用于提升产品处理速度和增大存储空间,从而给终端用户更优越的性能体验。

【国家自然科学基金】_s3c6410_基金支持热词逐年推荐_【万方软件创新助手】_20140801

2013年 序号 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37

科研热词 s3c6410 arm 嵌入式系统 嵌入式 视频传输 嵌入式linux 驱动程序 非局部均值滤波 降噪 车载终端 车载智能中心 温室 气调保鲜运输车 智能化 星型网络拓扑结构 无线自动滴灌 无线传输 数据存储 控制系统 报警 图像采集系统 图像处理 图像 同步采集 zigbee wifi usb u-boot stm32 sd卡启动系统 qt集成开发环境 opencv hkt-80收发模块 h264 camshift算法 arm11 3g

推荐指数 1 1 1 1 1 1 1 1 1

2011年 序号 1 2 3 4 5 6 7 8 9 10 11 12 13

科研热词 s3c6410 解码 红外遥控电路 红外图像 检漏定位 帧间差分 嵌入武多媒体系统 局部熵差 图像处理 wince sf6气体 qr码 directshow

推荐指数 2 1 1 1 1 1 1 1 1 1 1 1 1

推荐指数 4 4 3 3 2 2 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

2014年 序号 1ຫໍສະໝຸດ 2 3 4 5 6 7 8 9科研热词 网络主机 智能小区 数据采集 数据存储 嵌入式linux s3c6410 qt linux arm11

2012年 序号 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30

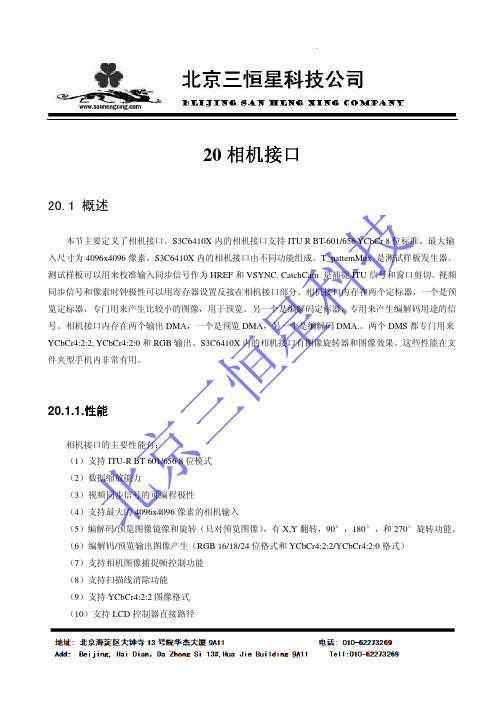

20 S3C6410 相机接口

20 相机接口20.1 概述本节主要定义了相机接口。

S3C6410X 内的相机接口支持 ITU R BT-601/656 YCbCr 8 位标准。

最大输 入尺寸为 4096x4096 像素。

S3C6410X 内的相机接口由不同功能组成。

T_pattemMux 是测试样板发生器。

测试样板可以用来校准输入同步信号作为 HREF 和 VSYNC. CatchCam 是捕捉 ITU 信号和窗口剪切。

视频 同步信号和像素时钟极性可以用寄存器设置反接在相机接口部分。

相机接口内存在两个定标器,一个是预 览定标器,专门用来产生比较小的图像,用于预览。

另一个是编解码定标器,专用来产生编解码用途的信 号。

相机接口内存在两个输出 DMA,一个是预览 DMA,另一个是编解码 DMA.。

两个 DMS 都专门用来 YCbCr4:2:2, YCbCr4:2:0 和 RGB 输出。

S3C6410X 内的相机接口有图像旋转器和图像效果。

这些性能在文 件夹型手机内非常有用。

20.1.1.性能 性能相机接口的主要性能有: (1)支持 ITU-R BT 601/656 8 位模式 (2)数据缩放能力 (3)视频同步信号的可编程极性 (4)支持最大的 4096x4096 像素的相机输入 (5)编解码/预览图像镜像和旋转(只对预览图像) ,有 X,Y 翻转,90°,180°,和 270°旋转功能。

(6)编解码/预览输出图像产生(RGB 16/18/24 位格式和 YCbCr4:2:2/YCbCr4:2:0 格式) (7)支持相机图像捕捉帧控制功能 (8)支持扫描线消除功能 (9)支持 YCbCr4:2:2 图像格式 (10)支持 LCD 控制器直接路径(11)支持交错相机输入图 20-1相机接口概述表 20-1 预览和编解码混合水平尺寸 预览 Prescaled input max hsize Scaler bypass TargetHsize(不旋转) 720 像素 4096 4096 像素(bypass YCbCr) 720 像素(Except Bypass) TargetHsize(旋转) 720 像素(RGB) 360 像素(YCbCr) 编解码 2048 像素 4096 像素 4096 像素(bypass YCbCr) 2048 像素(Except Bypass)20.1.2.外部接口 外部接口相机几口支持下面所述视频标准。

基于S3C6410的井下救援视频处理终端

基于S3C6410的井下救援视频处理终端

李文峰;苏谢明;徐克强

【期刊名称】《现代矿业》

【年(卷),期】2013(000)003

【摘要】针对现有井下救援视频信号差,易受环境干扰,系统集成度低,不能实时显示现场救援信息等问题,提出了一种适用于井下救援通信的嵌入式视频信号处理系统.系统主要包括井下视频采集端和井上救援指挥端.井下视频采集端系统采用Linux作为软件开发平台,利用S3C6410自带的编码器MFC对视频数据进行H.264标准压缩编码;井上救援指挥端系统在VS2005开发环境下实现视频解码,网络传输和应用程序的开发,并针对矿山救援环境特点优化开源H.264解码算法.该系统完成了救援现场视频处理,提高了设备集成度和视频画面清新度,实现了井下救援的可视化.

【总页数】3页(P44-46)

【作者】李文峰;苏谢明;徐克强

【作者单位】西安终南信息技术有限公司

【正文语种】中文

【相关文献】

1.基于Linux的S3C6410核心唯一性信息采集终端的研发 [J], 周倩;李会坤;陈慧;李秀英

2.基于S3C6410和3G网络的远程数据监控终端设计 [J], 王会;张国友;

3.基于S3C6410平台的RFID手持终端的设计与实现 [J], 杨海科;张建奇

4.基于S3C6410智能机柜监控终端的设计与实现 [J], 贾长青;吴凡;孙颖

5.基于S3C6410的无线网络学习终端设计 [J], 王立国

因版权原因,仅展示原文概要,查看原文内容请购买。

MEMORY存储芯片S3C6410X66-YB40中文规格书

28.7 SPECIAL FUNCTION REGISTERS28.7.1 REGISTER MAPMIPI HSI Tx Controller Register Map TableTable 28-4. Tx Controller Register Map TableRegister Address Description Reset Value TX_STATUS_REG 0x7E006000 MIPI HSI Tx controller status register 0x00010000 TX_CONFIG_REG 0x7E006004 MIPI HSI Tx controller configuration register 0xFFFFFF02Reserved register area 0x00000000 Reseved0x7E006008TX_INTSRC_REG 0x7E00600C MIPI HSI Tx controller interrupt source register 0x00000000 TX_INTMSK_REG 0x7E006010 MIPI HSI Tx controller interrupt mask register 0x8000001Fcontroller software reset 0x00000000 TX_SWRST_REG 0x7E006014 TxTX_CHID_REG 0x7E006018 MIPI HSI Tx controller channel ID register 0x00000000 TX_DATA_REG 0x7E00601C MIPI HSI Tx controller data register (FIFO input) 0x00000000MIPI HSI Rx Controller Register Map TableTable 28-5. Rx Controller Register Map TableRegister Address Description Reset Value RX_STATUS_REG 0x7E007000 MIPI HSI Rx controller status register 0x00010000 RX_CONFIG0_REG 0x7E007004 MIPI HSI Rx controller configuration register 0x0FFFFF02 RX_CONFIG1_REG 0x7E007008 MIPI HSI Rx controller configuration register 0x00FFFFFF RX_INTSRC_REG 0x7E00700C MIPI HSI Rx controller interrupt source register 0x00000000 RX_INTMSK_REG 0x7E007010 MIPI HSI Rx controller interrupt mask register 0x800001FFcontroller software reset 0x00000000 RX_SWRST_REG 0x7E007014 RxMIPI HSI Rx controller channel ID register 0x00000000 RX_CHID_REG0x7E007018RX_DATA_REG 0x7E00701C MIPI HSI Rx controller data register (FIFO output) 0x00000000MIPI HSI 6410X_UM28.8 INDIVIDUAL REGISTER DESCRIPTIONS (TX CONTROLLER)28.8.1 TX_STATUS_REGTX_STATUS_REG is an internal logic monitoring window.Table 28-6. TX_STATUS_REG register descriptionRegister Address R/W Description Reset Value TX_STATUS_REG 0x7E00_6000 R MIPI HSI Tx controller status register 0x00010000Bits Name Description R/W Reset Valuebit R0x0[31]reserved Reserved[30:28] next_state Next state* R 0x0bit R0x0[27]reserved Reservedstate Current state* R 0x0 [26:24] current[23:18] reserved Reserved bits R 0x00R0x0[17]FIFO_full TxFIFOfull0 : FIFO not full 1 : FIFO fullR0x1empty[16] FIFO_empty TxFIFO0 : FIFO not empty 1 : FIFO empty[15:13] reserved Reserved bits R 0x0 [12:8] tx_rd_point TxFIFO read point R 0x00 [7:5]reserved Reservedbits R0x0 [4:0] tx_wr_point TxFIFO write point R 0x00•State register value000 : IDLE001 : TxREQ010 : Tx011 : TxHOLD100 : TxIDLE101 : Reserved state110 : TxBRK111 : TxERR6410X_UM MIPI HSI28.8.2 TX_CONFIG_REGCONFIG_REG is used to set the configuration of Tx controller.Table 28-7. TX_CONFIG_REG register descriptionRegister Address R/W Description Reset ValueTX_CONFIG_REG 0x7E00_6004 R/W MIPI HSI Tx controller configuration register 0xFFFFFF02Bits Name Description R/W Reset Value [31:24] TxHOLD time TxHOLD state timer setting value R/W 0xFF [23:16] TxIDLE time TxIDLE state timer setting value R/W 0xFF [15:8] TxREQ time TxREQ state timer setting value R/W 0xFFR/W 0x0[7] TxHOLD time_en TxHOLD state timer enabler0 : disable 1 : enable[6] TxIDLE time_en TxIDLE state timer enablerR/W 0x00 : disable 1 : enableR/W 0x0[5] TxREQ time_en TxREQ state timer enabler0 : disable 1 : enableR/W 0x0[4] Err_clr Generated Error clear0 : stay 1 : clear[3:2] Width of CHID Width of channel ID R/W 0x0[1] Burst_mode Fixed channel ID modeR/W 0x10 : Burst ch ID mode 1 : Single ch ID modeR/W 0x0mode[0] Frame_modeFrame0 : Stream mode 1 : Frame mode28.8.3 TX_INTSRC_REGINTSRC_REG is interrupt source pending register.Table 28-8. TX_INTSRC_REG register descriptionRegister Address R/W Description Reset ValueTX_INTSRC_REG 0x7E00_600C R/W MIPI HSI Tx controller interrupt source register 0x00000000Bits Name Description R/W Reset Value [31:5] Reserved Reserved bits R 0x0000001[4] TxH_timeout TxHOLD state timeout interrupt (set ‘1’ for clearing) R/W 0x0[3] TxI_timeout TxIDLE state timeout interrupt (set ‘1’ for clearing) R/W 0x0[2] TxR_timeout TxREQ state timeout interrupt (set ‘1’ for clearing) R/W 0x0MIPI HSI 6410X_UM6410X_UM MIPI HSI28.8.5 TX_SWRST_REGSWRST_REG is software reset.Table 28-10. TX_SWRST_REG register descriptionRegister Address R/W Description Reset ValueTX_SWRST_REG 0x7E00_6014 R/W Tx controller software reset 0x00000000Bits Name Description R/W Reset Value [31:1] Reserved Reserved bits R 0x00000000R/W 0x0[0] Sw_rst Software reset0 : set 1 : reset28.8.6 TX_CHID_REGCHID_REG is used to transfer channel ID.Table 28-11. TX_CHID_REG register descriptionRegister Address R/W Description Reset ValueTX_CHID_REG 0x7E00_6018 R/W MIPI HSI Tx controller channel ID register 0x00000000Bits Name Description R/W Reset Value[31] Break_frame Break frame transfer in Frame modeR/W/C 0x0 In auto clear mode, this bit is automatically cleared.But the other mode, TxDATA send ‘0’ stream duringsetting ‘1’ at br_frame_clr bit.[30] Auto_clr Break frame auto clear bitR/W0x00 : auto clear & TxBRK state end1 : auto clear disable & TxBRK state continueframe continuing transfer W 0x0[29] Br_frame_clr Stopbreak[28:3] Reserved Reserved bits R 0x0000000ID R/W0x0 [2:0]CHID ChannelNOTE:In order to send data , the TX_CHID_REG must be set first and then the data to betransfered are pushed into the data fifo. The same channel ID is attached to each of the data when it sent throughTxDATA. If the channel ID is different from the previous one, you must set the new channel ID into theTX_CHID_REG before pushing data into the data fifo. Break frame is sent to Rx side when ‘1’ is inputted for theBreak_frame bit in the frame mode. This bit is automatically cleared after the transmission is completed (36 ‘0’sare transffered) in the auto clear mode (auto clear bit =0). In this case, the internal state goes to IDLE state. If not in the auto clear mode, the TxDATA continues to transfer ‘0’ while the internal state maintained in TxBRK state.Meanwhile, if the br_frame_clr bit is written as ‘1’, the state changes from RxBRK to IDLE and the TxDATA stops to transfer ‘0’s.。

MEMORY存储芯片S3C6410XH-66中文规格书

42.10 PIXEL SHADER42.10.1 OVERVIEWThe proposed shader consists of 4-way floating point SIMD architecture and small scalar core. Each data path has 4-way float type register and scalar register, respectively.The simplified pixel shader block diagram and its interface are shown in the Figure 6-1. The input data is pixel attributes such as position, color and texture coordinate coming from rasterizer. Instruction and predefined constants are downloaded from host processor for the shader execution. Temporary register, loop counterregister, predicate register are cooperated for pixel processing. For the texture mapping, the pixel shader interacts with texture unit. The processed pixel data is finally transferred to per-fragment units through output register.Figure 6-1 Pixel Shader Block DiagramProgrammable shader has two register groups according to its usage. One is special function register (SFR) for HW configuration and the other is program register for shader program. SFR can be accessed by only HOSTCPU. Some of program registers such as instruction memory, constant float register, constant integer register and constant Boolean register can be access by both HOST CPU and shader itself according to programmable shader operation mode. Other program register can be access by programmable shader and interface block such as rasterizer or per-fragment unit. In this document, the register which can be accessed by HOST CPU is briefly overviewed. The details of pixel shader operation are covered separated document “the Programmable Shader S/W Developer’s Guide”.GRAPHIC 3D 6410X_UM6410X_UM GRAPHIC3D FGTU_TSTAn Bit Description Initial StateTEXTURE _FORMAT [16:12] TextureFormat00000b = 1555 00001b = 56500010b = 4444 00011b = Depth Component 1600100b = 88(intensity/alpha)00101b = 8 (monochromatic map, replicated in all channel)00110b = 888800111b = 1BPP01000b = 2BPP 01001b = 4BPP01010b = 8BPP 01011b = S3TC01100b = YUV422 , Y1VY0U ordering01101b = YUV422 , VY1UY0 ordering01110b = YUV422 , Y1UY0V ordering01111b = YUV422 , UY1VY0 ordering10000b~11111b = reserved00000bUADDR _MODE [11:10] Mode used in U address00b = Repeat 01b = Flip10b = Clamp to edge 11b = reserved*Note: In non-parametric coordinate system, UADDR_MODE areset to clamp to edge.00bVADDR _MODE [9:8] Mode used in V address00b = Repeat 01b = Flip10b = Clamp to edge 11b = reserved*Note: In non-parametric coordinate system, VADDR_MODE areset to clamp to edge00bPADDR _MODE [7:6] Mode used in P address00b = Repeat 01b = Flip10b = Clamp to edge 11b = reserved*Note: In non-parametric coordinate system, PADDR_MODE areset to clamp to edge00breserved[5]reserved0b TEX_COOR [4] Texture Addressing Coordinate System0b = Parametric1b = Non-parametric0bMAG_FILTER [3] Bilinear Filter Control (Magnification)0b = Don’t filter between pixels in a map1b = Bilinear filter between pixels in a map0bTEX_FLT_EN [2] Bilinear filter Control (Minification)0b = Don’t filter between pixels in a map1b = Bilinear filter between pixels in a map0b MIPMAP_EN [1:0] MIPMAPControl00b = Don’t use MIPAMP01b = MIPMAP use, select nearest map10b = MIPMAP use, and linear interpolation between maps.11b = reserved00bGRAPHIC 3D 6410X_UM42.11.2.2 TEXTURE U SIZE REGISTER 0 ~ 7Register Address R/W Description Reset Value FGTU_USIZE0 0x72060004 R/W Texture 0’s U Size 0x00000000 FGTU_USIZE1 0x72060054 R/W Texture 1’s U Size 0x00000000 FGTU_USIZE2 0x720600A4 R/W Texture 2’s U Size 0x00000000 FGTU_USIZE3 0x720600F4 R/W Texture 3’s U Size 0x00000000 FGTU_USIZE4 0x72060144 R/W Texture 4’s U Size 0x00000000 FGTU_USIZE5 0x72060194 R/W Texture 5’s U Size 0x00000000 FGTU_USIZE6 0x720601E4 R/W Texture 6’s U Size 0x00000000 FGTU_USIZE7 0x72060234 R/W Texture 7’s U Size 0x00000000FGTU_USIZEn Bit Description Initial Statereserved 0 reserved [31:11]U_SIZE [10:0] U Size of Level 0 Texture 0x042.11.2.3 TEXTURE V SIZE REGISTER 0 ~ 7Register Address R/W Description Reset Value FGTU_VSIZE0 0x72060008 R/W Texture 0’s V Size 0x00000000 FGTU_VSIZE1 0x72060058 R/W Texture 1’s V Size 0x00000000 FGTU_VSIZE2 0x720600A8 R/W Texture 2’s V Size 0x00000000 FGTU_VSIZE3 0x720600F8 R/W Texture 3’s V Size 0x00000000 FGTU_VSIZE4 0x72060148 R/W Texture 4’s V Size 0x00000000 FGTU_VSIZE5 0x72060198 R/W Texture 5’s V Size 0x00000000 FGTU_VSIZE6 0x720601E8 R/W Texture 6’s V Size 0x00000000 FGTU_VSIZE7 0x72060238 R/W Texture 7’s V Size 0x00000000 FGTU_VSIZEn Bit Description Initial State reserved [31:11]reserved 0 V_SIZE [10:0] V Size of Level 0 Texture 0x06410X_UM GRAPHIC3D42.11.2.4 TEXTURE P SIZE REGISTER 0 ~ 7Register Address R/W Description Reset Value FGTU_PSIZE0 0x7206000C R/W Texture 0’s P Size 0x00000000 FGTU_PSIZE1 0x7206005C R/W Texture 1’s P Size 0x00000000 FGTU_PSIZE2 0x720600AC R/W Texture 2’s P Size 0x00000000 FGTU_PSIZE3 0x720600FC R/W Texture 3’s P Size 0x00000000 FGTU_PSIZE4 0x7206014C R/W Texture 4’s P Size 0x00000000 FGTU_PSIZE5 0x7206019C R/W Texture 5’s P Size 0x00000000 FGTU_PSIZE6 0x720601EC R/W Texture 6’s P Size 0x00000000 FGTU_PSIZE7 0x7206023C R/W Texture 7’s P Size 0x00000000FGTU_PSIZEn Bit Description Initial State reserved [31:11]reserved 0 P_SIZE [10:0] P Size of Level 0 Texture (the Depth of 3D Textures) 0x042.11.2.5 TEXTURE L1 OFFSET REGISTER 0 ~ 7Register Address R/W Description Reset Value FGTU_TOFFS_L1_0 0x72060010 R/W Texture 0’s Level 1 Texture Offset 0x00000000 FGTU_TOFFS_L1_1 0x72060060 R/W Texture 1’s Level 1 Texture Offset 0x00000000 FGTU_TOFFS_L1_2 0x720600B0 R/W Texture 2’s Level 1 Texture Offset 0x00000000 FGTU_TOFFS_L1_3 0x72060100 R/W Texture 3’s Level 1 Texture Offset 0x00000000 FGTU_TOFFS_L1_4 0x72060150 R/W Texture 4’s Level 1 Texture Offset 0x00000000 FGTU_TOFFS_L1_5 0x720601A0 R/W Texture 5’s Level 1 Texture Offset 0x00000000 FGTU_TOFFS_L1_6 0x720601F0 R/W Texture 6’s Level 1 Texture Offset 0x00000000 FGTU_TOFFS_L1_7 0x72060240 R/W Texture 7’s Level 1 Texture Offset 0x00000000FGTU_TOFFS_L1n Bit Description Initial State reserved[31:23]reserved0 OFFSET [22:0] Level 1 Texture Offset 0x0。

S3C6410的SPI控制器

S3C6410的SPI控制器1.SPI控制器1.1概述SPI总线是一种全双工串行同步通讯协议,SPI(Serial Peripheral Interface)串行外围接口能够支持串行数据传输,其包含两个独立的8/16/32位移位寄存器分别用于发送和接收。

在SPI传输期间,数据同步发送(串行移出)和接收在(串行移入)。

1.2SPI控制器支持下面的特征1)全双工,表示可以同时发送和接收。

2)用于发送和接收的8/16/32位移位寄存器。

3)8位预分频逻辑,由时钟配置寄存器的低八位决定。

4)3个时钟源,包括PCLK、USBCLK和Epll clock。

5)支持National Semiconductor Microwire的协议和Motorola的串行外设接口。

6)两个独立的发送和接收FIFO,each 16 samples deep by 32-bits wide。

7)支持主模式和从模式。

8)支持只接收没发送的操作。

9)发送/接收的最大频率为50MHZ,但在CPHA=1,且从发送模式时,最大频率为20MHz。

1.3信号描述S3C6410的SPI控制器和SPI接口的外部设备之间的外部信号有4个接口,这几个接口在SPI 禁用的时候可以用作通用的GPIO口。

XspiCLK:串行时钟信号,用于控制传输数据的时间,可作为输入和输出。

XspiMISO:在主模式下,主设备通过此引脚获取从设备的输出引脚输出的数据,此时作为输入;在从模式下,主设备通过此引脚输出数据到从设备,此时作为输出。

XspiMOSI:在主模式下,主设备通过此引脚输出数据给从设备,此时作为输出;在从模式下,主设备通过此引脚接收来之从设备输出的数据,此时作为输入。

XspiCS:从选择信号,当此引脚为低电平的时候,所有的数据发送/接收顺序被执行。

1.4SPI的操作S3C6410的SPI接口在S3C6410和外设之间传输一位串行数据,S3C6410的SPI支持CPU或DMA分别发送或接收FIFO,并且支持同时双向传输数据。

S3C6410各引脚的功能引脚号查询

S3C6410各引脚的功能引脚引脚名称特殊功能引脚功能说明A2NC_CA3 XpcmSOUT0/GPD4 在O状态下,PCM串行数据输出串行通信PCM(2通道)A4 VDDPCM LCD(液晶显示器)的IO VDD,电压2.5~3.3电源组A5 XM1DQM0 在O状态下,存储器端口1DRAM数据屏蔽(DRAM动态随机存储器,常见的是系统内存;数据只能存储很短时间)外部存储接口S3C6410 共享存储器端口( DRAM1)具体信号A6 XM1DATA1 在IO状态下,存储器端口1DRAM低于半数据总线A7VDD1电源组A8 VDDARM ARM1176核和缓存的内部VDD,该点电压未定(TBD)(To Be Decided)电源组A9 XM1DATA6 在IO状态下,存储器端口1DRAM低于半数据总线外部存储接口S3C6410 共享存储器端口( DRAM1)具体信号A10 XM1DATA9A11 XM1DATA12A12 XM1DATA18A13 XM1SCLK 在O状态下,1DRAM时钟A14 XM1SCLKN 在O状态下,存储器端口1DRAM反转时钟的Xm1SCLKA15 XmmcDATA1_4/GHP6 在IO状态下,数据(SD/SDIO/MMC卡接口通道1)MMC 2通道A16 XmmcCMD1/GPG6 在IO状态下,命令/响应(SD/SDIO/MMC 卡接口通道1)A17 CmmcCDN0/GPG0 在I状态下,卡删除(SD/SDIO/MMC 卡接口通道0)A18 CmmcCLK0/GPG0 在O状态下,时钟(SD/SDIO/MMC卡接口通道0)A19 XspiMOSI0/GPC2 在IO状态下,SPI主设备输出线路串行通信SPI(2通道)A20 Xi2cSCL/GPC8 在IO状态下,IIC总线时钟串行通信(IIC总线具体信号)A21 XuTXD2/GPB1 在O状态下,UART 2传输数据输出串行通信(UART具体信号)A22 XuRTSN0/GPA3 在O状态下,UART 0请求发送数据信号A23 XuTXD0/GPA1在O状态下,UART 0传输数据输出A24NC_DB1 NC_BB2 XpcmSIN1/ GPE3 在I 状态下,PCB 串行数据输入 串行通信 PCM (2通道)B3 XpcmEXTCLK 1/GPE1 在I 状态下,可选参考时钟 B4 XpcmSIN0/ GPD3 在I 状态下,PCB 串行数据输入 B5 XpcmEXTCLK 0/GPD1 在I 状态下,可选参考时钟B6 XM1DATA0 在IO 状态下,存储器端口1DRAM 低于半数据总线外部存储器接口 (S3C6410共享存储器端口) B7 XM1DATA3 B8 VDDM1 存储端口1的IO VDD;电压1.8~2.5电源组 B9 VDDM1 B10XM1DATA13在IO 状态下,存储器端口1DRAM 低于半数据总线外部存储器接口 (S3C6410共享存储器端口) B11 VDDARM ARM1176核和缓存的内部VDD,该点电压未定电源组B12 XM1DATA16 在IO 状态下,可作为存储器端口1DRAM 高于半数据总线使用,通过系统控制器设置外部存储接口 S3C6410 共享存储器端口( DRAM1)具体信号B13 XM1DATA17 B14 XM1DQS2 在IO 状态下,存储器端口1DRAM 数据选通 B15XM1DATA22在IO 状态下,可作为存储器端口1DRAM 高于半数据总线使用,通过系统控制器设置B16 XmmcDATA1_2/GHP4 在IO 状态下,数据(SD/SDIO/MMC 卡接口通道1)MMC 2通道 B17 VDDMMC USB .OTG .PHY 的内部VDD;电压2.5~3.3电源组 B18 XmmcDATA0_0/GHP2 在IO 状态下,数据(SD/SDIO/MMC 卡接口通道0)MMC 2通道B19 XspiMISO1/G PC4 在IO 状态下,SPI 主设备输入线路串行通信 SPI(2通道) B20 XspiMISO0/G PC0 B21 XuTXD3/ GPB3 在O 状态下,UART 3传输数据输出 串行通信(UART 具体信号) B22 XuTXD1/ GPA5 在O 状态下,UART 1传输数据输出 串行通信(UART 具体信号) B23XciYDATA7/ GPF12在I 状态下,在8位模式下,像素数据为YCbCr ;或在16位模式下为Y ;通过图像/视频处理 (相机接口具体信)B24 XciYDATA5/GPF10相机处理器A驱动B25NC_FC1 XM0ADDR0 在O状态下,存储器端口1DRAM地址总线外部存储接口S3C6410 共享存储器端口( DRAM0)具体信号C2 VDDARM ARM1176核和缓存的内部VDD,该点电压未定(TBD)电源组C3 XpcmSOUT1/GPE4在O状态下,PCM串行数据输出串行通信PCM(2通道)C4 XpcmFSYNC1/GPE2在O状态下,PCM同步指示字的开始C5 XpcmEXTCLK1/GPE0在I状态下,可选参考时钟C6 XM1DATA4 在IO状态下,存储器端口1DRAM低于半数据总线外部存储接口S3C6410 共享存储器端口(DRAM1)具体信号C7 XM1DATA2C8 XM1DATA5C9 XM1DATA7C10 VDDARM ARM1176核和缓存的内部VDD,该点电压未定(TBD)电源组C11 XM1DATA14 在IO状态下,存储器端口1DRAM低于半数据总线外部存储接口S3C6410 共享存储器端口( DRAM1)具体信号C12 XM1DATA10C13 XM1DATA19C14 VDDM1 存储端口1的IO VDD;电压1.8~2.5 电源组C15 XM1DATA20 在IO状态下,存储器端口1DRAM低于半数据总线外部存储接口S3C6410 共享存储器端口(DRAM1)具体信号C16 XmmcDATA1_6/GHP8 在IO状态下,数据(SD/SDIO/MMC卡接口通道1)存储设备MMC 2通道C17 XmmcDATA1_1/GHP3C18 XmmcDATA0_2/GHP4 在IO状态下,数据(SD/SDIO/MMC卡接口通道0)C19 XspiMOSI1/GPC6 在IO状态下,SPI主设备输出线路串行通信SPI(2通道)C20 XspiCS0/GPC3 在IO状态下,SPI片选(只对于从模式)C21 VDDEXT PCM的IO VDD音频(I/F-I^2S,AC97);电压3.3电源组C22 XuRTSN1/GPA7 在O状态下,UART 1请求发送数据信号串行通信(UART具体信号)C23 XpwmECLK/GPF13 在I状态下,PWM定时器外部时钟调制解调器接口(PWM 具体信号)C24 XciYDATA2/GPF7 在I状态下,在8位模式下,像素数据为YCbCr;或在16位模式下为Y;通过相机处理器A驱动图像/视频处理(相机接口具体信)C25 XciYDATA0/GPF5D1 XM0ADDR2 在O状态下,存储器端口0DRAM地址总线外部存储接口S3C6410 共享存储器端口(DRAM0)具体信号D2 XM0ADDR3D3 VDDARM ARM1176核和缓存的内部VDD,该点电压未定(TBD)(To Be Decided)电源组D6 XpcmFSYNC0/GPD2 在O状态下,PCM同步指示字的开始串行通信PCM(2通道)D7 XpcmEXTCLK0/GPD1在I状态下,可选参考时钟D8 VDDARM ARM1176核和缓存的内部VDD,该点电压未定(TBD)(To Be Decided)电源组D9 XM1DQS0 在IO状态下,存储器端口1DRAM数据选通在IO状态下,存储器端口1DRAM数据选通D10 XM1DATA15 在IO状态下,存储器端口1DRAM低于半数据总线外部存储接口S3C6410 共享存储器端口( DRAM1)具体信号D11 XM1DATA11D12 XM1DATA8D13 VDDI 电源组D14 XM1DQM2 在O状态下,存储器端口1DRAM数据屏蔽(DRAM动态随机存储器,常见的是系统内存;数据只能存储很短时间)外部存储接口S3C6410 共享存储器端口( DRAM1)具体信号D15 XM1DATA21 在IO状态下,可作为存储器端口1DRAM高于半数据总线使用,通过系统控制器设置D16 XM1DATA23D17 XspiCS1/GPC7 在IO状态下,SPI片选(只对于从模式)串行通信SPI(2通道)D18 VDDI电源组D19 XuRXD2/GPB0 在I状态下,UART 2接受数据输入串行通信(UART具体信号)D20 XuRXD0/GPA0在I状态下,UART 0接受数据输入D23 XpwmTOUT1/GPF15 在O状态下,PWM定时器输出调制解调器接口(PWM 具体信号)D24 XciVSYNC/GPF4 在I状态下,垂直同步,通过相机处理器A驱动图像/视频处理(相机接口具体信)D25 XciHREF/GPF1 在I状态下,水平同步,通过相机处理器A驱动E1 XM0ADDR5 在O状态下,存储器端口0DRAM地址总线外部存储接口S3C6410 共享存储器端口( DRAM0)具体信号E2 VDDARM ARM1176核和缓存的内部VDD,该点电压未定(TBD)(To Be Decided)电源组E3 XM0ADDR3 在O状态下,存储器端口0DRAM地址总线外部存储接口S3C6410 共享存储器端口( DRAM0)具体信号E23 XciYDATA1/GPF6 在I状态下,在8位模式下,像素数据为YCbCr;或在16位模式下为Y;通过相机处理器A驱动图像/视频处理(相机接口具体信)E24 XM1DATA28 在IO状态下,可作为存储器端口1DRAM高于半数据总线使用,通过系统控制器设置外部存储接口S3C6410 共享存储器端口( DRAM1)具体信号E25 XM1DQS3 在IO状态下,存储器端口1DRAM数据选通F1 XM0ADDR8/GPO8 在O状态下,存储器端口0DRAM地址总线外部存储接口S3C6410 共享存储器端口( DRAM0)具体信号F2 XM0ADDR6/GPO6F3 VDDARM ARM1176核和缓存的内部VDD,该点电压未定(TBD)(To Be Decided)电源组F4 VDDM0 存储端口0的IO VDD;电压1.8~2.5F22 XciPCLK/GPF2 在I状态下,像素时钟,通过相机处理器A驱动图像/视频处理(相机接口具体信)F23 XM1DATA24 在IO状态下,可作为存储器端口1DRAM高于半数据总线使用,通过系统控制器设置外部存储接口S3C6410 共享存储器端口( DRAM1)具体信号F24 XM1DATA25 F25 XM1DATA26G1 XM0ADDR10/GPO10 在O状态下,存储器端口0DRAM地址总线外部存储接口S3C6410 共享存储器端口( DRAM0)具体信号G2 XM0ADDR11/GPO11G3 VDDM0 存储端口0的IO VDD;电压1.8~2.5 电源组G4 XM0ADDR7/GPO7 在O状态下,存储器端口0DRAM地址总线外部存储接口S3C6410 共享存储器端口( DRAM1)具体信号G8 XM1DQM1 在O状态下,存储器端口1DRAM数据屏蔽G9 XM1DQS1 在IO状态下,存储器端口1DRAM数据选通G10 VDDM1 存储端口1的IO VDD;电压1.8~2.5 电源组G11 XmmcDATA1_在IO状态下,数据(SD/SDIO/MMC卡存储设备5/GHP7 接口通道1)MMC 2通道G12 XmmcDATA0_3/GHP5 在IO状态下,数据(SD/SDIO/MMC卡接口通道0)G13 XmmcCMD0/GPG1 在IO状态下,命令/响应(SD/SDIO/MMC 卡接口通道1)G14 Xi2cSDA 在IO状态下,IIC总线数据串行通信(IIC总线具体信号)G15 XIRSDBW/GPB4 在O状态下,IrDA收发控制信号(关机和带宽控制)串行通信(IrDA具体信号)G16 XuCTSN0/GPA2 在I状态下,UART 0清除发送数据信号串行通信(UART具体信号)G17 XciYDATA6/GPF11 在I状态下,在8位模式下,像素数据为YCbCr;或在16位模式下为Y;通过相机处理器A驱动图像/视频处理(相机接口具体信)G18 XciYDATA3/GPF8G22 XciCLK/GPF0 在O状态下,主时钟相机处理器AG23 XM1DATA29 在IO状态下,可作为存储器端口1DRAM高于半数据总线使用,通过系统p控制器设置外部存储器接口(S3C6410共享存储器端口)G24 XM1DATA27 G25 XM1DATA30H1 VDDIH2 XM0ADDR13/GPO13 在O状态下,存储器端口0DRAM地址总线外部存储接口S3C6410 共享存储器端口( DRAM0)具体信号H3 XM0ADDR15/GPO15H4 XM0ADDR12/GPO12H7 XM0ADDR4H8 VSSIP G;内部逻辑接地&ARM1176核和缓存电源组H9 XmmcDATA1_7/GHP9 在IO状态下,数据(SD/SDIO/MMC卡接口通道1)存储设备MMC 2通道H10 XmmcDATA1_3/GHP5H11 XmmcDATA1_0/GHP2H12 XspiCLK1/GPC5 在IO状态下,SPI时钟作为通道1 串行通信SPI(2通道)H13 XmmcDATA0_1/GHP3 在IO状态下,数据(SD/SDIO/MMC卡接口通道0)存储设备MMC 2通道H14 XspiCLK0/GPC1 在IO状态下,SPI时钟作为通道0串行通信SPI(2通道)H15 XuCTSN1/GPA6 在I状态下,UART 1清除发送数据信号串行通信(UART具体信号)H16 XpwmTOUT0/GPF14 在O 状态下,PWM 定时器输出调制解调器接口 (PWM 具体信号)H17XciYDATA4/ GPF9 在I 状态下,在8位模式下,像素数据为YCbCr ;或在16位模式下为Y ;通过相机处理器A 驱动图像/视频处理 (相机接口具体信) H18 VSSPERI P;USB 主设备,SDMMC,主设备I/F,LCD,PCM,外部I/F 和系统控制器 电源组H19 XciRSTN/GPF 3在O 状态下,软件复位到相机处理器A 驱动图像/视频处理 (相机接口具体信) H22 XM1DQM3 在O 状态下,存储器端口1DRAM 数据屏蔽 外部存储接口 S3C6410 共享存储器端口(DRAM1)具体信号H23XM1DATA31在IO 状态下,可作为存储器端口1DRAM 高于半数据总线使用,通过系统p 控制器设置H24 XM1ADDR0 在O 状态下,存储器端口1DRAM 地址总线H25 XM1ADDR3 J1 XM0AP/GPQ8 存储器端口0DRAM 自动预充电 外部存储接口 S3C6410 共享存储器端口( DRAM0)具体信号 J2 XM0WEN 在O 状态下,存储器端口1DRAM 写入有效J3 VDDARM ARM1176核和缓存的内部VDD,该点电压未定(TBD )电源组J4XM0ADDR14/GPO14 在O 状态下,存储器端口0DRAM 地址总线外部存储接口 S3C6410 共享存储器端口( DRAM0)具体信号 J7 VSSMEM 存储器端口0和1的IO 接地电源组J8XM0ADDR9/GPO9 在O 状态下,存储器端口0DRAM 地址总线外部存储接口 S3C6410 共享存储器端口(DRAM0)具体信号J11 CmmcCLK1/G PG0 在O 状态下,时钟(SD/SDIO/MMC 卡接口通道1)存储设备 MMC 2通道 J12 VSSIP G ;内部逻辑接地&ARM1176核和缓存 电源组J13 VSSPERI P;USB 主设备,SDMMC,主设备I/F,LCD,PCM,外部I/F 和系统控制器 J14 XuRXD3/ GPB2 在I 状态下,UART 3接受数据输入 串行通信(UART 具体信号) J15 XuRXD1/ GPA4 在I 状态下,UART 1接受数据输入 J18 VDDI电源组J19 VDDM1 存储端口1的IO VDD;电压1.8~2.5 J22 XM1ADDR9 在O 状态下,存储器端口1DRAM 地址总线外部存储接口 S3C6410 共享存储器端口(DRAM1)具体信号 J23 XM1ADDR2 J24XM1ADDR1J25 XM1ADDR6K1 XM0DATA15 在IO状态下,存储器端口0DRAM低于半数据总线外部存储接口S3C6410 共享存储器端口( DRAM0)具体信号K2 VDDM0 存储端口0的IO VDD;电压1.8~2.5 电源组K3 VDDARM ARM1176核和缓存的内部VDD,该点电压未定(TBD)电源组K4 XM0DATA14 在IO状态下,存储器端口0DRAM低于半数据总线外部存储接口S3C6410 共享存储器端口(DRAM0)具体信号K7 XM0DQM1在O状态下,存储器端口1DRAM数据屏蔽K8 VSSIP G;内部逻辑接地&ARM1176核和缓存电源组K18 XM1ADDR7 在O状态下,存储器端口1DRAM地址总线外部存储接口S3C6410 共享存储器端口( DRAM1)具体信号K19 XM1ADDR11 K22 XM1ADDR13 K23 XM1ADDR8 K24 XM1ADDR12 K25 XM1ADDR5L1 XM0DQM0在O状态下,存储器端口0DRAM数据屏蔽外部存储接口S3C6410 共享存储器端口( DRAM0)具体信号L2 XM0DATA13 在IO状态下,存储器端口0DRAM低于半数据总线L3 XM0SMCLK/GPp1 在O状态下,存储器端口DRAM0时钟外部存储接口S3C6410 共享存储器端口(DRAM0)具体信号L4 XM0OEN 存储器端口0 CF 输出有效选通外部存储接口S3C6410 共享存储器端口(CF)具体信号L7 XM0DATA10 在IO状态下,存储器端口0共同数据线外部存储接口S3C6410 共享存储器端口(DRAM0)具体信号L8 XM0DATA12 外部存储接口S3C6410 共享存储器端口(DRAM0)具体信号L9 VSSIP G;内部逻辑接地&ARM1176核和缓存电源组L17 VDDIL18 XM1CSN1 在O状态下,存储器端口1DRAM片选支持高达2个存储页外部存储接口S3C6410 共享存储器端口( DRAM1)具体信号L19 XM1ADDR4 在O状态下,存储器端口1DRAM地址总线外部存储接口S3C6410 共享存储器端L22 XM1RASN 在O 状态下,存储器端口1DRAM 行地址选通口( DRAM1)具体信号L23 XM1CSN0 在O 状态下,存储器端口1DRAM 片选支持高达2个存储页L24 XM1CASN 在O 状态下,存储器端口1DRAM 列地址选通L25 XM1ADDR15在O 状态下,存储器端口1DRAM 地址总线M1 VDDM0 存储端口0的IO VDD ;电压1.8~2.5 电源组M2 XM0DATA8 在IO 状态下,存储器端口0共同数据线外部存储接口 S3C6410 共享存储器端口( DRAM0)具体信号M3 XM0DATA11 M4 XM0DATA9 M7 XM0DATA2 M8 XM0DATA4 M9 VSSMEM 存储器端口0和1的IO 接地电源组M17 XM1ADDR14 在O 状态下,存储器端口1DRAM 地址总线外部存储接口 S3C6410 共享存储器端口( DRAM1)具体信号M18 XM1CKE0 在O 状态下,存储器端口1DRAM 时钟有效M19 XM1WEN 在O 状态下,存储器端口1DRAM M22 VDDIM23 XM1ADDR10 在O 状态下,存储器端口1DRAM 地址总线外部存储接口 S3C6410 共享存储器端口( DRAM1)具体信号M24 XM1CKE1 在O 状态下,存储器端口1DRAM 时钟有效M25XhiDATA17/GPL14在IO 状态下,数据总线,通过调制解压器芯片驱动 调制解调器接口 主设备I/F/HIS (MIPI )/Key I/F/ATA 具体信号 N1 XM0DATA1 在IO 状态下,存储器端口0共同数据线外部存储接口S3C6410 共享存储器端口(DRAM0)具体信号N2 XM0DATA0 N3 XM0DATA3 N4 XM0DATA6 N7 XM0CSN0 在O 状态下,存储器端口0SROM 片选支持高达两个存储页N8 XM0CSN5/ GPO3 在O 状态下,存储器端口0SROM/CF 片选支持高达两个存储页N9 VSSIP G ;内部逻辑接地&ARM1176核和缓存 电源组N17 XhiDATA16/G PL13 在IO 状态下,数据总线,通过调制解压器芯片驱动 调制解调器接口 主设备I/F/HIS (MIPI )/Key I/F/ATA 具体信号N18XhiDATA14/G PK14N19 VDDUHN22 XuHDP 在IO状态下,USB 数据引脚DATA(+)用作USB1.1 主设备调制解调器接口USB主设备具体信号N23 XhiDATA15/GPK15 在IO状态下,数据总线,通过调制解压器芯片驱动调制解调器接口主设备I/F/HIS(MIPI)/Key I/F/ATA 具体信号N24 XhiDATA13/GPK13N25 XhiDATA12/GPK12P1 VDDIP2 XM0DATA5 在IO状态下,存储器端口0共同数据线外部存储接口S3C6410 共享存储器端口(DRAM0)具体信号P3 XM0DATA7P4 XM0CSN2/GPO0 在O状态下,存储器端口0SROM/OneNAND/NAND Flash 片选支持高达两个存储页外部存储接口S3C6410 共享存储器端口(SROMC/OneNAND/NAND/DRAM0)具体信号P7 XM0CSN7/GPO5 在O状态下,存储器端口0DRAM 片选支持高达两个存储页P8 XM0CASN/GPQ1 在O状态下,存储器端口0DRAM列地址选通外部存储接口S3C6410 共享存储器端口(DRAM0)具体信号P9 VSSMEM 存储器端口0和1的IO接地电源组P17 VSSIP G;内部逻辑接地&ARM1176核和缓存P18 XhiDATA11/GPK11 在IO状态下,数据总线,通过调制解压器芯片驱动调制解调器接口主设备I/F/HIS(MIPI)/Key I/F/ATA 具体信号P19 XhiDATA9/GPK9P22 XUHDN 在IO状态下,USB 数据引脚DATA(-)用作USB1.1 主设备调制解调器接口USB主设备具体信号P23 XhiDATA10/GPK10 在IO状态下,数据总线,通过调制解压器芯片驱动调制解调器接口主设备I/F/HIS(MIPI)/Key I/F/ATA 具体信号P24 VDDHI SDMM(读卡器)的输入输出电压;电压2.5~3.3电源组P25 XhiDATA8/GPK8 在IO状态下,数据总线,通过调制解压器芯片驱动调制解调器接口主设备I/F/HIS(MIPI)/Key I/F/ATA 具体信号R1 VDDM0 存储端口0的IO VDD;电压1.8~2.5 电源组R2 XM0CSN3/GPO1 在O状态下,存储器端口0SROM/OneNAND/NAND Flash 片选支持高达两个存储页外部存储接口S3C6410 共享存储器端口(SROMC/OneNAND/NAND/R3 XM0CSN1DRAM0)具体信号R4 XM0W AITN/GPP2 在I状态下,存储器端口0SROM 等待外部存储接口S3C6410 共享存储器端口(SROMC)具体信号R7 XM0INTA TA/GPP8 在I状态下,存储器端口0 CF 从ATAPI控制器中断请求外部存储接口S3C6410 共享存储器端口(ATA)具体信号R8 XM0RDY0_ALE/GPP3 在I状态下,存储器端口0OneNAND 组件0 准备//在O状态下,存储器端口0 NAND Flash 地址锁存有效R9 VSSIP G;内部逻辑接地&ARM1176核和缓存电源组R17 VSSPERI P;USB主设备,SDMMC,主设备I/F,LCD,PCM,外部I/F和系统控制器R18 VDDALIVE 带点组件的内部ADD;电压1.0R19 XhiADR12/GPL12 在IO状态下,数据总线,通过调制解压器芯片驱动调制解调器接口主设备I/F/HIS(MIPI)/Key I/F/ATA 具体信号R22 XhiDATA5/GPK5R23 XhiDATA4/GPK4R24 XhiDATA6/GPK6R25 XhiDATA7/GPK7T1 XM0SCLK/GPQ2 在O状态下,0DRAM时钟外部存储接口S3C6410 共享存储器端口(DRAM0)具体信号T2 XM0CSN6/GPO4 在O状态下,存储器端口0DRAM 片选支持高达两个存储页T3 XM0CSN4/GPO2 在O状态下,存储器端口0SROM/CF 片选支持高达两个存储页外部存储接口S3C6410 共享存储器端口(SROMC/OneNAND/NAND/DRAM0)具体信号T4 XM0DQS0/GPQ5 在O状态下,存储器端口0SROM 片选支持高达两个存储页T7 XEFFVDDT8 VSSMPLL MPLL核接地电源组T18 XhiADR7/GPL7 在I状态下,地址总线,通过调制解压器芯片驱动.调制解调器接口主设备I/F/HIS(MIPI)/Key I/F/ATA 具体信号T19 XhiADR9/GPL9T22 XhiDATA1/GPK1 在IO状态下,数据总线,通过调制解压器芯片驱动调制解调器接口主设备I/F/HIS(MIPI)/Key I/F/ATA 具体信号T23 XhiDATA2/GPK2T24 XhiDATA3/GPK3T25 XhiDATA7/GPK7U1 XM0SCLKN/GPQ3 在O状态下,存储器端口0DRAM反转时钟的Xm0SCLK外部存储接口S3C6410 共享存储器端口(DRAM0)具体信号U2 XM0RASN/GPQ0 在O状态下,存储器端口0DRAM行地址选通U3 XM0WEN DMC/GPQ7 在O状态下,存储器端口0 CF写入有效选通U4 XM0INTSM1_FREN/GPP6U7 XM0CDATA/GPP14 在I状态下,存储器端口0 CF 卡检测外部存储接口S3C6410 共享存储器端口(ATA)具体信号U8 VSSMEM 存储器端口0和1的IO接地电源组U11 VSSPERI P;USB主设备,SDMMC,主设备I/F,LCD,PCM,外部I/F和系统控制器U12 VSSPERIU13 VSSIP G;内部逻辑接地&ARM1176核和缓存U14 VSSPERI P;USB主设备,SDMMC,主设备I/F,LCD,PCM,外部I/F和系统控制器U15 VDDALIVE 带点组件的内部ADD;电压1.0U18 XhiADR2/GPL2 在I状态下,地址总线,通过调制解压器芯片驱动调制解调器接口主设备I/F/HIS(MIPI)/Key I/F/ATA 具体信号U19 XhiADR0/GPLU22 XhiADR4/GPL4U23 XhiADR11/GPL11U24 XhiADR10/GPL10U25 XhiADR8/GPL8V1 VDDM0 存储端口0的IO VDD;电压1.8~2.5 电源组V2 XM0DQS1/GPQ6 在IO状态下,存储器端口0DRAM数据选通外部存储接口S3C6410 共享存储器端口(DRAM0)具体信号V3 XM0CKE/GPQ4 在O状态下,存储器端口0DRAM时钟有效V4 XM0WEATA/GPP12 在O状态下,存储器端口0 CF 写入有效选通外部存储接口S3C6410 共享存储器端口(ATA )具体信号V7 VSEPLL EPLL 核接地电源组V8 XOM3 在I 状态下,操作模式选择系统管理器 MISC 具体信号 V9XnRESET在I 状态下,XnRESET 暂停任何操作在处理和取代S3C6410 到一个已知的复位状态。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第21卷第4期宁波大学学报(理工版)V ol.21 No.4 2008年12月JOURNAL OF NINGBO UNIVERSITY ( NSEE ) Dec. 2008文章编号:1001-5132(2008)04-0505-05基于CPLD数字电子技术实验平台的设计与实现文雯,李宏(宁波大学信息科学与工程学院,浙江宁波 315211)摘要:以ALTERA公司CPLD器件MAXII EPM1270为系统核心,构建了一种将数字电路实验和系统可编程实验集于一身的综合实验平台. 平台能提供4种不同电路结构的工作模式,既可以在可编程逻辑器件FPGA/CPLD上完成EDA实验,又提供给学生自由发挥的自助实验区;还配有DDS函数信号发生器、等精度频率计、逻辑笔、脉冲信号源等模块,可完成小至一般数电实验大至数字系统的设计. 实际使用效果表明:该实验平台较好地满足了数字电子类实验课程需要,在提高学生对课程理解和应用方面有着积极作用.关键词:数字电子技术;在系统可编程;CPLD;多模式配置中图分类号:TP302 文献标识码:A随着科学技术的发展,尤其是微电子技术和计算机技术取得的重大进展,数字逻辑器件已由中、小规模的集成电路发展到大规模和超大规模可编程逻辑器件(PLD). 现代数字电子技术的主要教学内容也逐步向中大规模、超大规模集成电路和可编程器件转移,教学中普遍增加硬件描述语言(HDL),设计方法也从传统的手工设计转向用EDA工具进行设计[1,2].教学内容的改革迫切要求有与之配合的实验设备,但目前市场上主流的实验设备依然停留在传统的小规模通用集成电路与连线相结合的方式,设计中只能采用手工方法,使用分立器件、小规模集成电路及其组成的各种功能电路来完成实验,无法满足现代电子技术教学和学生实践能力培养的需要[3]. 市场上也有纯粹的EDA技术实验箱,但只能完成可编程实验,且内部的连线已被固定,电路结构无法变化,导致用户无法根据自己需要来改变连线结构,只能完成一些固定实验项目,极大地限制了实验项目数量,难于适应多种需求的开发设计[4]. 这些都无疑极大地限制了学生的想象力、主观能动性和创新思维的发挥.本文所设计的综合实验平台将传统数字电路实验和系统可编程实验集于一身,具有多种工作模式,独创性地配制让学生自由发挥的自助实验区,还配有DDS函数信号发生器、等精度频率计、逻辑笔、脉冲信号源等模块,可完成小至一般数电实验大至数字系统的设计. 适应了当前数字电路从集成器件向在系统可编程器件发展的趋势,与同类实验平台相比,具有功能强大、面对对象广、实验内容新颖、实验设计灵活实用等特点,对提高学生收稿日期:2008-03-06. 宁波大学学报(理工版)网址:基金项目:宁波大学实验技术开发项目(syjs-2006005).第一作者:文雯(1983-),女,广西桂林人,在读硕士研究生,主要研究方向:可编程器件的应用. E-mail: wendy8632@506 宁波大学学报(理工版) 2008的动手能力,创新能力有很大的帮助. 1 总体设计方案实验平台设计上充分考虑实验教学需求. 为使实验平台既支持在系统可编程实验,又能完成数电实验,创新性地采用可编程实验区结合自助实验区结构方式,将可编程实验与传统实验紧密结合. 可编程实验区以可编程核心板为设计主体,可完成各类EDA 实验. 自助实验区设有各类IC 插座、电阻电容,还有8位与可编程实验区复用逻辑电平输入、输出端口,可完成中小规模IC 的相关实验,也可与可编程实验区互连完成综合设计性实验.为向用户提供更丰富的电路资源,完成尽可能多的实验项目,平台利用多模式技术“分时复用”系统资源,在不同模式下对用户呈现不同的电路结构. 为适用更多类型的可编程器件,方便设备维修管理,将实验主板和可编程核心板独立设计,并将下载电路设计在核心板上. 为减少额外仪器使用,平台上设计有DDS 函数信号发生器、等精度频率计、逻辑笔、脉冲信号源等模块[5].根据上述设计思想和功能要求,实验平台总体结构如图1所示,它以ALTERA 公司CPLD 器件MAXII EPM1270作为系统核心,配合可编程目标板接口电路、复位电路、时钟源电路、按键接口电路、LED 显示模块电路、数码管显示电路、A/D 和D/A 转换电路、DDS 函数信号产生电路、测频电路、逻辑电平测试电路以及脉冲信号源产生电路等其他电路资源.2 具体设计及实现技术根据上述设计方案,系统整体功能由CPLD 控制外围电路实现,根据用户模式设置,改变按键、LED 、数码管与可编程核心板、自助实验区等的连线方式,控制A/D 、D/A 转换电路,构成多模式系统. 同时,CPLD 与DDS 芯片和数字电位器通信实现函数信号器,以等精度测量方式实现频率计,配合逻辑电平比较电路实现逻辑笔. 2路32种频率的脉冲信号源也由CPLD 对时钟源分频得到. 2.1 系统的多模式技术多模式是实验平台关键技术,它是指实验平台从物理结构上看电路结构是固定的,但内部的信息流在主控制器MAXII EPM1270控制下,对用户呈现不同的电路结构,该功能由CPLD 内部3个用VHDL描述的模块实现,整个设计如图2所示.图2 多模式配置原理模式配置中心根据用户模式输入,在不同模式下,分别控制按键动作选择模块和显示控制模块执行不同动作,并控制AD 和DA 转换电路.按键动作选择模块将8位按键信号在不同模式下,配置为高低电平输入、200ms 单次脉冲输入、4位BCD 码输入以及4位二进制码输入等不同功能,输出至可编程核心目标板不同端口和自助实验区8位逻辑电平输入端口处.显示控制模块将可编程核心板的不同端口信图1 实验平台总体结构框图第4期 文 雯,等:基于CPLD 数字电子技术实验平台的设计与实现 507号和自助实验区8位逻辑电平输出信号按照不同译码方式显示在8位7段数码管和8位逻辑电平指示LED 上. 数据既可以将按BCD 译码、16进制译码、7段译码方式显示在数码管上,也可以按并行方式或串行移位方式显示在8位LED 上.根据实验需要,系统共设4种模式分别适用于组合电路、时序电路、模数混合系统、自助实验等4种类型实验,极大增加了系统扩展性,更大程度地利用资源,从而能完成更多的实验项目. 2.2 DDS 函数信号发生器设计[6]DDS 函数信号发生器以高精度可编程波形发生芯片AD9833和数字电位器X9C103为核心,CPLD 通过SPI 接口与它们通信,控制输出信号波形、幅度及频率,电路结构如图3所示.通过设置AD9833内部控制寄存器确定输出的信号类型(正弦、方波和三角波),设置28位的频率寄存器初值k 以决定输出信号频率,输出信号频率公式为:28out mclk /2f k f =×,其中,mclk f 为主频时钟,当为25MHz 时,频率分辨率可达0.1Hz.AD9833输出的信号经THS4052高速运放反相放大输出. 设置X9C103控制寄存器确定数字电位器的抽头位置,通过改变电阻值改变后级反相比例放大电路放大倍数,输出信号幅度为:0out /500x V V R =×,其中,out V 为AD9833输出,约为0.6V ,x R 为数字电位器的电阻,抽头数为100,可以实现50mv 的精度. 为保证信号无失真放大,系统采用了高速运放THS4052.输出波形、频率及幅值设定后,可先计算出对应的DDS 频率寄存器初值以及数字电位器的抽头位置值,随后为AD9833复位(控制寄存器的D8位(RESET)写1),之后则为写控制寄存器、频率寄存器,然后AD9833输出刷新(控制寄存器的D8位(RESET)写0),同步输出所有函数信号,最后根据幅度设置要求,将控制字写入X9C103,改变其电阻值,进而改变输出信号幅度. 总体软件控制流程如图4所示.图4 软件控制流程实验平台的函数信号发生器能提供三角波、方波和正弦波3种波形信号,频率调节范围为1Hz ~999KHz ,其输出频率稳定度优于10-4,频率分辨率为0.1Hz ,幅度调节的范围从0.5~5V ,且共分10档.图3 DDS 信号发生器电路结构508 宁波大学学报(理工版) 20082.3 逻辑笔的实现技术逻辑笔是数字电路常用的测试工具,实验平台利用CPLD 配合双路低功耗高速电压比较器MAX9107实现了1个TTL/CMOS 电平兼容,能指示高电平、中电平、低电平、高阻态,脉冲信号的逻辑笔电路结构图如图5所示.图5 逻辑笔结构图通过电阻分压得到高低电平阈值电压V th+,V th-作为MAX9107的参考电压,比较结果OUT A 、OUT B 输出至CPLD 判断处理,CPLD 输出Pulse 信号用于高阻态和中电平的区别. 逻辑电平的判断是在CPLD 内用状态机实现的,各状态转换如图7所示. 初始状态为S0,OUT A =0,OUT B =1时,进入S1状态,为低电平;OUT A =1,OUT B =0,进入S2状态,为高电平;其他值时进入S3状态,区别高阻和中电平;Pulse 首先输出高电平,若满足OUT A =1,OUT B =0,则Pulse 接着输出低电平,进入S4以进行下一步测试,若OUT A =0,OUT B =1,则进入S5,为高阻态;否则进入S6,为中电平.图6 逻辑电平测试状态转换图2.4 等精度频率计及脉冲信号源设计待测信号经过整形电路作为CPLD 的输入信号,在CPLD 上利用等精度频率测量原理[7],实现在1Hz ~999KHz 范围内全频段相对误差为0.1%,频率分辨率优于1Hz 的频率计. 等精度测频的方法由图7说明,当检测到被测信号fx 的上升沿后,闸门控制模块打开闸门,同时对被测信号fx 和基准频率信号fs 计数,计数完预定时间后,并不立即结束,直至被测信号的下一上升沿时计数才停止,这样保证了在任何频率条件下测量时间总是被测信号的整数倍周期,则被测信号频率为:(/)fx fs Ns Nx =×,其中,Ns Nx ,分别为实际闸门时间内基准频率和待测频率计数值,基准频率信号fs 由50MHz 晶振信号分频得到. 闸门关闭后将结果输出至除法器进行计算,计算结果转为BCD 码后在数码管显示.图7 等精度频率计结构图脉冲信号是数字电子技术中常用的信号之一,实验平台上由CPLD 对50MHz 和11.0952MHz 晶振信号分频得到了2组16档0.5Hz ~50MHz 不同频率脉冲信号,完全满足实验需求.3 总结本文介绍的数字电子技术实验平台既可完成传统数字电路实验,又支持在系统可编程实验,采用开放式结构、模块化设计、模式可配置技术,具有功能强大、对象广泛、实验内容新颖、实验设计灵活使用等特点. 目前,已在我校数字电路实验等课程中投入使用,实际使用效果表明,该实验平台性能稳定、可靠性高,较好地满足了实验教学要求,学生学习热情很高,取得了明显的教学效果,实现了“既支持设计为主实验,又兼容验证模式实验”的教学改革目标,对提高学生的设计和创新能力有第4期文雯,等:基于CPLD数字电子技术实验平台的设计与实现 509较大帮助. 该实验平台也适用于EDA技术实验、数字系统设计实验及电子设计竞赛培训等课程.参考文献:[1]刘银萍, 陈惠珊. “数字电子技术”实验教学改革的探讨[J]. 实验室研究与探索, 2006, 25(8):981-983.[2]Kamai S A. Digital circuit using FPGAS[J]. Computers &Industrial Engineering, 1996, 31(1/2):127-129.[3]沈鸿星. CPLD数字实验系统设计[J]. 中国教育技术设备, 2006(6):61-62.[4]雷雪梅, 李树华. EDA教学实验箱的设计[J]. 内蒙古大学学报, 2004, 35(3):344-347.[5]李宏, 文雯. 一种新型数字电路与系统实验平台: 中国, 200720105545.4[P]. 2007-12-03.[6]刘国良, 廖力清, 施进平. AD9833型高精度可编程波形发生器及其应用[J]. 国外电子元器件, 2006(6):44-47.[7]潘松, 黄继业. EDA技术实用教程[M]. 北京: 科学出版社, 2005.[8]蒋璇, 臧春华. 数字系统设计与PLD应用[M]. 北京:电子工业出版社, 2005.[9]曹华伟, 麦宋平, 徐鸿. 大规模可编程逻辑器件实验箱的研制[J]. 实验技术与管理, 2004, 21(2):27-29.Design and Implementation of Digital Electronic TechnologyExperiment Platform Based on CPLDWEN Wen, LI Hong( Faculty of Information Science and Technology, Ningbo University, Ningbo 315211, China )Abstract: An integrated platform is presented on which both digital circuit experiment and in-system programmable experiment can be carried out .The platform is constructed on the basis of the CPLD MAXII EPM127 of ALTERA and consists of 4 work modes. These modes are engineered not only for in-system programmable experiments but also for a variety of digital circuit designs. The platform developed is also equipped with several components such as DDS function signal generator, logical pen, and pulse signal generator. The performance test results indicate that the platform adequately satisfies the need of digital electronic technology experiments curricula, and is conducive to students for better comprehension and application of courses.Key words: digital electronic technology; in-system programmable; CPLD; multimode configurationCLC number: TP302 Document code: A(责任编辑 章践立)。