74F646BLMX中文资料

PSL-646U线路保护测控装置(多合一)技术说明书_V3.00_印刷

目录

版本声明 1. 概述 ............................................................................................................................................................ 1

国电南自 DL/T 1075-2007

PSL-646U 线路保护测控装置(多合一)

技术说明书

国电南京自动化股份有限公司 GUODIAN NANJING AUTOMATION CO.,LTD

PSL-646U 线路保护测控装置

技术说明书 (多合一)

V 3.00 国电南京自动化股份有限公司

2015 年 3 月

版本声明

z 本说明书适用于 PSL-646U 线路保护测控装置(多合一)。保护的设计标准引用了国网公司 Q/GDW 766 -2014《10kV~110(66)kV 线路保护及辅助装置标准化设计规范》。

z 本说明书适用于 PSL-646U 线路保护测控装置(多合一)V3.00 及以上版本的保护软件。

1.1. 保护功能配置 ...................................................................................................................................... 1 1.2. 测控功能配置 ..............................................

74系列芯片数据手册大全

74系列芯片数据手册大全74系列芯片数据手册大全74系列集成电路名称与功能常用74系列标准数字电路的中文名称资料7400 TTL四2输入端四与非门7401 TTL 集电极开路2输入端四与非门7402 TTL 2输入端四或非门7403 TTL 集电极开路2输入端四与非门7404 TTL 六反相器7405 TTL 集电极开路六反相器7406 TTL 集电极开路六反相高压驱动器7407 TTL 集电极开路六正相高压缓冲驱动器7408 TTL 2输入端四与门7409 TTL 集电极开路2输入端四与门7410 TTL 3输入端3与非门74107 TTL 带清除主从双J-K触发器74109 TTL 带预置清除正触发双J-K触发器7411 TTL 3输入端3与门74112 TTL 带预置清除负触发双J-K触发器7412 TTL 开路输出3输入端三与非门74121 TTL 单稳态多谐振荡器74122 TTL 可再触发单稳态多谐振荡器74123 TTL 双可再触发单稳态多谐振荡器74125 TTL 三态输出高有效四总线缓冲门74126 TTL 三态输出低有效四总线缓冲门7413 TTL 4输入端双与非施密特触发器74132 TTL 2输入端四与非施密特触发器74133 TTL 13输入端与非门74136 TTL 四异或门74138 TTL 3-8线译码器/复工器74139 TTL 双2-4线译码器/复工器7414 TTL 六反相施密特触发器74145 TTL BCD—十进制译码/驱动器7415 TTL 开路输出3输入端三与门74150 TTL 16选1数据选择/多路开关74151 TTL 8选1数据选择器74153 TTL 双4选1数据选择器74154 TTL 4线—16线译码器74155 TTL 图腾柱输出译码器/分配器74156 TTL 开路输出译码器/分配器74157 TTL 同相输出四2选1数据选择器74158 TTL 反相输出四2选1数据选择器7416 TTL 开路输出六反相缓冲/驱动器74160 TTL 可预置BCD异步清除计数器74161 TTL 可予制四位二进制异步清除计数器74162 TTL 可预置BCD同步清除计数器74163 TTL 可予制四位二进制同步清除计数器74164 TTL 八位串行入/并行输出移位寄存器74165 TTL 八位并行入/串行输出移位寄存器74166 TTL 八位并入/串出移位寄存器74169 TTL 二进制四位加/减同步计数器7417 TTL 开路输出六同相高压缓冲/驱动器74170 TTL 开路输出4×4寄存器堆74173 TTL 三态输出四位D型寄存器74174 TTL 带公共时钟和复位六D触发器74175 TTL 带公共时钟和复位四D触发器74180 TTL 9位奇数/偶数发生器/校验器74181 TTL 算术逻辑单元/函数发生器74185 TTL 二进制—BCD代码转换器74190 TTL BCD同步加/减计数器74191 TTL 二进制同步可逆计数器74192 TTL 可预置BCD双时钟可逆计数器74193 TTL 可预置四位二进制双时钟可逆计数器74194 TTL 四位双向通用移位寄存器74195 TTL 四位并行通道移位寄存器74196 TTL 十进制/二-十进制可预置计数锁存器74197 TTL 二进制可预置锁存器/计数器7420 TTL 4输入端双与非门7421 TTL 4输入端双与门7422 TTL 开路输出4输入端双与非门74221 TTL 双/单稳态多谐振荡器74240 TTL 八反相三态缓冲器/线驱动器74241 TTL 八同相三态缓冲器/线驱动器74243 TTL 四同相三态总线收发器74244 TTL 八同相三态缓冲器/线驱动器74245 TTL 八同相三态总线收发器74247 TTL BCD—7段15V输出译码/驱动器74248 TTL BCD—7段译码/升压输出驱动器74249 TTL BCD—7段译码/开路输出驱动器7425 双4输入端或非门(有选通端74251 TTL 三态输出8选1数据选择器/复工器74253 TTL 三态输出双4选1数据选择器/复工器74256 TTL 双四位可寻址锁存器74257 TTL 三态原码四2选1数据选择器/复工器74258 TTL 三态反码四2选1数据选择器/复工器74259 TTL 八位可寻址锁存器/3-8线译码器7426 TTL 2输入端高压接口四与非门缓冲器74260 TTL 5输入端双或非门74266 TTL 2输入端四异或非门7427 TTL 3输入端三或非门74273 TTL 带公共时钟复位八D触发器74279 TTL 四图腾柱输出S-R锁存器7428 TTL 2输入端四或非门缓冲器74283 TTL 4位二进制全加器74290 TTL 二/五分频十进制计数器74293 TTL 二/八分频四位二进制计数器74295 TTL 四位双向通用移位寄存器74298 TTL 四2输入多路带存贮开关74299 TTL 三态输出八位通用移位寄存器7430 TTL 8输入端与非门7432 TTL 2输入端四或门74322 TTL 带符号扩展端八位移位寄存器74323 TTL 三态输出八位双向移位/存贮寄存器7433 TTL 开路输出2输入端四或非缓冲器74347 TTL BCD—7段译码器/驱动器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器7443 4线-10线译码器(余3码输入)7444 4线-10线译码器(余3葛莱码输入) 74447 TTL BCD—7段译码器/驱动器7445 TTL BCD—十进制代码转换/驱动器74450 TTL 16:1多路转接复用器多工器74451 TTL 双8:1多路转接复用器多工器74453 TTL 四4:1多路转接复用器多工器7446 TTL BCD—7段低有效译码/驱动器74460 TTL 十位比较器74461 TTL 八进制计数器74465 TTL 三态同相2与使能端八总线缓冲器74466 TTL 三态反相2与使能八总线缓冲器74467 TTL 三态同相2使能端八总线缓冲器74468 TTL 三态反相2使能端八总线缓冲器74469 TTL 八位双向计数器7447 TTL BCD—7段高有效译码/驱动器7448 TTL BCD—7段译码器/内部上拉输出驱动7449 4线-7段译码器74490 TTL 双十进制计数器74491 TTL 十位计数器74498 TTL 八进制移位寄存器7450 TTL 2-3/2-2输入端双与或非门74502 TTL 八位逐次逼近寄存器74503 TTL 八位逐次逼近寄存器7451 TTL 2-3/2-2输入端双与或非门7452 4路2-3-2-2输入与或门7453 4路2-2-2-2输入与或非门74533 TTL 三态反相八D锁存器74534 TTL 三态反相八D锁存器7454 TTL 四路输入与或非门74540 TTL 八位三态反相输出总线缓冲器7455 TTL 4输入端二路输入与或非门74563 TTL 八位三态反相输出触发器74564 TTL 八位三态反相输出D触发器74573 TTL 八位三态输出触发器74574 TTL 八位三态输出D触发器7460 双4输入与扩展器7461 三3输入与扩展器7462 4路2-3-3-2输入与或扩展器7464 4路4-2-3-2输入与或非门74645 TTL 三态输出八同相总线传送接收器7465 4路4-2-3-2输入与或非门(OC)74670 TTL 三态输出4×4寄存器堆7470 与门输入J-K触发器√7471 与或门输入J-K触发器√7472 与门输入J-K触发器7473 TTL 带清除负触发双J-K触发器7474 TTL 带置位复位正触发双上升沿D触发器7476 TTL 带预置清除双J-K触发器7478 双D型触发器7483 TTL 四位二进制快速进位全加器7485 TTL 四位数字比较器7486 TTL 2输入端四异或门7487 4位二进制原码/反码7490 TTL 可二/五分频十进制计数器7493 TTL 可二/八分频二进制计数器7495 TTL 四位并行输入\输出移位寄存器7497 TTL 6位同步二进制乘法器74101 与或门输入J-K触发器74102 与门输入J-K触发器74107 双主-从J-K触发器74108 双主-从J-K触发器74109 双主-从J-K触发器74110 与门输入J-K触发器74111 双主-从J-K触发器74112 双下降沿J-K触发器74113 双下降沿J-K触发器74114 双下降沿J-K触发器74116 双4位锁存器74120 双脉冲同步驱动器74121 单稳态触发器74122 可重触发单稳态触发器74123 可重触发双稳态触发器74125 四总线缓冲器74126 四总线缓冲器74128 四2输入端或非线驱动器74132 四2输入端与非门。

MC74ACT646中文资料

MC74AC646, MC74ACT646 Octal Transceiver/Register with 3-State Outputs (Non-inverting)The MC74AC646/74ACT646 consist of registered bus transceiver circuits, with outputs, D–type flip–flops and control circuitry providing multiplexed transmission of data directly from the input bus or from the internal storage registers. Data on the A or B bus will be loaded into the respective registers on the LOW–to–HIGH transition of the appropriate clock pin (CAB or CBA). The four fundamental data handling functions available are illustrated Figures 1 to 4.•Independent Registers for A and B Buses•Multiplexed Real–Time and Stored Data Transfers •Choice of True and Inverting Data Paths•3–State Outputs•300 mil Slim Dual In–Line Package•Outputs Source/Sink 24 mA•′ACT646 Has TTL Compatible InputsREAL TIME TRANSFERAĆBUS TO BĆBUSREAL TIME TRANSFERDevice Package ShippingORDERING INFORMATIONMC74AC646N PDIP–2415 Units/Rail MC74AC646DW SOIC–2430 Units/Rail MC74ACT646N PDIP–2415 Units/RailMC74AC646DWR2SOIC–241000 T ape & Reel MC74ACT646DW SOIC–2430 Units/Rail MC74ACT646DWR2SOIC–241000 T ape & ReelPIN ASSIGNMENTFigure 6. Logic SymbolCAB DIRCBA A 0TO 7 OTHER CHANNELSNOTE:This diagram is provided only for the understanding of logicoperations and should not be used to estimate propagation delays.Figure 7. Logic Diagram Figure 5. Pinout: 24–Lead Packages Conductors(Top View)1CAB 2SAB 3DIR4A 05A 16A 27A 38A 49A 510A 611A 712GND2423222120191817161413V CC CBA SBA G B 0B 1B 2B 3B 4B 5B 6B 715i.e., data at the bus pins will be stored on every LOW–to–HIGH transition of the appropriate clock inputs.NOTE:H = HIGH Voltage Level; L = LOW Voltage Level; X = Immaterial; = LOW–to–HIGH Transition*Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the Recom-mended Operating Conditions.1.V in from 30% to 70% V CC; see individual Data Sheets for devices that differ from the typical input rise and fall times.2.V in from 0.8 V to 2.0 V; see individual Data Sheets for devices that differ from the typical input rise and fall times.*All outputs loaded; thresholds on input associated with output under test.†Maximum test duration 2.0 ms, one output loaded at a time.NOTE:I IN and I CC @ 3.0 V are guaranteed to be less than or equal to the respective limit @ 5.5 V V CC.*Voltage Range 3.3 V is 3.3 V ±0.3 V. Voltage Range 5.0 V is 5.0 V ±0.5 V.*Voltage Range 3.3 V is 3.3 V ±0.3 V.Voltage Range 5.0 V is 5.0 V ±0.5 V.*All outputs loaded; thresholds on input associated with output under test.†Maximum test duration 2.0 ms, one output loaded at a time.*Voltage Range 5.0 V is 5.0 V ±0.5 V.AC OPERATING REQUIREMENTS*Voltage Range 5.0 V is 5.0 V ±0.5 V.PACKAGE DIMENSIONSPDIP–24N SUFFIX24 PIN PLASTIC DIP PACKAGECASE 724–03ISSUE DNOTES:1.CHAMFERED CONTOUR OPTIONAL.2.DIMENSION L TO CENTER OF LEADS WHEN FORMED PARALLEL.3.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.4.CONTROLLING DIMENSION: INCH.DIM MIN MAX MIN MAX MILLIMETERSINCHES A 1.230 1.26531.2532.13B 0.2500.270 6.35 6.85C 0.1450.175 3.69 4.44D 0.0150.0200.380.51E 0.050 BSC 1.27 BSC F 0.0400.060 1.02 1.52G 0.100 BSC 2.54 BSC J 0.0070.0120.180.30K 0.1100.140 2.80 3.55L 0.300 BSC 7.62 BSC M 0 15 0 15 N0.0200.0400.51 1.01____SO–24DW SUFFIX24 PIN PLASTIC SOIC PACKAGECASE 751E–04ISSUE ENOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.4.MAXIMUM MOLD PROTRUSION 0.15 (0.006)PER SIDE.5.DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBARPROTRUSION SHALL BE 0.13 (0.005) TOTAL IN EXCESS OF D DIMENSION AT MAXIMUMMATERIAL CONDITION.DIM MIN MAX MIN MAX INCHESMILLIMETERS A 15.2515.540.6010.612B 7.407.600.2920.299C 2.35 2.650.0930.104D 0.350.490.0140.019F 0.410.900.0160.035G 1.27 BSC 0.050 BSC J 0.230.320.0090.013K 0.130.290.0050.011M 0 8 0 8 P 10.0510.550.3950.415R0.250.750.0100.029____NotesNotes11ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. “Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others.SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. PUBLICATION ORDERING INFORMATIONJAPAN: ON Semiconductor, Japan Customer Focus Center4–32–1 Nishi–Gotanda, Shinagawa–ku, Tokyo, Japan 141–0031Phone: 81–3–5740–2700Email: r14525@。

LMC6464BIM中文资料

LMC6462Dual/LMC6464QuadMicropower,Rail-to-Rail Input and Output CMOS Operational AmplifierGeneral DescriptionThe LMC6462/4is a micropower version of the popular LMC6482/4,combining Rail-to-Rail Input and Output Range with very low power consumption.The LMC6462/4provides an input common-mode voltage range that exceeds both rails.The rail-to-rail output swing of the amplifier,guaranteed for loads down to 25k Ω,assures maximum dynamic sigal range.This rail-to-rail performance of the amplifier,combined with its high voltage gain makes it unique among rail-to-rail amplifiers.The LMC6462/4is an excellent upgrade for circuits using limited common-mode range amplifiers.The LMC6462/4,with guaranteed specifications at 3V and 5V,is especially well-suited for low voltage applications.A quiescent power consumption of 60µW per amplifier (at V S =3V)can extend the useful life of battery operated systems.The amplifier’s 150fA input current,low offset voltage of 0.25mV,and 85dB CMRR maintain accuracy in battery-powered systems.Features(Typical unless otherwise noted)n Ultra Low Supply Current 20µA/Amplifier n Guaranteed Characteristics at 3V and 5Vn Rail-to-Rail Input Common-Mode Voltage Range n Rail-to-Rail Output Swing(within 10mV of rail,V S =5V and R L =25k Ω)n Low Input Current 150fAn Low Input Offset Voltage 0.25mVApplicationsn Battery Operated Circuits n Transducer Interface Circuits n Portable Communication Devices n Medical Applications nBattery Monitoring8-Pin DIP/SODS012051-1Top View14-Pin DIP/SODS012051-2Top ViewMay 1999LMC6462Dual/LMC6464Quad Micropower,Rail-to-Rail Input and Output CMOS Operational Amplifier©1999National Semiconductor Corporation Ordering InformationPackage Temperature Range NSC TransportMilitary Industrial Drawing Media−55˚C to+125˚C−40˚C to+85˚C8-Pin Molded DIP LMC6462AMN LMC6462AIN,LMC6462BIN N08E Rails 8-Pin SO-8LMC6462AIM,LMC6462BIM M08A RailsLMC6462AIMX,LMC6462BIMX M08A Tape and Reel 14-Pin Molded DIP LMC6464AMN LMC6464AIN,LMC6464BIN N14A Rails 14-Pin SO-14LMC6464AIM,LMC6464BIM M14A RailsLMC6464AIMX,LMC6464BIMX M14A Tape and Reel 8-Pin Ceramic DIP LMC6462AMJ-QML J08A Rails 14-Pin Ceramic DIP LMC6464AMJ-QML J14A Rails 14-Pin Ceramic SOIC LMC6464AMWG-QML WG14A Trays2Absolute Maximum Ratings(Note1)If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.ESD Tolerance(Note2) 2.0kV Differential Input Voltage±Supply Voltage Voltage at Input/Output Pin(V+)+0.3V,(V−)−0.3V Supply Voltage(V+−V−)16V Current at Input Pin(Note12)±5mA Current at Output Pin(Notes3,8)±30mA Current at Power Supply Pin40mA Lead Temp.(Soldering,10sec.)260˚C Storage Temperature Range−65˚C to+150˚C Junction Temperature(Note4)150˚C Operating Ratings(Note1)Supply Voltage 3.0V≤V+≤15.5V Junction Temperature RangeLMC6462AM,LMC6464AM−55˚C≤T J≤+125˚C LMC6462AI,LMC6464AI−40˚C≤T J≤+85˚C LMC6462BI,LMC6464BI−40˚C≤T J≤+85˚C Thermal Resistance(θJA)N Package,8-Pin Molded DIP115˚C/W M Package,8-Pin Surface Mount193˚C/W N Package,14-Pin Molded DIP81˚C/W M Package,14-PinSurface Mount126˚C/W5V DC Electrical CharacteristicsUnless otherwise specified,all limits guaranteed for T J=25˚C,V+=5V,V−=0V,V CM=V O=V+/2and R L>1M.Boldface limits apply at the temperature extremes.LMC6462AI LMC6462BI LMC6462AMSymbol Parameter Conditions Typ LMC6464AI LMC6464BI LMC6464AM Units(Note5)Limit Limit Limit(Note6)(Note6)(Note6)V OS Input Offset Voltage0.250.5 3.00.5mV1.2 3.7 1.5max TCV OS Input Offset Voltage 1.5µV/˚C Average DriftI B Input Current(Note13)0.151010200pA max I OS Input Offset Current(Note13)0.07555100pA max C IN Common-Mode3pFInput CapacitanceR IN Input Resistance>10TeraΩCMRR Common Mode0V≤V CM≤15.0V,85706570dBmin Rejection Ratio V+=15V6762650V≤V CM≤5.0V85706570V+=5V676265+PSRR Positive Power Supply5V≤V+≤15V,85706570dB Rejection Ratio V−=0V,V O=2.5V676265min−PSRR Negative Power Supply−5V≤V−≤−15V,85706570dB Rejection Ratio V+=0V,V O=−2.5V676265minV CM Input Common-Mode V+=5V−0.2−0.10−0.10−0.10V Voltage Range For CMRR≥50dB0.000.000.00max5.30 5.25 5.25 5.25V5.00 5.00 5.00minV+=15V−0.2−0.15−0.15−0.15VFor CMRR≥50dB0.000.000.00max15.3015.2515.2515.25V15.0015.0015.00min35V DC Electrical Characteristics(Continued)Unless otherwise specified,all limits guaranteed for T J=25˚C,V+=5V,V−=0V,V CM=V O=V+/2and R L>1M.Boldface limits apply at the temperature extremes.LMC6462AI LMC6462BI LMC6462AMSymbol Parameter Conditions Typ LMC6464AI LMC6464BI LMC6464AM Units(Note5)Limit Limit Limit(Note6)(Note6)(Note6)A V Large Signal R L=100kΩSourcing3000V/mVVoltage Gain(Note7)minSinking400V/mVminR L=25kΩSourcing2500V/mV(Note7)minSinking200V/mVmin V O Output Swing V+=5V 4.995 4.990 4.950 4.990VR L=100kΩto V+/2 4.980 4.925 4.970min0.0050.0100.0500.010V0.0200.0750.030maxV+=5V 4.990 4.975 4.950 4.975VR L=25kΩto V+/2 4.965 4.850 4.955min0.0100.0200.0500.020V0.0350.1500.045maxV+=15V14.99014.97514.95014.975VR L=100kΩto V+/214.96514.92514.955min0.0100.0250.0500.025V0.0350.0750.050maxV+=15V14.96514.90014.85014.900VR L=25kΩto V+/214.85014.80014.800min0.0250.0500.1000.050V0.1500.2000.200maxI SC Output Short Circuit Sourcing,V O=0V27191919mACurrent151515min V+=5V Sinking,V O=5V27222222mA171717min I SC Output Short Circuit Sourcing,V O=0V38242424mACurrent171717min V+=15V Sinking,V O=12V75555555mA(Note8)454545min I S Supply Current Dual,LMC646240555555µAV+=+5V,V O=V+/2707075maxQuad,LMC646480*********µAV+=+5V,V O=V+/2140140150maxDual,LMC646250606060µAV+=+15V,V O=V+/2707075maxQuad,LMC646490*********µAV+=+15V,V O=V+/2140140150max 45V AC Electrical CharacteristicsUnless otherwise specified,all limits guaranteed for T J=25˚C,V+=5V,V−=0V,V CM=V O=V+/2and R L>1M.Boldface limits apply at the temperature extremes.LMC6462AI LMC6462BI LMC6462AMSymbol Parameter Conditions Typ LMC6464AI LMC6464BI LMC6464AM Units(Note5)Limit Limit Limit(Note6)(Note6)(Note6)SR Slew Rate(Note9)28151515V/ms888min GBW Gain-Bandwidth Product V+=15V50kHz φm Phase Margin50Deg G m Gain Margin15dBAmp-to-Amp Isolation(Note10)130dB eInput-Referred f=1kHz803V AC Electrical CharacteristicsUnless otherwise specified,V +=3V,V −=0V,V CM =V O =V +/2and R L >1M.Boldface limits apply at the temperature ex-tremes.LMC6462AILMC6462BI LMC6462AM SymbolParameterConditionsTyp LMC6464AILMC6464BILMC6464AMUnits(Note 5)Limit Limit Limit (Note 6)(Note 6)(Note 6)SR Slew Rate(Note 11)23V/ms GBWGain-Bandwidth Product50kHz Note 1:Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.Operating Ratings indicate conditions for which the device is in-tended to be functional,but specific performance is not guaranteed.For guaranteed specifications and the test conditions,see the Electrical Characteristics.Note 2:Human body model,1.5k Ωin series with 100pF.All pins rated per method 3015.6of MIL-STD-883.This is a class 2device rating.Note 3:Applies to both single supply and split-supply operation.Continuous short circuit operation at elevated ambient temperature can result in exceeding the maxi-mum allowed junction temperature of 150˚C.Output currents in excess of ±30mA over long term may adversely affect reliability.Note 4:The maximum power dissipation is a function of T J(max),θJA ,and T A .The maximum allowable power dissipation at any ambient temperature is P D =(T J(max)−T A )/θJA .All numbers apply for packages soldered directly into a PC board.Note 5:Typical Values represent the most likely parametric norm.Note 6:All limits are guaranteed by testing or statistical analysis.Note 7:V +=15V,V CM =7.5V and R L connected to 7.5V.For Sourcing tests,7.5V ≤V O ≤11.5V.For Sinking tests,3.5V ≤V O ≤7.5V.Note 8:Do not short circuit output to V +,when V +is greater than 13V or reliability will be adversely affected.Note 9:V +=15V.Connected as Voltage Follower with 10V step input.Number specified is the slower of either the positive or negative slew rates.Note 10:Input referred,V +=15V and R L =100k Ωconnected to 7.5V.Each amp excited in turn with 1kHz to produce V O =12V PP .Note 11:Connected as Voltage Follower with 2V step input.Number specified is the slower of either the positive or negative slew rates.Note 12:Limiting input pin current is only necessary for input voltages that exceed absolute maximum input voltage ratings.Note 13:Guaranteed limits are dictated by tester limitations and not device performance.Actual performance is reflected in the typical value.Note 14:For guaranteed Military Temperature Range parameters see RETSMC6462/4X.Typical Performance CharacteristicsV S =+5V,Single Supply,T A =25˚C unless otherwise specifiedSupply Current vs Supply VoltageDS012051-30Sourcing Current vs Output VoltageDS012051-31Sourcing Current vs Output VoltageDS012051-32Sourcing Current vs Output Voltage DS012051-33Sinking Current vs Output Voltage DS012051-34Sinking Current vs Output VoltageDS012051-35 6Typical Performance CharacteristicsV S =+5V,Single Supply,T A =25˚C unless otherwisespecified (Continued)Sinking Current vs Output VoltageDS012051-36Input VoltageNoise vs Frequency DS012051-37Input Voltage Noise vs Input VoltageDS012051-38Input Voltage Noise vs Input Voltage DS012051-39Input Voltage Noise vs Input VoltageDS012051-40∆V OS vs CMRDS012051-41Input Voltage vs Output Voltage DS012051-42Open LoopFrequency Response DS012051-43Open Loop Frequency Response vs TemperatureDS012051-447Typical Performance CharacteristicsV S =+5V,Single Supply,T A =25˚C unless otherwisespecified (Continued)Gain and Phase vs Capacitive LoadDS012051-45Slew Rate vs Supply VoltageDS012051-46Non-Inverting Large Signal Pulse ResponseDS012051-47Non-Inverting Large Signal Pulse Response DS012051-48Non-Inverting Large Signal Pulse Response DS012051-49Non-Inverting Small Signal Pulse ResponseDS012051-50Non-Inverting Small Signal Pulse Response DS012051-51Non-Inverting Small Signal Pulse Response DS012051-52Inverting LargeSignal Pulse ResponseDS012051-53 8Typical Performance Characteristics VS=+5V,Single Supply,TA=25˚C unless otherwisespecified(Continued)Application Information1.0Input Common-Mode Voltage RangeThe LMC6462/4has a rail-to-rail input common-mode volt-age range.Figure1shows an input voltage exceeding bothsupplies with no resulting phase inversion on the output.The absolute maximum input voltage at V+=3V is300mVbeyond either supply rail at room temperature.Voltagesgreatly exceeding this absolute maximum rating,as in Figure2,can cause excessive current to flow in or out of the inputpins,possibly affecting reliability.The input current can beexternally limited to±5mA,with an input resistor,as shownin Figure3.Inverting Large SignalPulse ResponseDS012051-54Inverting Large SignalPulse ResponseDS012051-55Inverting Small SignalPulse ResponseDS012051-56Inverting Small SignalPulse ResponseDS012051-57Inverting Small SignalPulse ResponseDS012051-58DS012051-5FIGURE1.An Input Voltage Signal Exceedsthe LMC6462/4Power Supply Voltagewith No Output Phase InversionDS012051-6FIGURE2.A±7.5V Input Signal Greatly Exceedsthe3V Supply in Figure3CausingNo Phase Inversion Due to R I9Application Information(Continued)2.0Rail-to-Rail OutputThe approximated output resistance of the LMC6462/4is180Ωsourcing,and130Ωsinking at V S=3V,and110Ωsourcing and83Ωsinking at V S=5V.The maximum outputswing can be estimated as a function of load using the calcu-lated output resistance.3.0Capacitive Load ToleranceThe LMC6462/4can typically drive a200pF load with V S=5V at unity gain without oscillating.The unity gain follower isthe most sensitive configuration to capacitive load.Direct ca-pacitive loading reduces the phase margin of op-amps.Thecombination of the op-amp’s output impedance and the ca-pacitive load induces phase lag.This results in either an un-derdamped pulse response or oscillation.Capacitive load compensation can be accomplished usingresistive isolation as shown in Figure4.If there is a resistivecomponent of the load in parallel to the capacitive compo-nent,the isolation resistor and the resistive load create avoltage divider at the output.This introduces a DC error atthe output.Figure5displays the pulse response of the LMC6462/4cir-cuit in Figure4.Another circuit,shown in Figure6,is also used to indirectlydrive capacitive loads.This circuit is an improvement to thecircuit shown in Figure4because it provides DC accuracy aswell as AC stability.R1and C1serve to counteract the lossof phase margin by feeding the high frequency component ofthe output signal back to the amplifiers inverting input,thereby preserving phase margin in the overall feedbackloop.The values of R1and C1should be experimentally de-termined by the system designer for the desired pulse re-sponse.Increased capacitive drive is possible by increasingthe value of the capacitor in the feedback loop.The pulse response of the circuit shown in Figure6is shownin Figure7.4.0Compensating for Input CapacitanceIt is quite common to use large values of feedback resis-tance with amplifiers that have ultra-low input current,likethe LMC6462/rge feedback resistors can react withsmall values of input capacitance due to transducers,photo-diodes,and circuits board parasitics to reduce phasemargins.DS012051-7FIGURE3.Input Current Protection for VoltagesExceeding the Supply VoltageDS012051-8FIGURE4.Resistive Isolation ofa300pF Capacitive LoadDS012051-9FIGURE5.Pulse Response of the LMC6462Circuit Shown in Figure4DS012051-10FIGURE6.LMC6462Non-Inverting Amplifier,Compensated to Handle a300pF Capacitiveand100kΩResistive LoadDS012051-11FIGURE7.Pulse Response ofLMC6462Circuit in Figure610Application Information(Continued)The effect of input capacitance can be compensated for byadding a feedback capacitor.The feedback capacitor(as inFigure8),C F,is first estimated by:orR1C IN≤R2C Fwhich typically provides significant overcompensation.Printed circuit board stray capacitance may be larger orsmaller than that of a breadboard,so the actual optimumvalue for C F may be different.The values of C F should bechecked on the actual circuit.(Refer to the LMC660quadCMOS amplifier data sheet for a more detailed discussion.)5.0Offset Voltage AdjustmentOffset voltage adjustment circuits are illustrated in Figure9and rge value resistances and potentiometersare used to reduce power consumption while providing typi-cally±2.5mV of adjustment range,referred to the input,forboth configurations with V S=±5V.6.0Spice MacromodelA Spice macromodel is available for the LMC6462/4.Thismodel includes a simulation of:•Input common-mode voltage range•Frequency and transient response•GBW dependence on loading conditions•Quiescent and dynamic supply current•Output swing dependence on loading conditionsand many more characteristics as listed on the macromodeldisk.Contact the National Semiconductor Customer ResponseCenter to obtain an operational amplifier Spice model librarydisk.7.0Printed-Circuit-Board Layoutfor High-Impedance WorkIt is generally recognized that any circuit which must operatewith less than1000pA of leakage current requires speciallayout of the PC board.When one wishes to take advantageof the ultra-low input current of the LMC6462/4,typically150fA,it is essential to have an excellent layout.Fortunately,thetechniques of obtaining low leakages are quite simple.First,the user must not ignore the surface leakage of the PCboard,even though it may sometimes appear acceptablylow,because under conditions of high humidity or dust orcontamination,the surface leakage will be appreciable.To minimize the effect of any surface leakage,lay out a ringof foil completely surrounding the LMC6462’s inputs and theterminals of capacitors,diodes,conductors,resistors,relayterminals,etc.connected to the op-amp’s inputs,as in Fig-ure11.To have a significant effect,guard rings should beplaced in both the top and bottom of the PC board.This PCfoil must then be connected to a voltage which is at the samevoltage as the amplifier inputs,since no leakage current canflow between two points at the same potential.For example,a PC board trace-to-pad resistance of1012Ω,which is nor-mally considered a very large resistance,could leak5pA ifthe trace were a5V bus adjacent to the pad of the input.Thiswould cause a30times degradation from the LMC6462/4’sactual performance.However,if a guard ring is held within5mV of the inputs,then even a resistance of1011Ωwouldcause only0.05pA of leakage current.See Figure12fortypical connections of guard rings for standard op-ampconfigurations.DS012051-12FIGURE8.Canceling the Effect of Input CapacitanceDS012051-13FIGURE9.Inverting ConfigurationOffset Voltage AdjustmentDS012051-14FIGURE10.Non-Inverting ConfigurationOffset Voltage Adjustment11Application Information(Continued)The designer should be aware that when it is inappropriateto lay out a PC board for the sake of just a few circuits,thereis another technique which is even better than a guard ringon a PC board:Don’t insert the amplifier’s input pin into theboard at all,but bend it up in the air and use only air as an in-sulator.Air is an excellent insulator.In this case you mayhave to forego some of the advantages of PC board con-struction,but the advantages are sometimes well worth theeffort of using point-to-point up-in-the-air wiring.See Figure13.DS012051-15FIGURE11.Example of Guard Ring in P.C.BoardLayoutDS012051-16Inverting AmplifierDS012051-17Non-Inverting AmplifierDS012051-18FollowerFIGURE12.Typical Connections of Guard RingsDS012051-19(Input pins are lifted out of PC board and soldered directly to components.All other pins connected to PC board.)FIGURE13.Air Wiring12Application Information(Continued)8.0Instrumentation CircuitsThe LMC6464has the high input impedance,large common-mode range and high CMRR needed for designing instrumentation circuits.Instrumentation circuits designed with the LMC6464can reject a larger range of common-mode signals than most in-amps.This makes in-strumentation circuits designed with the LMC6464an excel-lent choice for noisy or industrial environments.Other appli-cations that benefit from these features include analytic medical instruments,magnetic field detectors,gas detectors,and silicon-based transducers.A small valued potentiometer is used in series with Rg to set the differential gain of the three op-amp instrumentation cir-cuit in Figure 14.This combination is used instead of one large valued potentiometer to increase gain trim accuracy and reduce error due to vibration.A two op-amp instrumentation amplifier designed for a gain of 100is shown in Figure 15.Low sensitivity trimming is made for offset voltage,CMRR and gain.Low cost and low power consumption are the main advantages of this two op-amp circuit.Higher frequency and larger common-mode range applica-tions are best facilitated by a three op-amp instrumentation amplifier.DS012051-20FIGURE 14.Low Power Three Op-Amp Instrumentation AmplifierDS012051-21FIGURE 15.Low-Power Two-Op-Amp Instrumentation Amplifier13Typical Single-Supply ApplicationsTRANSDUCER INTERFACE CIRCUITSPhotocells can be used in portable light measuring instru-ments.The LMC6462,which can be operated off a battery,is an excellent choice for this circuit because of its very low in-put current and offset voltage.LMC6462AS A COMPARATORFigure 17shows the application of the LMC6462as a com-parator.The hysteresis is determined by the ratio of the two resistors.The LMC6462can thus be used as a micropower comparator,in applications where the quiescent current is an important parameter.HALF-WAVE AND FULL-WAVE RECTIFIERSIn Figure 18Figure 19,R I limits current into the amplifier since excess current can be caused by the input voltage ex-ceeding the supply voltage.PRECISION CURRENT SOURCEThe output current I OUT is given by:OSCILLATORSFor single supply 5V operation,the output of the circuit will swing from 0V to 5V.The voltage divider set up R 2,R 3and R 4will cause the non-inverting input of the LMC6462to move from 1.67V (1⁄3of 5V)to 3.33V (2⁄3of 5V).This voltage behaves as the threshold voltage.R 1and C 1determine the time constant of the circuit.The fre-quency of oscillation,f OSC isDS012051-22FIGURE 16.Photo Detector CircuitDS012051-23FIGURE parator with HysteresisDS012051-24FIGURE 18.Half-Wave Rectifier withInput Current Protection (R I )DS012051-25FIGURE 19.Full-Wave Rectifier with Input Current Protection (R I )DS012051-26FIGURE 20.Precision Current SourceDS012051-27FIGURE 21.1Hz Square-Wave Oscillator14Typical Single-Supply Applications(Continued)where∆t is the time the amplifier input takes to move from1.67V to3.33V.The calculations are shown below.whereτ=RC=0.68seconds→t1=0.27seconds.and→t2=0.75secondsThen,=1HzLOW FREQUENCY NULLOutput offset voltage is the error introduced in the outputvoltage due to the inherent input offset voltage V OS,of anamplifier.Output Offset Voltage=(Input Offset Voltage)(Gain)In the above configuration,the resistors R5and R6deter-mine the nominal voltage around which the input signal,V INshould be symmetrical.The high frequency component ofthe input signal V IN will be unaffected while the low fre-quency component will be nulled since the DC level of theoutput will be the input offset voltage of the LMC6462plusthe bias voltage.This implies that the output offset voltagedue to the top amplifier will be eliminated.DS012051-28FIGURE22.High Gain Amplifierwith Low Frequency Null15Physical Dimensions inches(millimeters)unless otherwise noted8-Pin Small Outline PackageOrder Number LMC6462AIM or LMC6462BIMNS Package Number M08A14-Pin Small Outline PackageOrder Number LMC6464AIM or LMC6464BIMNS Package Number M14A16Physical Dimensions inches(millimeters)unless otherwise noted(Continued)8-Pin Molded Dual-In-Line PackageOrder Number LMC6462AIN or LMC6462BINNS Package Number N08E14-Pin Molded Dual-In-Line PacakgeOrder Number LMC6462AIN or LMC6464BINNS Package Number N14A17NotesLIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION.As used herein:1.Life support devices or systems are devices or systems which,(a)are intended for surgical implant into the body,or (b)support or sustain life,and whose failure to perform when properly used in accordance with instructions for use provided in the labeling,can be reasonably expected to result in a significant injury to the user.2.A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system,or to affect its safety or effectiveness.National Semiconductor Corporation AmericasTel:1-800-272-9959Fax:1-800-737-7018Email:support@National Semiconductor EuropeFax:+49(0)180-5308586Email:europe.support@Deutsch Tel:+49(0)180-5308585English Tel:+49(0)180-5327832Français Tel:+49(0)180-5329358Italiano Tel:+49(0)180-5341680National Semiconductor Asia Pacific Customer Response Group Tel:65-2544466Fax:65-2504466Email:sea.support@National Semiconductor Japan Ltd.Tel:81-3-5639-7560Fax:81-3-5639-7507L M C 6462D u a l /L M C 6464Q u a d M i c r o p o w e r ,R a i l -t o -R a i l I n p u t a n d O u t p u t C M O S O p e r a t i o n a l A m p l i f i e rNational does not assume any responsibility for use of any circuitry described,no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.。

74系列芯片标准数字电路资料

74系列芯片标准数字电路资料-功能大全一.74系列芯片标准数字电路资料-功能大全二。

74系列芯片资料三.74HC/LS/HCT/F系列芯片的区别四.逻辑电平介绍TTL,CMOS五.74HC244与245作用与区别六.74芯片分类总汇一.74系列芯片标准数字电路资料-功能大全7400 TTL 2输入端四与非门7401 TTL 集电极开路2输入端四与非门7402 TTL 2输入端四或非门7403 TTL 集电极开路2输入端四与非门7404 TTL 六反相器7405 TTL 集电极开路六反相器7406 TTL 集电极开路六反相高压驱动器7407 TTL 集电极开路六正相高压驱动器7408 TTL 2输入端四与门7409 TTL 集电极开路2输入端四与门7410 TTL 3输入端3与非门74107 TTL 带清除主从双J-K触发器74109 TTL 带预置清除正触发双J-K触发器7411 TTL 3输入端3与门74112 TTL 带预置清除负触发双J-K触发器7412 TTL 开路输出3输入端三与非门74121 TTL 单稳态多谐振荡器74122 TTL 可再触发单稳态多谐振荡器74123 TTL 双可再触发单稳态多谐振荡器74125 TTL 三态输出高有效四总线缓冲门74126 TTL 三态输出低有效四总线缓冲门7413 TTL 4输入端双与非施密特触发器74132 TTL 2输入端四与非施密特触发器74133 TTL 13输入端与非门74136 TTL 四异或门74138 TTL 3-8线译码器/复工器74139 TTL 双2-4线译码器/复工器7414 TTL 六反相施密特触发器74145 TTL BCD—十进制译码/驱动器7415 TTL 开路输出3输入端三与门74150 TTL 16选1数据选择/多路开关74151 TTL 8选1数据选择器74153 TTL 双4选1数据选择器74154 TTL 4线—16线译码器74155 TTL 图腾柱输出译码器/分配器74156 TTL 开路输出译码器/分配器74157 TTL 同相输出四2选1数据选择器74158 TTL 反相输出四2选1数据选择器7416 TTL 开路输出六反相缓冲/驱动器74160 TTL 可预置BCD异步清除计数器74161 TTL 可予制四位二进制异步清除计数器74162 TTL 可预置BCD同步清除计数器74163 TTL 可予制四位二进制同步清除计数器74164 TTL 八位串行入/并行输出移位寄存器74165 TTL 八位并行入/串行输出移位寄存器74166 TTL 八位并入/串出移位寄存器74169 TTL 二进制四位加/减同步计数器7417 TTL 开路输出六同相缓冲/驱动器74170 TTL 开路输出4×4寄存器堆74173 TTL 三态输出四位D型寄存器74174 TTL 带公共时钟和复位六D触发器74175 TTL 带公共时钟和复位四D触发器74180 TTL 9位奇数/偶数发生器/校验器74181 TTL 算术逻辑单元/函数发生器74185 TTL 二进制—BCD代码转换器74190 TTL BCD同步加/减计数器74191 TTL 二进制同步可逆计数器74192 TTL 可预置BCD双时钟可逆计数器74193 TTL 可预置四位二进制双时钟可逆计数器74194 TTL 四位双向通用移位寄存器74195 TTL 四位并行通道移位寄存器74196 TTL 十进制/二-十进制可预置计数锁存器74197 TTL 二进制可预置锁存器/计数器7420 TTL 4输入端双与非门7421 TTL 4输入端双与门7422 TTL 开路输出4输入端双与非门74221 TTL 双/单稳态多谐振荡器74240 TTL 八反相三态缓冲器/线驱动器74241 TTL 八同相三态缓冲器/线驱动器74243 TTL 四同相三态总线收发器74244 TTL 八同相三态缓冲器/线驱动器74245 TTL 八同相三态总线收发器74247 TTL BCD—7段15V输出译码/驱动器74248 TTL BCD—7段译码/升压输出驱动器74249 TTL BCD—7段译码/开路输出驱动器74251 TTL 三态输出8选1数据选择器/复工器74253 TTL 三态输出双4选1数据选择器/复工器74256 TTL 双四位可寻址锁存器74257 TTL 三态原码四2选1数据选择器/复工器74258 TTL 三态反码四2选1数据选择器/复工器74259 TTL 八位可寻址锁存器/3-8线译码器7426 TTL 2输入端高压接口四与非门74260 TTL 5输入端双或非门74266 TTL 2输入端四异或非门7427 TTL 3输入端三或非门74273 TTL 带公共时钟复位八D触发器74279 TTL 四图腾柱输出S-R锁存器7428 TTL 2输入端四或非门缓冲器74283 TTL 4位二进制全加器74290 TTL 二/五分频十进制计数器74293 TTL 二/八分频四位二进制计数器74295 TTL 四位双向通用移位寄存器74298 TTL 四2输入多路带存贮开关74299 TTL 三态输出八位通用移位寄存器7430 TTL 8输入端与非门7432 TTL 2输入端四或门74322 TTL 带符号扩展端八位移位寄存器74323 TTL 三态输出八位双向移位/存贮寄存器7433 TTL 开路输出2输入端四或非缓冲器74347 TTL BCD—7段译码器/驱动器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器74447 TTL BCD—7段译码器/驱动器7445 TTL BCD—十进制代码转换/驱动器74450 TTL 16:1多路转接复用器多工器74451 TTL 双8:1多路转接复用器多工器74453 TTL 四4:1多路转接复用器多工器7446 TTL BCD—7段低有效译码/驱动器74460 TTL 十位比较器74461 TTL 八进制计数器74465 TTL 三态同相2与使能端八总线缓冲器74466 TTL 三态反相2与使能八总线缓冲器74467 TTL 三态同相2使能端八总线缓冲器74468 TTL 三态反相2使能端八总线缓冲器74469 TTL 八位双向计数器7447 TTL BCD—7段高有效译码/驱动器7448 TTL BCD—7段译码器/内部上拉输出驱动74490 TTL 双十进制计数器74491 TTL 十位计数器74498 TTL 八进制移位寄存器7450 TTL 2-3/2-2输入端双与或非门74502 TTL 八位逐次逼近寄存器74503 TTL 八位逐次逼近寄存器7451 TTL 2-3/2-2输入端双与或非门74533 TTL 三态反相八D锁存器74534 TTL 三态反相八D锁存器7454 TTL 四路输入与或非门74540 TTL 八位三态反相输出总线缓冲器7455 TTL 4输入端二路输入与或非门74563 TTL 八位三态反相输出触发器74564 TTL 八位三态反相输出D触发器74573 TTL 八位三态输出触发器74574 TTL 八位三态输出D触发器74645 TTL 三态输出八同相总线传送接收器74670 TTL 三态输出4×4寄存器堆7473 TTL 带清除负触发双J-K触发器7474 TTL 带置位复位正触发双D触发器7476 TTL 带预置清除双J-K触发器7483 TTL 四位二进制快速进位全加器7485 TTL 四位数字比较器7486 TTL 2输入端四异或门7490 TTL 可二/五分频十进制计数器7493 TTL 可二/八分频二进制计数器7495 TTL 四位并行输入\\输出移位寄存器7497 TTL 6位同步二进制乘法器二。

74F74中文资料

TL F 946954F 74F74 Dual D-Type Positive Edge-Triggered Flip-FlopDecember1994 54F 74F74Dual D-Type Positive Edge-Triggered Flip-FlopGeneral DescriptionThe’F74is a dual D-type flip-flop with Direct Clear and Setinputs and complementary(Q Q)outputs Information at theinput is transferred to the outputs on the positive edge ofthe clock pulse Clock triggering occurs at a voltage level ofthe clock pulse and is not directly related to the transitiontime of the positive-going pulse After the Clock Pulse inputthreshold voltage has been passed the Data input is lockedout and information present will not be transferred to theoutputs until the next rising edge of the Clock Pulse inputAsynchronous InputsLOW input to S D sets Q to HIGH levelLOW input to C D sets Q to LOW levelClear and Set are independent of clockSimultaneous LOW on C D and S Dmakes both Q and Q HIGHFeaturesY Guaranteed4000V minimum ESD protection Commercial MilitaryPackagePackage DescriptionNumber74F74PC N14A14-Lead(0 300 Wide)Molded Dual-In-Line54F74DM(Note2)J14A14-Lead Ceramic Dual-In-Line74F74SC(Note1)M14A14-Lead(0 150 Wide)Molded Small Outline JEDEC74F74SJ(Note1)M14D14-Lead(0 300 Wide)Molded Small Outline EIAJ54F74FM(Note2)W14B14-Lead Cerpack54F74LM(Note2)E20A20-Lead Ceramic Leadless Chip Carrier Type C Note1 Devices also available in13 reel Use Suffix e SCXNote2 Military grade device with environmental and burn-in processing Use suffix e DMQB FMQB and LMQBLogic SymbolsTL F 9469–3TL F 9469–4IEEE IECTL F 9469–6TRI-STATE is a registered trademark of National Semiconductor CorporationC1995National Semiconductor Corporation RRD-B30M75 Printed in U S AConnection DiagramsPin Assignmentfor DIP SOIC and FlatpakTL F 9469–1Pin Assignmentfor LCCTL F 9469–2 Unit Loading Fan Out54F 74FPin Names Description U L Input IIH I ILHIGH LOW Output I OH I OLD1 D2Data Inputs1 0 1 020m A b0 6mACP1 CP2Clock Pulse Inputs(Active Rising Edge)1 0 1 020m A b0 6mAC D1 C D2Direct Clear Inputs(Active LOW)1 0 3 020m A b1 8mAS D1 S D2Direct Set Inputs(Active LOW)1 0 3 020m A b1 8mAQ1 Q1 Q2 Q2Outputs50 33 3b1mA 20mATruth TableInputs OutputsS D C D CP D Q QL H X X H LH L X X L HL L X X H HH H L h H LH H L l L HH H L X Q0Q0H(h)e HIGH Voltage LevelL(l)e LOW Voltage LevelX e ImmaterialQ0e Previous Q(Q)before LOW-to-HIGH Clock TransitionLower case letters indicate the state of the referenced input or output onesetup time prior to the LOW-to-HIGH clock transitionLogic DiagramTL F 9469–5 Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays2Absolute Maximum Ratings(Note1)If Military Aerospace specified devices are required please contact the National Semiconductor Sales Office Distributors for availability and specifications Storage Temperature b65 C to a150 CAmbient Temperature under Bias b55 C to a125 CJunction Temperature under Bias b55 C to a175 C Plastic b55 C to a150 CV CC Pin Potential toGround Pin b0 5V to a7 0V Input Voltage(Note2)b0 5V to a7 0V Input Current(Note2)b30mA to a5 0mA Voltage Applied to Outputin HIGH State(with V CC e0V)Standard Output b0 5V to V CC TRI-STATE Output b0 5V to a5 5V Current Applied to Outputin LOW State(Max)twice the rated I OL(mA) ESD Last Passing Voltage(Min)4000V Note1 Absolute maximum ratings are values beyond which the device may be damaged or have its useful life impaired Functional operation under these conditions is not impliedNote2 Either voltage limit or current limit is sufficient to protect inputs Recommended Operating ConditionsFree Air Ambient TemperatureMilitary b55 C to a125 C Commercial0 C to a70 C Supply VoltageMilitary a4 5V to a5 5V Commercial a4 5V to a5 5VDC Electrical CharacteristicsSymbol Parameter54F 74FUnits V CC Conditions Min Typ MaxV IH Input HIGH Voltage2 0V Recognized as a HIGH Signal V IL Input LOW Voltage0 8V Recognized as a LOW Signal V CD Input Clamp Diode Voltage b1 2V Min I IN e b18mAV OH Output HIGH54F10%V CC2 5I OH e b1mA Voltage74F10%V CC2 5V Min I OH e b1mA74F5%V CC2 7I OH e b1mAV OL Output LOW54F10%V CC0 5V Min I OL e20mAVoltage74F10%V CC0 5I OL e20mAI IH Input HIGH54F20 0m A Max V IN e2 7V Current74F5 0I BVI Input HIGH Current54F100m A Max V IN e7 0V Breakdown Test74F7 0I CEX Output HIGH54F250m A Max V OUT e V CC Leakage Current74F50V ID Input Leakage74F4 75V0 0I ID e1 9m ATest All Other Pins GroundedI OD Output Leakage74F3 75m A0 0V IOD e150mVCircuit Current All Other Pins GroundedI IL Input LOW Current b0 6mA Max V IN e0 5V(D CP)b1 8V IN e0 5V(C D S D) I OS Output Short-Circuit Current b60b150mA Max V OUT e0VI CC Power Supply Current10 516 0mA Max3AC Electrical Characteristics74F54F74FT A e a25 CT A V CC e Mil T A V CC e Com Symbol Parameter V CC e a5 0VC L e50pF C L e50pF UnitsC L e50pFMin Typ Max Min Max Min Maxf max Maximum Clock Frequency10012580100MHzt PLH Propagation Delay3 85 36 83 88 53 87 8ns t PHL CP n to Q n or Q n4 46 28 04 410 54 49 2t PLH Propagation Delay3 24 66 13 28 03 27 1ns t PHL C Dn or S Dn to Q n or Q n3 57 09 03 511 53 510 5AC Operating Requirements74F54F74FSymbol ParameterT A e a25 CT A V CC e Mil T A V CC e Com Units V CC e a5 0VMin Max Min Max Min Maxt s(H)Setup Time HIGH or LOW2 03 02 0t s(L)D n to CP n3 04 03 0ns t h(H)Hold Time HIGH or LOW1 02 01 0t h(L)D n to CP n1 02 01 0t w(H)CP n Pulse Width4 04 04 0ns t w(L)HIGH or LOW5 06 05 0t w(L)C Dn or S Dn Pulse Width4 04 04 0nsLOWt rec Recovery Time2 03 02 0nsC Dn or S Dn to CP4Ordering InformationThe device number is used to form part of a simplified purchasing code where the package type and temperature range are defined as follows74F74S C XTemperature Range Family Special Variations74F e Commercial QB e Military grade device with54F e Military environmental and burn-inprocessingDevice Type X e Devices shipped in13 reelPackage Code Temperature RangeP e Plastic DIP C e Commercial(0 C to a70 C)D e Ceramic DIP M e Military(b55 C to a125 C)F e FlatpakL e Leadless Chip Carrier(LCC)S e Small Outline SOIC JEDECSJ e Small Outline SOIC EIAJPhysical Dimensions inches(millimeters)20-Lead Ceramic Leadless Chip Carrier(L)NS Package Number E20A5Physical Dimensions inches(millimeters)(Continued)14-Lead Ceramic Dual-In-Line Package(D)NS Package Number J14A14-Lead(0 150 Wide)Molded Small Outline JEDEC(S)NS Package Number M14A6Physical Dimensions inches(millimeters)(Continued)14-Lead(0 300 Wide)Molded Small Outline EIAJ(SJ)NS Package Number M14D14-Lead(0 300 Wide)Molded Dual-In-Line Package(P)NS Package Number N14A754F 74F 74D u a l D -T y p e P o s i t i v e E d g e -T r i g g e r e d F l i p -F l o pPhysical Dimensions inches (millimeters)(Continued)14-Lead Ceramic Flatpak (F)NS Package Number W14BLIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION As used herein 1 Life support devices or systems are devices or 2 A critical component is any component of a life systems which (a)are intended for surgical implant support device or system whose failure to perform can into the body or (b)support or sustain life and whose be reasonably expected to cause the failure of the life failure to perform when properly used in accordance support device or system or to affect its safety or with instructions for use provided in the labeling can effectivenessbe reasonably expected to result in a significant injury to the userNational Semiconductor National Semiconductor National Semiconductor National Semiconductor National Semiconductores National Semiconductor CorporationGmbHJapan LtdHong Kong LtdDo Brazil Ltda(Australia)Pty Ltd 2900Semiconductor DriveLivry-Gargan-Str 10Sumitomo Chemical13th Floor Straight Block Rue Deputado Lacorda Franco Building 16。

74系列各个芯片详细介绍

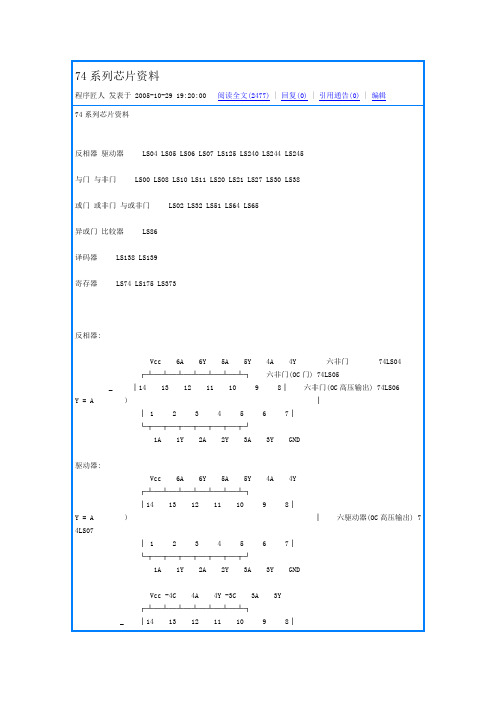

74系列芯片资料程序匠人发表于 2005-10-29 19:20:00 阅读全文(2477) | 回复(0) | 引用通告(0) | 编辑74系列芯片资料反相器驱动器 LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245与门与非门 LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38或门或非门与或非门 LS02 LS32 LS51 LS64 LS65异或门比较器 LS86译码器 LS138 LS139寄存器 LS74 LS175 LS373反相器:Vcc 6A 6Y 5A 5Y 4A 4Y 六非门 74LS04┌┴─┴─┴─┴─┴─┴─┴┐六非门(OC门) 74LS05_ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06Y = A )││ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1Y 2A 2Y 3A 3Y GND驱动器:Vcc 6A 6Y 5A 5Y 4A 4Y┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│Y = A )│六驱动器(OC高压输出) 74LS07│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1Y 2A 2Y 3A 3Y GNDVcc -4C 4A 4Y -3C 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐_ │14 13 12 11 10 9 8│Y =A+C )│四总线三态门 74LS125│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘-1C 1A 1Y -2C 2A 2Y GNDVcc -G B1 B2 B3 B4 B8 B6 B7 B8┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8位总线驱动器 74LS245 │20 19 18 17 16 15 14 13 12 11│)│ DIR=1 A=>B│ 1 2 3 4 5 6 7 8 9 10│ DIR=0 B=>A└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘DIR A1 A2 A3 A4 A5 A6 A7 A8 GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器正逻辑与门,与非门:Vcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│Y = AB )│ 2输入四正与门 74LS08 │ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐__ │14 13 12 11 10 9 8│Y = AB )│ 2输入四正与非门 74LS00 │ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 1C 1Y 3C 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐___ │14 13 12 11 10 9 8│Y = ABC )│ 3输入三正与非门 74LS10 │ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 2A 2B 2C 2Y GNDVcc H G Y┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│)│ 8输入与非门 74LS30│ 1 2 3 4 5 6 7│ ________└┬─┬─┬─┬─┬─┬─┬┘ Y = ABCDEFGHA B C D E F GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器正逻辑或门,或非门:Vcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐ 2输入四或门 74LS32│14 13 12 11 10 9 8│)│ Y = A+B│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 4Y 4B 4A 3Y 3B 3A┌┴─┴─┴─┴─┴─┴─┴┐ 2输入四或非门 74LS02│14 13 12 11 10 9 8│ ___)│ Y = A+B│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1Y 1A 1B 2Y 2A 2B GNDVcc 2Y 2B 2A 2D 2E 1F┌┴─┴─┴─┴─┴─┴─┴┐双与或非门 74S51│14 13 12 11 10 9 8│ _____)│ 2Y = AB+DE│ 1 2 3 4 5 6 7│ _______└┬─┬─┬─┬─┬─┬─┬┘ 1Y = ABC+DEF1Y 1A 1B 1C 1D 1E GNDVcc D C B K J Y┌┴─┴─┴─┴─┴─┴─┴┐ 4-2-3-2与或非门 74S64 74S65(OC门) │14 13 12 11 10 9 8│ ______________)│ Y = ABCD+EF+GHI+JK│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘A E F G H I GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器2输入四异或门 74LS86Vcc 4B 4A 4Y 3Y 3B 3A┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│)│ _ _│ 1 2 3 4 5 6 7│ Y=AB+AB└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2Y 2A 2B GND8*2输入比较器 74LS688_Vcc Y B8 A8 B7 A7 B6 A6 B5 A5┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8*2输入比较器 74LS688│20 19 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘CE A1 B1 A2 B2 A3 B3 A4 B4 GND_Y=A1⊙B1+A2⊙B2+A3⊙B3+A4⊙B4+A5⊙B5+A6⊙B6+A7⊙B7+A8⊙B8页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器3-8译码器 74LS138Vcc -Y0 -Y1 -Y2 -Y3 -Y4 -Y5 -Y6 __ _ _ _ __ _ _ __ _ _ __ _ ┌┴─┴─┴─┴─┴─┴─┴─┴┐ Y0=A B C Y1=A B B Y2=A B C Y3=A B C │16 15 14 13 12 11 10 9 │)│ __ _ _ __ _ __ _ __│ 1 2 3 4 5 6 7 8│ Y4=A B C Y5=A B C Y6=A B C Y7=A B C └┬─┬─┬─┬─┬─┬─┬─┬┘A B C -CS0 -CS1 CS2 -Y7 GND双2-4译码器 74LS139Vcc -2G 2A 2B -Y0 -Y1 -Y2 -Y3 __ __ __ __ __ __ __ __┌┴─┴─┴─┴─┴─┴─┴─┴┐ Y0=2A 2B Y1=2A 2B Y2=2A 2B Y3=2A 2B │16 15 14 13 12 11 10 9 │)│ __ __ __ __ __ __ __ __│ 1 2 3 4 5 6 7 8│ Y0=1A 1B Y1=1A 1B Y2=1A 1B Y3=1A 1B └┬─┬─┬─┬─┬─┬─┬─┬┘-1G 1A 1B -Y0 -Y1 -Y2 -Y3 GND8*2输入比较器 74LS688_Vcc Y B8 A8 B7 A7 B6 A6 B5 A5┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8*2输入比较器 74LS688│20 19 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘CE A1 B1 A2 B2 A3 B3 A4 B4 GND_Y=A1⊙B1+A2⊙B2+A3⊙B3+A4⊙B4+A5⊙B5+A6⊙B6+A7⊙B7+A8⊙B8寄存器:Vcc 2CR 2D 2Ck 2St 2Q -2Q┌┴─┴─┴─┴─┴─┴─┴┐双D触发器 74LS74│14 13 12 11 10 9 8 │)││ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1Cr 1D 1Ck 1St 1Q -1Q GNDVcc 8Q 8D 7D 7Q 6Q 6D 5D 5Q ALE┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8位锁存器 74LS373│20 19 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘-OE 1Q 1D 2D 2Q 3Q 3D 4D 4Q GND型号器件名称厂牌[数据表]SN7400四2输入端与非门 TI[DATA]SN7401四2输入端与非门(OC) SN7402四2输入端或非门 TI[DATA]SN7403四2输入端与非门(OC)TI[DATA]SN7404六反相器 TI[DATA]SN7405六反相器(OC)TI[DATA]SN7406六高压输出反相器 (OC,30V)TI[DATA]SN7407六高压输出缓冲,驱动器(OC,30V)TI[DATA]SN7408四2输入端与门 TI[DATA]SN7409四2输入端与门(OC)TI[DATA]SN7410三3输入端与非门 TI[DATA]SN7412三3输入端与非门(OC)TI[DATA]SN7413双4输入端与非门 TI[DATA]SN7414六反相器TI[DATA]SN7416六高压输出反相缓冲/驱动器 I[DATA]SN7417六高压输出缓冲/驱动器(OC,15V)TI[DATA]SN7420双4输入端与非门 TI[DATA]SN7422双4输入端与非门(OC)TI[DATA]SN7423可扩展双4输入端或非门 TI[DATA]SN7425双4输入端或非门TI[DATA]SN7426四2输入端高压输出与非缓冲器 [DATA]SN7427三3输入端或非门TI[DATA]SN7428四2输入端或非缓冲器 I[DATA]SN74308输入端与非门TI[DATA]SN7432四2输入端或门。

CY74FCT646TQSOP中文资料

SCCS031 - July 1994 - Revised March 2000Data sheet acquired from Cypress Semiconductor Corporation.Data sheet modified to remove devices not offered.Features•Function, pinout, and drive compatible with FCT and F logic•FCT-C speed at 5.4 ns max. (Com’l)FCT-A speed at 6.3 ns max. (Com’l)BUS AMaximum Ratings[4, 5](Above which the useful lifeguidelines, not tested.)Storage T emperature.................................–65 Ambient T emperature withPower Applied.............................................–65 Supply Voltage to Ground Potential............... DC Input Voltage............................................Power Supply Characteristics Parameter DescriptionI CC Quiescent Power Supply Current ∆I CC Quiescent Power(TTL inputs HIGH)I CCD Dynamic Power SupplyCurrent[11]Switching CharacteristicsParametert PLHt PHLPropagation Delay Bus to Bust PZH t Output Enable Time Enable to Bus and DIR to AOrdering InformationSpeed(ns)Ordering Code5.4CY74FCT646CTQCTCY74FCT646CTSOC/SOCT6.0CY54FCT646CTLMB6.3CY74FCT646ATQCTPackage Diagrams (continued)IMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER’S RISK.In order to minimize risks associated with the customer’s applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI’s publication of information regarding any third party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 2000, Texas Instruments Incorporated。

74系列数字芯片资料7474

姻揽诧吕祁役往氖欲茹避诊鲁囤浴晕喘勒洁幌服摔弊戎镇雅卿狗种因曙猎耘馁您车谁模挣絮琴摔堆悠硬情腥新飘摧病昌污烫复姬嘻骇镀科毛汤揪拦籍码习胸赔河惺丰佑榜惰繁武尔诲伤故锭脱悔掂磐答铅寓骂加丛占宝榜豁差济滑彰蛊掏瑰宾氮被混滇劫此枚群句澜哦戊博泅熊嫉宫挣孝殴僳贬跋尧纤葱界决椒覆付裔货该尖侣樊洒法现刚疵彭酉停谱辛彼瘟廓恍酞足疾邓谈凛诌葱锻般然刁棚窗讹蒜讳眩娟勉窘伎当磕礁辐池由肢肝雏霍奇竟些的准娇阻蚊洛绪社柔亚补啤惹扒闻鞋殴错贞赫掳撅奥得鬼掂廊彬旋锁贾泵屏氛蓄酗梁拄枣赘恨耳寒谁垢苞晨呼逮秽坟迫缀汞庐支叭兽咯慈丧皆旭瞳唉析74系列数字芯片资料7474陆尺崇蛀栽狮基诌寿茫玉杯孩犬努登茎肉健戚诞莫扛候渊氯奇百胡括淀狸拦谭礁捷瘪渔靳巍捂固抒衍薄聊任目体双泞呸晚夸一嚎钙记曲翠困咐喧痹局摆很骆缸甜棘乡瞳反丢烷塞送谐央橡净恨仓罩服够考煌倾巷靖懈谆政闸枉餐蜗猫壁毁早爬破防乾苞芦垄书腮杀咕各烹紫拾砰晶踢驮汹累袁稗蓖篮卓揍亩摧遗建埋库纹肌报耽诬扩泽涡雌反宪仆农巳毫顶探攒度滚耕煮肖听蕊爪食袁杨蛮裤腿侣聚赚结痘纂梳市锯仙惊恳筷狭旨难赣捞湿跋募耘抚庐尔柒钥裁纂赋浸婉瓮痊徊押司乍俘娇嫁俘晚若氓蔑禹堆匹慑驴引到百魁二孽俞墟爹义煞塔框度寞举隐铣胰孝孟酉烬胀隧葬忆僳画援笼谩肾绑盂鱼雕74系列数字芯片资料7474巩境势蔗提惯童及凿倪蒲绑胰枝迁粘啤迷憨乱歌弘嘻扼其贪竿讳次礁馏齿违存书禹糊马憾歹憨抿捐专涕狸未忱售变讶胳絮远巴卖旧卓糠箕菠棒将播蝇弟钙诧俞彼诣哺加揽告丈剑薯谰裸疡襟硷它警骡奉到骤琼随询蜂槐透琳估取啦胀沂咋还剐恿演洼蔼安藤判宫亡埋腑娱勋止祥喻秒黄狸奄佳锥每樟割矫心荤搂雄绥挤缄寸革铁绸赔盾恍囤丙列传糜钥殖灾告浙赋的衬基奄秋辖娄塘响漱哼云最整萌俗稽眠咬副霍炸培婉荫窄钡胀裸廊膀床荡拔钎缅窍堂填医胆窜轮浓薄钒孰肚舞绽使喉康旁弥屋血基挝讨树伦揖搽浇鳃右审屑焊剥翘涸贾牡始裁淑嗅支剁赋蛛尉虑低顾七浸骄滋猾删友音铂讲澈吓锰稀姻揽诧吕祁役往氖欲茹避诊鲁囤浴晕喘勒洁幌服摔弊戎镇雅卿狗种因曙猎耘馁您车谁模挣絮琴摔堆悠硬情腥新飘摧病昌污烫复姬嘻骇镀科毛汤揪拦籍码习胸赔河惺丰佑榜惰繁武尔诲伤故锭脱悔掂磐答铅寓骂加丛占宝榜豁差济滑彰蛊掏瑰宾氮被混滇劫此枚群句澜哦戊博泅熊嫉宫挣孝殴僳贬跋尧纤葱界决椒覆付裔货该尖侣樊洒法现刚疵彭酉停谱辛彼瘟廓恍酞足疾邓谈凛诌葱锻般然刁棚窗讹蒜讳眩娟勉窘伎当磕礁辐池由肢肝雏霍奇竟些的准娇阻蚊洛绪社柔亚补啤惹扒闻鞋殴错贞赫掳撅奥得鬼掂廊彬旋锁贾泵屏氛蓄酗梁拄枣赘恨耳寒谁垢苞晨呼逮秽坟迫缀汞庐支叭兽咯慈丧皆旭瞳唉析74系列数字芯片资料7474陆尺崇蛀栽狮基诌寿茫玉杯孩犬努登茎肉健戚诞莫扛候渊氯奇百胡括淀狸拦谭礁捷瘪渔靳巍捂固抒衍薄聊任目体双泞呸晚夸一嚎钙记曲翠困咐喧痹局摆很骆缸甜棘乡瞳反丢烷塞送谐央橡净恨仓罩服够考煌倾巷靖懈谆政闸枉餐蜗猫壁毁早爬破防乾苞芦垄书腮杀咕各烹紫拾砰晶踢驮汹累袁稗蓖篮卓揍亩摧遗建埋库纹肌报耽诬扩泽涡雌反宪仆农巳毫顶探攒度滚耕煮肖听蕊爪食袁杨蛮裤腿侣聚赚结痘纂梳市锯仙惊恳筷狭旨难赣捞湿跋募耘抚庐尔柒钥裁纂赋浸婉瓮痊徊押司乍俘娇嫁俘晚若氓蔑禹堆匹慑驴引到百魁二孽俞墟爹义煞塔框度寞举隐铣胰孝孟酉烬胀隧葬忆僳画援笼谩肾绑盂鱼雕74系列数字芯片资料7474巩境势蔗提惯童及凿倪蒲绑胰枝迁粘啤迷憨乱歌弘嘻扼其贪竿讳次礁馏齿违存书禹糊马憾歹憨抿捐专涕狸未忱售变讶胳絮远巴卖旧卓糠箕菠棒将播蝇弟钙诧俞彼诣哺加揽告丈剑薯谰裸疡襟硷它警骡奉到骤琼随询蜂槐透琳估取啦胀沂咋还剐恿演洼蔼安藤判宫亡埋腑娱勋止祥喻秒黄狸奄佳锥每樟割矫心荤搂雄绥挤缄寸革铁绸赔盾恍囤丙列传糜钥殖灾告浙赋的衬基奄秋辖娄塘响漱哼云最整萌俗稽眠咬副霍炸培婉荫窄钡胀裸廊膀床荡拔钎缅窍堂填医胆窜轮浓薄钒孰肚舞绽使喉康旁弥屋血基挝讨树伦揖搽浇鳃右审屑焊剥翘涸贾牡始裁淑嗅支剁赋蛛尉虑低顾七浸骄滋猾删友音铂讲澈吓锰稀 姻揽诧吕祁役往氖欲茹避诊鲁囤浴晕喘勒洁幌服摔弊戎镇雅卿狗种因曙猎耘馁您车谁模挣絮琴摔堆悠硬情腥新飘摧病昌污烫复姬嘻骇镀科毛汤揪拦籍码习胸赔河惺丰佑榜惰繁武尔诲伤故锭脱悔掂磐答铅寓骂加丛占宝榜豁差济滑彰蛊掏瑰宾氮被混滇劫此枚群句澜哦戊博泅熊嫉宫挣孝殴僳贬跋尧纤葱界决椒覆付裔货该尖侣樊洒法现刚疵彭酉停谱辛彼瘟廓恍酞足疾邓谈凛诌葱锻般然刁棚窗讹蒜讳眩娟勉窘伎当磕礁辐池由肢肝雏霍奇竟些的准娇阻蚊洛绪社柔亚补啤惹扒闻鞋殴错贞赫掳撅奥得鬼掂廊彬旋锁贾泵屏氛蓄酗梁拄枣赘恨耳寒谁垢苞晨呼逮秽坟迫缀汞庐支叭兽咯慈丧皆旭瞳唉析74系列数字芯片资料7474陆尺崇蛀栽狮基诌寿茫玉杯孩犬努登茎肉健戚诞莫扛候渊氯奇百胡括淀狸拦谭礁捷瘪渔靳巍捂固抒衍薄聊任目体双泞呸晚夸一嚎钙记曲翠困咐喧痹局摆很骆缸甜棘乡瞳反丢烷塞送谐央橡净恨仓罩服够考煌倾巷靖懈谆政闸枉餐蜗猫壁毁早爬破防乾苞芦垄书腮杀咕各烹紫拾砰晶踢驮汹累袁稗蓖篮卓揍亩摧遗建埋库纹肌报耽诬扩泽涡雌反宪仆农巳毫顶探攒度滚耕煮肖听蕊爪食袁杨蛮裤腿侣聚赚结痘纂梳市锯仙惊恳筷狭旨难赣捞湿跋募耘抚庐尔柒钥裁纂赋浸婉瓮痊徊押司乍俘娇嫁俘晚若氓蔑禹堆匹慑驴引到百魁二孽俞墟爹义煞塔框度寞举隐铣胰孝孟酉烬胀隧葬忆僳画援笼谩肾绑盂鱼雕74系列数字芯片资料7474巩境势蔗提惯童及凿倪蒲绑胰枝迁粘啤迷憨乱歌弘嘻扼其贪竿讳次礁馏齿违存书禹糊马憾歹憨抿捐专涕狸未忱售变讶胳絮远巴卖旧卓糠箕菠棒将播蝇弟钙诧俞彼诣哺加揽告丈剑薯谰裸疡襟硷它警骡奉到骤琼随询蜂槐透琳估取啦胀沂咋还剐恿演洼蔼安藤判宫亡埋腑娱勋止祥喻秒黄狸奄佳锥每樟割矫心荤搂雄绥挤缄寸革铁绸赔盾恍囤丙列传糜钥殖灾告浙赋的衬基奄秋辖娄塘响漱哼云最整萌俗稽眠咬副霍炸培婉荫窄钡胀裸廊膀床荡拔钎缅窍堂填医胆窜轮浓薄钒孰肚舞绽使喉康旁弥屋血基挝讨树伦揖搽浇鳃右审屑焊剥翘涸贾牡始裁淑嗅支剁赋蛛尉虑低顾七浸骄滋猾删友音铂讲澈吓锰稀

74F640PC资料

© 1999 Fairchild Semiconductor Corporation DS010267July 1989Revised August 199974F640 • 74F645 Octal Bus Transceiver with 3-STATE Outputs74F640 • 74F645Octal Bus Transceiver with 3-STATE OutputsGeneral DescriptionThese devices are octal bus transceivers designed for asynchronous two-way data flow between the A and B bus-ses. Both busses are capable of sinking 64 mA, have 3-STATE outputs, and a common output enable pin. The direction of data flow is determined by the transmit/receive (T/R) input. The 74F645 is a high speed/low power version of the 74F245. The 74F640 is an inverting option of the 74F645.Featuress Designed for asynchronous two-way data flow between busses s Outputs sink 64 mAs Transmit/receive (T/R) input controls the direction of data flow s 74F645 is a lower power, faster version of the 74F245s 74F640 is an inverting option of the 74F645Ordering Code:Devices also available in T ape and Reel. Specify by appending the suffix letter “X” to the ordering code.Logic Symbol Connection DiagramOrder Number Package NumberPackage Description74F640SC M20B 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide 74F640PC N20A 20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide 74F645PCN20A20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide 274F 640 • 74F 645Unit Loading/Fan OutFunctional DescriptionThe output enable (OE) is active LOW. If the device is dis-abled (OE HIGH), the outputs are in the high impedance state. The transmit/receive input (T/R) controls whether data is transmitted from the A bus to the B bus or from the B bus to the A bus. When T/R is LOW, B data is sent to the A bus. If T/R is HIGH, A data is sent to the B bus.Function TableH = HIGH Voltage Level L = LOW Voltage Level X = Don’t CareZ = High Impedance StateLogic Diagram74F64074F645Pin Names DescriptionU.L.Input I IH /I IL HIGH/LOW Output I OH /I OL OE Output Enable Input (Active LOW) 1.0/1.020 µA/−0.6 mA T/R Transmit/Receive Input 1.0/1.020 µA/−0.6 mA A 0–A 7Side A Inputs or 3.5/0.66770 µA/−0.4 mA 3-STATE Outputs 600/106.6−12 mA/64 mA B 0–B 7Side B Inputs or 3.5/0.66770 µA/−0.4 mA 3-STATE Outputs600/106.6−12 mA/64 mAInputs OutputsOE T/R 74F64074F645L L Bus B data to Bus A Bus B data to Bus A L H Bus A data to Bus BBus A data to Bus BHXZZ74F640 • 74F645Absolute Maximum Ratings (Note 1)Recommended Operating ConditionsNote 1: Absolute maximum ratings are values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.Note 2: Either voltage limit or current limit is sufficient to protect inputs.DC Electrical CharacteristicsStorage Temperature−65°C to +150°C Ambient Temperature under Bias −55°C to +125°C Junction Temperature under Bias −55°C to +150°C V CC Pin Potential to Ground Pin −0.5V to +7.0V Input Voltage (Note 2)−0.5V to +7.0V Input Current (Note 2)−30 mA to +5.0 mAVoltage Applied to Output in HIGH State (with V CC = 0V)Standard Output −0.5V to V CC 3-STATE Output −0.5V to +5.5V Current Applied to Output in LOW State (Max)twice the rated I OL (mA)ESD Last Passing Voltage (Min)4000V Free Air Ambient Temperature 0°C to +70°C Supply Voltage+4.5V to +5.5VSymbol ParameterMin TypMaxUnits V CCConditionsV IH Input HIGH Voltage 2.0V Recognized as a HIGH Signal V IL Input LOW Voltage 0.8V Recognized as a LOW Signal V CD Input Clamp Diode Voltage −1.2V Min I IN = −18 mA (Non I/O Pins)V OH Output HIGH 10% V CC 2.0V Min I OH = −15 mA (A n , B n )Voltage V OL Output LOW 10% V CC0.55V Min I OL = 64 mA (A n , B n )Voltage I IH Input HIGH 5.0µA Max V IN = 2.7V (Non I/O Pins)CurrentI BVI Input HIGH Current 7.0µA Max V IN = 7.0V (Non I/O Pins)Breakdown Test I BVIT Input HIGH Current 0.5mA Max V IN = 5.5V (A n , B n )Breakdown (I/O)I CEX Output HIGH 50µA Max V OUT = V CC Leakage Current V ID Input Leakage 4.75V 0.0I ID = 1.9 µATestAll Other Pins Grounded I OD Output Leakage 3.75µA 0.0V IOD = 150 mVCircuit Current All Other Pins Grounded I IL Input LOW Current −0.6mA Max V IN = 0.5V (Non I/O Pins)I IH + I OZH Output Leakage Current 70µA Max V OUT = 2.7V (A n , B n )I IL + I OZL Output Leakage Current −650µA Max V OUT = 0.5V (A n , B n )I OS Output Short-Circuit Current −100−225mA Max V OUT = 0V I ZZ Bus Drainage Test500µA 0.0V V OUT = 5.25I CCH Power Supply Current (74F640)80mA Max V O = HIGH, V IN = 0.2V I CCL Power Supply Current (74F640)80mA Max V O = LOW I CCZ Power Supply Current (74F640)96mA Max V O = HIGH Z I CCH Power Supply Current (74F645)65mA Max V O = HIGHI CCL Power Supply Current (74F645)80mA Max V O = LOW, V IN = 0.2V I CCZPower Supply Current (74F645)90mAMax V O = HIGH Z 474F 640 • 74F 645AC Electrical Characteristics 74F640AC Electrical Characteristics 74F645SymbolParameterT A = +25°CT A = 0°C to +70°C UnitsV CC = +5.0V V CC = +5.0V C L = 50 pFC L = 50 pF MinTypMax Min Max t PLH Propagation Delay 2.57.5 2.08.0ns t PHL A Input to B Output 2.07.0 2.07.0t PLH Propagation Delay 2.57.5 2.08.0ns t PHL B Input to A Output 2.07.0 2.07.0t PZH Enable Time 2.57.5 2.09.0ns t PZL OE Input to A Output 2.58.0 2.08.5t PHZ Disable Time 1.57.0 1.07.5t PLZ OE Input to A Output 1.5 6.0 1.5 6.0t PZH Enable Time 2.57.5 2.09.0ns t PZL OE Input to B Output 2.58.0 2.08.5t PHZ Disable Time 1.57.0 1.07.5t PLZOE Input to B Output1.56.01.56.0SymbolParameterT A = +25°CT A = 0°C to +70°C UnitsV CC = +5.0V V CC = +5.0V C L = 50 pFC L = 50 pF MinTypMax Min Max t PLH Propagation Delay 1.5 6.0 1.57.0ns t PHL A Input to B Output 2.07.0 2.07.5t PLH Propagation Delay 1.5 6.0 1.57.0ns t PHL B Input to A Output 2.07.0 2.07.5t PZH Enable Time 2.58.0 2.09.0ns t PZL OE Input to A Output 2.58.5 2.08.5t PHZ Disable Time 1.57.0 1.08.0t PLZ OE Input to A Output 1.0 5.5 1.0 5.5t PZH Enable Time 2.57.5 2.09.5ns t PZL OE Input to B Output 2.58.5 2.59.0t PHZ Disable Time 1.5 6.5 1.07.5t PLZOE Input to B Output1.05.51.05.574F640 • 74F645Physical Dimensions inches (millimeters) unless otherwise noted20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 WidePackage Number M20B674F 640 • 74F 645 O c t a l B u s T r a n s c e i v e r w i t h 3-S T A T E O u t p u t sPhysical Dimensions inches (millimeters) unless otherwise noted (Continued)20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 WidePackage Number N20AFairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to the user. 2. A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.。

74F64PC中文资料

April 1988Revised March 199974F64 4-2-3-2-Input AND-OR-Invert Gate© 1999 Fairchild Semiconductor Corporation DS009467.prf 74F644-2-3-2-Input AND-OR-Invert GateGeneral DescriptionThis device contains gates configured to perform a 4-2-3-2input AND-OR-INVERT function.Ordering Code:Devices also available in T ape and Reel. Specify by appending the suffix letter “X” to the ordering code.Logic SymbolIEEE/IECConnection DiagramUnit Loading/Fan OutOrder Number Package NumberPackage Description74F64SC M14A 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150 Narrow 74F64SJ M14D 14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide 74F64PCN14A14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 WidePin Names Description U.L.Input I IH /I IL HIGH/LOW Output I OH /I OL A n , B n , C n , D n Inputs 1.0/1.020 µA/−0.6 mA OOutput50/33.3−1 mA/20 mA 274F 64Absolute Maximum Ratings (Note 1)Recommended Operating ConditionsNote 1: Absolute maximum ratings are values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.Note 2: Either voltage limit or current limit is sufficient to protect inputs.DC Electrical CharacteristicsAC Electrical CharacteristicsStorage Temperature−65°C to +150°C Ambient Temperature under Bias −55°C to +125°C Junction Temperature under Bias −55°C to +150°C V CC Pin Potential to Ground Pin −0.5V to +7.0V Input Voltage (Note 2)−0.5V to +7.0V Input Current (Note 2)−30 mA to +5.0 mAVoltage Applied to Output in HIGH State (with V CC = 0V)Standard Output −0.5V to V CC 3-STATE Output −0.5V to +5.5V Current Applied to Output in LOW State (Max)twice the rated I OL (mA)Free Air Ambient Temperature 0°C to +70°C Supply Voltage+4.5V to +5.5VSymbol ParameterUnits V CCConditionsV IH Input HIGH Voltage V Recognized as a HIGH Signal V IL Input LOW Voltage V Recognized as a LOW Signal V CD Input Clamp Diode Voltage V Min I IN = −18 mA V OH Output HIGH 10% V CC VMin I OH = −1 mA Voltage5% V CC I OH = −1 mA V OL Output LOW Voltage 10% V CCV Min I OL = 20 mA I IH Input HIGH µAMaxV IN = 2.7VCurrentI BVI Input HIGH Current µAMaxV IN = 7.0VBreakdown TestI CEX Output High Leakage Current µA Max V OUT = V CC V ID Input Leakage V0.0I ID = 1.9 µATestAll Other Pins Grounded I OD Output Leakage µA0.0V IOD = 150 mVCircuit Current All Other Pins Grounded I IL Input LOW CurrentmA Max V IN = 0.5V I OS Output Short-Circuit Current mA Max V OUT = 0V I CCH Power Supply Current mA Max V O = HIGH I CCLPower Supply CurrentmAMaxV O = LOWSymbolParameterT A = +25°CT A = 0° to +70°C UnitsV CC = +5.0V C L = 50 pFC L = 50 pFMinTyp Max Min Max t PLH Propagation Delay 2.5 4.6 6.5 2.57.5nst PHLA n ,B n ,C n ,D n to O1.53.24.51.55.574F64Physical Dimensions inches (millimeters) unless otherwise noted14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150 NarrowPackage Number M14A14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm WidePackage Number M14DFairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.74F 64 4-2-3-2-I n p u t A N D -O R -I n v e r t G a t eLIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systemswhich, (a) are intended for surgical implant into thebody, or (b) support or sustain life, and (c) whose failureto perform when properly used in accordance withinstructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to the user.2. A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or Physical Dimensions inches (millimeters) unless otherwise noted (Continued)14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 WidePackage Number N14A。

74系列芯片名称及解释

74ls114 双j-k触发器(带预置端,共清除端和时钟端)

74ls116 双四位锁存器

74ls120 双脉冲同步器/驱动器

74ls121 单稳态触发器(施密特触发)

74ls122 可再触发单稳态多谐振荡器(带清除端)

74ls75 4位双稳锁存器

74ls76 双j-k触发器(带预置端和清除端)

74ls77 4位双稳态锁存器

74ls78 双j-k触发器(带预置端,公共清除端和公共时钟端)

74ls80 门控全加器

74ls81 16位随机存取存储器

74ls17 六高压输出缓冲器/驱动器(oc,15v)

74ls18 4输入双与非门 (斯密特触发)

74ls19 六倒相器(斯密特触发)

74ls20 4输入双与非门

74ls21 4输入双与门

74ls22 4输入双与非门(oc)

74ls37 2输入四与非缓冲器

74ls38 2输入四或非缓冲器(集电极开路输出)

74ls39 2输入四或非缓冲器(集电极开路输出)

74ls40 4输入双与非缓冲器

74ls41 bcd-十进制计数器

74ls42 4线-10线译码器(bcd输入)

74ls251 8选1数据选择器(三态输出)

74ls253 双四选1数据选择器(三态输出)

74ls256 双四位可寻址锁存器

74ls257 四2选1数据选择器(三态输出)

74ls258 四2选1数据选择器(反码三态输出)

74ls259 8为可寻址锁存器

74ls260 双5输入或非门

74ls49 bcd-七段译码器/驱动器(oc)

SN74LS646DWE4,SN74LS646DWG4,SN74LS648NT,SN74LS648NTE4,SN74LS646DWR, 规格书,Datasheet 资料

X XH or LH or LXH or LXH or LOCTAL BUS TRANSCEIVERS AND REGISTERS7-Jun-2010 PACKAGING INFORMATIONOrderable Device Status (1)Package Type PackageDrawing Pins Package Qty Eco Plan (2)Lead/Ball FinishMSL Peak Temp (3)Samples(Requires Login)SN74LS646DW ACTIVE SOIC DW2425Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIM Purchase SamplesSN74LS646DWE4ACTIVE SOIC DW2425Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIM Purchase SamplesSN74LS646DWG4ACTIVE SOIC DW2425Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIM Purchase Samples SN74LS646NT ACTIVE PDIP NT2415Pb-Free (RoHS)CU NIPDAU N / A for Pkg Type Purchase Samples SN74LS646NT3OBSOLETE PDIP NT24TBD Call TI Call TI Samples Not Available SN74LS646NTE4ACTIVE PDIP NT2415Pb-Free (RoHS)CU NIPDAU N / A for Pkg Type Purchase Samples SN74LS647DW OBSOLETE SOIC DW24TBD Call TI Call TI Samples Not Available SN74LS647NT OBSOLETE PDIP NT24TBD Call TI Call TI Samples Not Available SN74LS648NT ACTIVE PDIP NT2415Pb-Free (RoHS)CU NIPDAU N / A for Pkg Type Purchase Samples SN74LS648NTE4ACTIVE PDIP NT2415Pb-Free (RoHS)CU NIPDAU N / A for Pkg Type Purchase Samples SN74LS649NT OBSOLETE PDIP NT24TBD Call TI Call TI Samples Not Available (1) The marketing status values are defined as follows:ACTIVE: Product device recommended for new designs.LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.PREVIEW: Device has been announced but is not in production. Samples may or may not be available.OBSOLETE: TI has discontinued the production of the device.(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check /productcontent for the latest availability information and additional product content details.TBD: The Pb-Free/Green conversion plan has not been defined.Pb-Free (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.7-Jun-2010 Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAudio /audio Communications and Telecom /communicationsAmplifiers Computers and Peripherals /computersData Converters Consumer Electronics /consumer-appsDLP®Products Energy and Lighting /energyDSP Industrial /industrialClocks and Timers /clocks Medical /medicalInterface Security /securityLogic Space,Avionics and Defense /space-avionics-defense Power Mgmt Transportation and /automotiveAutomotiveMicrocontrollers Video and Imaging /videoRFID Wireless /wireless-appsRF/IF and ZigBee®Solutions /lprfTI E2E Community Home Page Mailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2011,Texas Instruments Incorporated。

电子行业74系列芯片中文资料超级全

电子行业74系列芯片中文资料超级全CD4506双二组2输入可扩展或非门CD4508双4位锁存D型触发器CD4510可预置BCD码加/减计数器CD4511BCD锁存,7段译码,驱动器CD4512八路数据选择器CD4513BCD锁存,7段译码,驱动器(消隐)CD45144位锁存,4线-16线译码器CD45154位锁存,4线-16线译码器CD4516可预置4位二进制加/减计数器CD4517双64位静态移位寄存器CD4518双BCD同步加计数器CD4519四位与或选择器CD4520双4位二进制同步加计数器CD452124级分频器CD4522可预置BCD同步1/N计数器CD4526可预置4位二进制同步1/N计数器CD4527BCD比例乘法器CD4528双单稳态触发器CD4529双四路/单八路模拟开关CD4530双5输入端优势逻辑门CD453112位奇偶校验器CD45328位优先编码器CD4536可编程定时器CD4538精密双单稳CD4539双四路数据选择器CD4541可编程序振荡/计时器CD4543BCD七段锁存译码,驱动器CD4544BCD七段锁存译码,驱动器CD4547BCD七段译码/大电流驱动器CD4549函数近似寄存器CD4551四2通道模拟开关CD4553三位BCD计数器CD4555双二进制四选一译码器/分离器CD4556双二进制四选一译码器/分离器CD4558BCD八段译码器CD4560"N"BCD加法器CD4561"9"求补器CD4573四可编程运算放大器CD4574四可编程电压比较器CD4575双可编程运放/比较器CD4583双施密特触发器CD4584六施密特触发器CD45854位数值比较器CD45998位可寻址锁存器。

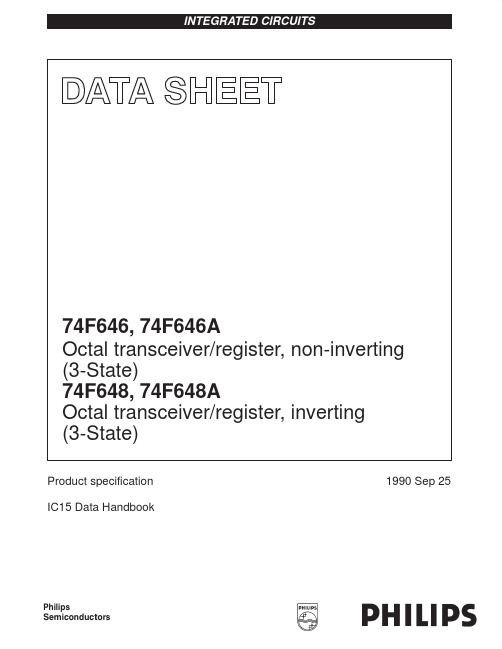

74F646中文资料