ADM9690ARNZ中文资料

MEMORY存储芯片ADM708ARZ-REEL中文规格书

Data SheetADuM1410/ADuM1411/ADuM1412FEATURESLow power operation 5 V operation1.3 mA per channel maximum at 0 Mbps to 2 Mbps 4.0 mA per channel maximum at 10 Mbps 3 V operation0.8 mA per channel maximum at 0 Mbps to 2 Mbps 1.8 mA per channel maximum at 10 Mbps Bidirectional communication 3 V/5 V level translationHigh temperature operation: 105°C Up to 10 Mbps data rate (NRZ)Programmable default output stateHigh common-mode transient immunity: >25 kV/µs 16-lead, RoHS compliant, SOIC wide body package Safety and regulatory approvalsUL recognition: 3750 V rms for 1 minute per UL 1577 CSA Component Acceptance Notice 5A VDE certificate of conformityDIN V VDE V 0884-10 (VDE V 0884-10): 2006-12 V IORM = 560 V peakTÜV approval: IEC/EN 60950-1V GND V V V V GND DD22OA OB OC OD2206580-001Figure 1. ADuM1410V GND V V V V CTRL GND DD22OA OB OC ID2206580-002Figure 2. ADuM1411V GND V V V V CTRL GNDDD22OA OB IC ID 2206580-003APPLICATIONSGeneral-purpose multichannel isolation SPI interface/data converter isolation RS-232/RS-422/RS-485 transceivers Industrial field bus isolationGENERAL DESCRIPTIONThe ADuM1410/ADuM1411/ADuM14121 are four-channel digital isolators based on Analog Devices, Inc., i Coupler® technology. Combining high speed CMOS and monolithic air core transformer technologies, these isolation components provide outstanding performance characteristics superior to alternatives such as optocoupler devices.By avoiding the use of LEDs and photodiodes, i Coupler devices remove the design difficulties commonly associated with opto-couplers. The usual concerns that arise with optocouplers, such as uncertain current transfer ratios, nonlinear transfer functions, and temperature and lifetime effects, are eliminated with the simple i Coupler digital interfaces and stable performance characteristics. The need for external drivers and other discrete components is eliminated with these i Coupler products. Furthermore, i Coupler1Protected by U.S. Patents 5,952,849; 6,873,065; 6,903,578; and 7,075,329.Figure 3. ADuM1412devices consume one-tenth to one-sixth the power of optocou-plers at comparable signal data rates.The ADuM1410/ADuM1411/ADuM1412 isolators provide four independent isolation channels in a variety of channel configu-rations and data rates (see the Ordering Guide) up to 10 Mbps. All models operate with the supply voltage on either side ranging from 2.7 V to 5.5 V , providing compatibility with lower voltage systems as well as enabling voltage translation functionality across the isolation barrier. All products also have a default output control pin. This allows the user to define the logic state the outputs are to adopt in the absence of the input power. Unlike other optocoupler alternatives, the ADuM1410/ADuM1411/ ADuM1412 isolators have a patented refresh feature that ensures dc correctness in the absence of input logic transitions and during power-up/power-down conditions.Data Sheet ADuM1410/ADuM1411/ADuM1412 SPECIFICATIONSELECTRICAL CHARACTERISTICS—5 V OPERATION4.5 V ≤ V DD1 ≤5.5 V, 4.5 V ≤ V DD2 ≤ 5.5 V; all minimum/maximum specifications apply over the entire recommended operation range, unless otherwise noted; all typical specifications are at T A = 25°C, V DD1 = V DD2 = 5 V. All voltages are relative to their respective ground. Table 1.Parameter Symbol Min Typ Max Unit Test Conditions/CommentsDC SPECIFICATIONSInput Supply Current per Channel,QuiescentI DDI (Q)0.50 0.73 mAOutput Supply Current per Channel,QuiescentI DDO (Q)0.38 0.53 mAADuM1410, Total Supply Current,Four Channels1DC to 2 MbpsV DD1 Supply Current I DD1 (Q) 2.4 3.2 mA DC to 1 MHz logic signal frequency V DD2 Supply Current I DD2 (Q) 1.2 1.6 mA DC to 1 MHz logic signal frequency10 Mbps (BRWZ Version Only)V DD1 Supply Current I DD1 (10)8.8 12 mA 5 MHz logic signal frequency V DD2 Supply Current I DD2 (10) 2.8 4.0 mA 5 MHz logic signal frequency ADuM1411, Total Supply Current,Four Channels1DC to 2 MbpsV DD1 Supply Current I DD1 (Q) 2.2 2.8 mA DC to 1 MHz logic signal frequency V DD2 Supply Current I DD2 (Q) 1.8 2.4 mA DC to 1 MHz logic signal frequency10 Mbps (BRWZ Version Only)V DD1 Supply Current I DD1 (10) 5.4 7.6 mA 5 MHz logic signal frequency V DD2 Supply Current I DD2 (10) 3.8 5.3 mA 5 MHz logic signal frequency ADuM1412, Total Supply Current,Four Channels1DC to 2 MbpsV DD1 or V DD2 Supply Current I DD1 (Q), I DD2(Q)2.0 2.6 mA DC to 1 MHz logic signal frequency10 Mbps (BRWZ Version Only)V DD1 or V DD2 Supply Current I DD1 (10), I DD2 (10) 4.6 6.5 mA 5 MHz logic signal frequencyAll ModelsInput Currents I IA, I IB, I IC,I ID, I CTRL1,I CTRL2, I DISABLE −10 +0.01 +10µA 0 V ≤ V IA, V IB, V IC, V ID ≤ V DD1 or V DD2,0 V ≤ V CTRL1, V CTRL2 ≤ V DD1 or V DD2,0 V ≤ V DISABLE ≤ V DD1Logic High Input Threshold V IH 2.0 V Logic Low Input Threshold V IL 0.8 VLogic High Output Voltages V OAH, V OBH,V OCH, V ODH (V DD1 or V DD2) − 0.1 5.0 V I Ox = −20 µA, V Ix = V IxH (V DD1 or V DD2) − 0.4 4.8 V I Ox = −4 mA, V Ix = V IxHLogic Low Output Voltages V OAL, V OBL,V OCL, V ODL0.0 0.1 V I Ox = 20 µA, V Ix = V IxL0.04 0.1 V I Ox = 400 µA, V Ix = V IxL0.2 0.4 V I Ox = 4 mA, V Ix = V IxL Rev. M | Page of 22ADuM1410/ADuM1411/ADuM1412 Data Sheet Parameter Symbol Min Typ Max Unit Test Conditions/Comments SWITCHING SPECIFICATIONSADuM1410ARWZ/ADuM1411ARWZ/ADuM1412ARWZMinimum Pulse Width2PW 1000 ns C L = 15 pF, CMOS signal levels Maximum Data Rate3 1 Mbps C L = 15 pF, CMOS signal levels Propagation Delay4t PHL, t PLH20 65 100 ns C L = 15 pF, CMOS signal levels Pulse Width Distortion, |t PLH − t PHL|4 PWD 40 ns C L = 15 pF, CMOS signal levels Propagation Delay Skew5t PSK50 ns C L = 15 pF, CMOS signal levels Channel-to-Channel Matching6t PSKCD/OD50 ns C L = 15 pF, CMOS signal levels ADuM1410BRWZ/ADuM1411BRWZ/ADuM1412BRWZMinimum Pulse Width2PW 100 ns C L = 15 pF, CMOS signal levels Maximum Data Rate310 Mbps C L = 15 pF, CMOS signal levels Propagation Delay4t PHL, t PLH20 30 50 ns C L = 15 pF, CMOS signal levels Pulse Width Distortion, |t PLH − t PHL|4 PWD 5 ns C L = 15 pF, CMOS signal levels Change vs. Temperature 5 ps/°C C L = 15 pF, CMOS signal levels Propagation Delay Skew5t PSK30 ns C L = 15 pF, CMOS signal levels Channel-to-Channel Matching,Codirectional Channels6t PSKCD 5 ns C L = 15 pF, CMOS signal levelsChannel-to-Channel Matching,Opposing-Directional Channels6t PSKOD 6 ns C L = 15 pF, CMOS signal levelsAll ModelsOutput Rise/Fall Time (10% to 90%) t R/t F 2.5 ns C L = 15 pF, CMOS signal levelsCommon-Mode Transient Immunity at Logic High Output7|CM H| 25 35 kV/µs V Ix = V DD1 or V DD2, V CM = 1000 V,transient magnitude = 800 VCommon-Mode Transient Immunity at Logic Low Output7 |CM L| 25 35 kV/µs V Ix = 0 V, V CM = 1000 V,transient magnitude = 800 VRefresh Rate f r 1.2 MbpsInput Enable Time8t ENABLE 2.0 µs V IA, V IB, V IC, V ID = 0 V or V DD1 Input Disable Time8t DISABLE 5.0 µs V IA, V IB, V IC, V ID = 0 V or V DD1Input Dynamic Supply Current per Channel9I DDI (D)0.12 mA/MbpsOutput Dynamic Supply Current per Channel9I DDO (D)0.04 mA/Mbps1 The supply current values for all four channels are combined when running at identical data rates. Output supply current values are specified with no output load present. The supply current associated with an individual channel operating at a given data rate can be calculated as described in the Power Consumption section. See Figure 8 through Figure 10 for information on per-channel supply current as a function of data rate for unloaded and loaded conditions. See Figure 11 through Figure 15 for total V DD1 and V DD2 supply currents as a function of data rate for ADuM1410/ADuM1411/ADuM1412 channel configurations.2 The minimum pulse width is the shortest pulse width at which the specified pulse width distortion is guaranteed.3 The maximum data rate is the fastest data rate at which the specified pulse width distortion is guaranteed.4 t PHL propagation delay is measured from the 50% level of the falling edge of the V Ix signal to the 50% level of the falling edge of the V Ox signal. t PLH propagation delay is measured from the 50% level of the rising edge of the V Ix signal to the 50% level of the rising edge of the V Ox signal.5 t PSK is the magnitude of the worst-case difference in t PHL or t PLH that is measured between units at the same operating temperature, supply voltages, and output load within the recommended operating conditions.6 Codirectional channel-to-channel matching is the absolute value of the difference in propagation delays between any two channels with inputs on the same side of the isolation barrier. Opposing-directional channel-to-channel matching is the absolute value of the difference in propagation delays between any two channels with inputs on opposing sides of the isolation barrier.7 |CM H| is the maximum common-mode voltage slew rate that can be sustained while maintaining V O > 0.8 V DD2. |CM L| is the maximum common-mode voltage slew rate that can be sustained while maintaining V O < 0.8 V. The common-mode voltage slew rates apply to both rising and falling common-mode voltage edges. The transient magnitude is the range over which the common mode is slewed.8 Input enable time is the duration from when V DISABLE is set low until the output states are guaranteed to match the input states in the absence of any input data logic transitions. If an input data logic transition within a given channel does occur within this time interval, the output of that channel reaches the correct state within the much shorter duration as determined by the propagation delay specifications within this data sheet. Input disable time is the duration from when V DISABLE is set high until the output states are guaranteed to reach their programmed output levels, as determined by the CTRL2 logic state (see Table 14).9 Dynamic supply current is the incremental amount of supply current required for a 1 Mbps increase in signal data rate. See Figure 8 through Figure 10 for information on per-channel supply current for unloaded and loaded conditions. See the Power Consumption section for guidance on calculating the per-channel supply current for a given data rate.Rev. M | Page of 22Data Sheet ADuM1410/ADuM1411/ADuM1412ELECTRICAL CHARACTERISTICS—3 V OPERATION2.7 V ≤ V DD1 ≤3.6 V, 2.7 V ≤ V DD2 ≤ 3.6 V; all minimum/maximum specifications apply over the entire recommended operation range, unless otherwise noted; all typical specifications are at T A = 25°C, V DD1 = V DD2 = 3.0 V. All voltages are relative to their respective ground. Table 2.Parameter Symbol Min Typ Max Unit Test Conditions/CommentsDC SPECIFICATIONSInput Supply Current per Channel,QuiescentI DDI (Q)0.25 0.38 mAOutput Supply Current per Channel,QuiescentI DDO (Q)0.19 0.33 mAADuM1410, Total Supply Current,Four Channels1DC to 2 MbpsV DD1 Supply Current I DD1 (Q) 1.2 1.6 mA DC to 1 MHz logic signalfrequency V DD2 Supply Current I DD2 (Q)0.8 1.0 mA DC to 1 MHz logic signalfrequency10 Mbps (BRWZ Version Only)V DD1 Supply Current I DD1 (10) 4.5 6.5 mA 5 MHz logic signal frequency V DD2 Supply Current I DD2 (10) 1.4 1.8 mA 5 MHz logic signal frequency ADuM1411, Total Supply Current,Four Channels1DC to 2 MbpsV DD1 Supply Current I DD1 (Q) 1.0 1.9 mA DC to 1 MHz logic signal frequency V DD2 Supply Current I DD2 (Q)0.9 1.7 mA DC to 1 MHz logic signal frequency10 Mbps (BRWZ Version Only)V DD1 Supply Current I DD1 (10) 3.1 4.5 mA 5 MHz logic signal frequency V DD2 Supply Current I DD2 (10) 2.1 3.0 mA 5 MHz logic signal frequency ADuM1412, Total Supply Current,Four Channels1DC to 2 MbpsV DD1 or V DD2 Supply Current I DD1 (Q), I DD2 (Q) 1.0 1.8 mA DC to 1 MHz logic signal frequency10 Mbps (BRWZ Version Only)V DD1 or V DD2 Supply Current I DD1 (10), I DD2 (10) 2.6 3.8 mA 5 MHz logic signal frequencyAll ModelsInput Currents I IA, I IB, I IC, I ID,I CTRL1,I CTRL2, I DISABLE −10 +0.01 +10µA 0 V ≤ V IA, V IB, V IC, V ID ≤ V DD1 or V DD2,0 V ≤ V CTRL1, V CTRL2 ≤ V DD1 or V DD2,0 V ≤ V DISABLE ≤ V DD1Logic High Input Threshold V IH 1.6 V Logic Low Input Threshold V IL 0.4 VLogic High Output Voltages V OAH, V OBH,V OCH, V ODH (V DD1 or V DD2) − 0.1 3.0 V I Ox = −20 µA, V Ix = V IxH (V DD1 or V DD2) − 0.4 2.8 V I Ox = −4 mA, V Ix = V IxHLogic Low Output Voltages V OAL, V OBL,V OCL, V ODL0.0 0.1 V I Ox = 20 µA, V Ix = V IxL0.04 0.1 V I Ox = 400 µA, V Ix = V IxL0.2 0.4 V I Ox = 4 mA, V Ix = V IxL Rev. M | Page of 22ADuM1410/ADuM1411/ADuM1412 Data Sheet。

adm显卡

adm显卡

ADM显卡是一款性能卓越的图形处理器,广泛用于个人电脑和服务器中。

它采用了先进的架构和技术,能够提供高质量的图形渲染和流畅的游戏体验。

首先,ADM显卡采用了最新的GPU架构,具有更高的计算性能和更低的功耗。

它采用了多个计算单元和多个渲染引擎,能够在游戏中呈现更真实的光影效果和更细腻的细节。

无论是在画质还是在性能上,ADM显卡都能够提供卓越的表现。

其次,ADM显卡采用了先进的显存技术,可以提供更大的显存容量和更快的存取速度。

这意味着它可以更好地处理大规模的纹理和模型,让游戏画面更加细腻和真实。

而且,它还支持高帧率和高分辨率输出,让玩家能够享受更顺畅的游戏体验。

此外,ADM显卡还支持多显示器输出和多重显卡互联技术。

这意味着用户可以通过连接多个显示器来扩展工作区域,提高生产效率。

而且,ADM显卡还支持多卡并行处理,可以将多个显卡组合在一起,提供更强大的图形处理能力。

除了游戏方面,ADM显卡还被广泛应用于科学计算和人工智能领域。

它的并行计算能力和大容量显存可以为科学家和研究人员提供强大的计算支持。

而且,ADM显卡还支持CUDA和OpenCL等计算框架,为开发者提供了广阔的创造空间。

总的来说,ADM显卡以其强大的性能和先进的技术,在图形渲染和计算领域表现突出。

它不仅可以提供高质量的游戏画面

和流畅的游戏体验,还能够用于科学计算和人工智能。

无论是个人用户还是专业用户,ADM显卡都是一个值得考虑的选择。

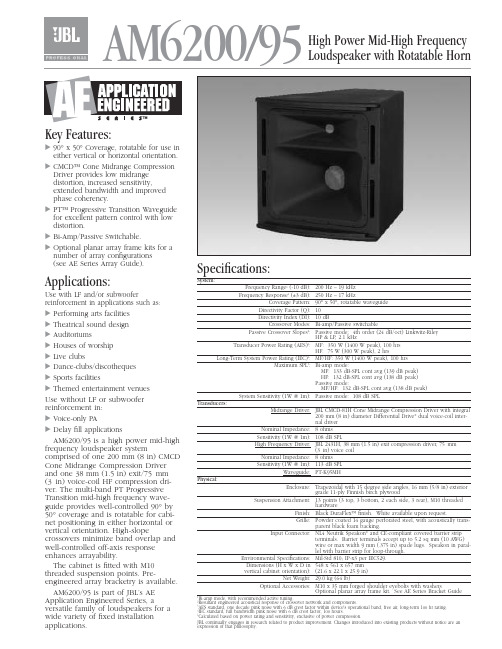

AM6200 95高功率中高频扬声器系统说明书

AM6200/95High Power Mid-High Frequency Loudspeaker with Rotatable HornKey Features:᭤90°x 50°Coverage, rotatable for use in either vertical or horizontal orientation. ᭤CMCD™ Cone Midrange Compression Driver provides low midrange distortion, increased sensitivity,extended bandwidth and improved phase coherency.᭤PT™ Progressive Transition Waveguide for excellent pattern control with low distortion.᭤Bi-Amp/Passive Switchable.᭤Optional planar array frame kits for a number of array configurations (see AE Series Array Guide).Applications:Use with LF and/or subwooferreinforcement in applications such as:᭤Performing arts facilities ᭤Theatrical sound design ᭤Auditoriums᭤Houses of worship ᭤Live clubs᭤Dance-clubs/discotheques ᭤Sports facilities᭤Themed entertainment venues Use without LF or subwoofer reinforcement in:᭤Voice-only PA᭤Delay fill applicationsAM6200/95 is a high power mid-high frequency loudspeaker systemcomprised of one 200 mm (8 in) CMCD Cone Midrange Compression Driver and one 38 mm (1.5 in) exit/75mm (3in) voice-coil HF compression dri-ver. The multi-band PT Progressive Transition mid-high frequency wave-guide provides well-controlled 90°by 50°coverage and is rotatable for cabi-net positioning in either horizontal or vertical orientation. High-slopecrossovers minimize band overlap and well-controlled off-axis response enhances arrayability.The cabinet is fitted with M10threaded suspension points. Pre-engineered array bracketry is available.AM6200/95 is part of JBL’s AE Application Engineered Series, aversatile family of loudspeakers for a wide variety of fixed installation applications.Specifications:System:Frequency Range 1(-10 dB):200 Hz – 19 kHz Frequency Response 1(±3 dB):250 Hz – 17 kHzCoverage Pattern:90°x 50°, rotatable waveguide Directivity Factor (Q):10Directivity Index (DI):10 dBCrossover Modes:Bi-amp/Passive switchablePassive Crossover Slopes 2:Passive mode: 4th order (24 dB/oct) Linkwitz-Riley HP & LP, 2.1 kHzTransducer Power Rating (AES)3:MF: 350 W (1400 W peak), 100 hrs HF: 75 W (300 W peak), 2 hrsLong-Term System Power Rating (IEC)4:MF/HF: 350 W (1400 W peak), 100 hrs Maximum SPL 5:Bi-amp mode:MF: 133 dB-SPL cont avg (139 dB peak)HF: 132 dB-SPL cont avg (138 dB peak)Passive mode:MF/HF: 132 dB-SPL cont avg (138 dB peak)System Sensitivity (1W @ 1m):Passive mode: 108 dB SPLTransducers:Midrange Driver:JBL CMCD-81H Cone Midrange Compression Driver with integral200 mm (8 in) diameter Differential Drive ®dual voice-coil inter-nal driverNominal Impedance:8 ohms Sensitivity (1W @ 1m):108 dB SPLHigh Frequency Driver:JBL 2431H, 38 mm (1.5 in) exit compression driver, 75mm(3in) voice coilNominal Impedance:8 ohms Sensitivity (1W @ 1m):113 dB SPLWaveguide:PT-K95MHPhysical:Enclosure:Trapezoidal with 15 degree side angles, 16 mm (5/8 in) exteriorgrade 11-ply Finnish birch plywoodSuspension Attachment:13 points (3 top, 3 bottom, 2 each side, 3 rear), M10 threadedhardwareFinish:Black DuraFlex™ finish. White available upon request.Grille:Powder coated 14 gauge perforated steel, with acoustically trans-parent black foam backing.Input Connector:NL4 Neutrik Speakon ®and CE-compliant covered barrier stripterminals. Barrier terminals accept up to 5.2 sq mm (10 AWG)wire or max width 9 mm (.375 in) spade lugs. Speakon in paral-lel with barrier strip for loop-through.Environmental Specifications:Mil-Std 810; IP-x3 per IEC529.Dimensions (H x W x D in 548 x 561 x 657 mm vertical cabinet orientation):(21.6 x 22.1 x 25.9 in)Net Weight:29.0 kg (64 lb)Optional Accessories: M10 x 35 mm forged shoulder eyebolts with washersOptional planar array frame kit. See AE Series Bracket GuideBi-amp mode, with recommended active tuning.Resultant engineered acoustical response of crossover network and components. AES standard, one decade pink noise with 6 dB crest factor within device's operational band, free air, long-term 100 hr rating.IEC standard, full bandwidth pink noise with 6 dB crest factor, 100 hours.Calculated based on power rating and sensitivity, exclusive of power compression.JBL continually engages in research related to product improvement. Changes introduced into existing products without notice are anexpression of that philosophy.᭤AM6200/95 High Power Mid-High Frequency Loudspeaker with Rotatable HornHorizontal 1/3 Octave PolarsSS AM6200/95CRP 5M 10/04᭤AM6200/95 High Power Mid-High Frequency Loudspeaker with Rotatable HornVertical 1/3 Octave PolarsJBL Professional8500 Balboa Boulevard, P.O. Box 2200Northridge, California 91329 U.S.A.©Copyright 2002 JBL ProfessionalAHarman International Company。

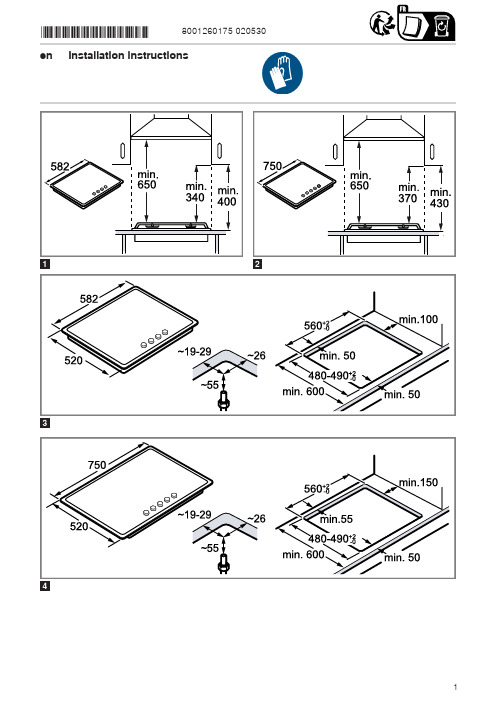

ID Gas Nz 气体蓄热器说明书

en Installation instructions1234enSafe installationFollow these safety instructions when installing the appliance.¡Read this instruction manual carefully.¡The images shown in these instructions are for guidance only.56¡The appliance can only be used safely if it is cor-rectly installed according to the safety instructions.The installer is responsible for ensuring that the appliance works perfectly at its installation loca-tion.WARNING ‒ Risk of explosion!Escaping gas may cause an explosion.▶All Installation, connection, regulating and conver-sion work to a different gas type must be carried out by an authorised professional while taking into account the respective applicable regulations and legal requirements as well as the regulations re-garding the local electricity and gas suppliers.Special attention must be paid to the provisions and guidelines that are applicable for the ventila-tion. For conversion work to a different gas type,we recommend that you call the after-sales ser-vice.¡Ensure that the kitchen is sufficiently ventilated, in particular when operating the gas cooking appli-ance.¡Do not connect the appliance to an exhaust gas system for combustion products.¡Never install the appliance in boats or in vehicles.¡The warranty applies only when using the appli-ance as intended.¡Before installing the appliance, check that the local conditions of the supplier are compatible with the appliance settings specified on the rating plate (type of gas and pressure, power, voltage).¡Secure the power cord to the cabinet to prevent it from touching hot parts of the oven or hob.¡Before any work is carried out on the appliance,switch off the power supply and the gas supply.¡Connect the appliance to the power supply using the earth.¡Do not make any changes to the inside of the ap-pliance. If required, contact our technical cus-tomer service.Before installing¡This appliance is a class 3 appliance in accord-ance with the EN 30-1-1 standard for gas appli-ances: Built-in appliance.¡The unit in which the appliance is installed must be stable and secured appropriately.¡The units in the vicinity of the appliance, the lamin-ated panels and the adhesive with which they are secured must be made of non-flammable, heat-resistant materials.¡Do not install this appliance above refrigerators,washing machines, dishwashers or similar.¡The appliance must only be installed on an oven with forced ventilation. Check the dimensions of the oven in the installation instructions for the oven.¡If you install an oven underneath the hob, the work surface thickness may differ from the dimensions given in these instructions. Take note of the in-formation in the oven installation instructions.¡If you install an exhaust air fan or an extractorhood, refer to the installation instructions for these.Always observe the minimum vertical distance to the hob.→ Fig. 1, → Fig. 2Preparing the units¡Make a cut-out in the worktop with the required di-mensions.→ Fig. 3, → Fig. 4¡Seal the cut surfaces of wooden work surfaces with a special glue seal to protect them from mois-ture.¡If there is no built-in oven underneath the hob, in-sert a non-flammable separator (e.g. metal or ply-wood) at a distance of 10 mm from the hob. This prevents access to the underside of the hob. The distance from the intermediate floor to the mains connection for the appliance must be at least 10mm.→ Fig. 5, → Fig. 6Positioning the applianceNote: Do not use silicone to bond the appliance to the worktop.1.Position the hob with the upper side facing down on a flat, stable surface.2.Apply the adhesive seal supplied to the lower edge of the hob. The adhesive seal prevents the penetration of liquids.→ Fig. 73.Screw the brackets supplied into the specified po-sition so that they can turn freely.→ Fig. 84.If you install the appliance in a 480 mm wide niche, you must remove the spacer, which is pre-installed on the back of some models.→ Fig. 95.Turn the hob around and insert it into the recess.Insert the hob in the front of the recess.→ Fig. 106.Turn the brackets and tighten them fully.→ Fig. 11The position of the brackets depends on the work-top thickness.Removing the appliance1.Disconnect the appliance from the electricity andgas connections.2.Unscrew the brackets and proceed in reverse or-der.Connecting the gasObserve the country-specific guidelines.CAUTION ‒ Risk of explosion!A gas leakage may cause an explosion.▶If any connection is handled, check the seal.¡Arrange the gas connection so that the shut-off valve is accessible.¡Ensure that the information on the rating plate re-garding the gas type and gas pressure complies with the local connection conditions.¡Connect the appliance to a fixed gas pipe or a flexible metal pipe.¡The flexible metal pipe must not come into contact with the moving parts of the unit in which the ap-pliance is installed (e.g. a drawer) and must not be routed through any spaces which might be-come obstructed.¡Gas connection elbow on the appliance: R 1/2.¡Do not move or twist the gas connection elbow.Spare parts for gas connectionYou can obtain the gas connection parts from the technical customer service.Pipe10008508Gas connection R 1/2→ Fig. 12LPG rubber hose connection1.Replace the appliance's gas inlet elbow with the pipe that is supplied in the accessory bag.→ Fig. 13, → Fig. 142.Insert the rubber hose into the end of the pipe andtighten the screw on the hose clamp.→ Fig. 15Electrical connection¡This appliance is type Y: The connection cable must only be replaced by technical customer ser-vice and not by the user. The cable type and the minimum cross section must be respected.¡The hobs are supplied with a power cord with or without a plug.¡Only connect appliances that are fitted with a plug to a correctly installed socket with protective earth conductor.¡If the plug is not accessible to the user, an all-pole isolating safety switch with a minimum contactopening of 3 mm must be provided.→ Fig. 16Converting the gas typeIf the country's regulations allow, this appliance can be adapted to other types of gas, if these are listed on the rating plate.You can find the right parts in the bag that is sup-plied with the appliance or you can obtain them from customer service. The table → Fig. 22 shows the right combination for the relevant burner and gas type.¡2 - Inner flameAdjusting the taps1.Turn the rotary knobs to the minimum power posi-tion and pull them out.2.With the tip of the screwdriver, push down on theflexible rubber holder to access the bypass screw.→ Fig. 17Never remove the sealing ring. The sealing rings prevent liquids and dirt from finding their way into the appliance and impairing its ability to function properly.3.When adjusting the bypass screws (M), refer tothe table → Fig. 22.‒A: Firmly tighten the bypass screws.‒B: The bypass screws must be flush with the fit-ting.→ Fig. 18Replacing the nozzles1.Remove all pan supports, burner caps and distrib-utors.2.Replace the nozzles using the appropriate wrenchand tighten them carefully to guarantee the seal.→ Fig. 19, → Fig. 20, → Fig. 21Ensure that the nozzle does not become detached during removal or fastening.Reinstalling the appliance▶Install the appliance components in reverse order.Checking if equipment is working1.Check that turning the rotary knob between theposition for maximum power and the position for minimum power does not cause the burner to go out or result in backfire.2.If the gas flow from the burner is not correct, inthe table → Fig. 22, check whether the nozzle and the position of the bypass screw are correct.Documenting the gas type conversion▶Attach the sticker showing the new gas type near to the rating plate.78。

MEMORY存储芯片ADM706ARZ-REEL中文规格书

Data SheetADM706P /ADM706R /ADM706S /ADM706T , ADM708R /ADM708S /ADM708TFEATURESPrecision supply voltage monitor2.63 V (ADM706P , ADM706R , ADM708R ) 2.93 V (ADM706S , ADM708S )3.08 V (ADM706T , ADM708T ) 100 µA quiescent current 200 ms reset pulse widthDebounced manual reset input (MR ) Independent watchdog timer1.6 sec timeout (ADM706P , ADM706R , ADM706S , ADM706T ) Reset outputActive high (ADM706P )Active low (ADM706R , ADM706S , ADM706T )Both active high and active low (ADM708R , ADM708S , ADM708T )FUNCTIONAL BLOCK DIAGRAMSWATCHDOG INPUT (WDI)POWER-FAIL POWER-FAIL OUTPUT (PFO)WATCHDOG OUTPUT (WDO)*VOLTAGE REFERENCE = 2.63V (P/R), 2.93V (S), 3.08V (T)MR V CC06435-001Figure 1. ADM706P /ADM706R /ADM706S /ADM706TPOWER-FAIL *VOLTAGE REFERENCE = 2.63V (R), 2.93V (S), 3.08V (T)MR V CC06435-002POWER-FAILOUTPUT (PFO)Voltage monitor for power fail or low battery warning Guaranteed RESET valid with V CC = 1 VSuperior upgrade for MAX706P/R/S/T, MAX708R/S/TAPPLICATIONSMicroprocessor systems Computers ControllersIntelligent instrumentsCritical microprocessor monitoring Battery operated systems Portable instrumentsGENERAL DESCRIPTIONThe ADM706P /ADM706R /ADM706S /ADM706T and the ADM708R /ADM708S /ADM708T microprocessor supervisory circuits are suitable for monitoring either 3 V or 3.3 V power supplies.The ADM706P /ADM706R /ADM706S /ADM706T provide power supply monitoring circuitry that generate a reset output during power-up, power-down, and brownout conditions. The reset output remains operational with V CC as low as 1 V .Independent watchdog monitoring circuitry is also provided. This activates if the watchdog input does not toggle within 1.6 sec. In addition, there is a 1.25 V threshold detector for a power fail warning, low battery detection, or to monitor an additional power supply. An active low debounced MR input is also included.Figure 2. ADM708R /ADM708S /ADM708TThe ADM706R , ADM706S , and ADM706T are identical except for the reset threshold monitor levels, which are 2.63 V , 2.93 V , and 3.08 V , respectively. The ADM706P is identical to the ADM706R in that the reset threshold is 2.63 V . It differs only in that it has an active high reset output.The ADM708R /ADM708S /ADM708T provide similar functio-nality as the ADM706R /ADM706S /ADM706T and only differ in that a watchdog timer function is not available. Instead, an active high reset output (RESET) is provided in addition to the active low (RESET ) output.All devices are available in narrow 8-lead PDIP and 8-lead SOIC packages.Data Sheet ADM706P/ADM706R/ADM706S/ADM706T, ADM708R/ADM708S/ADM708T SPECIFICATIONSV CC = 2.70 V to 5.5 V (ADM706P/ADM706R/ADM708R), V CC = 3.00 V to 5.5 V (ADM70xS), V CC = 3.15 V to 5.5 V (ADM70xT), T A =T MIN to T MAX unless otherwise noted.Rev. E | Pageof 16ADM706P/ADM706R/ADM706S/ADM706T, ADM708R/ADM708S/ADM708T Data SheetRev. E | Page of 16CIRCUIT INFORMATIONWATCHDOG INPUT (WDI)POWER-FAIL INPUT (PFI)POWER-FAIL OUTPUT (PFO)WATCHDOG OUTPUT (WDO)RESET,(P = RESET)*VOLTAGE REFERENCE = 2.63V (P/R), 2.93V (S), 3.08V (T)MR V CC06435-006Figure 13. ADM706P /ADM706R /ADM706S /ADM706T Functional BlockDiagramPOWER-FAIL *VOLTAGE REFERENCE = 2.63V (R), 2.93V (S), 3.08V (T)MR V CC06435-007POWER-FAIL OUTPUT (PFO)Figure 14.ADM708R /ADM708S /ADM708T Functional Block DiagramPOWER FAIL RESETThe reset output provides a reset (RESET or RESET ) output signal to the microprocessor whenever the V CC input is below the reset threshold. The actual reset threshold voltage is dependent on whether a P , R, S, or T suffix device is used. An internal timer holds the reset output active for 200 ms after the voltage on V CC rises above the threshold. This is intended as a power-on reset signal for the microprocessor. It allows time for both the power supply and the microprocessor to stabilize after power-up. If a power supply brownout or interruption occurs, the reset line is similarly activated and remains active for 200 ms after the supply recovers. If another interruption occurs during an active reset period, the reset timeout period continues for an additional 200 ms. The reset output is guaranteed to remain valid with V CC as low as 1 V . This ensures that the microprocessor is held in a stable shutdown condition as the power supply starts up.The ADM706P provides an active high RESET signal; theADM706R /ADM706S /ADM706T provide an active low RESET signal; and the ADM708R /ADM706S /ADM706T provide both RESET and RESET .MANUAL RESETThe MR input allows other reset sources, such as a manual reset switch, to generate a processor reset. The input is effectively debounced by the timeout period (200 ms typical). The MR input is TTL-/CMOS-compatible; it can also be driven by any logic reset output. If unused, the MR input can be tied high or left floating.06435-008NOTESRESET = COMPLEMENT OF RESETFigure 15. RESET , MR , and WDO TimingWATCHDOG TIMER (ADM706P /ADM706R / ADM706S /ADM706T )The watchdog timer circuit monitors the activity of themicroprocessor to check that it is not stalled in an indefinite loop. An output line on the processor is used to toggle the watchdog input (WDI) line. If this line is not toggled within the timeout period (1.6 sec), the watchdog output (WDO ) is driven low. The WDO output is connected to a nonmaskable interrupt (NMI) on the processor. Therefore, if the watchdog timer times out, an interrupt is generated. The interrupt service routine is used to rectify the problem.The watchdog timer is cleared either by a high to low or by a low to high transition on WDI. Pulses as narrow as 50 ns are detected. The timer is also cleared by RESET/RESET going active. Therefore, the watchdog timeout period begins after reset goes inactive.When V CC falls below the reset threshold, WDO is forced low whether or not the watchdog timer has timed out. Normally, this generates an interrupt, but it is overridden by RESET/RESET going active.06435-009Figure 16. Watchdog TimingData Sheet ADM706P/ADM706R/ADM706S/ADM706T, ADM708R/ADM708S/ADM708TRev. E | Page of 16COMPLIANT TO JEDEC STANDARDS MS-001CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS (IN PARENTHESES)ARE ROUNDED-OFF INCH EQUIVALENTS FORREFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.CORNER LEADS MAY BE CONFIGURED AS WHOLE OR HALF LEADS.070606-A0.070 (1.78)0.060 (1.52)0.045 (1.14)BSC0.325 (8.26)0.310 (7.87)0.300 (7.62)0.015 (0.38)GAUGE PLANEADM706P/ADM706R/ADM706S/ADM706T, ADM708R/ADM708S/ADM708T Data Sheet ORDERING GUIDEModel1Temperature Range Package Description Package Option ADM706PANZ −40°C to +85°C 8-Lead Plastic Dual In-Line Package [PDIP] N-8ADM706PARZ −40°C to +85°C 8-Lead Small Outline Package [SOIC_N] R-8ADM706PARZ-REEL −40°C to +85°C 8-Lead Small Outline Package [SOIC_N] R-8ADM706RANZ −40°C to +85°C 8-Lead Plastic Dual In-Line Package [PDIP] N-8ADM706RAR −40°C to +85°C 8-Lead Small Outline Package [SOIC_N] R-8ADM706RARZ −40°C to +85°C 8-Lead Small Outline Package [SOIC_N] R-8ADM706RARZ-REEL −40°C to +85°C 8-Lead Small Outline Package [SOIC_N] R-8ADM706RARZ-REEL7 −40°C to +85°C 8-Lead Small Outline Package [SOIC_N] R-8ADM706SANZ −40°C to +85°C 8-Lead Plastic Dual In-Line Package [PDIP] N-8ADM706SAR −40°C to +85°C 8-Lead Small Outline Package [SOIC_N] R-8ADM706SAR-REEL −40°C to +85°C 8-Lead Small Outline Package [SOIC_N] R-8ADM706SARZ −40°C to +85°C 8-Lead Small Outline Package [SOIC_N] R-8ADM706SARZ-REEL −40°C to +85°C 8-Lead Small Outline Package [SOIC_N] R-8ADM706TANZ −40°C to +85°C 8-Lead Plastic Dual In-Line Package [PDIP] N-8ADM706TAR −40°C to +85°C 8-Lead Small Outline Package [SOIC_N] R-8ADM706TAR-REEL −40°C to +85°C 8-Lead Small Outline Package [SOIC_N] R-8ADM706TARZ −40°C to +85°C 8-Lead Small Outline Package [SOIC_N] R-8ADM706TARZ-REEL −40°C to +85°C 8-Lead Small Outline Package [SOIC_N] R-8ADM708RANZ −40°C to +85°C 8-Lead Plastic Dual In-Line Package [PDIP] N-8ADM708RAR −40°C to +85°C 8-Lead Small Outline Package [SOIC_N] R-8ADM708RAR-REEL −40°C to +85°C 8-Lead Small Outline Package [SOIC_N] R-8ADM708RARZ −40°C to +85°C 8-Lead Small Outline Package [SOIC_N] R-8ADM708RARZ-REEL −40°C to +85°C 8-Lead Small Outline Package [SOIC_N] R-8ADM708SANZ −40°C to +85°C 8-Lead Plastic Dual In-Line Package [PDIP] N-8ADM708SAR −40°C to +85°C 8-Lead Small Outline Package [SOIC_N] R-8ADM708SAR-REEL −40°C to +85°C 8-Lead Small Outline Package [SOIC_N] R-8ADM708SARZ −40°C to +85°C 8-Lead Small Outline Package [SOIC_N] R-8ADM708SARZ-REEL −40°C to +85°C 8-Lead Small Outline Package [SOIC_N] R-8ADM708TANZ −40°C to +85°C 8-Lead Plastic Dual In-Line Package [PDIP] N-8ADM708TAR −40°C to +85°C 8-Lead Small Outline Package [SOIC_N] R-8ADM708TARZ −40°C to +85°C 8-Lead Small Outline Package [SOIC_N] R-8ADM708TARZ-REEL −40°C to +85°C 8-Lead Small Outline Package [SOIC_N] R-81 Z = RoHS Compliant Part.Rev. E | Page of 16。

半导体芯片ADM3202ARNZ-REEL中文规格书

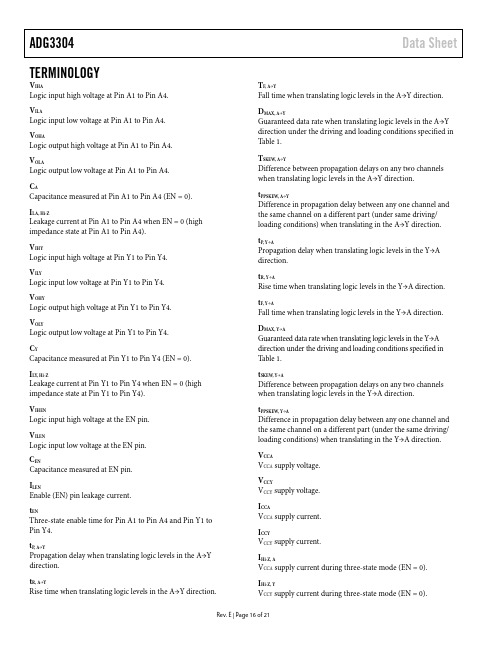

ADG3304Data Sheet Rev. E | Page 16 of 21TERMINOLOGYV IHALogic input high voltage at Pin A1 to Pin A4. V ILALogic input low voltage at Pin A1 to Pin A4. V OHA Logic output high voltage at Pin A1 to Pin A4. V OLA Logic output low voltage at Pin A1 to Pin A4. C A Capacitance measured at Pin A1 to Pin A4 (EN = 0). I LA, Hi-ZLeakage current at Pin A1 to Pin A4 when EN = 0 (high impedance state at Pin A1 to Pin A4).V IHYLogic input high voltage at Pin Y1 to Pin Y4. V ILYLogic input low voltage at Pin Y1 to Pin Y4. V OHY Logic output high voltage at Pin Y1 to Pin Y4. V OLY Logic output low voltage at Pin Y1 to Pin Y4. C Y Capacitance measured at Pin Y1 to Pin Y4 (EN = 0). I LY , Hi-ZLeakage current at Pin Y1 to Pin Y4 when EN = 0 (high impedance state at Pin Y1 to Pin Y4).V IHENLogic input high voltage at the EN pin.V ILENLogic input low voltage at the EN pin.C ENCapacitance measured at EN pin.I LENEnable (EN) pin leakage current.t ENThree-state enable time for Pin A1 to Pin A4 and Pin Y1 to Pin Y4.t P , A→YPropagation delay when translating logic levels in the A→Y direction.t R, A→YRise time when translating logic levels in the A→Y direction. T F, A→Y Fall time when translating logic levels in the A→Y direction. D MAX, A→Y Guaranteed data rate when translating logic levels in the A→Y direction under the driving and loading conditions specified in Table 1. T S KEW , A→Y Difference between propagation delays on any two channels when translating logic levels in the A→Y direction. t PPSKEW , A→Y Difference in propagation delay between any one channel and the same channel on a different part (under same driving/ loading conditions) when translating in the A→Y direction. t P , Y→A Propagation delay when translating logic levels in the Y→A direction. t R, Y→A Rise time when translating logic levels in the Y→A direction. t F, Y→A Fall time when translating logic levels in the Y→A direction. D MAX, Y→A Guaranteed data rate when translating logic levels in the Y→A direction under the driving and loading conditions specified in Table 1. t S KEW , Y→A Difference between propagation delays on any two channels when translating logic levels in the Y→A direction. t PPSKEW , Y→A Difference in propagation delay between any one channel and the same channel on a different part (under the same driving/ loading conditions) when translating in the Y→A direction. V CCA V CCA supply voltage. V CCY V CCY supply voltage. I CCA V CCA supply current. I CCY V CCY supply current. I Hi-Z, A V CCA supply current during three-state mode (EN = 0). I Hi-Z, Y V CCY supply current during three-state mode (EN = 0).Data SheetADG3304 Rev. E | Page 17 of 21THEORY OF OPERATIONThe ADG3304 level translator allows the level shifting necessary for data transfer in a system where multiple supply voltages are used. The device requires two supplies, V CCA and V CCY (V CCA ≤ V CCY ). These supplies set the logic levels on each side of the device. When driving the A pins, the device translates the V CCA -compatible logic levels to V CCY -compatible logic levels available at the Y pins. Similarly, because the device is capable of bidirectional translation, when driving the Y pins, the V CCY -compatible logic levels are translated to V CCA -compatible logic levels available at the A pins. When EN = 0, Pin A1 to Pin A4 and Pin Y1 to Pin Y4 are three-stated. When EN is driven high, the ADG3304 goes into normal operation mode and performs level translation. LEVEL TRANSLATOR ARCHITECTURE The ADG3304 consists of four bidirectional channels. Each channel can translate logic levels in either the A→Y or the Y→A direction. It uses a one-shot accelerator architecture, which ensures excellent switching characteristics. Figure 39 shows a simplified block diagram of a bidirectional channel.Y 04860-053Figure 39. Simplified Block Diagram of an ADG3304 Channel The logic level translation in the A→Y direction is performed using a level translator (U1) and an inverter (U2), while the translation in the Y→A direction is performed using Inverter U3 and Inverter U4. The one-shot generator detects a rising or falling edge present on either the A side or the Y side of the channel. It sends a short pulse that turns on the PMOS transistors (T1 to T2) for a rising edge, or the NMOS transistors (T3 to T4) for a falling edge. This charges/discharges the capacitive load faster, which results in faster rise and fall times.The inputs of the unused channels (A or Y) should be tied to their corresponding V CC rail (V CCA or V CCY ) or to GND. INPUT DRIVING REQUIREMENTS To ensure correct operation of the ADG3304, the circuit that drives the input of the ADG3304 channels should have an output impedance of less than or equal to 150 Ω and a minimum peak current driving capability of 36 mA. OUTPUT LOAD REQUIREMENTS The ADG3304 level translator is designed to drive CMOS-compatible loads. If current-driving capability is required, it is recommended to use buffers between the ADG3304 outputs and the load. ENABLE OPERATIONThe ADG3304 provides three-state operation at the A and Y I/O pins by using the enable pin (EN), as shown in Table 5. Table 5. Truth TableENY I/O Pins A I/O Pins 0Hi-Z 1 Hi-Z 1 1Normal operation 2Normal operation 21High impedance state.2 In normal operation, the ADG3304 performs level translation.While EN = 0, the ADG3304 enters into three-state mode. In this mode, the current consumption from both the V CCA and V CCY supplies is reduced, allowing the user to save power, which is critical, especially on battery-operated systems. The EN input pin can be driven with either V CCA -compatible or V CCY -compatible logic levels.POWER SUPPLIESFor proper operation of the ADG3304, the voltage applied to the V CCA must be less than or equal to the voltage applied to V CCY . To meet this condition, the recommended power-up sequence is V CCY first and then V CCA . The ADG3304 operates properly only after both supply voltages reach their nominal values. It is not recommended to use the part in a system where, during power-up, V CCA can be greater than V CCY due to a significant increase in the current taken from the V CCA supply. For optimum performance, the V CCA pin and V CCY pin should be decoupled to GND as close as possible to the device.。

9690低频低压解列装置使用说明书

03.事件记录 按“确定”键后,进入菜单,显示如下:

1.保护事件 2.遥信事件

4

9690 低频低压解列装置说明书

3.自检事件

4.事件清除

保护事件:可以记录 64 条保护动作的事件记录,记录编号为 0000~0063,按“确定”

第二部分 保护装置详细说明············································································· 10 一.9690 低频低压解列装置········································································· 10

5

9690 低频低压解列装置说明书

1 开关合位信号 对应开入量 1-14,第四排显示的是光标所在位置的开入量编号和名称。该通道采集到

开入量以后,则对应的位置由数字“0”变成“1”, 注意:开入量的电源为 DC24V,内供的,外面应接入的必须是无源节点。如果开入量

为电源 DC220V 或者 DC110V 的,则电源由外部提供,公共端接-220V,开入量信号接+220V. 开入量电源如果是非内供 24V,则需在订货时说明。

PASSWORD1 PASSWORD2 Address Baud Rate

Parity Address-2 Baud Rate-2 Parity-2 Language

MAC IP Sub Mask Gateway

名称 二次保护电压比例系数 二次保护电流比例系数 二次测量电压比例系数 二次测量电流比例系数 二次测量功率比例系数 接线方式 未定义 滚动显示项目选择 1 滚动显示项目选择 2 一级密码(改定值、投退用) 二级密码(做开出试验用) 装置通讯地址 装置通讯波特率 校验方式 装置通讯地址 装置通讯波特率 校验方式 未定义 MAC 地址 1 IP 地址设置 1 子网掩码 1 网关 1

进军顶级显卡市场 AMD Radeon RX 6900XT显卡首发评测

进军顶级显卡市场 AMD Radeon RX 6900XT显卡首发评测作者:《微型计算机》评测室来源:《微型计算机》2021年第01期在高端顯卡领域蛰伏多年的AMD终于凭借RX 6800XT显卡重返高端消费级显卡市场,从我们的评测结果来看,这款显卡的确拥有不小的市场竞争力。

不过AMD并未止步于此,优化的RDNA2架构、增强计算规模的NAVI 21核心,以及无限缓存等核心技术的加持,让AMD有能力冲击更高的显卡领域,AMD Radeon RX 6900XT(下文简称RX 6900XT)就是他们打开顶级显卡市场的敲门砖。

下面就请跟随本文来看看RX 6900XT的性能究竟有多强,它是否能给NVIDIA带来足够的压力。

AMD Radeon RX 6900XT技术解析在这个信息大爆炸的时代,我们每天都要通过各种途径接收大量信息,如果你已经记不太清RDNA2架构、NAVI 21核心或者无限缓存等技术的详细内容,其实也完全情有可原。

因此,我们不妨首先来简单了解一下RX 6900XT的核心技术,如果你想详细了解其技术内容,不妨移步《高端显卡市场争夺战打响!AMD Radeon RX 6800 XT & RX 6800显卡首发评测》一文,这里有RDNA2架构的详细解析,应该能够满足你的好奇心。

RNDA2架构:规模更大、性能更强RNDA2架构是一个基于RDNA改进、扩张和加入了大量全新功能的架构,它的规模更大、性能更强,同时拥有时下流行的光线追踪、VRS等高级功能,还提供了对DirectX 12终极版本的全面支持。

需要注意的是,RDNA和RDNA2的所有产品采用的是台积电的7nm工艺,虽然在不断的工艺发展和生产过程中,台积电会对后期工艺进行优化,但是仅凭优化一般很难达到功耗降低一半、频率提升30%这样的效果,因此RDNA2现在拥有的优势主要还是来自于其架构的设计。

另外,AMD还特别提到,RDNA 2的高频率和AMD目前在CPU中的设计经验的引入相关,AMD宣称在新的GPU设计和制造过程中使用了大量在CPU设计中曾使用到的技术或者经验,再加上优化过的微架构,最终实现了本代GPU超过2GHz的运行频率以及较低的功耗CU单元:提升能耗比,引入光线追踪单元RDNA2架构的NAVI 21核心在宏观上可以看做NAVI 10核心的扩大版本—后者拥有2个渲染引擎,每个渲染引擎包含了10个双CU单元,所以总计拥有2560个流处理器单元,而NAVI 21核心拥有4个渲染引擎,所以内部计算资源均相对NAVI 10翻倍。

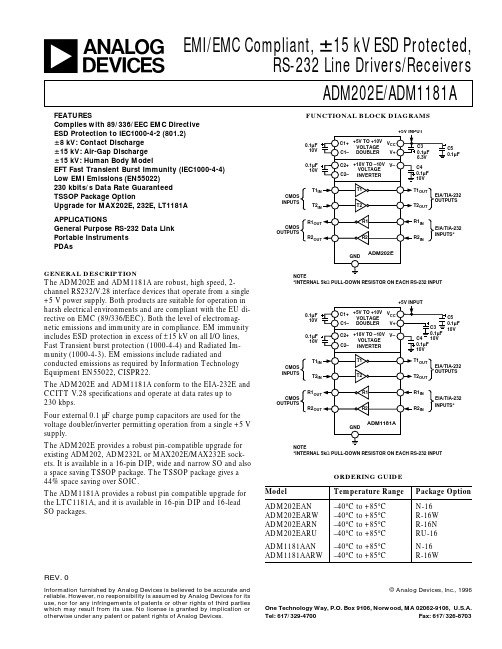

ADM202EAN中文资料

4.5 5.0 5.5

2.0 3.0

15

18

0.8 2.4

0.4 3.5

0.01 ± 10

–30

+30

0.4 0.8

1.1 2.4

0.7

3

5

7

± 5.0 ± 9.0

300 ± 15 ± 60

230

0.3 1

0.6 1

1.2 1.5

3

10

30

EM IMMUNITTY ESD Protection (I/O pins)

V

IOUT = 3.2 mA

V

IOUT = –1 mA

µA

TIN = GND to VCC

V V V V kΩ

Volts

Ω mA

All Transmitter Outputs

Loaded with 3 kΩ to Ground VCC = 0 V, VOUT = ± 2 V

kbps

RL = 3 kΩ to 7 kΩ, CL = 50 pF to 2500 pF

EFT Protection (I/O pins) EMI Immunity

Specifications subject to change without notice.

± 15 ± 15 ± 8 kV ±2

10

Volts mA mA

No Load RL = 3 kΩ to GND

V

TIN

V

TIN

The ADM202E and ADM1181A conform to the EIA-232E and CCITT V.28 specifications and operate at data rates up to 230 kbps.

ADM3490ARZ中文资料

FUNCTIONAL BLOCK DIAGRAMS

VCC

ADM3483/ ADM3485

ROБайду номын сангаас

R

RE

A

DE

B

DI

D

05524-027

05524-026

GND

Figure 1.

VCC

A

RO

R

B

ADM3488/ ADM3490

Z

DI

D

Y

GND

Figure 2.

ADM3491

A

RO

R

RE

B

DE

Z

DI

D

Y

05524-025

Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

MEMORY存储芯片ADM3202ARN中文规格书

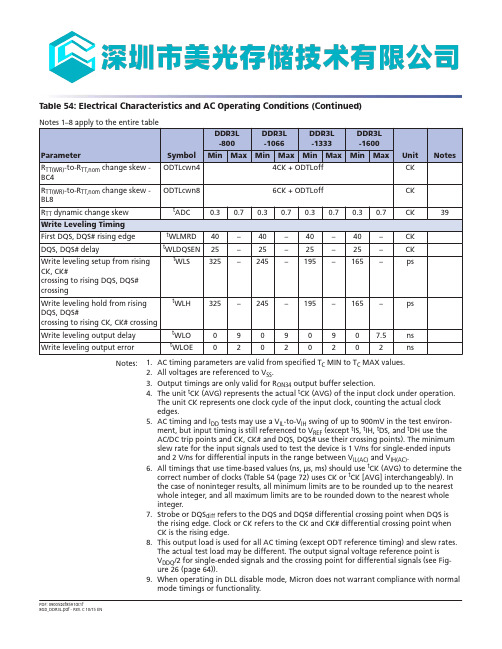

Table 54: Electrical Characteristics and AC Operating Conditions (Continued)Notes: 1.AC timing parameters are valid from specified T C MIN to T C MAX values.2.All voltages are referenced to V SS.3.Output timings are only valid for R ON34 output buffer selection.4.The unit t CK (AVG) represents the actual t CK (AVG) of the input clock under operation.The unit CK represents one clock cycle of the input clock, counting the actual clockedges.5.AC timing and I DD tests may use a V IL-to-V IH swing of up to 900mV in the test environ-ment, but input timing is still referenced to V REF (except t IS, t IH, t DS, and t DH use theAC/DC trip points and CK, CK# and DQS, DQS# use their crossing points). The minimumslew rate for the input signals used to test the device is 1 V/ns for single-ended inputsand 2 V/ns for differential inputs in the range between V IL(AC) and V IH(AC).6.All timings that use time-based values (ns, μs, ms) should use t CK (AVG) to determine thecorrect number of clocks (Table 54 (page 72) uses CK or t CK [AVG] interchangeably). Inthe case of noninteger results, all minimum limits are to be rounded up to the nearestwhole integer, and all maximum limits are to be rounded down to the nearest wholeinteger.7.Strobe or DQS diff refers to the DQS and DQS# differential crossing point when DQS isthe rising edge. Clock or CK refers to the CK and CK# differential crossing point whenCK is the rising edge.8.This output load is used for all AC timing (except ODT reference timing) and slew rates.The actual test load may be different. The output signal voltage reference point isV DDQ/2 for single-ended signals and the crossing point for differential signals (see Fig-ure 26 (page 64)).9.When operating in DLL disable mode, Micron does not warrant compliance with normalmode timings or functionality.Table 55: Electrical Characteristics and AC Operating Conditions for Speed ExtensionsTable 55: Electrical Characteristics and AC Operating Conditions for Speed Extensions (Continued)Table 55: Electrical Characteristics and AC Operating Conditions for Speed Extensions (Continued)Table 55: Electrical Characteristics and AC Operating Conditions for Speed Extensions (Continued)。

adm芯片

adm芯片ADM芯片是一种数字集成电路,可用于各种应用领域。

ADM 芯片的全称为Analog Devices(ADI)的高精度模拟数字转换器(ADC)与数字模拟转换器(DAC)芯片。

ADM芯片主要由模拟部分和数字部分组成,能够将模拟信号转换为数字信号或将数字信号转换为模拟信号。

ADM芯片采用高精度的模拟电路和先进的数字技术,具有高速、高精度和低功耗等特点。

它可以处理各种类型的信号,如声音、图像和传感器信号等。

ADM芯片的广泛应用包括通信设备、工业自动化、医疗器械、汽车电子等领域。

ADM芯片的核心技术是模拟数字转换器(ADC)和数字模拟转换器(DAC)。

ADC能够将模拟信号转换为数字信号,DAC能够将数字信号转换为模拟信号。

ADM芯片的ADC和DAC具有高分辨率、高采样率和低失真等优点,可以实现高质量的信号转换。

ADM芯片还集成了数字信号处理器(DSP),可以对数字信号进行复杂的算法处理。

DSP可以实现滤波、解调、编解码等功能,提高了ADM芯片的灵活性和性能。

ADM芯片的设计和制造需要专业的技术和设备。

ADI是一家拥有多年经验和先进工艺的半导体公司,可以提供高质量的ADM芯片和解决方案。

对于使用ADM芯片的应用,开发人员需要了解其性能参数和接口规范。

ADM芯片的性能参数包括分辨率、采样率、信噪比和动态范围等,接口规范包括电源电压、通信协议和引脚定义等。

总之,ADM芯片是一种功能强大、性能优异的数字集成电路,广泛应用于各种领域。

它能够实现模拟信号与数字信号的转换,并具有高速、高精度和低功耗等特点。

ADM芯片的设计和制造需要专业的技术和设备,开发人员需要了解其性能参数和接口规范。

有了ADM芯片的支持,各种应用系统可以实现更高的功能和性能。

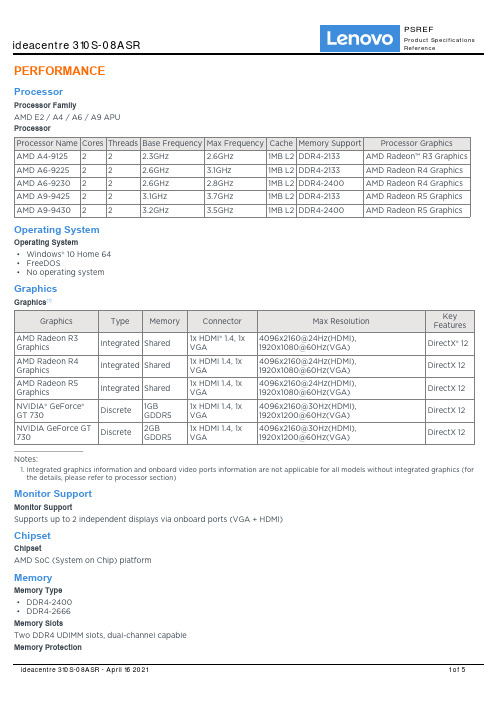

AMD E2 A4 A6 A9 APU处理器说明书

PERFORMANCEProcessorProcessor FamilyAMD E2 / A4 / A6 / A9 APUProcessorOperating SystemOperating SystemWindows® 10 Home 64••FreeDOS•No operating systemGraphicsGraphics[1]Notes:Integrated graphics information and onboard video ports information are not applicable for all models without integrated graphics (for 1.the details, please refer to processor section)Monitor SupportMonitor SupportSupports up to 2 independent displays via onboard ports (VGA + HDMI)ChipsetChipsetAMD SoC (System on Chip) platformMemoryMemory Type•DDR4-2400•DDR4-2666Memory SlotsTwo DDR4 UDIMM slots, dual-channel capableMemory ProtectionNon-ECCMax Memory[1]Up to 16GB DDR4-2666Notes:1.The max memory is based on the test results with current Lenovo® memory offerings. The system may support more memory as the technology develops.StorageStorage SupportUp to 2 drives, 1x 3.5" HDD + 1x 2.5" SSD3.5" HDD up to 2TB2.5" SSD up to 256GBRAIDNot supportStorage TypeRemovable StorageOptical•DVD burner (DVD??RW), SATA 1.5Gb/s, slim (9.0mm)•NoneCard Reader7-in-1 card reader (SD, SDHC, SDXC, MMC, MS, MS-Pro, MMC plus)••No card readerMulti-MediaAudio ChipHigh Definition (HD) Audio, Realtek® ALC662 codecPower SupplyPower SupplyDESIGNInput DeviceKeyboard•Lenovo Calliope Keyboard (USB connector), black•Lenovo Calliope Keyboard (USB connector), silver•Lenovo Calliope Wireless Keyboard, silver•No keyboardMouse•Lenovo Calliope Wireless Mouse, silverLenovo Calliope Mouse (USB connector), black••Lenovo Calliope Mouse (USB connector), silver•No mouseMechanicalButtons•Power buttonOptical drive eject button(for the models with ODD)•Form FactorSFF (8.4L)Dimensions (WxDxH)90 x 297 x 344mm (3.54 x 11.69 x 13.54 inches)Weight4.3 kg (9.5 lbs)Case ColorBlack••SilverBays•1x slim ODD bay•1x 2.5" disk bay•1x 3.5" disk bayExpansion Slots•One PCIe 2.0 x16, low-profile•One PCIe 2.0 x1, low-profile•Two M.2 slots (one for WLAN, one for SSD)CONNECTIVITYNetworkOnboard EthernetGigabit Ethernet, 1x RJ45WLAN + Bluetooth™•802.11ac 1x1 Wi-Fi + Bluetooth 4.0, M.2 card•No WLAN and BluetoothPortsFront Ports[1]•2x USB 2.0•2x USB 3.2 Gen 1•1x headphone / microphone combo jack (3.5mm)•1x microphone (3.5mm)Optional Front Ports1x card readerRear Ports[2]•2x USB 2.0•1x Ethernet (RJ-45)•1x HDMI 1.4•1x VGA•1x microphone (3.5mm)•1x line-in (3.5mm)•1x line-out (3.5mm)•1x power connectorNotes:1.The transfer speed of following ports will vary and, depending on many factors, such as the processing speed of the host device, file attributes and other factors related to system configuration and your operating environment, will be slower than theoretical speed.USB 2.0: 480 Mbit/s;USB 3.2 Gen 1 (SuperSpeed USB 5Gbps, formely USB 3.0 / USB 3.1 Gen 1): 5 Gbit/s;USB 3.2 Gen 2 (SuperSpeed USB 10Gbps, formely USB 3.1 Gen 2): 10 Gbit/s;USB 3.2 Gen 2x2 (SuperSpeed USB 20Gbps): 20 Gbit/s;Thunderbolt™ 3: 40 Gbit/s;FireWire 400: 400 Mbit/s;FireWire 800: 800 Mbit/s;For video ports on discrete graphics, please see graphics section 2.SECURITY & PRIVACYSecurityBIOS Security•Power-on password•Administrator passwordHard disk password•SERVICEWarrantyBase Warranty•1-year depot or mail-in service•1-year limited onsite service•2-year depot serviceCERTIFICATIONSGreen CertificationsGreen Certifications•ErP Lot 3•GREENGUARD®•RoHS compliant。

ANALOG DEVICES ADM9690 英文产品数据手册 Rev A

REV.AInformation furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.aADM9690One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: 781/329-4700World Wide Web Site: Fax: 781/326-8703© Analog Devices, Inc., 2000Power Supply and Watchdog TimerMonitoring CircuitFUNCTIONAL BLOCK DIAGRAMV V RESET(1)RESET(2)FEATURESPrecision Voltage Monitor (4.31 V)Watchdog Timeout MonitorSelectable Watchdog Timeout—0.75 ms, 1.5 ms,12.5 ms, 25 ms Two RESET Outputs APPLICATIONSMicroprocessor Systems Computers Printers ControllersIntelligent InstrumentsGENERAL DESCRIPTIONThe ADM9690 contains a voltage monitoring comparator and a watchdog timer monitor. It is designed to monitor the 5V power supply to a microprocessor and the microprocessor opera-tion via a watchdog function.The voltage monitoring comparator monitors the voltage on V MON . If it drops outside tolerance, as will happen during a power-fail, two reset signals are generated. Both reset signals go active (low) simultaneously. They will remain active while V MON is below the threshold, and for 50 ms (RESET(1)) or 60 ms (RESET(2)) after V MON climbs above the reset thresh-old. RESET(1) is intended to provide a power-on reset signal for the µP while RESET(2) is used to hold additional circuitry in a reset state until the µP has regained control following a power-up. The voltage monitoring circuitry remains operational with V CC as low as 2 V.The watchdog timer monitoring circuit is designed to monitor the activity on the WDI input. This input is normally connected to an output line on the µP. Its function is to check that the microprocessor has not stalled in an infinite loop. If there is a period of inactivity for the watchdog timeout period, both reset outputs are activated. As above, RESET(1) remains low for 50 ms while RESET(2) remains low for an additional 10 ms.The watchdog timer is restarted when RESET(1) goes inactive.The actual watchdog timeout period is adjustable using two select inputs SEL1 and SEL2.The ADM9690 is available in an 8-lead SOIC package. It is specified over the industrial temperature range.ADM9690–SPECIFICATIONS(V CC = Full Operating Range. T A = T MIN to T MAX unless otherwise noted) Parameter Min Typ Max Units Test Conditions/CommentsV CC OPERATING VOLTAGE RANGE 4.3 5.5VSUPPLY CURRENT55100µARESET AND WATCHDOG TIMERReset Voltage Threshold 4.2 4.31 4.42V V MON Falling T A = 0°C to +70°C Reset Threshold Hysteresis30mVReset Timeout Delay (t1)5075ms Figure 7, 8RESET(2) Timeout Delay (t2)1015ms Figure 7, 8WATCHDOG TIMEOUT PERIOD (TWD)0.40.75 1.28ms SEL2 = 0, SEL1 = 01.0 1.52.4ms SEL2 = 0, SEL1 = 19.012.519ms SEL2 = 1, SEL1 = 0182538ms SEL2 = 1, SEL1 = 1WDI INPUT PULSEWIDTH100ns V IL = 0.4, V IH = 3.5 VRESET(1)/(2) Output Voltage0.10.4V I SINK = 3.2 mA0.30.4V I SINK = 10 mA,0.450.7V I SINK = 15 mA,3.5V I SOURCE = 1 µAWDI INPUT THRESHOLDLogic Low0.8V150 ns PulseLogic High 3.5V150 ns PulseWDI Input Current 1.25µA WDI = V CC–5–1.2µA WDI = 0 VSEL1/2 Input Current–1+1µA SEL = V CC–10–510µA SEL = 0 VSpecifications subject to change without notice.–2–REV. AADM9690–3–REV. A ABSOLUTE MAXIMUM RATINGS*(T A = +25°C unless otherwise noted)V CC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +6 V V MON . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to V CC + 0.3 V Input CurrentV CC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 200 mA GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 200 mA Digital Output Current . . . . . . . . . . . . . . . . . . . . . . . 200 mA Power Dissipation, R-8 SOIC . . . . . . . . . . . . . . . . . . 400 mW θJA Thermal Impedance . . . . . . . . . . . . . . . . . . . . . . 120°C/W Industrial (A Version) . . . . . . . . . . . . . . . . . . –40°C to +85°C Lead Temperature (Soldering, 10 secs) . . . . . . . . . . . +300°C Vapor Phase (60 secs) . . . . . . . . . . . . . . . . . . . . . . +215°C Infrared (15 secs) . . . . . . . . . . . . . . . . . . . . . . . . . . +220°C Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C ESD Rating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 kV*Stresses above those listed under Absolute Maximum Ratings may cause perma-nent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum ratings for extended periods of time may affect device reliability.ORDERING GUIDETemperature Package Package Model Range Description Option ADM9690AR–40°C to +85°C8-Lead Narrow SO-8Body SOICPIN FUNCTION DESCRIPTIONSMnemonic FunctionV CC Power Supply Input; +5 V.V MON Voltage Monitoring Input.GND0 V. Ground reference for all signals.RESET(1)Logic Output. RESET(1) goes low if V MON falls below the Reset Threshold or the Watch-dog timer is not serviced within its timeout period. The reset threshold is typically 4.4 V for the ADM9690. RESET(1) remains low for 50 ms after V CC returns above the thresh-old. RESET(1) also goes low for 50 ms if the Watchdog Timer is not serviced within its timeout period.RESET(2)Logic Output. RESET(2) goes low simulta-neously with RESET(1) but remains low for an additional 10 ms.WDIWatchdog Input. If an edge is not detected on WDI within the selectable watchdog timeout period, RESET(1) and RESET(2) are forced low for their respective timeout periods. The watchdog timer restarts with each positive or negative going transition on the WDI line. Following a reset it is restarted when RESET(1) goes inactive (high). The Watch-dog Timer may be disabled if WDI is left floating or is driven to midsupply.SEL1, 2Watchdog Timeout selection inputs. Refer to Table I.PIN CONFIGURATIONV MON WDIV CCGND SEL1SEL2RESET(1)RESET(2)ADM9690–4–REV. A–Typical Performance CurvesCH1 1.0V CH2M 500ms V CC1.0V CH1380mVRESETFigure 1.Reset Output Voltage vs. SupplyTEMPERATURE – C4.4124.396–60120–3003060904.4104.4084.4064.4044.402R E S E T V O L T A G E T H R E S H O L D – V o l t s4.4004.398Figure 2.Reset Voltage Threshold vs. TemperatureFigure 5.Typical Application CircuitV CC – Volts10W A T C H D O G A N D R E S E T T I M E O U T P E R I O D – m s2.55.53.0 3.5 4.04.55.06.0 6.5Figure 3.Watchdog and Reset Timeout Period vs. Supply @ –40°CTEMPERATURE – CB A T T E R Y S U P P L YC U R R E N T – A72.068.8–60120–30030609071.671.270.870.470.069.669.2Figure 4.Supply Current vs. TemperatureADM9690–5–REV. AWhen V after V V MONRESET(1)RESET(2)Figure 7.Power-On RESET Timing WDIRESET(1)RESET(2)Figure 8.Watchdog RESET TimingADM9690–6–REV. AOUTLINE DIMENSIONSDimensions shown in inches and (mm).C 3135a –1.5–3/00 (r e v . A )P R I N T E D I N U .S .A .8-Lead Narrow Body SOIC(SO-8)PLANEBSC °。

昂盛达ASD969综合测试仪用户手册说明书

©版权归属于昂盛达电子有限公司Ver2.0 /Apr, 2021/ ASD969ASD969综合测试仪由测试仪及触控屏两部分组成,主要用于移动电源、适配器储能电在某些情况下,用错误配置的市电电压为设备供电可能造成市电保险丝断开。

图2.2ASD969前面板①电源开关②状态指示灯③ 测试接口②③④图2.3ASD969后面板② DC电源插座③USB接口④ RS232接口图2.4.1ASD969安卓触控屏注:产品如有更新功能或改善上位优化机,不再另行通知,只要联网会提示升级。

4.1.1所示。

图4.1.1标准电源协议电源,有5V、9V、12V、20V电压可供选择,可设置(0~5A),可显示测试曲线,如图4.1.2所示。

Leading Innovator in Power Testing Solution图4.1.2QC电源协议电源,有5V、9V、12V、15V、19V、20V电压可供选择,可设置电流),可显示测试曲线,并有CC1、CC2、CC1+CC2三种CC线连接方式可供选择,如图4.1.3所示。

标准负载恒流模式(CC图4.1.4恒流负载在开启测试后长按“OCP”按钮可进行过流设置,如图4.1.5所示。

图4.1.5OCP设置恒压模式(CV图4.1.6所示。

图4.1.6恒压负载协议负载,有5V、9V、12V、20V电压可供选择。

可选择恒流模式(CC 流(0~5A)或选择恒压模式(CV)设定电压,如图4.1.7所示。

图4.1.7QC负载图4.2.1 标准自动添加测试工序、设定测试条件和判定范围在参数设置界面完成,如图4.2.2所示图4.2.2 参数设置测试条件可指定测试组和通道,选择电源或负载类型、设定电压和电流参数,标准、QC或PD协议方式。

其设置在“编辑”界面完成,如图4.2.3所示;判定范围可设置电压或电流参数、D+/D-和纹波参数。

测试值在范围内则判定通过。

测试工序可编辑和保存,保存的工序可单步调试或复制粘贴、编辑、删除;自动测试按序号依次进行,可长按序号拖动进行自由排序;多道工序可保存为一个项目,项目数据可导出或导入至存储设备。

半导体传感器ADUM1201ARZ中文规格书

Data Sheet ADuM1400/ADuM1401/ADuM1402 Rev. L | Page 17 of 31ELECTRICAL CHARACTERISTICS—MIXED 3 V/5 V, 125°C OPERATION 13.0 V ≤ V DD1 ≤ 3.6 V ,4.5 V ≤ V DD2 ≤5.5 V; all minimum/maximum specifications apply over the entire recommended operation range, unless otherwise noted; all typical specifications are at T A = 25°C; V DD1 = 3.0 V , V DD2 = 5 V . These specifications apply to ADuM1400W , ADuM1401W , and ADuM1402W automotive grade versions. Table 7.ParameterSymbol Min Typ Max Unit Test Conditions DC SPECIFICATIONSInput Supply Current per Channel, QuiescentI DDI (Q) 0.26 0.31 mA Output Supply Current per Channel, QuiescentI DDO (Q) 0.19 0.21 mA ADuM1400W , Total Supply Current, Four Channels 2DC to 2 MbpsV DD1 Supply CurrentI DD1 (Q) 1.2 1.9 mA DC to 1 MHz logic signal freq. V DD2 Supply CurrentI DD2 (Q) 0.9 1.4 mA DC to 1 MHz logic signal freq. 10 Mbps (TRWZ Grade Only)V DD1 Supply CurrentI DD1 (10) 4.5 6.5 mA 5 MHz logic signal freq. V DD2 Supply CurrentI DD2 (10) 2.6 3.5 mA 5 MHz logic signal freq. ADuM1401W , Total Supply Current, Four Channels 2DC to 2 MbpsV DD1 Supply CurrentI DD1 (Q) 1.0 1.6 mA DC to 1 MHz logic signal freq. V DD2 Supply CurrentI DD2 (Q) 1.2 1.8 mA DC to 1 MHz logic signal freq. 10 Mbps (TRWZ Grade Only)V DD1 Supply CurrentI DD1 (10) 3.7 5.4 mA 5 MHz logic signal freq. V DD2 Supply CurrentI DD2 (10) 4.1 5.0 mA 5 MHz logic signal freq. ADuM1402W , Total Supply Current, FourChannels 2DC to 2 MbpsV DD1 Supply CurrentI DD1 (Q) 0.9 1.5 mA DC to 1 MHz logic signal freq. V DD2 Supply CurrentI DD2 (Q) 1.5 2.1 mA DC to 1 MHz logic signal freq. 10 Mbps (TRWZ Grade Only)V DD1 Supply CurrentI DD1 (10) 3.0 4.2 mA 5 MHz logic signal freq. V DD2 Supply CurrentI DD2 (10) 5.6 7.0 mA 5 MHz logic signal freq. For All ModelsInput CurrentsI IA , I IB , I IC , I ID , I E1, I E2 −10 +0.01+10µA 0 V ≤ V IA , V IB , V IC , V ID ≤ V DD1 or V DD2, 0 V ≤ V E1, V E2 ≤ V DD1 or V DD2 Logic High Input ThresholdV IH , V EH 1.6 V Logic Low Input ThresholdV IL , V EL 0.4 V Logic High Output VoltagesV OAH , V OBH , V OCH , V ODH (V DD1 or V DD2) − 0.1 V DD1, V DD2 V I Ox = −20 µA, V Ix = V IxH (V DD1 or V DD2) − 0.4V DD1, V DD2 − 0.2 V I Ox = −3.2 mA, V Ix = V IxH Logic Low Output Voltages V OAL , V OBL ,V OCL , V ODL 0.0 0.1 V I Ox = 20 µA, V Ix = V IxL 0.04 0.1 VI Ox = 400 µA, V Ix = V IxL0.2 0.4 V I Ox = 3.2 mA, V Ix = V IxLSWITCHING SPECIFICATIONSADuM1400WSRWZ /ADuM1401WSRWZ / ADuM1402WSRWZMinimum Pulse Width 3PW 1000 ns C L = 15 pF, CMOS signal levels Maximum Data Rate 41 Mbps C L = 15 pF, CMOS signal levels Propagation Delay 5t PHL , t PLH 50 70 100 ns C L = 15 pF, CMOS signal levels Pulse Width Distortion, |t PLH − t PHL |5PWD 40 ns C L = 15 pF, CMOS signal levels Propagation Delay Skew 6t PSK50 ns C L = 15 pF, CMOS signal levelsChannel-to-Channel Matching 7 t PSKCD /t PSKOD 50 ns C L = 15 pF, CMOS signal levelsData SheetADuM1400/ADuM1401/ADuM1402 Rev. L | Page 21 of 31ABSOLUTE MAXIMUM RATINGSAmbient temperature = 25°C, unless otherwise noted. Table 13.ParameterRating Storage Temperature (T ST )−65°C to +150°C Ambient Operating Temperature (T A )1−40°C to +105°C Ambient Operating Temperature (T A )2−40°C to +125°C Supply Voltages (V DD1, V DD2)3−0.5 V to +7.0 V Input Voltage (V IA , V IB , V IC , V ID , V E1, V E2)3, 4−0.5 V to V DDI + 0.5 V Output Voltage (V OA , V OB , V OC , V OD )3, 4−0.5 V to V DDO + 0.5 V Average Output Current per Pin 5Side 1 (I O1)−18 mA to +18 mA Side 2 (I O2)−22 mA to +22 mA Common-Mode Transients 6−100 kV/µs to +100 kV/µs 1 Does not apply to ADuM1400W , ADuM1401W , and ADuM1402W automotive grade versions.2 Applies to ADuM1400W , ADuM1401W , and ADuM1402W automotive grade versions.3 All voltages are relative to their respective ground.4 V DDI and V DDO refer to the supply voltages on the input and output sides of a given channel, respectively. See the PC Board Layout section.5 See Figure 4 for maximum rated current values for various temperatures.6 This refers to common-mode transients across the insulation barrier. Common-mode transients exceeding the Absolute Maximum Ratings may cause latch-up or permanent damage.Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability. ESD CAUTION Table 14. Maximum Continuous Working Voltage 1ParameterMax Unit Constraint AC Voltage, Bipolar Waveform565 V peak 50-year minimum lifetime AC Voltage, Unipolar WaveformBasic Insulation1131 V peak Maximum approved working voltage per IEC 60950-1 Reinforced Insulation560 V peak Maximum approved working voltage per IEC 60950-1 and VDE V 0884-10 DC VoltageBasic Insulation1131 V peak Maximum approved working voltage per IEC 60950-1 Reinforced Insulation560 V peak Maximum approved working voltage per IEC 60950-1 and VDE V 0884-10 1 Refers to continuous voltage magnitude imposed across the isolation barrier. See the Insulation Lifetime section for more details. Table 15. Truth Table (Positive Logic)V Ix Input 1V Ex Input 1, 2 V DDI State 1 V DDO State 1 V Ox Output 1 Notes HH or NC Powered Powered H LH or NC Powered Powered L XL Powered Powered Z XH or NC Unpowered Powered H Outputs return to the input state within 1 µs of V DDI power restoration. XL Unpowered Powered Z X X Powered Unpowered Indeterminate Outputs return to the input state within 1 µs of V DDO power restoration if the V Ex state is H or NC. Outputs return to a high impedance statewithin 8 ns of V DDO power restoration if the V Ex state is L.1V Ix and V Ox refer to the input and output signals of a given channel (A, B, C, or D). V Ex refers to the output enable signal on the same side as the V Ox outputs. V DDI and V DDO refer to the supply voltages on the input and output sides of the given channel, respectively.2 In noisy environments, connecting V Ex to an external logic high or low is recommended.。

AMD Socket AM2(940-pin)处理器 AMD 790GX 790X 主板 用户说明书

用户说明书AMD Socket AM2(940-pin)处理器AMD 790GX/790X主板商标所有的产品注册商标及公司名称皆属其公司所有产品内容若有更改,恕不另行通知V1.0 中文版 2008年8月MUA79008828A01常用除错卡代码表以下列出一些常见的自检代码,对一些可能出现的问题以及解决方式的列表,如果想了解更多的关于自检代码的信息,请参考本说明书后面的附录。

目录第1章配件 (1)1-1 包装内容 (1)1-2 主板介绍 (2)1-3 主板规格 (3)1-4 系统模块图 (7)第2章安装 (8)2-1 CPU安装 (8)2-2 跳线设置 (9)2-3 系统内存 (10)2-4 系统显卡组态 (11)2-5 背部I/O接口 (12)2-6 主板内部接口介绍 (12)第3章常用BIOS设置 (16)3-1 Main(主菜单) (16)3-2 Advanced(系统高级设定) (18)3-3 Boot(启动配置设定) (25)3-4 Security(BIOS密码设定) (26)3-5 Power(电源管理设置) (27)3-6 Q-Tune(超频功能设置) (30)3-7 EXIT(退出菜单 (34)第4章驱动以及应用程序 (35)第5章常见问题解答 (36)附录:磐正超磐手主板保修条例 (39)1-1包装内容内容 可选设备 A.主板 G.软驱数据线B.用户说明书 H.额外的USB2.0扩展端口连接C.CD I. DIY 小散热片D.I/O 挡板E.SATA II 数据线F.硬盘数据线A注:若您的包装内物品有任何的损坏或短缺情形,请与经销商联络。

ED H ICD1-2主板介绍●Socket AM2/AM2+Socket AM2/AM2+(940针)是AMD 高性能的Athlon AM2/AM2+处理器的接口,让用户体验到高效性能的执行能力。

预了解更多关于Athlon ™ AM2/AM2+处理器的新特色,请浏览AMD 的官方网站:●芯片组该主板使用AMD 790GX+SB750或790X+SB700 芯片,拥有稳定以及革新技术的特色 预了解更多关于AMD 芯片组的细节,请浏览AMD 的官方网站:●PCI-Express(PCI-E)支持新一代周边设备接口:PCI-E 2.0,PCI-E 2.0向下兼容PCI-E 1.0,拥有更快的传输速率,数据传输速率双向可达16GB/sec (PCI-E2.0 X16)。

重出江湖之作 迪兰恒进690G整合主板

重出江湖之作迪兰恒进690G整合主板

佚名

【期刊名称】《现代计算机:中旬刊》

【年(卷),期】2007()9

【摘要】迪兰恒进此次适时机的推出这款经典整合板M2A692,搭载AMD690G +SB600芯片组,集成X1250显卡,默认核心频率达到525MHz,比起公版的400MHz有了不少的提高,在运行游戏《HalfLife2》时,在800×600下达到了30帧以上,实际感受画面的流畅程度也可以接受,

【总页数】1页(P19-19)

【关键词】整合主板;迪兰恒进;江湖;核心频率;芯片组;显卡;帧

【正文语种】中文

【中图分类】TP303

【相关文献】

1.至高性价比迪兰恒进HD5550酷能++版显卡/再造亮点影驰GTX460黑将版显卡/超低价特供双敏UR880GT全固态特供版主板 [J],

2.精英PF21 Extreme主板/AOpen i855GMEm-LFS主板/迪兰恒进镭姬杀手9800SE黄金版AIW显示卡 [J],

3.迎接数字电视时代!迪兰恒进Theater 650 Pro全球独家发布!/INTEL"一板通"——杰微C19主板最高支持1066 MHz外频 [J],

4.高效游戏装备--迪兰恒进HD6790恒金1GB显卡 [J],

5.海量显存更给力迪兰恒进HD6750恒金D3 2G显卡 [J],

因版权原因,仅展示原文概要,查看原文内容请购买。

加拿大贝尔雷达V940I中文说明说

加拿大贝尔雷达V940I中文说明书

PWR 开机键

VOLUNCE . MUTE 声音大小调节(长按可调节声音大小)CITY 城市模式和高速模式的切换

BRT 主屏的亮度调节

RVW+CHG 同时按住两个键可进入主机菜单

下列是主机菜单选项

1.PILOT ( HWY 或H )显示全部文字或单独显示一个文字

2.VOICE 声音开关(开启)

3.PWR ON 开机模式,STD或FST 标准开机模式或快速开机模式,一般选择标准模式

4.AMUTE 自动静音开关(关闭)

5.CITY 城市模式调节,STD城市标准模式,LOX减低X频灵敏度模式

6.BANDS DFT 频段的调整,X频(一般关闭),K频STD标准K 频,PULS脉冲K频,HYPR高灵敏度K频,(选择HYPR高灵敏度K频),KA频(开启),POP(开启),LSR激光测速(开启),SWS 中国没有的频段(关闭)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

REV.AInformation furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.aADM9690One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: 781/329-4700World Wide Web Site: Fax: 781/326-8703© Analog Devices, Inc., 2000Power Supply and Watchdog TimerMonitoring CircuitFUNCTIONAL BLOCK DIAGRAMV V RESET(1)RESET(2)FEATURESPrecision Voltage Monitor (4.31 V)Watchdog Timeout MonitorSelectable Watchdog Timeout—0.75 ms, 1.5 ms,12.5 ms, 25 ms Two RESET Outputs APPLICATIONSMicroprocessor Systems Computers Printers ControllersIntelligent InstrumentsGENERAL DESCRIPTIONThe ADM9690 contains a voltage monitoring comparator and a watchdog timer monitor. It is designed to monitor the 5V power supply to a microprocessor and the microprocessor opera-tion via a watchdog function.The voltage monitoring comparator monitors the voltage on V MON . If it drops outside tolerance, as will happen during a power-fail, two reset signals are generated. Both reset signals go active (low) simultaneously. They will remain active while V MON is below the threshold, and for 50 ms (RESET(1)) or 60 ms (RESET(2)) after V MON climbs above the reset thresh-old. RESET(1) is intended to provide a power-on reset signal for the µP while RESET(2) is used to hold additional circuitry in a reset state until the µP has regained control following a power-up. The voltage monitoring circuitry remains operational with V CC as low as 2 V.The watchdog timer monitoring circuit is designed to monitor the activity on the WDI input. This input is normally connected to an output line on the µP. Its function is to check that the microprocessor has not stalled in an infinite loop. If there is a period of inactivity for the watchdog timeout period, both reset outputs are activated. As above, RESET(1) remains low for 50 ms while RESET(2) remains low for an additional 10 ms.The watchdog timer is restarted when RESET(1) goes inactive.The actual watchdog timeout period is adjustable using two select inputs SEL1 and SEL2.The ADM9690 is available in an 8-lead SOIC package. It is specified over the industrial temperature range.ADM9690–SPECIFICATIONS(V CC = Full Operating Range. T A = T MIN to T MAX unless otherwise noted) Parameter Min Typ Max Units Test Conditions/CommentsV CC OPERATING VOLTAGE RANGE 4.3 5.5VSUPPLY CURRENT55100µARESET AND WATCHDOG TIMERReset Voltage Threshold 4.2 4.31 4.42V V MON Falling T A = 0°C to +70°C Reset Threshold Hysteresis30mVReset Timeout Delay (t1)5075ms Figure 7, 8RESET(2) Timeout Delay (t2)1015ms Figure 7, 8WATCHDOG TIMEOUT PERIOD (TWD)0.40.75 1.28ms SEL2 = 0, SEL1 = 01.0 1.52.4ms SEL2 = 0, SEL1 = 19.012.519ms SEL2 = 1, SEL1 = 0182538ms SEL2 = 1, SEL1 = 1WDI INPUT PULSEWIDTH100ns V IL = 0.4, V IH = 3.5 VRESET(1)/(2) Output Voltage0.10.4V I SINK = 3.2 mA0.30.4V I SINK = 10 mA,0.450.7V I SINK = 15 mA,3.5V I SOURCE = 1 µAWDI INPUT THRESHOLDLogic Low0.8V150 ns PulseLogic High 3.5V150 ns PulseWDI Input Current 1.25µA WDI = V CC–5–1.2µA WDI = 0 VSEL1/2 Input Current–1+1µA SEL = V CC–10–510µA SEL = 0 VSpecifications subject to change without notice.–2–REV. AADM9690–3–REV. A ABSOLUTE MAXIMUM RATINGS*(T A = +25°C unless otherwise noted)V CC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +6 V V MON . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to V CC + 0.3 V Input CurrentV CC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 200 mA GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 200 mA Digital Output Current . . . . . . . . . . . . . . . . . . . . . . . 200 mA Power Dissipation, R-8 SOIC . . . . . . . . . . . . . . . . . . 400 mW θJA Thermal Impedance . . . . . . . . . . . . . . . . . . . . . . 120°C/W Industrial (A Version) . . . . . . . . . . . . . . . . . . –40°C to +85°C Lead Temperature (Soldering, 10 secs) . . . . . . . . . . . +300°C Vapor Phase (60 secs) . . . . . . . . . . . . . . . . . . . . . . +215°C Infrared (15 secs) . . . . . . . . . . . . . . . . . . . . . . . . . . +220°C Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C ESD Rating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 kV*Stresses above those listed under Absolute Maximum Ratings may cause perma-nent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum ratings for extended periods of time may affect device reliability.ORDERING GUIDETemperature Package Package Model Range Description Option ADM9690AR–40°C to +85°C8-Lead Narrow SO-8Body SOICPIN FUNCTION DESCRIPTIONSMnemonic FunctionV CC Power Supply Input; +5 V.V MON Voltage Monitoring Input.GND0 V. Ground reference for all signals.RESET(1)Logic Output. RESET(1) goes low if V MON falls below the Reset Threshold or the Watch-dog timer is not serviced within its timeout period. The reset threshold is typically 4.4 V for the ADM9690. RESET(1) remains low for 50 ms after V CC returns above the thresh-old. RESET(1) also goes low for 50 ms if the Watchdog Timer is not serviced within its timeout period.RESET(2)Logic Output. RESET(2) goes low simulta-neously with RESET(1) but remains low for an additional 10 ms.WDIWatchdog Input. If an edge is not detected on WDI within the selectable watchdog timeout period, RESET(1) and RESET(2) are forced low for their respective timeout periods. The watchdog timer restarts with each positive or negative going transition on the WDI line. Following a reset it is restarted when RESET(1) goes inactive (high). The Watch-dog Timer may be disabled if WDI is left floating or is driven to midsupply.SEL1, 2Watchdog Timeout selection inputs. Refer to Table I.PIN CONFIGURATIONV MON WDIV CCGND SEL1SEL2RESET(1)RESET(2)ADM9690–4–REV. A–Typical Performance CurvesCH1 1.0V CH2M 500ms V CC1.0V CH1380mVRESETFigure 1.Reset Output Voltage vs. SupplyTEMPERATURE – C604.4104.4084.4064.4044.402R E S E T V O L T A G E T H R E S H O L D – V o l t s4.4004.398Figure 2.Reset Voltage Threshold vs. TemperatureFigure 5.Typical Application CircuitV CC – Volts10W A T C H D O G A N D R E S E T T I M E O U T P E R I O D – m s2.55.53.0 3.5 4.04.55.06.0 6.5Figure 3.Watchdog and Reset Timeout Period vs. Supply @ –40°CTEMPERATURE – CA72.068.8–60120–30030609071.671.270.870.470.069.669.2Figure 4.Supply Current vs. TemperatureADM9690–5–REV. AWhen V after V V MONRESET(1)RESET(2)Figure 7.Power-On RESET Timing WDIRESET(1)RESET(2)Figure 8.Watchdog RESET TimingADM9690–6–REV. AOUTLINE DIMENSIONSDimensions shown in inches and (mm).C 3135a –1.5–3/00 (r e v . A )P R I N T E D I N U .S .A .8-Lead Narrow Body SOIC(SO-8)PLANEBSC °。