IRFBE_datasheet

IR2104_datasheet

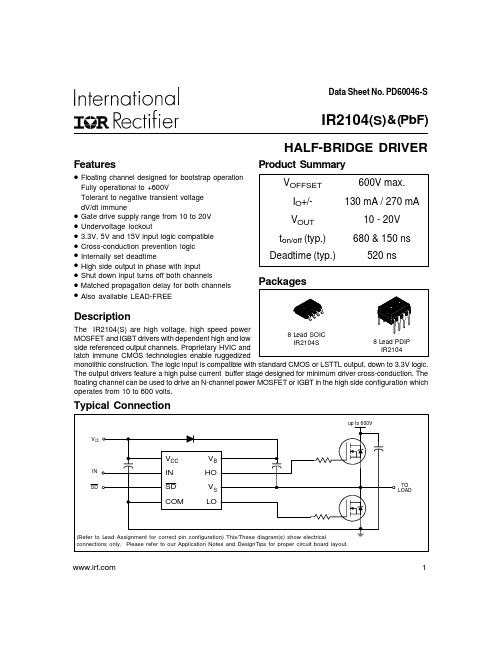

Data Sheet No. PD60046-STypical ConnectionProduct SummaryHALF-BRIDGE DRIVERFeatures•Fully operational to +600VdV/dt immune••Undervoltage lockout•••Internally set deadtime••••Also available LEAD-FREEDescriptionoperates from 10 to 600 volts. 1IR2104(S ) & (PbF)2IR2104(S) & (PbF)Absolute Maximum RatingsAbsolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to COM. The thermal resistance and power dissipation ratings are measured under board mounted and still air conditions.Note 1: Logic operational for V S of -5 to +600V. L ogic state held for V S of -5V to -V BS . (Please refer to the Design Tip DT97-3 for more details).Recommended Operating ConditionsThe Input/Output logic timing diagram is shown in Figure 1. For proper operation the device should be used within the recommended conditions. The V S offset rating is tested with all supplies biased at 15V differential.3IR2104(S) & (PbF)Dynamic Electrical CharacteristicsV BIAS (V CC , V BS ) = 15V, C L = 1000 pF and T A = 25°C unless otherwise specified.4IR2104(S) & (PbF)Functional Block DiagramLead DefinitionsSymbol DescriptionINLogic input for high and low side gate driver outputs (HO and LO), in phase with HO Logic input for shutdown V BHigh side floating supply HO High side gate drive output V S High side floating supply return V CC Low side and logic fixed supply LO Low side gate drive output COMLow side returnSDLead Assignments8 Lead PDIP 8 Lead SOICIR2104IR2104S12348765V CC IN SD COMV B HO V S LO12348765V CC IN SD COMV B HO V S LO5IR2104(S) & (PbF) Figure 5. Delay Matching Waveform DefinitionsFigure 4. Deadtime Waveform DefinitionsFigure 3. Shutdown Waveform DefinitionsFigure 1. Input/Output Timing DiagramSDINHO LOFigure 2. Switching Time Waveform Definitions6IR2104(S) & (PbF)7IR2104(S) & (PbF)8IR2104(S) & (PbF)9IR2104(S) & (PbF)10IR2104(S) & (PbF)11IR2104(S) & (PbF)IR2104(S) & (PbF)13IR2104(S) & (PbF)14IR2104(S) & (PbF)LEADFREE PART MARKING INFORMATIONORDER INFORMATIONPer SCOP 200-002Basic Part (Non-Lead Free)8-Lead PDIP IR2104 order IR21048-Lead SOIC IR2104S order IR2104S Leadfree Part8-Lead PDIP IR2104 order IR2104PbF 8-Lead SOIC IR2104S order IR2104SPbFIR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245 Tel: (310) 252-7105This product has been qualified per industrial levelData and specifications subject to change without notice. 4/2/2004。

IR2011SPBF;IR2011PBF;IR2011STRPBF;IR2011;IR2011S;中文规格书,Datasheet资料

1

/

IR2011(S) & (PbF)

Absolute Maximum Ratings

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to COM. The thermal resistance and power dissipation ratings are measured under board mounted and still air conditions.

Symbol

VB VS VHO VCC VLO VIN dVs/dt PD RTHJA TJ TS TL

Definition

High side floating supply voltage High side floating supply offset voltage High side floating output voltage Low side fixed supply voltage Low side output voltage Logic input voltage (HIN & LIN) Allowable offset supply voltage transient (figure 2) Package power dissipation @ TA £ +25°C Thermal resistance, junction to ambient Junction temperature Storage temperature Lead temperature (soldering, 10 seconds) (8-lead DIP) (8-lead SOIC) (8-lead DIP) (8-lead SOIC)

H3C SR6604[6608]路由器 安装指导

![H3C SR6604[6608]路由器 安装指导](https://img.taocdn.com/s3/m/67fdebde50e2524de5187ee2.png)

H3C SR6604/SR6608路由器安装指导杭州华三通信技术有限公司资料版本:T1-08040C-20110810-C-1.10Copyright © 2007-2011 杭州华三通信技术有限公司及其许可者版权所有,保留一切权利。

未经本公司书面许可,任何单位和个人不得擅自摘抄、复制本书内容的部分或全部,并不得以任何形式传播。

H3C、、Aolynk、、H3Care、、TOP G、、IRF、NetPilot、Neocean、NeoVTL、SecPro、SecPoint、SecEngine、SecPath、Comware、Secware、Storware、NQA、VVG、V2G、V n G、PSPT、XGbus、N-Bus、TiGem、InnoVision、HUASAN、华三均为杭州华三通信技术有限公司的商标。

对于本手册中出现的其它公司的商标、产品标识及商品名称,由各自权利人拥有。

由于产品版本升级或其他原因,本手册内容有可能变更。

H3C保留在没有任何通知或者提示的情况下对本手册的内容进行修改的权利。

本手册仅作为使用指导,H3C尽全力在本手册中提供准确的信息,但是H3C并不确保手册内容完全没有错误,本手册中的所有陈述、信息和建议也不构成任何明示或暗示的担保。

安全声明重要!在产品上电启动之前,请阅读本产品的安全与兼容性信息。

IMPORTANT! See Compliance and Safety information for the product before connecting to the supply.您可以通过以下步骤获取本产品的安全与兼容性信息:To obtain Compliance and Safety information, follow these steps:(1) 请访问网址:/Technical_Documents;Go to /Technical_Documents.(2) 选择产品类型以及产品型号;Choose the desired product category and model.(3) 您可以从安全与兼容性手册或安装手册中获取安全与兼容性信息。

IRGP4086PBF;中文规格书,Datasheet资料

tf

Fall time

td(on)

Turn-On delay time

tr

Rise time

— 65 —

— 30 —

IC = 25A, VCC = 196V

— 33 — ns RG = 10Ω, L=200μH, LS= 200nH

td(off) tf tst

EPULSE

Turn-Off delay time Fall time Shoot Through Blocking Time

2

/

240

VGE = 18V

200

VGE = 15V

VGE = 12V

160

VGE = 10V VGE = 8.0V

120

VGE = 6.0V

ICE (A)

80

40

0

0

4

8

12

16

VCE (V)

Fig 1. Typical Output Characteristics @ 25°C

––– 29 ––– ––– 65 ––– ––– 22 ––– — 36 — — 31 — — 112 —

S VCE = 25V, ICE = 25A nC VCE = 200V, IC = 25A, VGE = 15Ve

IC = 25A, VCC = 196V ns RG = 10Ω, L=200μH, LS= 200nH

Parameter Thermal Resistance Junction-to-Case-(each IGBT) d Case-to-Sink (flat, greased surface) Junction-to-Ambient (typical socket mount) d Weight

IRLML2803TRPBF;中文规格书,Datasheet资料

Gate-to-Source Charge

0.48 0.72 nC VDS = 24V

Qgd

Gate-to-Drain ("Miller") Charge

1.1 1.7

VGS = 10V, See Fig. 6 and 9

td(on)

Turn-On Delay Time

3.9

2

/

ID , Drain-to-Source Current (A)

10

VGS

TOP

15V

10V

7.0V

5.5V

4.5V

4.0V

3.5V

BOTTOM 3.0V

1

0.1 0.1

3.0V

20μs PULSE WIDTH

TJ = 25°C

A

1

10

VDS , Drain-to-Source Voltage (V)

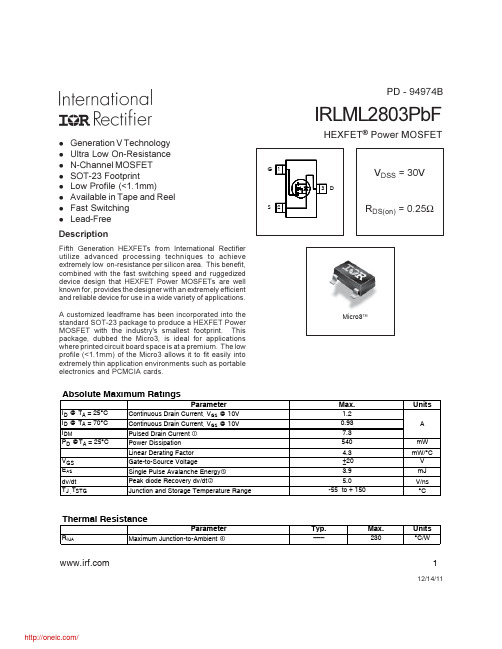

A customized leadframe has been incorporated into the standard SOT-23 package to produce a HEXFET Power MOSFET with the industry's smallest footprint. This package, dubbed the Micro3, is ideal for applications where printed circuit board space is at a premium. The low profile (<1.1mm) of the Micro3 allows it to fit easily into extremely thin application environments such as portable electronics and PCMCIA cards.

IRF7389TRPBF;IRF7389PBF;中文规格书,Datasheet资料

Min. Typ. Max. Units

Conditions

N-Ch 30 P-Ch -30

V

VGS = 0V, ID = 250µA VGS = 0V, ID = -250µA

N-Ch P-Ch

0.022 0.022

V/°C

Reference to 25°C, ID = 1mA Reference to 25°C, ID = -1mA

IDSS

IGSS Qg Qgs Qgd td(on) tr td(off) tf Ciss Coss Crss

Drain-to-Source Leakage Current

Gate-to-Source Forward Leakage Total Gate Charge Gate-to-Source Charge Gate-to-Drain ("Miller") Charge Turn-On Delay Time Rise Time Turn-Off Delay Time Fall Time Input Capacitance Output Capacitance Reverse Transfer Capacitance

P-Ch -2.5 A

N-Ch 30

ISM

Pulsed Source Current (Body Diode)

P-Ch -30

VSD

Diode Forward Voltage

N-Ch 0.78 1.0 P-Ch -0.78 -1.0

V

TJ = 25°C, IS = 1.7A, VGS = 0V TJ = 25°C, IS = -1.7A, VGS = 0V

IRF720PBF;IRF720LPBF;IRF720;中文规格书,Datasheet资料

Power MOSFETIRF720, SiHF720Vishay SiliconixFEATURES•Dynamic dV/dt Rating •Repetitive Avalanche Rated •Fast Switching •Ease of Paralleling •Simple Drive Requirements•Compliant to RoHS Directive 2002/95/ECDESCRIPTIONThird generation Power MOSFETs from Vishay provide the designer with the best combination of fast switching,ruggedized device design, low on-resistance and cost-effectiveness.The TO-220AB package is universally preferred for all commercial-industrial applications at power dissipation levels to approximately 50 W. The low thermal resistance and low package cost of the TO-220AB contribute to its wide acceptance throughout the industry.Notesa.Repetitive rating; pulse width limited by maximum junction temperature (see fig. 11).b.V DD = 50 V, starting T J = 25 °C, L = 30 mH, R g = 25 Ω, I AS = 3.3 A (see fig. 12).c.I SD ≤ 3.3 A, dI/dt ≤ 65 A/μs, V DD ≤ V DS , T J ≤ 150 °C.d. 1.6 mm from case.PRODUCT SUMMARYV DS (V)400 VR DS(on) (Ω)V GS = 10 V1.8Q g (Max.) (nC)20Q gs (nC) 3.3Q gd (nC)11ConfigurationSingleTO-220ABGDSORDERING INFORMATIONPackage TO-220AB Lead (Pb)-free IRF720PbF SiHF720-E3 SnPbIRF720SiHF720ABSOLUTE MAXIMUM RATINGS (T C = 25 °C, unless otherwise noted)PA AMETE SYMBOL LIMIT UNIT Drain-Source Voltage V DS400VGate-Source Voltage V GS ± 20VContinuous Drain Current V GS at 10 VT C = 25 °C I D3.3A T C = 100 °C2.1Pulsed Drain Current a I DM 13Linear Derating Factor0.40W/°C Single Pulse Avalanche Energy b E AS 190mJ Repetitive Avalanche Current a I AR 3.3 A Repetitive Avalanche Energy a E AR 5.0mJ Maximum Power Dissipation T C = 25 °CP D 50WPeak Diode Recovery dV/dt cdV/dt 4.0V/ns Operating Junction and Storage Temperature Range T J , T stg- 55 to + 150°C Soldering Recommendations (Peak Temperature)for 10 s 300d Mounting Torque6-32 or M3 screw10 lbf · in1.1N · mIRF720, SiHF720Vishay SiliconixNotesa.Repetitive rating; pulse width limited by maximum junction temperature (see fig. 11).b.Pulse width ≤ 300 μs; duty cycle ≤ 2 %.THERMAL RESISTANCE RATINGSPA AMETE SYMBOL TYP.MAX.UNITMaximum Junction-to-Ambient R thJA -62°C/W Case-to-Sink, Flat, Greased Surface R thCS 0.50-Maximum Junction-to-Case (Drain)R thJC- 2.5IRF720, SiHF720Vishay Siliconix TYPICAL CHARACTERISTICS (25 °C, unless otherwise noted)Fig. 1 - Typical Output Characteristics, T C = 25 °C Fig. 2 - Typical Output Characteristics, T C = 150 °CFig. 3 - Typical Transfer Characteristics Fig. 4 - Normalized On-Resistance vs. TemperatureIRF720, SiHF720 Vishay SiliconixFig. 5 - Typical Capacitance vs. Drain-to-Source Voltage Fig. 6 - Typical Gate Charge vs. Gate-to-Source Voltage Fig. 7 - Typical Source-Drain Diode Forward Voltage Fig. 8 - Maximum Safe Operating AreaIRF720, SiHF720Vishay SiliconixFig. 9 - Maximum Drain Current vs. Case TemperatureFig. 10a - Switching Time Test CircuitFig. 10b - Switching Time WaveformsFig. 11 - Maximum Effective Transient Thermal Impedance, Junction-to-CaseIRF720, SiHF720Vishay SiliconixFig. 12a - Unclamped Inductive Test CircuitFig. 12b - Unclamped Inductive WaveformsFig. 12c - Maximum Avalanche Energy vs. Drain CurrentFig. 13a - Basic Gate Charge Waveform Fig. 13b - Gate Charge Test CircuitIRF720, SiHF720Vishay SiliconixFig. 14 - For N-ChannelVishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several q ualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see /ppg?91043.Package InformationVishay SiliconixTO-220ABNote* M = 1.32 mm to 1.62 mm (dimension including protrusion)Heatsink hole for HVMMILLIMETERSINCHESDIM.MIN.MAX.MIN.MAX.A 4.25 4.650.1670.183b 0.69 1.010.0270.040b(1) 1.20 1.730.0470.068c 0.360.610.0140.024D 14.8515.490.5850.610E10.0410.510.3950.414e 2.41 2.670.0950.105e(1) 4.88 5.280.1920.208F 1.14 1.400.0450.055H(1)6.09 6.480.2400.255J(1) 2.41 2.920.0950.115L 13.3514.020.5260.552L(1)3.32 3.820.1310.150Ø P 3.54 3.940.1390.155Q2.603.000.1020.118ECN: X10-0416-Rev. M, 01-Nov-10DWG: 5471Legal Disclaimer Notice VishayDisclaimerALL PRODU CT, PRODU CT SPECIFICATIONS AND DATA ARE SU BJECT TO CHANGE WITHOU T NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively,“Vishay”), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.Statements regarding the suitability of products for certain types of applications are based on Vishay’s knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer’s responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and/or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer’s technical experts. Product specifications do not expand or otherwise modify Vishay’s terms and conditions of purchase, including but not limited to the warranty expressed therein.Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk and agree to fully indemnify and hold Vishay and its distributors harmless from and against any and all claims, liabilities, expenses and damages arising or resulting in connection with such use or sale, including attorneys fees, even if such claim alleges that Vishay or its distributor was negligent regarding the design or manufacture of the part. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.Material Category PolicyVishay Intertechnology, Inc. hereb y certifies that all its products that are identified as RoHS-Compliant fulfill the definitions and restrictions defined under Directive 2011/65/EU of The European Parliament and of the Council of June 8, 2011 on the restriction of the use of certain hazardous substances in electrical and electronic equipment (EEE) - recast, unless otherwise specified as non-compliant.Please note that some Vishay documentation may still make reference to RoHS Directive 2002/95/EC. We confirm that all the products identified as being compliant to Directive 2002/95/EC conform to Directive 2011/65/EU.分销商库存信息:VISHAYIRF720PBF IRF720LPBF IRF720。

IRLML6401TRPBF;中文规格书,Datasheet资料

Fig 1. Typical Output Characteristics

Fig 2. Typical Output Characteristics

100.0

2.0

-I D , Drain-to-Source Current (Α )

T J = 25°C

10.0

RDS(on) , Drain-to-Source On Resistance (Normalized)

0.1

20µs PULSE WIDTH Tj = 25°C

0.01 0.1 1 10 100

20µs PULSE WIDTH Tj = 150°C

0.01 0.1 1 10 100

-V DS , Drain-to-Source Voltage (V)

-VDS, Drain-to-Source Voltage (V)

1200 VGS = 0V, f = 1 MHZ Ciss = C gs + Cgd, C ds SHORTED Crss = C gd

10

ID = -4.3A VDS =-10V

1000

-VGS , Gate-to-Source Voltage (V)

C, Capacitance(pF)

800

Ciss

Min. Typ. Max. Units ––– ––– ––– ––– ––– ––– ––– ––– 22 8.0 -1.3 A -34 -1.2 33 12 V ns nC

Conditions MOSFET symbol showing the G integral reverse p-n junction diode. TJ = 25°C, IS = -1.3A, VGS = 0V TJ = 25°C, IF = -1.3A di/dt = -100A/µs

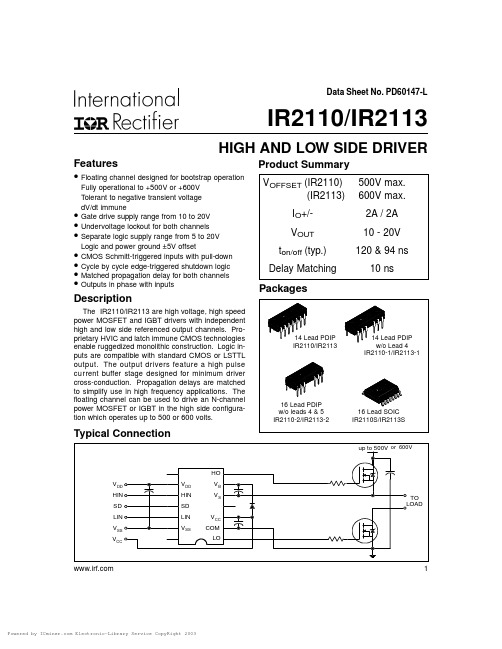

IR2110_datasheet

Min.

VS + 10 Note 1 Note 1 VS 10 0 VSS + 4.5 -5 VSS -40

Max.

VS + 20 500 600 VB 20 VCC VSS + 20 5 VDD 125

Units

V

°C

Note 1: Logic operational for VS of -4 to +500V. Logic state held for VS of -4V to -VBS.

Packages

14 Lead PDIP IR2110/IR2113

14 Lead PDIP w/o Lead 4 IR2110-1/IR2113-1

16 Lead PDIP w/o leads 4 & 5 IR2110-2/IR2113-2

16 Lead SOIC IR2110S/IR2113S

Typical Connection

Symbol

VIH VIL VOH VOL ILK IQBS IQCC IQDD IIN+ IINVBSUV+ VBSUVVCCUV+ VCCUVIO+ IO-

Definition

Logic “1” input voltage Logic “0” input voltage High level output voltage, VBIAS - VO Low level output voltage, VO Offset supply leakage current Quiescent VBS supply current Quiescent VCC supply current Quiescent VDD supply current Logic “1” input bias current Logic “0” input bias current VBS supply undervoltage positive going threshold VBS supply undervoltage negative going threshold VCC supply undervoltage positive going threshold VCC supply undervoltage negative going threshold Output high short circuit pulsed current Output low short circuit pulsed current

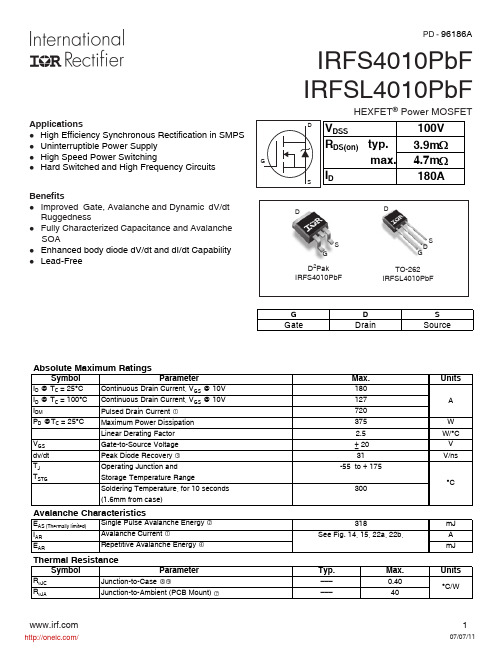

IRFS4010TRLPBF;IRFS4010PBF;IRFS4010TRRPBF;IRFSL4010PBF;中文规格书,Datasheet资料

100

ID, Drain-to-Source Current (A)

ID, Drain-to-Source Current (A)

1

0.1 0.1

4.0V

≤60μs PULSE WIDTH Tj = 25°C

1

10

100

VDS, Drain-to-Source Voltage (V)

Fig 1. Typical Output Characteristics

mended footprint and soldering echniques refer to application note #AN-994. Rθ is measured at TJ approximately 90°C RθJC value shown is at time zero

D Drain

S Source

Absolute Maximum Ratings

Symbol

Parameter

ID @ TC = 25°C ID @ TC = 100°C IDM PD @TC = 25°C

Continuous Drain Current, VGS @ 10V

c Continuous Drain Current, VGS @ 10V

à (Body Diode)

VSD

Diode Forward Voltage

trr

Reverse Recovery Time

Qrr

Reverse Recovery Charge

IRRM

Reverse Recovery Current

ton

Forward Turn-On Time

Min. Typ. Max. Units

IRF360_DataSheet

TO-3

Features:

n n n n n

Repetitive Avalanche Ratings Dynamic dv/dt Rating Hermetically Sealed Simple Drive Requirements Ease of Paralleling

Absolute Maximum Ratings

Ω

Test Conditions

VGS = 0V, ID = 1.0mA Reference to 25°C, ID = 1.0mA VGS = 10V, ID = 16A ➃ VGS = 10V, ID =25A ➃ VDS = VGS, ID =250µA VDS > 15V, IDS = 16A ➃ VDS=320V, VGS=0V VDS =320V VGS = 0V, TJ = 125°C VGS = 20V VGS = -20V VGS = 10V, ID =25A VDS = 200V VDD =200V, ID =25A, RG =2.35Ω

Min Typ Max Units

— — — — 0.42 30

°C/W

Test Conditions

Typical socket mount

For footnotes refer to the last page

2

IRF360

Fig 1. Typical Output Characteristics

Intrinsic turn-on time is negligible. Turn-on speed is substantially controlled by LS + LD.

Thermal Resistance

datasheetIRFP460

IRFP460N -CHANNEL 500V -0.22Ω-20A -TO-247PowerMESH ™MOSFETs TYPICAL R DS(on)=0.22Ωs EXTREMELY HIGH dv/dt CAPABILITY s 100%AVALANCHE TESTEDs VERY LOW INTRINSIC CAPACITANCES sGATE CHARGE MINIMIZEDDESCRIPTIONThis power MOSFET is designed using the company’s consolidated strip layout-based MESH OVERLAY ™process.This technology matches and improves the performances compared with standard parts from various sources.APPLICATIONSs HIGH CURRENT SWITCHINGs UNINTERRUPTIBLE POWER SUPPLY (UPS)s DC/DC COVERTERS FOR TELECOM,INDUSTRIAL,AND LIGHTING EQUIPMENT.®INTERNAL SCHEMATIC DIAGRAMSeptember 1998ABSOLUTE MAXIMUM RATINGSSymbol ParameterValue Unit V DS Drain-source Voltage (V GS =0)500V V DGR Drain-gate Voltage (R GS =20k Ω)500V V GS Gate-source Voltage±20V I D Drain Current (continuous)at T c =25o C 20A I D Drain Current (continuous)at T c =100o C 13A I DM (•)Drain Current (pulsed)80A P tot Total Dissipation at T c =25o C 250W Derating Factor2W/o C dv/dt(1)Peak Diode Recovery voltage slope 3.5V/nsT s tg Storage Temperature-65to 150o C T jMax.Operating Junction Temperature150oC(•)Pulse width limited by safe operating area(1)I SD ≤20 Α,di/dt ≤160A/µs,V DD ≤V (BR)DSS ,Tj ≤T JMAXTYPE V DSS R DS(on)I D IRFP460500V<0.27Ω20A123TO-2471/8THERMAL DATAR thj-case Rthj-amb R thc-sinkT l Thermal Resistance Junction-case MaxThermal Resistance Junction-ambient MaxThermal Resistance Case-sink TypMaximum Lead Temperature For Soldering Purpose0.5300.1300o C/WoC/Wo C/Wo CAVALANCHE CHARACTERISTICSSymbol Parameter Max Value UnitI AR Avalanche Current,Repetitive or Not-Repetitive(pulse width limited by T j max)20AE AS Single Pulse Avalanche Energy(starting T j=25o C,I D=I AR,V DD=50V)1000mJELECTRICAL CHARACTERISTICS(T case=25o C unless otherwise specified)OFFSymbol Parameter Test Conditions Min.Typ.Max.Unit V(BR)DSS Drain-sourceBreakdown VoltageI D=250µA V GS=0500VI DSS Zero Gate VoltageDrain Current(V GS=0)V DS=Max RatingV DS=Max Rating T c=125o C10100µAµAI GSS Gate-body LeakageCurrent(V DS=0)V GS=±20V±100nA ON(∗)Symbol Parameter Test Conditions Min.Typ.Max.Unit V GS(th)Gate ThresholdVoltageV DS=V GS I D=250µA234VR DS(on)Static Drain-source OnResistanceV GS=10V I D=12A0.220.27ΩI D(o n)On State Drain Current V DS>I D(o n)x R DS(on)ma xV GS=10V20A DYNAMICSymbol Parameter Test Conditions Min.Typ.Max.Unitg f s(∗)ForwardTransconductanceV DS>I D(o n)x R DS(on)ma x I D=12A13SC iss C os s C rss Input CapacitanceOutput CapacitanceReverse TransferCapacitanceV DS=25V f=1MHz V GS=0420050050pFpFpFIRFP460 2/8ELECTRICAL CHARACTERISTICS(continued)SWITCHING ONSymbol Parameter Test Conditions Min.Typ.Max.Unitt d(on) t r Turn-on TimeRise TimeV DD=250V I D=10AR G=4.7 ΩV GS=10V(see test circuit,figure1)3215nsnsQ g Q gs Q gd Total Gate ChargeGate-Source ChargeGate-Drain ChargeV DD=400V I D=20A V GS=10V1002137130nCnCnCSWITCHING OFFSymbol Parameter Test Conditions Min.Typ.Max.Unitt r(Voff) t f t c Off-voltage Rise TimeFall TimeCross-over TimeV DD=400V I D=20AR G=4.7 ΩV GS=10V(see test circuit,figure5)202547nsnsnsSOURCE DRAIN DIODESymbol Parameter Test Conditions Min.Typ.Max.UnitI SD I SDM(•)Source-drain CurrentSource-drain Current(pulsed)2080AAV SD(∗)Forward On Voltage I SD=20A V GS=0 1.6Vt rr Q rr I RRM Reverse RecoveryTimeReverse RecoveryChargeReverse RecoveryCurrentI SD=20A di/dt=100A/µsV DD=100V T j=150o C(see test circuit,figure3)700925nsµCA(∗)Pulsed:Pulse duration=300µs,duty cycle1.5%(•)Pulse width limited by safe operating areaSafe Operating Area Thermal ImpedanceIRFP4603/8Output Characteristics TransconductanceGate Charge vs Gate-source Voltage Transfer CharacteristicsStatic Drain-source On Resistance Capacitance VariationsIRFP460 4/8Normalized Gate Threshold Voltage vs Source-drain Diode Forward Characteristics Normalized On Resistance vs TemperatureIRFP4605/8Fig.1:Unclamped Inductive Load Test Circuit Fig.3:Switching Times Test Circuits For Resistive Load Fig.1:Unclamped Inductive Waveform Fig.4:Gate Charge test CircuitFig.5:Test Circuit For Inductive Load Switching And Diode Recovery TimesIRFP4606/8DIM.mm inch MIN.TYP.MAX.MIN.TYP.MAX.A 4.7 5.30.1850.209D 2.2 2.60.0870.102E 0.40.80.0160.031F 1 1.40.0390.055F32 2.40.0790.094F433.40.1180.134G 10.90.429H 15.315.90.6020.626L 19.720.30.7760.779L314.214.80.5590.4130.582L434.6 1.362L5 5.50.217M 230.0790.118Dia3.55 3.650.1400.144P025PTO-247MECHANICAL DATAIRFP4607/8Information furnished is believed to be accurate and reliable.However,STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use.No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics.Specification mentioned in this publication are subject to change without notice.This publication supersedes and replaces all information previously supplied.STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.The ST logo is a registered trademark of STMicroelectronics ©1998STMicroelectronics –Printed in Italy –All Rights ReservedSTMicroelectronics GROUP OF COMPANIESAustralia -Brazil -Canada -China -France -Germany -Italy -Japan -Korea -Malaysia -Malta -Mexico -Morocco -The Netherlands -Singapore -Spain -Sweden -Switzerland -Taiwan -Thailand -United Kingdom -U.S.A..IRFP4608/8。

IRF7756;中文规格书,Datasheet资料

HEXFET ® Power MOSFET3/17/04IRF7756PD -94159AIRF7756Source-Drain Ratings and CharacteristicsElectrical Characteristics @ T J = 25°C (unless otherwise specified)Notes:Repetitive rating; pulse width limited bymax. junction temperature.Pulse width ≤ 400µs ; duty cycle ≤ 2%.Surface mounted on FR-4 board, t ≤ 10sec .ParameterMin.Typ.Max.Units Conditions V (BR)DSSDrain-to-Source Breakdown Voltage -12––––––V V GS = 0V, I D = -250µA∆V (BR)DSS /∆T JBreakdown Voltage Temp. Coefficient –––-0.006–––V/°C Reference to 25°C, I D = -1mA ––––––0.040V GS = -4.5V, I D = -4.3A–––0.058V GS = -2.5V, I D = -3.4A–––0.087V GS = -1.8V, I D = -2.2A V GS(th)Gate Threshold Voltage -0.4–––-0.9V V DS = V GS , I D = -250µA g fs Forward Transconductance 13––––––S V DS = -10V, I D = -4.3A ––––––-1.0V DS = -9.6V, V GS = 0V ––––––-25V DS = -9.6V, V GS = 0V, T J = 70°C Gate-to-Source Forward Leakage ––––––-100V GS = -8.0V Gate-to-Source Reverse Leakage ––––––100V GS = 8.0V Q g Total Gate Charge–––1218I D = -4.3A Q gs Gate-to-Source Charge––– 1.8 2.7nC V DS = -6.0V Q gd Gate-to-Drain ("Miller") Charge ––– 2.9 4.4V GS = -4.5V t d(on)Turn-On Delay Time –––12–––V DD = -6.0V,t rRise Time–––18–––I D = -1.0A t d(off)Turn-Off Delay Time –––160–––R G = 6.0Ωt f Fall Time–––170––– V GS = -4.5V C iss Input Capacitance –––1400–––V GS = 0V C oss Output Capacitance–––310–––pF V DS = -10V C rssReverse Transfer Capacitance–––240–––ƒ = 1.0kHzI GSS µA ΩR DS(on)Static Drain-to-Source On-ResistanceI DSS Drain-to-Source Leakage Current nA nsIRF7756 3Fig 3. Typical Transfer CharacteristicsVs. Temperature0.51.01.52.0-V GS , Gate-to-Source Voltage (V)110100-I D , D r a i n -t o -S o u r c e C u r r e n t (Α)IRF7756Gate-to-Source VoltageFig 5. Typical Capacitance Vs.Drain-to-Source Voltage Fig 8. Maximum Safe Operating AreaForward Voltage110100-V DS , Drain-to-Source Voltage (V)04008001200160020002400C , C a p a c i t a n c e (p F )0.1110100-V DS , Drain-toSource Voltage (V)0.1110100-I D , D r a i n -t o -S o u r c e C u r r e n t (A )IRF7756 5Case TemperatureV DDV V Fig 10a. Switching Time Test CircuitFig 10b. Switching Time WaveformsIRF7756Fig 12. Typical On-Resistance Vs. DrainCurrentFig 11. Typical On-Resistance Vs. GateVoltageFig 13b. Gate Charge Test CircuitFig 13a.Basic Gate Charge Waveform VDSCurrent Sampling Resistors-V GS, Gate -to -Source Voltage (V)R D S (o n ), D r a i n -t o -S o u r c e O n R e s i s t a n c e (Ω)481216-I D , Drain Current (A)0.0200.0250.0300.0350.040R D S (o n ) , D r a i n -t o -S o u r c e O n R e s i s t a n c e (Ω)IRF7756 7Fig 14. Threshold Voltage Vs. Tempera-tureT J , Temperature ( °C )-V G S (t h ) G at e t h r e s h o l d V o l t a g e (V )Fig 15. Typical Power Vs. TimeTime (sec)P o w e r (W )TSSOP-8 Package Outline233 Kansas St., El Segundo, California 90245, USA Tel: (310) 252-7105TAC Fax: (310) 252-7903Visit us at for sales contact information. 3/049分销商库存信息: IRIRF7756。

IR115_datasheet (1)

Feb 21, 2011IR1153SFIXED 22.2kHz FREQUENCY, µPFC ONE CYCLE CONTROLIC WITH BROWN-OUT PROTECTIONFeaturesDescription Package• PFC IC with IR proprietary “One Cycle Control” • Continuous conduction mode boost type PFC • Fixed 22.2kHz switching frequency • Average current mode control • Input line sensed brownout protection • Output overvoltage protection • Open loop protection • Cycle by cycle peak current limit• VCC under voltage lockout • Programmable soft start • Micropower startup • User initiated micropower “Sleep Mode” • 750mA peak gate drive• Latch immunity and ESD protection The μPFC IR1153 power factor correction IC, based on IR proprietary"One Cycle Control" (OCC) technique, provides for high PF, low THD and excellent DC Bus regulation while enabling drastic reduction incomponent count, PCB area and design time as compared to traditional solutions. The IC is designed to operate in continuous conduction mode Boost PFC converters with average current mode control at a fixed 22.2kHz switching frequency. The IR1153 features include input-line sensed brown-out protection, dedicated pin for over voltage protection, cycle by cycle peak current limit, open loop protection, VCC UVLO, soft-start and micropower startup current of less than 75µA. In addition, for standby power requirements, the IC can be driven into a micropower sleep mode by pulling the OVP/EN pin low where the current consumption is less than 75uA. IR1153 is available in SO-8 package.Qualification InformationIndustrialQualification Level Comments: This family of ICs has passed JEDEC’s Industrial qualification.IR’s Consumer qualification level is granted by extension of the higherIndustrial level.Moisture Sensitivity LevelMSL2 260°C(per IPC/JEDEC J-STD-020)Machine ModelClass A(per JEDEC standard JESD22-A115)ESDHuman Body ModelClass 1A(per EIA/JEDEC standard EIA/JESD22-A114)IC Latch-Up Test Class I, Level A (per JESD78)RoHS Compliant YesAbsolute Maximum RatingsStresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. All voltages are absolute voltages referenced to COM. Thermal resistance and power dissipation are measured under board mounted and still air conditions.Parameters Symbol Min.Max.Units Remarks V CC Voltage V CC-0.3 20 V Not internally clampedISNS voltage V ISNS -10 0.3 VISNS Current I ISNS -2 2 mAV FB voltage V FB-0.3 6.5 VV OVP voltage V OVP -0.3 6.5 VV BOP voltage V BOP -0.3 9 VCOMP voltage V COMP -0.3 6.5 VGate Voltage V GATE-0.3 18 VJunction Temperature OperatingRange T J -40 150 °CStorage Temperature T S -55 150 °CThermal Resistance RθJA128 °C/WSOIC-8Package Power Dissipation P D 976 mWT AMB=25°C SOIC-8Electrical CharacteristicsThe electrical characteristics involve the spread of values guaranteed within the specified supply voltage and junction temperature range T J from – 25° C to 125°C. Typical values represent the median values, which are related to 25°C. If not otherwise stated, a supply voltage of V CC =15V is assumed for test condition.Supply SectionParameters SymbolMin.Typ.Max.Units Remarks Supply Voltage OperatingRangeV CC14 17 VV CC Turn On Threshold V CC ON 12.2 13.1 14 VV CC Turn Off Threshold(Under Voltage Lock Out)V CC UVLO 9.4 10.1 10.8 VV CC Turn On/Off Hysteresis V CC HYST 2.4 3 3.6 V7 mA C LOAD =1nF8 mA C LOAD =4.7nFOperating Current I CC3.5 5 mA OVP Mode, Inactive gateStart-up Current I CC START26 75 µA V CC=V CC ON - 0.2VSleep current I SLEEP 26 75 µAPinOVP/EN=V SLEEP-0.2VSleep Mode Threshold V SLEEP0.5 0.8 V Bias on OVP/EN pinOscillator SectionParameters SymbolMin.Typ.Max.Units Remarks20.2 22.2 24.2 T AMB=25°CFixed Oscillator Frequency f SW18.3 25 kHz -25°C < T AMB < 125°CMaximum Duty Cycle D MAX9399 % V COMP=5VMinimum Duty Cycle D MIN0 % Pulse SkippingProtection SectionParameters SymbolMin.Typ.Max.Units RemarksOpen Loop Protection (OLP)Threshold V OLP 17 19 21%V REFBias on VFB pinOutput OvervoltageProtection (OVP) Threshold V OVP 104 106 108%V REFBias on OVP/EN pinOutput Overvoltage Protection Reset Threshold V OVP(RST) 101 103 105%V REFBias on OVP/EN pinOVP Input Bias Current I OVP(Bias)-0.2 µABrown-out Protection(BOP) ThresholdV BOP0.66 0.76 0.86 V Bias on BOP pin Brown-out ProtectionEnable ThresholdV BOP(EN) 1.46 1.56 1.66 V Bias on BOP pin BOP Input Bias Current I BOP(Bias)-0.2 µAPeak Current LimitProtection ISNS Voltage Threshold (IPK LIMIT) V ISNS(PK)-0.58 -0.51 -0.44 V Bias on ISNS pinInternal Voltage Reference SectionParameters Symbol Min. Typ. Max. Units RemarksReference Voltage V REF 4.9 5 5.1 V Regulation Voltage on VFB pin,T AMB =25°C Line Regulation R REG 10 20 mV 14V < V CC < 17VTemp Stability T STAB0.4 % -25°C < T AMB < 125°C, Note 1 Total VariationΔV TOT4.835.12 V Line & TemperatureVoltage Error Amplifier SectionParameters Symbol Min. Typ. Max. Units RemarksTransconductance g m 35 49 59 µS30 44 58 T AMB =25°C Source Current (Normal Mode) I OVEA(SRC)17 80 µA-25°C < T AMB < 125°C-58 -44 -30 T AMB =25°CSink Current (Normal Mode) I OVEA(SNK)-80 -17 µA -25°C < T AMB < 125°C Soft Start Delay Time (calculated) t SS 35 msecR GAIN =8k Ω, C ZERO =0.33μF,C POLE =2nF V COMP Voltage (Fault) V COMP FLT 1 1.5 V @100uA steady stateEffective V COMP voltageV COMP EFF 4.7 4.9 5.1 VVFB Input Bias Current I FB(Bias) -0.2 µAOutput Low Voltage V OL 0.25 VOutput High Voltage V OH 5 5.45 VV COMP Start VoltageV COMP START210 325 435 mVCurrent Amplifier SectionMax.Units RemarksTyp.Min.Parameters SymbolDC Gain g DC 5.65 V/V2 kHz Average Current Mode, Note 1 Corner Frequency fCInput Offset Voltage V IO 4 16 mV Note 1ISNS Input Bias Current I ISNS(Bias)-57-13 µA170 320 470 nsBlanking Time TBLANKGate Driver SectionMax.Units Remarks Parameters SymbolMin.Typ.Gate Low Voltage V GLO 0.8 V I GATE = 200mA13.1 14.1 15.1 V CC=17V, Internally Clamped Gate High Voltage V GTH9.5 V V CC=11.5VnsC LOAD = 1nF, VCC=15V25Rise Time t rC LOAD = 4.7nF, VCC=15Vns6035C LOAD = 1nF, VCC=15VnsFall Time t fC LOAD = 4.7nF, VCC=15Vns65Output Peak Current I OPK750 mA C LOAD = 4.7nF, VCC=15V, Note 1 Gate Voltage at Fault V G fault0.08 V I GATE = 20mANote 1: Guaranteed by design, but not tested in productionBlock DiagramLead Assignments & DefinitionsIRS1144IR1153IR1144SIR1153 General DescriptionThe μPFC IR1153 IC is intended for power factor correction in continuous conduction mode Boost PFC converters operating at fixed switching frequency with average current mode control. The IC operates based on IR's proprietary "One Cycle Control" (OCC) PFC algorithm based on the concept of resettable integrator.Theory of OperationThe OCC algorithm based on the resettable integrator concept works using two loops - a slow outer voltage loop and a fast inner current loop. The outer voltage loop monitors the VFB pin and generates an error signal which controls the amplitude of the input current admitted into the PFC converter. In this way, the outer voltage loop maintains output voltage regulation. The voltage loop bandwidth is kept low enough to not track the 2xf AC ripple in the output voltage and thus generates an almost DC error signal under steady state conditions.The inner current loop maintains the sinusoidal profile of the input current and thus is responsible for power factor correction. The information about the sinusoidal variation in input voltage is inherently available in the input line current (or boost inductor current). Thus there is no need to sense the input voltage to generate a current reference. The current loop employs the boost inductor current information to generate PWM signals with a proportional sinusoidal variation. This controls the shape of the input current to be proportional to and in phase with the input voltage. Average current mode operation is envisaged by filtering the switching frequency ripple from the current sense signal using an appropriately sized on-chip RC filter. This filter also contributes to the bandwidth of the current control loop. Thus the filter bandwidth has to be high enough to track the 120Hz rectified, sinusoidal current waveform and also filter out the switching frequency ripple in the inductor current. In IR1153 this averaging function can effectively filter high ripple current ratios (as high as 40% at maximum input current) to accommodate designs with small boost inductances.The IC determines the boost converter instantaneous duty cycle based on the resettable integrator concept. The required signals are the voltage feedback loop error signal V m (which is the V COMP pin voltage minus a DC offset of V COMP,START) and the current sense signal V ISNS. The resettable integrator generates a cycle-by-cycle, saw-tooth signal called the PWM Ramp which has an amplitude V m and period 1/f SW hence a slope of V m*f SW. The current sense signal is amplified by the current amplifier by a factor g DC and fed into the summing node where it is subtracted from V m to generate the summer voltage (= V m–g DC*V ISNS). The summer voltage is compared with the PWM ramp by the PWM comparator of the IC to determine the gate drive duty cycle. The instantaneous duty is mathematically given by:D = (V m - g DC.V ISNS)/V mAssuming steady state condition where the voltage feedback loop is well regulated (V m & V OUT are DC signals) & hence instantaneous duty cycle follows the boost-converter equation (D = 1 – V IN(t)/V OUT), the control equation can be re-written as:V m = g DC.V ISNS/(V IN(t)/V OUT)Further, recognizing that V ISNS = I L(t).R SNS and re-arranging yields:g DC.I L(t).R SNS = V m V IN(t)/V OUTSince V m, V OUT & g DC are constant terms:I L(t) α V IN(t)Thus the inductor current follows the input voltage waveform & by definition power factor correction is achieved.Feature setFixed Frequency OperationThe IC is programmed to operate at a fixed frequency of 22.2kHz (Typ). Internalization of the oscillator offers excellent noise immunity even in the noisy PFC environment while integration of the oscillator into the OCC core of the IC eliminates need for digital calibration circuits. Both these factors render the gate drive jitter free thus contributing to elimination of audible noise in PFC magnetics.IC Supply Circuit & Low start-up currentThe IR1153 UVLO circuit maintains the IC in UVLO mode during start-up if VCC pin voltage is less than the VCC turn-on threshold, V CC,ON and current consumption is less than 75uA. Should VCC pin voltage should drop below V CC,UVLO during normal operation, the IC is pushed back into UVLO mode and VCC pin has to exceed V CC,ON again for normal operation. There is no internal voltage clamping of the VCC pin.User initiated Micropower Sleep modeThe IC can be actively pushed into a micropower Sleep Mode where current consumption is less than 75uA by pulling OVP/EN pin below the Sleep threshold, V SLEEP even while VCC is above V CC,ON. This allows the user to disable PFC during application stand-by situations in order to meet stand-by regulations. Since V SLEEP is less than 1V, even logic level signals can be employed.IR1153SIR1153 General DescriptionProgrammable Soft StartThe soft start process controls the rate of rise of the voltage feedback loop error signal thus providing a linear increase of the RMS input current that the PFC converter will admit. The soft start time is essentially controlled by voltage error amplifier compensation components selected and is therefore user programmable to some degree based on desired voltage feedback loop crossover frequency.Gate Drive CapabilityThe gate drive output stage of the IC is a totem pole driver with 750mA peak current drive capability. The gate drive is internally clamped at 14.1V (Typ). Gate drive buffer circuits (especially cost-effective base-followers) can be easily driven with the GATE pin of the IC to suit any system power level.System Protection FeaturesIR1153 protection features include Brown-out protection (BOP), Open-loop protection (OLP), Overvoltage protection (OVP), Cycle-by-cycle peak current limit (IPK LIMIT), Soft-current limit and VCC under voltage lock-out (UVLO).- BOP is based on direct input line sensing using a resistor divider/RC filter network. If BOP pin falls below the Brown-out protection threshold V BOP, a Brown-out situation is immediately detected the following response is executed - the gate drive pulse is disabled, VCOMP is actively discharged and IC is pushed into Stand-by Mode. The IC re-enters normal operation only after BOP pin exceeds V BOP(EN). During start-up the IC is held in Stand-by Mode until this pin exceeds V BOP(EN).- OLP is activated whenever the VFB pin voltage falls below V OLP threshold. Once open loop is detected the following response is immediately executed - the gate drive is immediately disabled, VCOMP is actively discharged and the IC is pushed into Stand-by mode. There is no voltage hysteresis associated with this feature. During start-up the IC is held in Stand-by Mode until VFB exceeds V OLP. - The OVP pin is a dedicated pin for overvoltage protection that safeguards the system even if there is a break in the VFB feedback loop due to resistor divider failure etc. An overvoltage fault is triggered when OVP pin voltage exceeds the V OVP threshold of 106%VREF. The response of the IC is to immediately terminate the gate drive output and hold it in that state. The gate drive is re-enabled only after OVP pin voltage drops below V OVP(RST) threshold of 103% VREF. The exact voltage level at which overvoltage protection is triggered can be programmed by the user by carefully designing the OVP pin resistor divider. Itis recommended NOT to set the OVP voltage trigger limit less than 106% of DC bus voltage, since this can endanger the situation where the OVP reset limit will be less than the DC bus voltage regulation point – in this condition the voltage loop can become unstable.- Soft-current limit is an output voltage fold-back type protection feature encountered when the PFC converter input current exceeds to a point where the V m voltage saturates. As mentioned earlier, the amplitude of input current is directly proportional to V m, the error voltage of the feedback loop. V m is clamped to a certain maximum voltage inside the IC (given by V COMP,EFF parameter in datasheet). If the input current causes the V m voltage to saturate at its maximum value, then any further increase in input current will cause the duty cycle to droop which immediately forces the V OUT voltage of the PFC converter to fold-back. Since the highest current is at the peak of the AC sinusoid, the droop in duty cycle commences at the peak of the AC sinusoid when the soft-current limit is encountered. In most converters, the design of the current sense resistor is performed based on soft-current limit (i.e. V m saturation) and at the system condition which demands highest input current (minimum V AC & maximum P OUT).- Cycle-by-cycle peak current limit protection instantaneously turns-off the gate output whenever the ISNS pin voltage exceeds V ISNS(PK) threshold in magnitude. The gate drive is held in the low state as long as the overcurrent condition persists. The gate drive is re-enabled when the magnitude of ISNS pin voltage falls below the V ISNS(PK) threshold. This protection feature incorporates a leading edge blanking circuit to improve noise immunity.IR1153S IR1153 Pin DescriptionPin COM: This is ground potential pin of the IC. All internal devices are referenced to this point. Pin COMP: External circuitry from this pin to ground compensates the system voltage loop and programs the soft start time. The COMP pin is essentially the output of the voltage error amplifier. The voltage loop error signal V m used in the control algorithm is derived from V COMP (V m =V COMP–V COMP,START). V COMP is actively discharged using an internal resistance to below V COMP,START threshold whenever the IC is pushed into Stand-by mode (BOP or OLP condition) or UVLO/Sleep mode. The gate drive output and logic functions of the IC are inactive if VCOMP is less than V COMP,START. Also during start-up, the VCOMP voltage has to be less than V COMP,START in order to commence operation (i.e. a pre-bias on VCOMP will not allow IC to commence operation).Pin ISNS: ISNS pin is tied to the input of the current sense amplifier of the IC. The voltage at this pin, which provides the current sense information to the IC, has to be a negative voltage wrt the COM pin. Also since the IC is based on average current mode, the entire inductor current information is necessary. A current sense resistor, located below system ground along the return path to the bridge rectifier, is the preferred current sensing method. ISNS pin is also the inverting input to the cycle-by-cycle peak current limit comparator. Whenever V ISNS exceeds V ISNS(PK) threshold in magnitude, the gate drive is instantaneously disabled. Any external filtering of the ISNS pin must be performed carefully in order to ensure that the integrity of the current sense signal is maintained for cycle-by-cycle peak current limit protection.Pin BOP (Brown-out Protection): This pin is used to sense the rectified AC input line voltage through a resistor divider/capacitor network which is in effect a voltage division and averaging network, representing a scaled down signal of the average rectified input voltage (average DC voltage + 2xf AC ripple). During start-up the BOP pin voltage has to exceed V BOP(EN) in order to enable the IC to exit Stand-by mode and enter normal operation. A Brown-out situation is detected whenever the pin voltage falls below V BOP and the IC is pushed into Stand-by mode. Subsequently the pin has to exceed V BOP(EN) for the IC to exit Stand-by and resume normal operation.Pin OVP/EN: The OVP/EN pin is connected to the non-inverting input of the OVP(OVP) overvoltage comparator shown in the block diagram and thus is used to detect output overvoltage situations. The output voltage information is communicated to the OVP pin using a resistive divider. This pin also serves the second purpose of an ENABLE pin. The OVP/EN pin can be used to activate the IC into “micropower sleep” mode by pulling the voltage on this pin below the V SLEEP threshold.Pin VFB: The converter output voltage is sensed via a resistive divider and fed into this pin. VFB pin is the inverting input of the output voltage error amplifier. The non-inverting input of this amplifier is connected to an internal 5V reference. The impedance of the divider string must be low enough that it does not introduce substantial error due to the input bias currents of the amplifier, yet high enough to minimize power dissipation. Typical value of external divider total impedance will be around 2MΩ. VFB pin is also the inverting input to the Open Loop comparator. The IC is held in Stand-by Mode whenever VFB pin voltage is below V OLP threshold.Pin VCC: This is the supply voltage pin of the IC and sense node for the undervoltage lock out circuit. It is possible to turn off the IC by pulling this pin below the minimum turn off threshold voltage, V CC(UVLO) without damage to the IC. This pin is not internally clamped.Pin GATE: This is the gate drive output of the IC. It provides a drive current of ±0.75A peak with matched rise and fall times. The gate drive output of the IC is clamped at 14.1V(Typ).IR1153 Modes of operationReferenced to States & Transition DiagramUVLO/Sleep Mode: The IC is in the UVLO/Sleep mode when VCC pin voltage is below V CC,ON at start-up or when VCC pin voltage drops below V CC,UVLO during normal operation or when OVP/EN pin voltage is below V SLEEP. The UVLO/Sleep mode is accessible from any other state of operation. This mode can be actively invoked by pulling the OVP/EN pin below V SLEEP even if VCC pin voltage is above V CC,ON. In the UVLO/Sleep state, the gate drive circuit is inactive, most of the internal circuitry is unbiased and the IC draws a quiescent current of I SLEEP which is less than 75uA. Also, the internal logic of the IC ensures that whenever the Sleep mode is actively invoked, the COMP pin is actively discharged below V COMP,START threshold prior to entering the sleep mode, in order to facilitate soft-start upon resumption of operation.Stand-by Mode: The IC is placed in Stand-by mode whenever an Open-loop and/or a Brown-out situation is detected. A Brown-out situation is sensed when BOP pin voltage is less than V BOP(EN) prior to system start-up and when BOP pin voltage drops below V BOP after start-up. An Open-loop situation is sensed anytime VFB pin voltage is less than V OLP. All internal circuitry is biased in the Stand-by Mode, but the gate is inactive and the IC draws a few mA of current. This state is accessible from any other state of operation of the IC. COMP pin is actively discharged to below V COMP,START whenever this state is entered from normal operation in order to facilitate soft-start upon resumption of operation. Soft Start Mode: During system start-up, the soft-start mode is activated once the VCC voltage has exceeded V CC,ON, the VFB pin voltage has exceeded V OLP and BOP pin voltage has exceeded V BOP(EN) and VCOMP voltage is less than V COMP,START i.e. a pre-bias on COMP pin greater than V COMP,START threshold will not allow IC to commence operation. The soft start time is the time required for the VCOMP voltage to charge through its entire dynamic range i.e. through V COMP,EFF. As a result, the soft-start time is dependent upon the component values selected for compensation of the voltage loop on the COMP pin. To an extent, keeping in mind the voltage feedback loop considerations, the soft-system start time is programmable.As VCOMP voltage rises gradually, the IC allows a higher and higher RMS current into the PFC converter. This controlled increase of the input current amplitude contributes to reducing system component stress during start-up.Normal Mode: The IC enters the normal operating mode once the soft start transition has been completed (for all practical purposes there is essentially no difference between the soft-start and normal modes). At this point the gate drive is switching and all protection functions of the IC are active. If, from the normal mode, the IC is pushed into either a Stand-by mode or UVLO/Sleep mode then COMP pin is actively discharged below V COMP,START and system will go through soft-start upon resumption of operation.OVP Mode: The IC enters OVP mode whenever an overvoltage condition is detected. A system overvoltage condition is recognized when OVP/EN pin voltage exceeds V OVP threshold. When this happens the IC immediately disables the gate drive and holds it in that state. The gate drive is re-enabled only when OVP/EN pin voltages are less than V OVP(RST) threshold. This state is accessible from both the soft start and normal modes of operation.IPK LIMIT Mode: The IC enters IPK LIMIT mode whenever the magnitude of ISNS pin voltage exceeds the V ISNS(PK) threshold triggering cycle-by-cycle peak overcurrent protection. When this happens, the IC immediately disables the gate drive and holds it in that state. Gate drive is re-enabled when magnitude of ISNS pin voltage drops below V ISNS(PK) threshold. This state is accessible from both the soft start and normal modes of operation.State & Transitions DiagramV FB< VORV BOP< VIR1153 Timing DiagramsVCC Undervoltage LockoutV o l t a g e o n V C C p i nSLEEPSLEEP V o l t a g e o n V O V P p i nSTAND-BY V o lta geo nB O Pp i n0.010.11107.0 V 9.0 V 11.0 V 13.0 V 15.0 V 17.0 VI S U P P L Y (m A )Supply voltageFigure 1: Supply Current vs.Supply Voltage9.0 V9.5 V 10.0 V 10.5 V 11.0 V 11.5 V 12.0 V 12.5 V 13.0 V 13.5 V 14.0 V -50 °C0 °C50 °C 100 °C 150 °CV C C U V L O T h r e s h o l d sT emperatureVCC UV+VCC UV-Figure 2: Undervoltage Lockout vs.Temperature3.13.23.33.43.53.63.73.83.94.04.1-50 °C0 °C50 °C 100 °C 150 °CI Q C C Q u i e s c e n t C u r r e n t (m A )T emperatureI CC @ Gate InactiveFigure 3: Icc Currrent vs. Temperature10.015.020.025.030.035.040.0-50 °C0 °C 50 °C 100 °C 150 °CC u r r e n t (u A )T emperatureI CCSTART and I SLEEPISLEEPICCSTARTFigure 4: Startup Current and SleepCurrent vs. Temperature21.021.522.022.523.023.5-50 °C0 °C 50 °C 100 °C 150 °C S w i t c h i n g F r e q u e n c y (K H z )T emperatureVcomp=5V Vcomp=1VFigure 5: Switching Frequency vs.Temperature 4.954.974.995.015.035.05-50 °C0 °C 50 °C 100 °C 150 °CR e f e r e n c e V o l t a g e (V )T emperatureFigure 6: Reference Voltage vs.Temperature40.042.044.046.048.050.052.054.0-50 °C0 °C50 °C 100 °C150 °CE A T r a n s c o n d u c t a n c e g m (u S )T emperatureFigure 7: Voltage Error Amplifier Transconductance vs. Temperature0.610.620.630.640.650.660.670.6-50 °C0 °C 50 °C 100 °C 150 °CE r r o r A m p l i f i e r S o u r c e /S i n k C u r r e n t (u A )T emperatureSource SinkFigure 8: Voltage Error Amplifier Source& Sink Current vs. Temperature5.505.555.605.655.705.755.80-50 °C0 °C 50 °C 100 °C 150 °CC u r r e n t S e n s e A m p l i f i e rD C G a i n g D C (V /V )T emperatureFigure 9: Current Amplifier DC Gain vs.Temperature-0.60-0.55-0.50-0.45-0.40-50 °C0 °C 50 °C 100 °C 150 °CP e a k C u r r e n t L i m i t T h r e s h o l d (V )T emperatureFigure 10: Peak Current Limit ThresholdV ISNS(PK) vs. Temperature1.001.021.041.061.081.10-50 °C0 °C 50 °C 100 °C 150 °C O V P T h r e s h o l d (%V r e f )T emperatureVOVPVOVP(RST)Figure 11: Over Voltage ProtectionThresholds vs. Temperature0.60.70.80.91.01.11.21.31.41.51.6-50 °C0 °C 50 °C 100 °C 150 °CB O P T h r e s h o l d (V )T emperatureVBOP(EN)VBOPFigure 12: Brown-Out Protection Thresholds vs. TemperaturePackage Details: SOIC8NTape and Reel Details: SOIC8NC LOADED TAPE FEED DIRECTIONPart Marking InformationOrdering InformationStandard PackComplete Part Number Base Part Number Package TypeForm QuantityTube/Bulk 95 IR1153SPBF IR1153S SOIC8NTape and Reel2500 IR1153STRPBFThe information provided in this document is believed to be accurate and reliable. However, International Rectifier assumes no responsibility for the consequences of the use of this information. International Rectifier assumes no responsibility for any infringement of patents or of other rights of third parties which may result from the use of this information. No license is granted by implication or otherwise under any patent or patent rights of International Rectifier. The specifications mentioned in this document are subject to change without notice. This document supersedes and replaces all information previously supplied.For technical support, please contact IR’s Technical Assistance Center/technical-info/WORLD HEADQUARTERS:233 Kansas St., El Segundo, California 90245Tel: (310) 252-7105。

IRF520NPBF;中文规格书,Datasheet资料

The TO-220 package is universally preferred for all commercial-industrial applications at power dissipation levels to approximately 50 watts. The low thermal resistance and low package cost of the TO-220 contribute to its wide acceptance throughout the industry.

IDSS

Drain-to-Source Leakage Current

IGSS

Qg Qgs Qgd td(on) tr td(off) tf

Gate-to-Source Forward Leakage Gate-to-Source Reverse Leakage Total Gate Charge Gate-to-Source Charge Gate-to-Drain ("Miller") Charge Turn-On Delay Time Rise Time Turn-Off Delay Time Fall Time

––– ––– 25 ––– ––– 250

µA VDS = 100V, VGS = 0V VDS = 80V, VGS = 0V, TJ = 150°C

––– ––– 100 nA VGS = 20V

––– ––– -100

VGS = -20V

––– ––– 25

ID = 5.7A

––– ––– 4.8 nC VDS = 80V

20µs PULSE WIDTH

1

TC = 175°C

IRF6648TRPBF;IRF6648TR1PBF;中文规格书,Datasheet资料

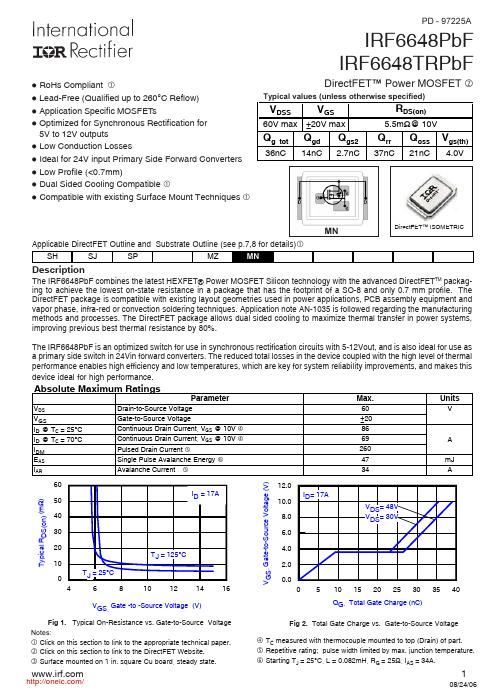

DirectFET Power MOSFETThe IRF6648PbF combines the latest HEXFET® Power MOSFET Silicon technology with the advanced DirectFET TM packag-ing to achieve the lowest on-state resistance in a package that has the footprint of a SO-8 and only 0.7 mm profile. The DirectFET package is compatible with existing layout geometries used in power applications, PCB assembly equipment and vapor phase, infra-red or convection soldering techniques. Application note AN-1035 is followed regarding the manufacturing methods and processes. The DirectFET package allows dual sided cooling to maximize thermal transfer in power systems,improving previous best thermal resistance by 80%.The IRF6648PbF is an optimized switch for use in synchronous rectification circuits with 5-12Vout, and is also ideal for use as a primary side switch in 24Vin forward converters. The reduced total losses in the device coupled with the high level of thermal performance enables high efficiency and low temperatures, which are key for system reliability improvements, and makes thisFig 1. Typical On-Resistance vs. Gate-to-Source VoltageFig 2. Total Gate Charge vs. Gate-to-Source VoltageDirectFET ISOMETRICMNl RoHs Compliantl Lead-Free (Qualified up to 260°C Reflow)l Application Specific MOSFET s lOptimized for Synchronous Rectification for 5V to 12V outputsl Low Conduction Lossesl Ideal for 24V input Primary Side Forward Converters l Low Profile (<0.7mm)l Dual Sided Cooling Compatiblel Compatible with existing Surface Mount TechniquesIRF6648PbF IRF6648TRPbFClick on this section to link to the appropriate technical paper. Click on this section to link to the DirectFET Website. T C measured with thermocouple mounted to top (Drain) of part. Repetitive rating; pulse width limited by max. junction temperature.Notes:46810121416V GS, Gate -to -Source Voltage (V)510152025303540Q G , Total Gate Charge (nC)PD - 97225AIRF6648PbFRepetitive rating; pulse width limited by max. junction temperature. Pulse width ≤ 400µs; duty cycle ≤ 2%.Notes:DD = 30V See Fig. 18GS = 0V iIRF6648PbFFig 3. Maximum Effective Transient Thermal Impedance, Junction-to-CaseUsed double sided cooling , mounting pad.Mounted on minimum footprint full size board with metalized back and with small clip heatsink.Notes:R θ is measured at T J of approximately 90°C.Surface mounted on 1 in. square Cu(still air).Mounted to a PCB with small clip heatsink (still air)Mounted on minimum footprint full size board with metalized back and with small clip heatsink (still air)t 1 , Rectangular Pulse Duration (sec)T h e r m a l R e s p o n s e ( Z )IRF6648PbFFig 7.Fig 8. Typical Capacitance vs.Drain-to-Source VoltageFig 9. Normalized Typical On-Resistance vs.Drain Current and Gate Voltage0.11101001000I D , D r a i n -t o -S o u r c e C u r r e n t (A )T J , Junction Temperature (°C)T y p i c a l R (N o r m a l i z e d )110100V DS , Drain-to-Source Voltage (V)100100010000C , C a p a c i t a n c e (p F )020*********I D , Drain Current (A)51015202530T y p i c a l R D S (o n ) (m Ω)IRF6648PbFFig 13. Threshold Voltage vs. TemperatureFig 12. Maximum Drain Current vs. Case TemperatureFig 10.Fig 14. Maximum Avalanche Energy vs. Drain Current01101001000I S D , R e v e r s e D r a i n C u r r e n t (A )255075100125150T C , Case Temperature (°C)0102030405060708090I D , D r a i n C u r r e n t (A )T J , Temperature ( °C )T y p i c a l V G S (t h ), G a t e t h r e s h o l d V o l t a g e (V )255075100125150Starting T J , Junction Temperature (°C)020406080100120140160180200E A S , S i n g l e P u l s e A v a l a n c h e E n e r g y (m J )IRF6648PbFDSCurrent Sampling ResistorsFig 15a. Gate Charge Test CircuitFig 15b. Gate Charge WaveformIdQgs1Qgs2Qgd QgodrFig 16b. Unclamped Inductive WaveformsI ASFig 16a. Unclamped Inductive Test CircuitFig 17b.Switching Time WaveformsV V DS90%10%d(on)d(off)rfFig 17a. Switching Time Test CircuitV DDIRF6648PbFFig 18. Diode Reverse Recovery Test Circuit for N-ChannelHEXFET®Power MOSFETs* V GS = 5V for Logic Level DevicesPlease see DirectFET application note AN-1035 for all details regarding the assembly of DirectFET.233 Kansas St., El Segundo, California 90245, USA Tel: (310) 252-7105TAC Fax: (310) 252-7903 Visit us at for sales contact information.08/06Note: For the most current drawings please refer to the IR website at:/package/分销商库存信息:IRIRF6648TRPBF IRF6648TR1PBF。

8F5E2 Datasheet说明书

8F5E2 DatasheetDocument HistoryContentsDocument History (2)Preface (4)Disclaimer (4)Customer Support Overview (4)ESD Warning (5)Precautions (6)Limited Product Warranty (6)Introduction (7)Product Features and Specifications (8)Interface function description (11)Typical Installation (13)Recovery Mode (13)Order Information (14)Mechanical Dimensions (15)PrefaceDisclaimerThe information contained within this user’s guide, including but not limited to any product specification, is subject to change without notice.Plink assumes no liability for any damages incurred directly or indirectly from any technical or typographical errors or omissions contained herein or for discrepancies between the product and the user’s guide.Customer Support OverviewIf you experience any difficulties after using the product, please freely contact us directly. Our tech can help you with product installation and difficulties.Our support section is available 24 hours a day, 7 days a week on our website at: /en/Jetson.html. Our technical support is always free.ESD WarningElectronic components and circuits are very sensitive to electrostatic discharge. Although the company will do anti-static protection design for the main interface on the circuit board when designing circuit board products, it is difficult to do anti-static safety protection for all components and circuits. Therefore, it is recommended to follow ESD safety precautions when handling any circuit board component.ESD protection measures include but are not limited to the following:- During transportation or storage, place the card in an ESD bag and do not take it out until installation.- Release the static electricity before touching the board. Using a discharge grounding wrist strap.- Operate the circuit board only in electrostatic discharge safety area.- Avoiding move circuit boards in carpeted areas.- Avoiding contact with components, try to handle the board by the edges.Precautions- Before using the product, please read this manual carefully and keep it properly for future reference- Please pay attention to and follow all warnings and guidelines marked on the product- Please use the matching power adapter to ensure the stability of current and voltage - Please use this product in a cool, dry and clean place- Do not use this product in the environment of alternating cold and heat to avoid condensation and damage to internal components- Do not splash any liquid on the product. It is forbidden to use organic solvent or corrosive liquid to clean the product- Do not use this product in dusty and messy environment. If it is not used for a long time, please pack the product- Do not use it in an environment with excessive vibration. Any falling or knocking may damage the lines and components- Do not plug and unplug the core board and peripheral modules when the power is on- Do not repair or disassemble the product by yourself. If the product fails, contact the company for repair in time- Do not modify or use unauthorized accessories by yourself, and the resulting damage will not be covered by warrantyLimited Product Warranty- Warranty period -Bottom plate and core plate: 3 years (non-human damage)- Contact informationContacts: RMAAddress: Room 718, Jinrongkemao Plaza, No. 15 Shangdi Xinxi Road, Haidian District, Beijing, ChinaE-mail: sales@Telephone:+86-010-********- Mailing instructions: Please contact the sale staff of the company in advance, then arrange technicians to verify and eliminate the errors caused by misoperation as soon as possible. After verification, please mail the equipment to the company.Please attach a list of items and the reason for failure when mailing for easy verification, so as to avoid loss and damage in the process of express delivery.Introduction8F5E2 is a IPC with NVIDIA® Jetson™ AGX Xavier and AGX ORIN 32GB core modules. The main interface is designed for electrostatic safety protection, and a high-reliability power supply application scheme is adopted. The input power supply has over voltage and reverse polarity protection functions, and has a wealth of external interfaces. The internal interface devices are all wide-temperature models.8F5E2 provides multiple independent Gigabit network ports through internal M.2 ports, miniPCIe ports, which is suitable for multi-network port scenarios.8F5E2 is designed based on worse environmental conditions and has good characteristics such as anti-seismic and dust-proof, and is suitable for V2X and other fields.Product Features and Specifications- Product size:198mm×197mm×45 mm- Power requirements:+12V- Working temperature:-25~+70℃- Weight:1340g- Optional expansion:32GB ~ 1TB SSD storage- Maximum scalability 512g TF card memory- 4G and WIFI module can be extended- The initial setting can be reset and restored*Remark:when this model is equipped with AGX Xavier module, only one USB Type A supports USB3.0, Supports only one M.2Key M connector and one miniPCIe connectorPanel and interface IDSFigure 1 Ports on the front panelFigure 2 Ports on the rear panel*There is no interface on the rear panel of the standard machine. The four network interfaces on the rear panel are optional. If you need to use them, please contact the sales staff in advance.Interface function descriptionTypical Installation- Ensure power off of all external system- Install the necessary external cables.(e.g. display cable connected to HDMI monitor, power input cable supplying power to the system, USB cable connecting keyboard and mouse...)- Connect the power cord to the power supply- 8F5E2 could be set as default automatic power on or switch on. Please consult the sales and technical staff of our company for specific methods.Recovery ModeJetson core module can work in normal mode and recovery mode. It can be operated in recovery mode to file system update, kernel update, boot loader update, BCT update and other operationsStep in Recovery mode:- Turn off the system power supply- Use a Micro-USB cable to connect OTG port of the 8F5E2 with USB of the Jetson developing host- Press and hold on Recovery button (REC) to supply system power. Keep REC button for 3seconds above, then release the recovery buttonThe system enters the Recovery mode, and you can perform subsequent operations.Order InformationE-commerce direct purchaseTaobao:https:///Jingdong:https:///index-11467104.html?from=pc Alibaba:https:///Mechanical Dimensions。

irfp200参数

irfp200参数英文回答:The IRFP200 is a power MOSFET transistor that is commonly used in various electronic applications. It is designed to handle high voltages and currents, making it suitable for power amplifiers, motor control circuits, and switching applications.One of the key parameters of the IRFP200 is its maximum drain-source voltage (Vds), which is typically rated at 100 volts. This means that the transistor can withstand a maximum voltage of 100 volts between its drain and source terminals.Another important parameter is the maximum drain current (Id), which is typically rated at 48 amps. This indicates the maximum current that can flow through the transistor when it is fully turned on.The IRFP200 also has a low on-resistance (Rds(on)), typically around 0.077 ohms. This low resistance allows for efficient power transfer and minimizes power losses in the transistor.Furthermore, the gate threshold voltage (Vgs(th)) of the IRFP200 is typically around 4 volts. This voltage level determines the minimum voltage required to turn on the transistor and allow current to flow from the drain to the source.In addition to these electrical parameters, the IRFP200 also has a TO-247 package, which provides good thermal dissipation and allows for easy mounting on a heat sink.Overall, the IRFP200 is a high-power MOSFET transistor with a maximum voltage rating of 100 volts, a maximum current rating of 48 amps, and a low on-resistance of 0.077 ohms. It is commonly used in applications that require high power handling and efficient switching.中文回答:IRFP200是一种功率MOSFET晶体管,广泛应用于各种电子设备中。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Power MOSFETIRFBE30, SiHFBE30Vishay SiliconixFEATURES•Dynamic dV/dt Rating •Repetitive Avalanche Rated •Fast Switching •Ease of Paralleling •Simple Drive Requirements •Lead (Pb)-free AvailableDESCRIPTIONThird generation Power MOSFETs from Vishay provide the designer with the best combination of fast switching,ruggedized device design, low on-resistance and cost-effectiveness.The TO-220 package is universally preferred for all commercial-industrial applications at power dissipation levels to approximately 50 W. The low thermal resistance and low package cost of the TO-220 contribute to its wide acceptance throughout the industry.Notesa.Repetitive rating; pulse width limited by maximum junction temperature (see fig. 11).b.V DD = 50 V, starting T J = 25 °C, L = 29 mH, R G = 25 Ω, I AS = 4.1 A (see fig. 12).c.I SD ≤ 4.1 A, dI/dt ≤ 100 A/µs, V DD ≤ 600, T J ≤ 150 °C.d. 1.6 mm from case.PRODUCT SUMMARYV DS (V)800R DS(on) (Ω)V GS = 10 V3.0Q g (Max.) (nC)78Q gs (nC)9.6Q gd (nC)45ConfigurationSingleTO-220GDSORDERING INFORMATIONPackage TO-220Lead (Pb)-free IRFBE30PbF SiHFBE30-E3 SnPbIRFBE30SiHFBE30ABSOLUTE MAXIMUM RATINGS T C = 25 °C, unless otherwise notedARAMETER SYMBOL LIMIT UNIT Drain-Source Voltage V DS800VGate-Source Voltage V GS ± 20 Continuous Drain Current V GS at 10 VT C = 25 °C I D4.1A T C = 100 °C2.6Pulsed Drain Current a I DM 16Linear Derating Factor1.0W/°C Single Pulse Avalanche Energy b E AS 260mJ Repetitive Avalanche Current a I AR 4.1 A Repetitive Avalanche Energy a E AR 13mJ Maximum Power Dissipation T C = 25 °CP D 125WPeak Diode Recovery dV/dt cdV/dt 2.0V/ns Operating Junction and Storage Temperature Range T J , T stg- 55 to + 150°C Soldering Recommendations (Peak Temperature)for 10 s 300d Mounting Torque6-32 or M3 screw10 lbf · in 1.1N · m * Pb containing terminations are not RoHS compliant, exemptions may apply捷多邦,您值得信赖的PCB打样专家!IRFBE30, SiHFBE30Vishay SiliconixNotesa.Repetitive rating; pulse width limited by maximum junction temperature (see fig. 11).b.Pulse width ≤ 300 µs; duty cycle ≤ 2 %.THERMAL RESISTANCE RATINGSARAMETER SYMBOL TY P .MAX.UNITMaximum Junction-to-Ambient R thJA -62°C/W Case-to-Sink, Flat, Greased Surface R thCS 0.50-Maximum Junction-to-Case (Drain)R thJC- 1.0IRFBE30, SiHFBE30Vishay Siliconix TYPICAL CHARACTERISTICS 25 °C, unless otherwise notedFig. 1 - Typical Output Characteristics, T C = 25 °CFig. 2 - Typical Output Characteristics, T C = 150 °CFig. 3 - Typical Transfer CharacteristicsFig. 4 - Normalized On-Resistance vs. TemperatureIRFBE30, SiHFBE30 Vishay SiliconixFig. 5 - Typical Capacitance vs. Drain-to-Source VoltageFig. 6 - Typical Gate Charge vs. Gate-to-Source VoltageFig. 7 - Typical Source-Drain Diode Forward VoltageFig. 8 - Maximum Safe Operating AreaIRFBE30, SiHFBE30Vishay SiliconixFig. 9 - Maximum Drain Current vs. Case Temperature Fig. 10a - Switching Time Test CircuitFig. 10b - Switching Time WaveformsFig. 11 - Maximum Effective Transient Thermal Impedance, Junction-to-CaseFig. 12a - Unclamped Inductive Test CircuitFig. 12b - Unclamped Inductive WaveformsIRFBE30, SiHFBE30Vishay SiliconixFig. 12c - Maximum Avalanche Energy vs. Drain CurrentFig. 13a - Basic Gate Charge WaveformFig. 13b - Gate Charge Test CircuitIRFBE30, SiHFBE30Vishay Siliconix Array Fig. 14 - For N-ChannelVishay Siliconix maintains wor ldwide manufactur ing capability. Pr oducts may be manufactur ed at one of sever al qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, par t mar king, andreliability data, see /ppg?91118.Disclaimer Legal Disclaimer NoticeVishayAll product specifications and data are subject to change without notice.Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, “Vishay”), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay’s terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.Product names and markings noted herein may be trademarks of their respective owners.。