NCP1510中文资料

KBPC1510中文资料

10

100

Fig. 2 - Forward Characteristics

KBPC10

Reverse Current ( uA )

Forward Current ( A )

10

KBPC35/50

KBPC15

1.0

1.0Tj=25 C0源自10.1KBPC25

Tj=25 C

0.01

0

20

40

60

80

100 120

140

0.01

0.2

0.4

0.6

0.8

1.0

1.2 1.4

1.6

Percent of Rated Peak Reverse Voltage (%)

Forward Voltage (V)

Fig. 3 - Non Repetitive Forward Surge Current

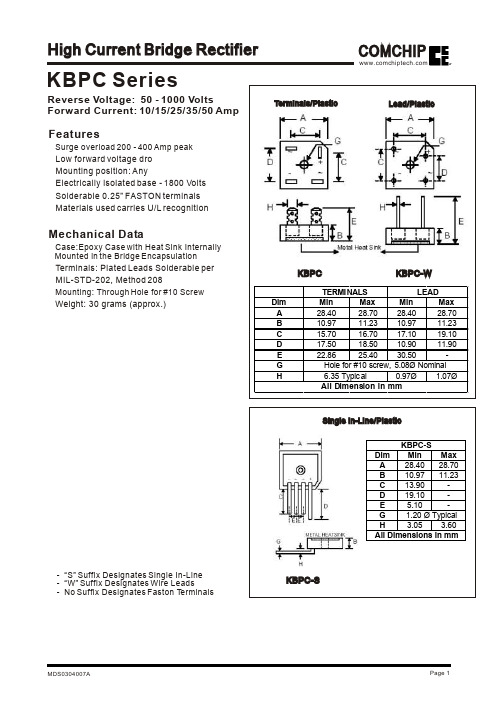

Mechanical Data

Case:Epoxy Case with Heat Sink Internally Mounted in the Bridge Encapsulation

Terminals: Plated Leads Solderable per MIL-STD-202, Method 208 Mounting: Through Hole for #10 Screw Weight: 30 grams (approx.)

NOTES: Also available on KBPC 10W/15W /25W/35W /50W series.

MDS0304007A

Page 2

元器件交易网

Silicon Bridge Rectifiers

光传输技术及应用智慧树知到期末考试章节课后题库2024年长春职业技术学院

光传输技术及应用智慧树知到期末考试答案章节题库2024年长春职业技术学院1.IP地址目前有两个版本,分别是()。

答案:IPv4###IPv62.OPUk帧的两个主要区域为()区域。

答案:OPUk开销###OPUk净荷3.B3 的中文名称为再生段误码监测字节()答案:错4.FFTC 的中文名称为光纤到路边()答案:对5.光传送网是以波分复用技术为基础、在光层组织网络的传送网,是DWDM下一代的骨干传送网,可以解决传统WDM网络对于波长/子波长业务调度能力差、组网保护能力弱等问题。

()答案:对6.材料的折射率随入射光频率的改变而改变的性质,称为色散。

()答案:对7.LPA的中文名称为高阶通道适配功能块()答案:对8.在一根光纤中由于光源光谱成分中不同波长的光波,在传播时速度的不同所引起的光脉冲展宽的现象,即入射的光脉冲在接收端发生脉冲展宽并引起信号畸变造成失真的现象叫色散。

()答案:对9.QoS技术包括流分类、流量监管、流量整形、接口限速、拥塞管理、拥塞避免等。

()答案:对10.光纤,完整名称叫做光导纤维,英文名是Optic Fiber。

它是一种由玻璃或塑料制成的纤维,可作为光传导工具。

()答案:对11.SOP的中文名称为紧凑型光通道保护板()答案:对12.PDH即同步数字系列,准同步方式也叫独立时钟方式,网内所有的时钟独立运行,虽然每个节点时钟精度都很高,但是因为时钟之间彼此独立运行,微小偏移的效果会积累。

()答案:错13.在WDM系统中,噪声的主要来源是光纤放大器。

()答案:对14.NCPL 的中文名称为主控时钟交叉板()答案:对15.RJ-11接口就是我们平常所说的网线接口。

()答案:错16.光端机就是光信号的终端设备()答案:对17.J0 的中文名称为再生段踪迹字节()答案:对18.OTUk(k=1,2,3,4)帧结构基于ODUk帧结构而来,并且采用前向纠错(FEC)扩展了该结构。

()答案:对19.光中继器是一种无源光器件。

LT1510IS中文

LT1510IS中文数据手册一、简介LT1510电流模式PWM电池充电器是最小、最简单和最高效的解决方案,可对包括锂离子(Li-Ion)、镍氢(NiMH)和镍镉(NiCd) 等需要恒定电流和/或恒定电压充电的新式可再充电电池进行快速充电。

内部开关能够提供 1.5ADC电流(2A峰值电流)。

0.1Ω内置电流检测电阻器使充电电流的设置非常简单易行。

需要一个电阻器(或一个由DAC提供的编程电流)将满充电电流(1.5A)的准确度设定在5%以内。

具0.5%基准电压准确度的LT1510可满足针对锂电池的严苛恒定电压充电要求。

LT1510能对2V至20V的电池进行充电。

无需实施电流的接地检测,而且电池的负端子可直接连接至地。

一个运行频率为200kHz(对于LT1510-5为500kHz)的饱和开关可提供高充电效率和小电感器尺寸。

在芯片和电池之间不需要布设一个隔离二极管,因为当拔去墙上适配器插头时,芯片将进入睡眠模式且仅吸收3μA电流。

另外,该器件还提供了软起动和停机功能。

LT1510采用具50°C/W热阻的16引脚熔丝引线功率SO封装、8引脚SO封装和16引脚PDIP 封装。

二、引脚SW:开关输出。

肖特基捕获二极管的引线长度必须非常短,且必须紧邻SW引脚和GND。

VCC:为了实现良好的旁路,需要使用10µF或更高的低ESR电容器,同时将引线长度保持最小。

VCC应在8V至28V之间,并且对于小于10V的VBAT,至少应比VBAT高2V;对于大于10V的VBAT,则应比VBAT高2.5V。

当VCC 低于7V时,开始欠压锁定并停止开关。

请注意,SW引脚至VCC引脚内部存在一个寄生二极管。

在有电池的情况下,请勿将VCC强制低于SW超过0.7V。

所有VCC引脚应靠近引脚短路。

BOOST:该引脚用于自举并驱动开关电源NPN晶体管至低导通电压,以降低功耗。

在正常操作中,打开开关时,VBOOST = VCC + VBAT。

NCP1015中文资料

Storage Temperature Range

ESD Capability, Human Body Model (HBM) (All pins except HV)

1 15

9.0 77 60 14 74 55 150 -60 to +150 2

demand.

3

5

DRAIN

Drain Connection

The internal drain MOSFET connection.

-

-

-

-

-

-

7

GND

The IC Ground

-

4

8

GND

The IC Ground

-

2

元器件交易网

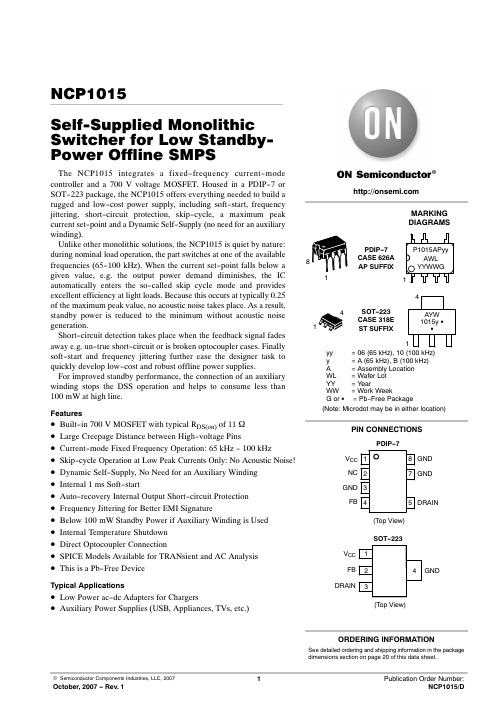

MARKING DIAGRAMS

8 1

PDIP-7 CASE 626A AP SUFFIX

P1015APyy AWL

YYWWG

1

4

4

SOT-223

CASE 318E

1

ST SUFFIX

AYW

1015yĂG G

1

yy y A WL YY WW G or G

= 06 (65 kHz), 10 (100 kHz) = A (65 kHz), B (100 kHz) = Assembly Location = Wafer Lot = Year = Work Week = Pb-Free Package

元器件交易网

NCP1015

Self-Supplied Monolithic Switcher for Low StandbyPower Offline SMPS

NCP1595A中文资料

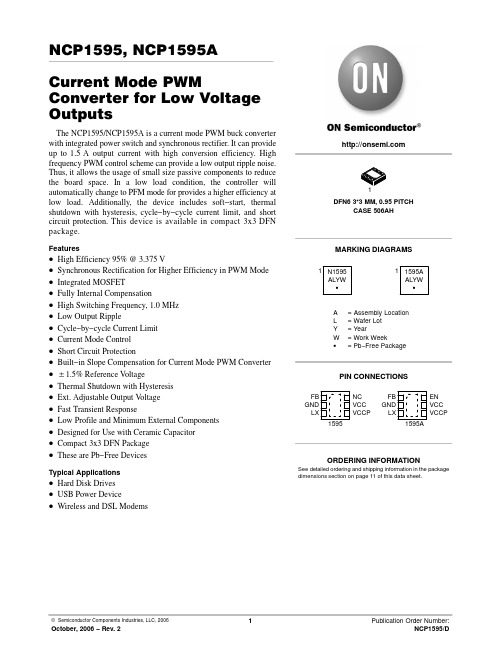

NCP1595, NCP1595A Current Mode PWM Converter for Low Voltage OutputsThe NCP1595/NCP1595A is a current mode PWM buck converter with integrated power switch and synchronous rectifier. It can provide up to 1.5 A output current with high conversion efficiency. High frequency PWM control scheme can provide a low output ripple noise. Thus, it allows the usage of small size passive components to reduce the board space. In a low load condition, the controller will automatically change to PFM mode for provides a higher efficiency at low load. Additionally, the device includes soft−start, thermal shutdown with hysteresis, cycle−by−cycle current limit, and short circuit protection. This device is available in compact 3x3 DFN package.Features•High Efficiency 95% @ 3.375 V•Synchronous Rectification for Higher Efficiency in PWM Mode •Integrated MOSFET•Fully Internal Compensation•High Switching Frequency, 1.0 MHz•Low Output Ripple•Cycle−by−cycle Current Limit•Current Mode Control•Short Circuit Protection•Built−in Slope Compensation for Current Mode PWM Converter •$1.5% Reference V oltage•Thermal Shutdown with Hysteresis•Ext. Adjustable Output V oltage•Fast Transient Response•Low Profile and Minimum External Components •Designed for Use with Ceramic Capacitor•Compact 3x3 DFN Package•These are Pb−Free DevicesTypical Applications•Hard Disk Drives•USB Power Device•Wireless and DSL ModemsSee detailed ordering and shipping information in the package dimensions section on page 11 of this data sheet.ORDERING INFORMATIONINV INFigure 1. Typical Operating CircuitABSOLUTE MAXIMUM RATINGSRating Symbol Value Unit Power Supply (Pin 4, 5)V IN7.0−0.3 (DC)−1.0 (100 ns)VInput / Output PinsPin 1,3,6V IO 6.5,−0.3 (DC)−1.0 (100 ns)VThermal Characteristics3x3 DFN Plastic PackageMaximum Power Dissipation @ T A = 25°CThermal Resistance Junction−to−AirP DR q JA145068.5mW°C/W Operating Junction Temperature Range (Note 4)T J−40 to + 150°C Operating Ambient Temperature Range T A−40 to + 85°C Storage Temperature Range T stg− 55 to +150°C Moisture Sensitivity Level (Note 3)1−Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.NOTE:ESD data available upon request.1.This device series contains ESD protection and exceeds the following tests:Human Body Model (HBM) 2.0 kV per JEDEC standard: JESD22−A114.Machine Model (MM) 200 V per JEDEC standard: JESD22−A115.tchup Current Maximum Rating: 150 mA per JEDEC standard: JESD78.3.Moisture Sensitivity Level (MSL): 1 per IPC/JEDEC standard: J−STD−020A.4.The maximum package power dissipation limit must not be exceeded.PD+TJ(max)*T AR q JAELECTRICAL CHARACTERISTICS(V IN = 5.0 V, V OUT = 1.2 V, T A = 25°C for typical value, −40°C v T A v 85°C for min/max values unless otherwise noted)Characteristic Symbol Min Typ Max Unit Operating Voltage V IN 4.0− 5.5V Under Voltage Lockout Threshold V UVLO 3.2 3.5 3.8V Under Voltage Lockout hysteresis V UVLO_HYS180mVP FET Leakage Current (Pin 5, 4) T A = 25°CT A = −40°C to 85°C I LEAK−P1.01015m AN FET Leakage Current (Pin 3, 2) T A = 25°CT A = −40°C to 85°C I LEAK−N1.01015m AFEEDBACK VOLTAGEFB Input Threshold (T A = −40°C to 85°C)V FB0.7880.8000.812V FB Input Current I FB10100nA Overvoltage Protect Higher than FB Threshold (T A = 25°C)V OVP 2.0 5.010.0% THERMAL SHUTDOWNThermal Shutdown Threshold (Note 5)T SHDN TBD160−°C Hysteresis T SDHYS30°C PWM SMPS MODEMinimum ON−Time TON MIN100ns Switching Frequency (T A = −40°C to 85°C)F OSC0.8 1.0 1.2MHz Internal PFET ON−Resistance (I LX = 100 mA, V IN = 5.0 V, T A = 25°C)(Note 5)R DS(ON)_P−0.20.3WInternal NFET ON−Resistance (I LX = 100 mA, V IN = 5.0 V, T A = 25°C)(Note 5)R DS(ON)_N−0.150.22W Maximum Duty Cycle D MAX−−100% Soft−Start Time (V IN = 5.0 V, V o = 1.2 V, I LOAD = 0 mA, T A = 25°C) (Note 6)T SS− 1.0−ms Main PFET Switch Current Limit (Note 5)I LIM 2.0 2.5A ENABLE (NCP1595A)Enable Threshold High (NCP1595A Only)V EN_H 1.8V Enable Threshold Low V EN_L0.4V Enable bias current ( EN = 0 V)I EN500TBD nA Total DeviceQuiescent Current Into V CCP (V IN = 5 V, V FB = 1.0 V, T A = 25°C)I CCP10m A Quiescent Current Into V CC (V IN = 5 V, V FB = 1.0 V, T A = 25°C)I CC900m A Shutdown Quiescent Current into V CC and V CCP (NCP1595A Only)(EN = 0, V IN = 5 V, V FB = 1.0 V, T A = 25°C)I CC_SD 1.5 3.0m A5.Values are design guarantee.6.Design guarantee, value depends on voltage at V OUT.PIN FUNCTION DESCRIPTIONSPin #Symbol Pin DescriptionNCP15951FB Feedback pin. Part is internally compensated. Only necessary to place a voltage divider or connect the out-put directly to this pin.2GND Ground3LX Pin connected internally to power switch. Connect externally to inductor.4VCCP Power connection to the power switch.5VCC IC power connection.6NC No ConnectionNCP1595A1FB Feedback pin. Part is internally compensated. Only necessary to place a voltage divider or connect the out-put directly to this pin.2GND Ground3LX Pin connected internally to power switch. Connect externally to inductor.4VCCP Power connection to the power switch.5VCC IC power connection.6EN Device Enable pin. This pin has an internal current source pull up. No connect is enable the device. With this pin pulled down below 0.4 V, the device is disabled and enters the shutdown mode.V INV INFigure 2. Detail Block DiagramEXTERNAL COMPONENT REFERENCE DATADevice V OUT Inductor Model Inductor (L1)C IN (C1)C OUT (C2)R1R2NCP1595/ NCP1595A 3.3 V CDC5D23 3R3 (1 A)CDRH6D38 3R3 (1.5 A)3.3 m H22 m F22 m F x 222 m F22 m F x 231 k10 kNCP1595/ NCP1595A 2.5 V CDC5D23 3R3 (1 A)CDRH6D38 3R3 (1.5 A)3.3 m H22 m F22 m F x 222 m F22 m F x 221 k10 kNCP1595/ NCP1595A 1.5 V CDC5D23 3R3 (1 A)CDRH6D38 3R3 (1.5 A)3.3 m H22 m F22 m F x 222 m F22 m F x 28 k10 kNCP1595/ NCP1595A 1.2 V CDC5D23 3R3 (1 A)CDRH6D38 3R3 (1.5 A)3.3 m H22 m F22 m F x 222 m F22 m F x 25 k10 kTYPICAL OPERATING CHARACTERISTICSLOW SIDE AMBIENT TEMPERATURE, (T A /°C)0.000.050.100.150.200.250.30−4002585Figure 3. Switch ON Resistance vs.TemperatureL O W S I D E S W I T C H O N R E S I S T A N C E /WFigure 4. Feedback Input Threshold vs.Temperature0.7850.7900.7950.8000.8050.8100.815−4002585AMBIENT TEMPERATURE, (T A /°C)F B I N P U T T H R E S H O L D V F B /VFigure 5. Switching Frequency vs.Temperature0.70.80.91.01.11.21.3−4002585AMBIENT TEMPERATURE, (T A /°C)S W I T C H F R E Q U E N C Y , F O S C /M H ZFigure 6. Main P−FET Current Limit vs.Temperature1.51.82.02.32.52.83.0−4002585AMBIENT TEMPERATURE, (T A /°C)M A I N P −F E T C U R R E N T L I M I T , I L I M /V600700800900100011001200−402585AMBIENT TEMPERATURE, (T A /°C)Q U I E S C E N T C U R R E N T I N T O V C C , I C C /m A Figure 7. Quiescent Current Into V CC vs.Temperature0123456−4002585S H U T D O W N Q U I E S C E N T C U R R E N T , I C C _S D /m AAMBIENT TEMPERATURE, (T A /°C)Figure 8. Shutdown Quiescent Current vs.TemperatureFigure 9. Output Voltage Change vs. OutputCurrentFigure 10. Efficiency vs. Output CurrentFigure 11. Output Voltage Change vs.Output CurrentFigure 12. Efficiency vs. Output CurrentFigure 13. Efficiency vs. Output CurrentFigure 14. Output Voltage Change vs.Output Current−1.5−1.0−0.50.00.51.01.51010010001000010100100010000−1.5−1.0−0.50.00.51.01.51010010001000010100100010000−1.5−1.0−0.50.00.51.01.51010010001000010100100010000O U T P U T E F F I C I E N C Y , %O U T P U T E F F I C I E N C Y , %O U T P U T V O L T A G E C H A N G E , D V O U T /%O U T P U T V O L T A G E C H A N G E , D V O U T /%O U T P U T V O L T A G E C H A N G E , D V O U T /%(V IN = 5 V, I LOAD = 700 mA, L = 3.3 m H, C OUT = 20 m F)Upper Trace: L X Pin Switching Waveform, 2 V / div.Middle Trace: Output Ripple Voltage, 20 mV / div.Lower Trace: Inductor Current, 1 A / div.(V IN = 5 V, I LOAD = 100 mA, L = 3.3 m H, C OUT = 20 m F)Upper Trace: L X Pin Switching Waveform, 2 V / div.Middle Trace: Output Ripple Voltage, 20 mV / div.Lower Trace: Inductor Current, 1 A / div.Figure 15. DCM Switching Waveform forV OUT = 3.3 V Figure 16. CCM Switching Waveform forV OUT = 3.3 V(V IN = 5 V, I LOAD = 100 mA, L = 3.3 m H, C OUT = 20 m F)Upper Trace: L X Pin Switching Waveform, 2 V / div.Middle Trace: Output Ripple Voltage, 20 mV / div.Lower Trace: Inductor Current, 1 A / div.(V IN = 5 V, I LOAD = 700 mA, L = 3.3 m H, C OUT = 20 m F)Upper Trace: L X Pin Switching Waveform, 2 V / div.Middle Trace: Output Ripple Voltage, 20 mV / div.Lower Trace: Inductor Current, 1 A / div.Figure 17. DCM Switching Waveform forV OUT = 1.2 V Figure 18. CCM Switching Waveform forV OUT = 1.2 V(V IN = 5 V, I LOAD = 10 mA, L = 3.3 m H, C OUT = 20 m F x 2)Upper Trace: Input Voltage, 2 V/ div.Middle Trace: Output Voltage, 1 V/ div.Lower Trace: Input Current, 1 A / div.(V IN = 5 V, I LOAD= 10 mA, L = 3.3 m H, C OUT = 20 m F x 2)Upper Trace: Input Voltage, 2 V/ div.Middle Trace: Output Voltage, 1 V / div.Lower Trace: Input Current, 1 A / div.Figure 19. Soft−Start Waveforms for V OUT = 3.3 V Figure 20. Soft−Start Waveforms for V OUT = 1.2 V(V IN = 5 V, L = 3.3 m H, C OUT = 20 m F x 2)Upper Trace: Output Dynamic Voltage, 100 mV / div. Lower Trace: Output Current, 500 mA / div.(V IN = 5 V, L = 3.3 m H, C OUT = 20 m F x 2)Upper Trace: Output Dynamic Voltage, 100 mV / div.Lower Trace: Output Current, 500 mA / div.(V IN = 5 V, L = 3.3 H, C OUT = 20 m F x 2)Upper Trace: Output Dynamic Voltage, 100 mV / div.Lower Trace: Output Current, 500 mA / div.(V IN = 5 V, L = 3.3 H, C OUT = 20 m F x 2)Upper Trace: Output Dynamic Voltage, 100 mV / div.Lower Trace: Output Current, 500 mA / div.Figure 21. Load Regulation for V OUT = 3.3 V Figure 22. Load Regulation for V OUT = 3.3 V Figure 23. Load Regulation for V OUT = 1.2 V Figure 24. Load Regulation for V OUT = 1.2 VDETAILED OPERATING DESCRIPTIONIntroductionNCP1595 operates as a current mode buck converter with switching frequency at 1.0 MHz. The P−Channel main switch is set by the positive edge of the clock cycle going into the PWM latch. The main switch is reset by the PWM latch in the following three cases:1.PWM comparator output trips as the peak inductorcurrent signal reaches a threshold level establishedby the error amplifier.2.The inductor current has reached the current limit.3.Overvoltage at output occurs.After a minimum dead time, the N−Channel synchronized switch will turn on and the inductor current will ramp down. If the inductor current ramps down to zero before the initiation of next clock cycle, the regulator runs at discontinuous conduction mode (DCM). Otherwise the regulator is at continuous conduction mode (CCM). The N−Channel switch will turn off when the clock cycle starts. The duty cycle is given by the ratio of output voltage to input voltage. The duty cycle is allowed to go to 100% to increase transient load response when going from light load to heavy load.Error Amplifier and Slope CompensationA fully internal compensated error amplifier is provided inside NCP1595. No external circuitry is needed to stabilize the device. The error amplifier provides an error signal to the PWM comparator by comparing the feedback voltage (800 mV) with internal voltage reference of 1.2 V. Current mode converter can exhibit instability at duty cycles over 50%. A slope compensation circuit is provided inside NCP1595 to overcome the potential instability. Slope compensation consists of a ramp signal generated by the synchronization block and adding this to the inductor current signal. The summed signal is then applied to the PWM comparator.Soft−Start and Current LimitA soft start circuit is internally implemented to reduce the in−rush current during startup. This helps to reduce the output voltage overshoot.The current limit is set to allow peak switch current in excess of 2 A. The intended output current of the system is 1.5 A. The ripple current is calculated to be approximately 350 mA with a 3.3 m H inductor. Therefore, the peak current at 1.5 A output will be approximately 1.7 A. A 2 A set point will allow for transient currents during load step. The current limit circuit is implemented as a cycle−by−cycle current limit. Each on−cycle is treated as a separate situation. Current limiting is implemented by monitoring the P−Channel switch current buildup during conduction with a current limit comparator. The output of the current limit comparator resets the PWM latch, immediately terminating the current cycle.Over−Voltage ProtectionOvervoltage occurs when the feedback voltage exceeds 5% of its regulated voltage. In this case, the P−Channel main switch will be reset and the N−Channel synchronized switch is turn on to sink current from the output voltage which helps to drop its feedback voltage back to the regulated voltage. Thermal ShutdownInternal Thermal Shutdown circuitry is provided to protect the integrated circuit in the event when maximum junction temperature is exceeded. When activated, typically at 160°C, the shutdown signal will disable the P−Channel and N−Channel switch. The thermal shutdown circuit is designed with 30°C of hysteresis. This means that the switching will not start until the die temperature drops by this amount. This feature is provided to prevent catastrophic failures from accidental device overheating. It is not intended as a substitute for proper heat sinking. NCP1595 is contained in the thermally enhanced DFN package.11APPLICATION INFORMATIONOutput Voltage SelectionThe output voltage is programmed through an external resistor divider connect from V OUT to FB then to GND.For internal compensation and noise immunity, the resistor from FB to GND should be in 10 k to 20 k ranges.The relationship between the output voltage and feedback resistor is given by:V OUT +V FB ǒ1)R1R2Ǔ(eq. 1)V OUT : Output voltage V FB : Feedback V oltageR1: Feedback resistor from V OUT to FB.R2: Feedback resistor from FB to GND.Input Capacitor selectionIn the PWM buck converter, the input current is pulsating current with switching noise. Therefore, a bypass input capacitor must choose for reduce the peak current drawn from the power supply. For NCP1595, low ESR ceramic capacitor of 10 m F should be used for most of cases. Also,the input capacitor should be placed as close as possible to the V CCA pin for effective bypass the supply noise.Inductor selectionThe inductor parameters are including three items, which are DC resistance, inductor value and saturation current.Inductor DC resistance will effect the convector overall efficiency, low DC resistor value can provide a higher efficiency. Thus, inductor value are depend on the inductorripple current, input voltage, output voltage, output current and operation frequency, the inductor value is given by:D IL +V OUT L F SWǒ1*V OUT V INǓ(eq. 2)D IL : peak to peak inductor ripple current L: inductor valueFSW: switching frequencyAfter selected a suitable value of the inductor, it should be check out the inductor saturation current. The saturation current of the inductor should be higher than the maximum load plus the ripple current.D IL(MAX)+D IOUT(MAX))D IL 2(eq. 3)D IL(MAX): Maximum inductor current D IOUT(MAX): Maximum output currentOutput Capacitor selectionOutput capacitor value is based on the target output ripple voltage. For NCP1595, the output capacitor is required a ceramic capacitors with low ESR value. Assume buck converter duty cycle is 50%. The output ripple voltage in PWM mode is given by:D VOUT [D ILǒ14 FSWCOUT)ESR Ǔ(eq. 4)In general, value of ceramic capacitor using 20 m F should be a good choice.ORDERING INFORMATIONDevicePackage Shipping †NCP1595MNR2G DFN−6(Pb−Free)3000 / Tape & Reel NCP1595AMNR2GDFN−6(Pb−Free)3000 / Tape & Reel†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.PACKAGE DIMENSIONSDFN6 3*3 MM, 0.95 PITCHCASE 506AH−01ǒmmǓ*For additional information on our Pb−Free strategy and solderingdetails, please download the ON Semiconductor Soldering andMounting Techniques Reference Manual, SOLDERRM/D.ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

NCP1015

DRAIN 3 (Top View)

©Ă Semiconductor Components Industries, LLC, 2007

Short-circuit detection takes place when the feedback signal fades away e.g. un-true short-circuit or is broken optocoupler cases. Finally soft-start and frequency jittering further ease the designer task to quickly develop low-cost and robust offline power supplies.

1

8

2

7

3

4

5

Figure 1. Typical Application Example

GND

PIN FUNCTION DESCRIPTION

Pin No.

SOT-223

PDIP-7

Pin Name

Function

Description

1

1

VCC

Powers the Internal Circuitry This pin is connected to an external capacitor of typically

For improved standby performance, the connection of an auxiliary winding stops the DSS operation and helps to consume less than 100ĂmW at high line.

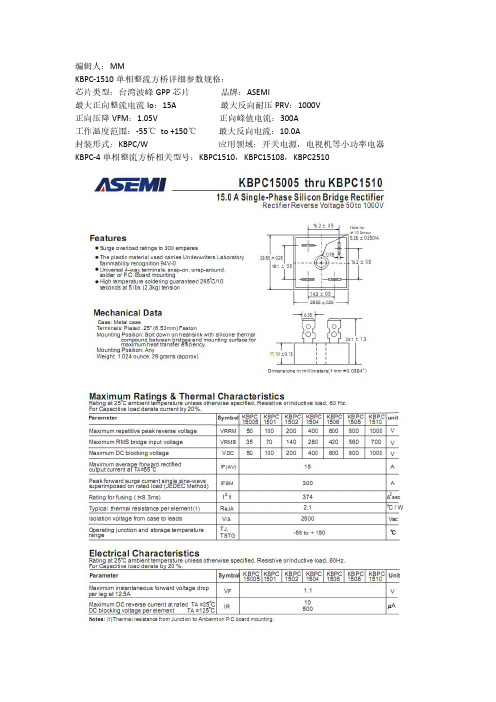

不用搜KBPC1510桥堆规格书了!ASEMI以将他摆在这里

编辑人:MM

KBPC-1510单相整流方桥详细参数规格:

芯片类型:台湾波峰GPP芯片品牌:ASEMI

最大正向整流电流Io:15A最大反向耐压PRV:1000V

正向压降VFM:1.05V正向峰值电流:300A

工作温度范围:-55℃to+150℃最大反向电流:10.0A

封装形式:KBPC/W应用领域:开关电源,电视机等小功率电器KBPC-4单相整流方桥相关型号:KBPC1510,KBPC15108,KBPC2510

强元芯电子是一家技术力量雄厚的公司,12年专注于电源领域的研发经验,可为客户提供全套的技术支持!本公司专业生产整流桥,肖特基,快恢复二极管,为ASEMI大陆地区一级代理商!强元芯在半导体行业有着12年的资质,以诚信经营为宗旨,打造百年诚信企业为方向,本着“客户就是上帝,要满足并超越客户需求”的客户观,快速发展;致力成为中国电子供应链中广大厂商优先选择的战略合作伙伴。

也许我们只是一个小小配件,却是您产品中不可或缺的一份子!

也许我们给你的价格不是最低的,但品质一定是最高的;我们宁可为价格解释一阵子,也不愿为质量道歉一辈子!。

GC1510资料

30VOLT ABRUPT JUNCTION VARACTOR DIODESDESCRIPTIONThe GC1500series varactors are silicon abrupt junction devices.They offer the highest Q and lowest series resis-tance available in a 30Volt silicon varactor.APPLICATIONSThe GC1500series varactors are used for narrow tomoderate band width tuning.They are available in val-ues appropriate for VHF through KU band frequencies.These devices are best used in low phase noise voltage controlled oscillators,low loss voltage variable filters and phase shifters.Standard capacitance tolerance is ±10%Other capaci-tance values and custom mechanical configurations are also available.All specifications shown are based on style 30package and include .18pF case capacitance.Consult package outline section of this catalog for other case styles plete electrical and mechani-cal data is alsoprovided.RATINGSMinimum Voltage Breakdown:30V at 10µA Maximum Leakage Current at:25V and 25ºC 0.02µA 25V and 125ºC 2.00µACapacitance-Temp.Coefficient:300ppm/ºC at V R =-4V Operating Temperature:-55ºC to +150ºC Storage Temperature:-65ºC to +200ºCTuning Varactors30VOLT ABRUPT JUNCTION VARACTOR DIODESELECTRICAL SPECIFICATIONS:T A =25°CNOTES:1.When ordering,specify the desired case style by adding its number as a suffix to the model number.Some limitations apply -consult factory for details.2.These values include a package capacitance of .18P ..3.Q is calculated from:Q=1π5jwhere f=50MHz and R I =Series resistance measured a 1GHz using transmission loss techniques.Capacitance is measured at 1MHz.4.GC1500A only available in Die Form.SEMICONDUCTOR OPERATION75T echnology Drive Lowell,MA 01851 T el:978-442-5600 Fax:978-937-374816Tuning Varactors。

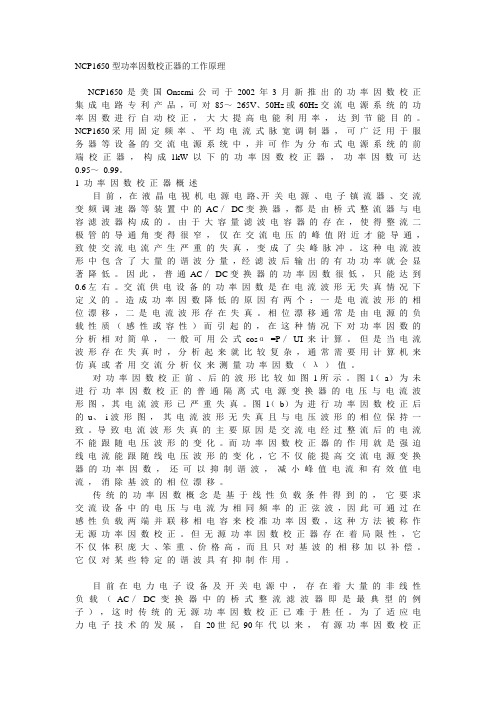

NCP1650型功率因数校正器

NCP1650型功率因数校正器的工作原理NCP1650是美国Onsemi公司于2002年3月新推出的功率因数校正集成电路专利产品,可对85~265V、50Hz或60Hz交流电源系统的功率因数进行自动校正,大大提高电能利用率,达到节能目的。

NCP1650采用固定频率、平均电流式脉宽调制器,可广泛用于服务器等设备的交流电源系统中,并可作为分布式电源系统的前端校正器,构成1kW以下的功率因数校正器,功率因数可达0.95~0.99。

1 功率因数校正器概述目前,在液晶电视机电源电路、开关电源、电子镇流器、交流变频调速器等装置中的AC/DC变换器,都是由桥式整流器与电容滤波器构成的。

由于大容量滤波电容器的存在,使得整流二极管的导通角变得很窄,仅在交流电压的峰值附近才能导通,致使交流电流产生严重的失真,变成了尖峰脉冲。

这种电流波形中包含了大量的谐波分量,经滤波后输出的有功功率就会显著降低。

因此,普通AC/DC变换器的功率因数很低,只能达到0.6左右。

交流供电设备的功率因数是在电流波形无失真情况下定义的。

造成功率因数降低的原因有两个:一是电流波形的相位漂移,二是电流波形存在失真。

相位漂移通常是由电源的负载性质(感性或容性)而引起的,在这种情况下对功率因数的分析相对简单,一般可用公式cosα=P/UI来计算。

但是当电流波形存在失真时,分析起来就比较复杂,通常需要用计算机来仿真或者用交流分析仪来测量功率因数(λ)值。

对功率因数校正前、后的波形比较如图1所示。

图1(a)为未进行功率因数校正的普通隔离式电源变换器的电压与电流波形图,其电流波形已严重失真。

图1(b)为进行功率因数校正后的u、i波形图,其电流波形无失真且与电压波形的相位保持一致。

导致电流波形失真的主要原因是交流电经过整流后的电流不能跟随电压波形的变化。

而功率因数校正器的作用就是强迫线电流能跟随线电压波形的变化,它不仅能提高交流电源变换器的功率因数,还可以抑制谐波,减小峰值电流和有效值电流,消除基波的相位漂移。

NCP15XH103J03RC;NCP15WF104J03RC;NCP15WB473J03RC;NCP15XM472J03RC;中文规格书,Datasheet资料

Ex.

Code

Individual Specifications

03

Standard Type

iPackaging Code RA RB RC RL

Packaging Plastic Taping 4mm Pitch (4000 pcs.) Paper Taping 4mm Pitch (4000 pcs.) Paper Taping 2mm Pitch (10000 pcs.) Paper Taping 2mm Pitch (15000 pcs.)

Jan.10,2012

o Part Numbering

NTC Thermistors for Temp. Sensor and Compensation Chip Type

(Part Number)

qProduct ID Product ID NC

NC P 18 XH 103 J 03 RB q we r t yu i

Jan.10,2012

NTC Thermistors

Cat.No.R44E-14 /

!Note • Please read rating and !CAUTION (for storage, operating, rating, soldering, mounting and handling) in this catalog to prevent smoking and/or burning, etc.

(/info/rohs.html).

/

!Note • Please read rating and !CAUTION (for storage, operating, rating, soldering, mounting and handling) in this catalog to prevent smoking and/or burning, etc.

AP1510中文资料

PWM Control 3A Step-Down ConverterFeatures- Input voltage: 3.6V to 23V. - Output voltage: 0.8V to V CC .- Duty ratio: 0% to 100% PWM control - Oscillation frequency: 300KHz typ.- Soft-start, Current limit, Enable function - Thermal Shutdown function- Built-in internal SW P-channel MOS - SOP-8L Pb-Free Package.Applications- PC Motherboard - LCD Monitor - Graphic Card- DVD-Video Player - Telecom Equipment - ADSL Modem- Printer and other Peripheral Equipment - Microprocessor core supply - Networking power supplyGeneral DescriptionAP1510 consists of step-down switching regulator with PWM control. These devices include a reference voltage source, oscillation circuit, error amplifier, internal PMOS and etc.AP1510 provides low-ripple power, high efficiency, and excellent transient characteristics. The PWM control circuit is able to very the duty ratio linearly from 0 up to 100%. This converter also contains an error amplifier circuit as well as a soft-start circuit that prevents overshoot at startup. An enable function, an over current protect function and a short circuit protect function are built inside, and when OCP or SCP happens, the operation frequency will be reduced from 300KHz to 30KHz. Also, an internal compensation block is built in to minimum external component count.With the addition of an internal P-channel Power MOS, a coil, capacitors, and a diode connected externally, these ICs can function as step-down switching regulators. They serve as ideal power supply units for portable devices when coupled with the SOP–8L mini-package, providing such outstanding features as low current consumption. Since this converter can accommodate an input voltage of up to 23V, it is also ideal when operating via an AC adapter.Pin AssignmentsOutput OCSET Output EN Vss VssV CCPin DescriptionsName Pin Description FB 1 Feedback pin.EN 2Power-off pinH: Normal operation (Step-down operation)L: Step-down operation stopped (All circuits deactivated)OCSET 3Add an external resistor to setmax output current.V CC 4 IC power supply pinOutput 5、6Switch Pin. Connect external inductor/diode here. Minimizetrace area at this pin to reduce EMI. V SS7、8GND PinPWM Control 3A Step-Down ConverterOrdering InformationAP1510X XPackage PackingS: SOP-8L Blank : TubeA : TapingBlock DiagramVccAbsolute Maximum Ratingsdamage. These values must therefore not be exceeded under any conditions.PWM Control 3A Step-Down ConverterElectrical Characteristics (V IN = 12V, T a =25°C , unless otherwise specified)Symbol Parameter Conditions Min.Typ. Max.Unit V FB Feedback Voltage I OUT =0.1A 0.7840.8 0.816V V IN Input Voltage -- 3.6 - 23 V ISW Switch Current -- 3.5 - - AI SSS Current ConsumptionDuring Power OffV ON/OFF =0V - 10 - µA∆V OUT/V OUT Line Regulation VIN = 5V~23V, I OUT =0.2A - 1 2 %∆V OUT/V OUTLoad Regulation I OUT = 0.1 to 3A - 0.2 0.5 %f OSC Oscillation Frequency Measure waveform at SW pin 240 300 360 KHz f OSC1 Frequency of Current Limitor Short Circuit ProtectMeasure waveform at SW pin 10 30 60 KHzV SH Evaluate oscillation at SW pin 2.0 - -V SL EN Pin Input Voltage Evaluate oscillation stop at SW pin - - 0.8 V I SH -- - 20 - µA I SL EN Pin Input Leakage Current -- - -10 - µA I OCSET OCSET Pin Bias Current -- 75 90 105 µA T SS Soft-Start Time -- 0.3 2 5 msV IN =5V, V FB =0V - 110 150 R DSON Internal MOSFET RdsonV IN =12V, V FB =0V -70 100 m ΩEFFI EfficiencyV IN = 12V, V OUT = 5VI OUT = 3A- 91 - %Typical Application CircuitVNote: V OUT = V FB x (1+R A /R B )R B =0.7K~5K ohmPWM Control 3A Step-Down Converter Typical Performance CharacteristicsPWM Control 3A Step-Down ConverterTypical Performance Characteristics (Continued)AP1510 Vout Ripple(Vin=12V; Vout=3.3V; Iout=0.1A) AP1510 Vout Ripple(Vin=12V; Vout=3.3V; Iout=3A)Test CircuitPWM Control 3A Step-Down ConverterFunction DescriptionPWM ControlThe AP1510 consists of DC/DC converters that employ a pulse-width modulation (PWM) system. In converters of the AP1510, the pulse width varies in a range from 0 to 100, according to the load current, and yet ripple voltage produced by the switching can easily be removed through a filter because the switching frequency remains constant. Therefore, these converters provide a low-ripple power over broad ranges of input voltage and load current.Under Voltage LockoutThe under voltage lockout circuit of the AP1510 assures that the high-side MOSFET driver outputs remain in the off state whenever the supply voltage drops below set parameters. Lockout occurs if V CC falls below 3.3V. Normal operation resumes once V CC rises above 3.5V. R DS(ON) Current LimitingThe current limit threshold is setting by connecting an external resistor from V CC supply to OCSET . The voltage drop across this resistor is due to the 100uA internal sink sets the voltage at the pin. When the PWM voltage is less than the voltage at OCSET, an over-current condition occurs.Marking Information( Top View )LogoPart no.ID code: internal Year: "01" =2001 "02" =2002Xth week: 01~52~AP1510YY WW XPWM Control 3A Step-Down ConverterPackage InformationPackage Type: SOP-8LDimensions In Millimeters Dimensions In InchesSymbolMin. Nom. Max. Min. Nom. Max.A 1.40 1.60 1.75 0.055 0.063 0.0690.040 - 0.100A1 0.10 - 0.25A2 1.30 1.45 1.50 0.051 0.057 0.059B 0.33 0.41 0.51 0.013 0.016 0.020C 0.19 0.20 0.25 0.0075 0.008 0.010D 4.80 5.05 5.30 0.189 0.199 0.209E 3.70 3.90 4.10 0.146 0.154 0.161e - 1.27 - - 0.050 -H 5.79 5.99 6.20 0.228 0.236 0.244L 0.38 0.71 1.27 0.015 0.028 0.050y - - 0.10 - - 0.004θ0O - 8O0O - 8O。

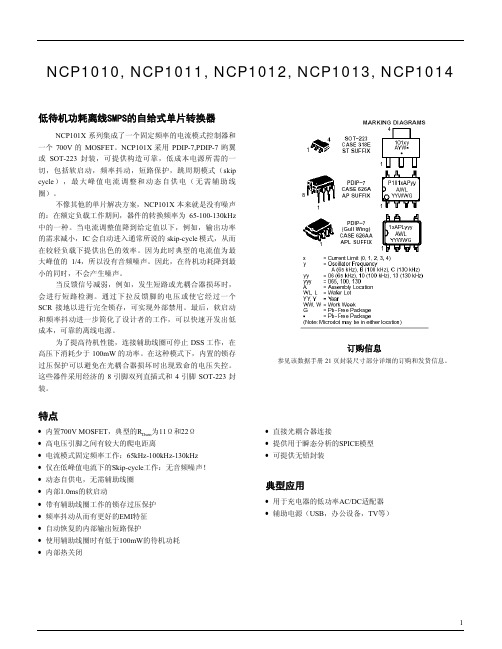

NCP1014中文数据手册

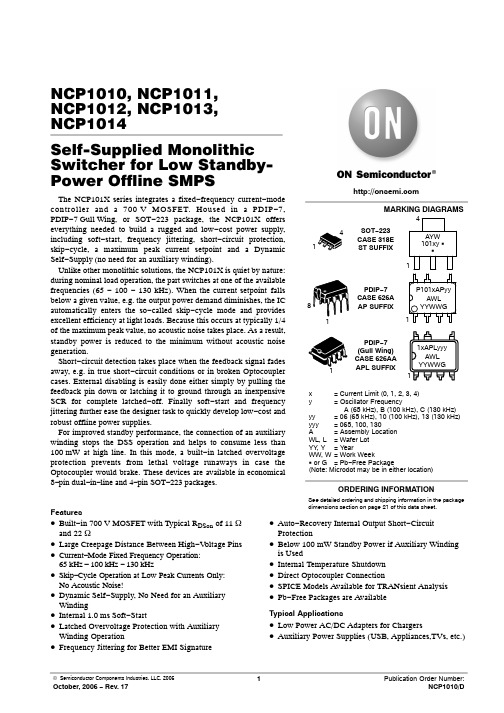

NCP1010, NCP1011, NCP1012, NCP1013, NCP1014低待机功耗离线SMPS的自给式单片转换器NCP101X 系列集成了一个固定频率的电流模式控制器和一个700V 的MOSFET 。

NCP101X 采用PDIP-7,PDIP-7 鸥翼或SOT-223封装,可提供构造可靠,低成本电源所需的一切,包括软启动,频率抖动,短路保护,跳周期模式(skip cycle ),最大峰值电流调整和动态自供电(无需辅助线圈)。

不像其他的单片解决方案,NCP101X 本来就是没有噪声的:在额定负载工作期间,器件的转换频率为65-100-130kHz 中的一种。

当电流调整值降到给定值以下,例如,输出功率的需求减小,IC 会自动进入通常所说的skip-cycle 模式,从而在较轻负载下提供出色的效率。

因为此时典型的电流值为最大峰值的1/4,所以没有音频噪声。

因此,在待机功耗降到最小的同时,不会产生噪声。

当反馈信号减弱,例如,发生短路或光耦合器损坏时,会进行短路检测。

通过下拉反馈脚的电压或使它经过一个SCR 接地以进行完全锁存,可实现外部禁用。

最后,软启动和频率抖动进一步简化了设计者的工作,可以快速开发出低成本,可靠的离线电源。

为了提高待机性能,连接辅助线圈可停止DSS 工作,在高压下消耗少于100mW 的功率。

在这种模式下,内置的锁存过压保护可以避免在光耦合器损坏时出现致命的电压失控。

这些器件采用经济的8引脚双列直插式和4引脚SOT-223封装。

订购信息参见该数据手册21页封装尺寸部分详细的订购和发货信息。

特点• 内置700V MOSFET ,典型的R Dson 为11Ω和22Ω• 高电压引脚之间有较大的爬电距离• 电流模式固定频率工作:65kHz-100kHz-130kHz • 仅在低峰值电流下的Skip-cycle 工作:无音频噪声!• 动态自供电,无需辅助线圈• 内部1.0ms 的软启动• 带有辅助线圈工作的锁存过压保护• 频率抖动从而有更好的EMI 特征• 自动恢复的内部输出短路保护• 使用辅助线圈时有低于100mW 的待机功耗• 内部热关闭• 直接光耦合器连接• 提供用于瞬态分析的SPICE 模型• 可提供无铅封装典型应用• 用于充电器的低功率AC/DC 适配器• 辅助电源(USB ,办公设备,TV 等)引脚连接NCP1014的最大输出功率特征值-Ip230Vac100-250Vac RDson11Ω-450 mA 动态自供电14W 6.0W11Ω-450 mA 辅助线圈19W8.0W1. 仅为特征值:Tamb=50℃, Fswitching=65kHz, 电路安装在推荐的最小敷铜区域内。

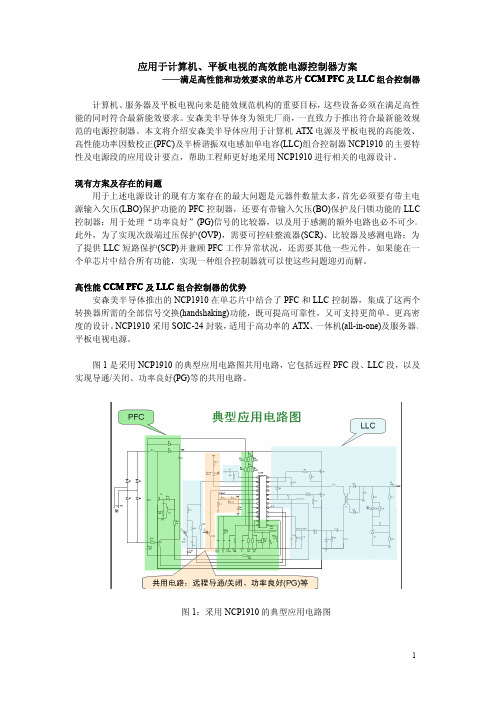

计算机,平板电视

应用于计算机、平板电视的高效能电源控制器方案LLC C组合控制器PFC C及LL——满足高性能和功效要求的单芯片CCM PF计算机、服务器及平板电视向来是能效规范机构的重要目标,这些设备必须在满足高性能的同时符合最新能效要求。

安森美半导体身为领先厂商,一直致力于推出符合最新能效规范的电源控制器。

本文将介绍安森美半导体应用于计算机ATX电源及平板电视的高能效、高性能功率因数校正(PFC)及半桥谐振双电感加单电容(LLC)组合控制器NCP1910的主要特性及电源段的应用设计要点,帮助工程师更好地采用NCP1910进行相关的电源设计。

现有方案及存在的问题用于上述电源设计的现有方案存在的最大问题是元器件数量太多,首先必须要有带主电源输入欠压(LBO)保护功能的PFC控制器,还要有带输入欠压(BO)保护及闩锁功能的LLC 控制器;用于处理“功率良好”(PG)信号的比较器,以及用于感测的额外电路也必不可少。

此外,为了实现次级端过压保护(OVP),需要可控硅整流器(SCR)、比较器及感测电路;为了提供LLC短路保护(SCP)并兼顾PFC工作异常状况,还需要其他一些元件。

如果能在一个单芯片中结合所有功能,实现一种组合控制器就可以使这些问题迎刃而解。

高性能CCM PFC及LLC组合控制器的优势安森美半导体推出的NCP1910在单芯片中结合了PFC和LLC控制器,集成了这两个转换器所需的全部信号交换(handshaking)功能,既可提高可靠性,又可支持更简单、更高密度的设计。

NCP1910采用SOIC-24封装,适用于高功率的ATX、一体机(all-in-one)及服务器、平板电视电源。

图1是采用NCP1910的典型应用电路图共用电路,它包括远程PFC段、LLC段,以及实现导通/关闭、功率良好(PG)等的共用电路。

图1:采用NCP1910的典型应用电路图PFC段具有以下一些特性:·固定频率连续导电模式(CCM)PFC可提供65kHz,100kHz、133kHz及200kHz选择;·可编程过流阈值提供优化的感测电阻;·过功率限制可根据平均输入电压限制电流;·PFC异常保护,可以在出现PFC异常的情况下,器件停止工作,即使输入为高线路电压;·欠压保护可避免反馈网络中出现错误连接的情况下受损;·快速瞬态响应旨在维持V bulk稳压:--过压保护可自动恢复OVP阈值(稳压电平的105%);--动态响应增强器可在V bulk降至低于其稳压电平的95%时,使用其内部200µA电流源来加快稳压环路速度;·冗余OVP(OVP2)使用专用引脚来闩锁V bulk OVP;·可调节线路输入欠压带50ms消隐时间(blank time),避免在低输入电压时受损;·V in2前馈可优化功率因数;·Power Boost可在极端线路瞬态条件下调节V bulk(如264Va c→90Vac);·可调节频率反走提升轻载能效;·软启动;·图腾柱(Totem Pole)驱动能力为±1.0A门驱动器。

ncp163中文规格书

vncp163中文规格书一、产品概述NCP163是一款高效、高精度、低功耗的电压调节器,适用于多种应用场景,如通信、医疗、工业控制等。

它具有体积小、集成度高、稳定性好等优点,可为用户提供稳定的电压输出。

二、性能参数1. 输入电压范围:9V-32V2. 输出电压范围:2.5V-5.0V3. 最大输出电流:15A4. 效率:>90%5. 精度:±2%6. 工作温度范围:-40℃-85℃三、电路连接与布局1. 输入端子:采用螺栓连接,连接导线截面积不小于10mm²。

2. 输出端子:采用螺栓连接,连接导线截面积不小于6mm²。

3. 散热片:与器件底部接触,确保良好的散热效果。

4. 安装方式:采用导轨式或独立式安装,方便快捷。

四、热设计要求为保证NCP163正常工作,应确保其工作温度不超过85℃。

建议采用自然散热或强制散热方式,根据实际情况选择合适的散热片和散热风扇。

五、电磁兼容性NCP163应符合相关国家和地区的电磁兼容标准,如FCC、CE等。

在设计和使用时应采取相应措施,以降低电磁干扰对周围设备和人体的影响。

六、环境适应性NCP163可在-40℃-85℃的温度范围内正常工作,但应避免在高温和高湿度的环境下长期工作,以免影响其性能和寿命。

在特殊环境下使用时,应采取相应措施,如防水、防尘等。

七、机械性能与安装要求NCP163的外形尺寸较小,安装时应注意尺寸和重量等因素,以免影响其稳定性和可靠性。

安装时应遵循产品手册中的要求,确保安装正确牢固。

在搬运和安装过程中,应避免强烈震动和冲击,以免损坏器件。

NCP1530中文资料

NCP1530600 mA PWM/PFMStep−Down Converter with External Synchronization PinThe NCP1530 is a PWM/PFM non−synchronous step−down (Buck) DC−DC converter for usage in systems supplied from 1−cell Li−ion, or 2 or more cells Alkaline/NiCd/NiMH batteries. It can operate in Constant−Frequency PWM mode or PWM/PFM mode in which the controller will automatically switch to PFM mode operation at low output loads to maintain high efficiency. The switching frequency can also be synchronized to external clock between 600 kHz and 1.2 MHz. The maximum output current is up to 600 mA. Applying an external synchronizing signal to SYN pin can supersede the PFM operation.The NCP1530 consumes only 47 m A (typ) of supply current (V OUT= 3.0 V, no switching) and can be forced to shutdown mode by bringing the enable input (EN) low. In shutdown mode, the regulator is disabled and the shutdown supply current is reduced to 0.5 m A (typ). Other features include built−in undervoltage lockout, internal thermal shutdown, an externally programmable soft−start time and output current limit protection. The NCP1530 operates from a maximum input voltage of 5.0 V and is available in a space saving, low profile Micro8™ package.Features•Pb−Free Package is Available•High Conversion Efficiency, up to 92% at V IN= 4.3 V,V OUT= 3.3 V, I OUT = 300 mA•Current−Mode PWM Control•Automatic PWM/PFM Mode for Current Saving at Low Output Loads •Internal Switching Transistor Support 600 mA Output Current(V IN = 5.0 V, V OUT= 3.3 V)•High Switching Frequency (600 kHz), Support Small Size Inductor and Capacitor, Ceramic Capacitors Can be Used •Synchronize to External Clock Signal up to 1.2 MHz•100% Duty Cycle for Maximum Utilization of the Supply Source •Programmable Soft−Start Time through External Chip Capacitor •Externally Accessible V oltage Reference•Built−In Input Undervoltage Lockout•Built−In Output Overvoltage Protection•Power Saving Shutdown Mode•Space Saving, Low Profile Micro8 PackageTypical Applications•PDAs•Digital Still Camera•Cellular Phone and Radios•Portable Test Equipment•Portable Scanners•Portable Audio SystemsSee detailed ordering and shipping information in the package dimensions section on page 14 of this data sheet.ORDERING INFORMATIONFigure 1. Typical Step−Down Converter ApplicationV IN = 2.8 V to 5.0 VV OUT = 3.0 V*Optional ComponentFigure 2. Simplified Functional Block DiagramEN 5SYN 2SS 34 GND6 V OUT8 LXV REF 7MAXIMUM RATINGS(not normal operating conditions) and are not valid simultaneously. If these limits are exceeded, device functional operation is not implied, damage may occur and reliability may be affected.1.This device series contains ESD protection and exceeds the following tests:Human Body Model (HBM) "2.0 kV per JEDEC standard: JESD22−A114.Machine Model (MM) "200 V per JEDEC standard: JESD22−A115.tchup Current Maximum Rating: "150 mA per JEDEC standard: JESD78.3.Moisture Sensitivity Level (MSL): 1 per IPC/JEDEC standard: J−STD−020A.typical value, 0°C ≤ T≤ 85°C for min/max values unless otherwise noted.) *V is the factory−programmed output voltage setting.5.Parameter guaranteed by design only, not tested in production.6.Loading capability decreases with V OUT decreases.25°C for typical value, 0°C ≤ T A ≤ 85°C for min/max values unless otherwise noted.) *V R is the factory−programmed output voltage setting.I S H D N , S H U T D O W N C U R R E N T (n A )T A , AMBIENT TEMPERATURE (°C)Figure 3. Output Voltage vs. Ambient Temperature(V OUT = 2.5 V)T A , AMBIENT TEMPERATURE (°C)V O U T , O U T P U T V O L T A G E (V )Figure 4. Output Voltage vs. Ambient Temperature(V OUT = 2.7 V)Figure 5. Output Voltage vs. Ambient Temperature(V OUT = 3.0 V)Figure 6. Output Voltage vs. Ambient Temperature(V OUT = 3.3 V)Figure 7. Supply Current vs. Ambient Temperature I I N , S U P P L Y C U R R E N T (m A )Figure 8. Shutdown Current vs. Ambient TemperatureT A , AMBIENT TEMPERATURE (°C)V O U T , O U T P U T V O L T A G E (V )T A , AMBIENT TEMPERATURE (°C)V O U T , O U T P U T V O L T A G E (V )T A , AMBIENT TEMPERATURE (°C)V O U T , O U T P U T V O L T A G E (V )T A , AMBIENT TEMPERATURE (°C)020406080100120140I L O A D , O U T P U T L O A D I N G C U R R E N T (m A )V IN , INPUT VOLTAGE (V)20406080100120140IL O A D , O U T P U T L O A D I N G C U R R E N T (m A )V IN , INPUT VOLTAGE (V)T A , AMBIENT TEMPERATURE (°C)Figure 9. Oscillator Frequency vs. Ambient Temperaturef O S C , O S C I L L A T O R F R E Q U E N C Y (k H z )R D S (O N ), P −F E T O N R E S I S T A N C E (W )Figure 11. PWM/PFM Switchover Current Thresholds vs. Input Voltage (V OUT = 2.5 V)I L O A D , O U T P U T L O A D I N G C U R R E N T (m A )Figure 12. PWM/PFM Switchover Current Thresholds vs. Input Voltage (V OUT = 2.7 V)V IN , INPUT VOLTAGE (V)Figure 13. PWM/PFM Switchover Current Thresholds vs. Input Voltage (V OUT = 3.0 V)Figure 14. PWM/PFM Switchover Current Thresholds vs. Input Voltage (V OUT = 3.3 V)020406080100120140I L O A D , O U T P U T L O A D I N G C U R R E N T (m A )V IN , INPUT VOLTAGE (V)I LOAD , OUTPUT LOAD CURRENT (mA)h , E F F I C I E N C Y (%)I LOAD , OUTPUT LOAD CURRENT (mA)h , E F F I C I E N C Y (%)h , E F F I C I E N C Y (%)Figure 19. Efficiency vs. Output Load Current(V IN = 4.0 V, V OUT = 3.0 V)Figure 20. Efficiency vs. Output Load Current(V IN = 5.0 V, V OUT = 3.0 V)D V O U T , O U T P U T V O L T A GE R E G U L A T I O N (%)I LOAD , OUTPUT LOAD CURRENT (mA)5.03.0D V O U T , O U T P U T V O L T A GE R E G U L A T I O N (%)I LOAD , OUTPUT LOAD CURRENT (mA)5.03.0−3.0−5.0I LOAD , OUTPUT LOAD CURRENT (mA)I LOAD , OUTPUT LOAD CURRENT (mA)Figure 21. Efficiency vs. Output Load Current(V IN = 4.3 V, V OUT = 3.3 V)h , E F F I C I E N C Y (%)Figure 22. Efficiency vs. Output Load Current(V IN = 5.0 V, V OUT = 3.3 V)D V O U T , O U T P U T V O L T A GE R E G U L A T I O N (%)Figure 23. Output Voltage Regulation vs.Output Load Current (V OUT = 2.5 V)Figure 24. Output Voltage Regulation vs.Output Load Current (V OUT = 2.7 V)Figure 25. Output Voltage Regulation vs.Output Load Current (V OUT = 3.0 V)Figure 26. Output Voltage Regulation vs.Output Load Current (V OUT = 3.3 V)I LOAD , OUTPUT LOAD CURRENT (mA)5.03.00D V O U T , O U T P U T V O L T A GE R E G U L A T I O N (%)I LOAD , OUTPUT LOAD CURRENT (mA)5.03.0(V IN = 3.5 V, V OUT = 2.5 V, I LOAD = 10 mA) Upper Trace: Output Voltage Ripple, 50 mVac/Div. Lower Trace: LX Pin Switching Waveform, 2.0 V/Div. Figure 27. PFM Switching Waveform and Output Ripple for V OUT = 2.5 V(V IN = 3.5 V, V OUT = 2.5 V, I LOAD = 80 mA) Upper Trace: Output Voltage Ripple, 50 mVac/Div. Lower Trace: LX Pin Switching Waveform, 2.0 V/Div. Figure 28. DCM PWM Switching Waveform and Output Ripple for V OUT = 2.5 V(V IN = 3.5 V, V OUT = 2.5 V, I LOAD = 600 mA) Upper Trace: Output Voltage Ripple, 50 mVac/Div. Lower Trace: LX Pin Switching Waveform, 2.0 V/Div. Figure 29. CCM PWM Switching Waveform and Output Ripple for V OUT = 2.5 V(V IN = 4.3 V, V OUT = 3.3 V, I LOAD = 10 mA) Upper Trace: Output Voltage Ripple, 50 mVac/Div. Lower Trace: LX Pin Switching Waveform, 2.0 V/Div. Figure 30. PFM Switching Waveform and Output Ripple for V OUT = 3.3 V(V IN = 4.3 V, V OUT = 3.3 V, I LOAD = 50 mA) Upper Trace: Output Voltage Ripple, 50 mVac/Div. Lower Trace: LX Pin Switching Waveform, 2.0 V/Div. Figure 31. DCM PWM Switching Waveform and Output Ripple for V OUT = 3.3 V(V IN = 4.3 V, V OUT = 3.3 V, I LOAD = 600 mA) Upper Trace: Output Voltage Ripple, 50 mVac/Div. Lower Trace: LX Pin Switching Waveform, 2.0 V/Div. Figure 32. CCM PWM Switching Waveform and Output Ripple for V OUT = 3.3 V(V IN = 3.5 V, V OUT = 2.5 V, C SS = 100 pF , No load)Upper Trace: Output Voltage, 2.0 V/Div.Lower Trace: EN Pin Waveform, 2.0 V/Div.Time Scale: 5.0 ms/Div.Figure 33. Soft−Start Output VoltageWaveform for V OUT= 2.5 V (V IN = 4.3 V, V OUT = 3.3 V, C SS = 100 pF , No load)Upper Trace: Output Voltage, 2.0 V/Div.Lower Trace: EN Pin Waveform, 2.0 V/Div.Time Scale: 5.0 ms/Div.Figure 34. Soft−Start Output VoltageWaveform for V OUT = 3.3 VDETAILED OPERATING DESCRIPTIONIntroductionThe NCP1530 series are step−down converters with a smart control scheme that operates with 600 kHz fixed Pulse Width Modulation (PWM) at moderate to heavy load currents, so that high efficiency, noise free output voltage can be generated. In order to improve the system efficiency at light loads, this device can be configured to work in auto−mode. In auto−mode operation, the control unit will detect the loading condition and switch to power saving Pulse Frequency Modulation (PFM) control scheme at light load. With these enhanced features, the converter can achieve high operating efficiency for all loading conditions. Additionally, the switching frequency can also be synchronized to external clock signal in between 600 kHz to 1.2 MHz range. The converter uses peak current mode PWM control as a core, with the high switching frequency incorporated. Good line and load regulation can be achieved easily with small value ceramic input and output capacitors. Internal integrated compensation voltage ramp ensures stable operation at all operating modes. NCP1530 series are designed to support up to 600 mA output current with cycle−by−cycle current limit protection.The Internal OscillatorThe oscillator that governs the switching of the PWM control cycle is self contained and no external timing component is required to setup the switching frequency. For PWM mode and auto−mode operation, all timing signals required for proper operation are derived from the internal oscillator. The internal fix frequency oscillator is trimmed to run at 600 kHz " 20% over full temperature range. In case the device is forced to operate at Synchronization mode by applying an external clock signal to SYN pin (pin 2), the external clock signal will supersede the internal oscillator and take charge of the switching operation.Voltage Reference and Soft−StartAn internal high accuracy voltage reference is included in NCP1530. This reference voltage governs all internal reference levels in various functional blocks required for proper operation. This reference voltage is precisely trimmed to 1.2 V " 1.5% over full temperature range. The reference voltage can be accessed externally at V REF pin (pin 7), with an external capacitor, C REF of 1.0 m F, privding up to 5.0 mA of loading. Additionally, NCP1530 has a Soft−Start circuit built around the voltage reference block that provide limits to the inrush current during start−up by controlling the ramp up of the internal voltage reference. The soft−start time can be user adjusted by an external capacitor, C SS, connecting to the SS pin (pin 3). During converter powerup, a 50 nA current flowing out from the SS pin will charge−up the timing capacitor. The voltage across the SS pin controls the ramp up of the internal reference voltage by slowly releasing it until the nominal value is reached. For an external timing capacitor of value C SS = 100 pF, the soft−start time is about 5.0 ms including the small logic delay time, Figure 33 and 34. In the case where the SS pin is left floating, a small built−in capacitor together with other parasitic capacitance will provide a minimum intrinsic soft−start time of 500 m s. As the soft−start function is implemented by simple circuitry, the final timing depends on non−linear functions, where accurate deterination of the soft−start timing is impossible. However, for simplicity, the empirical formula below can be used to estimate the soft−start time with respect to the value of the external capacitor.t SS in m s[50C SS in pF)500m sCurrent Mode Pulse−Width Modulation (PWM)Control SchemeWith the SYN pin (pin 2) connected to V IN, the converter will set to operate at constant switching frequency PWM mode. NCP1530 uses peak current mode control scheme to achieve good line and load regulation. The high switching frequency, 600 kHz, and a carefully compensated internal control loop, allows the use of low profile small value ceramic type input and output capacitor for stable operation. In current mode operation, the required ramp function is generated by sensing the inductor current (ISEN) and comparing with the voltage loop error amplifier (OTA) output. The OTA output is derived from feedback from the output voltage pin (V OUT − Pin 6) and the internal reference voltage (V REF − Pin 7). See Figure 2. On a cycle−by−cycle basis, the duty cycle is controlled to keep the output voltage within regulation. The current mode approach has outstanding line regulation performance and good overall system stability. Additionally, by monitoring the inductor current, a cycle−by−cycle current limit protection is implemented. Constant Frequency PWM scheme reduces output ripple and noise, which is one of the important characteristics for noise sensitive communication applications. The high switching frequency allows the use of small size surface mount components that saves significant PC board area and improves layout compactness and EMI performance.Power Saving Pulse−Frequency−Modulation (PFM) Control SchemeWith the SYN pin (pin 2) connected to ground or left open, the converter will operate in PWM/PFM auto mode. Under this operating mode, NCP1530 will stay in constant frequency PWM operation in moderate to heavy load conditions. When the load decreases down to a threshold point, the operation will switch to the power saving PFM operation automatically. The switchover mechanism depends on the input voltage, output voltage and the inductor current level. The mode change circuit will determine whether the converter should be operated in PWM or PFM mode. In order to maintain stable and smooth switching mode transition, a small hysteresis on the load current level for mode transition was implemented. The detailed mode transition characteristics for each voltage option are illustrated in Figures 11 and 14. PFM mode operation provides high conversion efficiency even at very light loading conditions. In PFM mode, most of the circuits inside the device will be turned off and the converter operates just as a simple voltage hysteretic converter. When the load current increases, the converter returns to PWM mode automatically.External Synchronization ControlThe NCP1530 has an internal fixed frequency oscillator of 600 kHz or can be synchronized to an external clock signal at SYN pin (pin 2). Connecting the SYN pin with an external clock signal will force the converter to operate in a pure PWM mode and the switching frequency will be synchronized. The external clock signal should be in the range of 600 kHz to 1.2 MHz and the pulse width should not be less than 300 ns. The detection of the pulse train is edge sensitive and independent of duty ratio. In the case where the external clock frequency is too low, the detection circuit may not be able to follow and will treat it as a disturbance, thus affecting the converters normal operation. The internal control circuit detects the rising edge of the pulse train and the switching frequency synchronized to the external clock signal. If the external clock signal ceases for several clock cycles, the converter will switch back to use the internal oscillator automatically. Power Saving Shutdown ModeNCP1530 can be disabled whenever the EN pin (pin 5) is tied to ground. In shutdown mode, the internal reference, oscillator and most of the control circuitries are turned off. With the device put in shutdown mode, the device current consumption will be as low as 0.5 m A (typ).Input Undervoltage Lockout Protection (UVLO)To prevent the P−Channel MOSFETs from operating below safe input voltage levels, an Undervoltage Lockout protection is incorporated in NCP1530. Whenever the input voltage, V IN drops below approximately 2.0 V, the protection circuitry will be activated and the converter operation will be stopped.Output Overvoltage Protection (OVP)In order to prevent the output voltage from going to high (when the load current is close to zero in a pure PWM mode and other abnormal conditions), an Output Overvoltage protection circuit is included in the NCP1530. In case the output voltage is higher than its nominal level by more than 12% maximum, the protection circuitry will stop the switching immediately.Internal Thermal ShutdownInternal thermal shutdown circuitry is provided to protect the integrated circuit in the event that the maximum junction temperature is exceeded. The protection will be activated at about 145°C with a hysteresis of 15°C. This feature is provided to prevent failures from unexpected overheating.Input Capacitor SelectionFor a PWM converter operating in continuous current mode, the input current of the converter is a square wave with a duty ratio of approximately V OUT/V IN. The pulsating nature of the input current transient can be a source of EMI noise and system instability. Using an input bypass capacitor can reduce the peak current transients drawn from the input supply source, thereby reducing switching noise significantly. The capacitance needed for the input bypass capacitor depends on the source impedance of the input supply. For NCP1530, a low ESR, low profile ceramic capacitor of 22 m F can be used for most of the cases. For effective bypass results, the input capacitor should be placed just next to V IN pin (pin 1) whenever it is possible.Inductor Value SelectionSelecting the proper inductance for the power inductor is a trade−off between inductor’s physical sizes, transient response, power delivering capability, output voltage ripple and power conversion efficiency. Low value inductor saves cost, PC board space and provides fast transient response, however suffers high inductor ripple current, core loss and lower overall conversion efficiency. The relationship between the inductance and the inductor ripple current is given by the equation in below.L+T ON(V IN*R DS(ON)I OUT*V F*V OUT)L_RIPPLE(P*P)Where L is the inductance required;T ON is the nominal ON time within a switching cycle; R DS(ON) is the ON resistance of the internal MOSFET; V F is the forward voltage drop of the Schottky diode; V IN is the worst−case input voltage;V OUT is the output voltage;I OUT is the maximum allowed loading current;I L_RIPPLE(P−P)is the acceptable inductor current ripple level.For ease of application, the previous equation was plotted in Figure 35 to help end user to select the right inductor for specific application. As a rule of thumb, the user needs to be aware of the maximum peak inductor current and should be designed not to exceed the saturation limit of the inductor selected. Low inductance can supply higher output current, but suffers higher output ripple and reduced efficiency, but it limits the output current capability. On the other hand, high inductance can improve output ripple and efficiency, at the same time, it also limits the output current capability. One other critical parameter of the inductor is its DC resistance. This resistance can introduce unwanted power loss and hence reduce overall efficiency. The basic rule is selecting an inductor with lowest DC resistance within the board space limitation.V IN , INPUT VOLTAGE (V)L , I N D U C T A N C E (m H )02.04.06.08.010123.03.54.04.55.0Figure 35. Inductor Selection ChartFlywheel Diode SelectionThe flywheel diode is turned on and carries load current during the off time. At high input voltages, the diode conducts most of the time. In the case where V IN approaches V OUT , the diode conducts only a small fraction of the cycle. While the output terminals are shorted, the diode will be subject to its highest stress. Under this condition, the diode must be able to safely handle the peak current circulating in the loop. So, it is important to select a flywheel diode that can meet the diode peak current and average power dissipation requirements. Under normal conditions, the average current conducted by the flywheel diode is given by,I D +V IN *V OUT V IN )V FI OUTWhere I D is the average diode current and V F is the forward voltage drop of the diode.A low forward voltage drop and fast switching diode must also be used to optimize converter efficiency.Schottky diodes are a good choice for low forward drop and fast switching times.Output Capacitor SelectionSelection of the output capacitor, C OUT is primarily governed by the required effective series resistance (ESR)of the capacitor. Typically, once the ESR requirement is met, the capacitance will be adequate for filtering. The output voltage ripple, V RIPPLE is approximated by,V RIPPLE [I L_RIPPLE(P *P) ǒESR )1OSC OUTǓWhere F OSC is the switching frequency and ESR is the effective series resistance of the output capacitor.From equation in above, it can be noted that the output voltage ripple is contributed to by two parts. For most of the cases, the major contributor is the capacitor’s ESR.Ordinary aluminum−electrolytic capacitors have high ESR and should be avoided. High quality Low ESR aluminum−electrolytic capacitors are acceptable and relatively inexpensive. Low ESR tantalum capacitors are another alternative. For even better performance, surface mounted ceramic capacitors can be used. Ceramic capacitors have lowest ESR among all choices. The NCP1530 is internally compensated for stable operation with low ESR ceramic capacitors. However, ordinary multi−layer ceramic capacitors have poor temperature and frequency performance, for switching applications, so only high quality, grade X5R and X7R ceramic capacitors can be used.PCB Layout RecommendationsGood PCB layout plays an important role in switching mode power conversion. Careful PCB layout can help to minimize ground bounce, EMI noise and unwanted feedbacks that can affect the performance of the converter.Hints suggested below can be used as a guideline in most situations.GroundingStar−ground connection should be used to connect the output power return ground, the input power return ground and the device power ground together at one point. All high current running paths must be thick enough for current flowing through and producing insignificant voltage drop along the path.Components PlacementPower components, i.e. input capacitor, inductor and output capacitor, must be placed as close together as possible. All connecting traces must be short, direct and thick. High current flowing and switching paths must be kept away from the feedback (V OUT , pin 6) terminal to avoid unwanted injection of noise into the feedback path.Feedback PathFeedback of the output voltage must be a separate trace separated from the power path. The output voltage sensing trace to the feedback (V OUT , pin 6) pin should be connected to the output voltage directly at the anode of the output capacitor.ORDERING INFORMATIONSpecifications Brochure, BRD8011/D.NOTE:The ordering information lists four standard output voltage device options. Additional device with output voltage ranging from 2.5 V to3.5 V in 100 mV increments can be manufactured. Contact your ON Semiconductor representative for availability.PACKAGE DIMENSIONSMicro8DM SUFFIX CASE 846A−02ISSUE FDIM MIN MAX MIN MAX INCHESMILLIMETERS A 2.90 3.100.1140.122B 2.90 3.100.1140.122C −−− 1.10−−−0.043D 0.250.400.0100.016G 0.65 BSC 0.026 BSC H 0.050.150.0020.006J 0.130.230.0050.009K 4.75 5.050.1870.199L0.400.700.0160.028NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSION A DOES NOT INCLUDE MOLDFLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.4.DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010)PER SIDE.5.846A−01 OBSOLETE, NEW STANDARD 846A−02.*For additional information on our Pb−Free strategy and solderingdetails, please download the ON Semiconductor Soldering and Mounting T echniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT*8XMicro8 is a trademark of International Rectifier.ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. “Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part.SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner. PUBLICATION ORDERING INFORMATION。

NCP1013AP065G中文资料

1

October, 2006 − Rev. 17

Publication Order Number: NCP1010/D

元器件交易网

NCP1010, NCP1011, NCP1012, NCP1013, NCP1014

PDIP−7

VCC 1 NC 2

8 GND 7 GND

RDSon − Ip

230 Vac

100 − 250 Vac

11 W − 450 mA DSS

14 W

6.0 W

ห้องสมุดไป่ตู้

11 W − 450 mA Auxiliary Winding

19 W

8.0 W

1. Informative values only, with: Tamb = 50°C, Fswitching = 65 kHz, circuit mounted on minimum copper area as recommended.

8

PDIP−7 CASE 626A AP SUFFIX

P101xAPyy AWL

YYWWG

excellent efficiency at light loads. Because this occurs at typically 1/4

1

1

of the maximum peak value, no acoustic noise takes place. As a result,

GND 3

FB 4

5 DRAIN

(Top View)

PIN CONNECTIONS

PDIP−7 (Gull Wing)

VCC 1 NC 2

8 GND 7 GND

GND 3

NCP1215DR2;NCP1215SNT1;NCP1215DR2G;中文规格书,Datasheet资料

NCP1215Low Cost Variable OFF Time Switched Mode Power Supply ControllerThe NCP1215 is a controller for low power off−line flyback Switchemode Power Supplies (SMPS) featuring low size, weight and cost constraints together with a good low standby power performance. The operating principle uses switching frequency reduction at light load by increasing the OFF Time. Also, when OFF Time expands, thepeak current is gradually reduced down to approximately 1/4 of the maximum peak current to prevent from exciting the transformer mechanical resonances. The risk of acoustic noise is thus greatly diminished while keeping good standby power performance.A low power internal supply block also ensures very low current consumption at startup without hampering the standby power performance.A special primary current sensing technique minimizes the impact of SMPS switching on control IC operation. The choice of peak voltage across the current sense resistor allows dissipation to be further reduced. The negative current sensing technique offers advantages over a traditional approach by avoiding the voltage drop incurred by traditional MOSFET source sensing. Thus, the IC drive capability is greatly improved.Finally, the bulk input ripple ensures a natural frequency dithering which smooths the EMI signature.Features•Variable OFF Time Control Method•Very Low Current Consumption at Startup•Natural Frequency Dithering for Improved EMI Signature •Current Mode Control Operation•Peak Current Compression Reduces Transformer Noise •Programmable Current Sense Resistor Peak V oltage •Undervoltage Lockout•These are Pb−Free DevicesTypical Applications•Auxiliary Power Supply•Standby Power Supply•AC−DC Adapter•Off−line Battery Charger8SOIC−8D SUFFIXCASE 75118534(Top View)FBCSNCPIN CONNECTIONS762NCCTGND GateV CCMARKINGDIAGRAMSFAA= Specific Device CodeA= Assembly LocationL= Wafer LotY= YearW= Work WeekG= Pb−Free Package6TSOP−6(SOT23−6, SC59−6)SN SUFFIXCASE 318GFAAYW GG16SOIC−813FBCS2GNDCT4Gate6(Top View)5V CCTSOP−6ORDERING INFORMATIONDevice Package Shipping†NCP1215SNT1G TSOP−6(Pb−Free)3000 Tape & Reel†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our T ape and Reel Packaging Specifications Brochure, BRD8011/D.NCP1215DR2G SOIC−8(Pb−Free)2500 Tape & ReelFigure 1. Typical ApplicationLineN+−*If your application requires a gate −source resistor, please refer to design guidelines in this document.Figure 2. Representative Block DiagramFBCTCSGNDGateV CCPIN FUNCTION DESCRIPTIONTSOP−6SOIC−8Symbol Description41FB The FB pin provides voltage feedback loop. The current injected into the pin determines theprimary switch OFF time interval. It also influences the peak value of the primary current.32CT Connection for an external timing programming capacitor.13CS The CS pin senses the power switch current.24GND Primary and internal ground.65Gate Output drive for an external power MOSFET.56Vcc Power supply voltage and Undervoltage Lockout.77NC Unconnected pin.88NC Unconnected pin.MAXIMUM RATINGSRating Symbol Value Unit Power Supply Voltage V cc18VFB Pins Voltage Range V FB−0.3 to 18V CS and CT Pin Voltage Range V in−0.3 to 10V Thermal Resistance, Junction−to−Air (SOIC−8 Version)R q JA178°C/W Junction Temperature T J150°C Storage Temperature Range T stg−60 to +150°C ESD Voltage Protection, Human Body Model (Except CT Pin)V ESD−HBM 2.0kV ESD Voltage Protection, Human Body Model for CT Pin V ESD−HBM−CT 1.5kV ESD Voltage Protection, Machine Model (Except CT Pin)V ESD−MM200V ESD Voltage Protection, Machine Model for CT Pin V ESD−MM−CT150V Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.ELECTRICAL CHARACTERISTICS (V CC = 12 V, for typical values T j = 25°C, for min/max values T j = 0°C to +105°C, unless otherwise noted.)Characteristic Symbol Min Typ Max Unit VOLTAGE FEEDBACKOffset Voltage V offset 1.05 1.19 1.34V Maximum CT Pin Voltage at FB Current = 25 m A (Including V offset)V CT−25m A 2.4 3.1 4.3V Maximum CT Pin Voltage at FB Current = 50 m A (Including V offset)V CT−50m A 3.6 4.6 6.2V CT PIN − OFF TIME CONTROLSource Current (CT Pin Grounded)I CT8.09.811.5m A Source Current Maximum Voltage Capability V CT−max− 6.5−V Minimum CT Pin Voltage (Pin Unloaded, Discharge Switch Turned On)V CT−min−−20mV CURRENT SENSEMinimum Source Current (I FB = 180 m A, CT Pin Grounded)I CS−min8.012.516m A Maximum Source Current (I FB = 0 m A, CT Pin Grounded)I CS−max404958m A Comparator Threshold Voltage V th154280mV Propagation Delay (CS Falling Edge to Gate Output)t delay−215310ns GATE DRIVESink Resistance (I sink= 30 mA)R OL254090W Source Resistance (I source= 30 mA)R OH6080130W POWER SUPPLYV CC Startup Voltage V startup−12.514.2V Undervoltage Lockout Threshold Voltage V UVLO7.29.0−V Hysteresis (V startup− V UVLO)V hys 2.2 3.5−V V CC Startup Current Consumption (V CC= 8.0 V)I CC−start− 2.8 6.5m A V CC Steady State Current ConsumptionI CC−SW0.550.9 1.75mA(C GATE= 1.0 nF, f SW= 100 kHz, FB open)TYPICAL CHARACTERISTICS−2511.55011.2250V s t a r t u p , (V )11.0T J , JUNCTION TEMPERATURE (°C)11.6T J , JUNCTION TEMPERATURE (°C)11.111.311.4125V o f f s e t , (V )1.08Figure 3. V startup Threshold vs. JunctionTemperatureFigure 4. V UVLO Threshold vs. JunctionTemperatureFigure 5. Operating Current Consumption vs.Junction TemperatureFigure 6. Offset Voltage vs. JunctionTemperatureT J , JUNCTION TEMPERATURE (°C)Figure 7. Current Sense Source Current vs.Junction TemperatureT J , JUNCTION TEMPERATURE (°C)Figure 8. Current Sense Threshold vs.Junction TemperatureT J , JUNCTION TEMPERATURE (°C)1.121.001.161.2075100−258.7508.4250V U V L O , (V )8.28.88.38.58.612575100−250.985500.97025I C C −S W , (m A )0.9600.990T J , JUNCTION TEMPERATURE (°C)0.9650.9750.98012575100−2550250125751001.041.061.101.141.181.02−2548.05046.525I C S −m a x , (m A )45.549.046.047.047.51257510048.5−25555040250V C S −t h , (m V )30653545501257510060−259.9509.6250I C T, (m A )9.4T J, JUNCTION TEMPERATURE (°C)10.0T J , JUNCTION TEMPERATURE (°C)9.59.79.8125I C S , (m A )Figure 9. CT pin Source Current vs. JunctionTemperatureFigure 10. CT pin Threshold vs. JunctionTemperatureFigure 11. Drive Sink and Source Resistancevs. Junction Temperature Figure 12. Current Sense Source Current vs.Feedback CurrentI fb , FEEDBACK CURRENT (m A)75100−255010250V C T −m i n , (m V )616812141257510010040R s o u r c e −R s i n k , (W )0120T J , JUNCTION TEMPERATURE (°C)206080APPLICATION INFORMATIONThe NCP1215 implements a current mode SMPS with a variable OFF−time dependant upon output power demand. It can be seen from the typical application that NCP1215 is designed to operate with a minimum number of external component. The NCP1215 incorporates the following features:•Frequency Foldback: Since the switch−off time increases when power demand decreases, the switching frequency naturally diminishes in light load conditions. This helps to minimize switching losses and offers excellent standby power performance.•Very Low Startup Current: The patented internal supply block is specially designed to offer a very low current consumption during startup. It allows the use of a very high value external startup resistor, greatly reducing dissipation, improving efficiency and minimizing standby power consumption.•Natural Frequency Dithering: The quasi−fixed T on mode of operation improves the EMI signature since the switching frequency varies with the natural bulk ripple voltage.•Peak Current Compression: As the load becomes lighter, the frequency decreases and can enter the audible range. To avoid exciting transformer mechanical resonances, hence generating acoustic noise, the NCP1215 includes a patented technique, which reduces the peak current as power goes down. As such, inexpensive transformer can be used without having noise problems.•Negative Primary Current Sensing: By sensingthe total current, this technique does not modify the MOSFET driving voltage (Vgs) while switching. Furthermore, the programming resistor together with the pin capacitance, forms a residual noise filter which blanks spurious spikes. Also fixing primary current level to a maximum value sets the maximum power limit.•Programmable Primary Current Sense: It offers a second peak current adjustment variable which improves the design flexibility.•Secondary or Primary Regulation: The feedback loop arrangement allows simple secondary or primary side regulation without significant additional external components.A detailed description of each internal block within the IC is given in the following.Feedback Loop ControlThe main task of the Feedback Loop Block is to control the SMPS output voltage through the change of primary switch OFF time interval. It sets the peak voltage of the timing capacitor, which varies upon the output power demand. Figure 13 shows the simplified internal schematic: Figure 13. Feedback Loop − OFF Time ControlFBTo OFFTimeVThe voltage feedback signal is sensed as a current injected through the FB pin.Figure 14. FB Loop Transfer CharacteristicOFF−TimeComparatorInputVoltageV DDV offset0 mThe transfer characteristic (output voltage to input current) of the feedback loop control block can be seen in Figure 14. V DD refers to the internal stabilized supply whereas the offset value sets the maximum switching frequency in lack of optocoupler current (e.g. an output short−circuit).To keep the switching frequency above the audio range in light load condition the FB pin also regulates in certain range the peak primary current. The corresponding block diagram can be seen from Figure 15.Figure 15. Feedback Loop − Current Sense ControlFBCSThe resulting current sense regulation characteristic can be seen from Figure 16.Figure 16. Current Sense Regulation CharacteristicC S P i n S o u r c e C u r r e n t12.5 m 50 m 0 m FB Pin Sink CurrentWhen the load goes light, the compression circuitry decreases the peak current. This has the effect of slightly increasing the switching frequency but the compression ratio is selected to not hamper the standby power.OFF Time ControlThe loop signal together with the internal current source,via an external capacitor, controls the switch −off time. This is portrayed in Figure 17.Figure 17. OFF Time ControlFrom Feedback Loop BlockDuring the switch −ON time, the CT capacitor is kept discharged by a MOSFET switch. As soon as the latch output changes to a low state, the voltage across CT created by the internal current source, starts to ramp −up until its value reaches the threshold given by the feedback loop demand.Figure 18. CT Pin Voltage (P out 1 u P out 2 u P out 3)V offsetV DDVCT Pin Voltageoff −minThe voltage that can be observed on CT pin is shown in Figure 18. The bold waveform shows the maximum output power when the OFF time is at its minimum. The IC allows an OFF time of several seconds.Primary Current SensingThe primary current sensing circuit is shown in Figure 19.Figure 19. Primary Current SensingWhen the primary switch is ON, the transformer current flows through the sense resistor R cs . The current creates a voltage, V cs which is negative with respect to GND. Since the comparator connected to CS pin requires a positive voltage, the voltage V shift is developed across the resistor R shift by a current source which level −shifts the negative voltage V cs . The level −shift current is in range from 12.5 to 50 m A depending on the Feedback Loop Control block signal (see more details in the Feedback Loop Control section).The peak primary current is thus equal to:I pk +Rshift R CS·I CS(eq. 1)A typical CS pin voltage waveform is shown in Figure 20.Figure 20. CS Pin VoltageTurn −onVFigure 20 also shows the effect of the inductor current of differing output power demand.The primary current sensing method we described, brings the following benefits compared to the traditional approach:•Maximum peak voltage across the current sense resistor is determined and can be optimized by the value of the shift resistor.•CS pin is not exposed to negative voltage, which could induce a parasitic substrate current within the IC and distort the surrounding internal circuitry.•The gate drive capability is improved because the current sense resistor is located out of the gate driver loop and does not deteriorate the turn −on and also turn −off gate drive amplitude.Gate DriverThe Gate Driver consists of a CMOS buffer designed to directly drive a power MOSFET.It features an unbalanced source and sink capabilities to optimize turn ON and OFF performance without additional external components. Since the power MOSFET turns −off at high drain current, to minimize its turn −off losses the sink capability of the gate driver is increased for a faster turn −off.To the opposite, the source capability is lower to slow −down power MOSFET at turn −on in order to reduce the EMI noise.Whenever the IC supply voltage is lower than the undervoltage threshold, the Gate Driver is low, pulling down the gate to ground. It eliminates the need for an external resistor.Startup CircuitAn external startup resistor is connected between high voltage potential of the input bulk capacitor and Vcc supply capacitor. The value of the resistor can be calculated as follows:R startup +V bulk *V startupI startup(eq. 2)Where:V startupV cc voltage at which IC starts operation (see spec.)I startup Startup current V bulk Input bulk capacitor’s voltageSince the V bulk voltage has obviously much higher value than V startup the equation can be simplified in the following way:R startup +V bulkI startup (eq. 3)The startup current can be calculated as follows:I startup +C Vcc V startupt startup)I CC −start(eq. 4)Where:C Vcc Vcc capacitor value t startup Startup timeI CC −startIC current consumption (see spec.)If the IC current consumption is assumed constant during the startup phase, one can obtain resulting equation for startup resistor calculation:R startup +V bulkC VccV startup t startup)I CC −start(eq. 5)Switching FrequencyThe switching frequency varies with the output load and input voltage. The highest frequency appears at highest input voltage and maximum output power.Since the peak primary current is fixed, the on time portion of the switching period can be calculated:t on +L pI pkV bulk(eq. 6)Where:L p Transformer primary inductance I pk Peak primary currentUsing equation for peak primary current estimation the switch −on time is:t on +L p R shiftR cs ·V bulk50·10−6(eq. 7)Minimum switch −on time occurs at maximum input voltage:t on −min +L p R shiftR cs ·V bulk −max50·10−6(eq. 8)As it can be seen from the above equation, the switch −on time linearly depends on the input bulk capacitor voltage.Since this voltage has ripple due to AC input voltage and input rectifier, it allows natural frequency dithering to improve EMI signature of the SMPS.The switch −off time is determined by the charge of an external capacitor connected to the CT pin. The minimum Toff value can be computed by:t off −min +C T Voffset I Ct +C T 1.210−5(eq. 9)+0.12·106C TWhere:V offset Offset voltage (see spec.)I Ct CT pin source current (see spec.)The maximum switching frequency then can be evaluated by:(eq. 10)f sw −max +1t on −min )t off −min+1L p ·R shiftV bulk ·R cs·50·10−6)0.12·106·C TAs output power diminishes, the switching frequency decreases because the switch −off time prolongs upon feedback loop. The range of the frequency change is sufficient to keep output voltage regulation in any light load condition.Application Design ExampleAn example of the typical wall adapter application is described hereafter.As a wall adapter it should be able to operate properly with wide range of the input voltage from 90 V AC up to 265 V AC.The bulk capacitor voltage then can be calculated:(eq. 11)V bulk −min +V AC −min 2Ǹ+90·2Ǹ+127VDC(eq. 12)V bulk −max +V AC −max 2Ǹ+265·2Ǹ+375VDCThe requested output power is 5.2 Watts.Assuming 80% efficiency the input power is equal to:(eq. 13)P in +P out h +5.20.8+6.5WThe average value of input current at minimum input voltage is:(eq. 14)I in −avg +P inVbulk −min+6.5127+51.2mA The suitable reflected primary winding voltage for 600 Vrated MOSFET switch is:(eq. 15)V flbk +600V *V bulk −max *V spike+600*375*100+125VUsing calculated flyback voltage the maximum duty cycle can be calculated:(eq. 16)d max +V flbkV flbk )V bulk −min +125125)127+0.496+0.5Following equation determines peak primary current:(eq. 17)I ppk +2·I in −avg d max+2·51.2·10−30.5+204.7mAThe desired maximum switching frequency at minimum input voltage is 75 kHz.The highest switching frequency occurs at the highest input voltage and its value can be estimated as follows:(eq. 18)f max −high +f max −lowV bulk −maxV bulk −min dmax +75·1033751270.5+110.7kHzThis frequency is much below 150 kHz, so that the desired operating frequency can be exploited for further calculation of the primary inductance:(eq. 19)L p +V bulk −min ·d maxI ppk ·f sw −max +127·0.50.2047·75·103+4.14mH分销商库存信息:ONSEMINCP1215DR2NCP1215SNT1NCP1215DR2G。

NCP1501中文资料