F063-template

完美国际人物代码解析

% O, a. S) m b* i; J$ ] <variable name="level" type="int">1</variable> 等级

% ^0 M% m1 v! I! H <variable name="level2" type="int">0</variable> & nbsp; 修真级别

<variable name="reserved1" type="int">0</variable>7 D1 G- f. y; g. `( z- c3 z

<variable name="reserved2" type="int">0</variable>) W& ~- y: m, W7 L

86174071505c2a0031870148dc9e81e1b710c30b2036f92704b6f7034818ec3a3005e280d30dd09d600918011207a900898298208f4000581cc83cbcbf5c024825000d063910c4060190bb2d5b731804db73186c3c7b186ca

S7通信_??????

S7通信的说明:S7-300支持S7通信,需要调用功能块FB14/15“GET/PUT”,FB12/13“BSEND/BRCV”或者FB8/9“USEND/URCV”。

通过:集成PN口,功能块在StandardLibrary->CommunicationBlocks。

CP,功能块在SIMATIC_NET_CP库。

对于S7-400,通过功能块SFB14/15“GET/PUT”,SFB12/13“BSEND/BRCV”或者SFB8/9“USEND/URCV”实现数据交换。

这些功能块的路径是StandardLibrary->SystemFunctionBlock。

通过CPU上集成PN口通讯的说明:通过开放的IE通讯,使用TCP,ISO-on-TCP以及UDP协议实现数据交换。

通过下面这些通讯块组态连接和数据交换:UDT65“TCON_PAR”数据结构,包括为连接分配的参数UDT66"TCON_ADR”数据结构,包括通讯对象的参数地址(UDP)FB65“TCON”用于建立连接FB66“TDISCON”用于释放连接FB63“TSEND”通过TCP和ISO-on-TCP发送数据FB64“TRCV”通过TCP和ISO-on-TCP接收数据FB67“TUSEND”通过UDP发送数据FB68“TURCV”通过UDP接收数据通过ISO-on-TCP,TCP,UDP或ISO连接的发送/接收通信PROFINETI/O(FC9/10"PNIO_SEND/PNIO_RECV")PLC的以太网连接模式:S7通信(通过以太网CP或集成的PN接口)ISO传输(通过以太网CP)ISO-on-TCP(通过以太网CP或集成的PN接口)TCP(通过以太网CP或集成的PN接口)UDP(通过以太网CP或集成的PN接口)E-mail(通过以太网CP)FTP(通过以太网CP)PROFINETIO(通过以太网CP或集成的PN接口)CBA(通过以太网CP或集成的PN接口)MODBUSTCP(通过以太网CP)2)如何使用FB63"TSEND",FB64"TRCV",FB65"TCON"和FB66"TDISCON"对S7-300或S7-400的集成以太网口进行TCP连接的编程?显示订货号描述:可以通过CPU集成的工业以太网接口使用基于工业以太网的开放式通信进行数据交换.下列的协议都支持开放式通信:TCPISO-on-TCPUDP下列通信块可以用于基于TCP协议的开放式通信:FB65"TCON"建立连接FB66"TDISCON"结束连接FB63"TSEND"发送数据FB64"TRCV"接收数据可以在StandardLibrary->CommunicationBlocks下找到这些通信块.建立TCP连接的连接参数保存在一个数据结构中.本例中,用到UDT65"TCON_PAR"这个数据结构,它是由用户来完成参数化的,TCP连接不在NetPro中组态.注意:关于基于工业以太网的开放式通信的详细内容请参见条目:1214574中的名为"SystemsoftwareforS7-300/400systemandstandardfunctions"的手册.例程描述:S7程序中包含了对FB65"TCON"的调用和带有建立TCP连接的连接参数数据结构UDT65"TCON_PAR".也包含了来自于StandardLibrary->CommunicationBlocks下的FB63"TSEND"和FB64"TRCV"的调用.FB63"TSEND"用于发送数据到S7站或S5站,以及到PC站或到第三方系统.FB64"TRCV"用于接收来自其他S7站,S5站,PC站和第三方系统的数据.首先为S7-300站创建硬件组态.注意配置MB10作为时钟存储器.发送请求由该时钟存储器触发.保存编译S7-300站的硬件组态,下载到CPU。

SST38LF6401RT 4M ×16 CMOS Advanced Multi-Purpose F

SummaryThe SST38LF6401RT is a 4M ×16 CMOS Advanced Multi-Purpose Flash Plus (Advanced MPF+) upgraded for space applications. It is manufactured with SST proprietary, high-performance CMOS SuperFlash ® technology. The split-gate cell design and thick-oxide tunneling injector attain better reliability and manufacturability compared with alternate approaches. The SST38L-F6401RT writes (program or erase) with a 3.0V to 3.6V power supply. This device conforms to JEDEC standard pin assignments for ×16 memories.SST38LF6401RT Parallel Rad Tolerant Flash MemoryFeatures• Density: 64 Mbit• Read access time: 90 ns • Page size (bytes): 8• Temperature range: –55°C to +125°C • Endurance: 10,000 cycles • Organized as 4M ×16• Single voltage read and write operations : 3.0V to 3.6V • Superior reliability, endurance: up to 10,000 cycles mini-mum, greater than 100 years data retention•Low-power consumption (typical values at 5 MHz)• Active current: 4 mA (typical)• Standby current: 3 µA (typical)• Auto low-power mode: 3 µA (typical)• 128-bit unique ID• Security-ID feature, 256 word, user one-time programmable• Protection and security features, hardware boot block protection/WP# input• Hardware Reset Pin (RST#)•Fast read and page read access times: 90 ns page read access times, 4-word page read buffer• Latched address and data• Fast erase times: sector-erase time: 18 ms (typical), block-erase time: 18 ms (typical), chip-erase time: 40 ms (typical)• Erase-suspend/resume capabilities• Fast word and write-buffer programming times:• Word-program time: 7 µs (typical)• Write buffer programming time: 1.75 µs/word(typical)• 16-word write buffer• Automatic write timing: internal V pp generation• End-of-write detection, toggle bits, data# polling, ry/by# output• CMOS I/O compatibility• JEDEC standard, Flash EEPROM pinouts and command sets• Pin, uniform (32 KWord) and non-uniform (8 KWord) op-tions available, user-controlled individual block (32 KWord) protection, using software only methods • Password protection • CFI Compliant•Packages available: 48-lead TSOP ceramic or plasticThe Microchip name and logo, the Microchip logo and SuperFlash are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries. All other trademarks mentioned herein are property of their respective companies.© 2020, Microchip Technology Incorporated. All Rights Reserved. 11/20 DS00003649AWhat is SuperFlash Technology?SuperFlash Technology is an innovative, highly reliable and versatile type of NOR Flash memory invented by Silicon Storage Technology (SST, which is owned by Microchip). SuperFlash memory is much more flexible and reliable than competing non-volatile memories. This technology utilizes a split-gate cell architecture which uses a robust thick-oxide process that requires fewer mask steps resulting in a lower-cost nonvolatile memory solution with excellent data retention and higher reliability.Advantages of SuperFlash Technology• Fast, fixed program and erase times (typical chip-erase time: 40 ms)• No pre-programming or verify required prior to erase (Results in significantly lower power consumption)• Superior reliability (10K cycles and 100 years data retention)• Inherent small sector size (4 KB erase sector vs. 64 KB), results in faster re-write operations and contributes to lowering overall power consumptionSpace Environment• Full wafer lot traceability• 48-lead hermetic ceramic dual flat package (CDFP)• Space-grade screening and qualification (QML and ESCC flow)• T otal ionizing dose: better than 50 Krad, (biased & unbiased) • Heavy ions and protons tested• Single event latch-up immune with a LET > 78 MeV .cm²/mg • Full SEU characterization• No SEU corruption up to 46 MeV .cm²/mgFunctional Block Diagram®。

(文档库)解码位置代码

解码位置代码在一个设备显现故障时,您需要明白该设备在系统中的物理位置,以即能够改换它。

errpt或lscfg命令提供了一个位置代码,指定了故障设备所在的位置。

有了位置代码和效劳器手册,或包括您的型号的IBM® Redbooks®,乃至您能够访问IBM Web 信息中心取得更有效的信息,您就能够够识别设备所在的确切位置。

简介碰到设备故障确信是一件麻烦事。

故障设备的类型可能是热插拔硬件,比如风扇冷却装置或热插拔外设组件互连(PCI)卡。

在这两种情形下,都需要明白设备的物理位置,然后才能改换它。

因此,您需要明白设备的位置代码。

故障设备会显示在错误报告中(利用 errpt 命令),该报告还会发布物理位置代码。

另外,利用 lscfg 命令能够取得您设备的物理位置。

在取得该位置后,应该如何定位设备?AIX 内部代码和物理代码AIX 提供了两种不同的代码,它们别离是:IBM AIX®(内部)位置系统代码物理位置代码AIX 内部位置代码可与物理代码配合利用来识别设备,咱们稍后会在本文这了解这种用法。

利用AIX 生成的那些代码引用了某些特定的设备,例如:10-80-00-3,0 SCSI CD Drive10-80-00-2,0 SCSI disk02-08-00 SAS disk上面的代码是访问实际设备的内部途径,能够利用 lsdev 命令来查看它们。

另一个咱们专门感爱好的位置代码是物理类型的,由固件生成。

例如:U789C.001.DQD3F62-P2-D3 SAS Disk Drive自从几年前发布了IBM POWER5 处置器以后,物理位置代码就成了定位设备的首选方式。

作为一项体会法那么,您需要的一般是物理代码。

这也是本文的重点。

表1 中提供的命令使您能够取得有关设备的各类信息。

表1. 取得有关您的设备的信息的命令命令描述lsdev -C -H -F "name status physloc location description"获得AIX(如果存在)和物理位置代码。

VF6常用命令和主要程序命令

VF6.0常用命令和主要程序命令一、主要命令:二、常用函数三、主要程序语句一、主要命令:1、CREATE作用:建立一个新的表。

格式:CREATE [<文件>|?](注意,命令字符可取前面四个字符,后面可省略不写,即CREA ,下同;中括号表示其中的参数是可选的;|管道符号表示两个参数只能选择一个,不能同时选择,下同。

)说明:文件指建立以.dbf为扩展名的VFP数据库文件,在命令后面加上一个问号表示系统会弹出对话框,要求用户输入想要建立的表名。

在命令中不加文件名或问号系统也会弹出对话框,要求用户输入想要建立的表名。

2、MODIFY STRUCTURE作用:显示表文件结构,并允许修改此表的结构。

格式:MODIFY STRUCTURE说明:只有在用USE命令打开表文件以后,才能显示或修改表文件的结构。

3、APPEND作用:在当前表的尾部(无论表中有无记录)追加记录(在当前表指当前正使用的表)。

格式:APPEND [BLANK]说明:在APPEND命令后面加上BLANK参数表示在当前表的尾部添加一条空白记录。

无BLANK参数时,表示在当前表的尾部添加一条记录并要求用户输入相应的字段内容。

4、INSERT作用:在表文件中间插入一个新记录。

格式:INSERT [BEFORE] [BLANK]说明:INSERT 在当前记录后插入一记录;INSERT BEFORE 在当前记录前插入一记录;INSERT BEFORE BLANK 在当前记录前插入一空记录。

5、BROWSE作用:主要用于打开浏览窗口,查阅表文件并同时进行修改。

格式:BROWSE6、USE作用:打开和关闭表文件。

格式:USE [<文件名>]USE说明:前一个命令用来打开<文件名>指定的表文件,该表如有备注型字段,则同时打开相应的备注文件(.fpt文件);后一个命令关闭当前打开的表文件。

7、LIST和DISPLAY作用:显示表(.dbf)的内容、结构或状态。

F6系列中文使用说明书(all)

使用手册ATEQ F6th 系列F620 / F610 / F6701.04 版Reference: RF-28300D-UF6系列使用手册修订由于持续更新,本使用手册中包含的信息,本设备的功能和设计如有更改,将不另行通知。

前言/演示:定义、特点和测量原理(#673) 前面板和界面 (#676)安装/ 配件:气源 (#677)启动 (#678)配件 (#682)选配件 (#683)错误消息 (#684)以 CC/min显示结果 (#687)F610 电子连接器 (#692/1)F620 电子连接器(#692/2)F670 电子连接器(#692/7)气动连接器(#693)参数/ 特殊循环:特殊循环 (#623)服务特殊循环 (#631)程序选择 (#679)程序参数 (#680)测试循环管理 (#681)爆裂测试 (#698)程序功能:功能管理 (#601)名称 (#602)程序链接 (#603)单位 (#604)自动连接器 (#605)测试检查 (#606)ATR (#607)预充气模式和充气模式 (#608) 阀代码 & 24V辅助输出 (#609) 循环结束 (#610)迷你阀 (#611)复工界限 (#612)密封零件 (#613)N 测试 (#614)参考容积 (#615)标记 (#617)温度校正 1 (#618)峰值保持 (#620) 正负号 (#621)过滤 (#622)流量水平 (#624)非负 (#625)绝对值 (#626)显示模式 (#627) 不排气(#630)蜂鸣器 (#639)外部排气 (#655)ATF (#685)隔断 (#686)By pass (#691)配置菜单:日期 / 时间 (#635)语言 (#642)电子调压阀 (#645)调压阀控制 (#646)稳定调压阀 (#647)压力传感器自动归零 (#648)自动短归零 (#649)排气水平 (#651)RS232 (#652)安全性 (#653)I/O 配置 (#654)IN7 测试 (#656)智能键 (#688)压力单位 (#695)USB (#696)结果菜单 / USB 菜单:储存 (#638)阀服务 (#658)I/O服务 (#661)系统信息 (#665)重置参数 (#669)结果菜单 (#689)服务 / USB (#690)CAN 状态 (#697)# 601: 功能管理# 602: 名称# 603: 程序链接# 604: 单位# 605: 自动连接器# 606: 测试检查# 607: ATR# 608: 预充气模式和充气模式# 609: 阀代码 & 24V 辅助输出# 610: 循环结束# 611: 迷你阀# 612: 复工界限# 613: 密封零件# 614: N 测试# 615: 参考容积# 617: 标记# 618: 温度校准 1# 620: 峰值保持# 621: 符号取反# 622: 过滤# 623: 特殊循环# 624: 流量水平# 625: 非负# 626: 绝对值# 627: 显示模式# 631: 服务特殊循环# 635: 日期 / 时间# 638: 储存# 639 : 蜂鸣器# 642: 语言# 645: 电子调压阀# 646: 调压阀控制# 647: 稳定调压阀# 648: 压力传感器自动归零# 649: 自动短归零# 651: 排气水平# 652: RS232# 653: 安全性# 654: I/O 配置# 655 : 外部排气# 656: IN7 测试# 658: 阀服务# 661: I/O 服务# 665: 系统信息# 669: 重置参数# 673: 定义,特性和测试原理# 676: 前面板和界面# 677: 气源# 678: 启动# 679: 程序选择# 680: 程序参数 (Leak)# 681: 测试循环管理# 682: 配件# 683: 选配件# 684: 错误消息# 685: ATF# 686: 隔断# 687: 以CC/min显示结果# 688: 智能键# 689: 结果菜单# 690: 服务 / USB# 691: By pass# 692/1: F610电子连接器# 692/2: F620电子连接器# 692/7: F670 电子连接器# 693: 气动# 695: 压力单位# 696: USB# 697: CAN 状态# 698 : 爆裂测试功能管理扩展菜单功能能够进行个性化设置和添加个人选项到测试循环当中。

西门子技术问题总汇

文档标题

如何设置模拟量输入模板 SM 431-7KF00的温度补偿? 如何解决 SIMATIC BATCH 的 IL43基本设备上 hotfix 安装的问题? 如果通过 PCS7 V6.1 SP1 DVD 单独安装 SIMATIC BATCH Report 需要注意哪些设置? 为什么冗余模拟量输出模块的每个通道只有一半电流输出? 使用WinCC/Web Navigator V6.1 SP1需要什么样的操作系统和软件? 是否 COM PROFIBUS 可以使用所有版本的 GSD 文件? 如何在 WinCC flexible 中组态与S7 控制器的 Profinet 连接? 如何在操作面板上设定定时器时间, 同时如何输出定时器的剩余时间? 数据块初始值与实际值的含义 如何通过窗口对象滚动条步进调节过程值参数? 使用 SINAUT ST7 向电子邮箱接受方发送文本信息 SMS 需要做何设置? 可以使用CPU317-2PN/DP替代在iMap中组态的CPU315-2PN/DP吗? 什么情况下插入C-PLUG卡或者C-PLUG有什么作用? 通过一台PC,可以使用哪种方式访问与IWLAN/PB link PNIO或IE/PB link PNIO连接的PROFIBUS设备? 当在SINAUT网络中使用4线变压器应该注意哪些设置? 在 SINAUT 网络中,使用MD3拨号调制解调器作为专线调制解调器时,要进行哪些设置? 如何安装 DCF77 天线, 当选择 DCF77 天线时需要注意什么? 使用SINAUT ST7向传真机发送文本信息时,需要进行哪些设置? 在 SINAUT 项目中发送短消息必须进行哪些特殊服务的设置? 如何在S7-300 PN CPU和CP343-1之间建立一个open TCP 通讯连接,以及如何进行数据交换? 如何在两个S7-300 PN CPU之间建立一个open TCP 通讯连接,以及如何进行数据交换? 哪些控制系统可以成功与SINAUT ST7一起使用? 使用“零-Modem”电缆连接 TIM 模块应该注意什么? 当用 SINAUT 诊断工具的ST1协议进行诊断时,为什么TIM的状态不能显示? TIM 3V-IE 和 TIM 3V-IE Advanced 模块在以太网上通信时使用哪个端口号? 如何对没有接入网络的S7-200CPU编程? 掉电后,LOGO!的程序会丢失吗? 从 PCS7 V6.1 起,为什么没有分配任何 hierarchy (PH) 的 测量点(变量)通过编译不能在OS中自动创建相应的变量? 在SFC中,如何实现从一个 Sequencer 跳出后回到另一个 Sequencer 的某个固定位置并继续执行? 如何实现过程变量的平均值归档? 存储文件的目标路径和备份可选路径有何作用? WinCC变量归档中如何实现采集周期小于500ms的变量归档? 为什么在 OS 上会显示如下信息“时间跳变通知-永久切换为从站模式”? 在西门子A&D产品支持网站是否可以下载关于ET200M的手册? 在S7-400上怎样安装冗余电源? UDT改变后怎样更新使用UDT产生的数据块。 为什么在FB块中使用OUT变量赋值被调用FB块的IN变量时出现错误信息34:4469? 如何查看4-mation导入-导出错误 不能正确引导8212-1QU IBM/Lenovo M52 ThinkCentre 实时趋势更新缓慢的原因 如何保存变量名字典CSV文件的格式

分销.u8供应链.零售常见问题

1.请问这个业务如何在分销中处理?给客户发了10件货,但是到达客户那里时客户只验收了9件,那么这一件的差异怎么办??解决方法:一般是先查明原因,得出处理结果,如果是仓库少发,并且不再发货,那做个退货冲掉销售(注:退货单上打上业务调整的勾)2. 单据额度是按业务员设置的,设置的是业务员额度,是不是做单据的时候超过业务员额度或超过客户档案里信用额度,系统都是控制呢解决方法:单据额度,是按照业务员去控制的。

信用额度,是按照客户去控制的3. 分销的的收款如何体现是预收款,还是销售后回款?解决方法:系统对预收款没有办法做到对预收款的款项余额的控制. 预付款现在没有控制的地方。

4.问下,DRP871中,TempQuery库mdf+log=34G,直接删除可以吧?解决方法:选择数据库--右键--属性---数据文件,这个进行设置。

5.咨询下,颜色、尺码为自由项,进入规格小票,自由项杯型不进入规格小票,录入销售订单时如何设置杯型为必录项。

解决方法:里面是库存单据自由项是否必输,但销售订单不是库存单据,所以杯型在销售订单可以不录入。

6.零售871修改了已经上传的VIP客户资料,状态变成未上传,是不是再上传就可以更新后台数据了。

解决方法:可以更新。

7.调拔申请单的数量批复后能否改为大于申请的数量,另只能册除不能增加商品是吗? 解决方法:设置审批流后也只能改小不能改大. 调拨出库单不能超过调拨申请。

如果需要增加,需要手工增加一个调拨出库单.8.臧总,单据打印模板,页面设置中的边距调整后(在机构业务端打印预览时,修改的)不能保存是什么原因呢?解决方法:单据的打印设置都得到系统管理端调整,报表的打印格式才可以在预揽时调整;和打印机没关系,除非是选用不同纸张的打印机。

用A4都没关系,如果选用不同纸张,就得设置多模板.9.店存余额上传的作用是什么啊?解决方法:传到零售管理端,零售管理端的库存数据来自门店的店存余额上传,先下载,就是将门店更新为与分销一致,然后再上传,将从分销下载到的数据往零售后台传。

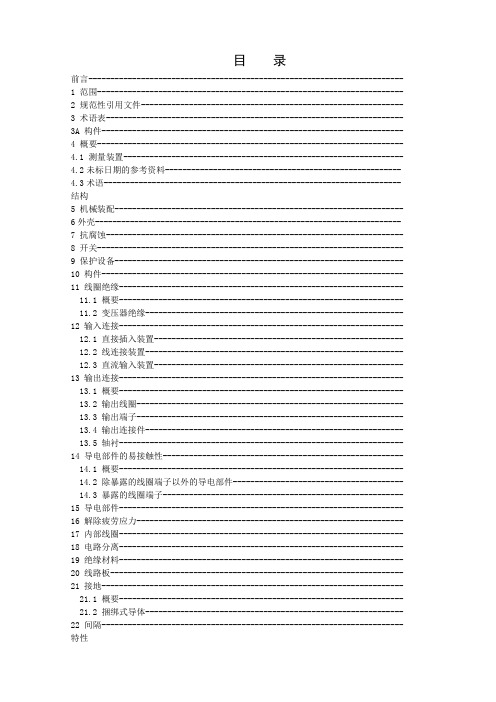

UL 1310 目录

目录前言------------------------------------------------------------------------1 范围----------------------------------------------------------------------2 规范性引用文件------------------------------------------------------------3 术语表-------------------------------------------------------------------- 3A 构件---------------------------------------------------------------------4 概要---------------------------------------------------------------------- 4.1 测量装置---------------------------------------------------------------- 4.2未标日期的参考资料------------------------------------------------------ 4.3术语-------------------------------------------------------------------- 结构5 机械装配------------------------------------------------------------------ 6外壳----------------------------------------------------------------------7 抗腐蚀--------------------------------------------------------------------8 开关----------------------------------------------------------------------9 保护设备------------------------------------------------------------------10 构件---------------------------------------------------------------------11 线圈绝缘-----------------------------------------------------------------11.1 概要-----------------------------------------------------------------11.2 变压器绝缘-----------------------------------------------------------12 输入连接-----------------------------------------------------------------12.1 直接插入装置---------------------------------------------------------12.2 线连接装置-----------------------------------------------------------12.3 直流输入装置---------------------------------------------------------13 输出连接-----------------------------------------------------------------13.1 概要-----------------------------------------------------------------13.2 输出线圈-------------------------------------------------------------13.3 输出端子-------------------------------------------------------------13.4 输出连接件-----------------------------------------------------------13.5 轴衬-----------------------------------------------------------------14 导电部件的易接触性-------------------------------------------------------14.1 概要-----------------------------------------------------------------14.2 除暴露的线圈端子以外的导电部件---------------------------------------14.3 暴露的线圈端子-------------------------------------------------------15 导电部件-----------------------------------------------------------------16 解除疲劳应力-------------------------------------------------------------17 内部线圈-----------------------------------------------------------------18 电路分离-----------------------------------------------------------------19 绝缘材料-----------------------------------------------------------------20 线路板-------------------------------------------------------------------21 接地---------------------------------------------------------------------21.1 概要-----------------------------------------------------------------21.2 捆绑式导体-----------------------------------------------------------22 间隔--------------------------------------------------------------------- 特性24 泄露电流测试-------------------------------------------------------------25 潮湿暴露后的泄露电流测试及电介质耐压测试---------------------------------26 最大输出电压测试---------------------------------------------------------27 最大输入测试-------------------------------------------------------------28 输出电流及功率测试------------------------------------------------------- 28.1 概要-----------------------------------------------------------------28.2固有限制-------------------------------------------------------------28.3 非固有限制-----------------------------------------------------------29 过电流保护装置的校准测试-------------------------------------------------30 满载输出电流测试---------------------------------------------------------31 正常温度测试-------------------------------------------------------------32 电介质耐压测试-----------------------------------------------------------32.1 概要-----------------------------------------------------------------32.2 感应电压-------------------------------------------------------------33 过电流及超温保护设备的承受力测试-----------------------------------------34 重复电介质耐压测试-------------------------------------------------------35 开关及控制的过载及承受能力测试-------------------------------------------36 次开关上的过载测试-------------------------------------------------------37 操作测试-----------------------------------------------------------------38 异常测试-----------------------------------------------------------------38.1 概要-----------------------------------------------------------------38.2 输出负载-------------------------------------------------------------38.3 变压器烧毁-----------------------------------------------------------38.4 反向极性-------------------------------------------------------------38.5 开关位置-------------------------------------------------------------38.6 构件损坏-------------------------------------------------------------38.7 线路板异常操作测试---------------------------------------------------38.8 逆流保护-------------------------------------------------------------39 绝缘材料上的测试---------------------------------------------------------40 解除疲劳应力测试--------------------------------------------------------- 40A 推迟解除测试------------------------------------------------------------41 直接插入的锋利边的安全测试-----------------------------------------------42 直接插入的输入接触安全测试-----------------------------------------------42.1 概要-----------------------------------------------------------------42.2 有折叠式的及可收回式的锋利边的装置-----------------------------------43 输出连接件的安全测试-----------------------------------------------------44 破坏性测试---------------------------------------------------------------44.1 概要-----------------------------------------------------------------44.2 直接插入装置的撞击---------------------------------------------------44.3 线连接装置的撞击-----------------------------------------------------44.4 直接插入装置的棒压力-------------------------------------------------44.5 直接插入装置的抗变形-------------------------------------------------45 捆绑导体测试------------------------------------------------------------- 制造及生产测试46 电介质耐压测试-----------------------------------------------------------额定48 概要--------------------------------------------------------------------- 标识49 细节--------------------------------------------------------------------- 49.1 概要----------------------------------------------------------------- 49.2 警告标识-------------------------------------------------------------49.3 使用----------------------------------------------------------------- 说明书50 使用说明----------------------------------------------------------------- 附录A参考标准--------------------------------------------------------------------。

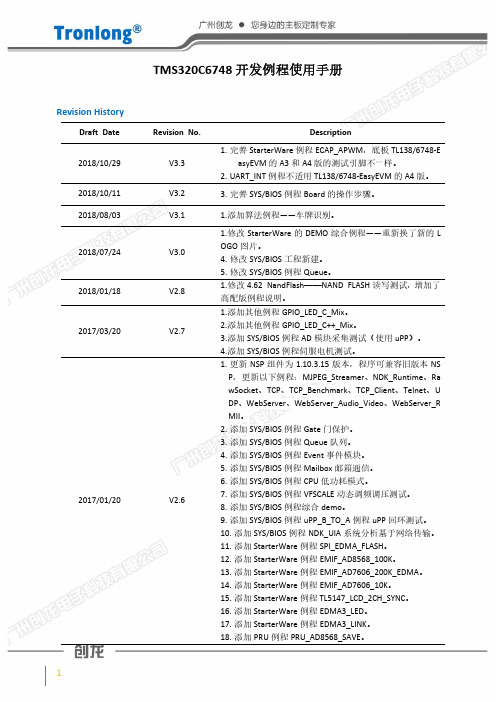

TMS320C6748开发例程使用手册

TMS320C6748开发例程使用手册Revision HistoryDraft Date Revision No. Description2018/10/29 V3.3 1.完善StarterWare例程ECAP_APWM,底板TL138/6748-EasyEVM的A3和A4版的测试引脚不一样。

2.UART_INT例程不适用TL138/6748-EasyEVM的A4版。

2018/10/11 V3.2 3.完善SYS/BIOS例程Board的操作步骤。

2018/08/03 V3.1 1.添加算法例程——车牌识别。

2014/05/05 V1.0 1.初始版本。

目录1 开发板准备 (16)1.1查看仿真器驱动是否正常安装 (17)2 程序加载和烧写 (19)2.1基于仿真器的程序加载和烧写 (19)2.1.1设置工程配置文件信息 (19)2.1.2测试仿真器是否正常连接 (20)2.1.3加载GEL文件 (21)2.1.4CCS连接开发板CPU (22)2.1.5查看CPU版本号 (23)2.1.6加载文件烧写程序 (24)2.1.7基于仿真器烧写程序到NAND FLASH (24)2.1.8NAND FLASH烧写格式镜像转换方法 (29)2.2基于串口的程序加载和烧写 (31)2.2.1串口加载和烧写格式镜像转换方法 (31)2.2.2程序加载和运行 (33)2.2.3基于串口烧写程序到NAND FLASH (39)2.2.4基于串口烧写程序到SPI FLASH (42)2.3基于SD卡运行程序 (44)2.3.1SD启动格式镜像转换方法 (44)2.3.2将程序烧写到SD卡 (46)2.3.3SD卡模式启动开发板 (49)2.4基于SD卡烧写程序到NAND FLASH (49)2.4.1格式化SD卡 (49)2.4.2准备烧写镜像 (53)2.5基于网络的程序烧写和启动 (55)3 CCS工程新建、编译和导入 (59)3.1裸机工程创建 (61)3.1.1新建工程 (61)3.1.2编写程序 (64)3.1.3编译和运行程序 (64)3.2SYS/BIOS工程创建 (66)3.2.1创建SYS/BIOS平台配置文件 (68)3.2.2新建SYS/BIOS工程 (74)3.2.3编译与运行程序 (79)3.3CCS工程导入和编译步骤 (79)3.4开启多线程编译 (86)3.5添加自动生成NAND FLASH烧写.ais文件 (88)4 基于StarterWare的Demo例程演示 (92)4.1DEMO——综合例程 (94)4.2GPIO_LED——GPIO输出(LED灯) (98)4.3GPIO_KEY——GPIO输入(按键中断) (98)4.4GPIO_KEY_EDMA——按键触发EDMA事件 (99)4.5GPIO_KEY_TIMER_EventCombine——按键及定时器中断 (101)4.6TIMER——定时器 (101)4.7TIMER_Dual_32-bit_Chained——关联32-bit模式定时器/计数器 (102)4.8TIMER_Dual_32-bit_UnChained——独立32-bit模式定时器/计数器 (104)4.9TIMER_Dual_32-bit_UnChained_4-bit_Prescaler——独立32-bit模式/额外4-bit分频定时器/计数器 (106)4.10UART0_INT——UART0串口中断收发 (108)4.11UART1_POLL——UART1串口查询收发 (110)4.12UART2_INT——UART2串口中断收发 (111)4.13UART2_EDMA——EDMA串口收发 (112)4.14RS485——RS485串口查询收发 (113)4.15TL_MULTUART_INT——多串口模块(查询方式) (114)4.16TL_MULTUART_POLL——多串口模块(中断方式) (116)4.17IIC_EEPROM——IICEEPROM读写 (117)4.18SPI_FLASH——SPI FLASH读写 (118)4.19SPI_EDMA_FLASH——SPI FLASH读写测试 (119)4.20SPI_DAC_AD5724——4通道DAC模块(模拟SPI总线) (120)4.21SPI_DAC_AD5724v2——4通道DAC模块(SPI总线) (124)4.22WatchDog——看门狗 (124)4.23NMI——不可屏蔽中断 (125)4.24PWM——高精度脉冲宽度调制器PWM输出 (125)4.25ECAP_APWM——增强型捕获模块ECAP辅助输出 (127)4.26PWM_ECAP——增强型捕获模块ECAP捕获 (130)4.27RTC——RTC时钟 (132)4.28LCD——LCD显示 (133)4.29VGA——VGA显示 (135)4.30LCD_TOUCH_4INCH3——4.3寸触摸屏 (136)4.31LCD_TOUCH——7寸触摸屏 (138)4.32LCD_TOUCH_5INCH6/10INCH4/12INCH/15INCH——多种尺寸触摸屏 (138)4.33GRLIB_DEMO——StarterWare图形库控件 (140)4.34MMCSD——SD卡读写 (140)4.35SATA——SATA枚举测试 (141)4.36USB_DEV_BULK——USB OTG从方式(USB BULK管道通信) (141)4.37USB_DEV_MSC——USB OTG从方式(虚拟存储设备) (150)4.38USB_DEV_SERIAL——USB OTG从方式(USB虚拟串口) (160)4.39USB_HOST_KEYBOARD——USB OTG主方式(USB键盘) (163)4.40USB_HOST_MOUSE——USB OTG主方式(USB鼠标) (163)4.41USB_HOST_MSC——USB OTG主方式(U盘内容查看) (165)4.42ENET_HTTPD——网络Web服务器 (166)4.43ENET_HTTPD_RMII——网络Web服务器(使用RMII接口) (169)4.44ENET_ECHO——网络Socket通信 (171)4.45AUDIO_LINE_OUT——Line Out音频输出(EMDA方式) (177)4.46AUDIO_LINE_OUT_INTR——Line Out音频输出(中断方式) (182)4.47AUDIO_LINE_OUT_POLL——Line Out音频输出(查询方式) (183)4.48AUDIO_LINE_OUT_WAV——Line Out音频输出(导入文件方式) (184)4.49AUDIO_MIC_IN——Mic In音频输入(EMDA方式) (187)4.50AUDIO_MIC_IN_INTR——Mic In音频输入(中断方式) (188)4.51AUDIO_MIC_IN_POLL——Mic In音频输入(查询方式) (189)4.52AUDIO_MIC_IN_SAVEMEM——Mic In音频输入(保存文件方式) (189)4.53AUDIO_MIC_IN_WAVE——Mic In音频输入(波形输入方式) (195)4.54AUDIO_LINE_IN——Line In音频输入(EMDA方式) (198)4.55AUDIO_LINE_INTR——Line In音频输入(中断方式) (199)4.56AUDIO_LINE_POLL——Line In音频输入(查询方式) (200)4.57AUDIO_LINE_IN_SAVEMEM——Line In音频输入(保存文件方式) (201)4.58AUDIO_LINE_IN_WAVE——Line In音频输入(波形输入方式) (206)4.59McBSP——McBSP总线数据收发 (209)4.60VPIF_OV2640——VPIF总线CMOS摄像头数据采集 (211)4.61Memory_Benchmark——内存读写速度测试 (213)4.62NandFlash——NAND FLASH读写测试 (213)4.63EMIF_AD7606——EMIFA总线8通道并口AD数据采集 (215)4.64EMIF_AD7606v2——EMIFA总线8通道并口AD数据采集 (219)4.65EMIF_AD7606_10K——使用CPU采集方式按10k速度采样 (222)4.66EMIF_AD7606_200K_EDMA——使用EDMA方式按200k采样率进行采样 (223)4.67EMIF_AD7656——EMIFA总线6通道并口AD数据采集 (224)4.68EMIF_AD7656v2——EMIFA总线6通道并口AD数据采集 (227)4.69EMIF_AD8568——EMIFA总线8通道并口AD数据采集 (229)4.70EMIF_AD8568v2——EMIFA总线8通道并口AD数据采集 (231)4.71EMIF_AD8568_100K——以100 KHz采样AD8568 8通道AD数据 (235)4.72EMIF_FPGA——EMIFA总线FPGA读写测试 (238)4.73EMIF_FPGA_DMA——EMIFA总线FPGA读写测试(经过EDMA优化) (240)4.74EDMA3——EDMA3一维数据传输 (242)4.75EDMA3_TRANSPOSE——EDMA3二维数据传输 (243)4.76uPP_B_TO_A——uPP总线FPGA读写测试 (244)4.77uPP_2CH——uPP板间双通信测试 (248)4.78TL2515_CAN——双CAN通信测试 (250)4.79TL5147_VGA——复合视频输入VGA显示测试 (252)4.80TL5147_LCD——复合视频输入LCD显示测试 (254)4.81TL5147_LCD_2CH——复合视频双通道输入LCD显示测试 (257)4.82H264Encoder——编码例程测试 (258)4.83NRF24L01——2.4G无线模块测试 (262)4.84HC-SR04——超声波测距测试 (265)4.85DHT11——温湿度传感器测试 (267)4.86WIFI_UART——串口WIFI模块测试 (269)4.87RFID——RFID射频识别测试 (273)4.88ECAP_REMOTE——红外遥控测试 (275)4.89BTUART——串口蓝牙模块测试 (277)4.90MPU6050——三轴加速陀螺仪测试 (279)4.91ZIGBEE——串口转Zigbee无线测试 (282)4.92ClockOut——时钟频率测试 (284)4.93DSPClockSpeed——CPU时钟测试 (287)4.94Fsfat——SD卡读写测试 (288)4.95SPI0——SPI0测试例程 (289)4.96UART2_INT_FIFO——UART2 FIFO中断模式 (291)4.97TL5147_LCD_3CH_Multi——TL5147摄像头实现3路图片采集 (292)4.98TL5147_LCD_2CH_SYNC——双路5147摄像头同时采集显示 (295)4.99EDMA3_LINK——EDMA链接工作方式 (296)4.100EDMA3_LED——EDMA方式让LED闪烁 (297)4.101EMIF_AD7606_PinBoard——EMIF拓展板测试 (297)5 基于SYS/BIOS的Demo例程演示 (300)5.1Board——综合例程 (300)5.2GPIO_LED——任务 (306)5.3GPIO_LED_MUTEX——抢占式多任务 (306)5.4GPIO_LED_STATIC——静态创建任务 (307)5.5Semaphore_Binary——二进制信号量 (311)5.6Semaphore_Counting——计数型信号量 (312)5.7Clock——时钟 (313)5.8Timestamp——SYS/BIOS时间戳(通用) (313)5.9Timestamp_C674x——SYS/BIOS时间戳(专用) (314)5.10Timer——定时器(通用) (314)5.11Timer_C674x——定时器(专用) (316)5.12Timer_C674x_Runtime——定时器(动态创建) (316)5.13Timer_C674x_Runtime_Reload——定时器(动态创建、更改定时周期) (317)5.14HWI_C674x——硬件中断(HWI设备专用组件) (317)5.15HWI_C674x_Hook——硬件中断(HWI挂钩函数) (318)5.16HWI_C674x_Nest——硬件中断(HWI中断嵌套) (319)5.17HWI_Runtime——硬件中断(HWI) (319)5.18HWI_Runtime_Post_SWI——硬件中断(HWI发布软件中断) (319)5.19HWI_Runtime_Post_Task——硬件中断(HWI触发任务) (320)5.20SWI——软件中断(静态配置) (320)5.21SWI_Runtime——软件中断(SWI) (322)5.22SWI_Runtime_Post_Conditionally_andn——软件中断(有条件触发ANDN)3225.23SWI_Runtime_Post_Conditionally_dec——软件中断(有条件触发DEC) (323)5.24SWI_Runtime_Post_Unconditionally_or——软件中断(无条件触发OR) (323)5.25MEMORY——内存分配 (324)5.26MMCSD——SD卡RAW模式 (325)5.27MMCSD_FatFs——SD卡FAT文件系统 (328)5.28UART1——UART1串口查询收发 (330)5.29UART2——UART2串口查询收发 (332)5.30UART2_INT——UART2串口中断接收 (333)5.31AudioLineInSave——Line In音频输入与保存 (334)5.32AudioMicInSave——MicIn音频输入与保存 (334)5.33AudioPlayMP3——MP3音频播放(SD卡) (335)5.34AudioPlayWAV——WAV音频播放(SD卡) (335)5.35LCD_TOUCH——触摸屏 (336)5.36TCP_Client——TCP客户端 (337)5.37TCP——TCP服务器 (344)5.38UDP——UDP通信 (348)5.39TCP_Benchmark——TCP发送/接收速度测试 (351)5.40Telnet——Telnet协议 (355)5.41Telnet——TFTP协议 (362)5.42WebServer——网络Web服务器 (368)5.43NDK_UIA——基于网络传输的系统分析 (376)5.44NDK_Runtime——网络Web服务器(支持串口输入IP) (384)5.45WebServer_RMII——网络Web服务器(使用RMII接口) (387)5.46WebServer_Audio_Video——Web服务器音视频实验 (395)5.47MJPEG_Streamer——IP Camera网络摄像头 (399)5.48RawSocket——以太网数据链路层通信 (402)5.49EDMA3——EDMA3一维数据传输 (413)5.50McBSP_LoopBack——McBSP内部回环测试 (414)5.51McBSP——McBSP外部回环测试 (415)5.52Gate——SYS/BIOS门保护 (416)5.53Queue——SYS/BIOS队列 (416)5.54Event——SYS/BIOS事件模块 (417)5.55Mailbox——SYS/BIOS邮箱通信 (418)5.56SLEEP——CPU低功耗模式 (418)5.57VFSCALE——动态调频调压测试 (419)5.58uPP_B_TO_A——uPP回环测试 (420)5.59ADS1278_uPP——AD模块采集测试(使用uPP) (423)5.60伺服电机测试——通过DSP与FPGA控制伺服电机运行 (424)6 算法Demo例程演示 (426)6.1FIR——有限长单位冲激响应滤波器 (426)6.2IIR——无限脉冲响应数字滤波器 (432)6.3Matrix——矩阵运算 (437)6.4FFT——快速傅里叶变换/逆变换 (439)6.5FFT_Benchmark——快速傅里叶变换/逆变换(打开/关闭缓存速度对比). 4426.6FFT_DIT2——基2时间抽取快速傅里叶变换/逆变换(原址计算) (465)6.8RGB2Gray——RGB24图像转灰度 (471)6.9HIST——灰度图像直方图 (475)6.10InteEqualize——直方图均衡化 (484)6.11ImageReverse——图像反色 (493)6.12Canny——边缘检测 (499)6.13Threshold——灰度图像二值化 (505)6.14LinerTrans——灰度图像线性变换 (512)6.15Zoom——图像缩放 (519)6.16Rotate——图像旋转 (525)6.17MATH——数学函数库 (532)6.18UniversalCopy——基于Codec Engine的数据复制算法 (533)6.19MP3Decode——MP3解码 (534)6.20MP3Decode_SD——MP3解码(使能缓存及通过SD存取) (535)6.21AACLCDecode——AACLCDecode AAC解码 (538)6.22AACHEv2Decode——AACHEv2Decode AAC解码 (539)6.23AACLCEncode——AACLCEncode AAC编码 (541)6.24G711ADecode——G711A率语音编码 (542)6.25G711ADecode——G711A率语音解码 (543)6.26ImageProcess——数字识别 (545)6.27FaceDetect——人脸识别跟踪 (548)6.28ImageProcessQR——二维码扫描 (549)6.29ImageProcessChar——文字识别 (553)6.30ImageProcessAlph——字母识别 (556)6.31Plate Recognition Demo——车牌识别 (559)7 基于TL-EasyBox实验板Demo例程演示 (569)7.1BUZZER——蜂鸣器 (570)7.2MATRIX_KEY——4x4键盘 (570)7.3DAC_TLC5615——DAC输出 (571)7.4EMIF_AD7606——EMIFA总线8通道并口AD数据采集 (573)7.6DCMOTOR——直流电机 (575)7.7STEPPERMOTOR——步进电机 (576)7.8EASYBOX_DEMO——实验板综合测试 (577)8 基于PRU的Demo例程演示 (579)8.1PRU_GPIO_LED——PRU控制GPIO输出 (583)8.2PRU_GPIO_KEY——PRU控制GPIO输入 (583)8.3PRU_TL5724_DAC——PRU驱动DAC输出测试 (583)8.4PRU_TL5724_DACv2——PRU控制AD5724输出连续波形 (585)8.5PRU_TL7606_ADC——PRU触发ADC采集模拟量 (588)8.6PRU_TL8568_ADC——PRU触发ADC采集模拟量 (590)8.7PRU_uPP_B_TO_A——PRU控制uPP传输数据 (591)8.8PRU_AD8568_SAVE——PRU控制AD8568采集数据存储SD卡 (595)8.9PRU_TIMER2_POLL——PRU控制定时器 (596)8.10PRU to DSP_Interrupt——PRU向DSP发送中断 (596)9 其它Demo例程演示 (597)9.1GPIO_LED_Assembly——GPIO输出(标准汇编) (597)9.2GPIO_LED_LinearAssembly——GPIO输出(线性汇编) (597)9.3GPIO_LED_C++——GPIO输出(C++) (597)9.4GPIO_KEYv2——不使用StarterWare函数库中断例程 (597)9.5GPIO_LED_C_Mix——C语言调用线性汇编、汇编语句及函数 (598)9.6GPIO_LED_C++_Mix——C++语言调用C语言、线性汇编、汇编语句及函数 598附录A (599)1TMS320C6748开发板准备测试开发板硬件将开发板的UART2连接到PC机。

ARM系列文档

Cortex™-A9 NEON™ Media ProcessingEngineRevision: r4p0Technical Reference ManualCortex-A9 NEON Media Processing EngineTechnical Reference ManualCopyright ©2008-2012 ARM. All rights reserved.Release InformationThe following changes have been made to this book.Change history Date Issue Confidentiality Change04 April 2008A Non-Confidential First release for r0p010 July 2008B Non-Confidential Restricted Access Second release for r0p012 Dec 2008C Non-Confidential Restricted Access First release for r1p024 September 2009D Non-Confidential Restricted Access First release for r2p027 November 2009E Non-Confidential Unrestricted Access Second release for r2p027 April 2010F Non-Confidential Unrestricted Access First release for r2p221 July 2011G Non-Confidential First release for r3p026 March 2012G2Non-Confidential First release for r4p0 Proprietary NoticeWords and logos marked with ® or ™ are registered trademarks or trademarks of ARM® in the EU and other countries, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.This document is intended only to assist the reader in the use of the product. ARM shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.Where the term ARM is used it means “ARM or any of its subsidiaries as appropriate”.Confidentiality StatusThis document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.Product StatusThe information in this document is final, that is for a developed product.Web AddressContentsCortex-A9 NEON Media Processing Engine Technical Reference ManualPrefaceAbout this book (v)Feedback (viii)Chapter1Introduction1.1About the Cortex-A9 NEON MPE ............................................................................ 1-21.2Applications .............................................................................................................1-41.3Product revisions ..................................................................................................... 1-5Chapter2Programmers Model2.1About this programmers model ................................................................................ 2-22.2New Advanced SIMD and VFP features .................................................................. 2-42.3Supported formats ................................................................................................... 2-52.4Advanced SIMD and VFP register access ............................................................... 2-62.5Register summary .................................................................................................. 2-102.6Register descriptions ............................................................................................. 2-11Chapter3Instruction Timing3.1About instruction cycle timing .................................................................................. 3-23.2Writing optimal VFP and Advanced SIMD code ...................................................... 3-33.3Cortex-A9 NEON MPE instructions .........................................................................3-43.4Instruction-specific scheduling ................................................................................. 3-9Appendix A RevisionsPrefaceThis preface introduces the Cortex-A9 NEON™ Media Processing Engine (MPE) TechnicalReference Manual. It contains the following sections:•About this book on page v•Feedback on page viii.About this bookThis book is for the Cortex-A9 NEON MPE.Product revision statusThe r n p n identifier indicates the revision status of the product described in this book, where:r n Identifies the major revision of the product.p n Identifies the minor revision or modification status of the product.Intended audienceThis book is written for system designers, system integrators, and verification engineers whoare designing a System-on-Chip (SoC) device that uses the Cortex-A9 NEON MPE. The bookdescribes the external functionality of the Cortex-A9 MPE.Using this bookThis book is organized into the following chapters:Chapter1 IntroductionRead this for an introduction to the Cortex-A9 implementation of the ARMAdvanced SIMD media processing architecture.Chapter2 Programmers ModelRead this for a description of the Cortex-A9 NEON programmers model.Chapter3 Instruction TimingRead this for a description of the cycle timings of instructions on the Cortex-A9NEON MPE.Appendix A RevisionsRead this for a description of the technical changes between released issues of thisbook.GlossaryThe ARM Glossary is a list of terms used in ARM documentation, together with definitions forthose terms. The ARM Glossary does not contain terms that are industry standard unless theARM meaning differs from the generally accepted meaning.See ARM Glossary, /help/topic/com.arm.doc.aeg0014-/index.html. ConventionsConventions that this book can use are described in:•Typographical conventionsTypographical conventionsThe typographical conventions are:italic Introduces special terminology, denotes cross-references, and citations.bold Highlights interface elements, such as menu names. Denotes signalnames. Also used for terms in descriptive lists, where appropriate.monospace Denotes text that you can enter at the keyboard, such as commands, fileand program names, and source code.monospace Denotes a permitted abbreviation for a command or option. You can enterthe underlined text instead of the full command or option name.monospace italic Denotes arguments to monospace text where the argument is to bereplaced by a specific value.monospace bold Denotes language keywords when used outside example code.< and > Enclose replaceable terms for assembler syntax where they appear in codeor code fragments. For example:MRC p15, 0 <Rd>, <CRn>, <CRm>, <Opcode_2>SMALL CAPITALS Applies when the relevant term is used in body text. For example:IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC,UNKNOWN, and UNPREDICTABLE.Additional readingThis section lists publications by ARM and by third parties.See Infocenter, , for access to ARM documentation.ARM publicationsThis book contains information that is specific to this product. See the following documents forother relevant information:•Cortex-A9 Technical Reference Manual (ARM DDI0388)•Cortex-A9 MPCore Technical Reference Manual (ARM DDI0407)•Cortex-A9 Floating-Point Unit Technical Reference Manual (ARM DDI0408)•Cortex-A9 MBIST Controller Technical Reference Manual (ARM DDI0414)•Cortex-A9 Configuration and Sign-Off Guide (ARM DII0146)•CoreSight™ PTM™-A9 Technical Reference Manual (ARM DDI0401)•CoreSight PTM-A9 Configuration and Sign-Off Guide (ARM DII0161)•CoreSight PTM-A9 Integration Manual (ARM DII0162)•CoreSight Program Flow Trace Architecture Specification (ARM IHI0035)•AMBA® Level 2 Cache Controller (L2C-310) Technical Reference Manual (ARM DDI0246)•L220 Cache Controller Technical Reference Manual (ARM DDI0329)•AMBA AXI Protocol Specification (ARM IHI0022)•AMBA Specification (ARM IHI0011)•ARM Architecture Reference Manual, ARMv7-A and ARMv7-R edition (ARM DDI0406)•RealView™ Compilation Tools Developer Guide (ARM DUI0203)•RealView ICE and RealView Trace User Guide (ARM DUI0155)•Intelligent Energy Controller Technical Overview (ARM DTO0005).Other publicationsThis section lists relevant documents published by third parties:•ANSI/IEEE Std 754-1985, IEEE Standard for Binary Floating-Point Arithmetic.FeedbackARM welcomes feedback on this product and its documentation.Feedback on this productIf you have any comments or suggestions about this product, contact your supplier and give:•The product name.•The product revision or version.•An explanation with as much information as you can provide. Include symptoms anddiagnostic procedures if appropriate.Feedback on contentIf you have comments on content then send an e-mail to errata@. Give:•the title•the number, ARM DDI 0409H•the page numbers to which your comments apply• a concise explanation of your comments.ARM also welcomes general suggestions for additions and improvements.NoteA RM tests the PDF only in Adobe Acrobat and Acrobat Reader, and cannot guarantee thequality of the represented document when used with any other PDF reader.Chapter1IntroductionThis chapter introduces the Cortex-A9 implementation of the ARM Advanced SIMD mediaprocessing architecture. It contains the following sections:•About the Cortex-A9 NEON MPE on page1-2•Applications on page1-4•Product revisions on page1-5.Introduction1.1About the Cortex-A9 NEON MPEThe Cortex-A9 NEON MPE extends the Cortex-A9 functionality to provide support for theARM v7 Advanced SIMD and Vector Floating-Point v3 (VFPv3) instruction sets. TheCortex-A9 NEON MPE supports all addressing modes and data-processing operationsdescribed in the ARM Architecture Reference Manual.The Cortex-A9 NEON MPE features are:•SIMD and scalar single-precision floating-point computation•scalar double-precision floating-point computation•SIMD and scalar half-precision floating-point conversion•8, 16, 32, and 64-bit signed and unsigned integer SIMD computation•8 or 16-bit polynomial computation for single-bit coefficients•structured data load capabilities•dual issue with Cortex-A9 processor ARM or Thumb instructions•independent pipelines for VFPv3 and Advanced SIMD instructions•large, shared register file, addressable as:—thirty-two 32-bit S (single) registers—thirty-two 64-bit D (double) registers—sixteen 128-bit Q (quad) registers.See the ARM Architecture Reference Manual for details of the information that the MPEcan hold in the different register formats.The Cortex-A9 NEON MPE provides high-performance SIMD vector operations for:•unsigned and signed integers•single bit coefficient polynomials•single-precision floating-point values.The operations include:•addition and subtraction•multiplication with optional accumulation•maximum or minimum value driven lane selection operations•inverse square-root approximation•comprehensive data-structure load instructions, including register-bank-resident tablelookup.See the ARM Architecture Reference Manual for details of the Advanced SIMD instructions.NoteT he Advanced SIMD architecture extension, its associated implementations, and supportingsoftware, are commonly referred to as NEON™ technology.1.1.1VFPv3 architecture hardware supportThe Cortex-A9 NEON MPE hardware supports single and double-precision add, subtract,multiply, divide, multiply and accumulate, and square root operations as described in the ARMVFPv3 architecture. It provides conversions between 16-bit, 32-bit and 64-bit floating-pointformats and ARM integer word formats, with special operations to perform conversions inround-towards-zero mode for high-level language support.All instructions are available in both the ARM and Thumb instruction sets supported by the Cortex-A9 processor family.The Cortex-A9 NEON MPE provides an optimized solution in performance, power, and area for embedded and media intensive applications.ARMv7 deprecates the use of VFP vector mode. The Cortex-A9 NEON MPE hardware does not support VFP vector operations. In this manual, the term vector refers to Advanced SIMD integer, polynomial and single-precision vector operations. The Cortex-A9 NEON MPE provides high speed VFP operation without support code. However, if an application requires VFP vector operation, then it must use support code. See the ARM Architecture Reference Manual for information on VFP vector operation support.NoteT his manual gives information specific to the Cortex-A9 NEON MPE implementation of the ARM Advanced SIMD and VFPv3 extensions. See the ARM Architecture Reference Manual for full instruction set and usage details.1.2ApplicationsThe Cortex-A9 NEON MPE provides mixed-data type SIMD and high-performance scalarfloating-point computation suitable for a wide spectrum of applications such as:•personal digital assistants and smartphones for graphics, voice compression anddecompression, user interfaces, Java interpretation, and Just In Time (JIT) compilation •games machines for intensive three-dimensional graphics, digital audio and in-gamephysics effects such as gravity•printers and MultiFunction Peripheral (MFP) controllers for high-definition colorrendering•set-top boxes for high-end digital audio and digital video, and interactivethree-dimensional user interfaces•automotive applications for engine management, power train computation, and in-carentertainment and navigation.1.3Product revisionsThis section describes the differences in functionality between product revisions:r0p0 - r1p0 There are no functionality changes although you must use the Cortex-A9 revisionr1p0 design with revision r1p0 NEON MPE.r1p0 - r2p0 There are no functionality changes although you must use the Cortex-A9 revisionr2p0 design with this revision r2p0 NEON MPE.r2p0 - r2p1 There are no functionality changes although you must use the Cortex-A9 revisionr2p1 design with this revision r2p1 NEON MPE.r2p1 - r2p2 There are no functionality changes.r2p2 - r3p0 There are no functionality changes.r3p0 - r4p0 There are no functionality changes.Chapter2Programmers ModelThis chapter describes the Cortex-A9 NEON MPE programmers model. It contains the followingsections:•About this programmers model on page2-2•New Advanced SIMD and VFP features on page2-4•Supported formats on page2-5•Advanced SIMD and VFP register access on page2-6•Register summary on page2-10•Register descriptions on page2-11.2.1About this programmers modelThis section introduces the VFPv3 and Advanced SIMD implementation provided by theCortex-A9 NEON MPE. In addition it provides information on initializing the Cortex-A9NEON MPE ready for application code execution. These are described in:•Advanced SIMD and VFP feature identification registers•Enabling Advanced SIMD and floating-point support.In addition to features provided in previous combined Advanced SIMD and VFPimplementations, the Cortex-A9 NEON MPE provides:•half-precision, 16-bit, floating-point value conversion•support for emulation of VFPv3-D32 and VFPv3-D16.See the ARM Architecture Reference Manual for more information.2.1.1Advanced SIMD and VFP feature identification registersThe Cortex-A9 NEON MPE implements the ARMv7 Advanced SIMD and VFP extensions.Software can identify these extensions and the features they provide, using the featureidentification registers. The extensions are in the coprocessor space for coprocessors CP10 andCP11. You can access the registers using the VMRS and VMSR instructions, for example:VMRS <Rd>, FPSID ; Read Floating-Point System ID RegisterVMRS <Rd>, MVFR1 ; Read Media and VFP Feature Register 1VMSR FPSCR, <Rt> ; Write Floating-Point System Control RegisterSee Advanced SIMD and VFP register access on page2-6 for a description of the registers.In addition there are coprocessor access control registers. See Non-secure Access ControlRegister on page2-7 and Coprocessor Access Control Register on page2-6.2.1.2Enabling Advanced SIMD and floating-point supportFrom reset, both the Advanced SIMD and VFP extensions are disabled. Any attempt to executeeither a NEON or VFP instruction results in an Undefined Instruction exception being taken. Toenable software to access Advanced SIMD and VFP features ensure that:•Access to CP10 and CP11 is enabled for the appropriate privilege level. See CoprocessorAccess Control Register on page2-6.•If Non-secure access to the Advanced SIMD features or VFP features is required, theaccess flags for CP10 and CP11 in the NSACR must be set to 1. See Non-secure AccessControl Register on page2-7.In addition, software must set the FPEXC.EN bit to 1 to enable most Advanced SIMD and VFPoperations. See Floating-Point Exception Register on page2-13.When Advanced SIMD and VFP operation is disabled because FPEXC.EN is 0, all AdvancedSIMD and VFP instructions are treated as undefined instructions except for execution of thefollowing in privileged modes:• a VMSR to the FPEXC or FPSID register• a VMRS from the FPEXC, FPSID, MVFR0 or MVFR1 registers.Example2-1 on page2-3 shows how to enable the Advanced SIMD and VFP in ARM UnifiedAssembly Language (UAL). This code must be executed in privileged mode.Example2-1 Enabling Advanced SIMD and VFP MRC p15,0,r0,c1,c0,2 ; Read CPACR into r0ORR r0,r0,#(3<<20) ; OR in User and Privileged access for CP10ORR r0,r0,#(3<<22) ; OR in User and Privileged access for CP11BIC r0, r0, #(3<<30) ; Clear ASEDIS/D32DIS if setMCR p15,0,r0,c1,c0,2 ; Store new access permissions into CPACRISB ; Ensure side-effect of CPACR is visibleMOV r0,#(1<<30) ; Create value with FPEXC (bit 30) set in r0VMSR FPEXC,r0 ; Enable VFP and SIMD extensionsAt this point the Cortex-A9 processor can execute Advanced SIMD and VFP instructions.NoteO peration is U NPREDICTABLE if you configure the Coprocessor Access Control Register (CPACR) so that CP10 and CP11 do not have identical access permissions.2.2New Advanced SIMD and VFP featuresThe Cortex-A9 NEON MPE implements the following new features in the ARMv7 AdvancedSIMD and VFP architectures:•Half-precision floating-point value conversion•Independent Advanced SIMD and VFP disable•Dynamically configurable VFP register bank size.Full details of the new instructions and control register fields are in the ARM ArchitectureReference Manual.2.2.1Half-precision floating-point value conversionThe half-precision floating-point value conversion adds support for both IEEE and the commongraphic representation, referred to as alternative-half-precision representation, of 16-bitfloating-point values. This provides a smaller memory footprint for applications requiring largenumbers of lower-precision floating-point values to be stored, while avoiding the overhead ofconversion in software.Additional VFP and Advanced SIMD instructions enable conversion of both individual valuesand vectors of values to and from single-precision floating-point representation. These valuescan then be processed using the rest of the VFP and Advanced SIMD instructions.See Floating-Point Status and Control Register on page2-11 for how to select IEEE oralternative half-precision modes.2.2.2Independent Advanced SIMD and VFP disableThe independent Advanced SIMD disables permit Cortex-A9 implementations with Cortex-A9NEON MPE to behave as though only the VFP extension were present. This lets you enableoptimal operating-system task scheduling between Cortex-A9 multi-processor clusterscontaining both Cortex-A9 NEON MPE and floating-point only units.The Cortex-A9 processor provides support for preventing use of this feature throughNon-secure access. See Non-secure Access Control Register on page2-7 and CoprocessorAccess Control Register on page2-6.2.2.3Dynamically configurable VFP register bank sizeThe dynamically configurable VFP register bank size provides additional support for bothVFPv3-D16 and VFPv3-D32 mixed multiprocessor clusters. Cortex-A9 NEON MPEimplements thirty-two 64-bit double-precision registers. VFP-only implementations are onlyrequired to support sixteen double-precision registers. This register bank disable control enablesemulation of a 16-entry double-precision register file, providing both enhanced compatibilityand more flexible task scheduling.Additional control is provided in the Non-Secure Access Control Register. See Non-secureAccess Control Register on page2-7 and Coprocessor Access Control Register on page2-6.2.3Supported formatsTable2-1 shows the formats supported for each of the Advanced SIMD and VFPv3 instructionsets implemented by the Cortex-A9 NEON MPE. All signed integers are two's complementrepresentations.Table2-1 Supported number formatsFormat Advanced SIMD VFPv38-bit signed/unsigned integer Yes No16-bit signed/unsigned integer Yes No32-bit signed/unsigned integer Yes Yes a64-bit signed/unsigned integer Yes No16-bit half-precision floating-point Yes a Yes a32-bit single-precision floating-point Yes Yes64-bit double-precision floating-point No Yes8-bit polynomials Yes No16-bit polynomials Yes Noa.For conversion purposes only.2.4Advanced SIMD and VFP register accessTable2-2 shows the system control coprocessor registers, accessed through CP15, thatdetermine access to Advanced SIMD and VFP registers, where:•CRn is the register number within CP15•Op1 is the Opcode_1 value for the register•CRm is the operational register•Op2 is the Opcode_2 value for the register.Table2-2 Coprocessor Access Control registersCRn Op1CRm Op2Name Descriptionc10c02CPACR See Coprocessor Access Control Registerc10c12NSACR See Non-secure Access Control Register on page2-72.4.1Coprocessor Access Control RegisterThe CPACR Register sets access rights for the coprocessors CP10 and CP11, that enable theCortex-A9 NEON MPE functionality. This register also enables software to determine if aparticular coprocessor exists in the system.The CPACR Register is:• a read/write register common to Secure and Non-secure states•accessible in privileged modes only•has a reset value of 0.Figure2-1 shows the CPACR Register bit assignments.Figure2-1 CPACR Register bit assignments Table2-3 shows the CPACR Register bit assignments.Table2-3 Coprocessor Access Control Register bit assignments Bits Field Function[31]ASEDIS Disable Advanced SIMD extension functionality:0 No instructions are disabled.1 Disables all instruction encodings identified in the ARM Architecture Reference Manual asbeing part of the Advanced SIMD extensions but that are not VFPv3 instructions.[30]D32DIS Disable use of D16-D31 of the VFP register file:0 No instructions are disabled.1 Disables all instruction encodings identified in the ARM Architecture Reference Manual asbeing VFPv3 instructions if they access any of registers D16-D31.[29:24]-See the Cortex-A9 Technical Reference Manual.Table2-3 Coprocessor Access Control Register bit assignments (continued) Bits Field Function[23:22]CP11Defines access permissions for the coprocessor. Access denied is the reset condition and is the behavior for nonexistent coprocessors.b00Access denied. Attempted access generates an Undefined Instruction exception.b01Privileged mode access only.b10Reserved.b11Privileged and User mode access.[21:20]CP10Defines access permissions for the coprocessor. Access denied is the reset condition and is the behavior for nonexistent coprocessors.b00Access denied. Attempted access generates an Undefined Instruction exception.b01Privileged mode access only.b10Reserved.b11Privileged and User mode access.[19:0]-See the Cortex-A9 Technical Reference Manual.Access to coprocessors in the Non-secure state depends on the permissions set in the Non-secureAccess Control Register.Attempts to read or write the CPACR Register access bits depend on the corresponding bit foreach coprocessor in Non-secure Access Control Register. Table2-4 shows the results ofattempted access to coprocessor access bits for each mode.Table2-4 Results of access to the CRACR Register NSACR[11:10]Secure privileged Non-secure privileged Secure or Non-secure Userb00R/W RAZ/WI Access prohibited ab01R/W R/W Access prohibited aer privilege access generates an Undefined Instruction exception.To access the CPACR Register, read or write CP15 with:MRC p15, 0,<Rd>, c1, c0, 2 ; Read Coprocessor Access Control RegisterMCR p15, 0,<Rd>, c1, c0, 2 ; Write Coprocessor Access Control RegisterWhen the CPACR is updated, the change to the register is guaranteed to be visible only after thenext Instruction Synchronization Barrier (ISB) instruction. When this register is updated,software must ensure that no instruction that depends on the new or old register values is issuedbefore the ISB instruction.Normally, software uses a read, modify, write sequence to update the CPACR, to avoidunwanted changes to the access settings for other coprocessors.NoteY ou must enable CP10 and CP11 in the CPACR Register before accessing any Advanced SIMDor VFP system registers.2.4.2Non-secure Access Control RegisterThe NSACR Register defines the Non-secure access rights for the Cortex-A9 NEON MPE andother system functionality.The NSACR Register is:• a read/write register in Secure state• a read-only register in Non-secure state•only accessible in privileged modes.Figure2-2 shows the bit assignments of the NSACR Register relevant to the Cortex-A9 MPE.See the Cortex-A9 Technical Reference Manual for details of other fields in this register.Figure2-2 NSACR Register bit assignments Table2-5 shows the NSACR Register bit assignments.Table2-5 NSACR Register bit assignments Bits Field Function[31:16]-See the Cortex-A9 Technical Reference Manual.[15]NSASEDIS Disable Non-secure Advanced SIMD extension functionality:0 Full access provided to CPACR.ASEDIS.1 The CPACR.ASEDIS bit when executing in Non-secure state has a fixed value of 1 andwrites to it are ignored.[14]NSD32DIS Disable Non-secure use of D16-D31 of the VFP register file:0 Full access provided to CPACR.D32DIS.1 The CPACR.D32DIS bit when executing in Non-secure state has a fixed value of 1 andwrites to it are ignored.[13:12]-See the Cortex-A9 Technical Reference Manual.[11]CP11Permission to access coprocessor 11:0 Secure access only. This is the reset value.1 Secure or Non-secure access.[10]CP10Permission to access coprocessor 10:0 Secure access only. This is the reset value.1 Secure or Non-secure access.[9:0]-See the Cortex-A9 Technical Reference Manual.To access the NSACR Register, read or write CP15 with:MRC p15, 0,<Rd>, c1, c1, 2 ; Read Non-secure Access Control Register dataMCR p15, 0,<Rd>, c1, c1, 2 ; Write Non-secure Access Control Register dataTable2-6 on page2-9 shows the results of attempted access for each mode.。

合泰HT66F002_HT66F0025_HT66F003_HT66F004

特性 .................................................................................................................................6 CPU 特性 ............................................................................................................................... 6 周边特性 ................................................................................................................................ 6

概述 .................................................................................................................................7 选型表 .............................................................................................................................7 方框图 .............................................................................................................................8 引脚图 .............................................................................................................................8 引脚说明 .......................................................................................................................10 极限参数 .......................................................................................................................16 直流电气特性 ...............................................................................................................16 交流电气特性 ...............................................................................................................18 ADC 电气特性..............................................................................................................19 运算放大器电气特性 ...................................................................................................19 LVR 电气特性 ..............................................................................................................20 LCD 电气特性 – HT66F004........................................................................................20 上电复位特性 ...............................................................................................................20 系统结构 .......................................................................................................................2/D 型 8-Bit Flash 单片机

a-tabs用法

a-tabs是一种常见的标签页组件,通常用于在网页上展示多个内容区域,并允许用户通过点击标签来切换不同的内容区域。

以下是a-tabs的基本用法:1. 引入a-tabs组件:首先,您需要在页面中引入a-tabs组件的脚本文件。

通常可以通过在HTML中添加相关的`<script>`标签来完成。

2. 创建标签页容器:使用`<a-tabs>`标签创建一个标签页的容器。

在`<a-tabs>`标签内,您可以添加多个`<a-tab>`标签来表示不同的标签页。

3. 定义标签页内容:每个`<a-tab>`标签用于定义一个标签页的内容。

您可以在`<a-tab>`标签内放置需要展示的内容,例如文本、图片、链接等。

4. 添加标签页切换事件:您可以使用`@change`事件来监听标签页切换的行为。

当用户点击不同的标签时,`@change`事件将被触发,并传递当前激活的标签的索引值或标识符。

以下是一个简单的示例代码,展示了如何使用a-tabs组件:```html<template><div><a-tabs @change="handleChange"><a-tab title="Tab 1">Content 1</a-tab><a-tab title="Tab 2">Content 2</a-tab><a-tab title="Tab 3">Content 3</a-tab></a-tabs></div></template><script>export default {methods: {handleChange(index) {console.log('Tab changed to:', index);}}}</script>```在上面的示例中,我们创建了一个包含三个标签页的a-tabs组件。

IEC-61162-420

Commission Electrotechnique Internationale International Electrotechnical Commission

PRICE CODE

XD

For price, see current cata001(E)

CONTENTS

FOREWORD...........................................................................................................................6 INTRODUCTION .....................................................................................................................8 1 2 3 Scope and object ..............................................................................................................9 Normative references...................................................................................................... 10 Definitions ...............................................................................................................

vue给子组件传递方法

vue给子组件传递方法为了在Vue中给子组件传递方法,有几种不同的方法可以使用。

下面是一些参考内容,可以帮助你在Vue中实现这个功能。

一、通过Props属性传递方法:1. 在父组件中定义一个方法,将其赋值给一个props属性。

```javascript<template><div><ChildComponent :parentMethod="myMethod"></ChildCompone nt></div></template><script>export default {methods: {myMethod() {// 这里编写需要传递给子组件的方法逻辑代码}}}</script>```2. 在子组件中通过props属性接收父组件传递的方法,并将其绑定到需要调用该方法的地方。

```javascript<template><div><button @click="parentMethod">点击触发父组件的方法</button></div></template><script>export default {props: {parentMethod: {type: Function, // 指定props属性的类型为函数required: true // 指定该props属性是必需的}}}</script>```二、使用事件广播与监听:1. 在父组件中,通过$emit方法触发一个自定义事件,并传递方法参数。

```javascript<template><div><ChildComponent></ChildComponent></div></template><script>export default {methods: {myMethod() {this.$emit('childMethod')}}}</script>```2. 在子组件中,使用$on方法监听父组件触发的自定义事件,并执行相应的方法。

ABAQUS调用FORTRAN程序

ABAQUS调用FORTRAN程序第一种方法:1. 建立工作目录/ ]"2. 将ABAQUS安装目录\6.4-pr11\site下的aba_param_dp.inc 或aba_param_sp.inc拷贝到工作目录,并改名为aba_param.inc;3. 将编译的fortran程序拷贝到工作目录;4. 将.obj文件拷贝到工作目录;5. 建立好输入文件.inp;6. 运行abaqus job=inp_name user=fortran name即可。

第二种方法:在Job模块里,创建工作,在Edit Job对话框中选择General选项卡,在User subroutine file 中点击Select按钮,从弹出对话框中选择你要调用的子程序文件(后缀为.for或.f)。

以下是网上摘录的资料,供参考:用户进行二次开发时,要在命令行窗口执行下面的命令:abaqus job=job_name user=sub_nameABAQUS会把用户的源程序编译成obj文件,然后临时生成一个静态库standardU.lib和动态库standardU.dll,还有其它一些临时文件,而它的主程序(如standard.exe和explicit.exe 等)则没有任何改变,由此看来ABAQUS是通过加载上述2个库文件来实现对用户程序的连接,而一旦运行结束则删除所有的临时文件。

这种运行机制与ANSYS、LS-DYNA、marc 等都不同。

这些生成的临时文件要到文件夹C:\Documents and Settings\Administrator\Local Settings\Temp\中才能找到,这也是6楼所说的藏了一些工作吧,大家不妨试一下。

1子程序格式(程序后缀是.f; .f90; .for;.obj??)答:我试过,.for格是应该是不可以的,至少6.2和6.3版本应该是不行,其他的没用过,没有发言权。

在Abaqus中,运行abaqus j=jobname user=username时,默认的用户子程序后缀名是.for (.f,.f90应该都不行的,手册上也有讲过),只有在username.for文件没有找到的情况下,才会去搜索username.obj,如果两者都没有,就会报错误信息。

铼钠克系统的编程格式

铼钠克系统的编程格式1. 介绍铼钠克系统是一种先进的编程框架,用于快速开发高效、可靠且安全的软件应用。

该系统的编程格式是一种约定俗成的规范,用于指导开发人员在铼钠克系统中进行编程。

本文将详细介绍铼钠克系统的编程格式,包括命名约定、代码结构、注释规范等内容。

2. 命名约定在铼钠克系统中,命名约定是非常重要的一部分。

良好的命名约定可以提高代码的可读性和可维护性。

以下是铼钠克系统的命名约定:•类名采用大驼峰式命名法(CamelCase),例如MyClass。

•方法名和变量名采用小驼峰式命名法(camelCase),例如myMethod。

•常量名全大写,使用下划线分隔单词,例如MAX_VALUE。

•包名采用全小写字母,使用点号分隔单词,例如com.example.myapp。

3. 代码结构在铼钠克系统中,代码结构的布局要合理、清晰。

下面是一个常见的代码结构示例:src/|-- main/| |-- java/| | |-- com/| | |-- example/| | |-- myapp/| | |-- model/| | |-- service/| | |-- controller/| | |-- utils/|-- test/| |-- java/| | |-- com/| | |-- example/| | |-- myapp/| | |-- model/| | |-- service/| | |-- controller/| | |-- utils/|-- resources/| |-- application.properties| |-- log4j.properties|-- pom.xml•src/main/java目录下存放项目的主要源代码。

•src/test/java目录下存放项目的测试代码。

•src/main/resources目录下存放项目的配置文件。

•pom.xml是Maven项目的配置文件。

TMS320F206设计中应注意的几个问题

TMS320F206设计中应注意的几个问题摘要:TMS320F206是TI公司TMS320C2XX系列芯片中具有代表性的一种,在介绍其特点、结构与性能的基础上,重点阐述了TMS320F206在软件及硬件设计中应注意的几个问题,给出了作者的一些实际经验。

关键词:DSP TMS320F206 软件设计硬件设计数字化已成为电子、通信和信息技术的发展趋势与潮流。

在这种趋势与潮流的推动下,数字信号处理的理论与实现手段获得了快速的发展,已成为当代发展最快的学科之一。

而DSP芯片作为数字信号处理,尤其是实时数字信号处理的主要方法和手段,自20 世纪70年代末、80年代初诞生以来,无论在性能上还是在价格上,都取得了突破性的迅猛发展。

从定点到浮点直到并行处理芯片,DSP 芯片的功能越来越强、速度越来越快(例如TI公司的并行处理芯片C6000系列的速度达到了2400MIPS的高指标);而且,DSP芯片的价格越来越低,开发与设计手段越来越多样化、越来越容易。

越来越高的性能价格比、日渐完善的开发方式使DSP的应用范围越来越大,已经广泛地应用于通信、雷达、声纳、遥感、生物医学、机器人、控制、精密机械、语音和图像处理等领域。

可以毫不夸张地说,以DSP芯片为基础的数字信号处理技术已成为当代电子、通信和信息处理技术不可或缺的重要手段。

从全球范围来看,生产DSP芯片的厂家主要有美国的TI公司、AD公司、Motorola 公司以及Lucent公司等。

其中TI公司以其卓越的产品性能、多层镒的产品系列、良好的性能价格比以及较好的售后服务,使其TMS320系列DSP芯片占据了接近一半的国际市场份额。

从定点、浮点到并行,已形成了一个较为完整的产品系列,因而获得了最广泛的应用。

TMS320系列产品大致是沿着下面三个方向在不断发展的。

定点DSP:C1X→C2X→C2XX→C5X→C54X→…;浮点DSP:C3X→C4X→…;内含多处理器的DSP:C8X→C6X…;TI公司的TMS320C2XX系列芯片是采用静态CMOS集成电路工艺制造的,其结构以 C5X为基础。

模板函数(templatefunction)出现编译链接错误(linkerror)之解析

模板函数(templatefunction)出现编译链接错误(linkerror)之解析总的结论:将template function 或者 template class的完整定义直接放在.h⽂件中,然后加到要使⽤这些template function的.cpp⽂件中。

1. 现象描述类似于参考⽂献[1],当我们以如下⽅式使⽤模板函数时,会出现模板函数声明、定义分离带来的链接错误:1// File "foo.h"2 template<typename T>3extern void foo();1// File "foo.cpp"2 #include <iostream>3 #include "foo.h"45 template<typename T>6void foo()7 {8 std::cout << "Here I am!\n";9 }使⽤时:1// File "main.cpp"2 #include "foo.h"34int main()5 {6 foo<int>();7 ...8 }在如此使⽤时,会报出link error.通常来说有两种解决办法:(1)将template function 或者 template class的完整定义直接放在.h⽂件中,然后加到要使⽤这些template function的.cpp⽂件中(当然,此法的确定是,对某些编译器⽽⾔,会造成最后⽣成的.exe⽂件⽐较⼤);(2)在.cpp⽂件中定义模板函数的时候,就将模板函数先实例化,例如:1// File "foo.cpp"2 #include <iostream>3 #include "foo.h"45 template<typename T> void foo()6 {7 std::cout << "Here I am!\n";8 }910 template void foo<int>();或者:把.cpp⽂件当成头⽂件⼀样加⼊到需要使⽤模板函数的.cpp⽂件中:1// File "main.cpp"2 #include "foo.cpp"//有可能会有点令⼈迷惑---这是本⽅法的缺点3 template void foo<int>();45int main()6 {7 foo<int>();8 ...9 }2.原理说明 参考⽂献[3]中已经有很好的说明,此处仅转载之。