加减法指令的实现

算术运算指令

2. 减法指令

(1) 不考虑借位的减法指令SUB 格式: SUB dest, src 操作: dest←(dest)-(src)

注:1.源和目的操作数不能同时为存储器操作数 2.不能把段寄存器作为操作数

指令例子:

SUB AL,60H SUB [BX+20H],DX SUB AX,CX

14

(2) 考虑借位的减法指令SBB SBB指令主要用于多字节的减法。 格式: SBB dest, src 操作: dest←(dest)-(src)-(CF)

思考: 程序的结果? (AL、BL、CL中数据的大小顺序22 )

3. 乘法指令

进行乘法时: 8位 8位→ 16位乘积 (即 AL mem8/reg8 → AX) 16位 16位→ 32位乘积

(即 AX mem16/reg16 → DX AX) (1) 无符号数的乘法指令MUL mem/reg

9

BUFFER1

ACH F8H 56H 2CH

BUFFER2

BEH 47H 9EH 30H

被 加 数

数 据 段

加 数

...

多字节加法示意图

10

程序段如下:

MOV CX,4 ;置循环次数

MOV SI,0 ;置SI初值为零

CLC

;清进位标志CF

LL: MOV AL,BUFFER2[SI]

ADC BUFFER1[SI],AL ;带进位加

8

ADC指令主要用于多字节加法运算中

例:有两个4字节的无符号数相加: 2C 56 F8 AC + 30 9E 47 BE = ? 设被加数、加数分别存放在BUFFER1及

BUFFER2开始的两个存储区内,结果放回 BUFFER1存储区,如下页图所示。

算术运算类指令

2009年6月2日星期二

15

2.双寄存器符号扩展指令CWD/CDQ/CQO

指令格式:CWD

CDQ

CQO 功能:CWD功能为将AX寄存器的内容符号扩展到DX中;

CDQ指令的功能为将EAX寄存器的内容符号扩展到EDX中; CQO指令的功能为将RAX寄存器的内容符号扩展到RDX中,只 能在64位方式下使用。 它们都不影响标志位。 一般来说符号扩展指令大都与除法指令相结合,为达到被除数的位数要 求而扩展。 【例3.29】 求0ABCH÷0200H(带符号数相除) 由于除数为字,则必须将原来的被除数进行符号扩展后才能相除。

2009年6月2日星期二

10

AL ╳ src (8位源操作数)

AX

(16位乘积)

字节乘法

AX

╳

src (16位源操作数)

DX AX 字乘法

(32位乘积)

╳

src (32位源操作数)

EDX EAX (64位乘积)

RAX

╳

src (64位源操作数)

RDX RAX (128位乘积)

32位乘法

64位乘法

【例】 设AX=65A0H,BX=B79EH,指令ADD BX,AX的执行情况如下:

0110010110100000 +)1011011110011110

10001110100111110

结果非零:ZF=0

最高位有进位:CF=1 最高位为0:SF=0

OF=最高位进位1⊕次高位进位1,则OF=0

无进位: AF=0 低8位为偶数个1:PF=0

状态标志位

OF SF ZF AF PF CF

Y **** Y Y **** Y Y **** Y Y **** Y

以内加减法的秘诀

以内加减法的秘诀儿童数学手指块算 20以内的加减法Ku620以内加减法的秘诀,【学前班的宝宝】,怎样能算得快,有简单。

20以内不进位加减法:1、11-20的数可以和孩子玩猜数游戏。

用3种方式描述数:1)个位是2,十位是1 。

2)1个十,5个一。

3)比11大,比13小。

用这些方式描述数,让孩子猜,或者反过来孩子描述大人猜,直到熟练。

2、用计数器拨数。

家长说数,孩子拨数。

边拨边说数的组成。

如12是由1个十和2个一组成的。

3、熟练背诵20以内的进位加减法口诀20以内进位加法口诀九二11 八三11 七四11 六五11九三12 八四12 七五12 两个六12九四13 八五13 七六13九五14 八六14 两个七14九六15 八七15九七16 两个八16九八17两个九18(不用九九18,而用两个九18,同乘法口诀统一起来)注:1、前面两个汉字是加数,后面阿拉伯数字表示和,这样可以分清哪是加数,哪是和;2、加法口诀是大数在前小数在后〈如九三12〉乘法口诀是小数在前大数在后〈如三九二十七〉;3、口算达到熟练的程度,不要让孩子数指头,或者固定一个加数往上数数,这样孩子习惯了很不好改。

10以内的加法口诀和20以内的进位加法口诀就是背诵,背诵,背诵。

熟能生巧再配合一些规律的讲解,这样孩子的计算能力才能提高。

4、背诵时间可以随机,不一定非要拿出大块时间来背,每天接送孩子上学放学的时间,路上就可以背。

5、每天一定要坚持出口算练习,一天30道题。

20以内退位减法20以内退位减法与20以内进位加法相反,就是把20以内退位减法转化为10以内加法。

口诀是:“减九加一,减八加二,减七加三,减六加四,减五加五。

”如何用口诀,以“减九加一”为例,“减九加一”是指一个数减去9,将这个数的个位加上1所得的结果就是它们的差。

例如:17-9=()就拿17的个位7加上1结果是8,即17-9=8,13-9=()就拿13的个位3加上1结果是4,即13-9=4“减八加二,减七加三,减六加四,减五加五”与“减九加一”的方法一样。

2_第3章 8086指令系统_加减运算指令比较指令52

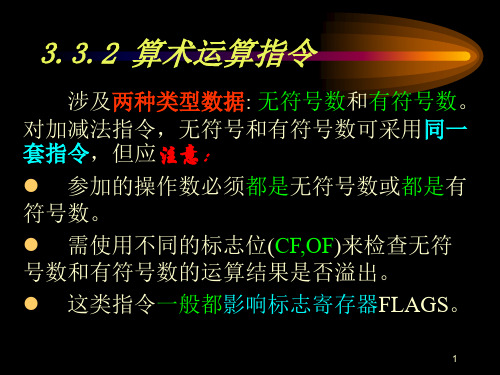

3.4.2 算术运算指令

算术运算指令涉及两种类型数据,即无符号数和有符号数 对加法指令和减法指令而言,无符号和有符号数可采用同

一套指令,其先决条件有两个: 一是参加的操作数必须同为无符号数或同为有符号数 二是要采用不同标志位来检查无符号数和有符号数的 运算结果是否溢出

而乘除运算指令则需要区分无符号数和有符号数

11 11

ADC指令的使用价值

主要用于由于数据较大(多字节),需要多次运算的加法 运算中。 例:有两个4字节的无符号数相加:

2D568F8CH+3C9E489BH=? 设 被加数存放在BUF1开始的存储区内

加数存放在BUF2开始的存储区内 要求和放回BUF1存储区 假设CPU进行8位的加法运算,为此将进行4次加法运算

.386

……

MOVZX AX, A

MOVZX BX, B

ADD

AX, BX

MOVZX BX, C

ADD

AX, BX

MOV

SUM, AX

;取第一个数,扩展0传送 ;取第二个数 ;加第二个数 ;取第三个数 ;加第三个数 ;保存三个数的和

20 20

[例] P,Q,R均为8位有符号数,求它们的和,送入TOTAL

这个问题的另一种方法:

MOV AL, A

;取第一个数

MOV AH, 0

;高8位清零,准备存放和的高8位

ADD AL, B

;加第二个数

ADC AH, 0

;如果有进位,存入AH

ADD AL, C

;加第三个数

ADC AH, 0

;如果有进位,加入AH

MOV SUM, AX ;保存三个数的和

19 19

这个问题的第三种方法:

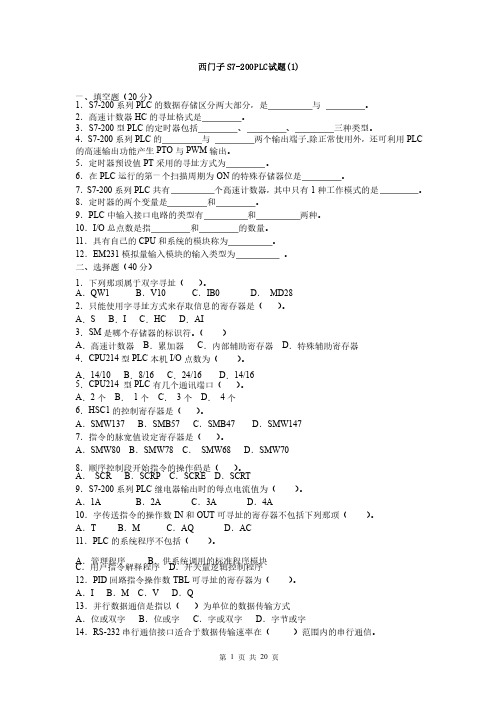

西门子S7-200PLC试题及答案

西门子S7-200PLC试题(1)分)一、填空题(20分)1.S7-200系列PLC的数据存储区分两大部分,是的数据存储区分两大部分,是 与。

2.高速计数器HC的寻址格式是的寻址格式是 。

3.S7-200型PLC的定时器包括三种类型。

的定时器包括 、、三种类型。

4.S7-200系列PLC的与两个输出端子,除正常使用外,除正常使用外,还可利用还可利用PLC输出。

的高速输出功能产生PTO与PWM输出。

5.定时器预设值PT采用的寻址方式为采用的寻址方式为 。

6.在PLC运行的第一个扫描周期为ON的特殊存储器位是的特殊存储器位是 。

7.S7-200系列PLC共有种工作模式的是 。

共有 个高速计数器,其中只有1种工作模式的是8.定时器的两个变量是.定时器的两个变量是 和。

9.PLC中输入接口电路的类型有两种。

中输入接口电路的类型有 和两种。

10.I/O总点数是指的数量。

总点数是指 和的数量。

11.具有自己的CPU和系统的模块称为和系统的模块称为 。

12.EM231模拟量输入模块的输入类型为模拟量输入模块的输入类型为 。

分)二、选择题(40分)1.下列那项属于双字寻址(.下列那项属于双字寻址( )。

A.QW1 B.V10 C.IB0 D.MD28 2.只能使用字寻址方式来存取信息的寄存器是(.只能使用字寻址方式来存取信息的寄存器是( )。

A.S B.I C.HC D.AI 3.SM是哪个存储器的标识符。

()A.高速计数器.内部辅助寄存器 D.特殊辅助寄存器.特殊辅助寄存器.累加器 C.内部辅助寄存器.高速计数器 B.累加器4.CPU214型PLC本机I/O点数为(点数为( )。

A.14/10 B.8/16 C.24/16 D.14/16 5.CPU214 型PLC有几个通讯端口(有几个通讯端口( )。

A.2个B.1个C.3个D.4个6.HSC1的控制寄存器是(的控制寄存器是( )。

A.SMW137 B.SMB57 C.SMB47 D.SMW147 7.指令的脉宽值设定寄存器是(.指令的脉宽值设定寄存器是( )。

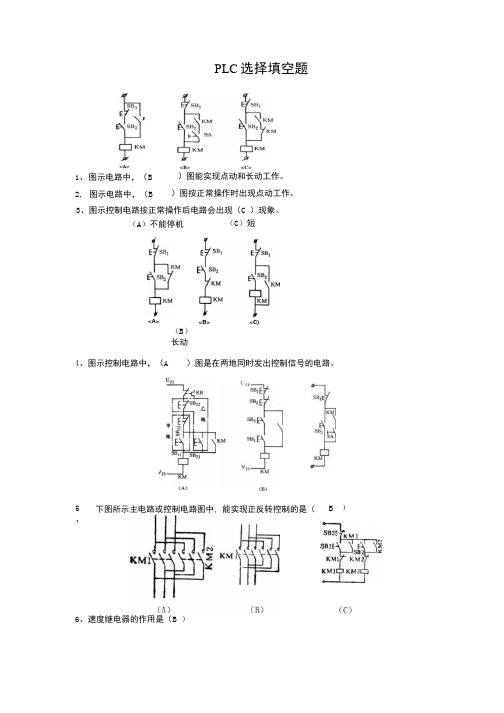

plc选择填空题.docx

PLC 选择填空题)图能实现点动和长动工作。

)图按正常操作时出现点动工作。

3、图示控制电路按正常操作后电路会出现(C )现象。

(A )不能停机(B )长动6、速度继电器的作用是(B )<A><B><C>4、图示控制电路中,(A)图是在两地同时发出控制信号的电路。

5、 能实现正反转控制的是( 下图所示主电路或控制电路图中, B )1、 图示电路中,(B 2, 图示电路中,(B<A>(C )短路<B> <C)C.限制速度D.用于能耗制动7、X6132卧式万能铳床主轴为满足顺铳和逆铳工艺要求,需正反转控制,采用的方法是( A )A.操作前,通过转换开关进行方向预选。

B.通过正反接触器改变相序控制电动机正反转。

C.通过机械方法改变传动链。

D.其他方法。

8、在外加电压一样的情况下,不能用交流励磁的接触器线圈替换直流励磁的接触器,是因为(C ),否则将烧毁线圈。

A交流线圈阻抗过大B交流线圈铁心发热厉害C交流线圈匝数小,电阻小9、下列低压电器不能起短路保护作用的低压电器有(C )A.断路器B.熔断器C接近开关10、直流接触器一般采用(B )灭弧装置A.电动力灭弧B.磁吹灭弧C.窄缝灭弧11、额定功率为5.5KW、电压380V、电流为11. 6A,起动电流为7倍额定电流的二相异步电动机直接起动,熔断器短路保护,熔体额定电流选择最合理的是(A )A. 20AB. 40AC. 80A12、PLC应用最广泛的编程语言是(A )A.梯形图B.语句表C.高级语言13、世界上第一台PC机是山(B )发明的。

A日本B美国C德国14、下列那项属于双字寻址(D )。

A. QW1B. V10C. IBOD. MD2815、只能使用字寻址方式来存取信息的寄存器是(D )。

A. SB. IC. HCD. AI16、SM是哪个存储器的标识符。

(D )A.高速计数器B.累加器C.内部辅助寄存器D.特殊辅助寄存器17、CPU214 型PLC 本机I/O 点数为(A )。

二算术逻辑运算指令

三、逻辑运算指令

⑵移位指令

• 累加器A循环左移指令: • RL A ; • 累加器A连同进位位循环左移指令: • RLC A ; • 累加器A循环右移指令: • RR A ; • 累加器A连同进位位循环右移指令 • RRC A ;

三、逻辑运算指令

• 例3-18:若(A)=10111101B=BDH, Cy=0

• 注:执行结果只影响PSW的奇偶校验位P (以A为操 作数时 )

二、算术运算指令

3.乘、除法指令

• MUL AB ; (A)←[(A)×(B)]7-0

•

(B)←[(A)×(B)]15-8

• 如果积大于255(FFH),则溢出标志OV置1,否则清0。进

位标志位Cy总为0。

二、算术运算指令

• 例3-17:设(A)=50H(80),(B) =0AH(160) 执行指令:MUL AB;

• 执行“ RLC A”的结果为 • (A)=01111010B=7AH,Cy=1 • A的内容扩大2倍

三、逻辑运算指令

2 .双操作数的逻辑运算指令

• ⑴逻辑“与”指令

• ANL A,Rn ;(A) ←(A)∧(Rn) • ANL A,direct ;(A) ←(A)∧(direct) • ANL A,@Ri ;(A) ←(A)∧((Ri)) • ANL A,#data ;(A) ←(A)∧data • ANL direct, A ;(direct)←(direct)∧(A) ANL direct,#data;(direct)←(direct)∧data

• 本指令不能简单的把累加器A中的16进制数变换成 BCD码

二、算术运算指令

• 例3-13:设累加器A内容为压缩BCD码56 (即01010110B),寄存器R3的内容为 压缩BCD码67(即01100111B),Cy内 容为1。执行下列的指令:

课件:第三章 计算机的算术运算加减法

G4 P4

G3 P3

S 16~S 13

S 12~S 9

G2 P2 S 8~S 5

G1 P1 S 4~S 1

BCLA

C12

BCLA

C8

BCLA

C4

BCLA

C0

加法器

加法器

加法器

加法器

A 16~A 13

A 12~A 9

B 16~B 13

B 12~B 9

A 8~A 5 B 8~B 5

A 4~A 1 B 4~B 1

再经过2ty后,才能产生第2、3、4小组内的C5~C7、C9~C11、 C13~C15。

以典型的四位ALU芯片(SN74181)为例介绍ALU的结 构及应用。

得[x+y]补=0.0110,x+y=+0.0110

[例2]X=-11001,Y=-00011,求X+Y=? 解:[x]补=1,00111,[y]补=1,11101

[x]补 = 1,00111 +)[y]补 = 1,11101 [x+y]补 =1 1,00100

丢掉

验算:

x=-11001=(-25)10 Y=(-3)10 X+Y=(-28)10 =(-11100)2

S 8~S 5

S 4~S 1

C16

4位C L A

C12

4位C L A

C8

4位C L A

C4

4位C L A

C0

加法器

加法器

加法器

加法器

A 1 6~A 1 3

A 1 2~A 9

B 1 6~B 1 3

B 1 2~B 9

A 8~A 5

B 8~B 5

A 4~A 1

微机原理与接口技术:加法减法运算指令

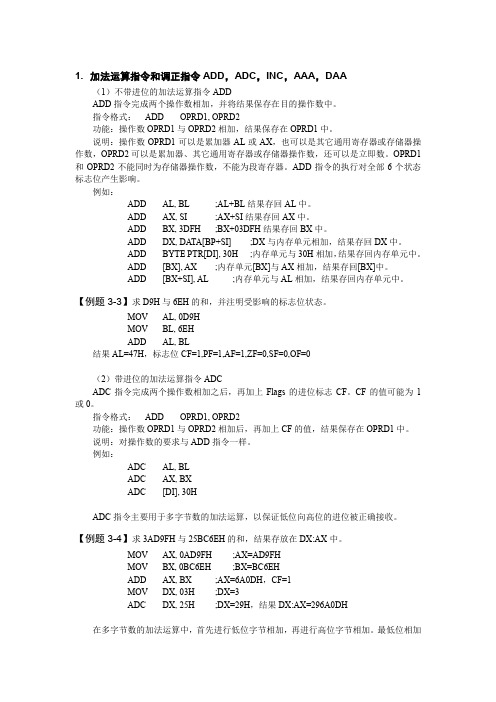

1. 加法运算指令和调正指令ADD,ADC,INC,AAA,DAA(1)不带进位的加法运算指令ADDADD指令完成两个操作数相加,并将结果保存在目的操作数中。

指令格式:ADD OPRD1, OPRD2功能:操作数OPRD1与OPRD2相加,结果保存在OPRD1中。

说明:操作数OPRD1可以是累加器AL或AX,也可以是其它通用寄存器或存储器操作数,OPRD2可以是累加器、其它通用寄存器或存储器操作数,还可以是立即数。

OPRD1和OPRD2不能同时为存储器操作数,不能为段寄存器。

ADD指令的执行对全部6个状态标志位产生影响。

例如:ADD AL, BL ;AL+BL结果存回AL中。

ADD AX, SI ;AX+SI结果存回AX中。

ADD BX, 3DFH ;BX+03DFH结果存回BX中。

ADD DX, DA TA[BP+SI] ;DX与内存单元相加,结果存回DX中。

ADD BYTE PTR[DI], 30H ;内存单元与30H相加,结果存回内存单元中。

ADD [BX], AX ;内存单元[BX]与AX相加,结果存回[BX]中。

ADD [BX+SI], AL ;内存单元与AL相加,结果存回内存单元中。

【例题3-3】求D9H与6EH的和,并注明受影响的标志位状态。

MOV AL, 0D9HMOV BL, 6EHADD AL, BL结果AL=47H,标志位CF=1,PF=1,AF=1,ZF=0,SF=0,OF=0(2)带进位的加法运算指令ADCADC指令完成两个操作数相加之后,再加上Flags的进位标志CF。

CF的值可能为1或0。

指令格式:ADD OPRD1, OPRD2功能:操作数OPRD1与OPRD2相加后,再加上CF的值,结果保存在OPRD1中。

说明:对操作数的要求与ADD指令一样。

例如:ADC AL, BLADC AX, BXADC [DI], 30HADC指令主要用于多字节数的加法运算,以保证低位向高位的进位被正确接收。

arm指令

一、加减法指令:1、MOV(move):数据传送指令2、MVN(move negative):数据取反传送指令3、ADD(add):加法4、ADC(add with carry):带进位加法5、SUB(subtract):减法6、RSB(reverse subtract):反向减法7、SBC(subtract with carry):带借位的减法SBC{<cond>}{S} <Rd>,<Rn>,<op2> ;Rd=Rn-op2-carry8、RSC(reverse subtract with carry):带借位的反向减法RSC{<cond>}{S} <Rd>,<Rn>,<op3> ;Rd= op3-Rn-!carry二、逻辑指令1、AND:逻辑与2、ORR(logical or):逻辑或3、EOR(exclusive or):逻辑异或4、BIC(bit clear):位清零5、CLZ(count leading zeros):位计数。

CLZ{<cond>} <Rd>,<Rm>;计算存储在Rm寄存器中各位为0的总个数。

三、乘法指令1、MUL(multiply):32位乘法2、MLA(multiply accumulate):32位乘加MLA{<cond>} {S} <Rd>,<Rn>,<op2>,<op3>;3、SMULL(signed multiplication long):64位有符号数乘法SMULL {<cond>}{S} <Rdl>,<Rdh>,<Rn>,<op2>;Rdh Rdl=Rn×op2,结果的高32位存入Rdh,低32位存入Rdl。

算术运算类指令

√ √ √ √ 累加器A中的内容与工作寄存 器Ri所指向地址单元中的内容 相加,结果存在A中

各标志位的形成方法: 如果位7有进位输出,则置位CY,否则清CY; 如果位3有进位输出,则置位AC,否则清AC; OV=CY7⊕CY6。 若累加器A中1的个数为奇数,则P=1,否则,P=0。

√ √ √ √ 累加器A中的内容减工作寄存器中 的内容再减借位位,结果存在A中

A←(A)-((Ri))-(CY)

√√

√ √ 累加器A中的内容减工作寄存器Ri 指向的地址单元中的内容再减借位 位,结果存在A中

在减法运算中

CY=1表示有借位,CY=0则无借位。 OV=1表明带符号数相减时,从一个正数减去一个负数结果为

√√

√

√

累加器A中的内容与立即数连同进位

位相加,结果存在A中

√√

√

√

累加器A中的内容与工作寄存器Rn中

的内容、连同进位位相加,结果存在

A中

√√

√

√

累加器A中的内容与工作寄存器Ri指

向的地址单元中的内容、连同进位位

相加,结果Байду номын сангаас在A中

3. 带借位减法指令(4条)

指令

功能

标志位

解释

PO A C VCY

SUBB A,direct

注意: DA A 只能用于加法运算

【例】:有两个BCD数36与45相加,结果应为BCD码81, 程序如下:

MOV A,#36H

ADD A,#45H

DA A

加法指令执行后得结果7BH;第三条指令对累加器A中的 结构进行十进制调整,低4位(为0BH)大于9,因此要加6, 最后得到调整的BCD码为81。

微机原理第02章(指令系统)2

加法指令:ADD, ADC和INC 减法指令:SUB, SBB, DEC, NEG和CMP 他们分别执行字或字节的加法和减法运算, 除 INC 和 DEC 不影响 CF 标志外,其他按定 义影响全部状态标志位 操作数组合:

运算指令助记符 reg, imm/reg/mem 运算指令助记符 mem, imm/reg

第2章:5. 求补指令NEG(negtive)

4.取补指令 格式:NEG OPRD (OPRAND ) 功能:OPRD取补 (取反加1) 相当0-操作数,所以算入减法; 且一般CF=1(0-肯定有借位), 只有OPRD=0时CF=0

第2章:例题2.9 求补运算

mov ax,0ff64h neg al ;AL=0-64H=9CH,AX=FF9CH ;OF=0, SF=1,ZF=0,PF=1,CF=1 sub al,9dh ;AL=9CH-9DH=FFH,AX=FFFFH ;OF=0,SF=1,ZF=0,PF=1,CF=1 neg ax ;AX=0-FFFFH=0001H ;OF=0,SF=0,ZF=0,PF=0,CF=1 dec al ;AL=01H-1=0,AX=0000H ;OF=0,SF=0,ZF=1,PF=1,CF=1 neg ax ;AX=0-0=0 ;OF=0,SF=0,ZF=1,PF=1,CF=0

第2章:例题2.10 符号扩展

mov al,64h

;AL=64H (机器数) ,表示10进制数100(真值)

cbw

;将符号0扩展,AX=0064H,仍然表示100

mov ax,0ff00h

;AX=FF00H,表示有符号10进制数-256

cwd

;将符号位“1”扩展,DX.AX=FFFFFF00H ;仍然表示-256

算术运算程序

;分母送AH ;商符号送B

den quot

ABS STH LD

AA@,n(即@undm分ue,mn1子)6×,×AA分H 母→→BB,;;,取分取分子母送符绝A号H对。值table

ABS A

;取分子绝对值

RPT #14 SUBC @den,A

;15次减法循环 完成除法

0.4 -00..88 -商0.5

*

example.asm

*

********************************************

.title “example.asm”

.mmregs

stack .usect “STACK”,10h ;为堆栈指定空间

.bss

a,4

;为变量分配9个字的空间

.bss

x,4

.bss

y,1

;16 384 ;512

;传送2个数据至分子、分母单元

2023年10月24日6时32分

2 除法运算

2. |被除数|>|除数|

例: 编写16384÷512的程序

LD MPYA ABS STH LD ABS RPT SUBC XC NEG STL

@den,16,A @num A A,@den @num,A A #15 @den,A 1,BLT A A,@quot

若ALU输出0,则(ALU输出)<<1+1→src 否则(src)<<1→src

重复指令: RPT #K

功能:RC=#K,重复执行下条指令K+1次。

2023年10月24日6时32分

2 除法运算

1. |被除数|<|除数|

例: 编写0.4÷(-0.8)的程序

大班数学20加减法教案

大班数学20加减法教案【篇一:20以内进位加法教案】活动名称:20以内的进位加法活动目标:1、利用“凑十法”学习20以内进位加法2、让幼儿在动手操作过程中理解“凑十法”3、培养幼儿学习数学的兴趣活动准备:活动过程:魔块、数位图每人各一份(一)开始部分:复习10的组成方法:师生对答的形式说组成;如:教师提问:小朋友我问你,1和9组成几?幼儿回答:老师我告诉您1和9组成10。

2和8组成几……(二)操作部分:利用学具学习20以内进位加法1、幼儿按要求取学具,并把取到的学具按指令摆好(1)首先,让幼儿用魔块在数位图上摆出10然后再加上1,让幼儿说出10加1等于11(2)用此方法学习10+2…10+9、教师小结:10加几就等于十几3、利用魔块学习进位加法(1)教师出示算式9+2让幼儿看算式取出魔块,先取9块再取2块放在数位图的右侧(2)比较两个数的大小,把多的魔块放在数位图的个位上,用少的来凑十,9和几组成10(9和1组成10),从旁边的2中拿出1个魔块放在个位数(3)让幼儿说出个位上现在是几(4)教师提问:个位满十怎么办?引导幼儿说出“满十进一,个位清零”(5)请幼儿说出数位图旁边还剩几个魔块?(1个)应该给他放在哪里?(个位)让幼儿读出数位图上的数(11),然后读算式9+2=114、让幼儿用语言复述9+2的运算过程:先把9放在数位图上,把2分成1和1,9加1等于10,10加1等于11,所以9+2=115、教师在黑白上写出:〃9 + 2 = 111 1结束部分:10 11 这种方法叫“凑十法” 6、用此方法学习20以内的进位方法7、教师小结:今天学习的是一位数加一位数结果比10大,个位满十向十位进一,这就是“进位加法”在计算进位加法的过程中要用“凑十法”来计算。

8、巩固练习幼儿有秩序的把学具送回原处【篇二:20以内的加法教案】20以内的加法一、课程分析:本课是学习10加几和十几加几。

学习10加几时,通过让学生摆小棒知道:10表示一个十、也就是十个一,几表示几个一,十个一和几个一合起来是十几个一,是十几;学习十几加几时,先让学生试着计算并交流,说出自己的算法。

加减法指令的实现

基本模型机的设计——加减法指令的实现1设计题目基本模型机系统分析与设计,利用所学的计算机组成原理课程中的知识和提供的实验平台完成设计任务,从而建立清晰完整的整机概念。

着重加减法指令的实现和设计,编制实验所需的程序,上机测试并分析所设计的程序。

2设计目的(1)巩固“电工电子学” 、“数字逻辑”、“汇编语言程序设计” 、和“计算机组成原理”等相关课程学习内容。

(2)掌握计算机组成原理实验平台的使用,加深对计算机各模块协同工作的认识,建立清晰完整的整机概念。

(3)通过使用 HKCPT软件了解程序编译 , 加载过程。

(4)通过单步 , 单拍调试 , 理解模型机中的数据流向。

3模型机的逻辑框图根据设计要求,模拟机的逻辑框图如下:DR1DR2累加器 A374374374374CYZDALALU-O244244DATA BUS166*2 PC374 IR2RAM 程序374 指令6264*3寄存器PC-O244 IR2-O 244 指令译码163*2 微地址寄存器ADDRESSBUS微地址4指令系统的设计4.1 指令类型(1)算术 / 逻辑运算指令如:进行加法、减法、取反、逻辑运算例如 : ADD A,RiSUB A,RiAND A,Ri(2)移位操作指令带进们位或不带进位的移位指令例如: RRC A, RiRR A(3)数据传送类指令CPU内部寄存器之间进行数据传递例如 : MOV A,RIMOV RI,A( 4)程序跳转指令程序跳转指令可分为无条件跳转指令和有条件跳转指令两大类. 它可以根据寄存器的内容是否为零来标志 (ZD), 有进位标志 (CY), 也可以根据实际情况自行设置。

例如 : 无条件跳转指令JMP addrZD=0 时跳转JZ addrCY=0 时跳转JC addr自定义的跳转语句JN addr( 5)存储器操作类指令存储器读/写指令,用来把内在单元写入寄存器中或把寄存器中的内容写入存储器。

汇编语言只用ADD指令实现整数和浮点数的加减乘法

课程项目报告一、要求:利用汇编语言完成以下功能:通过键盘输入二进制指令,对指令译码,完成相应的加、减和乘操作全过程。

只能使用汇编的ADD指令,不能使用汇编已有的其他加法、加法和乘法指令。

**其中00为加法,01为减法,10为乘法*指令格式二为:*操作码*第一定点数*第二定点数*第一浮点数*第二浮点数*7170 *696867*666564*63.........32*31.. 0*其中当操作码为11,第二定点数全为0,第一定点数分别为000,001,010时,分别执行第一浮点数和第二浮点数的加、减和乘法操作,浮点数格式采用IEEE754标准。

二、程序流程:1.通过中断输入要译码的二进制字符流;2.选择其前8位合成1个数(如00101001就可合并为29H),先对其进行要运算的判定。

通过依次移位将最左端的值放进CF位,判断其值为0或1跳转到相应的位置进行运算;3.此程序显然有六种运算:1)整数加法:最简单的一种,将两个操作数通过移位和设定寄存器的初值来获得,然后只需调用加法使两个寄存器相加即可,将结果存入result内存单元中。

并通过中断对结果进行输出到屏幕的显示。

2)整数减法:取数和加法一致,但由于规定只能使用加法指令,因此必须先将减数的值进行求补(取反加1),再进行加法指令即可,将结果存入result内存单元中。

并通过中断对结果进行输出到屏幕的显示。

3)整数乘法:利用硬件实现乘法的思想,通过判断第二个操作数的未判断的较低位决定是加被乘数还是加0的操作,然后将结果右移,直到将操作数的所有位判断完毕(最后一位不移位),将结果存入result内存单元中。

并通过中断对结果进行输出到屏幕的显示。

4)浮点数加法:前面取了前8位归并后,将指针的位置保留下来,现在将其指针弹栈继续对剩下的输入的字符进行操作。

首先调用子程序将剩下的输入字符流存入内存以待使用(将字符流转变成数值并组成一个完整的数字,即浮点数有三个数:1位的数符,8位的阶码,23位的数值)。

加减法指令的实现

加减法指令的实现1.设计目的通过使用软件HKCPT,了解程序编译,加载的过程。

通过微单步,单拍调试,理解模型机中的数据流向。

本实验主要是设计加减法指令的实现,将汇编语言程序设计与计算机组成原理2方面的知识结合到一起利用此软件平台实现连续几个数的加减运算,从而了解逻辑运算运算单元的运行过程。

2.设计原理计算机中CPU是核心,它是通过指令和微指令的执行来工作的。

指令是计算机要完成的某一项功能。

它对应到执行的过程中是一段微程序。

一段微程序含多条为指令,而一条微指令又含多个微命令。

一个微命令驱动某个硬件部件执行某种操作。

通过这样一个关系,从而达到由计算机指令来驱动计算机各个硬部件的协调工作以实现一条指令的执行。

在各个模块中,各模块的控制的控制信号都是手动模拟产生的。

而在真正的实验系统中,模型机的运行是在微程序的控制下,实现特定指令的功能。

在本实验平台中,模型机从内存中取出、解释、执行机器指令都将由微指令和之相配合的时序来完成,即一条机器指令对应一个微程序。

3.模型机的逻辑框图其中运算器由2片74L181构成8位字长的ALU单元。

2片74LS374作为2个数据锁存器(DR1、DR2),8芯插座ALU-IN作为数据输入端,可通过短8芯扁平电缆,把数据输入端连接到数据总线上。

数据输入锁存器DR1的EDR1为低电平,并且D1CK有上升沿时,那来自数据总线的数据打入锁存器DR1。

同样使EDR2为低电平、D2CK有上升沿时把数据总线上的数据打入数据锁存器DR2。

4.指令系统及指令格式4.1指令系统此次实验涉及的指令有以下几种:MOV A, #data 将立即数传递到通用寄存器A中ADD A, RI 将寄存器RI中的数据与累加器A中的数据相加的和存入 A SUB A, RI 将累加器A中的数据与寄存器RI中的数据之差存入 ASTA addr 将寄存器中内容写入存储器中HALT 停机指令4.2指令格式一般指令由操作码和操作码组成,如下所示:操作码地址码此实验所涉及指令的格式如下:MOV指令采用双字节指令,其格式如下:7 6 5 4 3 2 1 0操作码××RiDataSTA取数据指令,其格式如下:7 6 5 4 3 2 1 0操作码××××dataaddr停机指令(HALT),其格式如下:7 6 5 4 3 2 1 0操作码××××5.微程序的设计及实现方法5.1微程序入口地址的形成在本实验平台的硬件设计是采用的24位微指令,若微指令采用全水平不编码纯控制场的格式,那么至多可有24个微操作控制信号,可由微代码直接实现。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

课程设计任务书学生姓名:专业班级:计算机指导教师:工作单位:计算机科学与技术学院题目: 基本模型机的设计——加减法指令的实现初始条件:理论:学完“电工电子学”、“数字逻辑”、“汇编语言程序设计”、和“计算机组成原理”课程,掌握计算机组成原理实验平台的使用。

实践:计算机学院科学系实验中心提供计算机、实验的软件、硬件平台,在实验中心硬件平台验证设计结果。

要求完成的主要任务:(包括课程设计工作量及其技术要求,以及说明书撰写等具体要求)1、基本模型机系统分析与设计,利用所学的计算机组成原理课程中的知识和提供的实验平台完成设计任务,从而建立清晰完整的整机概念。

2、根据课程设计题目的要求,编制实验所需的程序,上机测试并分析所设计的程序。

3、课程设计的书写报告应包括:(1)课程设计的题目。

(2)设计的目的及设计原理。

(3)根据设计要求给出模型机的逻辑框图。

(4)设计指令系统,并分析指令格式。

(5)设计微程序及其实现的方法(包括微指令格式的设计,后续微地址的产生方法以及微程序入口地址的形成)。

(6)模型机当中时序的设计安排。

(7)设计指令执行流程。

(8)给出编制的源程序,写出程序的指令代码及微程序。

(9)说明在使用软件HKCPT的联机方式与脱机方式的实现过程(包括编制程序中加减法指令的时序分析,累加器A和有关寄存器、存储器的数据变化以及数据流程)。

(10)课程设计总结(设计的特点、不足、收获与体会)。

时间安排:周一:熟悉相关资料。

周二:系统分析,设计程序。

周三、四:编程并上实验平台调试周五:撰写课程设计报告。

指导教师签名:年月日系主任(或责任教师)签名:年月日实现普通的加、减法指令一、设计目的与原理1、实验目的本实验,通过掌握各个单元模块的工作原理,进一步将其组成完整的系统,构造成1台基本的模型计算机。

并通过这台模型计算机,对计算机的基本组成、部件的设计、部件间的连接、微程序控制器的设计、微指令和微程序的编制等过程有更深的了解,加深对理论课程的理解。

在本试验中,我们将规划读写内存、寄存器、数值计算等功能,并且编写相应的微程序。

具体上机调试各个模块单元以进一步掌握整机的概念。

2、实验原理在本设计中,数据通路的控制将由微程序控制器来完成。

在各个模块实验中,各模块的控制信号都是由实验者手动模拟产生的。

而在真正的实验系统中,模型机的运行是在微程序的控制下,实现特定指令的功能。

计算机从内存取出一条机器指令到指令执行结束的一个指令周期,全部由微指令和与之相匹配的序列来完成,即1条机器指令对应一个微程序。

二、总体设计1.模型机逻辑框图简单的模型计算机由算术逻辑运算单元、微程序单元、堆栈寄存器单元、累加器、启停、时序单元、总线和存储器单元组成。

下图为较典型的实验计算机整体逻辑框图:2、指令系统与指令格式实验平台内采用的是8位数据总线和8位地址总线方式,设计指令系统时,主要考虑的是指令的类型,寻址方式和编码方式。

指令类型包括算术/逻辑运算类指令、移位操作类指令(带进位或不带进位)、数据传送类指令、程序跳转指令(有条件或无条件)、存储器操作类指令等。

寻址方式包括直接地址寻址、寄存器直接寻址、寄存器间接寻址、立即数寻址等。

指令格式的设定一般与机器的字长、存储器的容量以及指令的功能有关。

主要包括操作码字段和地址码字段。

本实验中操作码为8位,数据的传送单位为8位。

3、微程序的设计及其实现方法3.1微指令格式设计微指令长24位,本阶段的设计任务是决定24位长的微指令是否分段定义,以及确定各段段长、决定各码位含义和有效性等。

由于模型机指令系统规模较小,功能也不太复杂,所以采用全水平不编码纯控制场的微指令格式。

因为在本设计平台的硬件设计中,微指令长24位,所以最多有24位微操作控制信号可由微码直接实现。

本实验计算机24位长的微指令,对应信号分别为:S0、S1、S2、S3、M、CN、AUL-O、EDR2、EDR1、RA-O、ERA、X1、X0、HALT、WR、RR、ELP、PC-O、IR2-O、EIR2、EIR1、RM、WM、MLD。

3.2微程序入口地址及后续微地址当微指令格式确定后,就需要确定后续微指令地址。

通常是先确定微程序分支处的微地址,因为微程序分支处需要进行判断测试。

微指令由ROM读出后直接给出下一条微指令的地址,这个地址就放在微地址寄存器中。

当微程序出现分支时,通过地址转移逻辑去修改微地址寄存器内容,并按修改好的微地址读出下条微指令。

在模型机中,微程序入口地址的确定采用“按操作法散转”方法,即用指令操作码的高4位作为核心扩展成8位的微程序入口地址MD0~MD7。

(如下表所示)在00H放置了一条取址指令,当实验平台开始运行时,微地址从00H开始运行,根据程序开始地址从内存中读出第一条指令。

微指令的运行顺序采用计数增量方法,下一条微指令的地址确定方法,是通过上一条微指令执行后微地址自动加一得到的。

例如:确定了一条程序的微程序入口地址为17H,那么当执行完17H这条微指令后,微地址加1,指向18H微地址。

4、时序的设计安排时序模块由监控单元产生一个PLS-O的信号来控制时序产生。

PLS-O信号经过时序单元的处理产生4个脉冲信号。

4个脉冲信号组成一个微周期,为不同的寄存器提供工作脉冲。

PLS1:微地址寄存器的工作脉冲,用来设置微程序的首地址及微地址加1.PLS2:PC计数器的工作脉冲,根据微指令的控制实现PC计数器加1和重置PC计数器(跳转指令)等功能。

PLS3:把24位微指令打入3片微指令锁存器。

PLS4:把当前总线上的数据打入微指令选通的寄存器中。

SIGNPLS1PLS2PLS3PLS45、指令执行流程根据模型机整机逻辑图和目前硬件条件来设计指令系统中每条指令的执行流程。

下面根据本实验编制的源程序来说明执行流程:(1) MOV A,#55H指令功能为:55H-->A,需执行如下操作:(PC)+1----->PC ;PC加1,为取本指令下一字节做准备(RAM)----->ODB----->IDB----->A ;取出本指令第二字节(即55H)送A(PC)+1---->PC ;PC加1,为取下条指令字节做准备(PC)---->IAB---->OAB ;PC计数器内容作访问内存地址(RAM)---->ODB---->IDB---->IR1 ;从内存该地址单元读出指令字节送指令寄存器IR1。

(2) MOV R0,#66;指令功能为:66H-->R0,需执行如下微操作:(PC)+1---->PC ;PC加1,为取本指令下一字节准备(RAM)----->ODB----->IDB----->R0 ;取出本指令第二字节(即66H)送R0(PC)+1---->PC ;PC加1,为取下条指令字节做准备(PC)---->IAB---->OAB ;PC计数器内容作访问内存地址(RAM)---->ODB---->IDB---->IR1 ;从内存该地址单元读出指令字节送指令寄存器IR1。

(3) ADD A,R0;指令功能为:(A)+(R0)--> A ,需执行如下微操作:(PC)+1----> PC ;PC加1,为取本指令下一字节准备(A)----> DR1 ;累加器A内容送ALU(R0)----> DR2 ;寄存器R0内容送ALU(A)+(R0)----->IDB----->A ;使ALU执行加法,结果经IDB最后送入累加器AC n+4 ---->CY ;根据加法结果置进位标志CY(PC)---->IAB---->OAB ;PC计数器内容作访问内存地址(RAM)---->ODB---->IDB---->IR1 ;从内存该地址单元读出指令字节送指令寄存器IR1。

(4) MOV R1,#33;指令功能为:66H-->R0,需执行如下微操作:(PC)+1---->PC ;PC加1,为取本指令下一字节准备(RAM)----->ODB----->IDB----->R0 ;取出本指令第二字节(即33H)送R1 (PC)+1---->PC ;PC加1,为取下条指令字节做准备(PC)---->IAB---->OAB ;PC计数器内容作访问内存地址(RAM)---->ODB---->IDB---->IR1 ;从内存该地址单元读出指令字节送指令寄存器IR1。

(5) SUB A,R1;指令功能为:(A)-(R1)--> A ,需执行如下微操作:(PC)+1----> PC ;PC加1,为取本指令下一字节准备(A)----> DR1 ;累加器A内容送ALU(R1)----> DR2 ;寄存器R0内容送ALU(A)-(R0)----->IDB----->A ;使ALU执行减法,结果经IDB最后送入累加器AC n+4 ---->CY ;根据加法结果置进位标志CY(PC)---->IAB---->OAB ;PC计数器内容作访问内存地址(RAM)---->ODB---->IDB---->IR1 ;从内存该地址单元读出指令字节送指令寄存器IR1。

(6) STA 10指令功能为:(A)-->10H ,需执行如下微操作:(PC)+1---->PC ;PC加1,为取本指令下一字节准备(PC)---->IAB---->OAB ;PC计数器内容作访问内存地址(RAM)----->ODB----->IDB----->IR2 ;取出本指令第二字节(即10H)送IR2 (PC)+1----> PC ;PC加1,为取下条指令字节做准备(IR2)---->IAB---->OAB ;IR2形成新的地址A---->ODB---->IDB---->(RAM) ;将A中的数存入内存中(PC)---->IAB---->OAB ;PC计数器内容作访问内存地址(RAM)---->ODB---->IDB---->IR1 ;从内存该地址单元读出指令字节送指令寄存器IR1。

(7) HALT指令功能为:置模型机于停机状态。

设计流程时,保证每条微指令所含的微操作的必要性和合理性。

总线IAB、IDB、OAB、ODB仅是传输信息的通路,没有寄存信息的功能。

三、程序1、源程序编制的源程序如下:MOV A,#55MOV R0,#66ADD A,R0MOV R1,#33SUB A,R1STA 10HALT2、程序的指令代码3、微程序微单步运行过程如下:四、实现过程1、联机方式启动软件后,在代码窗口输入源程序,单步运行,微单步运行。