Cyclone II器件中文资料

EP1C12Q240C8N中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

注意 表 1-1: (1) 该参数包括全局时钟引脚.

EP1C3 59,904

1 104

EP1C4 78,336

2 301

EP1C6 92,160

2 185

EP1C12 239,616

2 249

Cyclone器件在四方扁平封装(QFP),并提供节省空间

FineLine ® BGA封装(见

表1-2

通过 1–3).

于接口和支持ASSP和ASIC器件. Altera还提供新低成本串行配置设备

配置Cyclone器件.

特征

Cyclone器件系列具有以下特性:

■ 2,910 20060个LE,见

表1-1

■ 高达294,912 RAM位(36,864字节)

■ 通过低成本串行配置设备支持配置

■ 支持LVTTL,LVCMOS,SSTL-2和SSTL-3 I / O标准

65

EP1C4

—

EP1C6

—

EP1C12

—

EP1C20

—

104

—

—

—

—

—

—

—

249

301

98

185

185

—

—

—

173

185

249

—

—

—

—

233

301

须知 表 1-2: (1) TQFP:薄型四方扁平封装.

PQFP:塑料四方扁平封装. (2) Cyclone器件支持在同一封装内垂直迁移(即,设计人员可以之间迁移

BGA

1.0

441

21×21

文件 修订记录

表1-4

显示修订历史此文档.

表 1-4.文档修订历史记录

Cyclone II系列FPGA简介

I/O标准 3.3V/2.5V/1.8V LVTTL 3.3V/2.5V/1.8V/1.5V LVCMOS 3.3V PCI 3.3V PCI-X

性能 167MHz 167MHz 66MHz 100MHz

典型应用 通用 通用

PC和嵌入式 PC和嵌入式

2.5V/1.8VSSTLClass I 2.5V/1.8VSSTLClass II 1.8V/1.5V HSTL Class I 1.8V/1.5V HSTL Class II

Cyclone II 系列的IOE结构

a

15

I/O单元模块

Cyclone II器件支持多种单端I/O标准,包括LVTTL 、LVCMOS、SSTL、 HSTL、PCI和PCI-X。单端I/O标准具有比差分I/O标准更强的电流驱动能 力,在同如DDR 和DDR2 SDRAM 等高级存储器器件接口时非常重要。 Cyclone II器件也支持对特定I/O标准的可编程驱动强度控制,设置范围 为2-24mA。下表为Cyclone II器件支持的单端I/O标准和各自的性能。

Cyclone II系列FPGA简介

组员:盛传广 丁宁 徐兴龙 刘鑫 皮少华 柳媛瑾

a

1

Cyclone II系列FPGA简介

Cyclone II系列器件是Altera低成本Cyclone系 列的第二代产品,Cyclone II FPGA的成本比第一代 Cyclone 器件低30%,逻辑容量大3倍多。Cyclone II器件采用TSMC经验证的90nm低K绝缘材料工艺技术, 是业界成本最低的FPGA。Cyclone II通过使用新型 的架构,缩小裸片尺寸,在保证成本优势的前提下提 供了更高的集成度和性能。

167MHz

存储器

CYCLONE II系列FPGA的结构

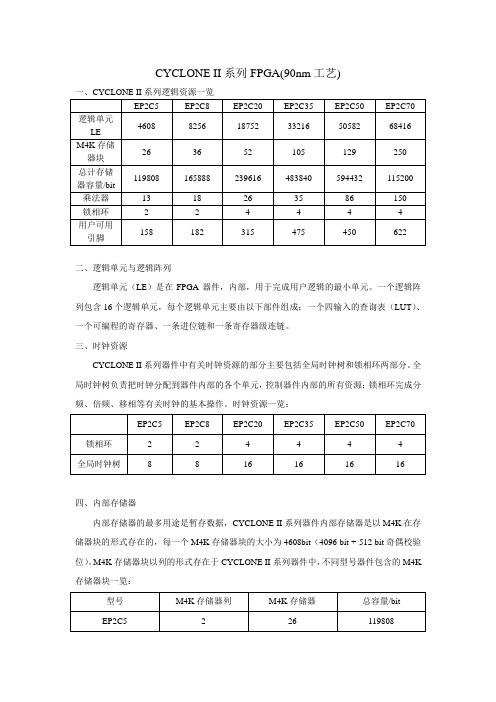

CYCLONE II系列FPGA(90nm工艺)二、逻辑单元与逻辑阵列逻辑单元(LE)是在FPGA器件,内部,用于完成用户逻辑的最小单元。

一个逻辑阵列包含16个逻辑单元,每个逻辑单元主要由以下部件组成:一个四输入的查询表(LUT)、一个可编程的寄存器、一条进位链和一条寄存器级连链。

三、时钟资源CYCLONE II系列器件中有关时钟资源的部分主要包括全局时钟树和锁相环两部分。

全局时钟树负责把时钟分配到器件内部的各个单元,控制器件内部的所有资源;锁相环完成分频、倍频、移相等有关时钟的基本操作。

时钟资源一览:四、内部存储器内部存储器的最多用途是暂存数据,CYCLONE II系列器件内部存储器是以M4K在存储器块的形式存在的,每一个M4K存储器块的大小为4608bit(4096 bit + 512 bit奇偶校验位)。

M4K存储器块以列的形式存在于CYCLONE II系列器件中,不同型号器件包含的M4K 存储器块一览:CYCLONE II 系列器件中的M4K 可以被配置为以下模式:单口模式、简单双口模式、完全双口模式、移位寄存器模式、只读存储器(ROM )模式和先入先出(fifo )模式。

五、FPGA 芯片的配置由于CYCLONE II 系列的FPGA 是基于SRAM 工艺制造的,SRAM 属于易失性的存储媒质,因此FPGA 在每次上电时必须重新配置。

CYCLONE II 系列的FPGA 支持3种配置方式:主动串行(AS )、被动串行(PS )和JATG 模式。

CYCLONE II 器件的配置分为3个阶段:复位阶段、配置阶段和初始化阶段。

六、FPGA 内部资源的使用锁相环(PLL )配置,锁相环一般用于同步输入时钟和输入数据,以及完成时钟综合,包括分频、倍频、移相等操作。

PLL 配置需求:CYCLONE II 系列器件中的M4K 配置为以下模式:单口RAM 模式、移位寄存器模式、只读存储器(ROM )模式和先入先出(fifo )模式。

Cyclone II系列FPGA简介

Cyclone II系列FPGA整体特性

Cyclone II器件容量有4608-68416个逻辑单元, 还具有新的增强特性,包括多达1.1Mbit的嵌入存储 器、多达150个嵌入18×18乘法器、锁相环、支持外 部存储器接口及差分和单端I/O标准。

Cyclone IIห้องสมุดไป่ตู้列的主要特点:

高效率的芯片结构支持从4608LE到68416LE的集成度。 包含内部嵌入式乘法器,支持DSP运算。 先进的I/O,支持PCI,DDR,DDR2等多种接口。 全局时钟管理及嵌入式锁相环。 支持Altera IP Core 及Nios II 嵌入式处理器。

26

2

4

182 315

75

125

EP2C35

33216 105

483840

35 4 475 200

EP2C50

50528 129

594432

86 4 450 192

EP2C70

68416 250

115200

150 4 622 275

4

Cyclone II系列FPGA整体特性

• Cyclone II 系列FPGA 的内部结构示意图

Cyclone II 系列的IOE结构

15

I/O单元模块

Cyclone II器件支持多种单端I/O标准,包括LVTTL 、LVCMOS、SSTL、 HSTL、PCI和PCI-X。单端I/O标准具有比差分I/O标准更强的电流驱动能 力,在同如DDR 和DDR2 SDRAM 等高级存储器器件接口时非常重要。 Cyclone II器件也支持对特定I/O标准的可编程驱动强度控制,设置范围 为2-24mA。下表为Cyclone II器件支持的单端I/O标准和各自的性能。

采用Cyclone与Cyclone-II系列器件进行设计

ALD/PRE ADATA

D

Q

ENA CLRN

32

Cyclone LE 工作模式

• 普通模式

– 通用的组合或寄存器逻辑

• 动态算术模式

– 为下列功能设计

• 加法器 • 计数器 • 累加器 • 比较器

– 使用进位级联从而获得更快的速度

• 由综合工具自动选择

33

addnsub

data1 data2 data3

30

Cyclone LE 输入输出

• 输入

– 4个数据 – 2个LE 进位输入和 1个LAB进位输入 – 一个动态加减控制 – 寄存器控制

• 输出

– 2个LE进位输出 – 2个行、列、直连输出 – 1个本地输出 – 1个LUT级联和1个寄存器级联信号

31

LE 寄存器控制

• 时钟与时钟使能 • 同步与异步清零 • 同步与异步装载以及数据 • 异步预设

36

LAB Carry-in

A1

B1

A2 B2

A3 B3

A4 B4

A5 B5

A6 B6

A7 B7

A8 B8

A9 B9 A10 B10

Cyclone 进位链

01

LLEe11 Sum1 LLEe22 Sum2 LLEe33 Sum3 LLEe44 Sum4 LE5 Sum5

01

LE6 Sum6

• 进位链可以在任何一个LE中停止 或开始

– DDR2 & QDRII

11

订购编码

EP2C35F484C7

EP2C 35 F 484 C 7

器件系列(EP1C = Cyclone; EP2C = Cyclone II) 大约的逻辑单元数(LE) x 1000 封装类型: F = Fineline BGA, P = PQFP 封装管脚数

Cyclone II EP2C5(8)启蒙板说明书V2.2

Cyclone II EP2C5/8 启蒙板说明书 Cyclone II EP2C5/8 Start Board User Manual Version 2.1 Copyright © 线路人生|Circuitry Life 线路人生|Circuitry Life 版本修订记录 Version 1.0 2.0 2.1 2.2 Author zhiyuh zhiyuh zhiyuh Zhiyuh Data 2009‐6‐3 2009‐6‐12 2009‐07‐09 2009‐08‐22 Cyclone II EP2C5/8 Start Board Description First draft. 根据 Rev.B 电路图修改相关内容,并补充各电路 与 FPGA 之间的引脚连接定义。

增加兼容设计方面的解释内容,完善部分 BOM。

修改首页图片,BOM 增加备注。

备注:关于修订的说明 ~ 2 ~ 线路人生|Circuitry Life Cyclone II EP2C5/8 Start Board 目录 1. 模块介绍 ........................................................................................................................... 4 1.1 1.2 模块主要功能 ............................................................................................................ 4 模块适用范围 ............................................................................................................ 4 2. 包装清单 ........................................................................................................................... 4 2.1 2.2 模块包装清单 ............................................................................................................ 4 安装说明 .................................................................................................................... 4 3. 硬件说明 ........................................................................................................................... 5 3.1 电路说明 .................................................................................................................... 5 FPGA 芯片及主要外围电路............................................................................... 5 电源电路 ............................................................................................................ 7 存储器电路 ........................................................................................................ 8 板载 LED 测试电路 .......................................................................................... 13 IO、控制线和总线引出接口 .......................................................................... 14 . 硬件的其它说明 .............................................................................................. 15 3.1.1. 3.1.2. 3.1.3. 3.1.4. 3.1.5. 3.1.6. 3.2 3.3 4. 5. 6. 7. 器件清单(BOM) ................................................................................................. 15 . 电路板相关尺寸参数 .............................................................................................. 17 使用注意事项 ................................................................................................................. 17 技术支持 ......................................................................................................................... 18 硬件原理图 ..................................................................................................................... 18 其它备注 ......................................................................................................................... 18 ~ 3 ~ 线路人生|Circuitry Life Cyclone II EP2C5/8 Start Board 1. 模块介绍 1.1 模块主要功能 数字系统和 SOPC 设计在广大学生和爱好者中已经形成了一定的学习氛围和规模,但市 场上的开发板和学习板良莠不齐,为此线路人生|Circuitry Life 特设计了本模块,中文名为 “Cyclone II EP2C5/8 启蒙板” ,英文名为“Cyclone II EP2C5/8 Start Board” 。

Altera Cyclone II

Altera Cyclone II

Altera Cyclone II FPGA 帮助Newtec 实现了灵活的高性能双向卫星宽带终端

在当今高速视频下载和数据传输环境中,互联网已经成为世界上很多家庭

的日常工具。

该技术虽然发展很快,但是欧洲仍有很多农村地区还没有宽带

接入——直到现在。

Altera 公司日前宣布,Newtec 获得大奖的Sat3Play 宽带终端采用了Cyclone II FPGA 来提供宽带服务。

Sat3Play 宽带终端是双向卫星系统的组成部分,支持ISP 和电信公司在还没有实现低成本宽带链接的地区提供语音、数据和电视服务。

Newtec 是卫星通信产品和解决方案的世界级供应商,产品包括DVB 调制器、数字电视、

射频分配网络、电视网络和IP 宽带接入网等。

Altera Cyclone II 器件实现了灵活、可更新的Sat3Play 宽带终端。

在终端中,Cyclone II 器件用作ASSP 协处理器,处理返回通道的上游调制,对协议封装数据进行滤波,传输并接收IP 数据包,同时处理PCI 等关键系统接口。

Newtec 营销副总裁Max d’Oreye 评论说:“多年以来,欧洲的部分互联网用户在宽带接入上一直没有选择余地。

受居住地区的限制,他们不得不使用PSTN 或者ISDN 来接入互联网。

现在,Sat3Play 用户可以随心所欲地随时随地接入互联网。

Altera 的Cyclone II FPGA 为这一大批量应用提供了高性价比解决方案,我们能够更高效地提高宽带终端的带宽,从而使这一接入方式成

为现实。

”。

Cyclone II代芯片分析

Cyclone II代芯片分析班级:1211自动化学号:2012118064姓名:英雄有泪Cyclone系列芯片是Altera公司推出的新一代低成本、中等规模的FPGA,其价格仅为Altera现有主流器件的30%~50%。

它通过去掉DSP块,MegaRAM,降低LVDS接口速率等指标后,可适应大多数设计的要求,同时分担用户所面临的成本压力。

该芯片采用0.13μm,全铜SRAM工艺,1.5v内核,同时还拥有2910个逻辑单元到20060个逻辑单元以及59904位RAM到294912位RAM,这使得它可用于实现多种复杂的功能。

此外,该芯片还提供了用于时钟管理的锁相环和用于连接工业标准外部存储器的专用I/O接口;而且,多种IP 核及Altera发布的Nios嵌入式微处理器软核均能在其上实现。

最后,我们具体实现了一个基于Cyclone FPGA的电子时钟的设计。

可编程器件方面,我们选用的是240管脚PQFP封装的EP1C12器件;配置时则是采用主动串行配置方案下的EPCS1器件。

在此,论文主要讲解了板卡的组成、内部设计及仿真,其中内部实现包括:原理图、PCB图的绘制和VHDL程序的编写。

Cyclone系列芯片的结构分析Cyclone现场可编程逻辑阵列芯片系列是一款低价格中等密度的FPGA,采用0.13μm的全铜SRAM工艺,容量从2910个逻辑单元到20060个逻辑单元(LEs:Logic Elements),1.5v内核。

Cyclone的性价比较高,它提供用于时钟控制的锁相环(PLLs:Phase-Locked Loops),同时它还有一个专用的双倍数据传输率(DDR)接口用于满足DDR SDARM和FCRAM(fast cycle RAM)存储器的需要,Cylone器件支持多种I/O标准接口,包括数据传输率可达311Mbps的LVDS(Low Voltage Differential Signaling,低电压差分信号)和66 MHz/32 bits的PCI接口,同时还支持ASSP(Application-specific Standard Products)和ASIC (Application-specific Integrated Circuit)器件。

EP1C6Q240I7N中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

更改摘要

— — — — — —

1–3

初稿

使用该设备插脚引线对于一个给定包所有计划中密度引脚

输入识别哪些I / O引脚可以迁移.在Quartus

® II

软件可以自动交叉引用和地点所有引脚你

当给定一个设备迁移列表.如果一个设备有电源或地 销,但这些相同引脚是不同装置,其在对用户I / O 迁移路径,Quartus II软件防护证销不作为 用户I / O在Quartus II软件.确防护这些引脚连接

100-Pin TQFP

0.5 256 16×16

144-Pin TQFP

0.5 484 22×22

240-Pin PQFP

0.5 1,024 34.6×34.6

256-Pin FineLine

BGA

1.0

289

17×17

324-Pin FineLine

BGA

1.0

361

19×19

400-Pin FineLine

1–2

初稿

2008年 5月

芯片中文手册,看全文,戳

文档修订历史记录

到电路板上相应平面. Quartus II软件储备 I / O引脚所必需与在同一个包有多个电源引脚较大密度布局电源引 脚.

表 1-3.旋风 QFP和 BGAFineLine包装规格

尺度

间距(mm) 区(毫米 ) 长短 × width (mm × mm)

高达288千位RAM.有这样锁相环路(PLL),用于时钟和一个专用双倍数据

速率(DDR)接口,以满足DDR SDRAM和快速周期RAM(FCRAM)内存需求特

点,Cyclone器件可用于数据通道应用提供具有成本效益解决

方案. Cyclone器件支持多种I / O标准,包括LVDS数据速率高达每

CycloneII器件672管脚的分布图适合学习DDR2

PT-EP2C35-1.9.xls Copyright © 2008 Altera Corp.

Disclaimer

Page 1 of 25

Pin Information for the Cyclone ® II EP2C35 Device Version 1.9 Note (1), (2)

Bank Number B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 VREFB Group VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N1 VREFB2N1 VREFB2N1 Pin Name / Function GND_PLL3 VCCD_PLL3 GND_PLL3 GND IO IO IO IO IO IO VCCIO2 IO IO IO IO IO IO IO GND IO IO IO IO IO VCCIO2 IO IO IO IO IO IO IO GND IO IO IO IO IO VCCIO2 IO IO IO IO IO Optional Function(s) Configuration F484/ Function U484 F5 E5 F6 ASDO nCSO CRC_ERROR CLKUSR C4 C3 D3 D4 D5 D6 E3 E4 C1 C2 F672 E4 H7 G7 E3 D3 B2 B3 E5 F6 C2 C3 G5 G6 F3 F4 D2 D1 F7 J5 J8 J7 H6 E2 E1 K6 K5 G4 G3 F3 D1 D2 G3 H4 H5 H6 E1 E2 F1 J6 K8 K7 F2 F1 G1 G2 H3 H4 J3 DQ2L6 DQ2L7 DM2L DQ0L0 CDPCLK0/DQS2L DQ0L1 DQ0L2 DQ0L3 DQ0L4 DQ1L6 DQ1L7 DQ1L8 DM1L0/BWS#1L0 DQ1L9 CDPCLK0/DQS2L DQ1L10 DQ1L11 DQ1L12 DQ1L13 DQ2L0 DQ2L1 DQ2L2 DQ2L3 DQ2L4 CDPCLK0/DQS2L DQ2L5 DQ2L6 DQ2L7 DQ1L0 DQ1L1 DQ1L2 DQ1L3 DQ1L4 CDPCLK0/DQS2L DQ1L5 DQ1L6 DQ1L7 DQ2L0 DQ2L1 DQ2L2 DQ2L3 DQ1L0 DQ1L1 DQ1L2 DQ1L3 DQS for x8/x9 in F484/ U484 DQS for x16/x18 in DQS for x8/x9 in F484/ U484 F672 DQS for x16/x18 in F672

Cyclone II Starter Kit中文手册

UG_EK2C20F484產品名稱:GFEC Cyclone II Starter Kit 研發電路板UG_EK2C20F484手冊版本: 2.3發表日期:2009年10月版權所有,不得翻印茂綸股份有限公司。

本產品的所有部份,包括配件及軟體等,其所有權歸茂綸股份有限公司(以下稱茂綸)所有,未經茂綸公司許可,不得任意地仿製、拷貝、騰寫或轉譯。

本使用手冊沒有任何型式的擔保、立場表達或其它暗示。

若有任何因本使用手冊或其所提到之產品的所有資訊,所引起直接或間接的資料流失、利益損失或事業終止,茂綸及其所屬員工恕不為其擔負任何責任。

除此之外,本使用手冊所提到的產品規格及資訊僅供參考,內容亦會隨時更新,恕不另行通知。

本使用手冊的所有部份,包括硬體及軟體,若有任何錯誤,茂綸沒有義務為其擔負任何責任。

本使用手冊中所提及的產品名稱僅做識別之用,而這些名稱可能是屬於其它公司的註冊商標或是版權,在此聲明如下:z Cyclone II 是Altera FPGA系列之名稱。

未提及之商標與名稱皆屬該公司所有。

在科技迅速的發展下,此發行手冊中的一些規格可能會有過時不適用的敘述,敬請見諒。

在此不擔保本手冊無任何疏忽或錯誤亦不排除會再更新發行。

手冊若有任何內容修改,恕不另行通知。

研發電路板若有任何配件及硬體上的變更,使用手冊都會隨時更新。

更新的詳細說明請您到茂綸的全球資訊網瀏覽,或直接與茂綸公司聯絡。

研發電路上的任何標簽或貼紙請勿自行撕毀與抺除,否則會影響到產品保固期限的認定標準。

目錄內容GFEC CYCLONE II STARTER KIT研發電路板規格概要 (6)本產品沒有附贈NIOS II LICENSE (6)ATTENTION (6)1.產品介紹 (7)1.1 產品規格 (8)1.2 注意事項 (9)1.3 光碟安裝 (10)2.GFEC CYCLONE II STARTER KIT研發電路板外觀及電源說明 (11)2.1. GFEC C YCLONE II S TARTER K IT研發電路板外觀圖說明 (11)2.2. 電源系統 (13)3.GFEC CYCLONE II研發電路板元件說明 (14)3.1. C YCLONE II D EVICE U8 (14)3.2. F LASH M EMORY(U2) (15)3.3. SDRAM(U1) (16)3.4. OSC(CLOCK) (17)3.5. PS2K EYBAORD (17)3.6. B ITS D IP S WITCH(S2) (17)3.7. LED(D1~D8) (17)3.8. P USH B UTTON (S1,S3,S4,S5,S6) (19)3.9. 16X2文字型LCD模組(U5) (19)3.10. RS-232(JP4) (20)3.11. E XPANSION P ROTOTYPE C ONNECTOR(CON1~4) (21)4.快速使用GFEC CYCLONE II研發電路板 (29)4.1. 軟硬體需求 (29)4.2. 電源安裝 (29)4.3. 軟體操作 (29)4.3.1. JTAG D OWNLOAD (29)4.3.2. A CTIVE S ERIAL P ROGRAMMING (AS) (33)4.4. AS M ODE (35)4.5. JTAG M ODE (35)5.附錄 (36)5.1. B YTEBLASTER MV/II在W INDOWS 2K/XP安裝指南 (36)5.2. M ICROSOFT W INDOW XP SP2相容性問題修正方法 (41)5.3. 如何將NIOS II放進C YCLONE II S TARTER K IT (41)5.4. 擴充板對應GFEC C YCLONE II S TARTER K IT I/O接腳 (42)5.5. USB版本之NIOS II S TARTER K IT說明 (47)5.6. 機構尺吋圖 (49)5.7. 電路圖 (51)聯絡茂綸股份有限公司台北總公司地址:<231>台北縣新店市北新路三段207-5號14FTEL:886-2-8913-2200FAX:886-2-8913-2277新竹分公司地址: <300>新竹市光復路一段526號3FTEL:886-3-578-6766FAX:886-3-577-4795高雄分公司地址:<800>高雄市左營區博愛二路366號20樓之1 TEL:886-7-557-5818FAX:886-7-557-5819技術支援專線TEL:0800819595茂綸全球資訊網頁GFEC Cyclone II Starter Kit 研發電路板 規格概要本產品沒有附贈NIOS II LicenseFeature• Altera Cyclone II Family EP2C20F484C8 Device(Provide 18752 LEs , 239,616 RAM Bits , 26 18X18 Multipliers , 4 PLLs) • Altera Serial Configuration Device EPCS4SI8• 16M Bytes SDRAM Memory (MT48LC4M32B2)• 8 M Bytes Flash Memory (AM29LV065D)• 2X16 Character LCD Module• PS2 Keyboard Interface• RS232 Serial Communication Port• 4 Bits DIP Switch• 5 Push Button Switchs• 8 LEDs• 50 Mhz Oscillator• Provide 185 In/Out Pin & 128 shareable In/Out Pin• USB Power Cable• Parallel Port Download Cable • User Define Extension Board 新版之Cyclone II Starter Kit 另有USB to RS-232 port ,相關說名請參考附錄5.5 Attentionz 當您拿到本實驗板後,請確認盒內東西是否完整z 本實驗板擴充I/O 電壓最多只能接受 3.3V 的信號,若不慎燒毀IC(EP2C20F484C8),本公司無保固之責任z 在正常使用下,本實驗板提供3個月的保固期1.產品介紹本實驗板是專門為Altera Cyclone II Device Family訂製的模擬板,若針對數位設計或NIOS II有興趣者可利用此實驗板模擬與實現自己想要的東西,本實驗板內建的FPGA為EP2C20F484C8,此IC提供18,752 LEs,315支一般I/O,239,616 bitsEmbedded Memory 。

DE2中文说明书--第1部分

第一章:关于工具包DE2工具包提供了使用Altera Cyclone II开发高级数字产品需要的所有模块。

此用户指南能使读者在30分钟内迅速浏览许多参考设计。

本章提供了工具包的关键信息。

工具包内容图1.1给出了DE2的图片。

DE2工具包包括以下部分:✓DE2开发板✓用于FPGA编程和控制的USB电缆✓DE2 实验光盘,包括DE2控制面板,参考设计,软件工具以及用户指南✓Altera Quartus II 5.0 网络光盘和Nios II 5.0 光盘✓附件包一个,内含:铜质支架,螺钉,橡皮脚若干✓装配在主板上的树脂玻璃一片✓9V直流Wall-mount电源图1.1. DE2 工具包组装橡皮脚用户可以使用附件袋中的铜脚,硅片和螺丝按照自己的项目组装合适的支架脚。

在DE2板上为每个6螺洞组装螺丝,铜脚和橡胶片,如图1.2所示。

如果需要额外的保护可以装上树脂玻璃片图1.2 橡皮脚安装方式获得帮助遇到问题可以从下几处获取帮助:发邮件至:support@中国台湾& 中国大陆: +886-3-550-8800韩国& 日本: +82-2-512-7661第二章:DE2开发板这一个章节将带你浏览DE2板上的每个部分及其特性DE2开发板DE2开发板使用了与大批量生产的高端产品(如最高QC标准的高密度PC主板和汽车infotainment系统)相一致的严格设计与布线准则。

主要的设计和布线思路如下所示:仔细安排器件及连接走线。

这种良好的排版可增加制造产量,并简化主板调试流程。

无跳线设计提高鲁棒性。

跳线易出错而且为不随时携带手册的用户带来不便。

部件的选择取决于片上容量。

我们选择了在PC 和DVD播放器中最常用的配置确保这些部件将来能够得到持续供应。

电源和IO口保护设计考虑到了大部分的现场意外情况。

开发板检测按图2.1测试开发板图2.1 DE2开发板组件及接口特性DE2主板为用户提供了用于多媒体开发的多种特性。

Cyclone II代芯片分析

Cyclone II代芯片分析班级:1211自动化学号:2012118064姓名:英雄有泪Cyclone系列芯片是Altera公司推出的新一代低成本、中等规模的FPGA,其价格仅为Altera现有主流器件的30%~50%。

它通过去掉DSP块,MegaRAM,降低LVDS接口速率等指标后,可适应大多数设计的要求,同时分担用户所面临的成本压力。

该芯片采用0.13μm,全铜SRAM工艺,1.5v内核,同时还拥有2910个逻辑单元到20060个逻辑单元以及59904位RAM到294912位RAM,这使得它可用于实现多种复杂的功能。

此外,该芯片还提供了用于时钟管理的锁相环和用于连接工业标准外部存储器的专用I/O接口;而且,多种IP 核及Altera发布的Nios嵌入式微处理器软核均能在其上实现。

最后,我们具体实现了一个基于Cyclone FPGA的电子时钟的设计。

可编程器件方面,我们选用的是240管脚PQFP封装的EP1C12器件;配置时则是采用主动串行配置方案下的EPCS1器件。

在此,论文主要讲解了板卡的组成、内部设计及仿真,其中内部实现包括:原理图、PCB图的绘制和VHDL程序的编写。

Cyclone系列芯片的结构分析Cyclone现场可编程逻辑阵列芯片系列是一款低价格中等密度的FPGA,采用0.13μm的全铜SRAM工艺,容量从2910个逻辑单元到20060个逻辑单元(LEs:Logic Elements),1.5v内核。

Cyclone的性价比较高,它提供用于时钟控制的锁相环(PLLs:Phase-Locked Loops),同时它还有一个专用的双倍数据传输率(DDR)接口用于满足DDR SDARM和FCRAM(fast cycle RAM)存储器的需要,Cylone器件支持多种I/O标准接口,包括数据传输率可达311Mbps的LVDS(Low Voltage Differential Signaling,低电压差分信号)和66 MHz/32 bits的PCI接口,同时还支持ASSP(Application-specific Standard Products)和ASIC (Application-specific Integrated Circuit)器件。

Cyclone II系列FPGA器件问答

1.问:Cyclone II系列器件是什么系列器件是什么??答:Cyclone II系列器件是Altera低成本Cyclone系列的第二代产品,Cyclone II FPGA 的成本比第一代Cyclone 器件低30%,逻辑容量大3倍多。

Cyclone II器件采用TSMC 经验证的90nm 低K 绝缘材料工艺技术,是业界成本最低的FPGA。

Cyclone II器件容量有4608~68416个逻辑单元,还具有新的增强特性,包括多达1.1Mbit 的嵌入存储器、多达150个嵌入18×18乘法器、锁相环、支持外部存储器接口及差分和单端I/O标准。

器件系列采用什么样的工艺技术??2.问:Cyclone II器件系列采用什么样的工艺技术答:Cyclone II器件系列是采用TSMC的1.2V、90nm、低K 绝缘材料工艺。

器件系列满足了哪些市场的需求??3.问:Cyclone II器件系列满足了哪些市场的需求答:Cyclone II器件系列是多种不同市场上大批量应用最优的低成本方案,包括消费电子、电信和无线、计算机外设、工业和汽车。

Cyclone II器件包含了许多新的增强特性,如嵌入存储器、嵌入乘法器、PLL和低成本的封装,这些都为诸如视频显示、数字电视、机顶盒、DVD 播放器、DSL调制解调器、家用网关和中低端路由器等批量应用进行了优化。

理想的替代方案??4.问:为什么Cyclone II 器件是ASIC 理想的替代方案答:Cyclone II系列提供了一种灵活的无风险的,且没有前期一次性工程费用或最小定货量的开发方式。

Cyclone II器件除了具有其它任何FPGA 无可匹敌的成本结构之外,还具有先进的特性,如用于高性能数字信号处理应用的嵌入式18×18乘法器和支持如DDR2(高达334Mbps)和QDRII(高达688Mbps)的存储器接口。

提供哪些封装??器件有哪些产品,,提供哪些封装5.问:Cyclone II器件有哪些产品答:Cyclone II系列包括6种器件,容量从4608~68416个逻辑单元。

Cyclone_II系列FPGA配置

杨宁1041121665Cyclone II系列FPGA配置杨宁 1041121665摘要:由于Cyclone II系列器件是用易失性的SRAM结构单元来存储配置数据的,所以在每次系统上电时都要进行重配置。

用户可以使用DCLK频率高达40MHz的AS(主动串行)模式、PS(被动串行)模式或是JTAG对FPGA器件进行配置操作。

另外,为了减小存储需求和配置时间,Cyclone II系列器件能够使用压缩数据进行配置。

本文的目的是让用户了解Cyclone II器件的配置特点,让用户掌握如何使用Cyclone II器件所支持的配置方式对此系列FPGA进行配置。

同时,也会介绍配置管脚的使用及配置文件的格式等相关信息。

关键词:Cyclone II; FPGA;配置第一节、Cyclone II器件配置概述:用户可以使用AS、PS 和JTAG 模式配置Cyclone II 系列FPGA。

选择何种配置方式取决于MSEL管脚的电平状态,请参照表1-1。

表1-1 Cyclone II 配置模式第二节、配置文件格式表2-1 列出了几个Cyclone II 系列器件的没有压缩过的配置文件的大小(近似值)。

如果要计算多器件配置时的配置数据的存储空间,可以将相应的值相加。

用表2-1 的值只是为了在设计之前大致的估计配置文件的大小。

不同的配置文件格式的大小并不一样,但即使是不同款的设计软件,只要目标器件一定的情况下,那么它编译的无压缩配置文件大小是固定的;而压缩过的文件大小在每次编译时都有所改变,这是由设计时的压缩比例来决定。

第三节、配置数据压缩Cyclone II 器件支持配置数据的压缩,这能节省配置数据存储的空间以及配置时间。

这个特性使得设计者能够将压缩过的配置数据存储在配置芯片或者其他的存储器(Flash)中,并且传送的也是压缩过的数据流文件。

在配置期间,Cyclone II 器件实时解压这些数据流并且将其配置到SRAM 单元中。

FPGA cyclone II

一、功能描述:Cyclone II 器件包括一个二维的行和列式架构来实现定制逻辑。

不同速度的行和列互连提供逻辑阵列模块(LABs),嵌入式存储模块和嵌入式乘法器。

逻辑阵列由LABs组成,每个LAB中有16个逻辑单元。

逻辑单元是实现用户逻辑功能的最小逻辑单位。

逻辑阵列模块分为行和列跨设备。

Cyclone II器件密度范围从4608到68416。

Cyclone II器件提供一个全局时钟网络和四个锁相环(PLLs)。

全局时钟网络由16个全局时钟线组成,全局时钟线可以驱动整个器件。

全局时钟网络可以为器件内的所有资源提供时钟,像输入/输出单元,锁存单元,嵌入式乘法器和嵌入式存储模块。

全局时钟线也可作为高扇出信号。

Cyclone II PLLs 提供通用时钟,该通用时钟具有时钟合成,相移以及高速差分I/O支持的外部输出。

M4K寄存器模块是内存加校验位为4K位的双端口寄存器模块。

这些模块提供高达260MHz的专用双端口,简单单端口或者高达36位的单端口寄存器。

在某些LABs之间这些块排列成列贯穿整个器件。

Cyclone II器件提供119到1152Kbits的嵌入式寄存器。

性能达到250MHz的嵌入式乘法器模块可以通过两个9*9位或者一个18*18位的乘法器实现。

嵌入式乘法器按列排列在整个器件内。

遍布在Cyclone II器件周围的I/O管脚由IOE反馈,IOE位于LAB行和列的终端。

I/O管脚支持各种单端和差分I/O标准,比如66MHz和33MHz,64位和32位PCI标准,PCI-X,和LVDS I/O标准,LVDS I/O标准的最大输入数据率为805Mbps和最大输出数据率为640Mbps。

每个IOE包括一个双向I/O缓冲区和三个寄存输入,输出和输出使能信号的三个寄存器。

随同延迟链一起的双用途DQS,DQ和DM管脚为外部寄存器提供高达167MHz的表面支持,寄存器如DDR,DDR2和单数据率SDRAM,和QDRII SRAM器件。

CYCLONE_II系列FPGA内部资源M4K的配置

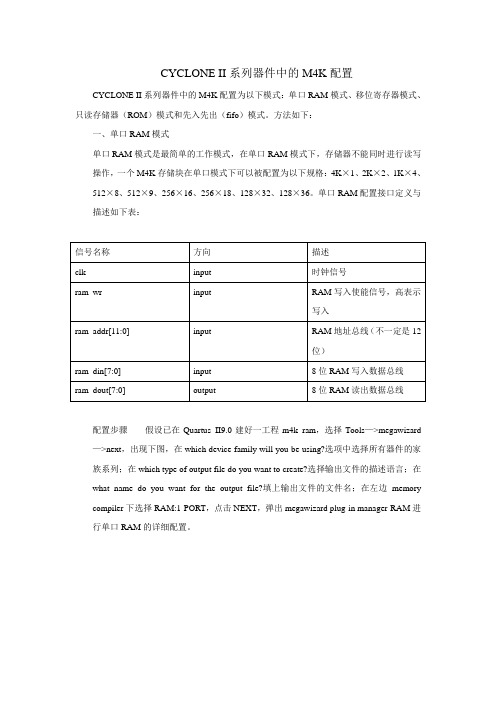

CYCLONE II系列器件中的M4K配置CYCLONE II系列器件中的M4K配置为以下模式:单口RAM模式、移位寄存器模式、只读存储器(ROM)模式和先入先出(fifo)模式。

方法如下:一、单口RAM模式单口RAM模式是最简单的工作模式,在单口RAM模式下,存储器不能同时进行读写操作,一个M4K存储块在单口模式下可以被配置为以下规格:4K×1、2K×2、1K×4、512×8、512×9、256×16、256×18、128×32、128×36。

单口RAM配置接口定义与描述如下表:配置步骤假设已在Quartus II9.0建好一工程m4k_ram,选择Tools—>megawizard —>next,出现下图,在which device family will you be using?选项中选择所有器件的家族系列;在which type of output file do you want to create?选择输出文件的描述语言;在what name do you want for the output file?填上输出文件的文件名;在左边memory compiler下选择RAM:1-PORT,点击NEXT,弹出megawizard plug-in manager-RAM进行单口RAM的详细配置。

图1图2二、只读存储器(ROM)模式利用CYCLONE II系列器件中的M4K生成单口ROM,配置步骤如下:步骤1 先生成一个.mif原始数据文件,用于配置ROM时引用,初始化ROM。

假设已建好一个工程,在Quartus II选择File—>new—>memory initialization file,如图3所示,单击OK,在弹出的对话框里words填上数据个数,size填上数据的位宽,单击OK,弹出如图4所示,将数据依次填充到文件中,保存并命名为XX.Mif。

CYCLONE II系列FPGA存储器模块

CYCLONE II系列FPGA存储器模块○1CYCLONE II 系列FPGA支持的双口RAM 类型:●单端口RAM●简单双端口RAM●真双端口RAM【在QUARTUS II中的库模块是AltSYNCRam】●混合真双端口RAM【允许不同读写宽度】○2CYCLONE II 系列FPGA存储器模块M4K寄存器清零的三种方法:●使用【异步】清零信号aclr●上电复位器件●assert the device-wide reset signal using the DEV_CLRn option○3地址时钟使能应用于:●高速缓冲储存●地址使能默认为【低】电平●读地址时钟使能时:读地址锁存在使能时的地址上,读出的数据就是锁定的那个地址单元的数据。

如:读地址锁存在0x05地址,则读出的数据就是0x05地址里面的数据值。

●Figure 8–3 shows an address clock enable block diagram. The address register output is fedback to its input via a multiplexer. The multiplexer output is selected by the address clock enable (addressstall) signal. Address latching is enabled when the addressstall signal goes high (active high). The output of the address register is then continuously fed into the input of the register until the addressstall signal goes low.●●●写地址时钟使能时:写入的数据依次写在锁定的地址上。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一、外文资料译文:Cyclone II器件系列简介关键词:cyclone II器件;特点;简介;在非常成功的第一代Cyclone器件系列之后,Altera的Cyclone II FPGA系列扩大低成本的FPGA的密度,最多达68,416个逻辑单元(LE),提供622个可用的输入/输出引脚和1.1M比特的嵌入式寄存器。

Cyclone II器件的制造基于300毫米晶圆,采用台积电90nm、低K值电介质工艺,这种工艺技术是使用低绝缘体过程以确保了快速有效性和低成本。

通过使硅片面积最小化,Cyclone II器件可以在单芯片上支持复杂的数字系统,而在成本上则可以和ASIC竞争。

不像其他用电力功耗和性能来换取低成本的FPGA卖主,Altera 最新一代低价位的FPGA——cyclone II FPGA系列,和同类90nmFPGA器件相比,它提高了百分之六十的性能和降低了一半的功耗。

低成本和优化特征使Cyclone II FPGA系列为各种各样的汽车、消费、通讯、视频处理、测试与测量、和其他最终市场提供理想的解决方案。

在参考设计、系统图,和IP,使用cyclone II FPGA系列可以帮助你迅速实现最总市场方案开发。

低成本的嵌入式解决方案Cyclone II 器件支持Nio s II 嵌入式处理器,能够自己完成自定义的嵌入式处理器。

Cyclone II器件还能够扩展各种外部存储器和I/O口或者嵌入式处理器的性能。

单个或多个NiosII嵌入式系统中嵌入式处理器也可以设计成cyclone II设备以提供一些额外的同时处理的能力或者甚至取代已经在你的系统中存在的嵌入式处理器。

使用cyclone II和nios II 能够拥有成本低和高性能处理方案的共同特点,和普通的产品相比,这个特点能够延长你的产品的生命周期,提高产品进入市场的时间。

低成本DSP方案单独使用cycloneII FPGA 系列或者或者作为数字信号处理(DSP)协处理器以提高数字信号处理(DSP)应用的性价比。

,你用以下cyclone II的特点和设计支持可以实现高性能低成本DSP系统:■150个18 × 18 乘法器■ 1.1 M比特的片内嵌入式存储器■高速的外部寄存器接口■数据处理的知识产权核■Mathworks Simulink 和Matlab设计软件与DSP Builder的接口■DSP 软件开发程序工具, Cyclone II 版本Cyclone II 器件包括一个强大的FPGA特征建立最优的低成本的应用包括广泛的密度,记忆,嵌入式乘数,和包装的选择。

Cyclone II器件支持低成本运用中常见的各种外部寄存器界面和I/O口协议。

来自Altera 和合作伙伴IP核使得Cyclone II界面和协议变的快速和简单。

Cyclone II设备系列拥有以下的特点:■4,608到68,416 LEs 的高密度的结构●M4K的嵌入式寄存器块●不减少逻辑的情况下有1.1M的可用的存储器●每个模块有4096比特寄存器(4,608比特每个模块包括512相同的比特)●可变的配置端口有×1, ×2, ×4, ×8, ×9, ×16, ×18, ×32和×36●×1, ×2, ×4, ×8, ×9, ×16, 和×18 配置的真实的双端口(一个读和一个写, 两个读,或者两个写) 操作●写入操作过程是字节写入●260-MHz 下运行■嵌入式乘法器●多达150名的18 -×18-bit乘数器,并且每个乘法器可配置为两个独立的9×9-bit的250-MHz性能的乘数器●可选的输入和输出的寄存器■先进的I/O口支持●支持高速微分I / O标准,包括LVDS,mini-LVDS,LVPECL,相对、微分HSTL,和差分SSTL●支持单端接地I / O标准,包括2.5-V和1.8-V,SSTL级别一和级别二、1.8-V和1.5-V HSTL级别一和级别二、3.3-V PCI和pci - x的1.0,330 -,2.5 -,1.8 -,和1.5-V LVCMOS,和3.3、2.5 ,1.8-V LVTTL●互连外围设备专业组(PCISIG) PCI 局部总线规格, 版本 3.0 符合 3.3-V的66或者32兆赫的33 -或64位接口的操作●拥有外部TI PHY总线接口和Altera公司PCI Express总线接口Megacore功能的PCI Express总线接口。

●133-MHz pci - x 1.0的规格兼容性●高速外部存储器的支持,包括Altera IP MegaCore 功能支持的外部单倍数据速率(SDR)、双倍数据速率(DDR)、DDR2 SDRAM器件以及第二代四倍数据速率(QDRII)SRAM器件,这些寄存器主要是为了易于使用。

●每个I/O 组成部分(IOE)有三个专用的存储器:一个输入寄存器,一个输出寄存器,和一个输入输出寄存器。

●可编程总线支持的特点●可编程输出设备扩展的特点●对I/O组成部分和逻辑门阵列进行可编程延时●I/O 存储分成单一的VCCIO和/或者VREF存储设置●I/O电压标准支持1.5-, 1.8-, 2.5-, 和3.3-接口●热插拔操作支持●实现了上电之前和上电过程中对器件和三态I/O缓冲的保护●可编程的高端输出●各种样品的终端匹配■灵活的时钟管理电路●层次时钟网路高达402.5-MHz的性能●每个器件多达四个可编程锁相环(PLL)和提供时钟乘法器和除法器,相移,可编程占空比, 和外部时钟输出, 被允许的系统时钟管理和频率合成●贯穿整个设备有多大16个全局时钟线在整个全局时钟网络中■设备的配置●快速系列配置的时间限制在100ms以内●减压的特性实现了更小的程序文件存储和更快的配置时间●支持多种配置模式: 主动配置方式,被动配置方式,和JTAG配置方式●支持低成本的配置设备的配置●设备配置支持多种电压 (包括 3.3, 2.5,或者 1.8 V)■知识产权●支持Altera 宏功能和Altera MegaCore 功能,并且支持Altera合作伙伴计划(AMPPSM)宏功能, 具有广泛的可编程处理器,开芯片和关芯片的接口,强大的功能,DSP功能和通讯功能和协议。

访问的Altera IPMegaStore可以下载IP MegaCore功能●Nios II可编程处理器的支持Cyclone II 的一些快速接通型号具有较短的上电复位(POR)时间。

拥有快速接通特性的器件在订购码中用字母“A‖标出。

例如:EP2C5A, EP2C8A, EP2C15A, 和EP2C20A。

EP2C5A只能提供汽车速度级型。

EP2C8A 和EP2C20A只能提供工业级型。

EP2C15A只能提供快速接通型,并且可以提供商业型的和工业型的。

标注有‖A‖的cyclone II 器件和没有标注‖A‖的器件具有相同的特性和功能,唯一的不同就是它具有较短的上电复位时间。

表格1—1列出了cyclone II 系列器件的特性。

表格1—2列出了cyclone II器件的封装和用户I/O管脚数。

表1注释:1.EP2C15A只能提供快速接通型。

这个器件具有较短的上电复位(POR) 时间,并且可以提供商业型的和工业型的。

2、EP2C5,EP2C8的,EP2C20选择性地支持快速接通的特点,拥有这个特点的型号用‖A‖在订购码中用标注出来。

EP2C5A只能提供汽车速度级型。

EP2C8A 和 EP2C20A只能提供工业级型。

3. 这是18x18个乘法器总的所有乘法器。

每个器件的9x9乘法器的所有数量乘以2等于18x18乘法器的数量。

表1-2注释:(1)在相同的封装下cyclone II 设备支持直接替换(例如:你能够在用484-pin FineLine BGA封装的EP2C20器件和具有相同的封装的EP2C35和EP2C50器件之间替换。

(2)Quartus II 软件I/O管脚数包括额外的管脚,TDI, TDO, TMS, 和TCK,这些管脚被用为通用的I/O管脚。

(3)TQFP = 薄四方扁平封装(4)PQFP = 塑封四方扁平封装(5)EP2C5F256 和EP2C8F256器件支持直接替换。

不过,不是所有的单一数据选通(DQS)管脚和相关数据(DQ)管脚都是支持的。

用F256封装的EP2C5 和EP2C15器件就不支持直接替换。

(6)EP2C5, EP2C8, 和EP2C15A 器件的I/O管脚数包括8个专用时钟管脚,并且这8个管脚能够被用作数据输入引脚。

EP2C20, EP2C35, EP2C50, 和EP2C70 器件的I/O管脚数包括16个专用时钟管脚,并且这16个管脚能够被用作数据输入引脚。

(7)EP2C8A, EP2C15A, 和EP2C20A有快速接通的特性,有较短的上电复位的时间。

EP2C15A只能提供快速接通的型号。

(8)EP2C5选择性地支持快速接通的特点,拥有这个特点的型号用‖A‖在订购码中用标注出来。

EP2C5A只能提供汽车级型号。

参考cyclone II 的汽车级器件手册部分。

在相同的封装下cyclone II 设备支持直接替换(例如:你能够在用672-pin FineLine BGA 封装的EP2C35, EPC50 和EP2C70器件之间移动。

)cyclone II 系列支持的直接替换的例子在表格1-3中标注出来了。

直接替换的意思是你能够替换到某种器件上,这种器件的专门引脚,配置引脚和电源引脚在高密度器件中有着相同的封装。

表格1-3的注释:(1)EP2C5F256 到 EP2C15AF256和EP2C5F256 到 EP2C20F256器件不支持直接替换。

(2)当封装从EP2C20F484器件替换到EP2C50F484器件时,总共有39个I/O引脚的封装没有移动。

(3)当封装从EP2C35F672器件替换 EP2C70F672器件时,总共有56个I/O引脚的封装没有移动(4)除了没有移动的I/O引脚,有34个DQ信号引脚也没有移动。

(5)引脚484 FBGA和 484 UBGA是一样的。

为了确保你的电路板布局能够适应已封装的可移动密度,我们在quartus II软件环境下进行直接替换(选择Assignments 菜单,然后Device,然后点击Migration Devices按钮)。

编译之后,检查I/O, DQ, LVDS和其他引脚的信息清单,这些引脚因为选择的路径而不可用是。

表格1-3列出了cyclone II器件的封装和当封装从一个器件移动到另外一耳光器件的时不能移动的I/O引脚的数量。