TMS320F28335外部中断总结

DSP实验四、TMS320F28335 定时器 中断 IO中断 控制LED亮灭

继续我的第四个实验;实现定时器中断函数处理LD4翻转、按键IO中断控制LD3翻转;学习目的:中断寄存器的设置,IO中断、定时器中断的使用,F28335共有三个定时器:timer0、timer1、timer2(timer2也可用于DSP/BIOS);功能描述:上电默认LD3、LD4灭;初始化完成后,LD4以1HZ(1S)频率做状态翻转;LD3接受按键控制,每触发一次按键,状态翻转一次。

电路连接说明:LD4、LD3设置为通用GPIO 上拉输出初始化后默认为输出LED灯灭状态;LD4、LD3控制LED灯的负极,如下图;本次实验选用定时器0,程序时刻读取计数器的值,当值为0时,产生定时器0中断,LD4状态翻转;IO按键SW12中断控制LD3状态翻转。

定时器0中断程序设计说明:步骤一、定时器0的预定标寄存器和计数器设置:定时器输入时钟为sysclkout(=135MHz),1、如果定时1S(即1Hz)中断一次(即计数结束),1Hz=135Mhz/1350/100000预定标寄存器(即分频器)设为1350,计数器设为100000;2、如果定时1ms(即1000Hz)中断一次,计算公式为:1000Hz=135Mhz/1350/100预定标寄存器同样设为1350,计数器设为100;赋值语句如下://定时器0 设为1Hz = 135MHz/(1350*100000)CpuTimer0Regs.PRD.all= 100000;//计数周期寄存器,100000周期后计数器减为0CpuTimer0Regs.TPR.bit.TDDR= 1350& 0xFF;//0x546 预定标寄存器(预分频器)CpuTimer0Regs.TPRH.bit.TDDRH = (1350>>8) & 0x00FF;//0x546 预定标寄存器(预分频器)步骤二、a)设置定时器0相关中断寄存器使能定时器0中断,即CpuTimer0Regs.TCR.bit.TIE= 1; //使能定时器0中断b)设置PIE级相关中断寄存器定时器0中断所在PIE组使能,即PIEIERx寄存器设置c)设置CPU级中断相关寄存器CPU级使能上述PIE对应的通道,即IER寄存器设置步骤三、中断向量入口映射位置设置,如下:EALLOW; // This is needed to write to EALLOW protected registersPieVectTable.TINT0 = &cpu_timer0_isr; //将中断函数物理地址赋值给中断向量入口PieVectTable.XINT3 = &key_GPIO50_isr;EDIS; // This is needed to disable write to EALLOW protected registersIO中断程序设计说明:步骤一、设置IO引脚功能复用寄存器为普通IO、设为上拉、输入状态、使能引脚滤波功能;外部中断源选择寄存器设置:如GpioIntRegs.GPIOXINT3SEL.bit.GPIOSEL=50;//按键引脚编号设置步骤二、使能外部中断源中断;XIntruptRegs.XINT3CR.bit.ENABLE=1;//使能中断设置触发方式:XIntruptRegs.XINT3CR.bit.POLARITY=0;//下降沿触发剩余步骤同定时器0中断的设置。

单片机开发 F28335中断系统

2.2 使能/禁止复用外设中断的处理 应用外设中断的使能/禁止标志位使能/禁止外设中断,PIEIER

和CPU IER寄存器主要是在同一组中断内设置中断优先级。如果要 修改PIEIER寄存器的设置,有两种方法。第一种方法是保护相应的 PIE标志寄存器标志位,防止中断丢失。第二种方法是清除相应的 PIE寄存器的标志位。

(4)使能CPU中断及全局中断,这个通过对IER和EINT寄存器相应位设置进 行使能或者失能。比如外部中断1,其代码如下:

IER |= M_INT1; // 使能CPU中断1(INT1)

EINT;

// 开全局中断

(5)编写中断服务函数

配置好中断后如果有触发,即会进入中断服务函数,中断服务函数名在前 面已定义好,所以要保证一致,否则将不会进入中断服务函数内执行。在 DSP28335软件开发中,要在中断服务函数名前加上关键字interrupt。例如 外部中断1的中断服务函数:

F28335中断系统

本讲主要内容

1.中断介绍 2.中断操作 3.中断相关寄存器 4.中断配置

1.中断介绍

1.1 中断概念 中断其实就是当 CPU 执行程序时,由于发生了某种随机的事件

(外部或内部),引起 CPU 暂时中断正在运行的程序,转去执行一 段特殊的服务程序(中断服务子程序或中断处理程序),以处理该事 件,该事件处理完后又返回被中断的程序继续执行,这一过程就称 为中断,引发中断的称为中断源。

PieCtrlRegs.PIEIER1.bit.INTx4 = 1; // 使能PIE组1的INT4

(2)使能外设中断,这个具体是由外设相关中断使能位来控制, 比如外部中断1,这个可由外部中断1的控制寄存器中相应中断使能 位来控制。

XIntruptRegs.XINT1CR.bit.ENABLE= 1;

[原]TMS320F28335项目开发记录2_CCS与JTAG仿真器连接问题汇总

![[原]TMS320F28335项目开发记录2_CCS与JTAG仿真器连接问题汇总](https://img.taocdn.com/s3/m/528b71fc102de2bd960588cb.png)

[原]TMS320F28335项目开发记录2_CCS与JTAG仿真器连接问题汇总CCS与仿真器连接问题实际使用过程中,仿真器和CCS连接可能出现这样或那样的问题,也许你的连接很成功,没碰到过什么问题,但我的问题的确不少,可能与电脑配置有关吧,也可能与人品有关吧;下面的自己的一些错误和解决方法总结,不一定对,但也算是一种解决方法,分享给大家:问题:1. jtag连接不上,报错:The controller has detected a dead JTAG clock.The user must turn-on or connect the JTAG clock for the target.连接dm8147没有问题,连接dsp f28335出现此问题;通过不接仿真器测试发现jtag的复位引脚11脚持续的发出低电平,该脚输入WID信号,WID信号输入有问题;所以,还是硬件28335板子硬件上的问题;最后得出:芯片没有问题,是JTAG硬件电路或其他电路的问题;看门狗的复位是由于Flash中没有程序,而复位的低电平脉冲不是造成仿真器连接不了的直接原因;仿真器连接不了,大部分原因是因为JTAG电路的问题,也不排除28335、虚焊、上电顺序等问题;最后查出JTAG上的引脚(TCK、RTCK)有问题!2. The controller has detected a target power loss.The user must turn-on or connect the power supply for the target.看看板子有没有上电。

3. Device is held in reset. Take the device out of reset, and retry the operation.不明原因。

4. The requested TCLK PLL frequency option is invalid.The utility or debugger has requested a selection ofthe JTAG PLL frequency or clock source that is invalid.The value of USCIF.TCLK_FREQUENCY is probably bad.手工设置jtag频率为0后报错5. Failure due to the controller command-finish taking too long.重启ccs或板子看看,一般可以解决。

TMS320F28335外部中断总结

TMS320F28335外部中断总结作者:Free 文章来源:Free 点击数:93 更新时间:2010-8-26在这里我们要十分清楚DSP的中断系统。

C28XX一共有16个中断源,其中有2个不可屏蔽的中断RESET和NMI、定时器1和定时器2分别使用中断13和14。

这样还有12个中断都直接连接到外设中断扩展模块PIE上。

说的简单一点就是PIE 通过12根线与28335核的12个中断线相连。

而PIE的另外一侧有12*8根线分别连接到外设,如AD、SPI、EXINT等等。

这样PIE共管理12*8=96个外部中断。

这12组大中断由28335核的中断寄存器IER来控制,即IER确定每个中断到底属于哪一组大中断(如IER |= M_INT12;说明我们要用第12组的中断,但是第12组里面的什么中断CPU并不知道需要再由PIEIER确定)。

接下来再由PIE模块中的寄存器PIEIER中的低8确定该中断是这一组的第几个中断,这些配置都要告诉CPU(我们不难想象到PIEIER共有12总即从PIEIER1-PIEIER12)。

另外,PIE模块还有中断标志寄存器PIEIFR,同样它的低8位是来自外部中断的8个标志位,同样CPU的IFR寄存器是中断组的标志寄存器。

由此看来,CPU的所有中断寄存器控制12组的中断,PIE的所有中断寄存器控制每组内8个的中断。

除此之外,我们用到哪一个外部中断,相应的还有外部中断的寄存器,需要注意的就是外部中断的标志要自己通过软件来清零。

而PIE和CPU的中断标志寄存器由硬件来清零。

EALLOW; // This is needed to write to EALLOW protected registersPieVectTable.XINT2 = &ISRExint; //告诉中断入口地址EDIS; // This is needed to disable write to EALLOW protected registersPieCtrlRegs.PIECTRL.bit.ENPIE = 1; // Enable the PIE block使能PIE PieCtrlRegs.PIEIER1.bit.INTx5= 1; //使能第一组中的中断5IER |= M_INT1; // Enable CPU 第一组中断EINT; // Enable Global interrupt INTMERTM; // Enable Global realtime interrupt DBGM也就是说,12组中的每个中断都要完成上面的相同配置,剩下的才是去配置自己的中断。

DSPTMS320F28335---GPIO学习心得

DSPTMS320F28335---GPIO学习⼼得DSPTMS320F28335器件⽀持 88 个 GPIO 引脚。

GPIO 控制和数据寄存器被映射到外设帧 1 以在寄存器上启⽤ 32 位运⾏(连同 16 位运⾏)。

表 4-15显⽰了 GPIO 寄存器映射。

GPACTRL-------控制寄存器GPAQSEL1------限定器选择1寄存器GPAQSEL2-----限定器选择2寄存器GPAMUX1------复⽤1寄存器GPAMUX2------复⽤2寄存器GPAPUIR------⽅向寄存器GPAPUD-------上拉禁⽤寄存器GPIO模块配置步骤:步骤1。

计划的器件引脚:步骤2。

启⽤或禁⽤内部上拉电阻:步骤3。

选择输⼊的资格:步骤4。

选择引脚功能:步骤5。

数字通⽤I / O,选择⽅向的脚:步骤6。

选择低功耗模式唤醒步骤7。

选择外部中断源GPIO数据寄存器GPADAT 0x6FC0 2 GPIO A 数据寄存器(GPIO0 ⾄ 31)GPASET 0x6FC2 2 GPIO A 数据设定寄存器(GPIO0 ⾄ 31)GPACLEAR 0x6FC4 2 GPIO A 数据清除寄存器(GPIO0 ⾄ 31)GPATOGGLE 0x6FC6 2 GPIO A 数据切换寄存器(GPIO0 ⾄ 31)GPIO输⼊采样时间设置:如果SYSCLKOUT=150M,max=6.67ns min=3.4nsTI⽂档: TSM320X2833X System control and interrupt regerence guide ----- SPRUFBO0~87 共88个I/O端⼝,其中GPIO0~GPIO31可以配置成8个核⼼中断。

28335的GPIO⼝可以分为三组,分别为A⼝(GPIO0~GPIO31),B⼝(GPIO32~GPIO63)和C⼝(GPIO64~GPIO87)。

1 GPXCTRL (A,B) 设定采样频率2 GPXQSELX(A,B,1,2) 采样次数3 GPXDIR(A,B,C)数据⽅向设置4 GPXPUD 设置内部上拉与否貌似设置成上拉之后就会变成外设功能引脚5 GPXDAT 作为输出时:写⼊1 0 对应输出⾼低电平作为输⼊时:读⼊1 0 对应输⼊⾼低电平6 GPXSET 作为输出时:写⼊1会拉⾼引脚7 GPXCLEAR 作为输出时:写⼊1会拉低引脚8GPXTOGGLE 作为输出时:写⼊1会输出⽬前引脚状态相反的电平 1---0 0---19 GPIOXINTnSEL n=1~7 。

基于TMS320F28335外部中断配置过程

基于TMS320F28335外部中断配置过程TMS320F28335外部中断的配置关键void main(void){// Step 1. Initialize System Control:InitSysCtrl();// Step 3. Clear all interrupts and initialize PIE vector table: DINT; //禁止全局中断InitPieCtrl();//初始化PIE模块//清除CPU寄存器IER = 0x0000;IFR = 0x0000;//初始化中断服务表InitPieVectTable();//指向PIE向量。

表注意EALLOW和EDIS的使用,要不中间写的都无效的EALLOW; // This is needed to write to EALLOW protected registers PieVectTable.XINT1 = &xint1_isr;PieVectTable.XINT2 = &xint2_isr;EDIS; // This is needed to disable write to EALLOW protected registers // 清除计数Xint1Count = 0; // Count Xint1 interruptsXint2Count = 0; // Count XINT2 interruptsLoopCount = 0; // Count times through idle loop// Enable Xint1 and XINT2 in the PIE: Group 1 interrupt 4 & 5 // Enable int1 which is connected to WAKEINT:PieCtrlRegs.PIECTRL.bit.ENPIE = 1; // Enable the PIE blockPieCtrlRegs.PIEIER1.bit.INTx4 = 1; // Enable PIE Gropu 1 INT4PieCtrlRegs.PIEIER1.bit.INTx5 = 1; // Enable PIE Gropu 1 INT5 IER |= M_INT1; // Enable CPU int1EINT;//使能全局中断// Enable Global Interrupts//初始化GPIOEALLOW;GpioCtrlRegs.GPAMUX1.bit.GPIO15 = 0; // GPI15 修改GpioCtrlRegs.GPADIR.bit.GPIO15 = 0; // inputGpioCtrlRegs.GPAQSEL1.bit.GPIO15 = 0; // Xint1 Synch to SYSCLKOUT onlyGpioCtrlRegs.GPAMUX1.bit.GPIO1 = 0; // GPIO1GpioCtrlRegs.GPADIR.bit.GPIO1 = 0; // inputGpioCtrlRegs.GPAQSEL1.bit.GPIO1 = 2; // XINT2 Qual using 6 samplesGpioCtrlRegs.GPACTRL.bit.QUALPRD0 = 0xFF; // Each sampling window is510*SYSCLKOUTEDIS;//配置GPIO中断EALLOW;GpioIntRegs.GPIOXINT1SEL.bit.GPIOSEL = 15;//配置GPIO寄存器GPIOXINT1SEL把GPIO15作为Xint1中断GpioIntRegs.GPIOXINT2SEL.bit.GPIOSEL = 1; // XINT2 is GPIO1 //配置GPIO寄存器GPIOXINT2SEL把GPIO1作为Xint2中断EDIS;// Configure XINT1XIntruptRegs.XINT1CR.bit.POLARITY = 0; // Falling edge interrupt XIntruptRegs.XINT2CR.bit.POLARITY = 1; // Rising edge interrupt// Enable XINT1 and XINT2XIntruptRegs.XINT1CR.bit.ENABLE = 1; // Enable Xint1XIntruptRegs.XINT2CR.bit.ENABLE = 1; // Enable XINT2// Step 6. IDLE loop:for(;;){}}interrupt void xint1_isr(void){}interrupt void xint2_isr(void)}------------------------------------------------------------------------------------------------------------------------------------------ GpioDataRegs.GPBCLEAR.all = 0x4; // GPIO34 is low Xint2Count++; PieCtrlRegs.PIEACK.all = PIEACK_GROUP1; GpioDataRegs.GPBCLEAR.all = 0x4; // GPIO34 is low Xint1Count++;PieCtrlRegs.PIEACK.all = PIEACK_GROUP1;void InitPieCtrl(void){// Disable Interrupts at the CPU level:DINT;// Disable the PIEPieCtrlRegs.PIECTRL.bit.ENPIE = 0;}//---------------------------------------------------------------------------// EnableInterrupts: // Clear all PIEIFR registers: PieCtrlRegs.PIEIFR1.all = 0; PieCtrlRegs.PIEIFR2.all = 0; PieCtrlRegs.PIEIFR3.all = 0; PieCtrlRegs.PIEIFR4.all = 0; PieCtrlRegs.PIEIFR5.all = 0; PieCtrlRegs.PIEIFR6.all = 0; PieCtrlRegs.PIEIFR7.all = 0; PieCtrlRegs.PIEIFR8.all = 0; PieCtrlRegs.PIEIFR9.all = 0; PieCtrlRegs.PIEIFR10.all = 0; PieCtrlRegs.PIEIFR11.all = 0; PieCtrlRegs.PIEIFR12.all = 0; // Clear all PIEIER registers: PieCtrlRegs.PIEIER1.all = 0; PieCtrlRegs.PIEIER2.all = 0; PieCtrlRegs.PIEIER3.all = 0; PieCtrlRegs.PIEIER4.all = 0; PieCtrlRegs.PIEIER5.all = 0; PieCtrlRegs.PIEIER6.all = 0; PieCtrlRegs.PIEIER7.all = 0; PieCtrlRegs.PIEIER8.all = 0; PieCtrlRegs.PIEIER9.all = 0; PieCtrlRegs.PIEIER10.all = 0; PieCtrlRegs.PIEIER11.all = 0; PieCtrlRegs.PIEIER12.all = 0;//---------------------------------------------------------------------------// This function enables the PIE module and CPU interrupts//void EnableInterrupts(){// Enable the PIEPieCtrlRegs.PIECTRL.bit.ENPIE = 1;}const struct PIE_VECT_TABLE PieVectTableInit =PIE_RESERVED, // 0 Reserved spacePIE_RESERVED, // 1 Reserved spacePIE_RESERVED, // 2 Reserved spacePIE_RESERVED, // 3 Reserved spacePIE_RESERVED, // 4 Reserved spacePIE_RESERVED, // 5 Reserved spacePIE_RESERVED, // 6 Reserved spacePIE_RESERVED, // 7 Reserved spacePIE_RESERVED, // 8 Reserved spacePIE_RESERVED, // 9 Reserved spacePIE_RESERVED, // 10 Reserved spacePIE_RESERVED, // 11 Reserved spacePIE_RESERVED, // 12 Reserved space// Non-Peripheral InterruptsINT13_ISR, // XINT13 or CPU-Timer 1INT14_ISR, // CPU-Timer2DATALOG_ISR, // Datalogging interrupt // Enable Interrupts at the CPU level EINT; // Enables PIE to drive a pulse into the CPU PieCtrlRegs.PIEACK.all = 0xFFFF;RTOSINT_ISR, // RTOS interruptEMUINT_ISR, // Emulation interruptNMI_ISR, // Non-maskable interruptILLEGAL_ISR, // Illegal operation TRAPUSER1_ISR, // User Defined trap 1USER2_ISR, // User Defined trap 2USER3_ISR, // User Defined trap 3USER4_ISR, // User Defined trap 4USER5_ISR, // User Defined trap 5USER6_ISR, // User Defined trap 6USER7_ISR, // User Defined trap 7USER8_ISR, // User Defined trap 8USER9_ISR, // User Defined trap 9USER10_ISR, // User Defined trap 10USER11_ISR, // User Defined trap 11USER12_ISR, // User Defined trap 12// Group 1 PIE VectorsSEQ1INT_ISR, // 1.1 ADCSEQ2INT_ISR, // 1.2 ADCrsvd_ISR, // 1.3XINT1_ISR, // 1.4XINT2_ISR, // 1.5ADCINT_ISR, // 1.6 ADCTINT0_ISR, // 1.7 Timer 0WAKEINT_ISR, // 1.8 WD, Low Power// Group 2 PIE VectorsEPWM1_TZINT_ISR, // 2.1 EPWM-1 Trip ZoneEPWM2_TZINT_ISR, // 2.2 EPWM-2 Trip ZoneEPWM3_TZINT_ISR, // 2.3 EPWM-3 Trip ZoneEPWM4_TZINT_ISR, // 2.4 EPWM-4 Trip ZoneEPWM5_TZINT_ISR, // 2.5 EPWM-5 Trip ZoneEPWM6_TZINT_ISR, // 2.6 EPWM-6 Trip Zone rsvd_ISR, // 2.7 rsvd_ISR, // 2.8// Group 3 PIE VectorsEPWM1_INT_ISR, // 3.1 EPWM-1 InterruptEPWM2_INT_ISR, // 3.2 EPWM-2 InterruptEPWM3_INT_ISR, // 3.3 EPWM-3 InterruptEPWM4_INT_ISR, // 3.4 EPWM-4 InterruptEPWM5_INT_ISR, // 3.5 EPWM-5 InterruptEPWM6_INT_ISR, // 3.6 EPWM-6 Interruptrsvd_ISR, // 3.7rsvd_ISR, // 3.8// Group 4 PIE VectorsECAP1_INT_ISR, // 4.1 ECAP-1 ECAP2_INT_ISR, // 4.2 ECAP-2 ECAP3_INT_ISR, // 4.3 ECAP-3 ECAP4_INT_ISR, // 4.4 ECAP-4 ECAP5_INT_ISR, // 4.5 ECAP-5 ECAP6_INT_ISR, // 4.6 ECAP-6 rsvd_ISR, // 4.7rsvd_ISR, // 4.8// Group 5 PIE VectorsEQEP1_INT_ISR, // 5.1 EQEP-1 EQEP2_INT_ISR, // 5.2 EQEP-2 rsvd_ISR, // 5.3rsvd_ISR, // 5.4rsvd_ISR, // 5.5rsvd_ISR, // 5.6rsvd_ISR, // 5.7rsvd_ISR, // 5.8// Group 6 PIE VectorsSPIRXINTA_ISR, // 6.1 SPI-A SPITXINTA_ISR, // 6.2 SPI-A MRINTA_ISR, // 6.3 McBSP-A MXINTA_ISR, // 6.4 McBSP-A MRINTB_ISR, // 6.5 McBSP-B MXINTB_ISR, // 6.6 McBSP-Brsvd_ISR, // 6.7rsvd_ISR, // 6.8// Group 7 PIE VectorsDINTCH1_ISR, // 7.1 DMA channel 1DINTCH2_ISR, // 7.2 DMA channel 2 DINTCH3_ISR, // 7.3 DMA channel 3 DINTCH4_ISR, // 7.4 DMA channel 4 DINTCH5_ISR, // 7.5 DMA channel 5 DINTCH6_ISR, // 7.6 DMA channel 6 rsvd_ISR, // 7.7rsvd_ISR, // 7.8// Group 8 PIE VectorsI2CINT1A_ISR, // 8.1 I2CI2CINT2A_ISR, // 8.2 I2Crsvd_ISR, // 8.3rsvd_ISR, // 8.4SCIRXINTC_ISR, // 8.5 SCI-C SCITXINTC_ISR, // 8.6 SCI-Crsvd_ISR, // 8.7rsvd_ISR, // 8.8// Group 9 PIE VectorsSCIRXINTA_ISR, // 9.1 SCI-A SCITXINTA_ISR, // 9.2 SCI-A SCIRXINTB_ISR, // 9.3 SCI-B SCITXINTB_ISR, // 9.4 SCI-B ECAN0INTA_ISR, // 9.5 eCAN-A ECAN1INTA_ISR, // 9.6 eCAN-A ECAN0INTB_ISR, // 9.7 eCAN-B ECAN1INTB_ISR, // 9.8 eCAN-B// Group 10 PIE Vectorsrsvd_ISR, // 10.1rsvd_ISR, // 10.2rsvd_ISR, // 10.3rsvd_ISR, // 10.4rsvd_ISR, // 10.5rsvd_ISR, // 10.6rsvd_ISR, // 10.7rsvd_ISR, // 10.8// Group 11 PIE Vectorsrsvd_ISR, // 11.1rsvd_ISR, // 11.2rsvd_ISR, // 11.3rsvd_ISR, // 11.4rsvd_ISR, // 11.5rsvd_ISR, // 11.6rsvd_ISR, // 11.7rsvd_ISR, // 11.8// Group 12 PIE VectorsXINT3_ISR, // 12.1XINT4_ISR, // 12.2XINT5_ISR, // 12.3XINT6_ISR, // 12.4XINT7_ISR, // 12.5rsvd_ISR, // 12.6LVF_ISR, // 12.7LUF_ISR, // 12.8};//---------------------------------------------------------------------------// InitPieVectTable://---------------------------------------------------------------------------// This function initializes the PIE vector table to a known state. // This function must be executed after boot time.//void InitPieVectTable(void){} // Enable the PIE Vector Table PieCtrlRegs.PIECTRL.bit.ENPIE = 1; int16 i; Uint32 *Source = (void *) &PieVectTableInit; Uint32 *Dest = (void *) &PieVectTable; EALLOW; for(i=0; i < 128; i++) *Dest++ = *Source++; EDIS;。

TMS320F28335经验若干要点

TMS320F28335经验若干要点TMS320F28335开发过程中常见问题总结1.SPI驱动TLE7241E出现返回值不对的问题。

主要是由于时序的不对,导致TLE7241E输入采样时数据还没有建立,所以TLE7241E 收到的命令不正确,所以返回值不正确。

2.SPI驱动EEPROM时,如果用金属物触到clock pin时,能正确运行,否则不能正确运行。

出现次问题也是由于时序的问题,金属物触到clock导致clock出现微小幅度的偏移,导致正好和eeprom 的时序对上,而不用金属物触碰时时序不正常,当使dsp MOSIpin数据发送提前半个周期后,eeprom工作正常。

3.示波器有时会导致显示的波形被消尖,所以用示波器测量时周期不能太大。

TMS320F28335笔记-I2C1.响应和非响应的区别是什么?关于i2c的响应问题:对于每一个接收设备(从设备,slaver),当它被寻址后,都要求在接收到每一个字节后产生一个响应。

因此,the master device 必须产生一个额外的时钟脉冲(第九个脉冲)用以和这个响应位相关联。

在这个脉冲期间,发出响应的从设备必须将SDA拉低并在时钟脉冲的高电平期间保持住。

这表示该设备给出了一个ACK。

如果它不拉低SDA 线,就表示不响应(NACK)。

另外,在从机(发送方)发送完最后一个字节后主设备(接收方)必须产生一个不响应位,用以通知从机(发送方)不要再发送信息了,这样从机就知道该将SDA释放了,而后,主机发出一个停止位给slaver。

总结下,i2c通讯中,SDA 和SCL 都是有主机控制的,从设备只是能够将SDA线拉低而已。

对于SCL线,从机是没有任何能力去控制的。

从机只能被动跟随SCL再说的清楚些:主机发送数据到从机的状态下:主机控制SCL信号线和SDA信号线,从机只是在SCL线为高的时候去被动读取SDA 线。

主机读取从机的数据:主机来发出时钟信号,从机只是保证在时钟信号为高电平的时候的SDA的状态而已。

DSPF28335---中断系统

DSPF28335---中断系统28335的中断系统中断概述通过硬件或软件驱动的信号,使CPU将当前的程序挂起,执行另一个称为中断服务子程序称为中断。

28335内部有16根中断线,其中有两个不可屏蔽中断(RESET、NMI)与16个可屏蔽中断(INT1-14、RTOSINT、DLOGINT),这里主要说明INT1-14。

在28335中,CPU定时器1、2一般预留给实时操作系统使用,中断线单独分配给INT13、INT14。

其余12个可屏蔽中断直接连接在外设中断扩展模块PIE上,供外部中断和处理器内部单元使用。

这就有一个问题,28335内部有很多个外设模块,这些外设都有自己的中断而且有很多个,那么剩余12个中断怎么够用。

为了解决这个问题所有引入PIE模块。

PIE通过12根线与28335核的12个中断线相连。

而PIE的另外一侧有12*8=96根线分别连接到外设,如AD、SPI、EXINT等等。

说明:PIE和CPU的中断标志寄存器由硬件来清零;但外部中断的标志位要通过软件来清零。

一.三级中断1.外设级中断如果有外设产生中断事件,则寄存器中相应的中断标志位被置一,如果相应的中断使能为(IE)被置位,那么外设就像PIE发出一个中断请求。

如果外设使能位没有被置位,那么中断标志(IF)位将保持为1直到软件清除。

2.PIE中断对于复用的中断源,PIE模块有相应的标志寄存器[PIEIFR(x,y) x=1-12,y=1-8]和中断使能寄存器PIEIER(x,y) ;对于每一个PIE中断组来说还有一个中断应答寄存器PIEACKx。

当有中断请求进入PIE模块的时候,如果相应的PIE中断标志位PIEIFR(x.y)和中断使能寄存器PIEIER(x,y)置1;这是PIE控制器就会检查PIEACKx标志位看CPU是否已经准备好接收这个PIE中断组的中断。

明:如果PIEACKZx被清零,PIE会把这个中断请求送到CPU级的INTx。

[DSP编程] TMS320F28335开发总结

![[DSP编程] TMS320F28335开发总结](https://img.taocdn.com/s3/m/3a78158b83d049649b66587d.png)

TMS320F28335开发总结1.如何查看CCS5.2中包含的源文件有哪些?以及他们的位置?CCS5.2工程中C语言源文件有两部分组成,一部分是在project路径下的.c文件,另外一部分是通过连接添加到工程里的(.project文件中的<linkedResources></linkedResources>字段)。

因此CCS5.2中的源文件一部分在工程目录下,另外一部分在.project文件中的<linkedResources></linkedResources>字段包含的路径下。

S中GEL文件的作用是什么?ccs的gel语言是一种交互式的命令,它是解释执行的,即不能被编译成可执行文件。

它的作用在于扩展了ccsstudio的功能,可以用gel来调用一些菜单命令,对DSP的存储器进行配置等等。

但是作者建议对于使用仿真器和DSP功能板的仿真环境用户来说,这种GEL语言文件是没必要加入到配置中的。

gel语言的重要性在于针对计算机模拟环境的用户,使用gel可以为其准备一个虚拟的DSP仿真环境,但也不是非用不可的。

3.引用例子中的源文件时要注意什么?使用CCS5.2导入例子中的源文件时,最好不要选择连接方式,而使用复制的方式,这样必要时可以更改这些源文件,而不会影响其他的程序的使用。

S5.2如果没有包含函数的声名头文件时也能运行但是结果会不正常,故当函数调用出现莫名其妙的问题时,要检查声名函数的头文件是否包含。

S5.2开发DSP28335程序时如何设置程序堆栈的大小?CCS5.2默认情况下堆栈的大小都为0x400,在Project->Properties->Build->C200 Linker->Basic Options下设置。

设置完堆栈的大小后,还要在cmd文件中分配堆栈存储空间的段的位置和大小,栈空间的段名为.stack用于函数中的临时变量,堆空间的段名为.sysmem用于c语言malloc函数分配内存,malloc最大可分配内存为Project->Properties->Build->C200 Linker->Basic Options下设置的大小减2。

19_TMS320F28335之中断系统(包你明白)

TMS320F28335项目开发记录9_28335之中断系统1.中断系统在这里我们要十分清楚DSP的中断系统。

C28XX一共有16个中断源,其中有2个不可屏蔽的中断RESET和NMI、定时器1和定时器2分别使用中断13和14。

这样还有12个中断都直接连接到外设中断扩展模块PIE上。

说的简单一点就是PIE通过12根线与28335核的12个中断线相连。

而PIE的另外一侧有12*8根线分别连接到外设,如AD、SPI、EXINT等等。

PIE共管理12*8=96个外部中断。

这12组大中断由28335核的中断寄存器IER来控制,即IER确定每个中断到底属于哪一组大中断(如IER |= M_INT12; 说明我们要用第12组的中断,但是第12组里面的什么中断CPU并不知道需要再由PIEIER确定)。

接下来再由PIE模块中的寄存器PIEIER中的低8确定该中断是这一组的第几个中断,这些配置都要告诉CPU (我们不难想象到PIEIER共有12总即从PIEIER1-PIEIER12)。

另外,PIE模块还有中断标志寄存器PIEIFR,同样它的低8位是来自外部中断的8个标志位,同样CPU的IFR寄存器是中断组的标志寄存器。

由此看来,CPU的所有中断寄存器控制12组的中断,PIE的所有中断寄存器控制每组内8个的中断。

除此之外,我们用到哪一个外部中断,相应的还有外部中断的寄存器,需要注意的就是外部中断的标志要自己通过软件来清零。

而PIE和CPU的中断标志寄存器由硬件来清零。

1. EALLOW; // This is needed to write to EALLOW protected registers2. PieVectTable.XINT2 = &ISRExint; //告诉中断入口地址3. EDIS; // This is needed to disable write to EALLOW protected registers4. PieCtrlRegs.PIECTRL.bit.ENPIE = 1; // Enable the PIE block使能PIE5. PieCtrlRegs.PIEIER1.bit.INTx5= 1; //使能第一组中的中断56. IER |= M_INT1; // Enable CPU 第一组中断7. EINT; // Enable Global interrupt INTM8. ERTM; // Enable Global realtime interrupt DBGM也就是说,12组中的每个中断都要完成上面的相同配置,剩下的才是去配置自己的中断。

DSP实验五、TMS320F28335-串口通信实验

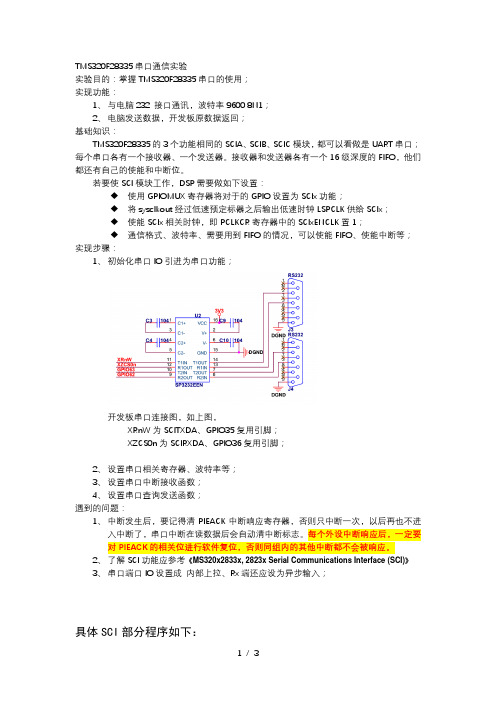

TMS320F28335串口通信实验实验目的:掌握TMS320F28335串口的使用;实现功能:1、与电脑232 接口通讯,波特率9600 8N1;2、电脑发送数据,开发板原数据返回;基础知识:TMS320F28335的3个功能相同的SCIA、SCIB、SCIC模块,都可以看做是UART串口;每个串口各有一个接收器、一个发送器。

接收器和发送器各有一个16级深度的FIFO,他们都还有自己的使能和中断位。

若要使SCI模块工作,DSP需要做如下设置:◆使用GPIOMUX寄存器将对于的GPIO设置为SCIx功能;◆将sysclkout经过低速预定标器之后输出低速时钟LSPCLK供给SCIx;◆使能SCIx相关时钟,即PCLKCR寄存器中的SCIxENCLK置1;◆通信格式、波特率、需要用到FIFO的情况,可以使能FIFO、使能中断等;实现步骤:1、初始化串口IO引进为串口功能;开发板串口连接图,如上图,XRnW为SCITXDA、GPIO35复用引脚;XZCS0n为SCIRXDA、GPIO36复用引脚;2、设置串口相关寄存器、波特率等;3、设置串口中断接收函数;4、设置串口查询发送函数;遇到的问题:1、中断发生后,要记得清PIEACK中断响应寄存器,否则只中断一次,以后再也不进入中断了,串口中断在读数据后会自动清中断标志。

每个外设中断响应后,一定要对PIEACK的相关位进行软件复位,否则同组内的其他中断都不会被响应。

2、了解SCI功能应参考《MS320x2833x, 2823x Serial Communications Interface (SCI)》3、串口端口IO设置成内部上拉、Rx端还应设为异步输入;具体SCI部分程序如下:/** ======= sci_uart ========*** Created on: 2017年9月19日* Author: liu*/#include"DSP2833x_Device.h"// DSP2833x Header File#include"DSP2833x_Examples.h"// DSP2833x Examples Include File#include"sci_uart.h"__interrupt void sciaRxIsr(void);/** ======== sci_uart_init ========*/void SCIA_uart_init(void){//GPIO35、36复用功能选择EALLOW;GpioCtrlRegs.GPBMUX1.bit.GPIO35 = 1 ; //SCIA_TXDAGpioCtrlRegs.GPBMUX1.bit.GPIO36 = 1 ; //SCIA_RXDAGpioCtrlRegs.GPBPUD.bit.GPIO35 = 0; // Enable pull-up for GPIO29 (SCITXDA)GpioCtrlRegs.GPBPUD.bit.GPIO36 = 0; // Enable pull-up for GPIO28 (SCIRXDA)//定义管脚为异步输入GpioCtrlRegs.GPBDIR.bit.GPIO36 = 0 ;//输入GpioCtrlRegs.GPBQSEL1.bit.GPIO36 = 3;//异步输入EDIS;//基本通信参数设置// Note: Clocks were turned on to the SCIA peripheral// in the InitSysCtrl() functionSciaRegs.SCICCR.all =0x0007; // 1 stop bit, No loopback// No parity,8 char bits,// async mode, idle-line protocolSciaRegs.SCICTL1.all =0x0003; // enable TX, RX, internal SCICLK,// Disable RX ERR, SLEEP, TXWAKESciaRegs.SCICTL2.all =0x0003;SciaRegs.SCICTL2.bit.TXINTENA =0; //查询发送SciaRegs.SCICTL2.bit.RXBKINTENA =1;//中断接收SciaRegs.SCIHBAUD=488>>8;// 9600 135MHz@LSPCLK = 33.75MHz /(9600*8)-1=4394 150MHz@LSPCLK = 37.5MHz /(9600*8)-1=488SciaRegs.SCILBAUD=488;SciaRegs.SCICTL1.all =0x0023; // Relinquish SCI from Reset// Initialize the SCI FIFO 禁止FIFO功能SciaRegs.SCIFFTX.bit.SCIFFENA = 0 ; //禁止SCI FIFO功能EALLOW;// This is needed to write to EALLOW protected registersPieVectTable.SCIRXINTA = &sciaRxIsr;EDIS;// This is needed to disable write to EALLOW protected registersPieCtrlRegs.PIEIER9.bit.INTx1=1;// PIE Group 9, int1IER |= M_INT9;// Enable CPU INTEINT;}void SCIA_UART_Send_Byte( unsigned char Dat){while(SciaRegs.SCICTL2.bit.TXRDY !=1);//等待SCIRXBUF准备好才写入下一个所要发送的数据SciaRegs.SCITXBUF = Dat;}//SCIA串口中断接收处理函数__interrupt void sciaRxIsr(void){if(SciaRegs.SCIRXST.bit.RXRDY == 1){SCIA_UART_Send_Byte( SciaRegs.SCIRXBUF.bit.RXDT );}PieCtrlRegs.PIEACK.all=PIEACK_GROUP9;}。

25_TI DSP入门芯片TMS320F28335

作为一个电子硬件工程师,怎么不能懂DSP,或者我们中有一些同学对DSP的理解还不是很多,今天就让我们给大家介绍一个DSP的入门芯片,来自TI的TMS320F28335。

相信看过了这一系列的内容,大家会对DSP有初步的了解。

TMS320F28335简介:TMS320F28335采用176引脚LQFP四边形封装,其功能结构参见参考文献。

其主要性能如下:高性能的静态CMOS技术,指令周期为6.67 ns,主频达150 MHz;高性能的32位CPU,单精度浮点运算单元(FPU),采用哈佛流水线结构,能够快速执行中断响应,并具有统一的内存管理模式,可用C/C++语言实现复杂的数学算法;6通道的DMA控制器;片上256 Kxl6的Flash存储器,34 Kxl6的SARAM存储器.1 Kx16 OTPROM和8 Kxl6的Boot ROM。

其中Flash,OTPROM,16 Kxl6的SARAM均受密码保护;控制时钟系统具有片上振荡器,看门狗模块,支持动态PLL调节,内部可编程锁相环,通过软件设置相应寄存器的值改变CPU的输入时钟频率;8个外部中断,相对TMS320F281X系列的DSP,无专门的中断引脚。

GPI00~GPI063连接到该中断。

GPI00一GPI031连接到XINTl,XINT2及XNMI外部中断,GPl032~GPI063连接到XINT3一XINT7外部中断;支持58个外设中断的外设中断扩展控制器(PIE),管理片上外设和外部引脚引起的中断请求;增强型的外设模块:18个PWM输出,包含6个高分辨率脉宽调制模块(HRPWM)、6个事件捕获输入,2通道的正交调制模块(QEP);3个32位的定时器,定时器0和定时器1用作一般的定时器,定时器0接到PIE模块,定时器1接到中断INTl3;定时器2用于DSP/BIOS的片上实时系统,连接到中断INTl4,如果系统不使用DSP/BIOS,定时器2可用于一般定时器;串行外设为2通道CAN模块、3通道SCI模块、2个McBSP(多通道缓冲串行接口)模块、1个SPI模块、1个I2C主从兼容的串行总线接口模块;12位的A/D转换器具有16个转换通道、2个采样保持器、内外部参考电压,转换速度为80 ns,同时支持多通道转换;88个可编程的复用GPIO引脚;低功耗模式;1.9 V内核,3.3 V I/O供电;符合IEEEll49.1标准的片内扫描仿真接口(JTAG);TMS320F28335的存储器映射需注意以下几点:片上外设寄存器块0~3只能用于数据存储区,用户不能在该存储区内写入程序。

TMS320F28335中文资料汇总

F2812与F28335的区别最大的区别就是28335是浮点的,而2812是定点的。

F2812主要指标150M H z/E M I F/128K BF l a s h/36K BR A M/G P I O56路/M c B S P/176-p i n P a c k a g e F28335主要指标300M F L O P S/独立D M A/512K BF l a s h/68K BR A M/32-b i t E M I/G P I O88路还有一点28335将2812的E V分解成了相互独立的e p w m,e c a p,e q三个模块互相之间互不干扰,因此可以比较方便地实现复杂的信号输出。

尤其是e p w m相对于E V中的p w m 输出功能,有了很大的提高。

F28335比F2812多了一个M A C单元,也就是速度增加了一倍。

F28335是带浮点运算的,动态范围更大。

F2833x的执行速度,比相同时钟频率的F28x x系列定点芯片,快50%。

处理数学运算性能提升2.45倍,控制算法性能提升1.57倍,D S P性能提升1.38倍。

总体性能提升近2倍。

TMS320F28335的ADCT M S320F28335上有16通道、12位的模数转换器A D C。

他可以被配置为两个独立的8通道输入模式,也可以通过配置A d c R e g s.A D C T R L1.b i t.S E Q_C A S C=1,将其设置为一个16通道的级联输入模式。

输入的方式可以通过配置A d c R e g s.A D C T R L1.b i t.A C Q_P S=1,将其设置为顺序采集。

即从低通道开始到高通道结束。

值得注意的是片上A D C的输入电压范围为0--3V,一旦超过3V,片上的A D C 模块将会被烧掉。

T I上的D A T A S H E E T介绍其A D C的精度可达到12位,实际上达到不了。

DSP实验四、TMS320F28335 定时器 中断 IO中断 控制LED亮灭

继续我的第四个实验;实现定时器中断函数处理LD4翻转、按键IO中断控制LD3翻转;学习目的:中断寄存器的设置,IO中断、定时器中断的使用,F28335共有三个定时器:timer0、timer1、timer2(timer2也可用于DSP/BIOS);功能描述:上电默认LD3、LD4灭;初始化完成后,LD4以1HZ(1S)频率做状态翻转;LD3接受按键控制,每触发一次按键,状态翻转一次。

电路连接说明:LD4、LD3设置为通用GPIO 上拉输出初始化后默认为输出LED灯灭状态;LD4、LD3控制LED灯的负极,如下图;本次实验选用定时器0,程序时刻读取计数器的值,当值为0时,产生定时器0中断,LD4状态翻转;IO按键SW12中断控制LD3状态翻转。

定时器0中断程序设计说明:步骤一、定时器0的预定标寄存器和计数器设置:定时器输入时钟为sysclkout(=135MHz),1、如果定时1S(即1Hz)中断一次(即计数结束),1Hz=135Mhz/1350/100000预定标寄存器(即分频器)设为1350,计数器设为100000;2、如果定时1ms(即1000Hz)中断一次,计算公式为:1000Hz=135Mhz/1350/100预定标寄存器同样设为1350,计数器设为100;赋值语句如下://定时器0 设为1Hz = 135MHz/(1350*100000)CpuTimer0Regs.PRD.all= 100000;//计数周期寄存器,100000周期后计数器减为0CpuTimer0Regs.TPR.bit.TDDR= 1350& 0xFF;//0x546 预定标寄存器(预分频器)CpuTimer0Regs.TPRH.bit.TDDRH = (1350>>8) & 0x00FF;//0x546 预定标寄存器(预分频器)步骤二、a)设置定时器0相关中断寄存器使能定时器0中断,即CpuTimer0Regs.TCR.bit.TIE= 1; //使能定时器0中断b)设置PIE级相关中断寄存器定时器0中断所在PIE组使能,即PIEIERx寄存器设置c)设置CPU级中断相关寄存器CPU级使能上述PIE对应的通道,即IER寄存器设置步骤三、中断向量入口映射位置设置,如下:EALLOW; // This is needed to write to EALLOW protected registersPieVectTable.TINT0 = &cpu_timer0_isr; //将中断函数物理地址赋值给中断向量入口PieVectTable.XINT3 = &key_GPIO50_isr;EDIS; // This is needed to disable write to EALLOW protected registersIO中断程序设计说明:步骤一、设置IO引脚功能复用寄存器为普通IO、设为上拉、输入状态、使能引脚滤波功能;外部中断源选择寄存器设置:如GpioIntRegs.GPIOXINT3SEL.bit.GPIOSEL=50;//按键引脚编号设置步骤二、使能外部中断源中断;XIntruptRegs.XINT3CR.bit.ENABLE=1;//使能中断设置触发方式:XIntruptRegs.XINT3CR.bit.POLARITY=0;//下降沿触发剩余步骤同定时器0中断的设置。

(完整)[原]TMS320F28335项目开发记录2_CCS与JTAG仿真器连接问题汇总,推荐文档

![(完整)[原]TMS320F28335项目开发记录2_CCS与JTAG仿真器连接问题汇总,推荐文档](https://img.taocdn.com/s3/m/8189e4fb4b73f242326c5fcd.png)

6. (Error -233 @ 0x0) The JTAG IR and DR scan-paths cannot circulate bits, they may be broken. An attempt to scan the JTAG scan-path has failed. The target's JTAG scan-path appears to be broken with a stuck-at-ones or stuck-at-zero fault. (Emulation package 5.0.747.0) 重启 ccs、重启板子、重启电脑都可以试试看,一般可以解决。 最后本人实在不行换了一根仿真器的线就可以了,很奇怪的错误。

2. The controller has detected a target power loss. The user must turn-on or connect the power supply for the target. 看看板子有没有上电。

3. Device is held in reset. Take the device out of reset, and retry the operation. 不明原因。。。

我当时碰到的两个问题: 如果在 X1、X2 引脚上引入晶振,XCLKIN 引脚需要接地!XCLKOUT 引脚悬空即可! TCK、RTCK 应该正确的接到 28335 的 TCK 引脚! JTAG 电路与 28335 连接示

“

”

At the end, Xiao Bian gives you a passage. Minand once said, "people who learn to learn are very happy people.". In every wonderful life, learning is an eternal theme. As a professional clerical and teaching position, I understand the importance of continuous learning, "life is diligent, nothing can be gained", only continuous learning can achieve better self. Only by constantly learning and mastering the latest relevant knowledge, can employees from all walks of life keep up with the pace of enterprise development and innovate to meet the needs of the market. This document is also edited by my studio professionals, there may be errors in the document, if there are errors, please correct, thank you!

TMS320F28335 外部中断分析与研究

【作者简介】鲁昕曈(2000-),女,河南新乡人,本科在读,从事通信工程研究。

1研究背景1.1DSP 的发展历史数字信号处理DSP 是如今的一门新兴学科,其发展经历了3个主要阶段。

最初数字信号处理只能依靠微处理器完成,但是微处理器的处理速度较为缓慢,不能满足当时大容量信息的需求。

随着大规模集成电路和半导体技术的发展,1982年第一代DSP 芯片TMS32010问世,它采用了NMOS 技术,速度比微处理器快数十倍,在语言合成等领域得到了广泛的使用,后来随着基于CMOS 制作的DSP 芯片的出现,存储容量也得到了进一步的改善,能够在图像硬件处理中占据一席之地。

20世纪90年代,第三、四、五代DSP 芯片的发明使运算速度又提高了许多。

其中第五代的集成度较高,因此逐渐渗入人们的生活、学习和工作当中,成为电子器件更迭的关键。

1.2DSP 的发展情况在数字化时代中,DSP 己成为电子信息、通信交流器件等方面的基石。

TMS320F28335是TI 公司研发的一个32位浮点数字控制处理器,它的外形丰富,设计多样化,性价比高。

该芯片具有丰富的系统资源,时钟控制灵活,提供了多种低功耗模式;有56个通用I/O 引脚可以复用,功能丰富;独特的寄存器保护模式可确保程序稳定地运行;PIE 中断扩展控制器能够增强芯片的中断处理能力。

故本文主要对TMS320F28335芯片的外部中断进行详细的介绍、分析与研究。

2DSP 中断概述CPU 在正常执行程序时,有时会接受实时性要求更高或者更高级别的指令,就需要中断现有的程序而去响应其他请求,进入中断服务程序;当执行完该程序时能够返回原有的程序继续执行,该过程就是中断响应机制。

中断的主要功能有:①实现CPU 与外部设备的速度配合;②实时控制;③出现故障时及时发现并处理;④实现人机互联。

3中断系统简介3.1中断源当某种软件或硬件事件发生时,计算机暂时停止当前的程序,而去执行另一个程序,处理完毕后又返回原程序继续执行。

DSP28335的调试总结,这是一份总结很全面的资料,我在学

DSP28335的调试总结,这是一份总结很全面的资料,我在学习开发板的一些总结,希望能得到同行的帮助,愿与大家一起学习和分享1DSP的PWM信号1.1简介DSP28335共12路16位的ePWM,能进行频率和占空比控制。

ePWM的时钟TBCLK=SYSCLKOUT/(HSPCLKDIV×CLKDIV):PWM信号频率由时基周期寄存器TBPDR和时基计数器的计数模式决定。

初始化程序采用的计数模式为递增计数模式。

在递增计数模式下,时基计数器从零开始增加,直到达到周期寄存器值(TBPDR)。

然后时基计数器复位到零,再次开始增加。

PWM信号周期与频率的计算如下:1.2端口对应关系通道相应PWM的A/B对应JP0B端口号1ePWM1A92ePWM1B103ePWM2A114ePWM2B125ePWM3A136ePWM3B147ePWM4A158ePWM4B169ePWM5A1710ePWM5B1811ePWM6A1912ePWM6B20说明:JP0B的端口号按“Z”字形顺序数。

1.3初始化程序注释void InitPwm1AB(float32f){Uint16T= 2343750/f-1.0;//系统时钟SYSCLKOUT=150MHz,TBCLK=6.6666667ns,在连续增计数模式下,f=150000000/(TBPDR+1) EALLOW;//先初始化通用输入输出口//GpioCtrlRegs.GPAPUD.bit.GPIO0 = 0;GpioCtrlRegs.GPAMUX1.bit.GPIO0 = 1;GpioCtrlRegs.GPAPUD.bit.GPIO1 = 0;GpioCtrlRegs.GPAMUX1.bit.GPIO1 = 1;EPwm1Regs.TBPHS.half.TBPHS= 0; // 在相位寄存器中设置计数器的起始计数位置//下面两条语句组合对PWM的时钟进行分频EPwm1Regs.TBCTL.bit.CLKDIV = 6;EPwm1Regs.TBCTL.bit.HSPCLKDIV = 0;EPwm1Regs.TBPRD = T; //在周期寄存器中设置计数器的计数周期//TBCTL为定时器控制寄存器EPwm1Regs.TBCTL.bit.CTRMODE= TB_COUNT_UP; //设置计数模式位为连续增计数模式,产生对称方波EPwm1Regs.TBCTL.bit.PHSEN = TB_DISABLE; // 将定时器相位使能位关闭EPwm1Regs.TBCTL.bit.PRDLD = TB_SHADOW;//映射寄存器SHADOW使能并配置映射寄存器为自动读写EPwm1Regs.TBCTL.bit.SYNCOSEL = TB_CTR_ZERO; // 定时器时钟源选择,一共有四种时钟源EPwm1Regs.CMPA.half.CMPA= 0.0001*T;// 设置EPWM1A比较值寄存器的比较值,即体现EPWM1A的占空比EPwm1Regs.CMPB= 0.0001*T;EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;//A模块比较模式EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;//B模块比较模式EPwm1Regs.CMPCTL.bit.LOADAMODE= CC_CTR_ZERO; // A模块比较使能,通过写0来清除SHDWAMODE位来使能load on CTR=ZeroEPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO; // B模块比较使能,通过写0来清除SHDWBMODE位来使能load on CTR=Zero//AQCTLA为输出A比较方式控制寄存器EPwm1Regs.AQCTLA.bit.ZRO = AQ_SET; // TBCTR(计数器)计到零时使输出为反向EPwm1Regs.AQCTLA.bit.CAU = AQ_CLEAR;//TBCTR(计数器)与CMPA在up 计数时相等使输出为high,这关系的输出的占空比EPwm1Regs.AQCTLB.bit.ZRO = AQ_SET;EPwm1Regs.AQCTLB.bit.CBU = AQ_CLEAR;EDIS;}2DSP的CAN通信2.1CAN2.0B协议简述TMS320F28335上有2个增强型CAN总线控制器,符合CAN2.0B协议,其总线波特率可达到1Mbps。

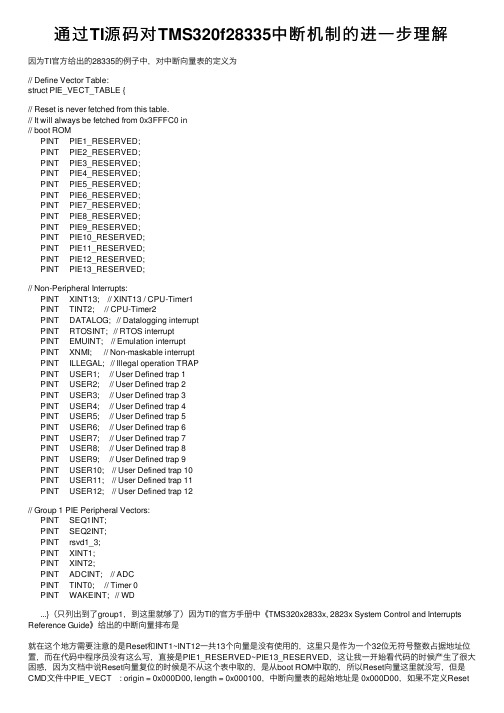

通过TI源码对TMS320f28335中断机制的进一步理解

通过TI源码对TMS320f28335中断机制的进⼀步理解因为TI官⽅给出的28335的例⼦中,对中断向量表的定义为// Define Vector Table:struct PIE_VECT_TABLE {// Reset is never fetched from this table.// It will always be fetched from 0x3FFFC0 in// boot ROMPINT PIE1_RESERVED;PINT PIE2_RESERVED;PINT PIE3_RESERVED;PINT PIE4_RESERVED;PINT PIE5_RESERVED;PINT PIE6_RESERVED;PINT PIE7_RESERVED;PINT PIE8_RESERVED;PINT PIE9_RESERVED;PINT PIE10_RESERVED;PINT PIE11_RESERVED;PINT PIE12_RESERVED;PINT PIE13_RESERVED;// Non-Peripheral Interrupts:PINT XINT13; // XINT13 / CPU-Timer1PINT TINT2; // CPU-Timer2PINT DATALOG; // Datalogging interruptPINT RTOSINT; // RTOS interruptPINT EMUINT; // Emulation interruptPINT XNMI; // Non-maskable interruptPINT ILLEGAL; // Illegal operation TRAPPINT USER1; // User Defined trap 1PINT USER2; // User Defined trap 2PINT USER3; // User Defined trap 3PINT USER4; // User Defined trap 4PINT USER5; // User Defined trap 5PINT USER6; // User Defined trap 6PINT USER7; // User Defined trap 7PINT USER8; // User Defined trap 8PINT USER9; // User Defined trap 9PINT USER10; // User Defined trap 10PINT USER11; // User Defined trap 11PINT USER12; // User Defined trap 12// Group 1 PIE Peripheral Vectors:PINT SEQ1INT;PINT SEQ2INT;PINT rsvd1_3;PINT XINT1;PINT XINT2;PINT ADCINT; // ADCPINT TINT0; // Timer 0PINT WAKEINT; // WD...}(只列出到了group1,到这⾥就够了)因为TI的官⽅⼿册中《TMS320x2833x, 2823x System Control and Interrupts Reference Guide》给出的中断向量排布是就在这个地⽅需要注意的是Reset和INT1~INT12⼀共13个向量是没有使⽤的,这⾥只是作为⼀个32位⽆符号整数占据地址位置,⽽在代码中程序员没有这么写,直接是PIE1_RESERVED~PIE13_RESERVED,这让我⼀开始看代码的时候产⽣了很⼤困惑,因为⽂档中说Reset向量复位的时候是不从这个表中取的,是从boot ROM中取的,所以Reset向量这⾥就没写,但是CMD⽂件中PIE_VECT : origin = 0x000D00, length = 0x000100,中断向量表的起始地址是 0x000D00,如果不定义Reset向量,那所有后⾯的向量不就向前⾯移动了两个地址,后来我为了地址对应就在向量表定义中加⼊了⼀⾏ PINTReset_RESERVED,结果编译报错,好像是CMD中分配的地址重叠了,因为多加了⼀项,我就把向量表中的最后⼀项注释掉了(group12的最后⼀项),编译过了,但是发现进不了指定中断(我这⾥⽤的是TI例程中看门狗中断的例⼦),只能进⼊中断向量表初始化时指定的默认中断(就是⼀个NOP空操作,这⾥多说⼀句,为什么⼀定要初始化中断向量表,因为⼀旦有中断发⽣,没有初始化中断向量表,中断向量表中的地址值是随机的,这样程序就跳转到⼀个随机地址,程序就跑飞了,所以开始给所有中断向量赋⼀个指定的地址值,⼀旦发⽣中断,程序就跳到那个地址去执⾏,这⾥TI给的代码中,这个初始化地址就是⼀个只包含⼀个NOP指令的函数不对程序产⽣影响),继续说我们的调试,我发现CPU是从0x0D4E这个地址中取出的中断函数(看PIECTRL Register的1~15位就知道了,第0位是PIE使能位),⽽⼿册上说WAKEINT这个中断也确实是在0x0D4E 这个地址上,⽽我们指定的中断服务函数PieVectTable.WAKEINT = &wakeint_isr却在下⼀个地址0x0D50的位置上(中断向量表每条中断向量都是32位的)。

F28335系统控制与中断

6.5 TMS320F28335外设中断扩展

6.5.2 向量表映射

第34页/共54页

6.5 TMS320F28335外设中断扩展

6.5.3 中断源

第35页/共54页

6.5 TMS320F28335外设中断扩展

6.5.3 中断源

第36页/共54页

6.5 TMS320F28335外设中断扩展

通过pieierx的相关位禁止中断并清除对应的pieifrx相关位3外设中断复用请求流程65tms320f28335外设中断扩展pie中断向量表65tms320f28335外设中断扩展pie中断向量表65tms320f28335外设中断扩展654pie配置寄存器pie控制寄存器pie中断答应寄存器pie中断标志寄存器pie中断使能寄存器65tms320f28335外设中断扩展654pie配置寄存器65tms320f28335外设中断扩展654pie配置寄存器65tms320f28335外设中断扩展654pie配置寄存器65tms320f28335外设中断扩展654pie配置寄存器65tms320f28335外设中断扩展655cpu中断寄存器65tms320f28335外设中断扩展655cpu中断寄存器65tms320f28335外设中断扩展655cpu中断寄存器65tms320f28335外设中断扩展655cpu中断寄存器65tms320f28335外设中断扩展655cpu中断寄存器65tms320f28335外设中断扩展656外部中断控制寄存器f28335共支持7个外部中断xint1int7xint13还有一个不可屏蔽的外部中断xnmi共用中断源

第53页/共54页

2、外部NMI中断控制寄存器(XNMICR)

3、外部中断x计数器(XINTxCTR) 4、外部NMI中断x计数器(XNMICTR),位定义与上相同

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

TMS320F28335外部中断总结作者:Free 文章来源:Free 点击数:93 更新时间:2010-8-26在这里我们要十分清楚DSP的中断系统。

C28XX一共有16个中断源,其中有2个不可屏蔽的中断RESET和NMI、定时器1和定时器2分别使用中断13和14。

这样还有12个中断都直接连接到外设中断扩展模块PIE上。

说的简单一点就是PIE 通过12根线与28335核的12个中断线相连。

而PIE的另外一侧有12*8根线分别连接到外设,如AD、SPI、EXINT等等。

这样PIE共管理12*8=96个外部中断。

这12组大中断由28335核的中断寄存器IER来控制,即IER确定每个中断到底属于哪一组大中断(如IER |= M_INT12;说明我们要用第12组的中断,但是第12组里面的什么中断CPU并不知道需要再由PIEIER确定)。

接下来再由PIE模块中的寄存器PIEIER中的低8确定该中断是这一组的第几个中断,这些配置都要告诉CPU(我们不难想象到PIEIER共有12总即从PIEIER1-PIEIER12)。

另外,PIE模块还有中断标志寄存器PIEIFR,同样它的低8位是来自外部中断的8个标志位,同样CPU的IFR寄存器是中断组的标志寄存器。

由此看来,CPU的所有中断寄存器控制12组的中断,PIE的所有中断寄存器控制每组内8个的中断。

除此之外,我们用到哪一个外部中断,相应的还有外部中断的寄存器,需要注意的就是外部中断的标志要自己通过软件来清零。

而PIE和CPU的中断标志寄存器由硬件来清零。

EALLOW; // This is needed to write to EALLOW protected registersPieVectTable.XINT2 = &ISRExint; //告诉中断入口地址EDIS; // This is needed to disable write to EALLOW protected registersPieCtrlRegs.PIECTRL.bit.ENPIE = 1; // Enable the PIE block使能PIE PieCtrlRegs.PIEIER1.bit.INTx5= 1; //使能第一组中的中断5IER |= M_INT1; // Enable CPU 第一组中断EINT; // Enable Global interrupt INTMERTM; // Enable Global realtime interrupt DBGM也就是说,12组中的每个中断都要完成上面的相同配置,剩下的才是去配置自己的中断。

如我们提到的EXINT,即外面来个低电平我们就进入中断,完成我们的程序。

在这里要介绍一下,DSP的GPIO口都可以配置为外部中断口,其配置方法如下:GpioCtrlRegs.GPBMUX2.bit.GPIO54 = 0; //选择他们是GPIO口GpioCtrlRegs.GPBMUX2.bit.GPIO55 = 0;GpioCtrlRegs.GPBMUX2.bit.GPIO56 = 0;GpioCtrlRegs.GPBMUX2.bit.GPIO57 = 0;GpioCtrlRegs.GPBDIR.bit.GPIO54 = 0;//选择他们都是输入口GpioCtrlRegs.GPBDIR.bit.GPIO55 = 0;GpioCtrlRegs.GPBDIR.bit.GPIO56 = 0;GpioCtrlRegs.GPBDIR.bit.GPIO57 = 0;GpioCtrlRegs.GPBQSEL2.bit.GPIO54= 0;//GPIO时钟和系统时钟一样且支持GPIOGpioCtrlRegs.GPBQSEL2.bit.GPIO55= 0;GpioCtrlRegs.GPBQSEL2.bit.GPIO56= 0;GpioCtrlRegs.GPBQSEL2.bit.GPIO57= 0;GpioIntRegs.GPIOXINT3SEL.bit.GPIOSEL = 54;//中断3选择GPIOGpioIntRegs.GPIOXINT4SEL.bit.GPIOSEL = 55;GpioIntRegs.GPIOXINT5SEL.bit.GPIOSEL = 56;GpioIntRegs.GPIOXINT6SEL.bit.GPIOSEL = 57;XIntruptRegs.XINT3CR.bit.POLARITY= 0;//触发模式为下降沿触发XIntruptRegs.XINT4CR.bit.POLARITY= 0;XIntruptRegs.XINT5CR.bit.POLARITY= 0;XIntruptRegs.XINT6CR.bit.POLARITY= 0;XIntruptRegs.XINT3CR.bit.ENABLE = 1;//使能中断XIntruptRegs.XINT4CR.bit.ENABLE = 1;XIntruptRegs.XINT5CR.bit.ENABLE = 1;XIntruptRegs.XINT6CR.bit.ENABLE = 1;注意一点就是外部中断1和2只能对GPIO0—GPIO31配置;外部中断3和4、5、6、7只对GPIO32—GPIO63配置。

简简单单DSP”系列学习活动——第四期中断结构学习1、外围帧寄存器2812将外围帧寄存器分为3个空间,分别是:外围帧0:直接映射到CPU存储器总线外围帧1:映射到32位外围总线外围帧2:映射到16位外围总线,只允许16操作这里所说的外围帧寄存器就是外设寄存器,如ADC寄存器。

映射就是分配地址,外围一个地址,CPU一个地址,外围地址映射到CPU地址上。

(1)有的寄存器受保护,对其进行操作的时候好,要屏蔽保护(EALLOW),操作完在开启保护(EDIS).(2)外围中断扩展PIE外设寄存器中的中断标志位必须由软件清0,才能允许下一次中断进入,而且每次中断后要把PIEACKx清0,只有PIEACKx=0,才可以把中断送到CPU级中断分为3级:a、外设级b、PIE级c、CPU级下面分别介绍这个不同的中断级以及这3级的联系a、外设级一旦外设产生了中断,对应的外设中断标志寄存器中的中断标志位IF就会置位,如果此时对应的中断使能位设为1,那么外设中断信号可以送到PIE控制器,如果外设的中断被禁止输入进来,那么外设中断标志位保持为1,直到软件清0。

外设级和PIE级的联系就在外设中断使能位那了,实际外设的中断使能位使能的就是允许外设中断进入PIE级,相当于PIE级的中断源,就像外设的中断源一样,有了中断事件,外设中断标志位就会置位,这里也是外设级就是PIE级得中断事件,有了外设级的中断标志位置位,中断使能位使能,那么PIE级的中断标志位才会置1.注意的是外设中断标志寄存器中的中断标志位必须由软件清0,才能允许下一次中断进入。

b、PIE级PIE级有两中寄存器,一种是中断标志寄存器PIEIFRx,上面已经说过他跟外设级的联系,另一个是中断使能寄存器PIEIERx,这个跟外设级的中断使能寄存器功能差不多,实现的是和CPU级的联系.PIE级还有两个寄存器,一个是控制寄存器PIECTRL,这个是控制整个PIE级的,还有一个应答寄存器PIEACK,在PIEIFRx置位,PIEIERx使能还要PIEACKx清0才能把中断送到CPU级。

这里注意的是PIEIFRx由硬件清0,但是PIEACKx要由软件清0.c、CPU级CPU级是最终控制中断响应的,也是有两种寄存器,一个是中断标志寄存器IFR,另一个是中断使能寄存器IER。

IFR是这三级中断的最终的中断标志位,IER是这三级中断的最终中断使能位,只有这三级中断标志位同时置位,三级中断同时使能,这里还有一个CPU级的中断屏蔽位INTM,在以上条件满足的前提下,中断屏蔽位INTM=0,CPU才能响应中断,找到中断向量,跳转到中断函数,执行中断操作,CPU级的中断标志位由硬件清0,在中断函数中不用管。

这就是它的中断过程。

3、96个中断介绍2812分为12组中断,每组中断有8个中断源,以INTx.y表示,其中x是组(x=1~12),y(y=1~8)是组中的位.在配置中断的时候,外设级的中断使能位要使能;PIECTRL寄存器使能PIE;要知道INTx.y中的xy是多少,找到PIEIERx(x=1~12)的x是多少,使能PIEIERx;PIEACKx(x=1~12)的x是多少给其清0;IERx(x=1~12)的x是多少,使能IERx;中断屏蔽位INTM=0;中断函数中要处理的:外设中断标志位软件清0PIEACKx(x=1~12)软件清0;4、C代码分析以定时器0的C代码分析timer0的中断向量INT1.7(x=1,y=7),用到的PIE级的中断使能寄存器是PIEIER1,CPU级的IER1.在2812的库函数中有一个定义中断入口地址的函数,用户的中断函数内容可以在这里面写,就不容另外赋中断地址了。

中断函数入口地址interrupt voidTINT0_ISR(void)。

在DSP复位后,进入中函数前,看门狗开着的,所以在进入中函数后第一件事情是关看门狗,在这个函数里面InitSysCtrl();中断是开着的需要关闭(DINT;),PIE 寄存器(InitPieCtrl();//初始化pie寄存器)(IER = 0x0000;//禁止所有的中断IFR = 0x0000;)、中断向量表是没有初始化的,所以要初始化(InitPieVectTable();//初始化pie中断向量表)。

InitSysCtrl();//初始化cpuDINT;//关中断InitPieCtrl();//初始化pie寄存器IER = 0x0000;//禁止所有的中断IFR = 0x0000;InitPieVectTable();//初始化pie中断向量表EALLOW;// This is needed to write to EALLOW protected registersPieVectTable.TINT0 = &cpu_timer0_isr;//指定中断服务子程序,这个地方要是用到了DSP的库函数DSP281X_DefaultIsr()函数就不需要了。

EDIS;InitCpuTimers();//初始化定时器0ConfigCpuTimer(&CpuTimer0,150,9.75);//配置你要定时的时间StartCpuTimer0();//定时器开始计数PieCtrlRegs.PIEIER1.bit.INTx7 = 1;//使能PIE级中断PIEIERx中的x=1,即使能的12组中的第1组第七个IER |= M_INT1;//使能CPU级的中断第1组EINT;// 使能INTMERTM;// 使能仿真时DBGM5、在中断函数中要做的interrupt voidTINT0_ISR(void)// CPU-Timer 0{PieCtrlRegs.PIEACK.all = PIEACK_GROUP1; //PIEACK清0CpuTimer0Regs.TCR.bit.TIF = 1;//外设中断标志位清0CpuTimer0Regs.TCR.bit.TRB = 1;//重新装载}。