数电-半导体存储器练习题33页PPT

合集下载

数字电子技术第9章半导体存储器简明教程PPT课件

为高电平,若有管子与其相连(如位线2和0),其相应

的MOS管导通,位线输出为0,而位线1和3没有管子

与字线相连,则输出为1。故存储器的内容取决于制造 工艺,。

9.1.3 可编程ROM 在某些应用中,程序需要经常修改,因此能够重复擦 写的EPROM被广泛应用。这种存储器利用编程器写 入后,信息可长久保持,因此可作为只读存储器。当 其内容需要变更时,可利用擦除器(由紫外线灯照射) 将其擦除,各单位内容复原为FFH,再根据需要利用 EPROM编程器编程,因此这种芯片可反复使用。

但把A9引脚接至11.5~12.5 V的高电平,则2764A 处于读Intel标识符模式。要读出2764A的编码必须顺 序读出两个字节,先让A1~A8全为低电平,而使A0从 低变高,分两次读取2764A的内容。当A0=0时,读出 的内容为制造商编码(陶瓷封装为89H,塑封为88H), 当A0=1时,则可读出器件的编码(2764A为08H, 27C64为07H)。

数字电子技术

第 9 章 半导体存储器

本章知识结构图

EXIT

第9章 半导体存储器

• 9.1 只读存储器 • 9.2 随机存取存储器

• 9.3 存储器容量的扩展

• 9.4 实例电路分析:存储系统的设计

EXIT

9.1

只读存储器

9.1.1 ROBiblioteka 的定义与基本结构只读存储器(ROM, 即Read-Only Memory)

1. EPROM (1)存储单元电路和工作原理 通常EPROM存储电路是利用浮栅MOS管构成的,

又称FAMOS管(Floating gate Avalanche Injection

Metal-Oxide-Semiconductor,即浮栅雪崩注入MOS

的MOS管导通,位线输出为0,而位线1和3没有管子

与字线相连,则输出为1。故存储器的内容取决于制造 工艺,。

9.1.3 可编程ROM 在某些应用中,程序需要经常修改,因此能够重复擦 写的EPROM被广泛应用。这种存储器利用编程器写 入后,信息可长久保持,因此可作为只读存储器。当 其内容需要变更时,可利用擦除器(由紫外线灯照射) 将其擦除,各单位内容复原为FFH,再根据需要利用 EPROM编程器编程,因此这种芯片可反复使用。

但把A9引脚接至11.5~12.5 V的高电平,则2764A 处于读Intel标识符模式。要读出2764A的编码必须顺 序读出两个字节,先让A1~A8全为低电平,而使A0从 低变高,分两次读取2764A的内容。当A0=0时,读出 的内容为制造商编码(陶瓷封装为89H,塑封为88H), 当A0=1时,则可读出器件的编码(2764A为08H, 27C64为07H)。

数字电子技术

第 9 章 半导体存储器

本章知识结构图

EXIT

第9章 半导体存储器

• 9.1 只读存储器 • 9.2 随机存取存储器

• 9.3 存储器容量的扩展

• 9.4 实例电路分析:存储系统的设计

EXIT

9.1

只读存储器

9.1.1 ROBiblioteka 的定义与基本结构只读存储器(ROM, 即Read-Only Memory)

1. EPROM (1)存储单元电路和工作原理 通常EPROM存储电路是利用浮栅MOS管构成的,

又称FAMOS管(Floating gate Avalanche Injection

Metal-Oxide-Semiconductor,即浮栅雪崩注入MOS

数字电路与逻辑设计半导体存储器PPT课件

•Yj =1,T7 、T8均导 通,触发器的输出才 与数据线接通,该单 元才能通过数据线传 送数据

第23页/共71页

的结构

二、RAM存储单元

• 动态MOS RAM(DRAM)

来自DR行AM存地储址数译据码原理: 器的输出

基于MOS管栅极电容的电荷存储效应

存储单元

写(行入制选X刷电择i 线 新路)控

根数 字长:指每个地址单元中的数据位数;也即是每次寻址后

从存储器中读出(或写入)的数据位数

第21页/共71页

的结构

二、RAM存储单元

• 静态MOS RAM(SRAM)

Xi (行选择线)

位 线 B

数 据 线D

本单元控制门

T3

T5 T1

VDD

T4 T6

T2

基本RS触发器

T7

T8

Yj (列选择线)

列存储单元公用的控制门

随机存取存储器:在运行状态可以随时进行读或写操作 RAM信息易失: 芯片必须供电才能保持存储的数据

只读存储器:通过特定方法写入数据,正常工作时只能读出 ROM信息非易失:信息一旦写入,即使断电也不会丢失

第2页/共71页

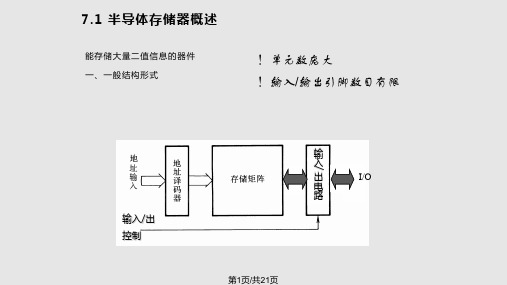

7.1 存储器概述

3. 存储器的主要性能指标:

容量:存储单元总数(bit) 1Kbit=1024bit=210bit 128Mbit=134217728bit=227bit

7.1 存储器概述

1. 存储器一般概念 • 存储器:专用于存放大量二进制数码的器件 • 按材料分类 1) 磁介质类——软磁盘、硬盘、磁带、… 2) 光介质类——CD、DVD、MO、… 3) 半导体介质类——SDRAM、EEPROM、FLASH ROM、… • 按功能分类 主要分RAM和ROM两类,不过界限逐渐模糊 RAM: SDRAM, 磁盘, ROM: CD, DVD, FLASH ROM, EEPROM

第23页/共71页

的结构

二、RAM存储单元

• 动态MOS RAM(DRAM)

来自DR行AM存地储址数译据码原理: 器的输出

基于MOS管栅极电容的电荷存储效应

存储单元

写(行入制选X刷电择i 线 新路)控

根数 字长:指每个地址单元中的数据位数;也即是每次寻址后

从存储器中读出(或写入)的数据位数

第21页/共71页

的结构

二、RAM存储单元

• 静态MOS RAM(SRAM)

Xi (行选择线)

位 线 B

数 据 线D

本单元控制门

T3

T5 T1

VDD

T4 T6

T2

基本RS触发器

T7

T8

Yj (列选择线)

列存储单元公用的控制门

随机存取存储器:在运行状态可以随时进行读或写操作 RAM信息易失: 芯片必须供电才能保持存储的数据

只读存储器:通过特定方法写入数据,正常工作时只能读出 ROM信息非易失:信息一旦写入,即使断电也不会丢失

第2页/共71页

7.1 存储器概述

3. 存储器的主要性能指标:

容量:存储单元总数(bit) 1Kbit=1024bit=210bit 128Mbit=134217728bit=227bit

7.1 存储器概述

1. 存储器一般概念 • 存储器:专用于存放大量二进制数码的器件 • 按材料分类 1) 磁介质类——软磁盘、硬盘、磁带、… 2) 光介质类——CD、DVD、MO、… 3) 半导体介质类——SDRAM、EEPROM、FLASH ROM、… • 按功能分类 主要分RAM和ROM两类,不过界限逐渐模糊 RAM: SDRAM, 磁盘, ROM: CD, DVD, FLASH ROM, EEPROM

电子技术基础数字部分第六章半导体存储器经典课件

n 地址单元的个数N与二进制地址码的位数 满足2n = N ,如:256个

8

3、输入/输出控制电路

(1)片选信号CS :解决芯片是否工作的问题;

(2)读写控制信号:决定是读信号还是写信号;

三、RAM的操作与定时

1、读操作

(1)欲读取单元的地址加到存储器的地址输入端; (2)加入有效的片选信号 CS; (3)在 R / W 线上加高电平,经过一段时间后,所选单元的内容出现

半导体存储器就是存储大量二值数据的半导体器件,是数字系统必不可 少的组成部分。这种存储包括:存储文字的编码数据、存储声音的编码数据、 存储图像的编码数据。

衡量存储器性能的重要计数指标——存储容量(目前动态存储器的容量 可达10亿位/片)、存取速度(一些高速存储器的存取时间仅10nS)。

1、存储容量

数 T7

据

线D

D T8

Yj (列选线 )

数 据

线

特点——数据由触发器记忆,只要不断电,数据可以永久保存。

2、DRAM存储单元

SRAM存储单元所用管子多,功耗大,集成度受到限制。 DRAM存储数据的原理——基于电容电荷的存储效应。

字线

X

位

V

线

CS

CW

存储单元电容

单管动态存储单元

杂散电容

常见的DRAM存储单元有两种结构: 单管(大容量DRAM存储单元普遍采 用单管结构) 、三管 ;

2学时

第六章 半导体存储器

1、半导体存储器的基本概念; 2、随机存储器RAM; 3、只读存储器ROM;

课后练习: P383-7.1.1 、P383-7.1.2

序言

随着半导体集成工艺的不断进步,电路的集成度越来越高。目前,大规 模集成电路LSI日新月异,LSI电路的一个重要应用领域就是半导体存储器。

8

3、输入/输出控制电路

(1)片选信号CS :解决芯片是否工作的问题;

(2)读写控制信号:决定是读信号还是写信号;

三、RAM的操作与定时

1、读操作

(1)欲读取单元的地址加到存储器的地址输入端; (2)加入有效的片选信号 CS; (3)在 R / W 线上加高电平,经过一段时间后,所选单元的内容出现

半导体存储器就是存储大量二值数据的半导体器件,是数字系统必不可 少的组成部分。这种存储包括:存储文字的编码数据、存储声音的编码数据、 存储图像的编码数据。

衡量存储器性能的重要计数指标——存储容量(目前动态存储器的容量 可达10亿位/片)、存取速度(一些高速存储器的存取时间仅10nS)。

1、存储容量

数 T7

据

线D

D T8

Yj (列选线 )

数 据

线

特点——数据由触发器记忆,只要不断电,数据可以永久保存。

2、DRAM存储单元

SRAM存储单元所用管子多,功耗大,集成度受到限制。 DRAM存储数据的原理——基于电容电荷的存储效应。

字线

X

位

V

线

CS

CW

存储单元电容

单管动态存储单元

杂散电容

常见的DRAM存储单元有两种结构: 单管(大容量DRAM存储单元普遍采 用单管结构) 、三管 ;

2学时

第六章 半导体存储器

1、半导体存储器的基本概念; 2、随机存储器RAM; 3、只读存储器ROM;

课后练习: P383-7.1.1 、P383-7.1.2

序言

随着半导体集成工艺的不断进步,电路的集成度越来越高。目前,大规 模集成电路LSI日新月异,LSI电路的一个重要应用领域就是半导体存储器。

清华数字电路第七章 半导体存储器PPT课件

16.08.2020

数电

7.1 概述

**PROM在出厂时存储内容全为1(或者全为0),用户 可根据自己的需要写入,利用通用或专用的编程器, 将某些单元改写为0(或为1)。

**PROM在出厂时存储内容全为1(或者全为0),用户 可根据自己的需要写入,利用通用或专用的编程器, 将某些单元改写为0(或为1)。

ROM可分为掩模ROM、可编程ROM(Programmable Read-Only Memory,简称PROM)和可擦除的可编程 ROM(Erasable Programmable Read-Only Memory, 简称EPROM)。

*掩模ROM在制造时,生产厂家利用掩模技术把数据 写入存储器中,一旦ROM制成,其存储的数据就固 定不变,无法更改。

第七章 半导体存储器

内容提要

本章将系统地介绍各种半导体存储器的工作原理 和使用方法。半导体存储器包括只读存储器(ROM) 和随机存储器(RAM)。在只读存储器中,介绍了掩 模ROM、PROM和快闪存储器等不同类型的ROM的 工作原理和特点;而在随机存储器中,介绍了静态 RAM(SRAM)和动态RAM(DRAM)两种类型。 此外,也介绍了存储器扩展容量的连接方法以及用存 储器设计组合逻辑电路,重点放在这里。

1. ROM的组成:

ROM电

路结构包含存

储矩阵、地址

译码器和输出

缓冲器三个部

分,其框图如

图7.2.1所示。

16.08.2020

数电

图7.2.1

7.2.1 掩模只读存储器

a.存储矩阵

存储矩阵是由许多存储单元排列而成。存储单元 可以是二极管、双极型三极管或MOS管,每个单元能 存放1位二值代码(0或1),而每一个或一组存储单元有 一个相应的地址代码。

数字逻辑电路教程PPT第6章半导体存储器

01

02

03

04

存储容量

根据需求选择合适的存储容量 。

数据安全

考虑数据是否需要长期保存, 以及是否需要加密保护。

读写速度

根据应用场景选择读写速度合 适的存储器。

可靠性和稳定性

选择经过严格测试和验证的优 质产品。

半导体存储器的发展趋势

容量更大

随着技术进步,半导体存储器 的容量不断增大。

速度更快

读写速度更快,满足高性能计 算和大数据处理的需求。

慢、集成度低。

NAND型闪存则具有写入速度快 、集成度高、成本低等优点,但

读取速度较慢、可靠性较低。

闪存的应用场景与限制

闪存广泛应用于各种存储卡、U盘、固态硬盘等存储器产品中。

由于闪存的写入和擦除次数有限,因此不适用于需要频繁读写的大型数据库应用。

同时,由于闪存的读取速度和可靠性受工艺和材料影响较大,因此不同品牌和型号 的闪存产品性能差异较大。

02

地址译码器:用于将输 入的地址信号转换为对 应的存储单元的地址。

03

04

控制逻辑:负责控制存 储单元的读写操作。

数据输入/输出缓冲器: 用于输入和输出数据。

RAM的工作原理

写入操作

当写入使能信号有效时,数据通过数据输入缓冲器进入存储单元,并保存在相应 的地址中。

读取操作

当读取使能信号有效时,控制逻辑从指定地址的存储单元中读取数据,并通过数 据输出缓冲器输出。

05

CATALOGUE

半导体存储器的比较与选择

RAM、ROM与闪存的比较

RAM

随机存取存储器,数据读 写速度快,但断电后数据 会丢失。

ROM

只读存储器,数据只能读 取不能写入,断电后数据 不会丢失。

数电-半导体存储器练习题

× √

B D

SRAM 以上都对

× ×

分析提示

DRAM利用 利用MOS管的栅极电容对电荷的存储效应存储信息, 管的栅极电容对电荷的存储效应存储信息, 利用 管的栅极电容对电荷的存储效应存储信息 电荷不能长期存储。 电荷不能长期存储。 SRAM 以寄存器为存储元件,只有在带电状态下才能存储信息。 以寄存器为存储元件,只有在带电状态下才能存储信息。 DRAM、 SRAM 属于“易失性”存储器,不能实现组合逻辑函 属于“易失性”存储器, 、 数。 EPROM,利用 管作存储元件, ,利用MOS管作存储元件,存储矩阵的字、位线交叉 管作存储元件 存储矩阵的字、 处接入不接入存储元件的连接方式决定所存储信息的内容是0或 , 处接入不接入存储元件的连接方式决定所存储信息的内容是 或1, 连接方式确定后所存储的信息可长期保存不变, 连接方式确定后所存储的信息可长期保存不变,可实现组合逻辑函 数

第

4

页

数字电子技术

第 7 章 半导体存储器

单项选择题 ( )。

4、有 10 位地址和 8 位字长的存储器,其存储容量为 、 位字长的存储器, A C 256×10 位 × 1024×10 位 ×

× ×

B D

512×8 位 × 1024×8 位 ×

× √

分析提示

10 位地址所对应 存储字数为: 210=1024 存储字数为: 每个字的字长为: 每个字的字长为: 8 位 字数× 存储容量 = 字数×字长 =1024 × 8 位

第

14

页

数字电子技术

第 7 章 半导体存储器

单项选择题 )。

14、只读存储器ROM,当电源断电后再通电时,所存储的内容 ( 、只读存储器 ,当电源断电后再通电时, A C 全部改变 不确定

《半导体存储器》PPT课件_OK

T3

主

从

1位

图7-2-2 动态CMOS移存单元

当CP=1时,主动态反相器接收信息,从动态反相器保持原存

信息;CP=0时,主动态反相器保持原存信息,从动态反相器随9 主

动态反相器变化。每经过一个CP,数据向右移动一位。

7.2.3 动态移存器和顺序存取存储器

1.动态移存器 动态移存器可用动态CMOS移存单元串接而成,主要用来组 成顺序存取存储器(SAM)。

• ••

CS1

• ••

21

图7-3-6 RAM的位

2.字扩展

适用于位数(字长)够用,但字数不够的情况。 如: 8K×8 → 32K×8 增加地址线。

D0

D7

•••

•••

•••

•••

I/O7···I/O0 VDD

OE 6264Ⅰ 1

GND

CS2

R/W A12 ···A0CS1

I/O7···I/O0 VDD

•••

A2 译

A3

码 X15 器

T0

1,1 位线 16,1

1,16 位线 16,16

I/O电路 G1 1

D

EN

G2

1

I/O

•

EN

T0' T15

T15'

1 EN G3

Y0 (列)

•••

Y15

Y 地址译码器

D G4 &

& G5

A4 A5 A6 A7

图7-3-1 256×1位RAM 示意图

CS

R/W

25

返回

第7章 半导体存储器

• 教学内容 : 半导体存储器的特点、分类及主要技术指标 ; 顺序存取存储器(SAM); 随机存取存储器(RAM) ;

主

从

1位

图7-2-2 动态CMOS移存单元

当CP=1时,主动态反相器接收信息,从动态反相器保持原存

信息;CP=0时,主动态反相器保持原存信息,从动态反相器随9 主

动态反相器变化。每经过一个CP,数据向右移动一位。

7.2.3 动态移存器和顺序存取存储器

1.动态移存器 动态移存器可用动态CMOS移存单元串接而成,主要用来组 成顺序存取存储器(SAM)。

• ••

CS1

• ••

21

图7-3-6 RAM的位

2.字扩展

适用于位数(字长)够用,但字数不够的情况。 如: 8K×8 → 32K×8 增加地址线。

D0

D7

•••

•••

•••

•••

I/O7···I/O0 VDD

OE 6264Ⅰ 1

GND

CS2

R/W A12 ···A0CS1

I/O7···I/O0 VDD

•••

A2 译

A3

码 X15 器

T0

1,1 位线 16,1

1,16 位线 16,16

I/O电路 G1 1

D

EN

G2

1

I/O

•

EN

T0' T15

T15'

1 EN G3

Y0 (列)

•••

Y15

Y 地址译码器

D G4 &

& G5

A4 A5 A6 A7

图7-3-1 256×1位RAM 示意图

CS

R/W

25

返回

第7章 半导体存储器

• 教学内容 : 半导体存储器的特点、分类及主要技术指标 ; 顺序存取存储器(SAM); 随机存取存储器(RAM) ;

数电半导体存储器和可编程器件PPT培训课件

8.4密封后的竞争性磋商响应文件均应:

后,浮栅上无放电回路,故能 1.遇心服务技巧

2.9对容器的检验(查)人员、操作人员进行安全技术教育和技术考核工作。

长期保存。 精致化的服务能够贯彻到眼神和表情。眼神呆若木鸡,服务就会显得生硬。服务要整体表达出真情诚意,眼神也要流露对顾客的感情,

这样才能令客户感受深刻。眼神的表达要经过系统训练,除了喜、怒、哀、乐这四种基本表情之外,还要表现出贴切、真诚、热忱、 关注等感情,努力做到“眼睛会说话”。

特点:使用灵活、方便。但具有易失性,即:掉电后, 数据就消失(也有非易失性的RAM,实际上类似于 ROM)。

※

分类: RAM按存储单元工作原理不同分为

SRAM(静态):存取速度快 DRAM(动态):结构简单、集成度高 NVRAM(非易失性)

RAM 按所用器件可分为 双极型 MOS型

※

1、RAM存储器的基本结构

组成基本SR锁存器

T5 T3

T4

位 线 B

T7

数 据

线D

DT1

D

T2

Yj (列选择线)

T6

D、 D:存储的一位二值

位 数据。

线 B

T5、T6:本单元控制门, 由行择线Xi控制。

T8

数 T7、T8:一列存储单 据 元公用的控制门, D线 由列选择线Yj控制。 ※

工作原理:

Xi(行选择线)

1

T5 T3

矩八阵位形地式址。线采用双译码(行、列译码),用两条地址线来

共同选择存储单元。

A0 A1

CS0 0 CS1 1

A2 A3 A4

地 址 译 码

存 储 器

A5 器 A6

阵 列

A7

后,浮栅上无放电回路,故能 1.遇心服务技巧

2.9对容器的检验(查)人员、操作人员进行安全技术教育和技术考核工作。

长期保存。 精致化的服务能够贯彻到眼神和表情。眼神呆若木鸡,服务就会显得生硬。服务要整体表达出真情诚意,眼神也要流露对顾客的感情,

这样才能令客户感受深刻。眼神的表达要经过系统训练,除了喜、怒、哀、乐这四种基本表情之外,还要表现出贴切、真诚、热忱、 关注等感情,努力做到“眼睛会说话”。

特点:使用灵活、方便。但具有易失性,即:掉电后, 数据就消失(也有非易失性的RAM,实际上类似于 ROM)。

※

分类: RAM按存储单元工作原理不同分为

SRAM(静态):存取速度快 DRAM(动态):结构简单、集成度高 NVRAM(非易失性)

RAM 按所用器件可分为 双极型 MOS型

※

1、RAM存储器的基本结构

组成基本SR锁存器

T5 T3

T4

位 线 B

T7

数 据

线D

DT1

D

T2

Yj (列选择线)

T6

D、 D:存储的一位二值

位 数据。

线 B

T5、T6:本单元控制门, 由行择线Xi控制。

T8

数 T7、T8:一列存储单 据 元公用的控制门, D线 由列选择线Yj控制。 ※

工作原理:

Xi(行选择线)

1

T5 T3

矩八阵位形地式址。线采用双译码(行、列译码),用两条地址线来

共同选择存储单元。

A0 A1

CS0 0 CS1 1

A2 A3 A4

地 址 译 码

存 储 器

A5 器 A6

阵 列

A7

数字逻辑电路半导体存储器资料PPT课件

用SIMOS管构成的存储单元

工作原理: 若G f 上充以负电荷,则 Gc处正常逻辑高电平下不 导通 若G f 上未充负电荷,则 Gc处正常逻辑高电平下导 通

第9页/共21页

“写入”:在叠栅管的D S上同时加上较高电压(25V),

漏源间形成导电沟道,沟道内电子获得动能,

在

受到G

上所加正电压的电场吸引下

第14页/共21页

7.3.1 RAM的基本结构与工作原理 以SRAM为例

第15页/共21页

7.3.2 存储单元

6只N沟道增强型MOS管 组成的静态存储单元

T1 ~ T4组成基本的锁存器,作存储单元

T5 ~ T8是门控管,起模拟开关的作用 T5和T6受控于地址译码器的输出

T7和T8决定存储单元是否与输入输出 电路I/O相连,受控于列地址译码器

第6页/共21页

7.2.2 可编程ROM

可编程ROM(programmable ROM,PROM) 总体结构与掩模ROM一样,但存储单元不同

熔丝由易熔合金制成 出厂时,每个结点上都 有 编程时将不用的熔断 !! 是一次性编程,不能改 写

第7页/共21页

7.2.3 可擦除的可编程ROM

EPROM

为储克 单元服不紫 同 外线擦除的EPRO M擦除慢,操作复杂的缺点 采用FLO TO X(浮栅隧道氧化层MO S管)

Gf与漏区之间有小的隧道区,当场强大到一定程度时, 在漏区和Gf 之间出现导电隧道,电子可以双向通过形成电流, 这种现象称为隧道效应。

第11页/共21页

7.2.4 利用ROM实现组合逻辑函数

第12页/共21页

地址译码器是一个与阵列,它的输出包含了输入地址变量的 全部最小项,每一条字线对应一个最小项; 存储矩阵是一个或阵列,每一位输出数据都是将地址译码器 输出的一些最小项相加。

相关主题

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

25、学习是劳动,是充满思想的劳动。——乌申斯基

谢谢!

数电-半导体存储器练习题

36、如果我们国家的法律中只有某种 神灵, 而不是 殚精竭 虑将神 灵揉进 宪法, 总体上 来说, 法律就 会更好 。—— 马克·吐 温 37、纲纪废弃之日,便是暴政兴起之 时。— —威·皮 物特

38、若是没有公众舆论的支持,法律 是丝毫 没有力 量的。 ——菲 力普斯 39、一个判例造出另一个判例,它们 迅速累 聚,进 而变成 法律。 ——朱 尼厄斯

40、人类法律,事物有规律,这夸大,也会招来人们的反感轻蔑和嫉妒。——培根 22、业精于勤,荒于嬉;行成于思,毁于随。——韩愈

23、一切节省,归根到底都归结为时间的节省。——马克思 24、意志命运往往背道而驰,决心到最后会全部推倒。——莎士比亚

谢谢!

数电-半导体存储器练习题

36、如果我们国家的法律中只有某种 神灵, 而不是 殚精竭 虑将神 灵揉进 宪法, 总体上 来说, 法律就 会更好 。—— 马克·吐 温 37、纲纪废弃之日,便是暴政兴起之 时。— —威·皮 物特

38、若是没有公众舆论的支持,法律 是丝毫 没有力 量的。 ——菲 力普斯 39、一个判例造出另一个判例,它们 迅速累 聚,进 而变成 法律。 ——朱 尼厄斯

40、人类法律,事物有规律,这夸大,也会招来人们的反感轻蔑和嫉妒。——培根 22、业精于勤,荒于嬉;行成于思,毁于随。——韩愈

23、一切节省,归根到底都归结为时间的节省。——马克思 24、意志命运往往背道而驰,决心到最后会全部推倒。——莎士比亚