5962-0050601Q2A中文资料

5962-9760807QYA资料

1Features•7.4SPECint95,6.1SPECfp95at 300MHz (estimated)•Superscalar (3instructions per clock peak)•Dual 16KB Caches •Selectable Bus Clock•32-bit Compatibility PowerPC Implementation •On-chip Debug Support•P D typical =3.5Watts (266MHz),Full Operating Conditions •Nap,Doze and Sleep Modes for Power Savings •Branch Folding•64-bit Data Bus (32-bit Data Bus Option)•4-Gbytes Direct Addressing Range•Pipelined Single/Double Precision Float Unit •IEEE 754Compatible FPU•IEEE P 1149-1Test Mode (JTAG/C0P)•f INT max =300MHz •f BUS max =75MHz•Compatible CMOS Input/TTL OutputScreening/Quality/PackagingThis product is manufactured in full compliance with:•CI-CGA 255:MIL-STD-883class Q or According to A TMEL-Grenoble standards •CBGA 255:Upscreenings based upon A TMEL-Grenoble standards •Full Military Temperature Range (T c =-55°C,T c =+125°C)IndustriaL Temperature Range (T c =-40°C,T c =+110°C)•Internal/IO Power Supply =2.5±5%//3.3V ±5%•255-lead CBGA Package and 255-lead CBGA with SCI (CI-CGA)PackageDescriptionThe PID7t-603e implementation of PowerPC 603e (after named 603r)is a low-power implementation of reduced instruction set computer (RISC)microprocessors Pow-erPC äfamily.The 603r implements 32-bit effective addresses,integer data types of 8,16and 32bits,and floating-point data types of 32and 64bits.The 603r is a low-power 2.5/3.3-volt design and provides four software controllable power-saving modes.The 603r is a superscalar processor capable of issuing and retiring as many as three instructions per clock.Instructions can execute out of order for increased perfor-mance;however,the 603r makes completion appear sequential.The 603r integrates five execution units and is able to execute five instructions in parallel.The 603r provides independent on-chip,16-Kbyte,four-way set-associative,physically addressed caches for instructions and data and on-chip instruction and data Memory Management Units (MMUs).The MMUs contain 64-entry,two-way set-associative,data and instruction translation look aside buffers that provide support for demand-paged virtual memory address translation and variable-sized block translation.The 603r has a selectable 32-or 64-bit data bus and a 32-bit address bus.The 603r interface protocol allows multiple masters to complete for system resources through a central external arbiter.The 603r supports single-beat and burst data transfers for memory accesses,and supports memory-mapped I/O.2TSPC603R2125A–HIREL–04/02The 603r uses an advanced,2.5/3.3V CMOS process technology and maintains full interface compatibility with TTL devices.The 603r integrates in-system testability and debugging features through JTAG boundary-scan capability.General DescriptionFigure 1.BlockDiagram3TSPC603R2125A –HIREL –04/02IntroductionThe 603r is a low-power implementation of the PowerPC microprocessor family of reduced instruction set computer (RISC)microprocessors.The 603r implements the 32-bit portion of the PowerPC architecture,which provides 32-bit effective addresses,integer data types of 8,16and 32bits,and floating-point data types of 32and 64bits.For 64-bit PowerPC microprocessors,the PowerPC architecture provides 64-bit integer data types,64-bit addressing,and other features required to complete the 64-bit architecture.The 603r provides four software controllable power-saving modes.Three of the modes (the nap,doze,and sleep modes)are static in nature,and progressively reduce the amount of power dissipated by the processor.The fourth is a dynamic power manage-ment mode that causes the functional units in the 603r to automatically enter a low-power mode when the functional units are idle without affecting operational perfor-mance,software execution,or any external hardware.The 603r is a superscalar processor capable of issuing and retiring as many as three instructions per clock.Instructions can execute out of order for increased performance;however,the 603r makes completion appear sequential.The 603e integrates five execution units —an integer unit (IU),a floating-point unit (FPU),a branch processing unit (BPU),a load/store unit (LSU)and a system register unit (SRU).The ability to execute five instructions in parallel and the use of simple instructions with rapid execution times yield high efficiency and throughput for 603r-based systems.Most integer instructions execute in one clock cycle.The FPU is pipelined so a single-precision multiply-add instruction can be issued every clock cycle.The 603r provides independent on-chip,16-Kbyte,four-way set-associative,physically addressed caches for instructions and data and on-chip instruction and data memory management units (MMUs).The MMUs contain 64-entry,two-way set-associative,data and instruction translation look aside buffers (DTLB and ITLB)that provide support for demand-paged virtual memory address translation and variable-sized block translation.The TLBs and caches use a least recently used (LRU)replacement algorithm.The 603r also supports block address translation through the use of two independent instruction and data block address translation (IBAT and DBAT)arrays of four entries each.Effec-tive addresses are compared simultaneously with all four entries in the BAT array during block translation.In accordance with the PowerPC architecture,if an effective address hits in both the TLB and BAT array,the BAT translation takes priority.The 603r has a selectable 32-or 64-bit data bus and a 32-bit address bus.The 603r interface protocol allows multiple masters to compete for system resources through a central external arbiter.The 603r provides a three-state coherency protocol that sup-ports the exclusive,modified,and invalid cache states.This protocol as a compatible subset of the MESI (modified/exclusive/shared/invalid)four-state protocol and operates coherently in systems that contain four-state caches.The 603r supports single-beat and burst data transfers for memory accesses,and supports memory-mapped I/O.The 603r uses an advanced,0.29µm 5metal layer CMOS process technology and maintains full interface compatibility with TTL devices.4TSPC603R2125A –HIREL –04/02Pin AssignmentsCBGA 255and CI-CGA 255PackagesFigure 2(pin matrix)shows the pinout as viewed from the top of the CBGA and CI-CGA packages.The direction of the top surface view is shown by the side profile of the packages.Figure 2.CBGA 255and CI –CGA 255Top View5TSPC603R2125A –HIREL –04/02Pinout ListingDDDD Table 1.Power and Ground Pins6TSPC603R2125A –HIREL –04/02DD 2.NC (no-connect)in the 603e BGA package;internally tied to GND in the 603r BGA package to indicate to the power supplythat a low-voltage processor is present.Signal DescriptionFigure 3,Table 3and Table 4describe the signals on the TSPC603r and indicate signal functions.The test signals,TRST,TMS,TCK,TDI and TDO,comply with subset P-1149.1of the IEEE testability bus standard.The 3signals LSSD_MODE,LI_TSTCLK and L2_TSTCLK are test signals for factory use only and must be pulled up to V DD for normal machine operations.Table 2.Signal Pinout Listing7TSPC603R2125A –HIREL –04/02Figure 3.Functional Signal GroupsTable 3.Address and Data Bus Signal Index8TSPC603R2125A –HIREL –04/02Table 4.Signal Index9TSPC603R2125A –HIREL –04/02Table 4.Signal Index (Continued)10TSPC603R2125A –HIREL –04/02DetailedSpecificationsScopeThis drawing describes the specific requirements for the microprocessor TSPC603r,in compliance with MIL-STD-883class B or ATMEL-Grenoble standard screening.Applicable Documents -STD-883:T est methods and procedures for -PRF-38535:General specifications for microcircuits.Requirements GeneralThe microcircuits are in accordance with the applicable documents and as specified herein.Design and Construction•Terminal connectionsThe terminal connections shall be as shown in Figure 15and Figure 3.•Lead material and finishLead material and finish shall be as specified in MIL-STD-1835.Absolute Maximum RatingsAbsolute maximum ratings are stress rating only and functional operation at the maxi-mum is not guaranteed.Stresses beyond those listed may affect device reliability or cause permanent damage to the device.Notes:1.Functional operating conditions are given in AC and DC electrical specifications.Stresses beyond the absolute maximumslisted may affect device reliability or cause permanent damage to the device.2.Caution :Input voltage must not be greater than OV DD by more than 2.5V at any times,including during power-on reset.3.Caution :OV DD voltage must not be greater than V DD /AV DD by more than 1.2V at any times,including during power-on reset.4.Caution :V DD /AV DD voltage must not be greater than OV DD by more than 0.4V at any times,including during power-on reset.(1)(2)(3)(4)TSPC603RRecommended Operating Conditions These are the recommended and tested operating conditions.Proper device operation outside of these conditions is not guaranteed.Thermal Characteristics The data found in this section concerns603r’s packaged in the255-lead21mmmulti-layer ceramic(MLC),ceramic BGA package.Data is shown for the case of usingthe Thermalloy#2328B heat sink.The internal thermal resistance for this package is negligible due to the exposed diedesign.A thermal interface material is recommended at the package lid-to-heat sinkinterface to minimize the thermal contact resistance.Additionally,the CBGA package offers an excellent thermal connection to the card andpower planes.Heat generated at the chip is dissipated through the package,the heatsink(when used)and the card.The parallel heat flow paths result in the lowest overallthermal resistance as well as offer significantly better power dissipation capability if aheat sink is not used.The thermal characteristics for the flip-chip CBGA and CI-CGA packages are as follows:Thermal resistance(junction-to-case)=R jc orθjc=0.095°C/Watt for the2packages.Thermal resistance(junction-to-ball)=R jb orθjb=3.5°C/Watt for the CBGA package.Thermal resistance(junction-to-bottom SCI)=R js orθjs=3.7°C/Watt for the CI-CGA package.The junction temperature can be calculated from the junction to ambient thermal resis-tance,as follow:Junction temperature:T j=T a+(R jc+R cs+R sa)*PWhere:T a is the ambient temperature in the vicinityof the deviceR jc is the die junction-to-case thermalresistance of the deviceR cs is the case-to-heat sink thermalresistance of the interface materialR sa is the heat sink-to-ambientthermal resistanceP is the power dissipated by the deviceDuring operation,the die-junction temperatures(T j)should be maintained less than thevalue specified in Table6.The thermal resistance of the thermal interface material(R cs)is typically about1°C/Watt.Assuming a T a of85°C and a consumption(P)of3.6Watts,the junction temperature ofthe device would be as follow:T j=85°C+(0.095°C/Watt+1°C/Watt+R sa)*3.5Watts.For the Thermalloy heat sink#2328B,the heat sink-to-ambient thermal resistance(R sa)versus airflow velocity is shown in Figure4.Figure4.CBGA Thermal Management ExampleAssuming an air velocity of1.0m/sec,the associated overall thermal resistance andjunction temperature,found in Table7will result.Table7.Thermal Resistance and Junction TemperatureVendors such as Aavid Engineering Inc.,Thermalloy,and Wakefield Engineering cansupply heat sinks with a wide range of thermal performance.Power Consideration The PowerPC603r is a microprocessor specifically designed for low-power operation.As the603e microprocessor version,the603r provides both automatic and pro-gram-controllable power reduction modes for progressive reduction of powerconsumption.This chapter describes the hardware support provided by the603r forpower management.Dynamic Power Management Dynamic power management automatically powers up and down the individual execu-tion units of the603r,based upon the contents of the instruction stream.For example,ifno floating-point instructions are being executed,the floating-point unit is automaticallypowered down.Power is not actually removed from the execution unit;instead,eachexecution unit has an independent clock input,which is automatically controlled on aclock-by-clock basis.Since CMOS circuits consume negligible power when they are notswitching,stopping the clock to an execution unit effectively eliminates its power con-sumption.The operation of DPM is completely transparent to software or any externalhardware.Dynamic power management is enabled by setting bit11in HID0onpower-up,of following HRESET.TSPC603R Programmable Power Modes The603r provides four programmable power states—full power,doze,nap and sleep.Software selects these modes by setting one(and only one)of the three power savingmode bits.Hardware can enable a power management state through external asynchro-nous interrupts The hardware interrupt causes the transfer of program flow to interrupthandler code.The appropriate mode is then set by the software.The603r provides aseparate interrupt and interrupt vector for power management—the system manage-ment interrupt(SMI).The603r also contains a decrement timer which allows it to enterthe nap or doze mode for a predetermined amount of time and then return to full poweroperation through the decrementer interrupt(DI).Note that the603r cannot switch fromon power management mode to another without first returning to full on mode.The napand sleep modes disable bus snooping;therefore,a hardware handshake is provided toensure coherency before the603r enters these power management modes.Table8summarizes the four power states.Table8.Power PC603r Microprocessor Programmable Power ModesPower Management Modes The following sections describe the characteristics of the603r’s power managementmodes,the requirements for entering and exiting the various modes,and the systemcapabilities provided by the603r while the power management modes are active.FULL-Power Mode with DPM Disabled:Full-power mode with DPM disabled powermode is selected when the DPM enable bit(bit11)in HID0is cleared.•Default state following power-up and HRESET.•All functional units are operating at full processor speed at all times.FULL-Power Mode with DPM Enabled:Full-power mode with DPM enabled(HID0[11]=1)provides on-chip power management without affecting the functionality or perfor-mance of the603r.•Required functional units are operating at full processor speed.•Functional units are clocked only when needed.•No software or hardware intervention required after mode is set.•Software/hardware and performance transparent.Doze Mode:Doze mode disables most functional units but maintains cache coherencyby enabling the bus interface unit and snooping.A snoop hit will cause the603r toenable the data cache,copy the data back to memory,disable the cache,and fullyreturn to the doze state.•Most functional units disabled.•Bus snooping and time base/decrementer still enabled.•Dose mode sequence:-Set doze bit(HID0[8)=1).-603r enters doze mode after several processor clocks.•Several methods of returning to full-power mode:-Assert INT,SMI,MCP or decrementer interrupts.-Assert hard reset or soft reset.•T ransition to full-power state takes no more than a few processor cycles.•PLL running and locked to SYSCLK.Nap Mode:The nap mode disables the603r but still maintains the phase locked loop (PLL)and the time base/decrementer.The time base can be used to restore the603r to full-on state after a programmed amount of time.Because bus snooping is disabled for nap and sleep mode,a hardware handshake using the quiesce request and quiesce acknowledge signals are requires to maintain data coherency.The 603r will assert the signal to indicate that it is ready to disable bus snooping. When the system has ensured that snooping is no longer necessary,it will assertand the603r will enter the sleep or nap mode.•Time base/decrementer still enabled.•Most functional units disabled(including bus snooping).•All nonessential input receivers disables.•Nap mode sequence:-Set nap bit(HID0[9]=1)-603r asserts quiesce request signal-System asserts quiesce acknowledge signal-603r enters sleep mode after several processor clocks•Several methods of returning to full-power mode:-Assert INT,SPI,MCP or decrementer interrupts-Assert hard reset or soft reset•T ransition to full-power takes no more than a few processor cycles.•PLL running and locked to SYSCLK.Sleep Mode:Sleep mode consumes the least amount of power of the four modes since all functional units are disabled.To conserve the maximum amount of power,the PLL may be disabled and the SYSCLK may be removed.Due to the fully static design of the 603r,internal processor state is preserved when no internal clock is present.Because the time base and decrementer are disabled while the603r is in sleep mode,the603r’s time base contents will have to be updated from an external time base following sleep mode if accurate time-of-day maintenance is required.Before the603r enters the sleep mode,the603r will assert the QREQ signal to indicate that it is ready to disable bus snooping.When the system has ensured that snooping is no longer necessary,it will assert QACK and the603r will enter the sleep mode.•All functional units disabled(including bus snooping and time base).•All nonessential input receivers disabled:-Internal clock regenerators disabled-PLL still running(see below)•Sleep mode sequence:-Set sleep bit(HID0[10]=1)-603r asserts quiesce request-System asserts quiesce acknowledge-603r enters sleep mode after several processor clocksTSPC603R•Several methods of returning to full-power mode:-Assert INT ,SMI,or MCP interrupts -Assert hard reset or soft reset•PLL may be disabled and SYSCLK may be removed while in sleep mode.•Return to full-power mode after PLL and SYSCLK disabled in sleep mode:-Enable SYSCLK-Reconfigure PLL into desired processor clock mode-System logic waits for PLL startup and relock time (100µsec)-System logic asserts one of the sleep recovery signals (for example,INT or SMI)Power Management Software ConsiderationsSince the 603r is a dual issue processor with out-of-order execution capability,care must be taken in how the power management mode is entered.Furthermore,nap and sleep modes require all outstanding bus operations to be completed before the power management mode is entered.Normally during system configuration time,one of the power management modes would be selected by setting the appropriate HID0mode ter on,the power management mode is invoked by setting the MSR[POW]bit.To pro-vide a clean transition into and out of the power management mode,the stmsr [POW]should be preceded by a sync instruction and followed by an isync instruction.Power DissipationDD power (AV DD ).OV DD power is system dependent but is typically ≤10%of V DD .Worst-case AV DD =15mW.2.Typical power is an average value measured at V DD =AV DD =2.5V ,OV V =3.3V ,in a system executing typical applicationsand benchmark sequences.3.Maximum power is measured at V DD =2.625V using a worst-case instruction mix.4.To calculate the power consumption at low temperature (-55°C),use a factor of 1.25.Table 9.Power Dissipation (1)(2)(3)(4)V DD /A V DD =2.5±5%V,O V DD =3.3±5%V,GND =0V,0°C ≤T C ≤125°C CPU Clock FrequencyMarking Each microcircuit is legible and permanently marked with the following information asminimum:•A TMEL logo•Manufacturer’s part number•Class B identification if applicable•Date-code of inspection lot•ESD identifier if available•Country of manufacturingElectrical CharacteristicsGeneral Requirements All static and dynamic electrical characteristics specified for inspection purposes and therelevant measurement conditions are given below:•Table10:Static electrical characteristics for the electrical variants•Table11:Dynamic electrical characteristics for the603rThese specifications are for166MHz to300MHz processor core frequencies.The pro-cessor core frequency is determined by the bus(SYSCLK)frequency and the settings ofthe PLL_CFG0to PLL_CFG3signals.All timings are respectively specified to the risingedge of SYSCLK.Static CharacteristicsTable10.Electrical CharacteristicsV=A V=2.5V±5%;O V=3.3±5%V,GND=0V,-55°C≤TC≤125°C2.Capacitance is periodically sampled rather than100%tested.3.Leakage currents are measured for nominal OV DD and V DD or both OV DD and V DD.Same variation(for example,both V DDand OV DD vary by either+5%or-5%).TSPC603RDynamic Characteristics•Clock AC SpecificationsTable 11provides the clock AC timing specifications as defined in Figure 5.2.Cycle-to-cycle jitter is guaranteed by design.3.Timing is guaranteed by design and characterization,and is not tested.4.PLL relock time is the maximumamount of time required for PLL lock after a stable V DD ,OV DD ,AV DD and SYSCLK are reached during the power-on reset sequence.This specification also applies when the PLL has been disabled and subse-quently re-enabled during sleep mode.Also note that must be held asserted for a minimum of 255bus clocks after the PLL relock time (100µs)during the power-on reset sequence.5.Caution :The SYSCLK frequency and PLL_CFG[0-3]settings must be chosen such that the resulting SYSCLK (bus)fre-quency ,CPU (core)frequency,and PLL (VCO)frequency do not exceed their respective maximum or minimum operating frequencies.Refer to the PLL_CFG[0-3]signal description for valid PLL_CFG[0-3]settings.Figure 5.SYSCLK Input Timing DiagramTable 11.Clock AC Timing Specifications (1)(2)(3)(4)V V V•Input AC specificationsTable 12provides the input AC timing specifications for the 603r as defined in Figure 6and Figure 7.of the input SYSCLK.Both input and output timings are measured at the pin.See Figure 7.2.Address/data/transfer attribute input signals are composed of thefollowing:A[0-31],AP[0-3],TT[0-4],TC[0-1],TBST,TSIZ[0-2],DH[0-31],DL[0-31],DP[9-7].3.All other input signals are composed of the following:TS,ABB,DBB,ARTRY ,BG,AACK,DBG,DBWO,TA,DRTRY ,TEA,,TBEN,4.The setup and hold time is with respect to the rising edge of HRESET.See Figure 7.5.t sysclk is the period of the external clock (SYSCLK)in nanoseconds (ns).The numbers given in the table must be multipliedby the period of SYSCLK to compute the actual time duration (in nanoseconds)of the parameter in question.6.These values are guaranteed by design,and are not tested.7.This specification is for configuration mode only.Also note that HRESET must be held asserted for a minimum of 255busclocks after the PLL relock time (100µs)during the power-on reset sequence.Figure 6.Input Timing DiagramTable 12.Input AC Timing Specifications (1)V V VTSPC603R Figure7.Mode Select Input Timing Diagram•Output AC SpecificationsTable13provides the output AC timing specifications for the603r(shown in Figure8). Table13.Output AC Timing Specifications(1)(2)V=A V=2.5V±5%;O V=3.3±5%V,GND=0V,C=50pF,-55°C≤Tnal in question.Both input and output timings are measured at the pin.See Figure8.2.All maximum timing specifications assume C L=50pF.3.This minimum parameter assumes C L=0pF.4.SYSCLK to output valid(5.5V to0.8V)includes the extra delay associated with discharging the external voltage from5.5V to0.8V instead of from V DD to0.8V(5V CMOS levels instead of3.3V CMOS levels).5.t sysclk is the period of the external bus clock(SYSCLK)in nanoseconds(ns).The numbers given in the table must be multi-plied by the period of SYSCLK to compute the actual time duration(ns)of the parameter in question.6.Output signal transitions from GND to2.0V or V DD to0.8V.7.Nominal precharge width for ABB and DBB is0.5*t sysclk.8.Nominal precharge width for is1.0*t sysclk.Figure8.Output Timing DiagramJTAG AC TimingSpecificationsTable14.JTAG AC Timing Specifications(independent of SYSCLK)V=A V=2.5V±5%;O V=3.3±5%V,GND=0V,C=50pF,-55°C≤T21TSPC603R2125A –HIREL –04/022.Non-test signal input timing with respect to TCK.3.Non-test signal output timing with respect to TCK.Figure 9.Clock Input Timing DiagramFigure 10.TRST Timing DiagramTable 14.JTAG AC Timing Specifications (independent of SYSCLK)V =A V =2.5V ±5%;O V =3.3±5%V,GND =0V,C =50pF,-55°C ≤T22TSPC603R2125A –HIREL –04/02Figure 11.Boundary-scan Timing DiagramFigure 12.Test Access Port Timing DiagramFunctional DescriptionPowerPC Registers andProgramming Model The PowerPC architecture defines register-to-register operations for most computa-tional instructions.Source operands for these instructions are accessed from theregisters or are provided as immediate values embedded in the instruction opcode.Thethree-register instruction format allows specification of a target register distinct from thetwo source operands.Load and store instructions transfer data between registers andmemory.PowerPC processors have two levels of privilege -supervisor mode of operation (typi-cally used by the operating system)and user mode of operation (used by the applicationsoftware).The programming models incorporate 32GPRs,32FPRs,special-purposeregisters (SPRs)and several miscellaneous registers.Each PowerPC microprocessoralso has its own unique set of hardware implementation (HID)registers.23TSPC603R2125A –HIREL –04/02Having access to privilege instructions,registers,and other resources allows the operat-ing system to control the application environment (providing virtual memory andprotecting operating-system and critical machine resources).Instructions that controlthe state of the processor,the address translation mechanism,and supervisor registerscan be executed only when the processor is operating in supervisor mode.The following sections summarize the PowerPC registers that are implemented in the603r.General-Purpose Registers(GPRs)The PowerPC architecture defines 32user-level,general-purpose registers (GPRs).These registers are either 32bits wide in 32-bit PowerPC microprocessors and 64bitswide in 64-bit PowerPC microprocessors.The GPRs serve as the data source or desti-nation for all integer instructions.Floating-Point Registers(FPRs)The PowerPC architecture also defines 32user-level,64-bit floating-point registers (FPRs).The FPRs serve as the data source or destination for floating-point instructions.These registers can contain data objects of either single-or double-precision float-ing-point formats.Condition Register (CR)The CR is a 32-bit user-level register that consists of eight four-bit fields that reflect theresults of certain operations,such as move,integer and floating-point compare,arith-metic,and logical instructions,and provide a mechanism for testing and branching.Floating-Point Status andControl Register (FPSCR)The floating-point status and control register (FPSCR)is a user-level register that con-tains all exception signal bits,exception summary bits,exception enable bits,androunding control bits needed for compliance with the IEEE 754standard.Machine State Register (MSR)The machine state register (MSR)is a supervisor-level register that defines the state ofthe processor.The contents of this register are saved when an exception is taken andrestored when the exception handling completes.The 603r implements the MSR as a32-bit register,64-bit PowerPC processors implement a 64-bit MSR.Segment Registers (SRs)For memory management,32-bit PowerPC microprocessors implement sixteen 32-bitsegment registers (SRs).To speed access,the 603r implements the segment registersas two arrays;a main array (for data memory accesses)and a shadow array (for instruc-tion memory accesses).Loading a segment entry with the Move to Segment Register(STSR)instruction loads both arrays.。

5962-9650501QXA资料

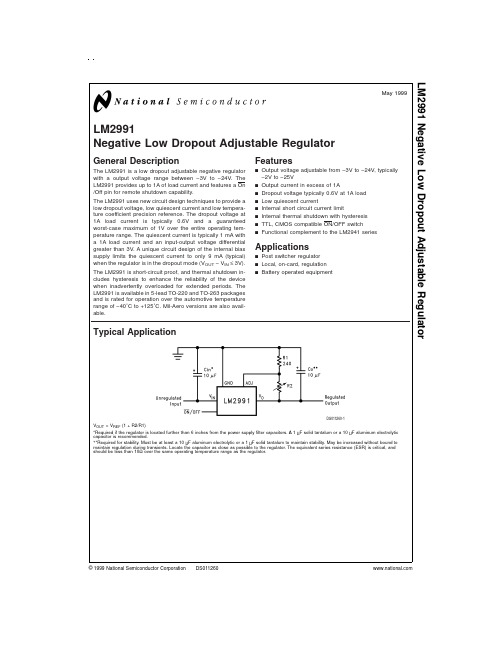

LM2991Negative Low Dropout Adjustable RegulatorGeneral DescriptionThe LM2991is a low dropout adjustable negative regulator with a output voltage range between −3V to −24V.The LM2991provides up to 1A of load current and features a On /Off pin for remote shutdown capability.The LM2991uses new circuit design techniques to provide a low dropout voltage,low quiescent current and low tempera-ture coefficient precision reference.The dropout voltage at 1A load current is typically 0.6V and a guaranteed worst-case maximum of 1V over the entire operating tem-perature range.The quiescent current is typically 1mA with a 1A load current and an input-output voltage differential greater than 3V.A unique circuit design of the internal bias supply limits the quiescent current to only 9mA (typical)when the regulator is in the dropout mode (V OUT −V IN ≤3V).The LM2991is short-circuit proof,and thermal shutdown in-cludes hysteresis to enhance the reliability of the device when inadvertently overloaded for extended periods.The LM2991is available in 5-lead TO-220and TO-263packages and is rated for operation over the automotive temperature range of −40˚C to +125˚-Aero versions are also avail-able.Featuresn Output voltage adjustable from −3V to −24V,typically −2V to −25Vn Output current in excess of 1An Dropout voltage typically 0.6V at 1A load n Low quiescent currentn Internal short circuit current limitn Internal thermal shutdown with hysteresis n TTL,CMOS compatible ON/OFF switchn Functional complement to the LM2941seriesApplicationsn Post switcher regulator n Local,on-card,regulation n Battery operated equipmentTypical ApplicationDS011260-1V OUT =V REF (1+R2/R1)*Required if the regulator is located further than 6inches from the power supply filter capacitors.A 1µF solid tantalum or a 10µF aluminum electrolytic capacitor is recommended.**Required for stability.Must be at least a 10µF aluminum electrolytic or a 1µF solid tantalum to maintain stability.May be increased without bound to maintain regulation during transients.Locate the capacitor as close as possible to the regulator.The equivalent series resistance (ESR)is critical,and should be less than 10Ωover the same operating temperature range as the regulator.May 1999LM2991Negative Low Dropout Adjustable Regulator©1999National Semiconductor Corporation Connection Diagrams and Ordering Information5-Lead TO-220Straight LeadsDS011260-9Front ViewOrder Number LM2991T See NS Package Number T05A5-Lead TO-220Bent,Staggered LeadsDS011260-2Front ViewOrder Number LM2991T Flow LB03See NS Package Number T05DTO2635-Lead Surface-Mount PackageDS011260-11Top ViewDS011260-12Side ViewOrder Number LM2991S See NS Package Number TS5B16-Lead Ceramic Dual-in-Line PackageDS011260-29Top ViewOrder Number LM2991J-QMLV5962-9650501VEAOrder Number LM2991J-QML5962-9650501QEASee NS Package Number J16A16-Lead Ceramic Surface-Mount PackageDS011260-30Top ViewOrder Number LM2991WG-QML5962-9650501QXASee NS Package Number WG16A 2Absolute Maximum Ratings(Note1)If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.Input Voltage−26V to+0.3V ESD Susceptibility(Note2)2kV Power Dissipation(Note3)Internally limited Junction Temperature(T Jmax)125˚C Storage Temperature Range−65˚C to+150˚C Lead Temperature(Soldering,10sec.)230˚COperating Ratings(Note1)Junction Temperature Range(T J)−40˚C to+125˚C Maximum Input Voltage(Operational)−26VElectrical CharacteristicsV IN=−10V,V O=−3V,I O=1A,C O=47µF,R1=2.7k,T J=25˚C,unless otherwise specified.Boldface limits apply overthe entire operating junction temperature range.Parameter Conditions Typical Min Max Units(Note4)Reference Voltage5mA≤I O≤1A−1.210−1.234−1.186V5mA≤I O≤1A,−1.27−1.15VV O−1V≥V IN≥−26VOutput Voltage−2−3V Range V IN=−26V−25−24V Line Regulation I O=5mA,V O−1V≥V IN≥−26V0.0040.04%/V Load Regulation50mA≤I O≤1A0.040.4% Dropout Voltage I O=0.1A,∆V O≤100mV0.10.2V0.3I O=1A,∆V O≤100mV0.60.8V1Quiescent Current I O≤1A0.75mA Dropout Quiescent V IN=V O,I O≤1A1650mA CurrentRipple Rejection V ripple=1Vrms,f ripple=1kHz,6050dBI O=5mAOutput Noise10Hz−100kHz,I O=5mA200450µVON/OFF Input(V OUT:ON) 1.20.8V Voltage(V OUT:OFF) 1.3 2.4ON/OFF Input V ON/OFF=0.8V(V OUT:ON)0.110µA Current V ON/OFF=2.4V(V OUT:OFF)40100Output Leakage V IN=−26V,V ON/OFF=2.4V60250µA Current V OUT=0VCurrent Limit V OUT=0V2 1.5ANote1:Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.Operating Ratings indicate conditions for which the deivce is in-tended to be functional,but do not guarantee specific performance limits.For guaranteed specifications and test conditions,see the Electrical Characteristics.Note2:Human body model,100pF discharged through a1.5kΩresistor.Note3:The maximum power dissipation is a function of T Jmax,θJA and T A.The maximum allowable power dissipation at any ambient temperature is P D=(T Jmax−T A)/θJA.If this dissipation is exceeded,the die temperature will rise above125˚C and the LM2991will go into thermal shutdown.For the LM2991,the junction-to-ambient thermal resistance is53˚C/W for the TO-220,73˚C/W for the TO-263,and junction-to-case thermal resistance is3˚C.If the TO-263package is used,the thermal resistance can be reduced by increasing the PC board copper area thermally connected to the ing0.5square inches of copper area,θJA is50˚C/W;with1square inch of copper area,θJA is37˚C/W;and with1.6or more square inches of copper area,θJA is32˚C/W.Note4:Typicals are at T J=25˚C and represent the most likely parametric norm.3Typical Performance CharacteristicsDropout VoltageDS011260-13Normalized Output VoltageDS011260-14Output VoltageDS011260-15Output Noise Voltage DS011260-16Quiescent Current DS011260-17Maximum Output CurrentDS011260-18Line Transient Response DS011260-19Load Transient Response DS011260-20Maximum Output CurrentDS011260-21Ripple Rejection DS011260-22Output Impedance DS011260-23ON /OFF Control VoltageDS011260-24 4Typical Performance Characteristics(Continued)Application HintsEXTERNAL CAPACITORSThe LM2991regulator requires an output capacitor to main-tain stability.The capacitor must be at least 10µF aluminum electrolytic or 1µF solid tantalum.The output capacitor’s ESR must be less than 10Ω,or the zero added to the regu-lator frequency response by the ESR could reduce the phase margin,creating oscillations.The shaded area in the Output Capacitor ESR graph indicates the recommended ESR range.An input capacitor,of at least 1µF solid tantalum or 10µF aluminum electrolytic,is also needed if the regulator is situated more than 6inches from the input power supply filter.MINIMUM LOADA minimum load current of 500µA is required for proper op-eration.The external resistor divider can provide the mini-mum load,with the resistor from the adjust pin to ground set to 2.4k Ω.SETTING THE OUTPUT VOLTAGEThe output voltage of the LM2991is set externally by a resis-tor divider using the following equation:V OUT =V REF x (1+R 2/R 1)−(I ADJ x R 2)where V REF =−1.21V.The output voltage can be pro-grammed within the range of −3V to −24V,typically an evenAdjust Pin CurrentDS011260-25Low Voltage BehaviorDS011260-26Maximum Power Dissipation (TO-220)DS011260-27Maximum Power Dissipation (TO-263)(See Note 3)DS011260-28Output Capacitor ESR RangeDS011260-55Application Hints(Continued)greater range of −2V to −25V.The adjust pin current is about 60nA,causing a slight error in the output voltage.However,using resistors lower than 100k Ωmakes the adjust pin cur-rent negligible.For example,neglecting the adjust pin cur-rent,and setting R2to 100k Ωand V OUT to −5V,results in an output voltage error of only 0.16%.ON/OFF PINThe LM2991regulator can be turned off by applying a TTL or CMOS level high signal to the ON/OFF pin (see Adjustable Current Sink Application).FORCING THE OUTPUT POSITIVEDue to an internal clamp circuit,the LM2991can withstand positive voltages on its output.If the voltage source pulling the output positive is DC,the current must be limited to 1.5A.A current over 1.5A fed back into the LM2991could damage the device.The LM2991output can also withstand fast posi-tive voltage transients up to 26V,without any current limiting of the source.However,if the transients have a duration of over 1ms,the output should be clamped with a Schottky di-ode to ground.Typical ApplicationsFully Isolated Post-Switcher RegulatorDS011260-6Adjustable Current SinkDS011260-10 6Equivalent SchematicD S 011260-87Physical Dimensions inches(millimeters)unless otherwise noted5-Lead T0-220,Straight Leads(T)Order Number LM2991TNS Package Number T05A5-Lead T0-220,Bent,Staggered Leads(T)Order Number LM2991T Flow LBO3NS Package Number T05D8Physical Dimensions inches(millimeters)unless otherwise noted(Continued)TO-2635-Lead Plastic Surface Mount PackageOrdering Number LM2991SNS Package Number TS5B9Physical Dimensions inches(millimeters)unless otherwise noted(Continued)16-Lead Ceramic Dual-in-Line PackageOrder Number LM2991J-QMLV5962-9650501VEAOrder Number LM2991J-QML5962-9650501QEANS Package Number J16A10Physical Dimensionsinches (millimeters)unless otherwise noted (Continued)LIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION.As used herein:1.Life support devices or systems are devices or systems which,(a)are intended for surgical implant into the body,or (b)support or sustain life,and whose failure to perform when properly used in accordance with instructions for use provided in the labeling,can be reasonably expected to result in a significant injury to the user.2.A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system,or to affect its safety or effectiveness.National Semiconductor Corporation AmericasTel:1-800-272-9959Fax:1-800-737-7018Email:support@National Semiconductor EuropeFax:+49(0)180-5308586Email:europe.support@Deutsch Tel:+49(0)180-5308585English Tel:+49(0)180-5327832Français Tel:+49(0)180-5329358Italiano Tel:+49(0)180-5341680National Semiconductor Asia Pacific Customer Response Group Tel:65-2544466Fax:65-2504466Email:sea.support@National Semiconductor Japan Ltd.Tel:81-3-5639-7560Fax:81-3-5639-750716-Lead Ceramic Surface-Mount PackageOrder Number LM2991WG-QML5962-9650501QXANS Package Number WG16ALM2991Negative Low Dropout Adjustable RegulatorNational does not assume any responsibility for use of any circuitry described,no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.元器件交易网。

API-526-2009(中文版)-上

API-526-2009(中文版)-上钢制法兰连接泄压阀——标准API 5262009年4月,第6版钢制法兰连接泄压阀1 范围此标准是钢制法兰连接泄压阀的采购规范。

弹簧直接荷载式和先导操作泄压阀的基本要素如下:——流道命名及面积——阀门进、出口规格及压力等级——材料——压力温度额定值——进、出口中心到法兰面的尺寸2 引用标准下列引用的文件对本文件的应用是不可缺少的。

对于标明日期的引用文件,仅该版适用。

未标明日期的引用文件,其最新版(包括任何修改)适用。

推荐规程API 520(所有部分),规格,选型及泄压设备现安装标准API 527,泄压阀阀座密封ASME B16.5,管法兰和法兰组件ASME 锅炉和压力容器规范(BPVC),第Ⅷ卷:压力容器,第1、2篇ASME BPVC,第Ⅱ部分:材料:ASME SA-216,可熔焊高温碳钢铸件ASME SA-217,高温承压马氏体及合金钢铸件ASME SA-351,承压奥氏体,奥氏体-铁素体(双相)钢铸件ASME SA-494,镍及镍合金铸件3 术语和定义API 520第Ⅰ部分定义了泄压阀术语。

4 责任4.1 买方为下列内容负首要责任:a)选择泄压阀的型号及所需的压力温度等级;b)指定材料能够抗工艺流体和环境腐蚀;c)基于排泄条件选择最小的流道面积。

排泄条件来自对泄压系统全面认识及适用规范和法规的要求;d)提供规格和选型数据。

4.2 制造方为下列内容负首要责任:a)设计制造的泄压阀满足本标准和采购规范的要求;b)发布基于认证测试数据的排泄能力;K 1.838L 2.853M 3.60N 4.34P 6.38Q 11.05R 16.00T 26.007 设计7.1 一般要求本标准讨论的泄压阀的设计制造应符合ASME BPVC第Ⅷ卷泄压设备的应用要求。

7.2 流道面积的确定最小有效流道面积应根据API 520第1部分确定。

7.3 阀门选型本标准中描述的阀门,进出口法兰规格和压力温度等级应按照表3到表16(弹簧荷载式泄压阀)和表17到表30(先导操作泄压阀)中的数据。

5962-8874701YA中文资料

3.3HERMETIC TO-3 FIXED VOLTAGE NEGATIVEREGULATORS APPROVED TO DESC DRAWINGSFEATURES•Output Voltages: -5V, -12V, -15V•Output Voltages Set Internally to ±1%•Built-In Thermal Overload Protection•Short Circuit Current Limiting•Similar To Industry Standards 7905, 7912, 7915•Hi-Rel Screening AvailableDESCRIPTIONThese three terminal negative regulators are supplied in a hermetically sealed TO-3metal package . All protective features are designed into the circuit, including thermal shutdown, current limiting and safe-area control. With heat sinking, they can deliver over 1.5 amps of output current. These units feature internally trimmed output voltages to ±1% of nominal voltage. Standard voltages are -5V, -12V, -15V. These units are ideally suited for Military applications where a hermetically sealed package is required.PART NUMBER DESIGNATORStandard Military Drawing Number Omnirel Part Number5962-8874601 YX OM1905NKM5962-8874701 YX OM1912NKM5962-8874801 YX OM1915NKMOM1915NKM OM1905NKM OM1912NKMOM1905NKM - OM1915NKM3.3ELECTRICAL CHARACTERISTICS -5 Volt VIN= -10V, I o= 500mA, -55°C T A 125°C (unless otherwise specified) Parameter Symbol Test Conditions Min.Max.UnitOutput Voltage V OUT T A= 25°C-4.95-5.05VV IN= -7.5V to -20V•-4.85-5.15VI O = 5mA to 1.0 A, P<20WLine Regulation V RLINE V IN= -7.5V to -20V12mV (Note 1)•25mV(Note 4)V IN= -8.0V to -12V5mV•12mV Load Regulation V RLOAD I O = 5mA to 1.5 Amp20mV (Note 1)•25mVI O = 250mA to 750 mA15mV•30mV Standby Current Drain I SCD 2.5mA• 3.0mA Standby Current Drain D I SCD V IN= -7.0V to -20V•0.4mA Change With Line(Line)Standby Current Drain D I SCD I O= 5mA to 1000mA•0.4mA Change With Load(Load)Dropout Voltage V DO D V OUT= 100mV, I O=1.0A• 2.5V Peak Output Current I O (pk) T A= 25°C 1.5 3.3A Short Circuit Current I DS V IN= -35V 1.2A (Note 2)• 2.8A Ripple Rejection D V IN f =120 Hz, D V IN= -10V63dBD V OUT(Note 3)•60dBOutput Noise Voltage N O T A= 25°C, f =10 Hz to 100KHz40µV/V (Note 3)RMS Long Term Stability D V OUT T A= 25°C, t = 1000 hrs.75mV (Note 3)D tNotes:1.Load and Line Regulation are specified at a constant junction temperature. Pulse testing with low duty cycle is used.Changes in output voltage due to heating effects must be taken into account separately.2.Short Circuit protection is only assured up to V IN= -35V.3.If not tested, shall be guaranteed to the specified limits.The • denotes the specifications which apply over the full operating temperature range.ABSOLUTE MAXIMUM RATINGS @ 25°CInput Voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -35 V Operating Junction Temperature Range . . . . . . . . . . . . . . . . . . . . . . . . . . .- 55°C to + 150°C Storage Temperature Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . - 65°C to + 150°C Typical Power/Thermal Charateristics:Rated Power @ 25°C T C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20WT A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.6W Thermal Resistance q JC . . . . .. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4.2°C/W aa q JA.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42°C/WOM1905NKM - OM1915NKM3.3PLANE2 PLCS.Pin Connection Pin 1: Ground Pin 2: Output Case: InputOM1905NKM - OM1915NKM3.3。

5962-88769022A资料

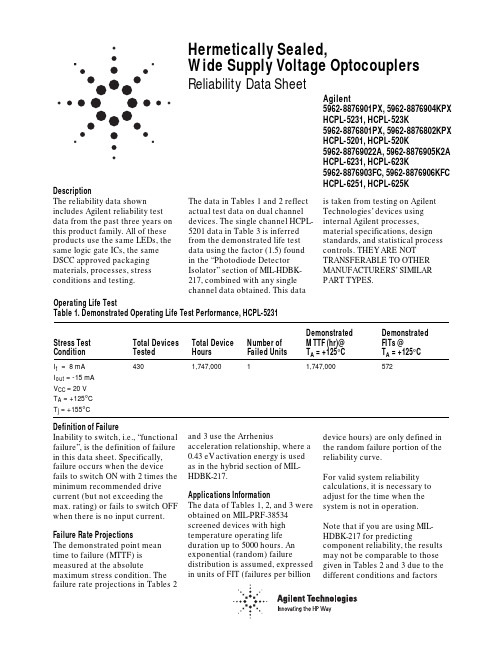

Hermetically Sealed,Wide Supply Voltage OptocouplersReliability Data SheetDescriptionThe reliability data shown includes Agilent reliability test data from the past three years on this product family. All of these products use the same LEDs, the same logic gate ICs, the same DSCC approved packaging materials, processes, stress conditions and testing.The data in Tables 1 and 2 reflect actual test data on dual channel devices. The single channel HCPL-5201 data in Table 3 is inferred from the demonstrated life test data using the factor (1.5) found in the “Photodiode Detector Isolator” section of MIL-HDBK-217, combined with any single channel data obtained. This dataDefinition of FailureInability to switch, i.e., “functional failure”, is the definition of failure in this data sheet. Specifically,failure occurs when the device fails to switch ON with 2 times the minimum recommended drive current (but not exceeding the max. rating) or fails to switch OFF when there is no input current.Failure Rate ProjectionsThe demonstrated point mean time to failure (MTTF) is measured at the absolutemaximum stress condition. The failure rate projections in Tables 2and 3 use the Arrheniusacceleration relationship, where a 0.43 eV activation energy is used as in the hybrid section of MIL-HDBK-217.Applications InformationThe data of Tables 1, 2, and 3 were obtained on MIL-PRF-38534screened devices with high temperature operating life duration up to 5000 hours. An exponential (random) failuredistribution is assumed, expressed in units of FIT (failures per billionis taken from testing on Agilent Technologies’ devices using internal Agilent processes,material specifications, design standards, and statistical process controls. THEY ARE NOT TRANSFERABLE TO OTHER MANUFACTURERS’ SIMILAR PART TYPES.device hours) are only defined in the random failure portion of the reliability curve.For valid system reliability calculations, it is necessary to adjust for the time when the system is not in operation.Note that if you are using MIL-HDBK-217 for predictingcomponent reliability, the results may not be comparable to those given in Tables 2 and 3 due to the different conditions and factorsOperating Life TestTable 1. Demonstrated Operating Life Test Performance, HCPL-5231Demonstrated Demonstrated Stress Test Total Devices Total Device Number of MTTF (hr)@FITs @Condition Tested Hours Failed Units T A = +125°C T A = +125°C I f = 8 mA 4301,747,00011,747,000572I out = -15 mA V CC = 20 V T A = +125°C T j = +155°CAgilent5962-8876901PX, 5962-8876904KPX HCPL-5231, HCPL-523K5962-8876801PX, 5962-8876802KPX HCPL-5201, HCPL-520K5962-88769022A, 5962-8876905K2A HCPL-6231, HCPL-623K5962-8876903FC, 5962-8876906KFC HCPL-6251, HCPL-625K Data subject to change.Copyright © 2000 Agilent Technologies, Inc.Obsoletes 5967-6008E 5968-9397E (2/00)Environmental TestingAll high reliability hermeticoptocouplers listed meet the 100%screening and qualityconformance inspection testing of MIL-PRF-38534, class H or class K as applicable.Table 4. ESDS Classification per Method 3015, MIL-STD-883that have been accounted for in MIL-HDBK-217. For example, it is unlikely that your application will exercise all available channels at full rated power with the LED(s)always ON as Agilent testing does.Thus, your application total power and duty cycle must be carefullyconsidered when comparing Tables 2 and 3 to predictions using MIL-HDBK-217.Electrostatic Discharge SensitivityPart NumberESD Class 5962-8876904KPX, HCPL-523K 35962-8876901PX, HCPL-523135962-8876802KPX, HCPL-520K 15962-8876801PX, HCPL-520115962-8876905K2A, HCPL-623K 15962-88769022A, HCPL-623115962-8876906KFC, HCPL-625K 35962-8876903FC, HCPL-62513Table 3. Reliability Projections for Single Channel Devices Listed in Title Typical (60% Confidence)90% Confidence AmbientJunctionMTTF FITs MTTF FITs Temperature (°C)Temperature (°C)(hr/fail)(fail/109hr)(hr/fail)(fail/109hr))1251451,297,000771674,0001,4841201401,498,000668778,0001,2851101302,018,0004961,051,0009521001202,759,0003621,440,000695901103,836,0002612,006,000499801005,429,0001842,844,00035270907,830,0001284,111,000243608011,531,000876,069,000165507017,369,000589,164,000109406026,814,0003714,186,00070305042,522,0002422,560,00044254554,133,0001828,763,00035Table 2. Reliability Projections for Dual Channel Devices Listed in Title Typical (60% Confidence)90% Confidence AmbientJunctionMTTF FITs MTTF FITs Temperature (°C)Temperature (°C)(hr/fail)(fail/109hr)(hr/fail)(fail/109hr))125155865,0001,157449,0002,227120150992,0001,009515,0001,9411101401,317,000759686,0001,4581001301,774,000564925,0001,081901202,427,0004121,268,000789801103,374,0002961,767,000566701004,774,0002092,505,00039960906,886,0001453,622,000276508010,141,000995,346,000187407015,274,000658,073,000124306023,580,0004212,496,00080255529,589,0003415,703,00064。

API598中文

最小试验压力

试验项目

磅/平方英寸(表压) 巴

阀门(蝶阀和止回阀除外)

高压密封和上密封

低压密封和上密封

60-100

4-7

蝶阀

高压密封

低压密封

60-100

4-7

止回阀

高压密封

125 磅级(铸铁)

NPS 2~12

200 14

NPS14~48

150 11

250 磅级(铸铁)

NPS 2~12

500 35

NPS 14~24

0

C

D

24

C

D

40

C

D

56

c

D

· 对于液体试验,1毫升(cm3)相当于16滴。 :在规定的最短试验持续时间内(见表4)无泄漏.对于液体试验,“o”滴表示在每 个规定的最短试验持续即闭 内无可见泄漏.对于气体试验,“o”气泡表示在每个规定的最短试验持续时间内泄 漏量小于1个气泡。 ‘最大允许泄漏率应是公称通径每英寸每分钟o.18立方英寸(3cm)。 ‘最大允许泄漏率应是公称通径每英寸每小时1.5标准立方英尺(o.04Zm')。 ·对于规格大于NPS 24的止回阀,允许的泄漏率应由买方与制造厂商定。 3.9.3 使用非金属(如,陶瓷)密封材料的阀门,其密封试验的允许泄漏率应与表5规 定的同类型和规格的金属密封阀门相同。 第4章 压力试验方法 4.1 概述 4.1.1 对于具有允许应急的或补充的向密封面或填料部位注入密封脂这种结构的阀 门,在试验时,注入系统应是空的和不起作用的,油封式旋塞阀除外。 4.1.2 当液体作为试验介质进行试验时,阀门内应基本上没有空气。 4.1.3 要求的保护涂层,如油漆,可能掩盖表面缺陷。在检查和压力试验前,任何 表面不应有这类涂层(磷化处理或类似的化学处理用于保护阀门表面是允许的,甚至可 在试验前进行,只要这类处理不掩盖气孔等缺陷)。 4.1.4 当进行闸阀、旋塞阀和球阀密封试验时,阀门制造厂应采用这样的试验方法, 在阀座和阀盖间的阀体腔内注满介质并加压。这样能确保不至由于在试验中逐渐向上述 部位充注介质和加压而使密封面的泄漏未被察觉。 4.1.5 当进行阀门密封试验时,阀门制造厂的试验方法应能确保不使用过大的力来 关闭阀门.所 施加的关闭力可在MSSSP--91的适当数值中确定,但在任何情况下这个力不能超过阀门 制造广 公布的值。 4.2 壳体试验

5082-A901-MO000资料

Features• Low Power Consumption • Industry Standard Size• Industry Standard Pinout • Choice of Character Size7.6 mm (0.30 in), 10 mm (0.40 in), 10.9 mm (0.43 in), 14.2 mm (0.56 in), 20 mm (0.80 in)• Choice of ColorsAlGaAs Red, High Efficiency Red (HER), Yellow, Green• Excellent Appearance Evenly Lighted Segments±50° Viewing Angle• Design FlexibilityCommon Anode or Common CathodeSingle and Dual DigitLeft and Right Hand Decimal Points±1. Overflow Character• Categorized for Luminous IntensityYellow and Green Categorized for ColorUse of Like Categories Yields a Uniform Display• Excellent for Long Digit String Multiplexing DescriptionThese low current seven segment displays are designed for applica-tions requiring low power consumption. They are tested and selected for their excellent low current characteristics to ensure that the segments are matched at low currents. Drive currents as low as 1 mA per segment are available.Pin for pin equivalent displays are also available in a standard current or high light ambient design. The standard current displays are available in all colors and are ideal for most applica-tions. The high light ambient displays are ideal for sunlight ambients or long string lengths. For additional information see the 7.6 mm Micro Bright Seven Segment Displays, 10 mm Seven Segment Displays, 7.6 mm/10.9 mm Seven Segment Displays, 14.2 mm Seven Segment Displays, 20 mm Seven Segment Displays, or High Light Ambient Seven Segment Displays data sheets.Low Current Seven SegmentDisplays Technical Data HDSP-335x SeriesHDSP-555x SeriesHDSP-751x SeriesHDSP-A10x Series HDSP-A80x Series HDSP-A90x Series HDSP-E10x Series HDSP-F10x Series HDSP-G10x Series HDSP-H10x Series HDSP-K12x, K70x Series HDSP-N10x SeriesHDSP-N40x SeriesDevicesAlGaAs HER Yellow Green Package HDSP-HDSP-HDSP-HDSP-Description Drawing A1017511A801A9017.6 mm Common Anode Right Hand Decimal A A1037513A803A9037.6 mm Common Cathode Right Hand Decimal B A1077517A807A9077.6 mm Common Anode ±1. Overflow C A1087518A808A9087.6 mm Common Cathode ±1. Overflow D F10110 mm Common Anode Right Hand Decimal E F10310 mm Common Cathode Right Hand Decimal F F10710 mm Common Anode ±1. Overflow G F10810 mm Common Cathode ±1. Overflow H G10110 mm Two Digit Common Anode Right Hand Decimal X G10310 mm Two Digit Common Cathode Right Hand Decimal Y E100335010.9 mm Common Anode Left Hand Decimal I E101335110.9 mm Common Anode Right Hand Decimal J E103335310.9 mm Common Cathode Right Hand Decimal K E106335610.9 mm Universal ±1. Overflow[1]L H101555114.2 mm Common Anode Right Hand Decimal M H103555314.2 mm Common Cathode Right Hand Decimal N H107555714.2 mm Common Anode ±1. Overflow O H108555814.2 mm Common Cathode ±1. Overflow P K121K70114.2 mm Two Digit Common Anode Right Hand Decimal R K123K70314.2 mm Two Digit Common Cathode Right Hand Decimal S N10020 mm Common Anode Left Hand Decimal Q N101N40120 mm Common Anode Right Hand Decimal T N103N40320 mm Common Cathode Right Hand Decimal U N10520 mm Common Cathode Left Hand Decimal V N106N40620 mm Universal ±1. Overflow[1]W Note:1. Universal pinout brings the anode and cathode of each segment’s LED out to separate pins. See internal diagrams L or W.Part Numbering System5082-x xx x-x x x xxHDSP-x xx x-x x x xxMechanical Options[1]00: No mechanical optionColor Bin Options[1,2]0: No color bin limitationMaximum Intensity Bin[1,2]0: No maximum intensity bin limitationMinimum Intensity Bin[1,2]0: No minimum intensity bin limitationDevice Configuration/Color[1]G: GreenDevice Specific Configuration[1]Refer to respective datasheetPackage[1]Refer to Respective datasheetNotes:1. For codes not listed in the figure above, please refer to the respective datasheet or contact your nearest Agilent representative fordetails.2. Bin options refer to shippable bins for a part-number. Color and Intensity Bins are typically restricted to 1 bin per tube (excep-tions may apply). Please refer to respective datasheet for specific bin limit information.Package DimensionsPackage Dimensions (cont.)Package Dimensions (cont.)*The Side View of package indicates Country of Origin.Package Dimensions (cont.)Package Dimensions (cont.)Package Dimensions (cont.)Internal Circuit DiagramInternal Circuit Diagram (cont.)Absolute Maximum RatingsAlGaAs Red - HDSP-HERA10X/E10X/H10X HDSP-751X/Yellow GreenK12X/N10X/N40X335X/555X/HDSP-A80X HDSP-A90X Description F10X, G10X Series K70X Series Series Series Units Average Power per Segment or DP375264mW Peak Forward Current per 45mA Segment or DPDC Forward Current per15[1]15[2]mA Segment or DPOperating Temperature Range-20 to +100-40 to +100°C Storage Temperature Range -55 to +100°C Reverse Voltage per Segment 3.0V or DPWave Soldering Temperature for 3Seconds (1.60 mm [0.063 in.] below 250°C seating body)Notes:1. Derate above 91°C at 0.53 mA/°C.2. Derate HER/Yellow above 80°C at 0.38 mA/°C and Green above 71°C at 0.31 mA/°C.Electrical/Optical Characteristics at T A = 25°CAlGaAs RedDeviceSeriesHDSP-Parameter Symbol Min.Typ.Max.Units Test Conditions315600I F = 1 mA A10x3600I F = 5 mA330650I F = 1 mAF10x, G10x3900I F = 5 mA390650I F = 1 mA E10x Luminous Intensity/Segment[1,2]I Vµcd(Digit Average)3900I F = 5 mA400700I F = 1 mAH10x, K12x4200I F = 5 mA270590I F = 1 mAN10x, N40x3500I F = 5 mA1.6I F = 1 mAForward Voltage/Segment or DP V F 1.7V I F = 5 mA1.82.2I F = 20 mA PkAll Devices Peak WavelengthλPEAK645nmDominant Wavelength[3]λd637nmReverse Voltage/Segment or DP[4]V R 3.015V I R = 100 µATemperature Coefficient of∆V F/°C-2 mV mV/°CV F/Segment or DPA10x255F10x, G10x320E10x340Thermal Resistance LED RθJ-PIN°C/W/SegH10x, K12x Junction-to-Pin400N10x, N40x430High Efficiency RedDeviceSeriesHDSP-Parameter Symbol Min.Typ.Max.Units Test Conditions160270I F = 2 mA 751x1050I F = 5 mA200300I F = 2 mA Luminous Intensity/Segment[1,2]I V mcd(Digit Average)1200I F = 5 mA335x, 555x,K70x270370I F = 2 mA1480I F = 5 mA1.6I F = 2 mAForward Voltage/Segment or DP V F 1.7V I F = 5 mA2.1 2.5I F = 20 mA Pk All Devices Peak WavelengthλPEAK635nmDominant Wavelength[3]λd626nmReverse Voltage/Segment or DP[4]V R 3.030V I R = 100 µATemperature Coefficient of∆V F/°C-2mV/°CV F/Segment or DP751x200335x Thermal Resistance LED RθJ-PIN280°C/WJunction-to-Pin555x, K70x345YellowDeviceSeriesHDSP-Parameter Symbol Min.Typ.Max.Units Test Conditions Luminous Intensity/Segment[1,2]250420I F = 4 mA(Digit Average)I V mcd1300I F = 10 mA1.7I F = 4 mAForward Voltage/Segment or DP V F 1.8V I F = 5 mA A80x2.1 2.5I F = 20 mA PkPeak WavelengthλPEAK583nmDominant Wavelength[3,5]λd581.5585592.5nmReverse Voltage/Segment or DP[4]V R 3.030V I R = 100 µATemperature Coefficient of∆V F/°C-2mV/°CV F/Segment or DPThermal Resistance LED RθJ-PIN200°C/WJunction-to-PinGreenDeviceSeriesHDSP-Parameter Symbol Min.Typ.Max.Units Test Conditions Luminous Intensity/Segment[1,2]250475I F = 4 mA(Digit Average)I V mcd1500I F = 10 mA1.9I F = 4 mAForward Voltage/Segment or DP V F 2.0V I F = 10 mA A90x2.1 2.5I F = 20 mA PkPeak WavelengthλPEAK566nmDominant Wavelength[3,5]λd571577nmReverse Voltage/Segment or DP[4]V R 3.030V I R = 100 µATemperature Coefficient of∆V F/°C-2mV/°CV F/Segment or DPThermal Resistance LED RθJ-PIN200°C/WJunction-to-PinNotes:1. Device case temperature is 25°C prior to the intensity measurement.2. The digits are categorized for luminous intensity. The intensity category is designated by a letter on the side of the package.3. The dominant wavelength, λd, is derived from the CIE chromaticity diagram and is the single wavelength which defines the color of thedevice.4. Typical specification for reference only. Do not exceed absolute maximum ratings.5. The yellow (HDSP-A800) and Green (HDSP-A900) displays are categorized for dominant wavelength. The category is designated by anumber adjacent to the luminous intensity category letter.AlGaAs RedIntensity Bin Limits (mcd)AlGaAs RedHDSP-A10xIV Bin Category Min.Max.E0.3150.520F0.4280.759G0.621 1.16H0.945 1.71I 1.40 2.56J 2.10 3.84K 3.14 5.75L 4.708.55HDSP-E10x/F10x/G10xIV Bin Category Min.Max.D0.3910.650E0.5320.923F0.755 1.39G 1.13 2.08H 1.70 3.14HDSP-H10x/K12xIV Bin Category Min.Max.C0.4150.690D0.5650.990E0.810 1.50F 1.20 2.20G 1.80 3.30H 2.73 5.00I 4.097.50HDSP-N10xIV Bin Category Min.Max.A0.2700.400B0.3250.500C0.4150.690D0.5650.990E0.810 1.50F 1.20 2.20G 1.80 3.30H 2.73 5.00I 4.097.50Intensity Bin Limits (mcd), continued HERHDSP-751xIV Bin Category Min.Max.B0.1600.240C0.2000.300D0.2500.385E0.3150.520F0.4280.759G0.621 1.16HDSP-751xIV Bin Category Min.Max.B0.2400.366C0.3000.477D0.3910.650E0.5320.923F0.755 1.39G 1.13 2.08H 1.70 3.14HDSP-555x/K70xIV Bin Category Min.Max.A0.2700.400B0.3250.500C0.4150.690D0.5650.990E0.810 1.50F 1.20 2.20G 1.80 3.30H 2.73 5.00I 4.097.50Intensity Bin Limits (mcd), continued YellowHDSP-A80xIV Bin Category Min.Max.D0.2500.385E0.3150.520F0.4250.760G0.625 1.14H0.940 1.70I 1.40 2.56J 2.10 3.84K 3.14 5.76L 4.718.64M7.0713.00N10.6019.40O15.9029.20P23.9043.80Q35.8065.60GreenHDSP-A90xIV Bin Category Min.Max.E0.3150.520F0.4250.760G0.625 1.14H0.940 1.70I 1.40 2.56J 2.10 3.84K 3.14 5.76L 4.718.64M7.0713.00N10.6019.40O15.9029.20P23.9043.80Q35.8065.60Electrical/OpticalFor more information on electrical/optical characteristics, please see Application Note 1005.Contrast Enhancement For information on contrast enhancement, please see Application Note 1015.Soldering/Cleaning Cleaning agents from the ketone family (acetone, methyl ethyl ketone, etc.) and from the chorinated hydrocarbon family (methylene chloride, trichloro-ethylene, carbon tetrachloride, etc.) are not recommended for cleaning LED parts. All of these various solvents attack or dissolve the encapsulating epoxies used to form the package of plastic LED parts.For information on soldering LEDs, please refer to Application Note 1027.Note:All categories are established for classification of products. Productsmay not be available in all categories. Please contact your localAgilent representatives for further clarification/information.Color Categories/semiconductorsFor product information and a complete list ofdistributors, please go to our web site.For technical assistance call:Americas/Canada: +1 (800) 235-0312 or(916) 788 6763Europe: +49 (0) 6441 92460China: 10800 650 0017Hong Kong: (+65) 6271 2451India, Australia, New Zealand: (+65) 6271 2394Japan: (+81 3) 3335-8152(Domestic/International), or0120-61-1280(Domestic Only)Korea: (+65) 6271 2194Malaysia, Singapore: (+65) 6271 2054Taiwan: (+65) 6271 2654Data subject to change.Copyright © 2005 Agilent Technologies, Inc.Obsoletes 5988-8412ENJanuary 19, 20055989-0080EN。

5962-8776601SA中文资料

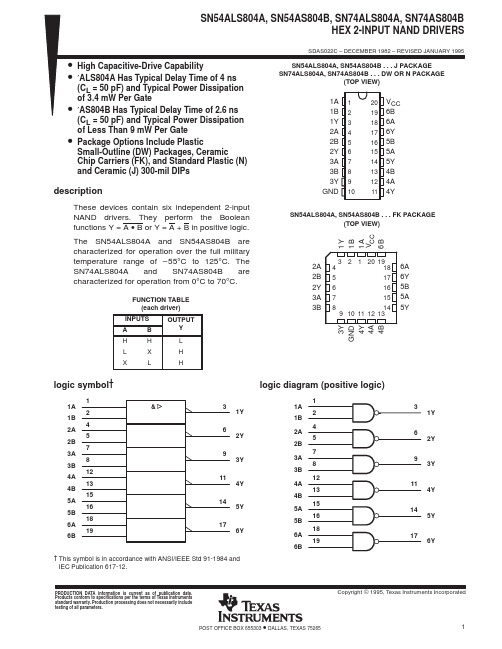

PACKAGING INFORMATIONOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)5962-87766012A ACTIVE LCCC FK201TBD Call TI Level-NC-NC-NC 5962-8776601RA ACTIVE CDIP J201TBD Call TI Level-NC-NC-NC 5962-8776601SA ACTIVE CFP W201TBD Call TI Level-NC-NC-NC 5962-88693012A ACTIVE LCCC FK201TBD Call TI Level-NC-NC-NC 5962-8869301RA ACTIVE CDIP J201TBD Call TI Level-NC-NC-NC SN54ALS804AJ ACTIVE CDIP J201TBD Call TI Level-NC-NC-NC SN54AS804BJ ACTIVE CDIP J201TBD Call TI Level-NC-NC-NC SN74ALS804ADW ACTIVE SOIC DW2025Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74ALS804ADWE4ACTIVE SOIC DW2025Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74ALS804ADWR ACTIVE SOIC DW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74ALS804ADWRE4ACTIVE SOIC DW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74ALS804AN ACTIVE PDIP N2020Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NCSN74ALS804ANE4ACTIVE PDIP N2020Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NCSN74AS804BDW ACTIVE SOIC DW2025Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AS804BDWE4ACTIVE SOIC DW2025Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AS804BDWR ACTIVE SOIC DW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AS804BDWRE4ACTIVE SOIC DW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AS804BN ACTIVE PDIP N2020Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NCSN74AS804BNE4ACTIVE PDIP N2020Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NC SNJ54ALS804AFK ACTIVE LCCC FK201TBD Call TI Level-NC-NC-NC SNJ54ALS804AJ ACTIVE CDIP J201TBD Call TI Level-NC-NC-NC SNJ54AS804BFK ACTIVE LCCC FK201TBD Call TI Level-NC-NC-NC SNJ54AS804BJ ACTIVE CDIP J201TBD Call TI Level-NC-NC-NC SNJ54AS804BW ACTIVE CFP W201TBD Call TI Level-NC-NC-NC (1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan-The planned eco-friendly classification:Pb-Free(RoHS)or Green(RoHS&no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free(RoHS):TI's terms"Lead-Free"or"Pb-Free"mean semiconductor products that are compatible with the current RoHS requirementsfor all6substances,including the requirement that lead not exceed0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Green(RoHS&no Sb/Br):TI defines"Green"to mean Pb-Free(RoHS compatible),and free of Bromine(Br)and Antimony(Sb)based flame retardants(Br or Sb do not exceed0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. T o minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements. Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetwork Microcontrollers Security /securityTelephony /telephonyVideo & Imaging /videoWireless /wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright 2005, Texas Instruments Incorporated。

5962-9452602MGA中文资料

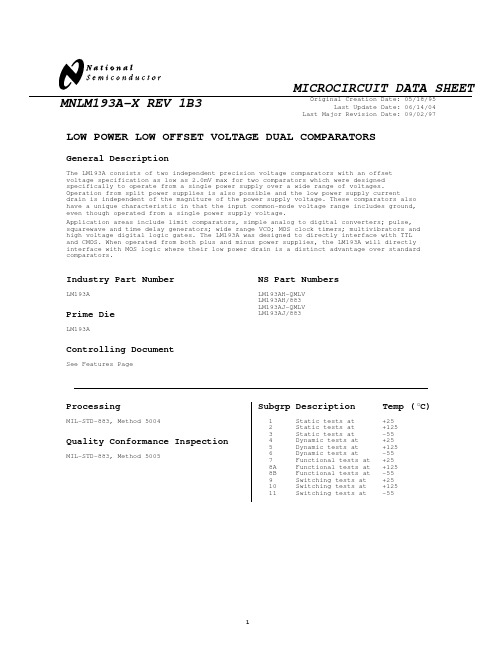

Original Creation Date: 05/18/95Last Update Date: 06/14/04Last Major Revision Date: 09/02/97MNLM193A-X REV 1B3MICROCIRCUIT DATA SHEETLOW POWER LOW OFFSET VOLTAGE DUAL COMPARATORSGeneral DescriptionThe LM193A consists of two independent precision voltage comparators with an offset voltage specification as low as 2.0mV max for two comparators which were designed specifically to operate from a single power supply over a wide range of voltages.Operation from split power supplies is also possible and the low power supply currentdrain is independent of the magniture of the power supply voltage. These comparators also have a unique characteristic in that the input common-mode voltage range includes ground,even though operated from a single power supply voltage.Application areas include limit comparators, simple analog to digital converters; pulse,squarewave and time delay generators; wide range VCO; MOS clock timers; multivibrators and high voltage digital logic gates. The LM193A was designed to directly interface with TTL and CMOS. When operated from both plus and minus power supplies, the LM193A will directly interface with MOS logic where their low power drain is a distinct advantage over standard comparators.NS Part NumbersLM193AH-QMLV LM193AH/883LM193AJ-QMLV LM193AJ/883Industry Part NumberLM193APrime DieLM193AControlling DocumentSee Features PageProcessingMIL-STD-883, Method 5004Quality Conformance InspectionMIL-STD-883, Method 5005Subgrp Description Temp ( C)o 1Static tests at +252Static tests at +1253Static tests at -554Dynamic tests at +255Dynamic tests at +1256Dynamic tests at -557Functional tests at +258A Functional tests at +1258B Functional tests at -559Switching tests at +2510Switching tests at +12511Switching tests at-55MICROCIRCUIT DATA SHEET MNLM193A-X REV 1B3Features- Wide supply- Voltage range 2.0Vdc to 36Vdc- Single or dual supplies +1.0Vdc to +18Vdc- Very low supply current drain (0.4mA)independent of supply voltage- Low input biasing current 25nA Typ- Low input offset current +3nA Typ- Input common-mode voltage rangeincludes ground- Differential input voltage rangeequal to the power supply voltage- Low output saturation voltage 250mV at 4mA Typ- Output voltage compatible with TTL,DTL, ECL, MOS and CMOS logic systemsCONTROLLING DOCUMENTS:LM193AH/883 5962-9452602MGALM193AH-QMLV 5962-9452602VGALM193AJ-QMLV 5962-9452602VPALM193AJ/883 5962-9452602MPAMICROCIRCUIT DATA SHEET MNLM193A-X REV 1B3(Absolute Maximum Ratings)(Note 1)Supply Voltage, V+36Vdc or +18VdcDifferential Input Voltage(Note 6)36VdcInput Voltage-0.3Vdc to +36VdcInput Current (Vin < -0.3 Vdc)(Note 5)50mAMaximum Junction Temperature150 CPower Dissipation(Note 2, 3)METAL CAN660mWCERDIP780mWOutput Short-Circuit to Gnd(Note 4)ContinuousOperating Temperature Range-55 C to +125 CThermal ResistanceThetaJAMETAL CAN (Still Air)174 C/W(500LF/Min Air flow)99 C/WCERDIP (Still Air)146 C/W(500LF/Min Air flow)85 C/WThetaJCMETAL CAN44 C/WCERDIP33 C/WLead Temperature(Soldering, 10 seconds)+260 CESD Tolerance(Note 7)500VNote 1:Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.Operating Ratings indicate conditions for which the device is functional, but do notguarantee specific performance limits. For guaranteed specifications and testconditions, see the Electrical Characteristics. The guaranteed specifications applyonly for the test conditions listed. Some performance characteristics may degradewhen the device is not operated under the listed test conditions.Note 2:The maximum power dissipation must be derated at elevated temperatures and isdictated by Tjmax (maximum junction temperature ), ThetaJA (package junction toambient thermal resistance), and TA (ambient temperature). The maximum allowablepower dissipation at any temperature is Pdmax = (Tjmax - TA)/ThetaJA or the numbergiven in the Absolute Maximum Ratings, whichever is lower.Note 3:The LM193A must be derated based on a 150 C maximum junction temperature. The low bias dissipation and the ON-OFF characteristic of the outputs keeps the chipdissipation very small (PD<100mV), provided the output transistors are allowed tosaturate.Note 4:Short circuits from the output to V+ can cause excessive heating and eventualdestruction. When considering short circuits to ground, the maximum output current isapproximately 20mA independent of the magnitude of V+.MNLM193A-X REV 1B3MICROCIRCUIT DATA SHEET(Continued)Note 5:This input current will only exist when the voltage at any of the input leads is driven negative. It is due to the collector-base junction of the input PNPtransistors becoming forward biased and thereby acting as input diode clamps. Inaddition to this diode action, there is also lateral NPN parasitic transistor actionon the IC chip. This transistor action can cause the output voltages of thecomparators to go to the V+ voltage level (or to ground for a large overdrive) forthe time duration that an input is driven negative. This is not destructive andnormal output states will re-establish when the input voltage, which was negative,again returns to a value greater than -0.3Vdc.Note 6:Positive excursions of input voltage may exceed the power supply level. As long as the other voltage remains within the common-mode range, the comparator will provide aproper output state. The low input voltage state must not be less than -0.3Vdc (or0.3Vdc below the magnitude of the negative power supply, if used).Note 7:Human body model, 1.5K Ohms in series with 100pF.MNLM193A-X REV 1B3MICROCIRCUIT DATA SHEETElectrical CharacteristicsDC PARAMETERS(The following conditions apply to all the following parameters, unless otherwise specified.)DC:V+ = 5V, Vcm = 0SYMBOL PARAMETER CONDITIONS NOTES PIN-NAME MIN MAX UNITSUB-GROUPSIcc Supply Current Rl = Infinity 1.0mA1, 2,3V+ = 36V, Rl = Infinity 2.5mA1, 2,3Icex Output LeakageCurrent V+ = 30V, Vin+ = 1V, Vo = 30, Vin- = 0-0.650.65uA1-1.0 1.0uA2, 3Isink Output SinkCurrent Vo = 1.5V, Vin- = 1V, Vin+ = 0 6.0mA14.0mA2, 3Vsat Output SaturationVoltage Isink = 4mA, Vin- = 1V, Vin+ = 00.4V10.7V2, 3Vio Input OffsetVoltage-2.0 2.0mV1-4.0 4.0mV2, 3 V+ = 30V, Vcm = 0-2.0 2.0mV1-4.0 4.0mV2, 3 V+ = 30V, Vcm = 28.5V-2.0 2.0mV1V+ = 30V, Vcm = 28.0V-4.0 4.0mV2, 3Iib+Input BiasCurrent Vout = 1.5V-100-1nA1-300-1nA2, 3Iib-Input BiasCurrent Vout = 1.5V-100-1nA1-300-1nA2, 3Iio Input offsetCurrent Rs = 50 Ohms, Vout = 1.5V-2525nA1-100100nA2, 3Vcm Common ModeVoltage V+ = 30V128.5V1128V2, 3PSRR Power SupplyRejection RatioV+ = 5V to 30V, Rs = 50 Ohms60dB1CMRR Common ModeRejection Ratio V+ = 30V, Vcm = 0V to 28.5V,Rs = 50 Ohms60dB1Vdiff DifferentialInput Voltage V+ = 30V, +Vin = 36V, -Vin = 0V4500nA1, 2,3V+ = 30V, +Vin = 0V, -Vin = +36V4500nA1, 2,3Avs Voltage Gain V+ = 15V, 1V <= Vout <= 11V,RPULLUP = 15K 250V/mV4 225V/mV5, 6MNLM193A-X REV 1B3MICROCIRCUIT DATA SHEETElectrical CharacteristicsAC PARAMETERS(The following conditions apply to all the following parameters, unless otherwise specified.)AC:Vcc = 5V, Vcm = 0SYMBOL PARAMETER CONDITIONS NOTES PIN-NAME MIN MAX UNITSUB-GROUPStRLH Response Time V+ = 5V, Vod = 5mV3 5.0uS9V+ = 5V, Vod = 50mV30.8uS9 tRHL Response Time V+ = 5V, Vod = 5mV3 2.5uS9V+ = 5V, Vod = 50mV30.8uS9DC PARAMETERS: DRIFT VALUES(The following conditions apply to all the following parameters, unless otherwise specified.)DC:V+ = 5V, Vcm = 0. "Delta calculations performed on Jan S and QMLV devices at Group B, Subgroup 5 ONLY."Vio Input OffsetVoltageV+ = 30V, Vcm = 0-11mV1Iib+Input BiasCurrent-1515nA1Iib-Input BiasCurrent-1515nA1Note 1:Parameter guaranteed by the Vio testsNote 2:Datalog reading in K = V/mV.Note 3:Bench TestedNote 4:The value for Vdiff is not data logged during Read and Record.MICROCIRCUIT DATA SHEET MNLM193A-X REV 1B3Graphics and DiagramsGRAPHICS#DESCRIPTION06048HRA2CERDIP (J), 8 LEAD (B/I CKT)09319HRA2METAL CAN (H), TO-99, 8 LD, .200 DIA P.C.(B/I CKT)H08CRF METAL CAN (H), TO-99, 8LD .200 DIA P.C. (P/P DWG)J08ARL CERDIP (J), 8 LEAD (P/P DWG)P000171A METAL CAN (H), TO-99, 8LD, .200 DIA P.C. (PINOUT)P000172B CERDIP (J), 8 LEAD (PINOUT)See attached graphics following this page.N MIL/AEROSPACE OPERATIONS 2900 SEMICONDUCTOR DRIVE SANTA CLARA, CA 95050123456 78 IN- AIN+ AOUTPUT AGND IN+ BIN- B OUTPUT BV+LM193AH, LM193HCONNECTION DIAGRAM TOP VIEWP000171A8 - PIN METAL CANN MIL/AEROSPACE OPERATIONS2900 SEMICONDUCTOR DRIVESANTA CLARA, CA 95050LM193J, LM193AJCONNECTION DIAGRAMTOP VIEWP000172B8 - LEAD DIP1 8234 5 7 6 OUTPUT AIN- AIN+ AV-IN + BIN- B OUTPUT B V+MICROCIRCUIT DATA SHEET MNLM193A-X REV 1B3Revision HistoryRev ECN #Rel Date Originator Changes1A2M000281701/16/03Rose Malone Update MDS: MNLM193A-X, Rev. 1A1 to MNLM193A-X, Rev.1A2. Main Table Adding reference to LM193AJ/883 andSMD number, B/I CKTS and Pin Out for J pkg.1A3M000408706/14/04Rose Malone Updated MDS: MNLM193A-X, Rev. 1A2 to MNLM193A-X, Rev.1A3. Updated Burn-In Ckt from 05363HRA2 to 09319HRA2in Graphics Section.1B3M000439106/14/04Rose Malone Update MDS: MNLM193A-X, Rev. 1A3 to 1B3. Added Note 4to Vdiff parameter and to note section.8。

5962-9452801QXA中文资料