LTC2305IMS#PBF;LTC2301CDE#PBF;LTC2301CMS#PBF;LTC2301CDE#TRPBF;中文规格书,Datasheet资料

HID 灯集成电路驱动器UCC2305 及其应用电路原理图

HID灯集成电路驱动器UCC2305及其应用电路原理图一、引言高强度气体放电(HID:High intensity Discharge)灯实际上包括了一大类采用小型高内压弧光管发光的照明产品,基本上有三种类型:水银蒸气(MV)灯,金属卤化物(MH)灯和高、低压钠(HPS或LPS)灯。

HID灯全都按与日光灯相似的放电原理工作:当灯管里充填的气体,如被镇流器提供的电流激活时便会发光。

HID灯和日光灯的关键区别是灯管里的压力更高。

金属卤化物(MH)灯是为改善水银蒸气灯的亮度、显色性差和效率相对低的特征而设计。

MH灯功能非常象水银蒸气灯,但因在灯管内添加了如铊、铟和钠金属的碘化物(卤化物),故比之只有水银蒸气能发放更多和更优质的光。

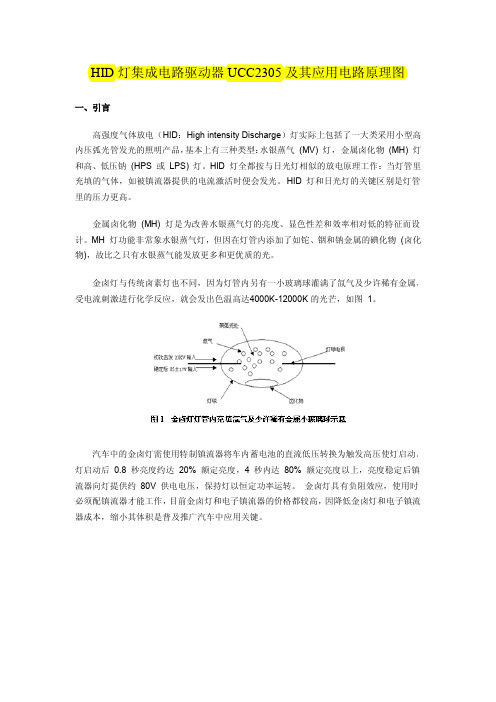

金卤灯与传统卤素灯也不同,因为灯管内另有一小玻璃球灌满了氙气及少许稀有金属,受电流刺激进行化学反应,就会发出色温高达4000K-12000K的光芒,如图1。

汽车中的金卤灯需使用特制镇流器将车内蓄电池的直流低压转换为触发高压使灯启动。

灯启动后0.8秒亮度约达20%额定亮度,4秒内达80%额定亮度以上,亮度稳定后镇流器向灯提供约80V供电电压,保持灯以恒定功率运转。

金卤灯具有负阻效应,使用时必须配镇流器才能工作,目前金卤灯和电子镇流器的价格都较高,因降低金卤灯和电子镇流器成本,缩小其体积是普及推广汽车中应用关键。

车用金卤灯镇流器系统主要由包括从9-16V汽车硫酸铅电池输入的直流-直流变换器,高压点火器,200-400Hz全桥逆变器以及保证稳态功率输出的控制电路4部分组成(图2)。

DC/DC变换器须满足在9-16V输入电压范围内能输出直流电60-500V的压,并具有输入过压、输出短路/开路和过流保护功能。

点火器的功能是产生瞬间高压20-30KV的击穿灯管放电。

全桥逆变器提供200-400Hz全桥功率开关管的驱动信号,完成DC-AC逆变,实现灯管两端电压极性反转,防止灯管单端发黑,延长灯管寿命。

微斯米微波式芯片公司2014年产品说明书

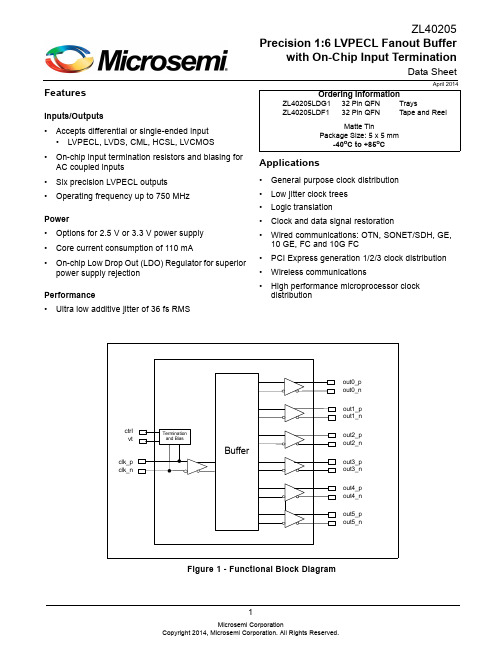

1FeaturesInputs/Outputs •Accepts differential or single-ended input •LVPECL, LVDS, CML, HCSL, LVCMOS •On-chip input termination resistors and biasing for AC coupled inputs•Six precision LVPECL outputs •Operating frequency up to 750 MHzPower •Options for 2.5 V or 3.3 V power supply •Core current consumption of 110 mA•On-chip Low Drop Out (LDO) Regulator for superior power supply rejectionPerformance •Ultra low additive jitter of 36 fs RMSApplications•General purpose clock distribution •Low jitter clock trees •Logic translation•Clock and data signal restoration•Wired communications: OTN, SONET/SDH, GE,10 GE, FC and 10G FC•PCI Express generation 1/2/3 clock distribution •Wireless communications•High performance microprocessor clock distributionApril 2014Figure 1 - Functional Block DiagramZL40205Precision 1:6 LVPECL Fanout Bufferwith On-Chip Input TerminationData SheetOrdering InformationZL40205LDG1 32 Pin QFN TraysZL40205LDF132 Pin QFNTape and ReelMatte TinPackage Size: 5 x 5 mm-40o C to +85o CTable of ContentsFeatures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Inputs/Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Performance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Change Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41.0 Package Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52.0 Pin Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63.0 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73.1 Clock Inputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73.2 Clock Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123.3 Device Additive Jitter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .153.4 Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.4.1 Sensitivity to power supply noise. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.4.2 Power supply filtering. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.4.3 PCB layout considerations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .164.0 AC and DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .175.0 Performance Characterization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .206.0 Typical Behavior . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .217.0 Package Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .238.0 Mechanical Drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24List of FiguresFigure 1 - Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Figure 2 - Pin Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 Figure 3 - Simplified Diagram of Input Stage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Figure 4 - Clock Input - LVPECL - DC Coupled. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 5 - Clock Input - LVPECL - AC Coupled. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 6 - Clock Input - LVDS - DC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 7 - Clock Input - LVDS - AC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 8 - Clock Input - CML- AC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Figure 9 - Clock Input - HCSL- AC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Figure 10 - Clock Input - AC-coupled Single-Ended . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Figure 11 - Clock Input - DC-coupled 3.3V CMOS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Figure 12 - Simplified Output Driver. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 13 - LVPECL Basic Output Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 14 - LVPECL Parallel Output Termination. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 15 - LVPECL Parallel Thevenin-Equivalent Output Termination. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 16 - LVPECL AC Output Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Figure 17 - LVPECL AC Output Termination for CML Inputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Figure 18 - Additive Jitter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Figure 19 - Decoupling Connections for Power Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Figure 20 - Differential and Single-Ended Output Voltages Parameter Definitions . . . . . . . . . . . . . . . . . . . . . . . . 18 Figure 21 - Input To Output Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19Change SummaryPage Item Change1Applications Added PCI Express clock distribution.6Pin Description Added exposed pad to Pin Description.8Figure 4 and Figure 5Removed 22 ohm series resistors from Figure 4 and 5. These resistor are not required; however there is no impact to performance if the resistors are included.16Power supply filtering 18Figure 20Clarification of V ID and V OD .Below are the changes from the February 2013 issue to the April 2014 issue:Page Item Change8Figure 4Changed text to indicate the circuit is not recommended for VDD_driver=2.5V.Below are the changes from the November 2012 issue to the February 2013 issue:Corrected typo of 0.3 Ohm to 0.15 Ohm.1.0 Package DescriptionThe device is packaged in a 32 pin QFNFigure 2 - Pin Connections2.0 Pin DescriptionPin # Name Description3, 6clk_p, clk_n,Differential Input (Analog Input). Differential (or single ended) input signals.For all input configurations see “Clock Inputs” on page 728, 27, 26, 25, 24, 23, 18, 17, 16, 15, 14, 13out0_p, out0_nout1_p, out1_nout2_p, out2_nout3_p, out3_nout4_p, out4_nout5_p, out5_nDifferential Output (Analog Output). Differential outputs.9, 19,22, 32vdd Positive Supply Voltage. 2.5 V DC or 3.3 V DC nominal.1, 8vdd_core Positive Supply Voltage. 2.5 V DC or 3.3 V DC nominal.2, 7,20, 21gnd Ground. 0 V.4vt On-Chip Input Termination Node (Analog). Center tap between internal 50 Ohmtermination resistors.The use of this pin is detailed in section 3.1, “Clock Inputs“, for various input signal types.5ctrl Digital Control for On-Chip Input Termination (Input). Selects differential input mode;0: DC coupled LVPECL or LVDS modes1: AC coupled differential modesThis pin are internally pulled down to GND. The use of this pin is detailed in section 3.1,“Clock Inputs“, for various input signal types.10, 11,12, 29,30, 31NC No Connection. Leave unconnected.Exposed Pad Device GND.3.0 Functional DescriptionThe ZL40205 is an LVPECL clock fan out buffer with six output clock drivers capable of operating at frequencies up to 750MHz.The ZL40205 provides an internal input termination network for DC and AC coupled inputs; optional input biasing for AC coupled inputs is also provided. The ZL40205 can accept DC or AC coupled LVPECL and LVDS input signals, AC coupled CML or HCSL input signals, and single ended signals. A pin compatible device with external termination is also available.The ZL40205 is designed to fan out low-jitter reference clocks for wired or optical communications applications while adding minimal jitter to the clock signal. An internal linear power supply regulator and bulk capacitors minimize additive jitter due to power supply noise. The device operates from 2.5V+/-5% or 3.3V+/-5% supply. Its operation is guaranteed over the industrial temperature range -40°C to +85°C.The device block diagram is shown in Figure 1; its operation is described in the following sections.3.1 Clock InputsThe device has a differential input equipped with two on-chip 50 Ohm termination resistors arranged in series with a center tap. The input can accept many differential and single-ended signals with AC or DC coupling as appropriate. A control pin is available to enable internal biasing for AC coupled inputs. A block diagram of the input stage is in Figure 3.Receiverclk_n 50clk_pVt 50BiasctrlFigure 3 - Simplified Diagram of Input StageThis following figures give the components values and configuration for the various circuits compatible with the input stage and the use of the Vt and ctrl pins in each case.In the following diagrams where the ctrl pin is logically one and the Vt pin is not connected, the Vt pin can be instead connected to VDD with a capacitor. A capacitor can also help in Figure 4 between Vt and VDD. This capacitor will minimize the noise at the point between the two internal termination resistors and improve the overall performance of the device.Figure 4 - Clock Input - LVPECL - DC CoupledFigure 5 - Clock Input - LVPECL - AC CoupledFigure 6 - Clock Input - LVDS - DC CoupledFigure 7 - Clock Input - LVDS - AC CoupledFigure 8 - Clock Input - CML- AC CoupledFigure 9 - Clock Input - HCSL- AC CoupledFigure 10 - Clock Input - AC-coupled Single-EndedFigure 11 - Clock Input - DC-coupled 3.3V CMOS3.2 Clock OutputsLVPECL has a very low output impedance and a differential signal swing between 1V and 1.6 V. A simplified diagram for the output stage is shown in Figure 12.The LVPECL to LVDS output termination is not shown since there is a different device with the same inputs and LVDS outputs.out_pout_nFigure 12 - Simplified Output DriverThe methods to terminate the ZL40205 LVPECL drivers are shown in the following figures.Figure 15 - LVPECL Parallel Thevenin-Equivalent Output TerminationFigure 16 - LVPECL AC Output TerminationFigure 17 - LVPECL AC Output Termination for CML Inputs3.3 Device Additive JitterThe ZL40205 clock fanout buffer is not intended to filter clock jitter. The jitter performance of this type of device is characterized by its additive jitter. Additive jitter is the jitter the device would add to a hypothetical jitter-free clock as it passes through the device. The additive jitter of the ZL40205 is random and as such it is not correlated to the jitter of the input clock signal.The square of the resultant random RMS jitter at the output of the ZL40205 is equal to the sum of the squares of the various random RMS jitter sources including: input clock jitter; additive jitter of the buffer; and additive random jitter due to power supply noise. There may be additional deterministic jitter sources, but they are not shown in Figure 18.Figure 18 - Additive Jitter3.4 Power SupplyThis device operates employing either a 2.5V supply or 3.3V supply.3.4.1 Sensitivity to power supply noisePower supply noise from sources such as switching power supplies and high-power digital components such as FPGAs can induce additive jitter on clock buffer outputs. The ZL40205 is equipped with a low drop out (LDO) regulator and on-chip bulk capacitors to minimize additive jitter due to power supply noise. The on-chip regulation, recommended power supply filtering, and good PCB layout all work together to minimize the additive jitter from power supply noise.3.4.2 Power supply filteringJitter levels may increase when noise is present on the power pins. For optimal jitter performance, the device should be isolated from the power planes connected to its power supply pins as shown in Figure 19. •10 µF capacitors should be size 0603 or size 0805 X5R or X7R ceramic, 6.3 V minimum rating •0.1 µF capacitors should be size 0402 X5R ceramic, 6.3 V minimum rating •Capacitors should be placed next to the connected device power pins •A 0.15 Ohm resistor is recommended3.4.3 PCB layout considerationsThe power nets in Figure 19 can be implemented either as a plane island or routed power topology without changing the overall jitter performance of the device.ZL402051891922320.1 µF 0.1 µFvdd_core10 µF 0.1 µF0.15 Ωvdd0.1 µF 10 µFFigure 19 - Decoupling Connections for Power PinsAbsolute Maximum Ratings*Parameter Sym.Min.Max.Units 1Supply voltage V DD_R-0.5 4.6V 2Voltage on any digital pin V PIN-0.5VDD V 4LVPECL output current I out30mA 5Soldering temperature T260 °C 6Storage temperature T ST-55125 °C 7Junction temperature T j125 °C 8Voltage on input pin V input VDD V 9Input capacitance each pin C p500fF 4.0 AC and DC Electrical Characteristics* Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.* Voltages are with respect to ground (GND) unless otherwise statedRecommended Operating Conditions*Characteristics Sym.Min.Typ.Max.Units1Supply voltage 2.5 V mode V DD25 2.375 2.5 2.625V2Supply voltage 3.3 V mode V DD33 3.135 3.3 3.465V3Operating temperature T A-402585°C* Voltages are with respect to ground (GND) unless otherwise statedDC Electrical Characteristics - Current ConsumptionCharacteristics Sym.Min.Typ.Max.Units Notes 1Supply current LVPECL drivers -unloadedI dd_unload110mA Unloaded2Supply current LVPECL drivers - loaded (all outputs are active)I dd_load209mA Including powerto R L = 50DC Electrical Characteristics - Inputs and Outputs - for 3.3 V SupplyCharacteristics Sym.Min.Typ.Max.Units Notes1CMOS control logic high-level inputvoltageV CIH0.7*V DD V2CMOS control logic low-level inputvoltageV CIL0.3*V DD V3CMOS control logic Input leakagecurrentI IL1µA V I = V DD or 0 V4Differential input common modevoltageV CM 1.1 2.0V5Differential input voltage difference V ID0.251V6Differential input resistance V IR80100120ohm* This parameter was measured from 125 MHz to 750 MHz.* This parameter was measured from 125 MHz to 750 MHz.Figure 20 - Differential and Single-Ended Output Voltages Parameter Definitions7LVPECL output high voltage V OH V DD -1.40V 8LVPECL output low voltage V OL V DD - 1.62V 9LVPECL output differential voltage*V OD0.50.9VDC Electrical Characteristics - Inputs and Outputs - for 2.5 V SupplyCharacteristicsSym.Min.Typ.Max.Units Notes1Differential input common mode voltageV CM 1.1 1.6V 2Differential input voltage difference V ID 0.251V 3Differential input resistance V IR 80100120ohm 4LVPECL output high voltage V OH V DD -1.40V 5LVPECL output low voltage V OL V DD - 1.62V 6LVPECL output differential voltage*V OD0.40.9VDC Electrical Characteristics - Inputs and Outputs - for 3.3 V SupplyCharacteristicsSym.Min.Typ.Max.Units NotesAC Electrical Characteristics* - Inputs and Outputs (see Figure 21) - for 2.5/3.3 V supply.Characteristics Sym.Min.Typ.Max.Units Notes 1Maximum Operating Frequency1/t p750MHz2Input to output clock propagation delay t pd012ns3Output to output skew t out2out50100ps4Part to part output skew t part2part80300ps5Output clock Duty Cycle degradation t PWH/ t PWL-202Percent6LVPECL Output clock slew rate r SL0.75 1.2V/ns* Supply voltage and operating temperature are as per Recommended Operating ConditionsInputt Pt PWL t pdt PWHOutputFigure 21 - Input To Output TimingAdditive Jitter at 2.5 V*Output Frequency (MHz)Jitter MeasurementFilterTypical RMS (fs)Notes112512 kHz - 20 MHz 1392212.512 kHz - 20 MHz 1093311.0412 kHz - 20 MHz 85442512 kHz - 20 MHz 57550012 kHz - 20 MHz 506622.0812 kHz - 20 MHz 40775012 kHz - 20 MHz36Additive Jitter at 3.3 V*Output Frequency (MHz)Jitter MeasurementFilterTypical RMS (fs)Notes112512 kHz - 20 MHz 1152212.512 kHz - 20 MHz 853311.0412 kHz - 20 MHz 72442512 kHz - 20 MHz 55550012 kHz - 20 MHz 486622.0812 kHz - 20 MHz 41775012 kHz - 20 MHz395.0 Performance Characterization*The values in this table were taken with an approximate slew rate of 0.8 V/ns.*The values in this table were taken with an approximate slew rate of 0.8 V/ns.Additive Jitter from a Power Supply Tone*Carrier frequencyParameterTypicalUnitsNotes125MHz 25 mV at 100 kHz 115fs RMS 750MHz25 mV at 100 kHz59fs RMS* The values in this table are the additive periodic jitter caused by an interfering tone typically caused by a switching power supply. For this test, measurements were taken over the full temperature and voltage range for V DD = 2.5 V. The magnitude of the interfering tone is measured at the DUT.6.0 Typical BehaviorTypical Phase Noise at 622.08 MHzTypical Waveformat 155.52 MHzV OD versus FrequencyPropagation Delay versus TemperatureNote:This is for a single device. For more details see thePower Supply Tone Frequency (at 25 mV) versus PSRR at 125 MHz Power Supply Tone Frequency (at 25 mV) versus Additive Jitter at 125 MHzPower Supply Tone Magnitude (at 100 kHz) versus PSRR at 125 MHz Power Supply Tone Magnitude (at 100 kHz) versus Additive Jitter at 125 MHz7.0 Package CharacteristicsThermal DataParameter Symbol Test Condition Value UnitJunction to Ambient Thermal Resistance ΘJA Still Air1 m/s2 m/s 37.433.131.5o C/WJunction to Case Thermal Resistance ΘJC24.4o C/W Junction to Board Thermal Resistance ΘJB19.5o C/W Maximum Junction Temperature*T jmax125o C Maximum Ambient Temperature T A85o C© 2014 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense and security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world’s standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif. and has approximately 3,400 employees globally. Learn more at .Microsemi Corporate Headquarters One One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (800) 713-4113Outside the USA: +1 (949) 380-6100Sales: +1 (949) 380-6136Fax: +1 (949) 215-4996E-mail: ***************************Information relating to products and services furnished herein by Microsemi Corporation or its subsidiaries (collectively “Microsemi”) is believed to be reliable. However, Microsemi assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Microsemi or licensed from third parties by Microsemi, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Microsemi, or non-Microsemi furnished goods or services may infringe patents or other intellectual property rights owned by Microsemi.This publication is issued to provide information only and (unless agreed by Microsemi in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Microsemi without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user’s responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical and other products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Microsemi’s conditions of sale which are available on request.For more information about all Microsemi productsvisit our website at TECHNICAL DOCUMENTATION – NOT FOR RESALE。

2305芯片

2305芯片

2305芯片是一种高性能低功耗的微控制器芯片,适用于各种

智能设备和嵌入式系统。

该芯片采用先进的制造工艺和设计技术,集成了处理器核心、存储器和各种外设接口,具有强大的计算和控制能力。

首先,2305芯片采用先进的制造工艺,例如7纳米和14纳米

制程,确保芯片的性能和功耗方面的平衡。

先进的制造工艺可以在有限的面积上集成更多的晶体管,从而提供更高的计算能力和更低的功耗。

其次,2305芯片的处理器核心采用了先进的架构和指令集,

如ARM Cortex-M系列。

这些处理器核心具有高度优化的指令集和高度并行的执行单元,可以执行复杂的算法和实时控制任务。

同时,这些处理器核心还支持多核操作,可以平衡多个任务的执行。

第三,2305芯片具有丰富的外设接口,如串口、并行接口、

SD卡接口等。

这些外设接口可以与外部设备进行高速数据传

输和控制,实现与外部设备的连接和通信。

此外,2305芯片

还具有各种模拟接口,如模数转换器和比较器,可以实现对模拟信号的采集和处理。

第四,2305芯片还配备了大容量的存储器,包括闪存和RAM。

这些存储器可以存储程序代码、数据和配置信息,支持灵活的存储器管理和数据访问。

最后,2305芯片还支持多种通信协议,如CAN总线、SPI、I2C等。

通过这些通信协议,2305芯片可以与其他设备进行高效的数据交换和通信,实现设备之间的互连和协作。

总的来说,2305芯片是一款高性能低功耗的微控制器芯片,具有处理器核心、存储器和丰富的外设接口。

它适用于各种智能设备和嵌入式系统,提供强大的计算和控制能力,支持多核操作和多种通信协议。

Linear Technology LTC6363 系列精密、低功耗差分放大器 ADC 驱动器系列说

LTC6363 系列精密、低功耗差分放大器/ADC 驱动器系列特点⏹提供用户设置增益或0.5V/V、1V/V、2V/V的固定增益⏹折合到输入端噪声:2.9nV/√Hz⏹电源电流:2mA(最大值)⏹增益误差:45ppm(最大值)⏹增益误差漂移:0.5ppm/°C(最大值)⏹CMRR:94dB(最小值)⏹失调电压:100µV(最大值)⏹输入失调电流:50nA(最大值)⏹快速建立时间:720ns 至18 位,8V P–P输出⏹电源电压范围:2.8V (±1.4V) 至11V (±5.5V) ⏹差分轨到轨输出⏹输入共模范围包含地⏹低失真:115dB SFDR,2kHz 时,18V P–P⏹增益带宽积:500MHz⏹–3dB 带宽:35MHz⏹低功耗关断:20µA (V S = 3V)⏹8 引脚MSOP 和2 mm × 3mm 8 引脚DFN 封装应用⏹20 位、18 位和16 位SAR ADC 驱动器⏹单端至差分转换⏹低功耗ADC 驱动器⏹电平转换器⏹差分线路驱动器⏹电池供电仪器仪表说明LTC®6363系列包括四款全差分、低功耗、低噪声放大器,提供轨到轨输出,针对SAR ADC 驱动进行了优化。

LTC6363 是一款独立的差分放大器,其增益通常利用四个外部电阻设置。

LTC6363–0.5、LTC6363–1 和LTC6363–2 均有内部匹配电阻,形成增益分别为0.5V/V、1V/V 和2V/V 的固定增益模块。

每个固定增益放大器都有激光调整的精密片内电阻,可实现精确、超稳定的增益和出色的CMRR。

系列选型表产品型号增益配置LTC6363 用户设置LTC6363–0.5 0.5V/VLTC6363–1 1V/VLTC6363–22V/V所有注册商标和商标均属各自所有人所有。

典型应用从以地为基准的单端输入到LTC2378–20 SAR ADC 的直流耦合接口LTC6363–1 驱动LTC2378–20f IN = 2kHz,–1dBFS,131k 点FFTLTC6363 系列 绝对最大额定值(注释 1)总电源电压 (V + – V –) ........................................... 12V 输入电压(+IN 、–IN )(注释 2)LTC6363–0.5 ........ (V –) – 14.9V 至 (V +) + 14.9V LTC6363–1 ........... (V –) – 11.1V 至 (V +) + 11.1V LTC6363–2 ........... (V –) – 7.45V 至 (V +) + 7.45V 输入电流(+IN 、–IN )LTC6363(注释 3)............................................................................. ±10mA 输入电流(V OCM 、SHDN )(注释 3) .................................................. ±10mA 输出短路持续时间(注释 4) ......................................... 受散热限制 工作温度范围(注释 5)LTC6363I/LTC6363I–0.5/LTC6363I–1/ LTC6363I–2 ................................... –40°C 至 85°C LTC6363H/LTC6363H–0.5/LTC6363H–1/LTC6363H–2 ............................... –40°C 至 125°C 额定温度范围(注释 6)LTC6363I/LTC6363I–0.5/LTC6363I–1/LTC6363I–2 .................................. –40°C 至 85°C LTC6363H/LTC6363H–0.5/LTC6363H–1/LTC6363H–2............................... –40°C 至 125°C 最高结温 .............................................................. 150°C 存储温度范围 .................................. –65°C 至 150°C MSOP 引脚温度(焊接,10 秒) ................ 300°C引脚配置LTC6363LTC6363LTC6363–0.5/LTC6363–1/LTC6363–2订购信息 /product/LTC6363#orderinfo管装卷带和卷盘 器件标识* 封装说明温度范围 LTC6363IMS8#PBF LTC6363IMS8#TRPBF LTGSQ 8 引脚塑料 MSOP –40°C 至 85°C LTC6363HMS8#PBFLTC6363HMS8#TRPBFLTGSQ8 引脚塑料 MSOP –40°C 至 125°C LTC6363IMS8–0.5#PBF LTC6363IMS8–0.5#TRPBF LTGST 8 引脚塑料 MSOP –40°C 至 85°C LTC6363HMS8–0.5#PBF LTC6363HMS8–0.5#TRPBF LTGST 8 引脚塑料 MSOP –40°C 至 125°C LTC6363IMS8–1#PBF LTC6363IMS8–1#TRPBF LTGSR 8 引脚塑料 MSOP –40°C 至 85°C LTC6363HMS8–1#PBF LTC6363HMS8–1#TRPBF LTGSR 8 引脚塑料 MSOP –40°C 至 125°C LTC6363IMS8–2#PBF LTC6363IMS8–2#TRPBF LTGSS 8 引脚塑料 MSOP –40°C 至 85°C LTC6363HMS8–2#PBFLTC6363HMS8–2#TRPBFLTGSS8 引脚塑料 MSOP–40°C 至 125°CLTC6363 系列订购信息无铅表面处理卷带和卷盘(迷你型)卷带和卷盘器件标识*封装说明温度范围LTC6363IDCB#TRMPBF LTC6363IDCB#TRPBF LGVG 8 引脚(2mm × 3mm) 塑料DFN –40°C 至85°CLTC6363HDCB#TRMPBF LTC6363HDCB#TRPBF LGVG 8 引脚(2mm × 3mm) 塑料DFN –40°C 至125°CTRM = 500 片。

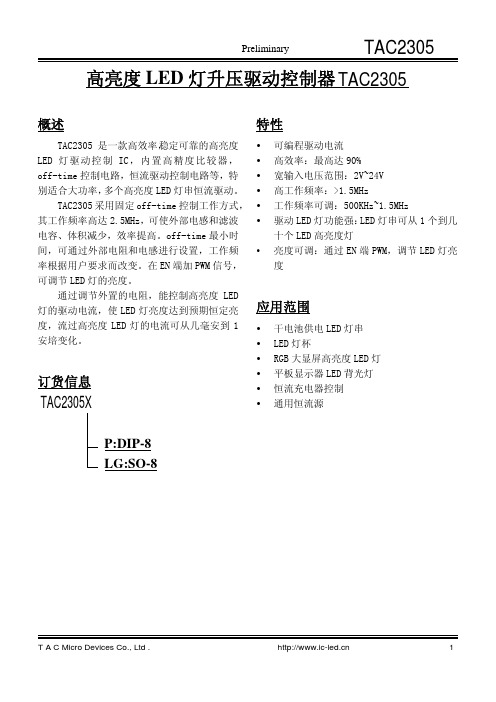

TAC2305升压恒流IC

Preliminary

Preliminary

Preliminary

Preliminary

通过储能电感的最大电流为I

LMAX =250/R

CS

(mA),通过LED的平均电流ILED约为3R×I

LMAX。

Rcs

阻值不同,就可设置通过LED的驱动电流,R CS越小,驱动电流越大。

R

CS

的选择公式如下:

Rcs=250mV

(I LED+0.5×I L)

I LED为通过LED灯的电流;I L为通过电感L的峰值电流

例如:I L=150mA I LED=500mA 则R CS=0.43Ω

RC和CC的选用

RC和CC为补电容和电阻,通常在工作频率高才使用。

MOSFET的选用

首先要考虑MOS管的耐压,一般要求MOS管的耐压高于输出电压2倍。

其次,根据驱动LED灯电流的大小,选择MOS管的I DS最大电流。

一般情况下,应选用MOS管的I DS最大电流是LED灯驱动电流的5倍以上。

另外,MOS管的内阻要小,以减小在MOS管上的功率损耗;MOS 管的R DS应小于0.3欧以下,LED驱动电流越大;R DS应越小,R DS越小,变换效率越高。

包装。

LMX2305TMX;中文规格书,Datasheet资料

LMX2305LMX2305 PLLatinum Frequency Synthesizer for RF Personal CommunicationsLiterature Number: SNAS108ATL W 12459LMX2305 PLLatinum 550 MHz Frequency Synthesizer for RF Personal CommunicationsPRELIMINARYAugust1996 LMX2305PLLatinum TM550MHz Frequency Synthesizerfor RF Personal CommunicationsGeneral DescriptionThe LMX2305is a high performance frequency synthesizerwith an integrated prescaler designed for RF operation up to550MHz It is fabricated using National’s ABiC IV BiCMOSprocessThe LMX2305contains a dual modulus prescaler which canselect either a64 65or a128 129divide ratio at input fre-quencies of up to550MHz LMX2305 which employs thedigital phase lock loop technique combined with a highquality reference oscillator and a loop filter provides thetuning voltage for the voltage controlled oscillator to gener-ate a very stable low noise local oscillator signalSerial data is transferred into the LMX2305via a three lineMICROWIRE TM interface(Data Enable Clock) Supply volt-age can range from2 65V to5 5V The LMX2305featuresvery low current consumption typically4 0mA at2 75VThe LMX2305is available in a TSSOP20-pin surface mountplastic packageFeaturesY RF operation up to550MHzY2 65V to5 5V operationY Low current consumptionI CC e4 0mA(typ)at V CC e2 75VY Dual modulus prescaler 64 65or128 129Y Internal balanced low leakage charge pumpY Small-outline plastic surface mount TSSOP0 173 wide packageApplicationsY Analog Cellular telephone systems(AMPS ETACS NMT)Y Portable wireless communications(PCS PCN cordless)Y Wireless local area networks(WLANs)Y Other wireless communication systemsY PagersBlock DiagramTL W 12459–1TRI-STATE is a registered trademark of National Semiconductor CorporationMICROWIRE TM and PLLatinum TM are trademarks of National Semiconductor CorporationC1996National Semiconductor Corporation RRD-B30M126 Printed in U S A http www national com ObsoleteConnection DiagramLMX2305TL W 12459–220-Lead (0 173 Wide)Thin ShrinkSmall Outline Package (TM)Order Number LMX2305TM or LMX2305TMXSee NS Package Number MTC20Pin DescriptionsPin No Pin Name I O Description1OSC INIOscillator input A CMOS inverting gate input intended for connection to a crystal resonator for operation as an oscillator The input has a V CC 2input threshold and can be driven from an external CMOS or TTL logic gate May also be from a reference oscillator 3OSC OUTO Oscillator output4V P Power supply for charge pump Must be t V CC5V CC Power supply voltage input Input may range from 2 65V to 5 5V Bypass capacitors should be placed as close as possible to this pin and be connected directly to the ground plane 6D o OInternal charge pump output For connection to a loop filter for driving the input of an external VCO 7GND Ground8LD O Lock detect Output provided to indicate when the VCO frequency is in ‘‘lock’’ When the loop is locked the pin’s output is HIGH with narrow low pulses10f IN IPrescaler input Small signal input from the VCO 11CLOCK I High impedance CMOS Clock input Data is clocked in on the rising edge into the various counters and registers13DATA I Binary serial data input Data entered MSB first LSB is control bit High impedance CMOS input 14LEI Load enable input (with internal pull-up resistor) When LE transitions HIGH data stored in the shift registers is loaded into the appropriate latch (control bit dependent) Clock must be low when LE toggles high or low See Serial Data Input Timing Diagram15FC I Phase control select (with internal pull-up resistor) When FC is LOW the polarity of the phase comparator and charge pump combination is reversed16BISW OAnalog switch output When LE is HIGH the analog switch is ON routing the internal charge pump output through BISW (as well as through D o ) 17f OUT O Monitor pin of phase comparator input CMOS output18w pO Output for external charge pump w p is an open drain N-channel transistor and requires a pull-up resistor19PWDN IPower Down (with internal pull-up resistor) PWDN e HIGH for normal operation PWDN e LOW for power savingPower down function is gated by the return of the charge pump to a TRI-STATE condition 20w r OOutput for external charge pump w r is a CMOS logic output2 9 12NCNo connecthttp www national com2Ob s ol et eFunctional Block DiagramTL W 12459–3Note 1 The power down function is gated by the charge pump to prevent any unwanted frequency jumps Once the power down pin is brought low the part will go into power down mode when the charge pump reaches a TRI-STATE conditionhttp www national com3Ob s ol et eAbsolute Maximum Ratings (Notes 1and 2)If Military Aerospace specified devices are required please contact the National Semiconductor Sales Office Distributors for availability and specifications Power Supply Voltage V CC b 0 3V to a 6 5V V P b 0 3V to a 6 5V Voltage on Any Pin with GND e 0V (V I )b 0 3V to V CC a 0 3V Storage Temperature Range (T S )b 65 C to a 150 CLead Temperature (T L )(solder 4sec )a 260 CRecommended Operating ConditionsPower Supply Voltage V CC 2 65V to 5 5V V P V CC to a 5 5V Operating Temperature (T A )b 40 C to a 85 CNote 1 Absolute Maximum Ratings indicate limits beyond which damage to the device may occur Operating Ratings indicate conditions for which the device is intended to be functional but do not guarantee specific perform-ance limits For guaranteed specifications and test conditions see the Elec-trical Characteristics The guaranteed specifications apply only for the test conditions listedNote 2 This device is a high performance RF integrated circuit with an ESD rating k 2keV and is ESD sensitive Handling and assembly of this device should only be done at ESD workstationsElectrical Characteristics V CC e 2 75V V P e 2 75V b 40 C k T A k 85 C except as specifiedSymbol ParameterConditionsMinTyp Max Units I CC Power Supply Current 46mA I CC-PWDN Power Down Current30180m A f IN RF Input Operating Frequency 45550MHzf OSC Oscillator Input Operating Frequency 522MHz f w Phase Detector Frequency 10MHz Pf IN Input Sensitivity V CC e 2 65V to 5 5V b 10a 6dBmV OSC Oscillator Sensitivity OSC IN 0 5V PP V IH High-Level Input Voltage 0 7V CCV V IL Low-Level Input Voltage0 3V CCV I IH High-Level Input Current (Clock Data)V IH e V CC e 5 5Vb 1 01 0m A I IL Low-Level Input Current (Clock Data)V IL e 0V V CC e 5 5V b 1 01 0m A I IH Oscillator Input CurrentV IH e V CC e 5 5V 100m A I IL V IL e 0V V CC e 5 5V b 100m AI IH High-Level Input Current (LE FC)V IH e V CC e 5 5V b 1 01 0m A I ILLow-Level Input Current (LE FC)V IL e 0V V CC e 5 5Vb 1001 0m AExcept f IN and OSC INhttp www national com4Ob s ol et eElectrical Characteristics V CC e 2 75V V P e 2 75V b 40 C k T A k 85 C except as specified (Continued)Symbol ParameterConditionsMin TypMaxUnits I D o -source Charge Pump Output CurrentV D o e V P 2b 2 5b 1 0mA I D o -sink V D o e V P 21 02 5mAI D o -Tri Charge Pump TRI-STATE Current 0 5V s V D o s V P b 0 5V b 5 05 0nA T A e b 40 C k T A k 85 C V OH High-Level Output Voltage I OH e b 1 0mA V CC b 0 8VV OL Low-Level Output VoltageI OL e 1 0mA 0 4V V OH High-Level Output Voltage (OSC OUT )I OH e b 200m A V CC b 0 8V V OL Low-Level Output Voltage (OSC OUT )I OL e 200m A 0 4V I OL Open Drain Output Current (w p )V OL e 0 4V 1 0mA I OH Open Drain Output Current (w p )V OH e 2 75V 100m A t CS Data to Clock Set Up Time See Data Input Timing 50ns t CH Data to Clock Hold Time See Data Input Timing 10ns t CWH Clock Pulse Width High See Data Input Timing 50ns t CWL Clock Pulse Width Low See Data Input Timing 50ns t ES Clock to Enable Set Up Time See Data Input Timing 50ns t EWEnable Pulse WidthSee Data Input Timing50nsExcept OSC OUThttp www national com5Ob s ol et eFunctional DescriptionThe simplified block diagram below shows the 19-bit data register the 14-bit R Counter and the R15Latch and the 18-bit N Counter (intermediate latches are not shown) The data stream is clocked (on the rising edge)into the DATA input MSB first If the Control Bit (last bit input)is HIGH the DATA is transferred into the R Counter (programmable reference divider)and the S Latch (prescaler select 64 65or 128 129) If the Control Bit (LSB)is LOW the DATA is transferred into the N Counter (programmable divider)TL W 12459–1PROGRAMMABLE REFERENCE DIVIDER (R COUNTER)AND PRESCALER SELECT (R15LATCH)If the Control Bit (last bit shifted into the Data Register)is HIGH data is transferred from the 19-bit shift register into a 14-bit latch (which sets the 14-bit R Counter)and the 1-bit R15Latch which sets the prescaler 64 65or 128 129 Serial data format is shown belowTL W 12459–1414-BIT PROGRAMMABLE REFERENCE DIVIDER RATIO (R COUNTER)Divide14R 13R 12R 11R 10R R 9R 8R 7R 6R 5R 4R 3R 2R1RatioR 3000000000000114000000100###############1638311111111111111Notes Divide ratios less than 3are prohibitedDivide ratio 3to 16383R1to R14 These bits select the divide ratio of the programmable reference dividerC Control bit (set to HIGH level to load R counter and R15Latch)Data is shifted in MSB first1-BIT PRESCALER SELECT (R15LATCH)Prescaler 15R Select P 128 129064 651http www national com6Ob s ol et eFunctional Description (Continued)PROGRAMMABLE DIVIDER (N COUNTER)The N counter consists of the 7-bit swallow counter (A counter)and the 11-bit programmable counter (B counter) If the Control Bit (last bit shifted into the Data Register)is LOW data is transferred from the 19-bit shift register into a 7-bit latch which sets the 7-bit Swallow (A)Counter and an 11-bit latch which sets the 11-bit programmable (B)Counter Serial data format is shown belowTL W 12459–15Note S8to S18 Programmable counter divide ratio control bits (3to 2047)7-BIT SWALLOW COUNTER DIVIDE RATIO (A COUNTER)Divide N 7N 6N 5N 4N 3N 2N 1Ratio A 0000000011########1271111111Note Divide ratio 0to 127B t A11-BIT PROGRAMMABLE COUNTER DIVIDE RATIO (B COUNTER)Divide 18N 17N 16N 15N 14N 13N 12N 11N 10N N 9N 8Ratio B 30000000001141############204711111111111Note Divide ratio 3to 2047(Divide ratios less than 3are prohibited)B t APULSE SWALLOW FUNCTION f VCO e (P c B)a A c f OSC Rf VCO Output frequency of external voltage controlled oscil-lator (VCO)B Preset divide ratio of binary 11-bit programmablecounter (3to 2047)APreset divide ratio of binary 7-bit swallow counter (0s A s 127 A s B)f OSC Output frequency of the external reference frequencyoscillator R Preset divide ratio of binary 14-bit programmable ref-erence counter (3to 16383)P Preset modulus of dual modulus prescaler (64or 128)http www national com7Ob s ol et eFunctional Description (Continued)SERIAL DATA INPUT TIMINGTL W 12459–16Notes Parenthesis data indicates programmable reference divider dataData shifted into register on clock rising edge Data is shifted in MSB firstTest Conditions The Serial Data Input Timing is tested using a symmetrical waveform around V CC 2 The test waveform has an edge rate of 0 6V ns withamplitudes of 2 2V V CC e 2 7V and 2 6V V CC e 5 5VPhase CharacteristicsIn normal operation the FC pin is used to reverse the polari-ty of the phase detector Both the internal and any external charge pump are affectedDepending upon VCO characteristics FC pin should be set accordinglyWhen VCO characteristics are like (1) FC should be set HIGH or OPEN CIRCUITWhen VCO characteristics are like (2) FC should be set LOWWhen FC is set HIGH or OPEN CIRCUIT the monitor pin of the phase comparator input f out is set to the reference divider output f r When FC is set LOW f out is set to the programmable divider output f pVCO CharacteristicsTL W 12459–17PHASE COMPARATOR AND INTERNAL CHARGE PUMP CHARACTERISTICSTL W 12459–18Notes Phase difference detection range b 2q to a 2qThe minimum width pump up and pump down current pulses occur at the D o pin when the loop is locked FC e HIGHhttp www national com8Ob s ol et eAnalog SwitchThe analog switch is useful for radio systems that utilize a frequency scanning mode and a narrow band mode The purpose of the analog switch is to decrease the loop filter time constant allowing the VCO to adjust to its new frequency in a shorter amount of time This is achieved by adding another filter stage in parallel The output of the charge pump is normally through the D o pin but when LE is set HIGH the charge pump output also becomes available at BISW A typical circuit is shown below The second filter stage (LPF-2)is effective only when the switch is closed (in the scanning mode)TL W 12459–19Typical Crystal Oscillator CircuitA typical circuit which can be used to implement a crystal oscillator is shown belowTL W 12459–20Typical Lock Detect CircuitA lock detect circuit is needed in order to provide a steady LOW signal when the PLL is in the locked state A typical circuit is shown belowTL W 12459–21http www national com9Ob s ol e t e分销商库存信息: NATIONAL-SEMICONDUCTOR LMX2305TMX。

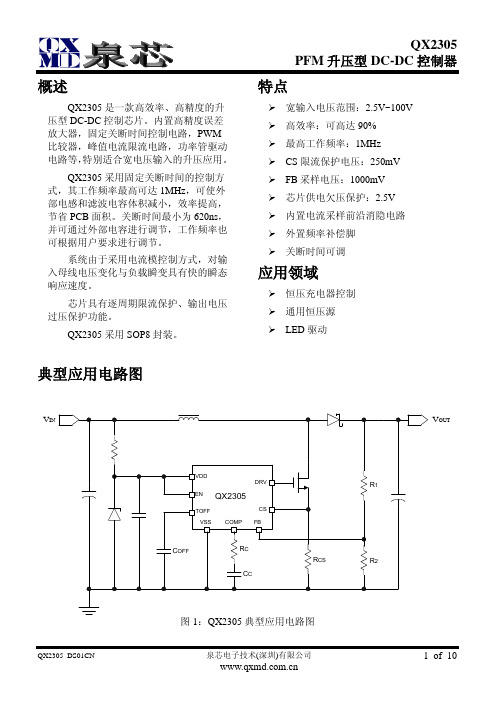

QX2305升压型DC-DC控制器

极限参数(注 1)

参数

符号

描述

最小值 最大值 单位

电压

VMAX

VDD 最大电压

EN、COMP、FB、DRV、CS 和 VMIN_MAX TOFF 脚电压

-0.3

7

V

VDD+0.3

V

最大功耗 温度

PSOP8 TJ TA

TSTG TSD

SOP8 最大功耗

结温范围

-20

工作温度

-20

存储温度

-40

焊接温度范围(时间少于 30 秒)

芯片通过 CS 管脚采样电感电流,实 现峰值电流控制,此外,CS 脚还用来限制 最大输入电流,实现过流保护功能。

系统关断时间可通过连接到TOFF管 脚的电容COFF来设置,通过设定关断时间, 可设置系统的工作频率。

COMP 管脚是误差放大器输出端,可 以在 COMP 脚外接电阻、电容来实现频率 补偿。

客户服务中心

泉芯电子技术(深圳)有限公司 地址:中国深圳市南山区南头关口二路智恒新兴产业园 22 栋 4 楼 邮编:518052 电话:+86-0755-88852177 传真:+86-0755-86350858 网址:

QX2305_DS01CN

泉芯电子技术(深圳)有限公司

DRV 脚接 500pF 电容 DRV 脚接 500pF 电容

1000

KHz

ns

V

0.8

V

50

ns

50

ns

QX2305_DS01CN

泉芯电子技术(深圳)有限公司

5 of 10

TOFF(us) IINQ(uA)

典型参数曲线

除非特别说明,VDD=5V,TA =25 oC

展讯系列各芯片组的参数

展讯系列各芯片组的参数

一、展讯A系列芯片组参数

展讯A系列芯片组是展讯公司旗下高性能芯片组产品,主要应用于智能手机、平板电脑等移动设备产品。

以下是展讯A系列芯片组的主要参数:

•CPU核心:八核心ARM Cortex-A76/A55

•GPU型号:ARM Mali-G76/G52

•制程工艺:7nm

•支持的无线通信标准:5G/4G/3G

•支持的摄像头像素:最高支持1亿像素

•视频解码支持:最高支持8K@30fps

二、展讯B系列芯片组参数

展讯B系列芯片组是展讯公司面向中低端市场推出的芯片组产品,主要应用于入门级智能手机、平板电脑等产品。

以下是展讯B系列芯片组的主要参数:

•CPU核心:四核心ARM Cortex-A53

•GPU型号:ARM Mali-T720

•制程工艺:12nm

•支持的无线通信标准:4G/3G

•支持的摄像头像素:最高支持5000万像素

•视频解码支持:最高支持1080p@30fps

以上是展讯公司旗下A系列和B系列芯片组的主要参数。

展讯公司不断创新技术,推出高性能和低功耗的芯片组产品,满足不同市场需求。

LTC2302资料

123026fT YPICAL APPLICATIONF EATURESA PPLICATIONSD ESCRIPTION 1-/2-Channel, 12-Bit ADCsThe L TC ®2302/L TC2306 are low noise, 500ksps, 1-/2-chan-nel, 12-bit ADCs with an SPI/MICROWIRE compatible serial interface. These ADCs include a fully differential sample-and-hold circuit to reduce common mode noise. The internal conversion clock allows the external serial output data clock (SCK) to operate at any frequency up to 40MHz.The L TC2302/L TC2306 operate from a single 5V supply and draw just 2.8mA at a sample rate of 500ksps. The auto-shutdown feature reduces the supply current to 14μA at a sample rate of 1ksps.The L TC2302/L TC2306 are packaged in a tiny 10-pin 3mm × 3mm DFN. The low power consumption and small size make the L TC2302/L TC2306 ideal for battery-operated and portable applications, while the 4-wire SPI compat-ible serial interface makes these ADCs a good match for isolated or remote data acquisition systems.8192 Point FFT , f IN = 1kHz (L TC2306)n12-Bit Resolutionn 500ksps Sampling Rate n Low Noise: SINAD = 72.8dB n Guaranteed No Missing Codes n Single 5V SupplynAuto-Shutdown Scales Supply Current with Sample Raten Low Power: 14mW at 500ksps 70μW at 1ksps 35μW Sleep Moden 1-Channel (L TC2302) and 2-Channel (L TC2306) Versionsn Unipolar or Bipolar Input Ranges (Software Selectable)n Internal Conversion Clockn SPI/MICROWIRE ™ Compatible Serial Interface n Separate Output Supply OV DD(2.7V to 5.25V)n Software Compatible with the L TC2308n 10-Pin (3mm × 3mm) DFN PackagenHigh Speed Data Acquisition n Industrial Process Control n Motor Control n Accelerometer Measurements n Battery-Operated Instrumentsn Isolated and/or Remote Data AcquisitionTYPENUMBER OF INPUT CHANNELS128Int Reference L TC2308Ext ReferenceL TC2302L TC2306L , L T , L TC and L TM are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.CH0 (IN +CH1 (IN –ANALOG INPUTS 0V TO 4.096V UNIPOLAR±2.048V BIPOLAR REFFREQUENCY (kHz)0–40–20020023026 TA01b–60–8050100150250–100–120–50–30–10–70–90–110–130–140M A G N I T U D E (d B )f SMPL = 500kHz SINAD = 72.8dB THD = –88.7dB223026fA BSOLUTE MAXIMUM RATINGS Supply Voltage (V DD , OV DD ) .........................–0.3V to 6V Analog Input Voltage (Note 3) C H0(IN +)-CH1(IN –),REF ..............................(GND – 0.3V) to (V DD + 0.3V)Digital Input Voltage (Note 3) .............................(GND – 0.3V) to (V DD + 0.3V)(Notes 1, 2)LEAD FREE FINISH TAPE AND REEL PART MARKING*PACKAGE DESCRIPTIONTEMPERATURE RANGE L TC2302CDD#PBF L TC2302CDD#TRPBF LDGV 10-Lead (3mm × 3mm) Plastic DFN 0°C to 70°C L TC2302IDD#PBF L TC2302IDD#TRPBF LDGV 10-Lead (3mm × 3mm) Plastic DFN –40°C to 85°C L TC2306CDD#PBF L TC2306CDD#TRPBF LDGW 10-Lead (3mm × 3mm) Plastic DFN 0°C to 70°C L TC2306IDD#PBFL TC2306IDD#TRPBFLDGW10-Lead (3mm × 3mm) Plastic DFN–40°C to 85°CConsult L TC Marketing for parts specifi ed with wider operating temperature ranges. *The temperature grade is identifi ed by a label on the shipping container .Consult L TC Marketing for information on non-standard lead based fi nish parts.For more information on lead free part marking, go to: http://www.linear .com/leadfree/ For more information on tape and reel specifi cations, go to: http://www.linear .com/tapeandreel/ORDER INFORMATIONTOP VIEW11L TC2302DD PACKAGE10-LEAD (3mm s 3mm) PLASTIC DFN10967845321OV DD SCK SDI GND V REFSDO CONVST V DD IN +IN –T JMAX = 150°C, θJA = 43°C/WEXPOSED PAD (PIN 11) IS GND, MUST BE SOLDERED TO PCBTOP VIEW11L TC2306DD PACKAGE10-LEAD (3mm s 3mm) PLASTIC DFN10967845321OV DD SCK SDI GND V REFSDO CONVST V DD CH0CH1T JMAX = 150°C, θJA = 43°C/WEXPOSED PAD (PIN 11) IS GND, MUST BE SOLDERED TO PCBP IN CONFIGURATION Digital Output Voltage ...(GND – 0.3V) to (OV DD + 0.3V)Power Dissipation ...............................................500mW Operating Temperature RangeL TC2302C/L TC2306C ...............................0°C to 70°C L TC2302I/L TC2306I ..............................–40°C to 85°C Storage Temperature Range ...................–65°C to 150°C323026fCONVERTER AND MULTIPLEXER CHARACTERISTICS SYMBOL PARAMETERCONDITIONS MIN TYP MAX UNITSV IN +Absolute Input Range (CH0, CH1, IN +)(Note 9)l –0.05V DD V V IN –Absolute Input Range (CH0, CH1, IN –)Unipolar (Note 9)Bipolar (Note 9)l l –0.05–0.05V DD /2V DDV V V IN + – V IN –Input Differential Voltage Range V IN = V IN + – V IN – (Unipolar)V IN = V IN + – V IN – (Bipolar)l l 0 to V REF ±V REF /2V VI IN Analog Input Leakage Current l±1μA C IN Analog Input CapacitanceSample Mode Hold Mode555pF pF CMRRInput Common Mode Rejection Ratio70dBThe l denotes the specifi cations which apply over the full operating temperature range, otherwise specifi cations are at T A = 25°C. (Notes 4, 5)PARAMETERCONDITIONSMIN TYP MAX UNITS Resolution (No Missing Codes)l12Bits Integral Linearity Error (Note 6)l ±0.3±1LSB Differential Linearity Error l±0.25±1LSB Bipolar Zero Error (Note 7)l±1±6LSB Bipolar Zero Error Drift 0.002LSB/°C Unipolar Zero Error (Note 7)l±1±6LSB Unipolar Zero Error Drift0.002LSB/°C Unipolar Zero Error Match (L TC2306)±0.3±3LSB Bipolar Full-Scale Error (Note 8)l ±1.5±8LSB Bipolar Full-Scale Error Drift 0.05LSB/°C Unipolar Full-Scale Error (Note 8)l±1.2±6LSB Unipolar Full-Scale Error Drift0.05LSB/°C Unipolar Full-Scale Error Match (L TC2306)±0.3±3LSBANALOG INPUT The l denotes the specifi cations which apply over the full operating temperature range, otherwisespecifi cations are at T A = 25°C. (Note 4)SYMBOLPARAMETER CONDITIONSMIN TYP MAX UNITSV REF Input Rangel 0.1V DD V I REF Reference Input Current f SMPL = 0ksps, V REF = 4.096Vf SMPL = 500ksps, V REF = 4.096Vl l5023080260μA μA C REFReference Input Capacitance55pFREFERENCE INPUT The l denotes the specifi cations which apply over the full operating temperature range,otherwise specifi cations are at T A = 25°C. (Note 4)423026fSYMBOL PARAMETERCONDITIONS MIN TYP MAX UNITSV IH High Level Input Voltage V DD = 5.25V l 2.4V V IL Low Level Input Voltage V DD = 4.75V l 0.8V I IN High Level Input Current V IN = V DDl±10μA C IN Digital Input Capacitance 5pF V OH High Level Output Voltage OV DD = 4.75V , I OUT = –10μAOV DD = 4.75V , I OUT = –200μA l 44.74V VV OL Low Level Output Voltage OV DD = 4.75V , I OUT = 160μA OV DD = 4.75V , I OUT = 1.6mA l 0.050.4V V I OZ Hi-Z Output Leakage V OUT = 0V to OV DD , CONVST High l±10μA C OZ Hi-Z Output Capacitance CONVST High 15pF I SOURCE Output Source Current V OUT = 0V –10mA I SINKOutput Sink CurrentV OUT = OV DD10mADIGITAL INPUTS AND DIGITAL OUTPUTS The l denotes the specifi cations which apply over thefull operating temperature range, otherwise specifi cations are at T A = 25°C. (Note 4)SYMBOL PARAMETER CONDITIONSMIN TYP MAX UNITSV DD Supply Voltagel 4.755 5.25V OV DD Output Driver Supply Voltage l 2.75.25V I DD Supply CurrentSleep Mode C L = 25pFCONVST = 5V , Conversion Done l l2.873.515mA μA P DPower Dissipation Sleep Mode1435mW μWPOWER REQUIREMENTS The l denotes the specifi cations which apply over the full operating temperaturerange, otherwise specifi cations are at T A = 25°C. (Note 4)SYMBOL PARAMETERCONDITIONS MIN TYP MAX UNITS SINAD Signal-to-(Noise + Distortion) Ratio f IN = 1kHz l 7172.8dB SNR Signal-to-Noise Ratio f IN = 1kHzl 7173.2dBTHD Total Harmonic Distortion f IN = 1kHz, First 5 Harmonics l –88–78dB SFDRSpurious Free Dynamic Range f IN = 1kHz l7989dB Channel-to-Channel Isolation f IN = 1kHz –109dB Full Linear Bandwidth (Note 11)700kHz –3dB Input Linear Bandwidth 25MHz Aperature Delay 13ns T ransient ResponseFull-Scale Step 240nsDYNAMIC ACCURACY The l denotes the specifi cations which apply over the full operating temperature range,otherwise specifi cations are at T A = 25°C. A IN = –1dBFS. (Notes 4, 10)TIMING CHARACTERISTICSThel denotes the specifi cations which apply over the full operating temperature range, otherwise specifi cations are at T A = 25°C. (Note 4)SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS f SMPL(MAX)Maximum Sampling Frequency l500kHz f SCK Shift Clock Frequency l40MHz t WHCONV CONVST High Time(Note 9)l20ns t HD Hold Time SDI After SCK↑l 2.5ns t SUDI Setup Time SDI Stable Before SCK↑l0ns t WHCLK SCK High Time f SCK = f SCK(MAX)l10ns t WLCLK SCK Low Time f SCK = f SCK(MAX)l10ns t WLCONVST CONVST Low Time During Data T ransfer(Note 9)l410ns t HCONVST Hold Time CONVST Low After Last SCK↓(Note 9)l20ns t CONV Conversion Time l 1.3 1.6μs t ACQ Acquisition Time7th SCK↑ to CONVST↑ (Note 9)l240ns t dDO SDO Data Valid After SCK↓C L = 25pF (Note 9)l10.812.5ns t hDO SDO Hold Time SCK↓C L = 25pF l4ns t en SDO Valid After CONVST↓C L = 25pF l1115ns t dis Bus Relinquish Time C L = 25pF l1115ns t r SDO Rise Time C L = 25pF4ns t f SDO Fall Time C L = 25pF4ns t CYC Total Cycle Time2μsNote 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.Note 2: All voltage values are with respect to ground with V DD and OV DD wired together (unless otherwise noted).Note 3: When these pin voltages are taken below ground or above V DD, they will be clamped by internal diodes. These products can handle input currents greater than 100mA below ground or above V DD without latchup. Note 4: V DD = 5V, OV DD = 5V, V REF = 4.096V, f SMPL = 500ksps, unless otherwise specifi ed.Note 5: Linearity, offset and full-scale specifi cations apply for a single-ended analog input with respect to GND for the L TC2306 and IN+ with respect to IN– tied to GND for the L TC2302.Note 6: Integral nonlinearity is defi ned as the deviation of a code from a straight line passing through the actual endpoints of the transfer curve. The deviation is measured from the center of the quantization band.Note 7: Bipolar zero error is the offset voltage measured from –0.5LSB when the output code fl ickers between 0000 0000 0000 and 1111 1111 1111. Unipolar zero error is the offset voltage measured from +0.5LSB when the output code fl ickers between 0000 0000 0000 and 0000 0000 0001.Note 8: Full-scale bipolar error is the worst-case of –FS or +FS untrimmed deviation from ideal fi rst and last code transitions and includes the effect of offset error. Unipolar full-scale error is the deviation of the last code transition from ideal and includes the effect of offset error.Note 9: Guaranteed by design, not subject to test.Note 10: All specifi cations in dB are referred to a full-scale ±2.048V input with a 4.096V reference voltage.Note 11: Full linear bandwidth is defi ned as the full-scale input frequency at which the SINAD degrades to 60dB or 10 bits of accuracy.523026f623026fT YPICAL PERFORMANCE CHARACTERISTICS Integral Nonlinearity vs Output CodeDifferential Nonlinearity vsOutput Code1kHz Sine Wave 8192 Point FFT PlotSNR vs Input FrequencySINAD vs Input FrequencyTHD vs Input FrequencySupply Current vs Sampling FrequencySupply Current vs Temperature(L TC2302) T A = 25°C, V DD = OV DD = 5V , V REF = 4.096V , f SMPL= 500ksps, unless otherwise noted.OUTPUT CODEI N L (L S B )00.250.50409623026 G01–0.25–0.50–1.00102420483072–0.751.000.75OUTPUT CODED N L (L S B )0.250.50409623026 G02–0.25–0.50–1.00102420483072–0.751.000.75FREQUENCY (kHz)0–40–20020023026 G03–60–8050100150250–100–120–50–30–10–70–90–110–130–140M A G N I T U D E (d B )SNR = 73.2dB SINAD = 72.8dBTHD = –89.5dBFREQUENCY (kHz)150S N R (d B )70758010100100023026 G04656055FREQUENCY (kHz)150S I N A D (d B )70758010100100023026 G05656055FREQUENCY (kHz)1–80T HD (d B )–70–6010100100023026 G06–90–85–75–65–95–100SAMPLING FREQUENCY (ksps)12.0S U P P L Y C U RR E N T (m A )2.53.03.510100100023026 G071.51.00.50TEMPERATURE (°C)–502.0SU P P L Y C U R R E N T (m A )2.22.62.83.04.03.40507523026 G082.43.63.83.2–2525100125723026fSleep Current vs TemperatureTYPICAL PERFORMANCE CHARACTERISTICSAnalog Input Leakage Current vs TemperatureOffset Error vs TemperatureFull-Scale Error vs Temperature(L TC2302) T A = 25°C, V DD = OV DD = 5V , V REF = 4.096V , f SMPL = 500ksps, unless otherwise noted.TEMPERATURE (°C)–500S L E E P C U R R E N T (μA )13451070507523026 G092896–2525100125TEMPERATURE (°C)–500I N P U T L E A K A G E C U R R E N T (n A )10030040050010007000507523026 G10200800900600–2525100125TEMPERATURE (°C)–50–1.0–1.5–2.0–2.5O F F S E T E R R O R (L S B )–0.50.51.01.52.50507523026 G1102.0–2525100125TEMPERATURE (°C)–50F U L L -S C A L E E R R O R (L S B )1.52523026 G120–1.0–2550–1.5–2.02.01.00.5–0.575100125823026fT YPICAL PERFORMANCE CHARACTERISTICS Integral Nonlinearity vs Output CodeDifferential Nonlinearity vsOutput Code1kHz Sine Wave 8192 Point FFT PlotSNR vs Input FrequencySINAD vs Input FrequencyTHD vs Input FrequencySupply Current vs Sampling FrequencySupply Current vs Temperature(L TC2306) T A = 25°C, V DD = OV DD = 5V , V REF = 4.096V , f SMPL = 500ksps, unless otherwise noted.OUTPUT CODEI N L (L S B)00.250.50409623026 G13–0.25–0.50–1.00102420483072–0.751.000.75–0.751.000.75M A G N I T U D E (d B )FREQUENCY (kHz)150S N R (d B )70758010100100023026 G16656055FREQUENCY (kHz)150S I N A D (d B )70758010100100023026 G17656055FREQUENCY (kHz)1–80T H D (d B )–70–6010100100023026 G18–90–85–75–65–95–100SAMPLING FREQUENCY (ksps)12.0S U P P L Y C U R R E N T (m A )2.53.03.510100100023026 G191.51.00.5TEMPERATURE (°C)–502.0S U P P L Y C U R R E N T (m A )2.22.62.83.04.03.40507523026 G202.43.63.83.2–2525100125923026fSleep Current vs TemperatureTYPICAL PERFORMANCE CHARACTERISTICSAnalog Input Leakage Current vs TemperatureOffset Error vs TemperatureFull-Scale Error vs Temperature(L TC2306) T A = 25°C, V DD = OV DD = 5V , V REF = 4.096V , f SMPL = 500ksps, unless otherwise noted.TEMPERATURE (°C)–500S L E E P C U R R E N T (μA )13451070507523026 G212896–2525100125TEMPERATURE (°C)–500I N P U T L E A K A G E C U R R E N T (n A )10030040050010007000507523026 G22200800900600–2525100125TEMPERATURE (°C)–50O F F S E T E R R O R (L S B )1.52523026 G230–1.0–2550–1.5–2.02.01.00.5–0.575100125TEMPERATURE (°C)–50F U L L -S C A L E E R R O R (L S B )1.52523026 G240–1.0–2550–1.5–2.02.01.00.5–0.575100125P IN FUNCTIONSL TC2302SDO (Pin 1): Three-State Serial Data Out. SDO outputs the data from the previous conversion. SDO is shifted out serially on the falling edge of each SCK pulse. SDO is enabled by a low level on CONVST.CONVST (Pin 2): Conversion Start. A rising edge at CONVST begins a conversion. For best performance, ensure that CONVST returns low within 40ns after the conversion starts or after the conversion ends.V DD (Pin 3): 5V Supply. The range of V DD is 4.75V to 5.25V. Bypass V DD to GND with a 0.1μF ceramic capacitor and a 10μF tantalum capacitor in parallel.IN+, IN– (Pin 4, Pin 5): Positive (IN+) and Negative (IN–) Differential Analog Inputs.V REF (Pin 6): Reference Input. Connect an external refer-ence at V REF . The range of the external reference is 0.1V to V DD. Bypass to GND with a minimum 10μF tantalum capacitor in parallel with a 0.1μF ceramic capacitor. GND (Pin 7): Ground. All GND pins must be connected to a solid ground plane.SDI (Pin 8): Serial Data Input. The SDI serial bit stream confi gures the ADC and is latched on the rising edge of the fi rst 6 SCK pulses.SCK (Pin 9): Serial Data Clock. SCK synchronizes the serial data transfer. The serial data input at SDI is latched on the rising edge of SCK. The serial data output at SDO transitions on the falling edge of SCK.OV DD (Pin 10): Output Driver Supply. Bypass OV DD to GND with a 0.1μF ceramic capacitor close to the pin. The range of OV DD is 2.7V to 5.25V.Exposed Pad (Pin 11): Exposed Pad Ground. Must be soldered directly to ground plane.L TC2306SDO (Pin 1): Three-State Serial Data Out. SDO outputs the data from the previous conversion. SDO is shifted out serially on the falling edge of each SCK pulse. SDO is enabled by a low level on CONVST.CONVST (Pin 2): Conversion Start. A rising edge at CONVST begins a conversion. For best performance, ensure that CONVST returns low within 40ns after the conversion starts or after the conversion ends.V DD (Pin 3): 5V Supply. The range of V DD is 4.75V to 5.25V. Bypass V DD to GND with a 0.1μF ceramic capacitor and a 10μF tantalum capacitor in parallel.CH0, CH1 (Pin 4, Pin 5): Channel 0 and Channel 1 Analog Inputs. CH0, CH1 can be confi gured as single-ended or differential input channels. See the Analog Input Multi-plexer section.V REF (Pin 6): Reference Input. Connect an external refer-ence at V REF .The range of the external reference is 0.1V to V DD. Bypass to GND with a minimum 10μF tantalum capacitor in parallel with a 0.1μF ceramic capacitor. GND (Pin 7): Ground. All GND pins must be connected to a solid ground plane.SDI (Pin 8): Serial Data Input. The SDI serial bit stream confi gures the ADC and is latched on the rising edge of the fi rst 6 SCK pulses.SCK (Pin 9): Serial Data Clock. SCK synchronizes the serial data transfer. The serial data input at SDI is latched on the rising edge of SCK. The serial data output at SDO transitions on the falling edge of SCK.OV DD (Pin 10): Output Driver Supply. Bypass OV DD to OGND with a 0.1μF ceramic capacitor close to the pin. The range of OV DD is 2.7V to 5.5V.Exposed Pad (Pin 11): Exposed Pad Ground. Must be soldered directly to ground plane.1023026f1123026fB LOCK DIAGRAM TEST CIRCUITSTIMING DIAGRAMSVoltage Waveforms for SDO Delay Times, t dDO and t hDOVoltage Waveforms for t disLoad Circuit for t dis Waveform 1Load Circuit for t dis Waveform 2, t enSDISDO SCK CONVSTCH0 (IN +CH1 (IN –REFV OVVSCKSDOOH OLSDOWAVEFORM 1(SEE NOTE 1)SDOWAVEFORM 2(SEE NOTE 2)CONVST NOTE 1: WAVEFORM 1 IS FOR AN OUTPUT WITH INTERNAL CONDITIONS SUCH THAT THE OUTPUT IS HIGH UNLESS DISABLED BY THE OUTPUT CONTROL NOTE 2: WAVEFORM 2 IS FOR AN OUTPUT WITH INTERNAL CONDITIONS SUCH THAT THE OUTPUT IS LOW UNLESS DISABLED BY THE OUTPUT CONTROL23026 TD021223026fTIMING DIAGRAMSt WLCLK (SCK Low Time)t WHCLK (SCK High Time)t HD (Hold Time SDI After SCK ↑)t SUDI (Setup Time SDI Stable Before SCK ↑)Voltage Waveforms for t enVoltage Waveforms for SDO Rise and Fall Times t r , t fA PPLICATIONS INFORMATIONSCKSDICONVSTSDOOH OLOverviewThe L TC2302/L TC2306 are low noise, 500ksps, 1-/2-chan-nel, 12-bit successive approximation register (SAR) A/D converters. The L TC2306 includes a 2-channel analog input multiplexer (MUX) while the L TC2302 includes an input MUX that allows the polarity of the differential input to be selected. Both ADCs include an SPI-compatible se-rial port for easy data transfers and can operate in either unipolar or bipolar mode. Unipolar mode should be used for single-ended operation with the L TC2306, since single-ended input signals are always referenced to GND. The L TC2302/L TC2306 can be put into a power-down sleep mode during idle periods to save power .Conversions are initiated by a rising edge on the CONVST input. Once a conversion cycle has begun, it cannot be restarted. Between conversions, a 6-bit input word (D IN ) at the SDI input confi gures the MUX and programs vari-ous modes of operation. As the D IN bits are shifted in, data from the previous conversion is shifted out on SDO. After the 6 bits of the D IN word have been shifted in, the ADC begins acquiring the analog input in preparation for the next conversion as the rest of the data is shifted out.The acquire phase requires a minimum time of 240ns for the sample-and-hold capacitors to acquire the analog input signal.During the conversion, the internal 12-bit capacitive charge-redistribution DAC output is sequenced through a successive approximation algorithm by the SAR starting from the most signifi cant bit (MSB) to the least signifi cant bit (LSB). The sampled input is successively compared with binary weighted charges supplied by the capacitive DAC using a differential comparator . At the end of a conver-sion, the DAC output balances the analog input. The SAR contents (a 12-bit data word) that represent the sampled analog input are loaded into 12 output latches that allow the data to be shifted out.Programming the L TC2306 and L TC2302The software compatible L TC2302/L TC2306/L TC2308 fam-ily features a 6-bit D IN word to program various modes of operation. Don’t care bits (X) are ignored. The SDI data bits are loaded on the rising edge of SCK, with the S/D bit loaded on the fi rst rising edge (see Figure 6 in the Timing1323026fA PPLICATIONS INFORMATION Figure 1a. Example MUX Confi gurationsFigure 1b. Changing the MUX Assignment “On the Fly”and Control section). The input data word for the L TC2306 is defi ned as follows:S/D O/SXXUNIXS/D = SINGLE-ENDED/DIFFERENTIAL BIT O/S = ODD/SIGN BIT UNI = UNIPOLAR/BIPOLAR BIT X = DON’ T CAREFor the L TC2302, the input data word is defi ned as:XO/SXXUNIXAnalog Input MultiplexerThe analog input MUX is programmed by the S/D and O/S bits of the D IN word for the L TC2306 and the O/S bit of the D IN word for the L TC2302. Table 1 and Table 2 list MUX confi gurations for all combinations of the confi guration bits. Figure 1a shows several possible MUX confi gurations and Figure 1b shows how the MUX can be reconfi gured from one conversion to the next.Driving the Analog InputsThe analog inputs of the L TC2302/L TC2306 are easy to drive. Each of the analog inputs of the L TC2306 (CH 0 and CH1) can be used as a single-ended input relative to GND or as a differential pair . The analog inputs of theL TC2302 (IN +, IN –) are always configured as a differential pair . Regardless of the MUX confi guration, the “+” and “–” inputs are sampled at the same instant. Any unwanted signal that is common to both inputs will be reduced by the common mode rejection of the sample-and-hold cir-cuit. The inputs draw only one small current spike while2 Single-Ended1 Differential+(–)–(+) 1 Differential+(–)–(+)2nd Conversion1st Conversion+–S/D 0011O/S 0101CH0+–+CH1–++WITH RESPECT TO GNDNOTE: UNIPOLAR MODE SHOULD BE USEDFOR SINGLE-ENDED OPERATION, SINCE INPUT SIGNALS ARE ALWAYS REFERENCED TO GNDTable 1. Channel Configurationfor the L TC2306O/S 01IN ++–IN ––+Table 2. Channel Configuration for the L TC23021423026fA PPLICATIONS INFORMATION Figure 2b. Analog Input Equivalent Circuit for Large Filter CapacitancesFigure 2a. Analog Input Equivalent Circuitcharging the sample-and-hold capacitors during the acquire mode. In conversion mode, the analog inputs draw only a small leakage current. If the source impedance of the driving circuit is low, the ADC inputs can be driven directly. Otherwise, more acquisition time should be allowed for a source with higher impedance.ReferenceA low noise, stable reference is required to ensure full performance. The L T ®1790 and L T6660 are adequate for most applications. The L T6660 is available in 2.5V , 3V , 3.3V and 5V versions, and the L T1790 is available in 1.25V , 2.048V , 2.5V , 3V , 3.3V , 4.096V and 5V versions. The exceptionally low input noise allows the input range to be optimized for the application by changing the reference voltage. The V REF input must be decoupled with a 10μF capacitor in parallel with a 0.1μF capacitor , so verify that the device providing the reference voltage is stable with capacitive loads.If the voltage reference is 5V and can supply 5mA, it can be used for both V REF and V DD . V DD must be connected to a clean analog supply, and a quiet 5V reference voltage makes a convenient supply for this purpose.Input FilteringThe noise and distortion of the input amplifi er and other circuitry must be considered since they will add to the ADC noise and distortion. Therefore, noisy input circuitryshould be fi ltered prior to the analog inputs to minimize noise. A simple 1-pole RC fi lter is suffi cient for many applications.The analog inputs of the L TC2302/L TC2306 can be modeled as a 55pF capacitor (C IN ) in series with a 100Ω resistor (R ON ) as shown in Figure 2a. C IN gets switched to the selected input once during each conversion. Large fi lter RC time constants will slow the settling of the inputs. It is important that the overall RC time constants be short enough to allow the analog inputs to completely settle to 12-bit resolution within the acquisition time (t ACQ ) if DC accuracy is important.When using a fi lter with a large C FIL TER value (e.g., 1μF), the inputs do not completely settle and the capacitive input switching currents are averaged into a net DC current (I DC ). In this case, the analog input can be modeled by an equivalent resistance (R EQ = 1/(f SMPL • C IN )) in series with an ideal voltage source (V REF /2) as shown in Figure 2b. The magnitude of the DC current is then approximately I DC = (V IN – V REF /2)/R EQ , which is roughly proportional to V IN . To prevent large DC drops across the resistorR FIL TER , a filter with a small resistor and large capacitor should be chosen. When running at the minimum cycle time of 2μs, the input current equals 106μA at V IN = 5V , which amounts to a full-scale error of 0.5LSB when using a fi lter resistor (R FIL TER ) of 4.7Ω. Applications requiring lower sample rates can tolerate a larger fi lter resistor for the same amount of full-scale error .V IN23026 F02aV IN23026 F02bA PPLICATIONS INFORMATIONFigure 3a. Optional RC Input Filtering for Single-Ended Input Figure 3b. Optional RC Input Filtering for Differential Inputs Figure 4. 1kHz Sine Wave 8192 Point FFT Plot (L TC2306)Figures 3a and 3b show respective examples of input fi ltering for single-ended and differential inputs. For the single-ended case in Figure 3a, a 50Ω source resistor and a 2000pF capacitor to ground on the input will limit the input bandwidth to 1.6MHz. High quality capacitors and resistors should be used in the RC fi lter since these components can add distortion. NPO and silver mica type dielectric capacitors have excellent linearity. Carbon surface mount resistors can generate distortion from self heating and from damage that may occur during soldering. Metal fi lm surface mount resistors are much less susceptible to both problems.Dynamic PerformanceFFT (fast fourier transform) test techniques are used to test the ADC’s frequency response, distortion and noise at the rated throughput. By applying a low distortion sine wave and analyzing the digital output using an FFT algorithm, the ADC’s spectral content can be examined for frequencies outside the fundamental.Signal-to-Noise and Distortion Ratio (SINAD)The signal-to-noise and distortion ratio (SINAD) is the ratio between the RMS amplitude of the fundamental input frequency to the RMS amplitude of all other frequency components at the A/D output. The output is band-limited to frequencies from above DC and below half the sampling frequency. Figure 4 shows a typical SINAD of 72.8dB with a 500kHz sampling rate and a 1kHz input. A SNR of 73.2dB can be achieved with the L TC2302/L TC2306.Total Harmonic Distortion (THD)Total Harmonic Distortion (THD) is the ratio of the RMS sum of all harmonics of the input signal to the fundamental itself. The out-of-band harmonics alias into the frequency band between DC and half the sampling frequency(f SMPL/2). THD is expressed as:THDV V V VVN=+++2022324221log...where V1 is the RMS amplitude of the fundamental fre-quency and V2 through V N are the amplitudes of the second through Nth harmonics.40206080002050307090103040MAGNITUDE(dB)SNR = 73.2dBSINAD = 72.8dBTHD = –88.7dB1523026f。

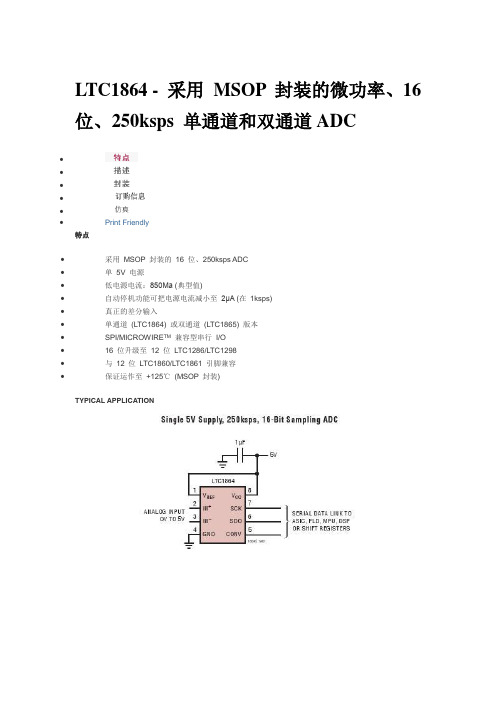

LTC1864

LTC1864 - 采用MSOP 封装的微功率、16 位、250ksps 单通道和双通道ADC••••••Print Friendly特点•采用MSOP 封装的16 位、250ksps ADC•单5V 电源•低电源电流:850Μa (典型值)•自动停机功能可把电源电流减小至2μA (在1ksps)•真正的差分输入•单通道(LTC1864) 或双通道(LTC1865) 版本•SPI/MICROWIRE TM兼容型串行I/O•16 位升级至12 位LTC1286/LTC1298•与12 位LTC1860/LTC1861 引脚兼容•保证运作至+125℃(MSOP 封装)TYPICAL APPLICATIONBACK TO TOP描述LTC®1864/LTC1865 是采用MSOP 和SO-8 封装的16 位A/D 转换器,采用单5V工作电源。

在250ksps 采样速率条件下,电源电流仅为850μA。

在较低的速度下,电源电流将减小,原因是LTC1864/LTC1865 在转换操作之间自动断电。

这些16 位开关电容器逐次逼近型ADC 包括采样及保持电路。

LTC1864 具有一个差分模拟输入和一个可调基准引脚。

LTC1865 提供了一个可利用软件来选择的双通道MUX 和一个可调基准引脚(在MSOP 封装版本上)。

三线式串行I/O、小外形MSOP 或SO-8 封装、以及极高的采样速率与功率之比使得这些ADC 非常适合于紧凑、低功率、高速系统。

这些ADC 可在比例式应用中使用,或与外部基准一起使用。

高阻抗模拟输入以及可在缩减的电压范围内(低至1V 全标度) 运作的能力使得它们在许多应用中可与信号源直接相连,从而免除了增设外部增益级的需要。

BACK TO TOP封装SO-8, MSOP-8BACK TO TOP订购信息•以PBF 结尾的器件型号表示这些是无铅型器件。

如需了解有关含铅涂层器件的信息,请与凌力尔特公司联系。

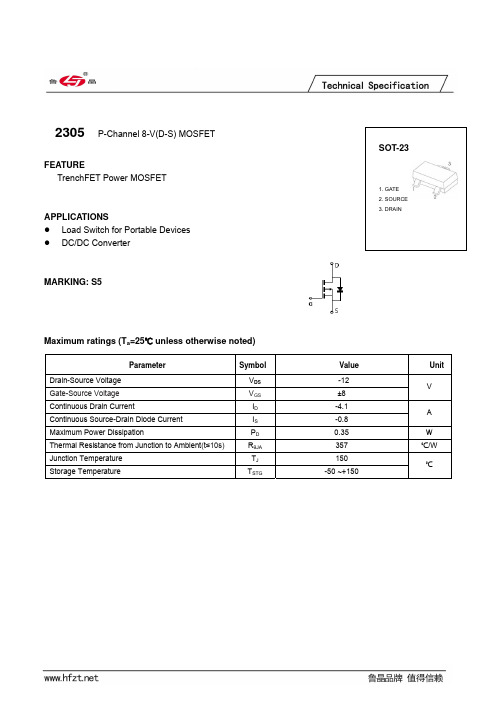

MC2305ADS规格书

o

Symbol

VGS(th) IGSS IDSS ID(on)

A

Test Conditions

VDS = VGS, ID = -250 uA

VDS = 0 V, VGS = ±8 V

Limits Unit Min Typ Max

-0.7

±100

nA uA A

VDS = -16 V, VGS = 0 V

A

rDS(on) g fs VSD Qg Qgs Qgd Ciss Coss Crss t d(on) tr td(off) tf

VDS = -5 V, VGS = -4.5 V VGS = -4.5 V, ID = -3.6 A VGS = -2.5 V, ID = -3.1 A VGS = -1.8 V, ID = -2.7 A VDS = -5 V, ID = -1.25 A IS = -0.46 A, VGS = 0 V

VDS = -16 V, VGS = 0 V, T J = 55oC

-1 -10 -10 52 72 120 12 -0.60 12.0 2.0 2.0

1312 130 106

Drain-Source On-Resistance Forward Tranconductance Diode Forward Voltage

2

Freescale

Si 2305ADS/ MC2305ADS

Typical Electrical Characteristics

Figure 1. On-Region Characteristics

Figure 2. On-Resistance Variation with Drain Current and Gate Voltage

笔记本电源管理芯片

笔记本电源管理芯片,i/o(2009-11-06 22:23:06)转载标签:杂谈笔记本电源管理芯片大全:ADP3421/ADP3410/ADP3205/ADP3180/ADP3806/ADP3203/ADP3020电源管理芯片大全RT9237/RT9237CS/RT9231/RT9241/RT9231A/RT9241A/RT9241B电源管理芯片大全RT9221/RT9600/RT9602/RT9603/RT9222/RT9224/RT9224A/RT9223电源管理芯片大全RT9227A/RT9228/RT9238/RT9248A/RT9173/RT9202/RC5051M 电源管理芯片大全5090MTC/RC5093MTC/5098MTC/SC1470/SC1205/SC1214TS电源管理芯片大全SC1155CSW/SC1154CSW/SC1153CSW/SC1189SW//SC1185ACSW电源管理芯片大全SC1402ISS/SC2422ACS//SC1164CSW/SC1150/ISL6524CB/RC5053M电源管理芯片大全/ISL6522CB/ISL6556BCB/ISL6566CRZ/4500M/HIP6501ACB电源管理芯片大全HIP6521CB/HIP6502/HIP6016CB/HIP6017CB/HIP6018BCB/HIP6019BCB电源管理芯片大全HIP6020CB/HIP6021CB/HIP6601/HIP6602BCB/HIP6603CB/HIP6004ECB电源管理芯片大全HIP6620BAB/HIP6301CB/HIP6520/HIP6302CB/HIP6303CS/SC1163电源管理芯片大全SC1159/SC1486/ST75185C/SC2434SW/SC1480/SC1403/SC1404 电源管理芯片大全SC1485/SC1486/SC1474/SC1476/SC1211/SC451/SC1470电源管理芯片大全IRU3013/IRU3004CW/IRU3055CQTR/IRU1150CM/MS-5/MS-7/5322电源管理芯片大全CS5301/L6916D/L6917CB/LM2637M/LM2638M/ICE2AS01/KA7500B笔记本电源管理芯片ADP3421/ADP3410/ADP3205/ADP3180/ADP3806/ADP3203/ADP3020笔记本电源管理芯片ADP3170/ADP3188/ADP3181/ADP3166/ADP3163/ADP3165/ADP3168笔记本电源管理芯片ADP3169/ADP3415/ADP3416/ADP3417/ADP3418/ADP3155/ADP3422笔记本电源管理芯片ADP3207/MAX3243/MAX1902/MAX1999/MAX785/MAX786/MAX1717笔记本电源管理芯片MAX1604/MAX1987/MAX1887/ISL6223/ISL6565/ISL6225/ISL6218笔记本电源管理芯片ISL6566/ISL6568/ISL6563笔记本电源管理芯片MAX1904(SSOP)/MAX1904(BGA的)/MAX1634/MAX1710/MAX1711笔记本电源管理芯片MAX1904/MAX1714/MAX1715/MAX1718/MAX1772/MAX1773/MAX1901笔记本电源管理芯片MAX1908/MAX1632/MAX1545/MAX1535/MAX1631/MAX1909/MAX1977笔记本电源管理芯片MAX1504/MAX1845/MAX1844/MAX1980/MAX1532/MAX1907/MAX1617笔记本电源管理芯片MAX8734/MAX8743/MAX8724/MAX1644/MAX1645/ISL6207/ISL6559CB笔记本电源管理芯片ISL6217/ISL6264/ISL6227/ISL6255/SC1485/SC1404笔记本电源管理芯片LT3728LX/LTC1709/LTC1439/LTC3735/LTC1628/LTC1707/LTC1736笔记本电源管理芯片MB3887/MB3878/LTC1778/LTC1511/LTC1709/LTC1439/LM8463笔记本电源管理芯片LM2729/LM2641/VT8235/LTC3728/SC1476/SC1474/SC1404/SC451笔记本电源管理芯片SC1403/SC1470/SC1486/TPS51120/TPS51020/PU2211A/VT6105笔记本电源管理芯片VT8235/VT1612/VT8237/VT8233/VT8235(BGA的)/LTC3707/LTC3716笔记本IO芯片大全PC87591S(VPCQ01)/PC 87591L(VPC01)/PC 97317IBW/PC 87393 VGJ笔记本IO芯片大全TB62501F/TB62506F/TB6808F/KB910QF/KB910QB4/KB910LQF/KB910LQFA1笔记本IO芯片大全KB3910QB0/KB910SFC1/KB3910SF/PC87591E-VLB/IT8510E/PS5130笔记本IO芯片大全PC87591E (-VPCI01),(VPCQ01)/PC 97551-VPC/PC87570-ICC/VPC笔记本IO芯片大全PC87391VGJ/TB6807F/W83L950D/LPC47N249-AQQ/PCI4510/PC8394T笔记本IO芯片大全PC87392/PC87541L/PC87541V/LPC47N253-AQQ/PC87591E-VLB笔记本IO芯片大全LPC47N250-SD/LPC47N252-SG/LPC47N254-AQQ。

触摸屏驱动芯片

觸摸屏驅動芯片列表

1、2046 是4线式触摸屏控制器ADS7846的替代产品,支持1.5V~5.25V低压I/O界面,与现有的ADS7846 可实现100%的PIN to PIN 替换,使用相同的插座产品特性:

2.2V TO 5.25V 工作电压范围

1.5V TO 5.25V 数字输入输出

内置2.5V 参考电压

直接电池电压检测功能(0V to 6V)

片上温度检测功能

触摸压力检测功能

QSPITM 和SPITM 3-WIRE 界面

自动掉电保护功能

QFN-16封装

可应用于:

手机

PDA 个人数字助理

便携式设备

自动销售终端

寻呼机

触摸屏监控器

蜂窝电话

2、TSC2003是TI公司生产的采用TSSOP一16封装的四线电阻式触摸屏控制芯片,集成了多个功能模块,具有测量电量、片上温度和触摸压力等功能,通过I2C总线与单片机连接。

TSC2003是一款基于命令控制的触摸屏检测器件,通过I2C总线发送控制命令来控制芯片采集X轴、Y轴和Z轴的压力等相关量。

3、触摸屏驱动IC UH7843可完全替换TCS2046 AR7643及AKM4812 特点:4 wire Touch Panel interface,12-bit analog to digital converter up to 125KHZ conversion,SSOP-16 QFN-16以及客户要求的封装

PIN TO PIN 。

4、。

ltc4359ims原理

ltc4359ims原理LTC4359IMS原理解析LTC4359IMS是一款电源优先级控制器,可用于多种电源系统中。

它提供了一种简单而有效的方式,以确保系统在多个电源供电情况下的稳定和可靠运行。

LTC4359IMS的工作原理是基于电源优先级的控制。

当系统连接到多个电源时,LTC4359IMS会根据预设的优先级规则选择供电源。

它通过比较各个电源的电压来确定最高优先级的电源,并将其连接到系统。

当最高优先级的电源电压低于设定的阈值时,LTC4359IMS会自动切换到下一个优先级更高的电源。

这种电源优先级控制机制确保了系统在供电源故障或电压波动的情况下的稳定工作。

LTC4359IMS具有多种保护功能,以确保系统的安全运行。

它具有过电流保护和过温保护功能,可以在电流超过设定值或温度过高时自动断开电源连接。

此外,它还具有反向电流保护功能,可以防止电源之间的电流逆流。

这些保护功能能够有效地保护系统免受电源故障和其他意外情况的影响。

除了电源优先级控制和保护功能外,LTC4359IMS还具有一些额外的功能,以提高系统的性能和灵活性。

它具有可调的电压阈值和延迟时间,可以根据实际需求进行设置。

此外,它还具有电流限制功能,可以限制系统的最大电流,以防止电源过载。

总的来说,LTC4359IMS是一款功能强大的电源优先级控制器,适用于各种电源系统。

它通过电压比较和优先级切换的方式,确保系统在多个电源供电情况下的稳定和可靠运行。

它还具有多种保护功能和额外的功能,以提高系统的安全性和性能。

LTC4359IMS的出现为多电源系统的设计和应用提供了一种简单而有效的解决方案。

2305 MOS管

LTC2612IMS8中文资料

ELECTRICAL CHARACTERISTICS

CONDITIONS

MIN 12 12

LTC2622 TYP MAX

MIN 14 14

LTC2612 TYP MAX

MIN 16 16

LTC2602 TYP MAX

UNITS Bits Bits

± 0.5 ± 0.75 ±4 ±3 0.1 0.2 0.2 0.4 1 ±1 ±5

元器件交易网

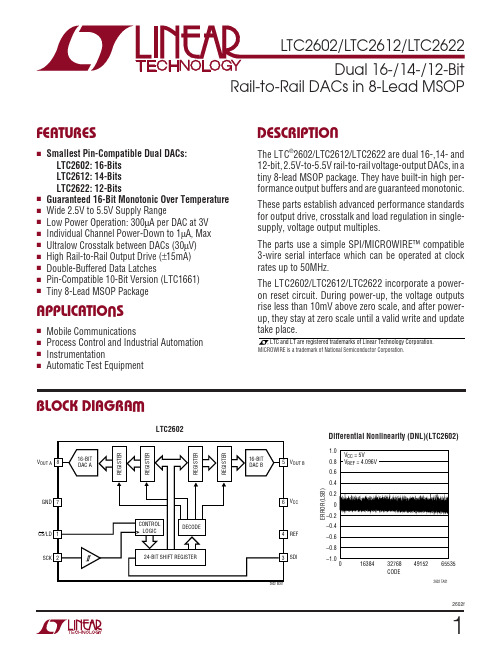

LTC2602/LTC2612/LTC2622 Dual 16-/14-/12-Bit Rail-to-Rail DACs in 8-Lead MSOP

FEATURES

s

DESCRIPTIO

s s s s s s s s s

U APPLICATIO S

s s s s

The q denotes specifications which apply over the full operating temperature range, otherwise specifications are at TA = 25°C. VCC = 2.5V to 5.5V, VREF ≤ VCC, VOUT unloaded, unless otherwise noted.

VCC = 5V, VREF = 4.096V Code = 0 q VCC = 5V, VREF = 4.096V, (Note 7) q

± 0.1 ±0.7 ±3

± 0.1 ±0.7 ±3

2

U

LSB LSB

2602f

W

U

U

W WБайду номын сангаас

W

元器件交易网

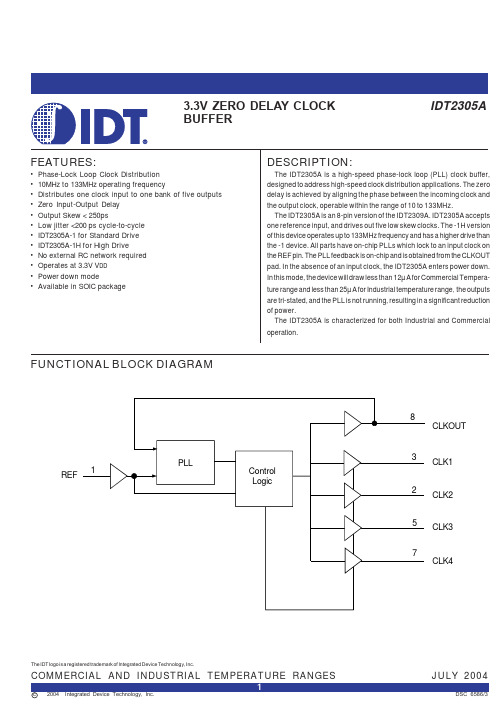

IDT2305A-1DCGI资料

—

50

µA

—

100

µA

—

0.4

V

2.4

—

V

—

12

µA

—

32

mA

SWITCHING CHARACTERISTICS (2305A-1) - COMMERCIAL(1,2)

Symbol

Parameter

Conditions

Min.

t1

Output Frequency

10pF Load

10

30pF Load

CLKOUT CLK4 VDD CLK3

COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES

ABSOLUTE MAXIMUM RATINGS(1)

Symbol VDD VI (2) VI

IIK (VI < 0) IO (VO = 0 to VDD) VDD or GND TA = 55°C (in still air)(3) TSTG Operating Temperature Operating Temperature

All outputs equally loaded

—

t6

Delay, REF Rising Edge to CLKOUT Rising Edge Measured at VDD/2

—

t7

Device-to-Device Skew

Measured at VDD/2 on the CLKOUT pins of devices

COMMERCIAL AND INDUSTRIAL

c 2004 Integrated Device Technology, Inc.

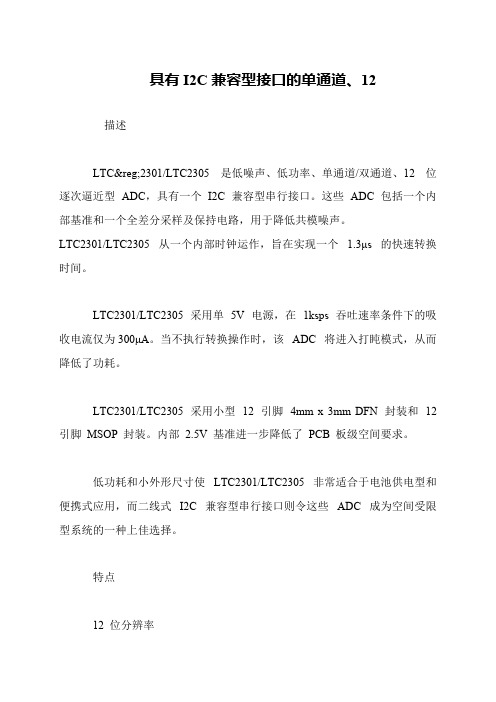

具有I2C兼容型接口的单通道、12

具有I2C兼容型接口的单通道、12

描述

LTC®2301/LTC2305 是低噪声、低功率、单通道/双通道、12 位逐次逼近型ADC,具有一个I2C 兼容型串行接口。

这些ADC 包括一个内部基准和一个全差分采样及保持电路,用于降低共模噪声。

LTC2301/LTC2305 从一个内部时钟运作,旨在实现一个 1.3μs的快速转换时间。

LTC2301/LTC2305 采用单5V 电源,在1ksps 吞吐速率条件下的吸收电流仅为300μA。

当不执行转换操作时,该ADC 将进入打盹模式,从而降低了功耗。

LTC2301/LTC2305 采用小型12 引脚4mm x 3mm DFN 封装和12 引脚MSOP 封装。

内部 2.5V 基准进一步降低了PCB 板级空间要求。

低功耗和小外形尺寸使LTC2301/LTC2305 非常适合于电池供电型和便携式应用,而二线式I2C 兼容型串行接口则令这些ADC 成为空间受限型系统的一种上佳选择。

特点

12 位分辨率。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。