东南大学半导体集成电路2002考研真题

东南大学半导体物理考研复习系列试题(A卷)

共 9 页

第 5 页

(luobin 考研复习卷)

产生率 2.(15分) 如果稳定光照射在一块均匀掺杂的 n 型半导体中均匀产生非平衡载流子, 14 3 1 2 为 Gop 3 10 cm s ,且无外场作用,空穴迁移率 p 430cm / V s , p 5us , 半导体的长度远远大于空穴的扩散长度,如图所示。假设样品左侧存在表面复合,表面复 合率为 U s 7.5 10 cm s ,比例系数(表面复合速度)为 s 。

共 9 页 第 1 页 (luobin 考研复习卷)

位于导带底下方 0.026eV 处,半导体的状态为 __________ (填“简并” , “弱简并” 或“非简并” ) ,判断的依据为 __________ 。 8. 强电场效应会使半导体器件的载流子速度达到饱和,还可能使载流子成为热载流子, 影响器件性能。半导体器件的热载流子由于具备高能量,常常会导致载流子 __________ ; 热 载 流 子 可 与 晶 格 发 生 碰 撞 电 离 , 利 用 这 一 原 理 可 以 制 备 __________ 器件。 9. 早期锗硅等半导体材料常利用测其电阻率的办法来估计纯度,室温下较纯 Ge 样品的 电子迁移率 n 3900cm2 / V s ,锗原子密度 4.42 1022 cm3 ,若测得室温下电阻 率为 10 cm ,则利用此方法测得 n 型锗的掺杂浓度为 __________ ,这种测量方法 来估计纯度的局限性是 __________ 。 10. 金属的费米能级位于导带之上, n 型半导体与金属接触形成整流接触,那么半导体与 金属的功函数哪个大? __________ 。由于半导体与金属之间存在整体载流子水平差 异,所以会产生载流子(电子)的扩散,形成内建电场;内建电场几乎全部建立在半 导体一侧的原因是 __________ 。具有整流接触的金-半接触称为肖特基接触,肖特基 结相比普通 pn 结, 在高频高速器件具有更重要的作用, 其原因在于肖特基接触不存在 电荷存储现象。肖特基接触不存在电荷存储现象的原因是 __________ 。制造 pn 结 可选用的技术主要有合金、扩散、外延生长、 __________ 等,用掺杂制作 pn 结克 服了金-半接触的一大缺点: __________ 。 11. 下图是 p 型半导体的能带图。三图中哪些图表明半导体存在电流? __________ 。图

《半导体集成电路》考试题目及参考答案

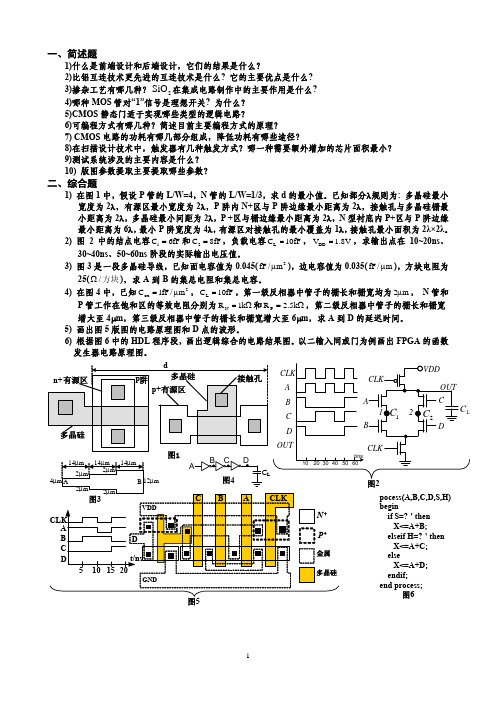

? ?第一部分 考试试题第 0 章 绪论1.什么叫半导体集成电路?2.按照半导体集成电路的集成度来分,分为哪些类型,请同时写出它们对应的英文缩写?3.按照器件类型分,半导体集成电路分为哪几类?4.按电路功能或信号类型分,半导体集成电路分为哪几类5.什么是特征尺寸?它对集成电路工艺有何影响6.名词解释:集成度、wafer size 、die size 、摩尔定律?第 1 章 集成电路的基本制造工艺1.四层三结的结构的双极型晶体管中隐埋层的作用?2.在制作晶体管的时候,衬底材料电阻率的选取对器件有何影响?。

3.简单叙述一下 pn 结隔离的 NPN 晶体管的光刻步骤?4.简述硅栅p 阱 CMOS 的光刻步骤?5.以 p 阱 CMOS 工艺为基础的BiCMOS 的有哪些不足?6.以 N 阱 CMOS 工艺为基础的BiCMOS 的有哪些优缺点?并请提出改进方法。

7. 请画出 NPN 晶体管的版图,并且标注各层掺杂区域类型。

8.请画出 C MOS 反相器的版图,并标注各层掺杂类型和输入输出端子。

第 2 章 集成电路中的晶体管及其寄生效应1.简述集成双极晶体管的有源寄生效应在其各工作区能否忽略?。

2. 什么是集成双极晶体管的无源寄生效应?3. 什么是 MOS 晶体管的有源寄生效应?4. 什么是 MOS 晶体管的闩锁效应,其对晶体管有什么影响?5. 消除“Latch-up ”效应的方法?6.如何解决 MOS 器件的场区寄生 MOSFET 效应?7. 如何解决 MOS 器件中的寄生双极晶体管效应?第 3 章 集成电路中的无源元件1.双极性集成电路中最常用的电阻器和 MOS 集成电路中常用的电阻都有哪些?2.集成电路中常用的电容有哪些。

3. 为什么基区薄层电阻需要修正。

4. 为什么新的工艺中要用铜布线取代铝布线。

5. 运用基区扩散电阻,设计一个方块电阻 200 欧,阻值为 1K 的电阻,已知耗散功率为 20W /c ㎡,该电阻上的压降为 5V,设计此电阻。

东南大学考研真题管理学原理2002答案

东南大学2002年攻读硕士学位研究生入学考试试卷试题编号:449试题科目:管理原理一、简答题(共三小题,每题8分,共24分)1.简述梅奥对人际关系学说的贡献。

2.简述经营决策中外部环境的影响。

3.简述扁平式组织结构的特点。

二、论述题(共三小题,每题20分,共60分)1.试在多种激励理论中选择介绍两种理论的主要内容,并举一例加以进一步说明。

2.试述韦伯的科层组织理论,并分析它的现实意义。

3.试述组织发展的阶段理论,并举一例加以说明。

三、案例分析(16分)2000万销售额为何完不成?先锋通讯信息公司是一个以开发和生产通信交换机辅助设备为主的高科技公司,它的前身是一个邮电器材制造企业,由一批信息学院的教师承包。

这批科技人员承包之始带去了一些科技成果,其中的一个已较成熟,生产后投放市场销路很好,第一年即扭亏为盈。

教授出生的总经理意识到只有不断的保持产品开发的领先性,才能使得企业持续发展。

因此,他在年初的企业年度计划会上,按照目标管理的方法,将当年的经营指标—100万元利润做了分解:按销售利润率5%计算,销售部要完成2000万销售额,制造部要完成500套设备的制造任务,开发部负责开发三个新产品,财务部要将资金利润率提高2个百分点、成本下降2%,人事部对所有员工进行一次培训(培训费用掌握在20万元以内)。

在年度计划会上,销售部经理首先发难,认为比去年增加50%的2000万销售指标无法完成,总经理在解释了他所采用的目标管理新方法后,棉里藏针地说:如果你觉得实在完不成任务可以辞职。

在总经理讲出这样的话以后,年度目标计划在没有反对意见的情况下得以通过。

开过年度计划会后,总经理就一头扎到中试车间带领一批人从事新产品开发。

到年底,中试车间捷报频传,但总经理却吃惊地发现,公司的销售和利润指标都未能完成。

总经理大惑不解,甚至怀疑当初和他一起下海的伙伴们是否有了异心。

你认为总经理现在应该怎么办呢?。

半导体集成电路复习题及答案

第8章动态逻辑电路填空题对于一般的动态逻辑电路,逻辑部分由输出低电平的网组成,输出信号与电源之间插入了栅控制1、极为时钟信号的 ,逻辑网与地之间插入了栅控制极为时钟信号的。

【答案:NMOS, PMOS, NOMS】对于一个级联的多米诺逻辑电路,在评估阶段:对PDN网只允许有跳变,对 PUN网只允许有跳变,2、PDN与PDN相连或PUN与PUN相连时中间应接入。

【答案:】解答题从逻辑功能,电路规模,速度3方面分析下面2电路的相同点和不同点。

从而说明CMOS动态组合逻辑1、电路的特点。

【答案:】图A是CMOS静态逻辑电路。

图B是CMOS动态逻辑电路。

2电路完成的均是NAND的逻辑功能。

图B的逻辑部分电路使用了2个MOS管,图A使用了4个MOS管,由此可以看出动态组合逻辑电路的规模为静态电路的一半。

图B的逻辑功能部分全部使用NMOS管,图A即使用NMOS也使用PMOS,由于NMOS的速度高于PMOS,说明动态组合逻辑电路的速度高于静态电路。

2、分析下面的电路,指出它完成的逻辑功能,说明它和一般动态组合逻辑电路的不同,说明其特点。

【答案:】该电路可以完成OUT=AB的与逻辑。

与一般动态组合逻辑电路相比,它增加了一个MOS管M kp,这个MOS 管起到了电荷保持电路的作用,解决了一般动态组合逻辑电路存在的电荷泄漏的问题。

3、分析下列电路的工作原理,画出输出端OUT的波形。

【答案:】答案:4、结合下面电路,说明动态组合逻辑电路的工作原理。

【答案:】动态组合逻辑电路由输出信号与电源之间插入的时钟信号PMOS,NMOS逻辑网和逻辑网与地之间插入的时钟信号NMOS组成。

当时钟信号为低电平时,PMOS导通,OUT被拉置高电平。

此时电路处于预充电阶段。

当时钟信号为低电平时,PMOS截至,电路与V DD的直接通路被切断。

这时NOMS导通,当逻辑网处于特定逻辑时,电路输出OUT被接到地,输出低电平。

否则,输出OUT仍保持原状态高电平不变。

东南大学考研真题—东南大学2002年管理学

东南大学2002年攻读硕士学位研究生入学考试试题一、概念解释(共30分,每题5分)1.权力2.概念技能3.满意因素4.具体环境5.态度6.反馈控制二、论述题(共30分,每题15分)1.有机型组织的特点,应用条件与管理重点。

2.管理者的作用类型及其影响因素。

三、分析题(40分)我国有句古话:“失败乃成功之母”,但现在有管理学家指出,对于现代社会的企业来说,情况可能正相反,企业运行中很可能会出现“成功是失败之母”,试解释这句话的管理学含义,分析积极意义存在的前提条件以及这句话对现代企业管理所产生的影响。

参考答案东南大学2002年攻读硕士学位研究生入学考试试题一、概念解释(共30分,每题5分)1.权力(9.9邓力文修改整理)答:权力指影响别人行为的能力,这是对权力最简单的理解。

对管理过程和职能的领导而言,一般认为,这种能力包括三个方面:①领导者个人的专长权,即产生于领导者所拥有的专门知识或特殊技能;②领导者的个人影响权,即来自于追随者认可的个人经历、性格或榜样产生的力量;③领导者担任的管理岗位所赋予的管理制度权力。

管理意义上的领导,一般是指上述的第三种权力。

所以,领导就是关于如何有效行使管理制度权力的过程。

显然,上述三种权力中,第一和第二种权力的主观性较强。

如果领导的权力发挥主要来自这两种权力,无论是组织的稳定性还是组织成员的职业生涯,都将受到不稳定因素的冲击。

因此,在管理中,权力的配置至关重要。

2.概念技能3.满意因素答:满意因素,即激励因素。

美国心理学家赫茨伯格将企业中影响人的工作的因素分为满意因素和不满意因素两大类。

满意因素即可以使人得到很大的激励和对工作的满足的因素。

赫茨伯格归纳出六个满意因素:(1)工作上的成就感;(2)工作上得到承认和赞赏;(3)工作本身的挑战性和兴趣;(4)工作职务上的责任感;(5)工作的发展前途;(6)个人成长和晋升的机会。

满意因素都是属于工作本身方面的因素,是适合个人成长的因素,满意因素得到满足,就能产生巨大的满足感和激励作用。

《半导体集成电路》考试题目及参考答案(DOC)

《半导体集成电路》考试题目及参考答案(DOC)1.双极性集成电路中最常用的电阻器和MOS集成电路中常用的电阻都有哪些?2.集成电路中常用的电容有哪些。

3. 为什么基区薄层电阻需要修正。

4. 为什么新的工艺中要用铜布线取代铝布线。

5. 运用基区扩散电阻,设计一个方块电阻200欧,阻值为1K的电阻,已知耗散功率为20W/c㎡,该电阻上的压降为5V,设计此电阻。

第4章TTL电路1.名词解释电压传输特性开门/关门电平逻辑摆幅过渡区宽度输入短路电流输入漏电流静态功耗瞬态延迟时间瞬态存储时间瞬态上升时间瞬态下降时间瞬时导通时间2. 分析四管标准TTL与非门(稳态时)各管的工作状态?3. 在四管标准与非门中,那个管子会对瞬态特性影响最大,并分析原因以及带来那些困难。

4. 两管与非门有哪些缺点,四管及五管与非门的结构相对于两管与非门在那些地方做了改善,并分析改善部分是如何工作的。

四管和五管与非门对静态和动态有那些方面的改进。

5. 相对于五管与非门六管与非门的结构在那些部分作了改善,分析改进部分是如何工作的。

6. 画出四管和六管单元与非门传输特性曲线。

并说明为什么有源泄放回路改善了传输特性的矩形性。

7. 四管与非门中,如果高电平过低,低电平过高,分析其原因,如与改善方法,请说出你的想法。

8. 为什么TTL与非门不能直接并联?9. OC门在结构上作了什么改进,它为什么不会出现TTL与非门并联的问题。

第5章MOS反相器1. 请给出NMOS晶体管的阈值电压公式,并解释各项的物理含义及其对阈值大小的影响(即各项在不同情况下是提高阈值还是降低阈值)。

2. 什么是器件的亚阈值特性,对器件有什么影响?3. MOS晶体管的短沟道效应是指什么,其对晶体管有什么影响?4. 请以PMOS晶体管为例解释什么是衬偏效应,并解释其对PMOS晶体管阈值电压和漏源电流的影响。

5. 什么是沟道长度调制效应,对器件有什么影响?6. 为什么MOS晶体管会存在饱和区和非饱和区之分(不考虑沟道调制效应)?7.请画出晶体管的D DS特性曲线,指出饱和区和I V非饱和区的工作条件及各自的电流方程(忽略沟道长度调制效应和短沟道效应)。

半导体集成电路练习题

半导体集成电路练习题一、基础知识类1. 填空题1.1 半导体材料主要包括________、________和________。

1.2 PN结的正向特性是指________,反向特性是指________。

1.3 MOS晶体管的三个工作区分别是________、________和________。

2. 判断题2.1 半导体集成电路的导电性能介于导体和绝缘体之间。

()2.2 N型半导体中的自由电子浓度高于P型半导体。

()2.3 CMOS电路具有静态功耗低的特点。

()二、数字电路类1. 选择题1.1 TTL与非门电路中,当输入端全部为高电平时,输出为()。

A. 高电平B. 低电平C. 不确定D. 无法判断A. 与门B. 或门C. 非门D. 异或门A. PMOS管导通时,NMOS管截止B. PMOS管截止时,NMOS管导通C. PMOS管和NMOS管同时导通D. PMOS管和NMOS管同时截止2. 填空题2.1 数字电路中的逻辑门主要有________、________、________和________等。

2.2 半加器是由________和________组成的。

2.3 全加器的三个输入端分别是________、________和________。

三、模拟电路类1. 选择题A. 非反相比例运算放大器B. 反相比例运算放大器C. 电压跟随器D. 差分放大器1.2 在运算放大器电路中,虚短是指________。

()A. 输入端短路B. 输出端短路C. 输入端与地之间短路D. 输入端与输出端之间短路A. 低通滤波器允许低频信号通过,抑制高频信号B. 高通滤波器允许低频信号通过,抑制高频信号C. 带通滤波器允许一定频率范围的信号通过D. 带阻滤波器允许一定频率范围的信号通过2. 填空题2.1 模拟信号的特点是________、________和________。

2.2 运算放大器的主要参数有________、________和________。

东南大学考研半导体物理基础(5)

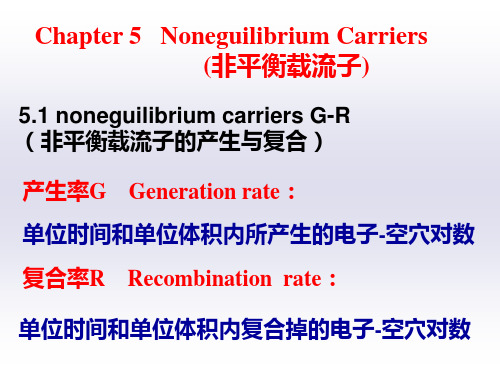

若外界条件撤除(如光照停止),经过一段时间后, 若外界条件撤除(如光照停止),经过一段时间后,系统才会 ),经过一段时间后 恢复到原来的热平衡状态。有的非子生存时间长、有的短。 恢复到原来的热平衡状态。有的非子生存时间长、有的短。非子的 平均生存时间——非子的寿命τ。 非子的寿命τ 平均生存时间 非子的寿命

大注入

∆p cn (n0 + n1 + ∆p) + cp ( p0 + p1 + ∆p) τ= = U Nt cncp (n0 + p0 + ∆p)

1 1 τ= + =τ p +τ n Nt cp Nt cn

3 其它复合

(1)表面复合 ) 半导体表面状态对非平衡载流子也有很大影响, 半导体表面状态对非平衡载流子也有很大影响,表 面处的杂质和表面特有的缺陷也在禁带形成复合中心。 面处的杂质和表面特有的缺陷也在禁带形成复合中心。 表面氧化层、水汽、杂质的污染、表面缺陷或损伤。 表面氧化层、水汽、杂质的污染、表面缺陷或损伤。

* 俘获电子 * 发射电子 * 俘获空穴 * 发射空穴

Electron capture Electron emission Hole capture Hole emission

电子俘获(capture)率: 电子俘获 电子产生( 电子产生 emission)率: 率 空穴俘获率: 空穴俘获率: 空穴产生率: 空穴产生率:

通过复合中心复合的普遍公式

n0∆p + p0∆p + ∆p U= 1 1 (n0 + n1 + ∆p) + ( p0 + p1 + ∆p) cp Nt cn Nt

2

非平衡载流子的寿命为

东南大学专用集成电路样卷

0 1 1 0 1 1 1

x1 x1 x1

Vdd D A

CLK

x2

C

B

x3

3)

5)在 10~20ns 期间:

VOUT CL VDD 1.125V ; C1 C L

x1

x2

6)

(用 Weinberger 结构)

VDD

X1 X2 X3

在 10~20ns 期间:

VOUT CL VDD 0.75V C1 C2 CL

2m VDD

图2 A CLK pocess(A,B,C,D,S,H) begin if S=? ' then X<=A+B; elseif H=? ' then X<=A+C; else X<=A+D; endif; end process; 图6

C

B

N

D t/ns 10 15 20

GND

P

金属 多晶硅

;

在 10~20ns 期间: VOUT 0V ;

X1X3

X2 X1X3+X2 Z=X1X3+X2

4

4) 1) 为 d=(2+6+2+6+1+2+2+8+2+2+1) =34。 t t f 1 t r1 (1 2.5) (4 4 2) 1 56 ps a b 2)集总电阻为:

10 16 10 R 27 ( ) 162 5 8 5 tbc tcd

0 1 1 0

t

X1

A A B f

C A

D

C B H

D

+

东南大学半导体物理考研复习系列试题(D卷)

决定迁移率的参数是有效质量和平均自由时间。有效质量是关于能带结构的一个重要 性质。有效质量是将晶体中 __________ 作用概括在其中,有效质量的引入,使得处 理晶体中的电子在 __________ 问题时忽略难以确定的晶格力,使问题简单化。对于

学号

GaAs ,导带底附近的曲率很大,因此导带电子的有效质量很小。有效质量增大,迁 移率 __________ ( “增加”或“减小” ) 。决定迁移率的另外一个重要因素是连续碰 撞间的平均自由时间,它主要与 __________ 和 __________ 有关。

3.(12分) 何谓漂移运动?何谓扩散运动?何谓迁移率、扩散系数?

共 9 页

第 3 页

(luobin 考研复习卷)

并说明温度及掺杂浓度对这两种散射 4.(12分) 简述常见掺杂半导体中两种主要散射机制, 机制的影响和原因。

5.(16分) 某种半导体与金属接触。

(1)解释欧姆接触和整流接触特性; (2) n 型半导体与金属形成整流接触,画出接触后 的能带图,解释接触后能带的形成过程; (3)为什么金-半二极管 (肖特基二极管) 消除了载 流子注入后的存储时间? (4)实际欧姆接触面临什么问题,怎样解决的? (5)下图是金属和轻掺杂半导体的能带图,画出接 触后的能带图, 包括费米能级、 在金属半导体界面 处通过 Wm、WS 、χ 或者 E g 表示出的价带偏移量和导带偏移量以及其他能带弯曲,定性 指出电荷耗尽区和积累区(设不存在界面缺陷) ,这是一个肖特基接触还是欧姆接触?

9 3

(4)求光照稳定时半导体的附加电导率及半导体准费米能级之差。

共 9 页

第 6 页

(luobin 考研复习卷)

电路考研考试题及答案

电路考研考试题及答案一、选择题(每题2分,共20分)1. 在电路中,电阻的单位是:A. 欧姆B. 安培C. 伏特D. 瓦特答案:A2. 根据基尔霍夫电压定律,沿着任何闭合路径,电压的代数和等于:A. 零B. 正无穷C. 负无穷D. 不确定答案:A3. 电流的参考方向可以是:A. 正向B. 反向C. 任意方向D. 只有正向答案:C4. 电感元件的伏安关系为:A. v = L(di/dt)B. i = C(dv/dt)C. v = R * iD. i = G * v5. 在理想变压器中,原边与副边的电压比与什么成正比:A. 匝数比B. 电流比C. 电阻比D. 电感比答案:A6. 电路的功率因数是:A. 有功功率与视在功率的比值B. 有功功率与无功功率的比值C. 无功功率与视在功率的比值D. 视在功率与无功功率的比值答案:A7. 一个电路的总电阻是10Ω,当串联一个5Ω的电阻后,总电阻变为:A. 5ΩB. 10ΩC. 15ΩD. 20Ω答案:C8. 电路中电流的瞬时值表达式为i(t) = 10sin(100πt),其频率为:A. 50HzB. 100HzC. 200HzD. 500Hz答案:A9. 在RLC串联电路中,当电感和电容的阻抗相等时,电路的总阻抗:B. 最小C. 不变D. 不确定答案:B10. 一个电路的总功率为100W,总电流为5A,总电压为:A. 20VB. 10VC. 50VD. 20V答案:C二、填空题(每题2分,共10分)1. 电路中的功率可以分为_______功率和_______功率。

答案:有功;无功2. 电路的总阻抗等于电阻与_______的平方和的平方根。

答案:电抗3. 电路的谐振频率可以通过公式_______计算。

答案:f = 1/(2π√(LC))4. 在电路中,当电流通过电阻时,会产生_______。

答案:热量5. 电路中,电流的相位与电压的相位之间的关系称为_______。

半导体集成电路习题及答案

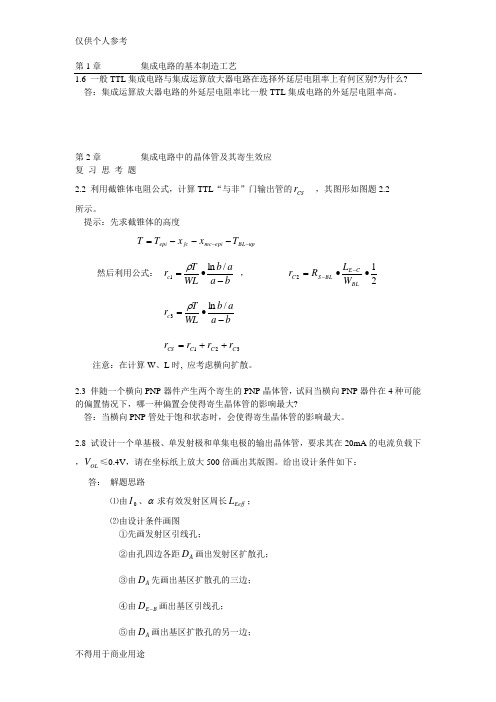

第1章 集成电路的基本制造工艺1.6 一般TTL 集成电路与集成运算放大器电路在选择外延层电阻率上有何区别?为什么? 答:集成运算放大器电路的外延层电阻率比一般TTL 集成电路的外延层电阻率高。

第2章 集成电路中的晶体管及其寄生效应 复 习 思 考 题2.2 利用截锥体电阻公式,计算TTL “与非”门输出管的CS r 2.2所示。

提示:先求截锥体的高度up BL epi m c jc epi T x x T T -----= 然后利用公式: ba ab WL Tr c -∙=/ln 1ρ ,212∙∙=--BL C E BL S C W L R r ba ab WLTr c -∙=/ln 3ρ 321C C C CS r r r r ++=注意:在计算W 、L 时, 应考虑横向扩散。

2.3 伴随一个横向PNP 器件产生两个寄生的PNP 晶体管,试问当横向PNP 器件在4种可能的偏置情况下,哪一种偏置会使得寄生晶体管的影响最大?答:当横向PNP 管处于饱和状态时,会使得寄生晶体管的影响最大。

2.8 试设计一个单基极、单发射极和单集电极的输出晶体管,要求其在20mA 的电流负载下 ,OL V ≤0.4V ,请在坐标纸上放大500倍画出其版图。

给出设计条件如下: 答: 解题思路⑴由0I 、α求有效发射区周长Eeff L ;⑵由设计条件画图①先画发射区引线孔;②由孔四边各距A D 画出发射区扩散孔; ③由A D 先画出基区扩散孔的三边; ④由B E D -画出基区引线孔; ⑤由A D 画出基区扩散孔的另一边;⑥由A D 先画出外延岛的三边; ⑦由C B D -画出集电极接触孔; ⑧由A D 画出外延岛的另一边; ⑨由I d 画出隔离槽的四周;⑩验证所画晶体管的CS r 是否满足V V O L 4.0≤的条件,若不满足,则要对所作的图进行修正,直至满足V V O L 4.0≤的条件。

(CS C O L r I V V 00ES += 及己知V V C 05.00ES =)第3章 集成电路中的无源元件 复 习 思 考 题3.3 设计一个4k Ω的基区扩散电阻及其版图。